半導体装置の製造方法、フラッシュメモリの製造方法、およびスタティックランダムアクセスメモリの製造方法ならびにフラッシュメモリ

【課題】同一のレジストパターンにより、ドライエッチングおよびウエットエッチングを連続的に行なう際に、変質したレジスト表面層を剥がれなくするように改良された、半導体装置の製造方法を提供することを主要な目的とする。

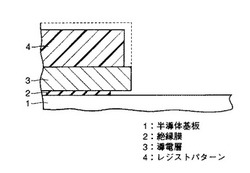

【解決手段】半導体基板1の上に、絶縁膜2と導電層3を順次形成する。導電層3の上にレジストパターン4を形成する。レジストパターン4をマスクに用いて、導電層3をドライエッチングする。レジストパターン4の表層部を一部削る。レジストパターン4をマスクに用いて、絶縁膜2をウエットエッチングする。

【解決手段】半導体基板1の上に、絶縁膜2と導電層3を順次形成する。導電層3の上にレジストパターン4を形成する。レジストパターン4をマスクに用いて、導電層3をドライエッチングする。レジストパターン4の表層部を一部削る。レジストパターン4をマスクに用いて、絶縁膜2をウエットエッチングする。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、一般に、半導体装置の製造方法に関するものであり、より特定的には、ドライエッチとウエットエッチを連続して行なう工程を含む半導体装置の製造方法に関する。この発明は、また、ドライエッチおよびウエットエッチを連続して行なう工程を含む、フラッシュメモリの製造方法に関する。この発明は、そのような製造方法により製造したフラッシュメモリに関する。この発明は、さらに、スタティックランダムアクセスメモリ(以下、SRAMと略する)の製造方法に関する。

【背景技術】

【0002】

図11は、従来のフラッシュメモリのメモリセルの断面図である。

図11を参照して、P型不純物を含む半導体基板1の表面中にP型不純物領域1aが形成されている。半導体基板1の上に、トンネル酸化膜3を介在させてフローティングゲート4が形成されている。P型不純物領域1aの表面中であって、フローティングゲート4の両側にソース/ドレイン領域2a,2bが形成されている。フローティングゲート4の上に絶縁膜8が形成されている。絶縁膜8の上にコントロールゲート9が形成されている。コントロールゲート9を覆うように、半導体基板1の上に絶縁層10,11が形成されている。

【0003】

次に、フラッシュメモリの動作について説明する。

書込動作においては、ドレイン領域2bに6〜8V程度のドレイン電圧を、コントロールゲート9に10〜15V程度のゲート電圧を印加する。ソース領域2aと半導体基板1の電位は接地電位に保たれる。このとき、チャネル領域2cには数百μAの電流が流れる。ソース領域2aからドレイン領域2bに流れた電子のうち、ドレイン領域2b近傍で加速された電子は、高エネルギを有する電子(ホットエレクトロン)となる。この電子は、コントロールゲート9に印加されたゲート電圧による電界のため、矢印12の方向に流れ、フローティングゲート4に注入される。フローティングゲート4に電子の蓄積が行なわれると、トランジスタのしきい値電圧が高くなる。このしきい値電圧が一定値よりも高くなった場合が“0”と呼ばれる状態である。

【0004】

次に、データ消去動作について説明する。まず、ソース領域2aに10〜15V程度のソース電圧を印加し、コントロールゲート9と半導体基板1は接地電位に保持する。次に、ドレイン領域2bをフローティングとし、ソース領域2aに印加するソース電圧による電界により、フローティングゲート4に蓄積されていた電子は、矢印13の方向に、トンネル絶縁膜3を通過して半導体基板1内に流れる。このようにしてフローティングゲート4内部に蓄積されていた電子が引抜かれることによって、トランジスタのしきい値が高くなる。このしきい値電圧が所定の値より低い状態が、“1”と呼ばれるデータを消去された状態である。この消去状態によって、同一半導体装置内に形成されたメモリセルの一括消去が可能となる。さらに、読出動作においては、コントロールゲート9に5V程度のゲート電圧を印加し、ドレイン領域2bに1〜2V程度のドレイン電圧を印加したときに、チャネル領域2cに電流が流れるかどうか、つまり、トランジスタがON状態かOFF状態かによってデータが“1”か“0”かの判定をするというものである。

【0005】

次に、上記のように構成されるフラッシュメモリの製造方法について説明する。

まず、図12を参照して、単結晶シリコンからなる半導体基板1上にメモリセル同士、周辺回路のトランジスタ同士およびセルと周辺トランジスタを分離する素子分離酸化膜を形成した後、メモリセルが形成されるP型不純物領域1aを形成した後、基板の上面を酸化し、二酸化シリコン(SiO2)からなるトンネル絶縁膜3を形成する。

【0006】

図13を参照して、トンネル絶縁膜3上に、CVD(Chemical Vapor Deposition)技術によって、多結晶シリコンを積層し、これをメモリセル領域のみX方向(紙面に向かって水平方向。図中では表示しない)にエッチングして、フローティングゲート4を形成する。次に、同様にCVD技術によって、絶縁膜8(たとえば、シリコン窒化(SiN)膜、シリコン酸化膜)を形成する。次に、周辺回路領域の絶縁膜8、上記多結晶シリコン、トンネル絶縁膜3を除去する。次に、多結晶シリコン(ポリシリコン)(フローティングゲート)4の形成と同じ要領で、CVD技術によって、コントロールゲート9となる多結晶シリコンを積層する。

【0007】

次に、図14を参照して、多結晶シリコンを形成した領域のうち、ゲート電極として残したい領域については、その上部にレジストパターン14をY方向(紙面に向かって垂直方向)に形成し、レジストパターン14をマスクとして、トンネル絶縁膜3の表面が露出するまで異方性エッチングを行なう。

【0008】

その後、レジストパターン14をプラズマアッシング等の方法を用いて除去する。

図15を参照して、矢印15の方向に沿って不純物イオンを注入し、P型不純物領域1aの上部にP型不純物領域1aよりも不純物濃度が大きなN型高濃度不純物領域(ソース/ドレイン領域)2a,2bの形成を行なう。その後、図11に戻って、CVD技術等を用いてシリコン酸化膜からなる絶縁層10,11を、保護膜として形成することで、フラッシュメモリが完成する。

【発明の概要】

【発明が解決しようとする課題】

【0009】

以上のように構成される半導体装置の製造方法の問題点について、簡略化した図面を用いて説明する。

【0010】

図16を参照して、シリコン基板1の上に、SiO2膜2を形成する。SiO2膜2の上に、ポリシリコン膜3を堆積する。ポリシリコン膜3の上に、写真製版により、レジストパターン4を形成する。レジストパターン4をマスクにして、ポリシリコン膜3をドライエッチングし、続いて、連続的にSiO2膜2を、フッ酸(HF)液によりエッチングする。

【0011】

このとき、図17を参照して、フッ酸液で処理する際に、ポリシリコン膜3のドライエッチング時に、変質した、レジストパターン4の表面層5が剥がれる。剥がれたレジスト表面層5がシリコン基板1の上に再付着し、この剥がれたレジスト表面層5の下のSiO2膜2のエッチングが阻害されるという問題点があった。また、剥がれたレジスト表面層5が、フッ酸処理槽中に流出し、異物として槽を汚染するという問題点があった。

【0012】

そして、ポリシリコンエッチングを、塩素(Cl)系のガスを使って行なった場合に、特にこのような問題が発生しやすかった。

【0013】

また、ポリシリコン膜の上に絶縁膜、たとえばSiO2膜、SiN膜が堆積されている場合に、SiO2/SiN膜をドライエッチングし、ポリシリコン膜をドライエッチングし、次に、SiO2膜をフッ酸液でウエットエッチングするという連続処理を行なうと、一層このような問題が発生しやすかった。

【0014】

この発明は、上記のような問題点を解決するためになされたもので、レジストパターンの表面変質層が剥がれることを防止することができるように改良された半導体装置の製造方法を提供することにある。

【0015】

この発明の他の目的は、レジストパターンの表面変質層が剥がれないように改良された、フラッシュメモリの製造方法を提供することにある。

【0016】

この発明の他の目的は、レジストパターンの表面変質層が剥がれないように改良された、スタティックランダムアクセスメモリの製造方法の製造方法を提供することにある。

【課題を解決するための手段】

【0017】

請求項1に係る半導体装置の製造方法においては、まず、半導体基板の上に絶縁膜と導電層を順次形成する。このときの形成は、成膜のみで形成してもよいし、成膜後にパターニングを行なって形成してもよい(第1工程)。上記導電層の上にレジストパターンを形成する(第2工程)。上記レジストパターンをマスクに用いて、上記導電層をドライエッチングする(第3工程)。上記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする(第4工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をウエットエッチングする(第5工程)。

【0018】

この発明によれば、レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけるので、これらが剥がれなくなる。

【0019】

請求項2に係る半導体装置の製造方法においては、上記第4工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後熱処理する工程を含む。

【0020】

請求項3に係る半導体装置の製造方法においては、上記第4工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0021】

請求項4に係る半導体装置の製造方法においては、上記第4工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することによって行なう。

【0022】

請求項5に係るフラッシュメモリは、半導体基板を備える。上記半導体基板の上にダミーゲート領域が設けられている。上記半導体基板の上に、上記ダミーゲート領域を挟むようにメモリセル領域と周辺回路領域が設けられている。上記ダミーゲート領域は、上記半導体基板の上に形成された分離酸化膜を含む。上記分離酸化膜の上に、その周辺回路領域側の端部が上記メモリセル領域側に後退した第1導電層が設けられている。上記第1導電層の上に、その周辺回路領域側の端部が上記メモリセル領域側に後退した絶縁層が設けられている。上記分離酸化膜の上に、上記第1導電層および上記絶縁層を覆うように、第2導電層が設けられている。

【0023】

請求項6に係る半導体装置の製造方法においては、まず、半導体基板の上に絶縁膜と導電層を順次形成する(第1工程)。第2の絶縁膜を形成する(第2工程)。上記第2の絶縁膜の上にレジストパターンを形成する(第3工程)。上記レジストパターンをマスクに用いて、上記第2の絶縁膜と上記導電層をドライエッチングする(第4工程)。上記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする(第5工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をウエットエッチングする(第6工程)。

【0024】

請求項7に係る半導体装置の製造方法においては、上記第5工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0025】

請求項8に係る半導体装置の製造方法においては、上記第5工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0026】

請求項9に記載の半導体装置の製造方法においては、上記第5工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【0027】

請求項10に係るフラッシュメモリの製造方法においては、まず、半導体基板の表面に、メモリセル領域と周辺回路領域を分離する分離酸化膜を形成する(第1工程)。上記半導体基板の表面上にトンネル酸化膜を形成する(第2工程)。上記トンネル酸化膜の上に第1ポリシリコン層を形成する(第3工程)。上記トンネル酸化膜と上記第1ポリシリコン層を所望の形にパターニングする(第4工程)。上記第1ポリシリコン層の上に絶縁膜を形成する(第5工程)。上記絶縁膜の上に、その端部が分離酸化膜上に位置し、かつ上記メモリセル領域のみを覆う、レジストパターンを形成する(第6工程)。上記レジストパターンをマスクに用いて、上記周辺回路領域の上にある、上記絶縁膜および上記第1ポリシリコン層をドライエッチングにより除去する(第7工程)。上記レジストパターンの表面変質層と、該レジストパターンの表面より下にある正常な部分をくっつけ、これらを剥がれなくする(第8工程)。上記レジストパターンを再びマスクに用いて、上記周辺回路領域の上にある上記トンネル酸化膜をウエットエッチングにより除去する(第9工程)。上記レジストパターンを除去する(第10工程)。上記半導体基板の上であって、上記周辺回路領域の上に、周辺トランジスタ用のゲート酸化膜を形成する(第11工程)。上記半導体基板の上に第2ポリシリコン層を形成する(第12工程)。上記第2ポリシリコン層の上に、エッチングマスク用の酸化膜を形成する(第13工程)。上記メモリセル領域にコントロールゲートを形成し、周辺回路のトランジスタゲートを形成する(第14工程)。上記絶縁膜および上記第1ポリシリコン層をパターニングし、フローティングゲートを形成する(第15工程)。

【0028】

請求項11に係るフラッシュメモリの製造方法においては、上記第8工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む。

【0029】

請求項12に係るフラッシュメモリの製造方法においては、上記第8工程は乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む。

【0030】

請求項13に係るフラッシュメモリの製造方法においては、上記第8工程は乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【0031】

請求項14に係るSRAMの製造方法においては、まず、半導体基板の表面に、分離酸化膜を形成する(第1工程)。上記半導体基板上にゲート酸化膜を成膜する(第2工程)。上記ゲート酸化膜上に第1ポリシリコン層を成膜する(第3工程)。活性領域から分離酸化膜上に及ぶような開口部を有するレジストパターンを形成する(第4工程)。上記レジストパターンをマスクとして、上記第1ポリシリコン層をドライエッチングにより除去する(第5工程)。上記レジストパターンの表面の変質層と表面より下にある正常な部分をくっつけ、これらを剥がれなくする(第6工程)。上記レジストパターンを再びマスクに用いて、パターン底のゲート酸化膜をウエットエッチングにより除去する(第7工程)。上記レジストパターンを除去する(第8工程)。第2ポリシリコン層を形成する(第9工程)。アクセストランジスタ、ドライバトランジスタ、周辺回路のトランジスタのゲート電極となるパターンをレジストにて形成する(第10工程)。上記レジストパターンをマスクとして、第1ポリシリコン層、第2ポリシリコン層をドライエッチングする(第11工程)。上記レジストパターンを除去する(第12工程)。n領域のみにn型不純物をドーピングする(第13工程)。熱処理を行なう(第14工程)。

【0032】

請求項15に記載のSRAMの製造方法においては、上記第6工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0033】

請求項16に係るSRAMの製造方法においては、上記第6工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0034】

請求項17に記載のSRAMの製造方法においては、上記第6工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【0035】

その他、本発明の半導体装置の製造方法においては、まず、半導体基板の上に、絶縁膜と導電層を順次形成する。このときの形成は、成膜のみでも、成膜後にパターニングを行なうの、どちらにも対応する(第1工程)。上記導電層の上にレジストパターンを形成する(第2工程)。上記レジストパターンをマスクに用いて、上記導電層をドライエッチングする(第3工程)。上記レジストパターンの表層部を一部削る(第4工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をエッチングする。

【0036】

この発明によれば、レジストパターンの表層部を一部削るので、変質したレジストパターンの表面が除去される。

【0037】

本発明の半導体装置の製造方法においては、上記第4工程を、O2プラズマを用いるエッチングにより行なう。

【0038】

本発明の半導体装置の製造方法においては、上記第3工程におけるドライエッチングを、O2を混入したガスを用いて行ない、それによって、上記第4工程を、上記導電層のドライエッチングのシークエンスの中で行なう。

【0039】

本発明の半導体装置の製造方法においては、まず、半導体基板の上に絶縁膜と導電層を順次形成する。このときの形成は、成膜のみで形成してもよいし、成膜後にパターニングを行なって形成してもよい(第1工程)。上記導電層の上にレジストパターンを形成する(第2工程)。上記レジストパターンをマスクに用いて、上記導電層をドライエッチングする(第3工程)。上記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする(第4工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をエッチングする(第5工程)。

【0040】

この発明によれば、レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけるので、これらが剥がれなくなる。

【0041】

本発明の半導体装置の製造方法においては、上記第4工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後熱処理する工程を含む。

【0042】

本発明の半導体装置の製造方法においては、上記第4工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0043】

本発明の半導体装置の製造方法においては、上記第4工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することによって行なう。

【0044】

本発明のフラッシュメモリの製造方法においては、まず、半導体基板の表面に、メモリセル領域と周辺回路領域を分離する分離酸化膜を形成する(第1工程)。上記半導体基板の表面上にトンネル酸化膜を形成する(第2工程)。上記トンネル酸化膜の上に第1ポリシリコン層を形成する(第3工程)。上記トンネル酸化膜と上記第1ポリシリコン層を所望の形にパターニングする(第4工程)。上記第1ポリシリコン層の上に絶縁膜を形成する(第5工程)。上記絶縁膜の上に、その端部が分離酸化膜上に位置し、かつ上記メモリセル領域のみを覆う、レジストパターンを形成する(第6工程)。上記レジストパターンをマスクに用いて、上記周辺回路領域の上にある、上記絶縁膜および上記第1ポリシリコン層をドライエッチングにより除去する(第7工程)。上記レジストパターンの表層部を一部削る(第8工程)。上記レジストパターンを再びマスクに用いて、上記周辺回路領域の上にある上記トンネル酸化膜を除去する(第9工程)。上記レジストパターンを除去する(第10工程)。上記半導体基板の上であって、上記周辺回路領域の上に、周辺トランジスタ用のゲート酸化膜を形成する(第11工程)。上記半導体基板の上に第2ポリシリコン層を形成する(第12工程)。上記第2ポリシリコン層の上に、エッチングマスク用の酸化膜を形成する(第13工程)。上記メモリセル領域にコントロールゲートを形成し、周辺回路のトランジスタゲートを形成する(第14工程)。上記絶縁膜および上記第1ポリシリコン層をパターニングし、フローティングゲートを形成する(第15工程)。

【0045】

この発明によれば、レジストパターンの表層部を一部削るので、レジストパターンの表面変質層が除去される。

【0046】

本発明のフラッシュメモリは、半導体基板を備える。上記半導体基板の上にダミーゲート領域が設けられている。上記半導体基板の上に、上記ダミーゲート領域を挟むようにメモリセル領域と周辺回路領域が設けられている。上記ダミーゲート領域は、上記半導体基板の上に形成された分離酸化膜を含む。上記分離酸化膜の上に、その周辺回路領域側の端部が上記メモリセル領域側に後退した第1導電層が設けられている。上記第1導電層の上に、その周辺回路領域側の端部が上記メモリセル領域側に後退した絶縁層が設けられている。上記分離酸化膜の上に、上記第1導電層および上記絶縁層を覆うように、第2導電層が設けられている。

【0047】

本発明の半導体装置の製造方法においては、上記の製法において、上記導電層はポリシリコン膜であり、上記ドライエッチングは塩素ガスを用いて行なわれる。

【0048】

本発明のフラッシュメモリの製造方法においては、上記フラッシュメモリの製造方法の第6工程におけるドライエッチングを、塩素ガスを用いて行なう。

【0049】

本発明の半導体装置の製造方法においては、まず半導体基板の上に絶縁膜と導電層を順次形成する(第1工程)。第2の絶縁膜を形成する(第2工程)。上記第2の絶縁膜の上にレジストパターンを形成する(第3工程)。上記レジストパターンをマスクに用いて、上記第2の絶縁膜と導電層をドライエッチングする(第4工程)。上記レジストパターンの表層部を一部削る(第5工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をエッチングする(第6工程)。

【0050】

本発明の半導体装置の製造方法においては、上記第5工程を、O2プラズマを用いるエッチングにより行なう。

【0051】

本発明の半導体装置の製造方法においては、上記第4工程におけるドライエッチングをO2を混入したガスを用いて行ない、それによって、上記第5工程を、上記導電層のドライエッチングのシークエンスの中で行なう。

【0052】

本発明の半導体装置の製造方法においては、まず、半導体基板の上に絶縁膜と導電層を順次形成する(第1工程)。第2の絶縁膜を形成する(第2工程)。上記第2の絶縁膜の上にレジストパターンを形成する(第3工程)。上記レジストパターンをマスクに用いて、上記第2の絶縁膜と上記導電層をドライエッチングする(第4工程)。上記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする(第5工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をエッチングする(第6工程)。

【0053】

本発明の半導体装置の製造方法においては、上記第5工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0054】

本発明の半導体装置の製造方法においては、上記第5工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0055】

本発明の半導体装置の製造方法においては、上記第5工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【0056】

本発明のフラッシュメモリの製造方法においては、まず、半導体基板の表面に、メモリセル領域と周辺回路領域を分離する分離酸化膜を形成する(第1工程)。上記半導体基板の表面上にトンネル酸化膜を形成する(第2工程)。上記トンネル酸化膜の上に第1ポリシリコン層を形成する(第3工程)。上記トンネル酸化膜と上記第1ポリシリコン層を所望の形にパターニングする(第4工程)。上記第1ポリシリコン層の上に絶縁膜を形成する(第5工程)。上記絶縁膜の上に、その端部が分離酸化膜上に位置し、かつ上記メモリセル領域のみを覆う、レジストパターンを形成する(第6工程)。上記レジストパターンをマスクに用いて、上記周辺回路領域の上にある、上記絶縁膜および上記第1ポリシリコン層をドライエッチングにより除去する(第7工程)。上記レジストパターンの表層部を、一部削ることをO2プラズマを用いるエッチングにより行なう(第8工程)。上記レジストパターンを再びマスクに用いて、上記周辺回路領域の上にある上記トンネル酸化膜を除去する(第9工程)。上記レジストパターンを除去する(第10工程)。上記半導体基板の上であって、上記周辺回路領域の上に、周辺トランジスタ用のゲート酸化膜を形成する(第11工程)。上記半導体基板の上に第2ポリシリコン層を形成する(第12工程)。上記第2ポリシリコン層の上に、エッチングマスク用の酸化膜を形成する(第13工程)。上記メモリセル領域にコントロールゲートを形成し、周辺回路のトランジスタゲートを形成する(第14工程)。上記絶縁膜および上記第1ポリシリコン層をパターニングし、フローティングゲートを形成する(第15工程)。

【0057】

本発明のフラッシュメモリの製造方法においては、上記第7工程のドライエッチングをO2を混入したガスを用いて行ない、上記第8工程のレジストパターンの表層部を一部削ることをドライエッチングのシークエンス中で行なうことを特徴とする。

【0058】

本発明のフラッシュメモリの製造方法においては、まず、半導体基板の表面に、メモリセル領域と周辺回路領域を分離する分離酸化膜を形成する(第1工程)。上記半導体基板の表面上にトンネル酸化膜を形成する(第2工程)。上記トンネル酸化膜の上に第1ポリシリコン層を形成する(第3工程)。上記トンネル酸化膜と上記第1ポリシリコン層を所望の形にパターニングする(第4工程)。上記第1ポリシリコン層の上に絶縁膜を形成する(第5工程)。上記絶縁膜の上に、その端部が分離酸化膜上に位置し、かつ上記メモリセル領域のみを覆う、レジストパターンを形成する(第6工程)。上記レジストパターンをマスクに用いて、上記周辺回路領域の上にある、上記絶縁膜および上記第1ポリシリコン層をドライエッチングにより除去する(第7工程)。上記レジストパターンの表面変質層と、該レジストパターンの表面より下にある正常な部分をくっつけ、これらを剥がれなくする(第8工程)。上記レジストパターンを再びマスクに用いて、上記周辺回路領域の上にある上記トンネル酸化膜を除去する(第9工程)。上記レジストパターンを除去する(第10工程)。上記半導体基板の上であって、上記周辺回路領域の上に、周辺トランジスタ用のゲート酸化膜を形成する(第11工程)。上記半導体基板の上に第2ポリシリコン層を形成する(第12工程)。上記第2ポリシリコン層の上に、エッチングマスク用の酸化膜を形成する(第13工程)。上記メモリセル領域にコントロールゲートを形成し、周辺回路のトランジスタゲートを形成する(第14工程)。上記絶縁膜および上記第1ポリシリコン層をパターニングし、フローティングゲートを形成する(第15工程)。

【0059】

本発明のフラッシュメモリの製造方法においては、上記第8工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む。

【0060】

本発明のフラッシュメモリの製造方法においては、上記第8工程は乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む。

【0061】

本発明のフラッシュメモリの製造方法においては、上記第8工程は乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【0062】

本発明のSRAMの製造方法においては、まず、半導体基板の表面に、分離酸化膜を形成する(第1工程)。上記半導体基板上にゲート酸化膜を成膜する(第2工程)。上記ゲート酸化膜上に第1ポリシリコン層を成膜する(第3工程)。活性領域から分離酸化膜上に及ぶような開口部を有するレジストパターンを形成する(第4工程)。上記レジストパターンをマスクとして、上記第1ポリシリコン層をドライエッチングにより除去する(第5工程)。上記レジストパターンの表層部を一部削る(第6工程)。上記レジストパターンを再びマスクに用いて、パターン底のゲート酸化膜を除去する(第7工程)。上記レジストパターンを除去する(第8工程)。上記第2ポリシリコン層を形成する(第9工程)。アクセストランジスタ、ドライバトランジスタ、周辺回路のトランジスタのゲート電極となるパターンをレジストにて形成する(第10工程)。上記レジストパターンをマスクとして、上記第1ポリシリコン層、上記第2ポリシリコン層をドライエッチングする(第11工程)。上記レジストパターンを除去する(第12工程)。n領域のみにn型不純物をドーピングする(第13工程)。熱処理を行なう(第14工程)。

【0063】

本発明のSRAMの製造方法においては、上記第6工程をO2プラズマを用いたエッチングにより行なう。

【0064】

本発明のSRAMの製造方法においては、上記第5工程において、ドライエッチングにO2を混入したガスを用いて行ない、上記第6工程のレジストパターンの表層部を一部削ることをドライエッチングのシークエンス中で行なう。

【0065】

本発明のSRAMの製造方法においては、まず、半導体基板の表面に、分離酸化膜を形成する(第1工程)。上記半導体基板上にゲート酸化膜を成膜する(第2工程)。上記ゲート酸化膜上に第1ポリシリコン層を成膜する(第3工程)。活性領域から分離酸化膜上に及ぶような開口部を有するレジストパターンを形成する(第4工程)。上記レジストパターンをマスクとして、上記第1ポリシリコン層をドライエッチングにより除去する(第5工程)。上記レジストパターン表面の変質層と表面より下にある正常な部分をくっつけ、これらを剥がれなくする(第6工程)。上記レジストパターンを再びマスクに用いて、パターン底のゲート酸化膜を除去する(第7工程)。上記レジストパターンを除去する(第8工程)。第2ポリシリコン層を形成する(第9工程)。アクセストランジスタ、ドライバトランジスタ、周辺回路のトランジスタのゲート電極となるパターンをレジストにて形成する(第10工程)。上記レジストパターンをマスクとして、第1ポリシリコン層、第2ポリシリコン層をドライエッチングする(第11工程)。上記レジストパターンを除去する(第12工程)。n領域のみにn型不純物をドーピングする(第13工程)。熱処理を行なう(第14工程)。

【0066】

本発明のSRAMの製造方法においては、上記第6工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0067】

本発明のSRAMの製造方法においては、上記第6工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0068】

本発明のSRAMの製造方法においては、上記第6工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【図面の簡単な説明】

【0069】

【図1】実施の形態1に係る製造方法を説明するための、半導体装置の断面図である。

【図2】実施の形態5に係る半導体装置の製造方法の順序の第1の工程における半導体装置の断面図である。

【図3】実施の形態5に係る半導体装置の製造方法の順序の第2の工程における半導体装置の断面図である。

【図4】実施の形態5に係る半導体装置の製造方法の順序の第3の工程における半導体装置の断面図である。

【図5】実施の形態10に係るフラッシュメモリの製造方法により製造した半導体装置の断面図である。

【図6】実施の形態10に係るフラッシュメモリの製造方法の順序の第1の工程における半導体装置の断面図である。

【図7】実施の形態10に係るフラッシュメモリの製造方法の順序の第2の工程における半導体装置の断面図である。

【図8】実施の形態10に係るフラッシュメモリの製造方法の順序の第3の工程における半導体装置の断面図である。

【図9】実施の形態10に係る半導体装置の製造方法の順序の第4の工程における半導体装置の断面図である。

【図10】実施の形態10に係る半導体装置の製造方法の順序の第5の工程における半導体装置の断面図である。

【図11】従来のフラッシュメモリのメモリセルの断面図である。

【図12】従来のフラッシュメモリの製造方法の順序の第1の工程における半導体装置の断面図である。

【図13】従来のフラッシュメモリの製造方法の順序の第2の工程における半導体装置の断面図である。

【図14】従来のフラッシュメモリの製造方法の順序の第3の工程における半導体装置の断面図である。

【図15】従来のフラッシュメモリの製造方法の順序の第4の工程における半導体装置の断面図である。

【図16】従来の半導体装置の製造方法の問題点を示す第1の工程における半導体装置の断面図である。

【図17】従来の半導体装置の製造方法の問題点を示す第2の工程における半導体装置の断面図である。

【図18】実施の形態3に係る方法を説明するための半導体装置の断面図である。

【図19】実施の形態7に係る製造方法の順序の第1の工程における半導体装置の断面図である。

【図20】実施の形態7に係る製造方法の順序の第2の工程における半導体装置の断面図である。

【図21】実施の形態7に係る製造方法の順序の第3の工程における半導体装置の断面図である。

【図22】高抵抗負荷型SRAMメモリセルの等価回路図である。

【図23】実施の形態11に係る方法の製造方法の順序の第1の工程における半導体装置の断面図である。

【図24】実施の形態11に係る方法の製造方法の順序の第2の工程における半導体装置の断面図である。

【図25】実施の形態11に係る方法の製造方法の順序の第3の工程における半導体装置の断面図である。

【発明を実施するための形態】

【0070】

本発明の実施の形態は、写真製版−ポリシリコンドライエッチング−HF液ウエットエッチングを、連続的に行なうまたは写真製版−シリコン酸化膜ドライエッチング−ポリシリコンドライエッチング−HF液ウエットエッチングを連続的に行なう、という工程を含む半導体装置の製造方法のすべてについて適用される。以下、実施の形態を図について説明する。

【0071】

実施の形態1

図1を参照して、シリコン基板1の上にSiO2膜2を形成する。SiO2膜2の上にポリシリコン膜3を形成する。このときの形成は、成膜のみでも、成膜後にパターニングを行なうのどちらにも対応する。ポリシリコン膜3の上にレジストパターン4を形成する。レジストパターン4をマスクにして、ポリシリコン膜3をエッチングする。その後、O2プラズマ処理(アッシング処理)を行なう。O2プラズマ処理は、ポリシリコン膜3のエッチングのシークエンス中、または別装置で行なわれる。レジストパターン4の表面を、約10nm除去した後、レジストパターン4をマスクにして、SiO2膜2の、HF液処理を行なう。本発明の実施の形態によれば、O2プラズマ処理により、レジストパターン4の表層部を一部除去しているので、図17に示す従来方法によって生じた問題点は解消される。すなわち、剥がれたレジスト表面変質層がSiO2膜2のエッチングを妨げるという問題は生じない。なお、HF液処理の前に、レジストパターン4が、元のパターンの位置より後退している(点線で示した分だけ水平方向に後退している)が、問題は生じない。

【0072】

実施の形態2

本実施の形態も、変質レジストを除去する目的で行なわれる。本実施の形態では、ポリシリコンのエッチングのシークエンスの中で、変質レジストの除去が行なわれる。すなわち、ポリシリコン膜のメインエッチ、オーバーエッチング後に、O2を混入したエッチングを行なう。たとえば、次のようなエッチングシークエンスで行なう。

【0073】

メインエッチング→Cl2ガスを用いるオーバーエッチング→Cl2+O2ガスを用いる後処理

この場合は、O2プラズマ処理とは異なるため、レジストパターンの後退は少なくなる。なお、O2ガスを混入したエッチングは、オーバーエッチングの途中から行なってもよい。

【0074】

実施の形態3

図18を参照して、シリコン基板1の上にSiO2膜2を形成する。SiO2膜2の上にポリシリコン膜3を形成する。このときの形成は成膜のみでも、成膜後にパターニングを行なうのどちらにも対応する。その後、第2の絶縁膜7を成膜後、第2の絶縁膜7の上に、レジストパターン4を形成する。レジストパターン4をマスクにして、第2の絶縁膜7とポリシリコン膜3をエッチングする。その後、O2プラズマ処理(アッシング処理)を行なう。O2プラズマ処理は、ポリシリコン膜3のエッチングのシークエンス中、または別装置で行なわれる。レジストパターン4の表面を、約10nm除去した後、レジストパターン4をマスクにして、SiO2膜2の、HF液処理を行なう。本発明の実施の形態によれば、O2プラズマ処理により、レジストパターン4の表層部を一部除去しているので、図17に示す従来方法によって生じた問題点は解消される。すなわち、剥がれたレジスト表面変質層がSiO2膜2のエッチングを妨げるという問題は生じない。なお、HF液処理の前に、レジストパターン4が、元のパターンの位置より後退している(点線で示した分だけ水平方向に後退している)が、問題は生じない。

【0075】

実施の形態4

本実施の形態も、変質レジストを除去する目的で行なわれる。本実施の形態では、第2の絶縁膜7のエッチング後、ポリシリコンのエッチングのシークエンスの中で、変質レジストの除去が行なわれる。すなわち、ポリシリコン膜のメインエッチ、オーバエッチング後に、O2を混入したエッチングを行なう。たとえば、次のようなエッチングシークエンスで行なう。

【0076】

メインエッチング→Cl2ガスを用いるオーバエッチング→Cl2+O2ガスを用いる後処理

この場合は、O2プラズマ処理とは異なるため、レジストパターンの後退は少なくなる。なお、O2ガスを混入したエッチングは、オーバエッチングの途中から行なってもよい。

【0077】

実施の形態5

本実施の形態は、変質した表面レジストを硬化することによって、変質部の剥がれを防止するものである。

【0078】

図2を参照して、シリコン基板1の上にSiO2膜2を形成する。SiO2膜2の上にポリシリコン膜3を形成する。ポリシリコン膜3の上に、レジストパターン4を形成する。レジストパターン4をマスクにして、ポリシリコン膜3をエッチングする。このとき、レジストパターン4の表面が変質する。図中、6は、変質したレジスト表面層を表わしている。

【0079】

図3を参照して、変質したレジスト表面層6を硬化するために、レジスト表面層6をN2雰囲気中で、ディープ紫外線キュア(以下、DUVキュア処理と略す)する。具体的には、波長約250nm〜600nmの光を、レジストパターン4に100秒間照射し、シリコン基板1の載っているステージを約100℃〜150℃まで昇温する。本実施の形態によれば、DUV光で、変質した表面レジスト層6と下の正常なレジスト層4の感光基を分解し、これらを交わらせる。図中7は、交わってできた層を表わしている。

【0080】

図4を参照して、この状態で、熱処理を行ない、変質層6を下の正常なレジスト層4とくっつける。これによって、変質したレジスト表面層6の剥がれを防止できる。また、DUVキュア処理によって、波長の短い光がレジスト表面層6に照射されるので、表面の残留エッチングガスが化学反応により除去されるという効果も生じ、残留ガスの悪影響が除去される。本実施の形態に係る工程を要約すると、次のとおりである。

【0081】

ポリシリコンエッチ→DUVキュア(N2雰囲気)→HF液ウエットエッチング

実施の形態6

本実施の形態は、実施の形態3の変形例である。N2雰囲気の代わりに、Dry Air(乾燥空気)雰囲気中で、DUVキュア処理を行なう。この処理を行なうと、レジストの表面変質層と下の正常なレジスト層を交わらせて、これらを硬化するだけでなく、変質層が、Dry Air中のO2と、DUV光により発生するO3(オゾン)とにより、数nm程度、除去されるという新たな効果が生じる。

【0082】

本実施の形態の工程を要約すれば、次のとおりである。

ポリシリコンエッチ→DUVキュア(Dry Air雰囲気)→HF液ウエットエッチング

実施の形態7

本実施の形態は、変質した表面レジストを硬化することによって、変質部の剥がれを防止するものである。

【0083】

図19を参照して、シリコン基板1の上にSiO2膜2を形成する。SiO2膜2の上にポリシリコン膜3を形成する。このときの形成は成膜のみでも、成膜後にパターニングを行なうのどちらにも対応する。その後、第2の絶縁膜7を成膜後、第2の絶縁膜7の上に、レジストパターン4を形成する。レジストパターン4をマスクにして、第2の絶縁膜7とポリシリコン膜3をエッチングする。このとき、レジストパターン4の表面が変質する。図中、6は、変質したレジスト表面層を表わしている。

【0084】

図20を参照して、変質したレジスト表面層6を硬化するために、レジスト表面層6をN2雰囲気中で、ディープ紫外線キュア(以下、DUVキュア処理と略する)する。具体的には、波長約250nm〜600nmの光を、レジストパターン4に100秒間照射し、シリコン基板1の載っているステージを約100℃〜150℃まで昇温する。本実施の形態によれば、DUV光で、変質した表面レジスト層6と下の正常なレジスト層4の感光基を分解し、これらを交わらせる。図中7は、交わってできた層を表わしている。

【0085】

図21を参照して、この状態で、熱処理を行ない、変質層6を下の正常なレジスト層4とくっつける。これによって、変質したレジスト表面層6の剥がれを防止できる。また、DUVキュア処理によって、波長の短い光がレジスト表面層6に照射されるので、表面の残留エッチングガスが化学反応により除去されるという効果も生じ、残留ガスの悪影響が除去される。本実施の形態に係る工程を要約すると、次のとおりである。

【0086】

ポリシリコンエッチ→DUVキュア(N2雰囲気)→HF液ウエットエッチング

実施の形態8

本実施の形態は、実施の形態7の変形例である。N2雰囲気の代わりに、Dry Air(乾燥空気)雰囲気中で、DUVキュア処理を行なう。この処理を行なうと、レジストの表面変質層と下の正常なレジスト層を交わらせて、これらを硬化するだけでなく、変質層が、Dry Air中のO2と、DUV光により発生するO3(オゾン)とにより、数nm程度、除去されるという新たな効果が生じる。

【0087】

本実施の形態の工程を要約すれば、次のとおりである。

ポリシリコンエッチ→DUVキュア(Dry Air雰囲気)→HF液ウエットエッチング

実施の形態9

本実施の形態も、実施の形態5と7の変形例である。本実施の形態ではDUVキュアを行なわず、ウェハをDry Air雰囲気で満たされたオーブン中で、たとえば150℃で、1時間、ベーキングする。変質層と下層の正常層の交わる効果は少ないが、変質層と下層の正常層が、接している部分で、硬化する際に、これらがつながることが期待できる。

【0088】

本実施の形態の工程を要約すれば次のとおりである。

ポリシリコンエッチング→オーブン処理(150℃,1時間,Dry Air)→HF液ウエットエッチング

実施の形態10

本実施の形態は、上述した発明を、実際の半導体装置に適用したものである。本実施の形態では、2層スタックトポリシリコン膜によりセルを形成する、フラッシュメモリの製造方法について述べる。

【0089】

図5は、実施の形態10に係る方法によって製造したフラッシュメモリの断面図である。フラッシュメモリは、半導体基板1を備える。半導体基板1の上にダミーゲート14を含むダミーゲート領域が設けられている。半導体基板の上に、ダミーゲート領域を挟むようにメモリセル領域と周辺回路領域が設けられている。ダミーゲート領域は、半導体基板1の上に形成された分離酸化膜8を含む。分離酸化膜8の上に、第1導電層10が設けられている。第1導電層10の周辺回路領域側の端部10aはメモリセル領域側に後退している。第1導電層10の上に絶縁層11が設けられている。絶縁層11の周辺回路領域側の端部11aはメモリセル領域側に後退している。分離酸化膜8の上に、第1導電層10および絶縁層11を覆うように、第2導電層13が設けられている。

【0090】

図5を参照して、メモリセルでは、フローティングゲート、ポリ−ポリ絶縁膜が必要だが、周辺回路では、これらの膜は不要である。

【0091】

以下、図5に示すフラッシュメモリの製造方法について説明する。

図6を参照して、半導体基板1の上に、分離酸化膜8とトンネル酸化膜9を形成する。その後、半導体基板1の上に第1ポリシリコン層(フローティングゲートになるもの)10をX方向(紙面に向かって水平方向。図中では表示しない)にエッチング後、ポリ−ポリ絶縁膜11を形成する。

ポリ−ポリ絶縁膜11の上に、その端部が分離酸化膜8上に位置し、かつメモリセル領域のみを覆う、レジストパターン15を、写真製版処理によって形成する。

【0092】

次に、図7を参照して、CCl4あるいはCHCl3などのフロロカーボン系のエッチングガスを用いて、レジストパターン15をマスクにし、ポリ−ポリ絶縁膜11をエッチングし、次に第1ポリシリコン層10をエッチングする。

【0093】

この後、連続して、トンネル酸化膜9をHF液でエッチングすると、レジスト表面の変質層が剥がれるため、上述した実施の形態1−9の方法をここで適用する。すなわち、レジストパターン15の表面の変質層を除去するか、あるいは、変質層とその下にある正常なレジスト層とをくっつけ、レジスト表面の変質層が剥がれるのを防止する。

【0094】

次に、そのような処理を行なった後、レジストパターン15をマスクにして、周辺回路領域のトンネル酸化膜9のエッチング除去を行なう。本発明の実施の形態では、上記実施の形態1または2を適用している。その後、レジストパターン15を除去する。周辺回路領域にゲート酸化膜12を形成する。

【0095】

次に、図8を参照して、第2ポリシリコン層13とエッチングマスク用酸化膜16を半導体基板1の上に形成する。さて、本実施の形態によれば、レジスト表面の変質層が剥がれるのを防止する処理を行なうと、レジストパターン15が、O2プラズマまたはエッチングシークエンス中に混入しているO2のために、後退する。そのため、トンネル酸化膜9のエッチング除去時、ポリ−ポリ絶縁膜11が、従来のフローのものより、メモリセル領域側に後退して仕上がる。このため、後工程で、この領域で、すなわち、分離酸化膜8の上で、ダミーゲート14を形成する際、急激な段差変化は生じない。すなわち、分離酸化膜8+第2ポリシリコン層13(矢印A部分)からすぐに分離酸化膜8+第1ポリシリコン層10+ポリ−ポリ絶縁層11+第2ポリシリコン層13(矢印C部分)にいくという急激な段差変化は生じないで、分離酸化膜8+第2ポリシリコン層13(矢印A部分)→分離酸化膜8+第2ポリシリコン層13+第1ポリシリコン層10(矢印B部分)→分離酸化膜8+第2ポリシリコン層13+ポリ−ポリ絶縁膜11+第1ポリシリコン10(矢印C部分)というように、段差が緩やかに推移する。したがって、この領域および周辺で、後工程における写真製版、加工処理が容易になるという利点が生じる。

【0096】

図8と図9を参照して、エッチングマスク用酸化膜16をパターニングし、メモリセルのコントロールゲート13、周辺回路のトランジスタゲート13をパターニングする。

【0097】

図10を参照して、メモリセル領域だけ、エッチングマスク用酸化膜16を使って、ポリ−ポリ絶縁膜11、フローティングゲート10をエッチングする。これにより、図5に示す、フラッシュメモリが完成する。

【0098】

実施の形態11

SRAMに本発明を適用した例を以下に示す。

【0099】

図22は、高抵抗負荷型SRAMメモリセルの等価回路である。図中の記憶ノード1は、アクセストランジスタ1のソース、ドライバトランジスタ2のドレイン、ドライバトランジスタ1のゲートを結ぶ必要がある。

【0100】

この部分に本発明を適用した例を以下に示す。

図23は、たとえばN型基板51中に作ったPウェル52内にフィールド酸化膜53を作って分離を行ない、各トランジスタ共通のゲート酸化膜、ゲート電極、ポリシリコン54を成膜した状態である。

【0101】

次に、図24を参照して、レジストパターン55を形成し、いわゆるゲート直接コンタクト56を作る。

【0102】

すなわち、レジストパターン55を作り、ポリシリコン54をドライエッチングし、次にゲート酸化膜56をウエットエッチングするが、このときに今まで述べてきたような、レジストパターン表面の異常が発生するため、既に述べた実施の形態を適用する。

【0103】

図25は、ゲート直接コンタクトと、ドライバトランジスタ1のゲート電極57が完成した図である。図中のコンタクト、活性領域のn+領域が記憶ノード1に相当する。

【0104】

この構造にディープ紫外光による手段を用いた場合、ゲート直接コンタクトの中の残留したエッチングガスの残留物、たとえば塩素(Cl2)とかカーボン(C)などが除去されるため、コンタクト抵抗が低く、n+−Pウェル間に結晶欠陥が発生せず、すなわち記憶ノード1に蓄えられた電荷がリークしないという効果も期待できる。

【0105】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0106】

1 半導体基板、2 絶縁膜、3 導電層、4 レジストパターン。

【技術分野】

【0001】

この発明は、一般に、半導体装置の製造方法に関するものであり、より特定的には、ドライエッチとウエットエッチを連続して行なう工程を含む半導体装置の製造方法に関する。この発明は、また、ドライエッチおよびウエットエッチを連続して行なう工程を含む、フラッシュメモリの製造方法に関する。この発明は、そのような製造方法により製造したフラッシュメモリに関する。この発明は、さらに、スタティックランダムアクセスメモリ(以下、SRAMと略する)の製造方法に関する。

【背景技術】

【0002】

図11は、従来のフラッシュメモリのメモリセルの断面図である。

図11を参照して、P型不純物を含む半導体基板1の表面中にP型不純物領域1aが形成されている。半導体基板1の上に、トンネル酸化膜3を介在させてフローティングゲート4が形成されている。P型不純物領域1aの表面中であって、フローティングゲート4の両側にソース/ドレイン領域2a,2bが形成されている。フローティングゲート4の上に絶縁膜8が形成されている。絶縁膜8の上にコントロールゲート9が形成されている。コントロールゲート9を覆うように、半導体基板1の上に絶縁層10,11が形成されている。

【0003】

次に、フラッシュメモリの動作について説明する。

書込動作においては、ドレイン領域2bに6〜8V程度のドレイン電圧を、コントロールゲート9に10〜15V程度のゲート電圧を印加する。ソース領域2aと半導体基板1の電位は接地電位に保たれる。このとき、チャネル領域2cには数百μAの電流が流れる。ソース領域2aからドレイン領域2bに流れた電子のうち、ドレイン領域2b近傍で加速された電子は、高エネルギを有する電子(ホットエレクトロン)となる。この電子は、コントロールゲート9に印加されたゲート電圧による電界のため、矢印12の方向に流れ、フローティングゲート4に注入される。フローティングゲート4に電子の蓄積が行なわれると、トランジスタのしきい値電圧が高くなる。このしきい値電圧が一定値よりも高くなった場合が“0”と呼ばれる状態である。

【0004】

次に、データ消去動作について説明する。まず、ソース領域2aに10〜15V程度のソース電圧を印加し、コントロールゲート9と半導体基板1は接地電位に保持する。次に、ドレイン領域2bをフローティングとし、ソース領域2aに印加するソース電圧による電界により、フローティングゲート4に蓄積されていた電子は、矢印13の方向に、トンネル絶縁膜3を通過して半導体基板1内に流れる。このようにしてフローティングゲート4内部に蓄積されていた電子が引抜かれることによって、トランジスタのしきい値が高くなる。このしきい値電圧が所定の値より低い状態が、“1”と呼ばれるデータを消去された状態である。この消去状態によって、同一半導体装置内に形成されたメモリセルの一括消去が可能となる。さらに、読出動作においては、コントロールゲート9に5V程度のゲート電圧を印加し、ドレイン領域2bに1〜2V程度のドレイン電圧を印加したときに、チャネル領域2cに電流が流れるかどうか、つまり、トランジスタがON状態かOFF状態かによってデータが“1”か“0”かの判定をするというものである。

【0005】

次に、上記のように構成されるフラッシュメモリの製造方法について説明する。

まず、図12を参照して、単結晶シリコンからなる半導体基板1上にメモリセル同士、周辺回路のトランジスタ同士およびセルと周辺トランジスタを分離する素子分離酸化膜を形成した後、メモリセルが形成されるP型不純物領域1aを形成した後、基板の上面を酸化し、二酸化シリコン(SiO2)からなるトンネル絶縁膜3を形成する。

【0006】

図13を参照して、トンネル絶縁膜3上に、CVD(Chemical Vapor Deposition)技術によって、多結晶シリコンを積層し、これをメモリセル領域のみX方向(紙面に向かって水平方向。図中では表示しない)にエッチングして、フローティングゲート4を形成する。次に、同様にCVD技術によって、絶縁膜8(たとえば、シリコン窒化(SiN)膜、シリコン酸化膜)を形成する。次に、周辺回路領域の絶縁膜8、上記多結晶シリコン、トンネル絶縁膜3を除去する。次に、多結晶シリコン(ポリシリコン)(フローティングゲート)4の形成と同じ要領で、CVD技術によって、コントロールゲート9となる多結晶シリコンを積層する。

【0007】

次に、図14を参照して、多結晶シリコンを形成した領域のうち、ゲート電極として残したい領域については、その上部にレジストパターン14をY方向(紙面に向かって垂直方向)に形成し、レジストパターン14をマスクとして、トンネル絶縁膜3の表面が露出するまで異方性エッチングを行なう。

【0008】

その後、レジストパターン14をプラズマアッシング等の方法を用いて除去する。

図15を参照して、矢印15の方向に沿って不純物イオンを注入し、P型不純物領域1aの上部にP型不純物領域1aよりも不純物濃度が大きなN型高濃度不純物領域(ソース/ドレイン領域)2a,2bの形成を行なう。その後、図11に戻って、CVD技術等を用いてシリコン酸化膜からなる絶縁層10,11を、保護膜として形成することで、フラッシュメモリが完成する。

【発明の概要】

【発明が解決しようとする課題】

【0009】

以上のように構成される半導体装置の製造方法の問題点について、簡略化した図面を用いて説明する。

【0010】

図16を参照して、シリコン基板1の上に、SiO2膜2を形成する。SiO2膜2の上に、ポリシリコン膜3を堆積する。ポリシリコン膜3の上に、写真製版により、レジストパターン4を形成する。レジストパターン4をマスクにして、ポリシリコン膜3をドライエッチングし、続いて、連続的にSiO2膜2を、フッ酸(HF)液によりエッチングする。

【0011】

このとき、図17を参照して、フッ酸液で処理する際に、ポリシリコン膜3のドライエッチング時に、変質した、レジストパターン4の表面層5が剥がれる。剥がれたレジスト表面層5がシリコン基板1の上に再付着し、この剥がれたレジスト表面層5の下のSiO2膜2のエッチングが阻害されるという問題点があった。また、剥がれたレジスト表面層5が、フッ酸処理槽中に流出し、異物として槽を汚染するという問題点があった。

【0012】

そして、ポリシリコンエッチングを、塩素(Cl)系のガスを使って行なった場合に、特にこのような問題が発生しやすかった。

【0013】

また、ポリシリコン膜の上に絶縁膜、たとえばSiO2膜、SiN膜が堆積されている場合に、SiO2/SiN膜をドライエッチングし、ポリシリコン膜をドライエッチングし、次に、SiO2膜をフッ酸液でウエットエッチングするという連続処理を行なうと、一層このような問題が発生しやすかった。

【0014】

この発明は、上記のような問題点を解決するためになされたもので、レジストパターンの表面変質層が剥がれることを防止することができるように改良された半導体装置の製造方法を提供することにある。

【0015】

この発明の他の目的は、レジストパターンの表面変質層が剥がれないように改良された、フラッシュメモリの製造方法を提供することにある。

【0016】

この発明の他の目的は、レジストパターンの表面変質層が剥がれないように改良された、スタティックランダムアクセスメモリの製造方法の製造方法を提供することにある。

【課題を解決するための手段】

【0017】

請求項1に係る半導体装置の製造方法においては、まず、半導体基板の上に絶縁膜と導電層を順次形成する。このときの形成は、成膜のみで形成してもよいし、成膜後にパターニングを行なって形成してもよい(第1工程)。上記導電層の上にレジストパターンを形成する(第2工程)。上記レジストパターンをマスクに用いて、上記導電層をドライエッチングする(第3工程)。上記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする(第4工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をウエットエッチングする(第5工程)。

【0018】

この発明によれば、レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけるので、これらが剥がれなくなる。

【0019】

請求項2に係る半導体装置の製造方法においては、上記第4工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後熱処理する工程を含む。

【0020】

請求項3に係る半導体装置の製造方法においては、上記第4工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0021】

請求項4に係る半導体装置の製造方法においては、上記第4工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することによって行なう。

【0022】

請求項5に係るフラッシュメモリは、半導体基板を備える。上記半導体基板の上にダミーゲート領域が設けられている。上記半導体基板の上に、上記ダミーゲート領域を挟むようにメモリセル領域と周辺回路領域が設けられている。上記ダミーゲート領域は、上記半導体基板の上に形成された分離酸化膜を含む。上記分離酸化膜の上に、その周辺回路領域側の端部が上記メモリセル領域側に後退した第1導電層が設けられている。上記第1導電層の上に、その周辺回路領域側の端部が上記メモリセル領域側に後退した絶縁層が設けられている。上記分離酸化膜の上に、上記第1導電層および上記絶縁層を覆うように、第2導電層が設けられている。

【0023】

請求項6に係る半導体装置の製造方法においては、まず、半導体基板の上に絶縁膜と導電層を順次形成する(第1工程)。第2の絶縁膜を形成する(第2工程)。上記第2の絶縁膜の上にレジストパターンを形成する(第3工程)。上記レジストパターンをマスクに用いて、上記第2の絶縁膜と上記導電層をドライエッチングする(第4工程)。上記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする(第5工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をウエットエッチングする(第6工程)。

【0024】

請求項7に係る半導体装置の製造方法においては、上記第5工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0025】

請求項8に係る半導体装置の製造方法においては、上記第5工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0026】

請求項9に記載の半導体装置の製造方法においては、上記第5工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【0027】

請求項10に係るフラッシュメモリの製造方法においては、まず、半導体基板の表面に、メモリセル領域と周辺回路領域を分離する分離酸化膜を形成する(第1工程)。上記半導体基板の表面上にトンネル酸化膜を形成する(第2工程)。上記トンネル酸化膜の上に第1ポリシリコン層を形成する(第3工程)。上記トンネル酸化膜と上記第1ポリシリコン層を所望の形にパターニングする(第4工程)。上記第1ポリシリコン層の上に絶縁膜を形成する(第5工程)。上記絶縁膜の上に、その端部が分離酸化膜上に位置し、かつ上記メモリセル領域のみを覆う、レジストパターンを形成する(第6工程)。上記レジストパターンをマスクに用いて、上記周辺回路領域の上にある、上記絶縁膜および上記第1ポリシリコン層をドライエッチングにより除去する(第7工程)。上記レジストパターンの表面変質層と、該レジストパターンの表面より下にある正常な部分をくっつけ、これらを剥がれなくする(第8工程)。上記レジストパターンを再びマスクに用いて、上記周辺回路領域の上にある上記トンネル酸化膜をウエットエッチングにより除去する(第9工程)。上記レジストパターンを除去する(第10工程)。上記半導体基板の上であって、上記周辺回路領域の上に、周辺トランジスタ用のゲート酸化膜を形成する(第11工程)。上記半導体基板の上に第2ポリシリコン層を形成する(第12工程)。上記第2ポリシリコン層の上に、エッチングマスク用の酸化膜を形成する(第13工程)。上記メモリセル領域にコントロールゲートを形成し、周辺回路のトランジスタゲートを形成する(第14工程)。上記絶縁膜および上記第1ポリシリコン層をパターニングし、フローティングゲートを形成する(第15工程)。

【0028】

請求項11に係るフラッシュメモリの製造方法においては、上記第8工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む。

【0029】

請求項12に係るフラッシュメモリの製造方法においては、上記第8工程は乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む。

【0030】

請求項13に係るフラッシュメモリの製造方法においては、上記第8工程は乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【0031】

請求項14に係るSRAMの製造方法においては、まず、半導体基板の表面に、分離酸化膜を形成する(第1工程)。上記半導体基板上にゲート酸化膜を成膜する(第2工程)。上記ゲート酸化膜上に第1ポリシリコン層を成膜する(第3工程)。活性領域から分離酸化膜上に及ぶような開口部を有するレジストパターンを形成する(第4工程)。上記レジストパターンをマスクとして、上記第1ポリシリコン層をドライエッチングにより除去する(第5工程)。上記レジストパターンの表面の変質層と表面より下にある正常な部分をくっつけ、これらを剥がれなくする(第6工程)。上記レジストパターンを再びマスクに用いて、パターン底のゲート酸化膜をウエットエッチングにより除去する(第7工程)。上記レジストパターンを除去する(第8工程)。第2ポリシリコン層を形成する(第9工程)。アクセストランジスタ、ドライバトランジスタ、周辺回路のトランジスタのゲート電極となるパターンをレジストにて形成する(第10工程)。上記レジストパターンをマスクとして、第1ポリシリコン層、第2ポリシリコン層をドライエッチングする(第11工程)。上記レジストパターンを除去する(第12工程)。n領域のみにn型不純物をドーピングする(第13工程)。熱処理を行なう(第14工程)。

【0032】

請求項15に記載のSRAMの製造方法においては、上記第6工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0033】

請求項16に係るSRAMの製造方法においては、上記第6工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0034】

請求項17に記載のSRAMの製造方法においては、上記第6工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【0035】

その他、本発明の半導体装置の製造方法においては、まず、半導体基板の上に、絶縁膜と導電層を順次形成する。このときの形成は、成膜のみでも、成膜後にパターニングを行なうの、どちらにも対応する(第1工程)。上記導電層の上にレジストパターンを形成する(第2工程)。上記レジストパターンをマスクに用いて、上記導電層をドライエッチングする(第3工程)。上記レジストパターンの表層部を一部削る(第4工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をエッチングする。

【0036】

この発明によれば、レジストパターンの表層部を一部削るので、変質したレジストパターンの表面が除去される。

【0037】

本発明の半導体装置の製造方法においては、上記第4工程を、O2プラズマを用いるエッチングにより行なう。

【0038】

本発明の半導体装置の製造方法においては、上記第3工程におけるドライエッチングを、O2を混入したガスを用いて行ない、それによって、上記第4工程を、上記導電層のドライエッチングのシークエンスの中で行なう。

【0039】

本発明の半導体装置の製造方法においては、まず、半導体基板の上に絶縁膜と導電層を順次形成する。このときの形成は、成膜のみで形成してもよいし、成膜後にパターニングを行なって形成してもよい(第1工程)。上記導電層の上にレジストパターンを形成する(第2工程)。上記レジストパターンをマスクに用いて、上記導電層をドライエッチングする(第3工程)。上記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする(第4工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をエッチングする(第5工程)。

【0040】

この発明によれば、レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけるので、これらが剥がれなくなる。

【0041】

本発明の半導体装置の製造方法においては、上記第4工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後熱処理する工程を含む。

【0042】

本発明の半導体装置の製造方法においては、上記第4工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0043】

本発明の半導体装置の製造方法においては、上記第4工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することによって行なう。

【0044】

本発明のフラッシュメモリの製造方法においては、まず、半導体基板の表面に、メモリセル領域と周辺回路領域を分離する分離酸化膜を形成する(第1工程)。上記半導体基板の表面上にトンネル酸化膜を形成する(第2工程)。上記トンネル酸化膜の上に第1ポリシリコン層を形成する(第3工程)。上記トンネル酸化膜と上記第1ポリシリコン層を所望の形にパターニングする(第4工程)。上記第1ポリシリコン層の上に絶縁膜を形成する(第5工程)。上記絶縁膜の上に、その端部が分離酸化膜上に位置し、かつ上記メモリセル領域のみを覆う、レジストパターンを形成する(第6工程)。上記レジストパターンをマスクに用いて、上記周辺回路領域の上にある、上記絶縁膜および上記第1ポリシリコン層をドライエッチングにより除去する(第7工程)。上記レジストパターンの表層部を一部削る(第8工程)。上記レジストパターンを再びマスクに用いて、上記周辺回路領域の上にある上記トンネル酸化膜を除去する(第9工程)。上記レジストパターンを除去する(第10工程)。上記半導体基板の上であって、上記周辺回路領域の上に、周辺トランジスタ用のゲート酸化膜を形成する(第11工程)。上記半導体基板の上に第2ポリシリコン層を形成する(第12工程)。上記第2ポリシリコン層の上に、エッチングマスク用の酸化膜を形成する(第13工程)。上記メモリセル領域にコントロールゲートを形成し、周辺回路のトランジスタゲートを形成する(第14工程)。上記絶縁膜および上記第1ポリシリコン層をパターニングし、フローティングゲートを形成する(第15工程)。

【0045】

この発明によれば、レジストパターンの表層部を一部削るので、レジストパターンの表面変質層が除去される。

【0046】

本発明のフラッシュメモリは、半導体基板を備える。上記半導体基板の上にダミーゲート領域が設けられている。上記半導体基板の上に、上記ダミーゲート領域を挟むようにメモリセル領域と周辺回路領域が設けられている。上記ダミーゲート領域は、上記半導体基板の上に形成された分離酸化膜を含む。上記分離酸化膜の上に、その周辺回路領域側の端部が上記メモリセル領域側に後退した第1導電層が設けられている。上記第1導電層の上に、その周辺回路領域側の端部が上記メモリセル領域側に後退した絶縁層が設けられている。上記分離酸化膜の上に、上記第1導電層および上記絶縁層を覆うように、第2導電層が設けられている。

【0047】

本発明の半導体装置の製造方法においては、上記の製法において、上記導電層はポリシリコン膜であり、上記ドライエッチングは塩素ガスを用いて行なわれる。

【0048】

本発明のフラッシュメモリの製造方法においては、上記フラッシュメモリの製造方法の第6工程におけるドライエッチングを、塩素ガスを用いて行なう。

【0049】

本発明の半導体装置の製造方法においては、まず半導体基板の上に絶縁膜と導電層を順次形成する(第1工程)。第2の絶縁膜を形成する(第2工程)。上記第2の絶縁膜の上にレジストパターンを形成する(第3工程)。上記レジストパターンをマスクに用いて、上記第2の絶縁膜と導電層をドライエッチングする(第4工程)。上記レジストパターンの表層部を一部削る(第5工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をエッチングする(第6工程)。

【0050】

本発明の半導体装置の製造方法においては、上記第5工程を、O2プラズマを用いるエッチングにより行なう。

【0051】

本発明の半導体装置の製造方法においては、上記第4工程におけるドライエッチングをO2を混入したガスを用いて行ない、それによって、上記第5工程を、上記導電層のドライエッチングのシークエンスの中で行なう。

【0052】

本発明の半導体装置の製造方法においては、まず、半導体基板の上に絶縁膜と導電層を順次形成する(第1工程)。第2の絶縁膜を形成する(第2工程)。上記第2の絶縁膜の上にレジストパターンを形成する(第3工程)。上記レジストパターンをマスクに用いて、上記第2の絶縁膜と上記導電層をドライエッチングする(第4工程)。上記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする(第5工程)。上記レジストパターンをマスクに用いて、上記絶縁膜をエッチングする(第6工程)。

【0053】

本発明の半導体装置の製造方法においては、上記第5工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0054】

本発明の半導体装置の製造方法においては、上記第5工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0055】

本発明の半導体装置の製造方法においては、上記第5工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【0056】

本発明のフラッシュメモリの製造方法においては、まず、半導体基板の表面に、メモリセル領域と周辺回路領域を分離する分離酸化膜を形成する(第1工程)。上記半導体基板の表面上にトンネル酸化膜を形成する(第2工程)。上記トンネル酸化膜の上に第1ポリシリコン層を形成する(第3工程)。上記トンネル酸化膜と上記第1ポリシリコン層を所望の形にパターニングする(第4工程)。上記第1ポリシリコン層の上に絶縁膜を形成する(第5工程)。上記絶縁膜の上に、その端部が分離酸化膜上に位置し、かつ上記メモリセル領域のみを覆う、レジストパターンを形成する(第6工程)。上記レジストパターンをマスクに用いて、上記周辺回路領域の上にある、上記絶縁膜および上記第1ポリシリコン層をドライエッチングにより除去する(第7工程)。上記レジストパターンの表層部を、一部削ることをO2プラズマを用いるエッチングにより行なう(第8工程)。上記レジストパターンを再びマスクに用いて、上記周辺回路領域の上にある上記トンネル酸化膜を除去する(第9工程)。上記レジストパターンを除去する(第10工程)。上記半導体基板の上であって、上記周辺回路領域の上に、周辺トランジスタ用のゲート酸化膜を形成する(第11工程)。上記半導体基板の上に第2ポリシリコン層を形成する(第12工程)。上記第2ポリシリコン層の上に、エッチングマスク用の酸化膜を形成する(第13工程)。上記メモリセル領域にコントロールゲートを形成し、周辺回路のトランジスタゲートを形成する(第14工程)。上記絶縁膜および上記第1ポリシリコン層をパターニングし、フローティングゲートを形成する(第15工程)。

【0057】

本発明のフラッシュメモリの製造方法においては、上記第7工程のドライエッチングをO2を混入したガスを用いて行ない、上記第8工程のレジストパターンの表層部を一部削ることをドライエッチングのシークエンス中で行なうことを特徴とする。

【0058】

本発明のフラッシュメモリの製造方法においては、まず、半導体基板の表面に、メモリセル領域と周辺回路領域を分離する分離酸化膜を形成する(第1工程)。上記半導体基板の表面上にトンネル酸化膜を形成する(第2工程)。上記トンネル酸化膜の上に第1ポリシリコン層を形成する(第3工程)。上記トンネル酸化膜と上記第1ポリシリコン層を所望の形にパターニングする(第4工程)。上記第1ポリシリコン層の上に絶縁膜を形成する(第5工程)。上記絶縁膜の上に、その端部が分離酸化膜上に位置し、かつ上記メモリセル領域のみを覆う、レジストパターンを形成する(第6工程)。上記レジストパターンをマスクに用いて、上記周辺回路領域の上にある、上記絶縁膜および上記第1ポリシリコン層をドライエッチングにより除去する(第7工程)。上記レジストパターンの表面変質層と、該レジストパターンの表面より下にある正常な部分をくっつけ、これらを剥がれなくする(第8工程)。上記レジストパターンを再びマスクに用いて、上記周辺回路領域の上にある上記トンネル酸化膜を除去する(第9工程)。上記レジストパターンを除去する(第10工程)。上記半導体基板の上であって、上記周辺回路領域の上に、周辺トランジスタ用のゲート酸化膜を形成する(第11工程)。上記半導体基板の上に第2ポリシリコン層を形成する(第12工程)。上記第2ポリシリコン層の上に、エッチングマスク用の酸化膜を形成する(第13工程)。上記メモリセル領域にコントロールゲートを形成し、周辺回路のトランジスタゲートを形成する(第14工程)。上記絶縁膜および上記第1ポリシリコン層をパターニングし、フローティングゲートを形成する(第15工程)。

【0059】

本発明のフラッシュメモリの製造方法においては、上記第8工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む。

【0060】

本発明のフラッシュメモリの製造方法においては、上記第8工程は乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む。

【0061】

本発明のフラッシュメモリの製造方法においては、上記第8工程は乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【0062】

本発明のSRAMの製造方法においては、まず、半導体基板の表面に、分離酸化膜を形成する(第1工程)。上記半導体基板上にゲート酸化膜を成膜する(第2工程)。上記ゲート酸化膜上に第1ポリシリコン層を成膜する(第3工程)。活性領域から分離酸化膜上に及ぶような開口部を有するレジストパターンを形成する(第4工程)。上記レジストパターンをマスクとして、上記第1ポリシリコン層をドライエッチングにより除去する(第5工程)。上記レジストパターンの表層部を一部削る(第6工程)。上記レジストパターンを再びマスクに用いて、パターン底のゲート酸化膜を除去する(第7工程)。上記レジストパターンを除去する(第8工程)。上記第2ポリシリコン層を形成する(第9工程)。アクセストランジスタ、ドライバトランジスタ、周辺回路のトランジスタのゲート電極となるパターンをレジストにて形成する(第10工程)。上記レジストパターンをマスクとして、上記第1ポリシリコン層、上記第2ポリシリコン層をドライエッチングする(第11工程)。上記レジストパターンを除去する(第12工程)。n領域のみにn型不純物をドーピングする(第13工程)。熱処理を行なう(第14工程)。

【0063】

本発明のSRAMの製造方法においては、上記第6工程をO2プラズマを用いたエッチングにより行なう。

【0064】

本発明のSRAMの製造方法においては、上記第5工程において、ドライエッチングにO2を混入したガスを用いて行ない、上記第6工程のレジストパターンの表層部を一部削ることをドライエッチングのシークエンス中で行なう。

【0065】

本発明のSRAMの製造方法においては、まず、半導体基板の表面に、分離酸化膜を形成する(第1工程)。上記半導体基板上にゲート酸化膜を成膜する(第2工程)。上記ゲート酸化膜上に第1ポリシリコン層を成膜する(第3工程)。活性領域から分離酸化膜上に及ぶような開口部を有するレジストパターンを形成する(第4工程)。上記レジストパターンをマスクとして、上記第1ポリシリコン層をドライエッチングにより除去する(第5工程)。上記レジストパターン表面の変質層と表面より下にある正常な部分をくっつけ、これらを剥がれなくする(第6工程)。上記レジストパターンを再びマスクに用いて、パターン底のゲート酸化膜を除去する(第7工程)。上記レジストパターンを除去する(第8工程)。第2ポリシリコン層を形成する(第9工程)。アクセストランジスタ、ドライバトランジスタ、周辺回路のトランジスタのゲート電極となるパターンをレジストにて形成する(第10工程)。上記レジストパターンをマスクとして、第1ポリシリコン層、第2ポリシリコン層をドライエッチングする(第11工程)。上記レジストパターンを除去する(第12工程)。n領域のみにn型不純物をドーピングする(第13工程)。熱処理を行なう(第14工程)。

【0066】

本発明のSRAMの製造方法においては、上記第6工程は、N2雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0067】

本発明のSRAMの製造方法においては、上記第6工程は、乾燥空気雰囲気中で上記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む。

【0068】

本発明のSRAMの製造方法においては、上記第6工程は、乾燥空気雰囲気中、上記レジストパターンを熱処理することにより行なう。

【図面の簡単な説明】

【0069】

【図1】実施の形態1に係る製造方法を説明するための、半導体装置の断面図である。

【図2】実施の形態5に係る半導体装置の製造方法の順序の第1の工程における半導体装置の断面図である。

【図3】実施の形態5に係る半導体装置の製造方法の順序の第2の工程における半導体装置の断面図である。

【図4】実施の形態5に係る半導体装置の製造方法の順序の第3の工程における半導体装置の断面図である。

【図5】実施の形態10に係るフラッシュメモリの製造方法により製造した半導体装置の断面図である。

【図6】実施の形態10に係るフラッシュメモリの製造方法の順序の第1の工程における半導体装置の断面図である。

【図7】実施の形態10に係るフラッシュメモリの製造方法の順序の第2の工程における半導体装置の断面図である。

【図8】実施の形態10に係るフラッシュメモリの製造方法の順序の第3の工程における半導体装置の断面図である。

【図9】実施の形態10に係る半導体装置の製造方法の順序の第4の工程における半導体装置の断面図である。

【図10】実施の形態10に係る半導体装置の製造方法の順序の第5の工程における半導体装置の断面図である。

【図11】従来のフラッシュメモリのメモリセルの断面図である。

【図12】従来のフラッシュメモリの製造方法の順序の第1の工程における半導体装置の断面図である。

【図13】従来のフラッシュメモリの製造方法の順序の第2の工程における半導体装置の断面図である。

【図14】従来のフラッシュメモリの製造方法の順序の第3の工程における半導体装置の断面図である。

【図15】従来のフラッシュメモリの製造方法の順序の第4の工程における半導体装置の断面図である。

【図16】従来の半導体装置の製造方法の問題点を示す第1の工程における半導体装置の断面図である。

【図17】従来の半導体装置の製造方法の問題点を示す第2の工程における半導体装置の断面図である。

【図18】実施の形態3に係る方法を説明するための半導体装置の断面図である。

【図19】実施の形態7に係る製造方法の順序の第1の工程における半導体装置の断面図である。

【図20】実施の形態7に係る製造方法の順序の第2の工程における半導体装置の断面図である。

【図21】実施の形態7に係る製造方法の順序の第3の工程における半導体装置の断面図である。

【図22】高抵抗負荷型SRAMメモリセルの等価回路図である。

【図23】実施の形態11に係る方法の製造方法の順序の第1の工程における半導体装置の断面図である。

【図24】実施の形態11に係る方法の製造方法の順序の第2の工程における半導体装置の断面図である。

【図25】実施の形態11に係る方法の製造方法の順序の第3の工程における半導体装置の断面図である。

【発明を実施するための形態】

【0070】

本発明の実施の形態は、写真製版−ポリシリコンドライエッチング−HF液ウエットエッチングを、連続的に行なうまたは写真製版−シリコン酸化膜ドライエッチング−ポリシリコンドライエッチング−HF液ウエットエッチングを連続的に行なう、という工程を含む半導体装置の製造方法のすべてについて適用される。以下、実施の形態を図について説明する。

【0071】

実施の形態1

図1を参照して、シリコン基板1の上にSiO2膜2を形成する。SiO2膜2の上にポリシリコン膜3を形成する。このときの形成は、成膜のみでも、成膜後にパターニングを行なうのどちらにも対応する。ポリシリコン膜3の上にレジストパターン4を形成する。レジストパターン4をマスクにして、ポリシリコン膜3をエッチングする。その後、O2プラズマ処理(アッシング処理)を行なう。O2プラズマ処理は、ポリシリコン膜3のエッチングのシークエンス中、または別装置で行なわれる。レジストパターン4の表面を、約10nm除去した後、レジストパターン4をマスクにして、SiO2膜2の、HF液処理を行なう。本発明の実施の形態によれば、O2プラズマ処理により、レジストパターン4の表層部を一部除去しているので、図17に示す従来方法によって生じた問題点は解消される。すなわち、剥がれたレジスト表面変質層がSiO2膜2のエッチングを妨げるという問題は生じない。なお、HF液処理の前に、レジストパターン4が、元のパターンの位置より後退している(点線で示した分だけ水平方向に後退している)が、問題は生じない。

【0072】

実施の形態2

本実施の形態も、変質レジストを除去する目的で行なわれる。本実施の形態では、ポリシリコンのエッチングのシークエンスの中で、変質レジストの除去が行なわれる。すなわち、ポリシリコン膜のメインエッチ、オーバーエッチング後に、O2を混入したエッチングを行なう。たとえば、次のようなエッチングシークエンスで行なう。

【0073】

メインエッチング→Cl2ガスを用いるオーバーエッチング→Cl2+O2ガスを用いる後処理

この場合は、O2プラズマ処理とは異なるため、レジストパターンの後退は少なくなる。なお、O2ガスを混入したエッチングは、オーバーエッチングの途中から行なってもよい。

【0074】

実施の形態3

図18を参照して、シリコン基板1の上にSiO2膜2を形成する。SiO2膜2の上にポリシリコン膜3を形成する。このときの形成は成膜のみでも、成膜後にパターニングを行なうのどちらにも対応する。その後、第2の絶縁膜7を成膜後、第2の絶縁膜7の上に、レジストパターン4を形成する。レジストパターン4をマスクにして、第2の絶縁膜7とポリシリコン膜3をエッチングする。その後、O2プラズマ処理(アッシング処理)を行なう。O2プラズマ処理は、ポリシリコン膜3のエッチングのシークエンス中、または別装置で行なわれる。レジストパターン4の表面を、約10nm除去した後、レジストパターン4をマスクにして、SiO2膜2の、HF液処理を行なう。本発明の実施の形態によれば、O2プラズマ処理により、レジストパターン4の表層部を一部除去しているので、図17に示す従来方法によって生じた問題点は解消される。すなわち、剥がれたレジスト表面変質層がSiO2膜2のエッチングを妨げるという問題は生じない。なお、HF液処理の前に、レジストパターン4が、元のパターンの位置より後退している(点線で示した分だけ水平方向に後退している)が、問題は生じない。

【0075】

実施の形態4

本実施の形態も、変質レジストを除去する目的で行なわれる。本実施の形態では、第2の絶縁膜7のエッチング後、ポリシリコンのエッチングのシークエンスの中で、変質レジストの除去が行なわれる。すなわち、ポリシリコン膜のメインエッチ、オーバエッチング後に、O2を混入したエッチングを行なう。たとえば、次のようなエッチングシークエンスで行なう。

【0076】

メインエッチング→Cl2ガスを用いるオーバエッチング→Cl2+O2ガスを用いる後処理

この場合は、O2プラズマ処理とは異なるため、レジストパターンの後退は少なくなる。なお、O2ガスを混入したエッチングは、オーバエッチングの途中から行なってもよい。

【0077】

実施の形態5

本実施の形態は、変質した表面レジストを硬化することによって、変質部の剥がれを防止するものである。

【0078】

図2を参照して、シリコン基板1の上にSiO2膜2を形成する。SiO2膜2の上にポリシリコン膜3を形成する。ポリシリコン膜3の上に、レジストパターン4を形成する。レジストパターン4をマスクにして、ポリシリコン膜3をエッチングする。このとき、レジストパターン4の表面が変質する。図中、6は、変質したレジスト表面層を表わしている。

【0079】

図3を参照して、変質したレジスト表面層6を硬化するために、レジスト表面層6をN2雰囲気中で、ディープ紫外線キュア(以下、DUVキュア処理と略す)する。具体的には、波長約250nm〜600nmの光を、レジストパターン4に100秒間照射し、シリコン基板1の載っているステージを約100℃〜150℃まで昇温する。本実施の形態によれば、DUV光で、変質した表面レジスト層6と下の正常なレジスト層4の感光基を分解し、これらを交わらせる。図中7は、交わってできた層を表わしている。

【0080】

図4を参照して、この状態で、熱処理を行ない、変質層6を下の正常なレジスト層4とくっつける。これによって、変質したレジスト表面層6の剥がれを防止できる。また、DUVキュア処理によって、波長の短い光がレジスト表面層6に照射されるので、表面の残留エッチングガスが化学反応により除去されるという効果も生じ、残留ガスの悪影響が除去される。本実施の形態に係る工程を要約すると、次のとおりである。

【0081】

ポリシリコンエッチ→DUVキュア(N2雰囲気)→HF液ウエットエッチング

実施の形態6

本実施の形態は、実施の形態3の変形例である。N2雰囲気の代わりに、Dry Air(乾燥空気)雰囲気中で、DUVキュア処理を行なう。この処理を行なうと、レジストの表面変質層と下の正常なレジスト層を交わらせて、これらを硬化するだけでなく、変質層が、Dry Air中のO2と、DUV光により発生するO3(オゾン)とにより、数nm程度、除去されるという新たな効果が生じる。

【0082】

本実施の形態の工程を要約すれば、次のとおりである。

ポリシリコンエッチ→DUVキュア(Dry Air雰囲気)→HF液ウエットエッチング

実施の形態7

本実施の形態は、変質した表面レジストを硬化することによって、変質部の剥がれを防止するものである。

【0083】

図19を参照して、シリコン基板1の上にSiO2膜2を形成する。SiO2膜2の上にポリシリコン膜3を形成する。このときの形成は成膜のみでも、成膜後にパターニングを行なうのどちらにも対応する。その後、第2の絶縁膜7を成膜後、第2の絶縁膜7の上に、レジストパターン4を形成する。レジストパターン4をマスクにして、第2の絶縁膜7とポリシリコン膜3をエッチングする。このとき、レジストパターン4の表面が変質する。図中、6は、変質したレジスト表面層を表わしている。

【0084】

図20を参照して、変質したレジスト表面層6を硬化するために、レジスト表面層6をN2雰囲気中で、ディープ紫外線キュア(以下、DUVキュア処理と略する)する。具体的には、波長約250nm〜600nmの光を、レジストパターン4に100秒間照射し、シリコン基板1の載っているステージを約100℃〜150℃まで昇温する。本実施の形態によれば、DUV光で、変質した表面レジスト層6と下の正常なレジスト層4の感光基を分解し、これらを交わらせる。図中7は、交わってできた層を表わしている。

【0085】

図21を参照して、この状態で、熱処理を行ない、変質層6を下の正常なレジスト層4とくっつける。これによって、変質したレジスト表面層6の剥がれを防止できる。また、DUVキュア処理によって、波長の短い光がレジスト表面層6に照射されるので、表面の残留エッチングガスが化学反応により除去されるという効果も生じ、残留ガスの悪影響が除去される。本実施の形態に係る工程を要約すると、次のとおりである。

【0086】

ポリシリコンエッチ→DUVキュア(N2雰囲気)→HF液ウエットエッチング

実施の形態8

本実施の形態は、実施の形態7の変形例である。N2雰囲気の代わりに、Dry Air(乾燥空気)雰囲気中で、DUVキュア処理を行なう。この処理を行なうと、レジストの表面変質層と下の正常なレジスト層を交わらせて、これらを硬化するだけでなく、変質層が、Dry Air中のO2と、DUV光により発生するO3(オゾン)とにより、数nm程度、除去されるという新たな効果が生じる。

【0087】

本実施の形態の工程を要約すれば、次のとおりである。

ポリシリコンエッチ→DUVキュア(Dry Air雰囲気)→HF液ウエットエッチング

実施の形態9

本実施の形態も、実施の形態5と7の変形例である。本実施の形態ではDUVキュアを行なわず、ウェハをDry Air雰囲気で満たされたオーブン中で、たとえば150℃で、1時間、ベーキングする。変質層と下層の正常層の交わる効果は少ないが、変質層と下層の正常層が、接している部分で、硬化する際に、これらがつながることが期待できる。

【0088】

本実施の形態の工程を要約すれば次のとおりである。

ポリシリコンエッチング→オーブン処理(150℃,1時間,Dry Air)→HF液ウエットエッチング

実施の形態10

本実施の形態は、上述した発明を、実際の半導体装置に適用したものである。本実施の形態では、2層スタックトポリシリコン膜によりセルを形成する、フラッシュメモリの製造方法について述べる。

【0089】

図5は、実施の形態10に係る方法によって製造したフラッシュメモリの断面図である。フラッシュメモリは、半導体基板1を備える。半導体基板1の上にダミーゲート14を含むダミーゲート領域が設けられている。半導体基板の上に、ダミーゲート領域を挟むようにメモリセル領域と周辺回路領域が設けられている。ダミーゲート領域は、半導体基板1の上に形成された分離酸化膜8を含む。分離酸化膜8の上に、第1導電層10が設けられている。第1導電層10の周辺回路領域側の端部10aはメモリセル領域側に後退している。第1導電層10の上に絶縁層11が設けられている。絶縁層11の周辺回路領域側の端部11aはメモリセル領域側に後退している。分離酸化膜8の上に、第1導電層10および絶縁層11を覆うように、第2導電層13が設けられている。

【0090】

図5を参照して、メモリセルでは、フローティングゲート、ポリ−ポリ絶縁膜が必要だが、周辺回路では、これらの膜は不要である。

【0091】

以下、図5に示すフラッシュメモリの製造方法について説明する。

図6を参照して、半導体基板1の上に、分離酸化膜8とトンネル酸化膜9を形成する。その後、半導体基板1の上に第1ポリシリコン層(フローティングゲートになるもの)10をX方向(紙面に向かって水平方向。図中では表示しない)にエッチング後、ポリ−ポリ絶縁膜11を形成する。

ポリ−ポリ絶縁膜11の上に、その端部が分離酸化膜8上に位置し、かつメモリセル領域のみを覆う、レジストパターン15を、写真製版処理によって形成する。

【0092】

次に、図7を参照して、CCl4あるいはCHCl3などのフロロカーボン系のエッチングガスを用いて、レジストパターン15をマスクにし、ポリ−ポリ絶縁膜11をエッチングし、次に第1ポリシリコン層10をエッチングする。

【0093】

この後、連続して、トンネル酸化膜9をHF液でエッチングすると、レジスト表面の変質層が剥がれるため、上述した実施の形態1−9の方法をここで適用する。すなわち、レジストパターン15の表面の変質層を除去するか、あるいは、変質層とその下にある正常なレジスト層とをくっつけ、レジスト表面の変質層が剥がれるのを防止する。

【0094】

次に、そのような処理を行なった後、レジストパターン15をマスクにして、周辺回路領域のトンネル酸化膜9のエッチング除去を行なう。本発明の実施の形態では、上記実施の形態1または2を適用している。その後、レジストパターン15を除去する。周辺回路領域にゲート酸化膜12を形成する。

【0095】

次に、図8を参照して、第2ポリシリコン層13とエッチングマスク用酸化膜16を半導体基板1の上に形成する。さて、本実施の形態によれば、レジスト表面の変質層が剥がれるのを防止する処理を行なうと、レジストパターン15が、O2プラズマまたはエッチングシークエンス中に混入しているO2のために、後退する。そのため、トンネル酸化膜9のエッチング除去時、ポリ−ポリ絶縁膜11が、従来のフローのものより、メモリセル領域側に後退して仕上がる。このため、後工程で、この領域で、すなわち、分離酸化膜8の上で、ダミーゲート14を形成する際、急激な段差変化は生じない。すなわち、分離酸化膜8+第2ポリシリコン層13(矢印A部分)からすぐに分離酸化膜8+第1ポリシリコン層10+ポリ−ポリ絶縁層11+第2ポリシリコン層13(矢印C部分)にいくという急激な段差変化は生じないで、分離酸化膜8+第2ポリシリコン層13(矢印A部分)→分離酸化膜8+第2ポリシリコン層13+第1ポリシリコン層10(矢印B部分)→分離酸化膜8+第2ポリシリコン層13+ポリ−ポリ絶縁膜11+第1ポリシリコン10(矢印C部分)というように、段差が緩やかに推移する。したがって、この領域および周辺で、後工程における写真製版、加工処理が容易になるという利点が生じる。

【0096】

図8と図9を参照して、エッチングマスク用酸化膜16をパターニングし、メモリセルのコントロールゲート13、周辺回路のトランジスタゲート13をパターニングする。

【0097】

図10を参照して、メモリセル領域だけ、エッチングマスク用酸化膜16を使って、ポリ−ポリ絶縁膜11、フローティングゲート10をエッチングする。これにより、図5に示す、フラッシュメモリが完成する。

【0098】

実施の形態11

SRAMに本発明を適用した例を以下に示す。

【0099】

図22は、高抵抗負荷型SRAMメモリセルの等価回路である。図中の記憶ノード1は、アクセストランジスタ1のソース、ドライバトランジスタ2のドレイン、ドライバトランジスタ1のゲートを結ぶ必要がある。

【0100】

この部分に本発明を適用した例を以下に示す。

図23は、たとえばN型基板51中に作ったPウェル52内にフィールド酸化膜53を作って分離を行ない、各トランジスタ共通のゲート酸化膜、ゲート電極、ポリシリコン54を成膜した状態である。

【0101】

次に、図24を参照して、レジストパターン55を形成し、いわゆるゲート直接コンタクト56を作る。

【0102】

すなわち、レジストパターン55を作り、ポリシリコン54をドライエッチングし、次にゲート酸化膜56をウエットエッチングするが、このときに今まで述べてきたような、レジストパターン表面の異常が発生するため、既に述べた実施の形態を適用する。

【0103】

図25は、ゲート直接コンタクトと、ドライバトランジスタ1のゲート電極57が完成した図である。図中のコンタクト、活性領域のn+領域が記憶ノード1に相当する。

【0104】

この構造にディープ紫外光による手段を用いた場合、ゲート直接コンタクトの中の残留したエッチングガスの残留物、たとえば塩素(Cl2)とかカーボン(C)などが除去されるため、コンタクト抵抗が低く、n+−Pウェル間に結晶欠陥が発生せず、すなわち記憶ノード1に蓄えられた電荷がリークしないという効果も期待できる。

【0105】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0106】

1 半導体基板、2 絶縁膜、3 導電層、4 レジストパターン。

【特許請求の範囲】

【請求項1】

半導体基板の上に絶縁膜と導電層を順次形成する第1工程と、

前記導電層の上にレジストパターンを形成する第2工程と、

前記レジストパターンをマスクに用いて、前記導電層をドライエッチングする第3工程と、

前記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする第4工程と、

前記レジストパターンをマスクに用いて、前記絶縁膜をウエットエッチングする第5工程と、を備えた半導体装置の製造方法。

【請求項2】

前記第4工程は、N2雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第4工程は、乾燥空気雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項1に記載の半導体装置の製造方法。

【請求項4】

前記第4工程は、乾燥空気雰囲気中、前記レジストパターンを熱処理することにより行なう、請求項1に記載の半導体装置の製造方法。

【請求項5】

半導体基板と、

前記半導体基板の上に設けられたダミーゲート領域と、

前記半導体基板の上に、前記ダミーゲート領域を挟むように設けられたメモリセル領域と周辺回路領域と、を備え、

前記ダミーゲート領域は、

前記半導体基板の上に形成された分離酸化膜と、

前記分離酸化膜の上に設けられ、その周辺回路領域側の端部が前記メモリセル領域側に後退した第1導電層と、

前記第1導電層の上に設けられ、その周辺回路領域側の端部が前記メモリセル領域側に後退した絶縁層と、

前記分離酸化膜の上に、前記第1導電層および前記絶縁層を覆うように設けられた第2導電層と、を含むフラッシュメモリ。

【請求項6】

半導体基板の上に絶縁膜と導電層を順次形成する第1工程と、

第2の絶縁膜を形成する第2工程と、

前記第2の絶縁膜の上にレジストパターンを形成する第3工程と、

前記レジストパターンをマスクに用いて、前記第2の絶縁膜と前記導電層をドライエッチングする第4工程と、

前記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする第5工程と、

前記レジストパターンをマスクに用いて、前記絶縁膜をウエットエッチングする第6工程と、を備えた、半導体装置の製造方法。

【請求項7】

前記第5工程は、N2雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項6に記載の半導体装置の製造方法。

【請求項8】

前記第5工程は、乾燥空気雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項6に記載の半導体装置の製造方法。

【請求項9】

前記第5工程は、乾燥空気雰囲気中、前記レジストパターンを熱処理することにより行なう、請求項6に記載の半導体装置の製造方法。

【請求項10】

半導体基板の表面に、メモリセル領域と周辺回路領域を分離する分離酸化膜を形成する第1工程と、

前記半導体基板の表面上にトンネル酸化膜を形成する第2工程と、

前記トンネル酸化膜の上に第1ポリシリコン層を形成する第3工程と、

前記トンネル酸化膜と前記第1ポリシリコン層を所望の形にパターニングする第4工程と、

前記第1ポリシリコン層の上に絶縁膜を形成する第5工程と、

前記絶縁膜の上に、その端部が分離酸化膜上に位置し、かつ前記メモリセル領域のみを覆う、レジストパターンを形成する第6工程と、

前記レジストパターンをマスクに用いて、前記周辺回路領域の上にある、前記絶縁膜および前記第1ポリシリコン層をドライエッチングにより除去する第7工程と、

前記レジストパターンの表面変質層と、該レジストパターンの表面より下にある正常な部分をくっつけ、これらを剥がれなくする第8工程と、

前記レジストパターンを再びマスクに用いて、前記周辺回路領域の上にある前記トンネル酸化膜をウエットエッチングにより除去する第9工程と、

前記レジストパターンを除去する第10工程と、

前記半導体基板の上であって、前記周辺回路領域の上に、周辺トランジスタ用のゲート酸化膜を形成する第11工程と、

前記半導体基板の上に第2ポリシリコン層を形成する第12工程と、

前記第2ポリシリコン層の上に、エッチングマスク用の酸化膜を形成する第13工程と、

前記メモリセル領域にコントロールゲートを形成し、周辺回路のトランジスタゲートを形成する第14工程と、

前記絶縁膜および前記第1ポリシリコン層をパターニングし、フローティングゲートを形成する第15工程と、を備えたフラッシュメモリの製造方法。

【請求項11】

前記第8工程は、N2雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む、請求項10に記載のフラッシュメモリの製造方法。

【請求項12】

前記第8工程は、乾燥空気雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む、請求項10に記載のフラッシュメモリの製造方法。

【請求項13】

前記第8工程は、乾燥空気雰囲気中、前記レジストパターンを熱処理することにより行なう、請求項10に記載のフラッシュメモリの製造方法。

【請求項14】

半導体基板の表面に、分離酸化膜を形成する第1工程と、

前記半導体基板上にゲート酸化膜を成膜する第2工程と、

前記ゲート酸化膜上に第1ポリシリコン層を成膜する第3工程と、

活性領域から分離酸化膜上に及ぶような開口部を有するレジストパターンを形成する第4工程と、

前記レジストパターンをマスクとして、前記第1ポリシリコン層をドライエッチングにより除去する第5工程と、

前記レジストパターンの表面の変質層と表面より下にある正常な部分をくっつけ、これらを剥がれなくする第6工程と、

前記レジストパターンを再びマスクに用いて、パターン底のゲート酸化膜をウエットエッチングにより除去する第7工程と、

前記レジストパターンを除去する第8工程と、

第2ポリシリコン層を形成する第9工程と、

アクセストランジスタ、ドライバトランジスタ、周辺回路のトランジスタのゲート電極となるパターンをレジストにて形成する第10工程と、

前記レジストパターンをマスクとして、前記第1ポリシリコン層、前記第2ポリシリコン層をドライエッチングする第11工程と、

前記レジストパターンを除去する第12工程と、

n領域のみにn型不純物をドーピングする第13工程と、

熱処理を行なう第14工程と、を備えた、スタティックランダムアクセスメモリの製造方法。

【請求項15】

前記第6工程は、N2雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項14に記載のスタティックランダムアクセスメモリの製造方法。

【請求項16】

前記第6工程は、乾燥空気雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項14に記載のスタティックランダムアクセスメモリの製造方法。

【請求項17】

前記第6工程は、乾燥空気雰囲気中、前記レジストパターンを熱処理することにより行なう、請求項14に記載のスタティックランダムアクセスメモリの製造方法。

【請求項1】

半導体基板の上に絶縁膜と導電層を順次形成する第1工程と、

前記導電層の上にレジストパターンを形成する第2工程と、

前記レジストパターンをマスクに用いて、前記導電層をドライエッチングする第3工程と、

前記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする第4工程と、

前記レジストパターンをマスクに用いて、前記絶縁膜をウエットエッチングする第5工程と、を備えた半導体装置の製造方法。

【請求項2】

前記第4工程は、N2雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第4工程は、乾燥空気雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項1に記載の半導体装置の製造方法。

【請求項4】

前記第4工程は、乾燥空気雰囲気中、前記レジストパターンを熱処理することにより行なう、請求項1に記載の半導体装置の製造方法。

【請求項5】

半導体基板と、

前記半導体基板の上に設けられたダミーゲート領域と、

前記半導体基板の上に、前記ダミーゲート領域を挟むように設けられたメモリセル領域と周辺回路領域と、を備え、

前記ダミーゲート領域は、

前記半導体基板の上に形成された分離酸化膜と、

前記分離酸化膜の上に設けられ、その周辺回路領域側の端部が前記メモリセル領域側に後退した第1導電層と、

前記第1導電層の上に設けられ、その周辺回路領域側の端部が前記メモリセル領域側に後退した絶縁層と、

前記分離酸化膜の上に、前記第1導電層および前記絶縁層を覆うように設けられた第2導電層と、を含むフラッシュメモリ。

【請求項6】

半導体基板の上に絶縁膜と導電層を順次形成する第1工程と、

第2の絶縁膜を形成する第2工程と、

前記第2の絶縁膜の上にレジストパターンを形成する第3工程と、

前記レジストパターンをマスクに用いて、前記第2の絶縁膜と前記導電層をドライエッチングする第4工程と、

前記レジストパターンの表面の変質層と、該レジストパターンの表面より下にある正常な層とをくっつけ、これらを剥がれなくする第5工程と、

前記レジストパターンをマスクに用いて、前記絶縁膜をウエットエッチングする第6工程と、を備えた、半導体装置の製造方法。

【請求項7】

前記第5工程は、N2雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項6に記載の半導体装置の製造方法。

【請求項8】

前記第5工程は、乾燥空気雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項6に記載の半導体装置の製造方法。

【請求項9】

前記第5工程は、乾燥空気雰囲気中、前記レジストパターンを熱処理することにより行なう、請求項6に記載の半導体装置の製造方法。

【請求項10】

半導体基板の表面に、メモリセル領域と周辺回路領域を分離する分離酸化膜を形成する第1工程と、

前記半導体基板の表面上にトンネル酸化膜を形成する第2工程と、

前記トンネル酸化膜の上に第1ポリシリコン層を形成する第3工程と、

前記トンネル酸化膜と前記第1ポリシリコン層を所望の形にパターニングする第4工程と、

前記第1ポリシリコン層の上に絶縁膜を形成する第5工程と、

前記絶縁膜の上に、その端部が分離酸化膜上に位置し、かつ前記メモリセル領域のみを覆う、レジストパターンを形成する第6工程と、

前記レジストパターンをマスクに用いて、前記周辺回路領域の上にある、前記絶縁膜および前記第1ポリシリコン層をドライエッチングにより除去する第7工程と、

前記レジストパターンの表面変質層と、該レジストパターンの表面より下にある正常な部分をくっつけ、これらを剥がれなくする第8工程と、

前記レジストパターンを再びマスクに用いて、前記周辺回路領域の上にある前記トンネル酸化膜をウエットエッチングにより除去する第9工程と、

前記レジストパターンを除去する第10工程と、

前記半導体基板の上であって、前記周辺回路領域の上に、周辺トランジスタ用のゲート酸化膜を形成する第11工程と、

前記半導体基板の上に第2ポリシリコン層を形成する第12工程と、

前記第2ポリシリコン層の上に、エッチングマスク用の酸化膜を形成する第13工程と、

前記メモリセル領域にコントロールゲートを形成し、周辺回路のトランジスタゲートを形成する第14工程と、

前記絶縁膜および前記第1ポリシリコン層をパターニングし、フローティングゲートを形成する第15工程と、を備えたフラッシュメモリの製造方法。

【請求項11】

前記第8工程は、N2雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む、請求項10に記載のフラッシュメモリの製造方法。

【請求項12】

前記第8工程は、乾燥空気雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、熱処理する工程であることを含む、請求項10に記載のフラッシュメモリの製造方法。

【請求項13】

前記第8工程は、乾燥空気雰囲気中、前記レジストパターンを熱処理することにより行なう、請求項10に記載のフラッシュメモリの製造方法。

【請求項14】

半導体基板の表面に、分離酸化膜を形成する第1工程と、

前記半導体基板上にゲート酸化膜を成膜する第2工程と、

前記ゲート酸化膜上に第1ポリシリコン層を成膜する第3工程と、

活性領域から分離酸化膜上に及ぶような開口部を有するレジストパターンを形成する第4工程と、

前記レジストパターンをマスクとして、前記第1ポリシリコン層をドライエッチングにより除去する第5工程と、

前記レジストパターンの表面の変質層と表面より下にある正常な部分をくっつけ、これらを剥がれなくする第6工程と、

前記レジストパターンを再びマスクに用いて、パターン底のゲート酸化膜をウエットエッチングにより除去する第7工程と、

前記レジストパターンを除去する第8工程と、

第2ポリシリコン層を形成する第9工程と、

アクセストランジスタ、ドライバトランジスタ、周辺回路のトランジスタのゲート電極となるパターンをレジストにて形成する第10工程と、

前記レジストパターンをマスクとして、前記第1ポリシリコン層、前記第2ポリシリコン層をドライエッチングする第11工程と、

前記レジストパターンを除去する第12工程と、

n領域のみにn型不純物をドーピングする第13工程と、

熱処理を行なう第14工程と、を備えた、スタティックランダムアクセスメモリの製造方法。

【請求項15】

前記第6工程は、N2雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項14に記載のスタティックランダムアクセスメモリの製造方法。

【請求項16】

前記第6工程は、乾燥空気雰囲気中で前記レジストパターンの表面にディープ紫外光を照射し、その後、該レジストパターンを熱処理する工程を含む、請求項14に記載のスタティックランダムアクセスメモリの製造方法。

【請求項17】

前記第6工程は、乾燥空気雰囲気中、前記レジストパターンを熱処理することにより行なう、請求項14に記載のスタティックランダムアクセスメモリの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【公開番号】特開2011−129936(P2011−129936A)

【公開日】平成23年6月30日(2011.6.30)

【国際特許分類】

【出願番号】特願2011−1124(P2011−1124)

【出願日】平成23年1月6日(2011.1.6)

【分割の表示】特願2000−7585(P2000−7585)の分割

【原出願日】平成12年1月17日(2000.1.17)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【出願人】(591036505)株式会社ルネサスセミコンダクタエンジニアリング (6)

【Fターム(参考)】

【公開日】平成23年6月30日(2011.6.30)

【国際特許分類】

【出願日】平成23年1月6日(2011.1.6)

【分割の表示】特願2000−7585(P2000−7585)の分割

【原出願日】平成12年1月17日(2000.1.17)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【出願人】(591036505)株式会社ルネサスセミコンダクタエンジニアリング (6)

【Fターム(参考)】

[ Back to top ]