半導体装置の製造方法、半導体装置及び電子機器

【課題】半導体装置に含まれる貫通孔を微細化した場合であっても、メッキで貫通孔の内部に貫通電極を形成する。

【解決手段】半導体装置100の製造方法は、基板10の表面10a側にシード層30を形成するシード層形成工程と、シード層形成工程後、シード層30上に配線層40を形成する配線層形成工程と、配線層形成工程後、基板10の裏面10bからシード層30に達する貫通孔10cを形成する貫通孔形成工程と、貫通孔形成工程後、貫通孔10c内にメッキで貫通電極60を形成する貫通電極形成工程と、貫通電極形成工程後、シード層30を複数に分断する分断工程とを含んでいる。

【解決手段】半導体装置100の製造方法は、基板10の表面10a側にシード層30を形成するシード層形成工程と、シード層形成工程後、シード層30上に配線層40を形成する配線層形成工程と、配線層形成工程後、基板10の裏面10bからシード層30に達する貫通孔10cを形成する貫通孔形成工程と、貫通孔形成工程後、貫通孔10c内にメッキで貫通電極60を形成する貫通電極形成工程と、貫通電極形成工程後、シード層30を複数に分断する分断工程とを含んでいる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法、半導体装置及び電子機器に関する。

【背景技術】

【0002】

近年、小型化、高精度化しているセンサーパッケージにおいて、配線を引きまわす際にTSV(Through Silicon Vias)を応用した形態が望まれている。そして、TSVにおいては接続配線の微細化が求められており、それに伴い貫通孔が微細化する傾向にある。

ところで、半導体基板に形成された貫通孔に電解メッキ法を用いて貫通電極を形成する場合、この貫通孔の内部に拡散防止層(例えばチタンタングステン(TiW)やチタン(Ti)を含んだ膜)やシード層を形成することは既に知られている(例えば、特許文献1を参照)。また、上記シード層は、例えば銅(Cu)や金(Au)等をスパッタすることで形成されることも既に知られている。

【0003】

以下、特許文献1に記載の貫通電極の製造方法を、図5を用いて簡単に説明する。前記製造方法は、図5(a)に示すように、まず半導体基板10の一方の面10aに第1絶縁膜20を形成する。そして、第1絶縁膜20上にパターニングされた配線層40を形成する。その後、半導体基板10の他方の面10b側から配線層40に達する貫通孔10cを形成する。次に、図5(b)に示すように、貫通孔10cが形成されて露出した半導体基板10及び第1絶縁膜20の壁面と、半導体基板10の他方の面10b上とに第2絶縁膜50を形成する。そして、第2絶縁膜50と配線層40とを覆うようにシード層30を形成する。最後に、図5(c)に示すように、電解メッキを実施して、貫通孔10cの内部に貫通電極60を形成する。この貫通電極60は、第2絶縁膜50及びシード層30を介して、貫通孔10cの内部にメッキを充填することで形成される。メッキを充填できる理由は、電解メッキを実施した場合、シード層30の表面からメッキが成長するからである。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−218689号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、近年の半導体装置の微細化により、端子ピッチは狭くなり、それに伴い貫通孔10cが微細化する傾向がある。微細化した貫通孔10cに上述した貫通電極の製造方法を用いると、以下のような方法となる。

まず、図6(a)に示すように、微細化した貫通孔10cの内部に第2絶縁膜50を形成する。その後、シード層50を形成する場合、例えばスパッタ法を用いると、図6(b)に示すように、半導体基板10の他方の面10b上及び貫通孔10cの開口部近傍にはシード層50は形成される。

【0006】

しかしながら、配線層40の近傍(いわゆる、ビア底)までシード層50を形成することは困難となる場合がある。このため、電解メッキ法を用いて電極を形成した場合、ビア底近傍においては電極が形成されない場合がある。ゆえに、貫通孔10cが微細化した場合には、電解メッキ法を用いて貫通孔10cの内部に貫通電極60を形成するのが困難となるといった課題がある。

【0007】

そこで、本発明は、このような事情に鑑みてなされたものであって、貫通孔を微細化した場合であっても、メッキで貫通孔の内部に貫通電極を形成することができる半導体装置の製造方法、その製造方法により製造された半導体装置及びその半導体装置を用いた電子機器を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題を解決するための本発明の一態様は、半導体基板の一方の面側にシード層を形成するシード層形成工程と、前記シード層形成工程後、前記シード層上に配線層を形成する配線層形成工程と、前記配線層形成工程後、前記半導体基板の他方の面から前記シード層に達する貫通孔を形成する貫通孔形成工程と、前記貫通孔形成工程後、前記貫通孔内にメッキで貫通電極を形成する貫通電極形成工程と、前記貫通電極形成工程後、前記シード層を複数に分断する分断工程とを含むことを特徴とする半導体装置の製造方法である。

【0009】

上記態様の製造方法は、シード層上に配線層を形成する工程と、半導体基板の他方の面からシード層に達する貫通孔を形成する工程とを含んでいる。つまり、半導体基板の一方の面側に予めシード層を形成し、その後、貫通孔を形成しているので、貫通孔に貫通電極をメッキで形成する際には、ビア底にあるシード層は表面が露出した状態となっている。このため、貫通孔が微細化した場合であっても、ビア底にあるシード層からメッキを成長させることができるので、貫通孔の内部をメッキで充填することができる。ゆえに、貫通孔の内部に貫通電極を形成することができ、その結果、貫通電極と配線層とを電気的に接続することができる。

【0010】

また、本発明の別の態様は、前記分断工程を、ダイシングライン上で導通しているシード層をダイシングラインに沿ってダイシングすることとしても良い。

上記態様の製造方法は、ダイシングライン上で導通しているシード層をダイシングラインに沿ってダイシングする工程を含んでいる。このため、例えばエッチング等の方法を用いることなくシード層を電気的に絶縁することができるので、半導体装置の製造を容易にすることができる。

【0011】

また、本発明の別の態様は、半導体基板と、前記半導体基板の一方の面側に形成されたシード層と、前記シード層上に形成された配線層と、前記半導体基板の他方の面から前記半導体基板を貫通して前記シード層に接続する貫通電極とを含むことを特徴とする半導体装置である。

上記態様の半導体装置は、シード層上に形成された配線層と、半導体基板の他方の面から半導体基板及び第1絶縁膜を貫通してシード層に接続する貫通電極とを含んでいる。このため、貫通孔が微細化した場合であっても、貫通電極と配線層とは導通をとることができる。よって、半導体装置が小型化した場合(つまり、端子ピッチが狭くなった場合)であっても、その半導体装置を動作させることができる。

【0012】

また、本発明の別の態様は、上記態様の半導体装置を含むことを特徴とする電子機器である。

上記態様の電子機器は、上記態様の半導体装置を含んでいる。このため、電子機器を小型化した場合であっても、半導体装置を動作させることができる。よって、その電子機器を動作させることができる。

【図面の簡単な説明】

【0013】

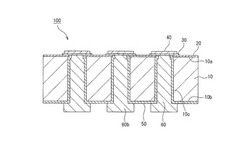

【図1】本発明の実施形態に係る半導体装置を示す断面図。

【図2】本発明の実施形態に係る半導体装置の製造方法を示す断面図。

【図3】配線層形成工程後の能動面側から見た平面図。

【図4】ダイシングによるシード層の分断を示す図。

【図5】従来の半導体装置の製造方法を示す断面図(その1)。

【図6】従来の半導体装置の製造方法を示す断面図(その2)。

【発明を実施するための形態】

【0014】

以下、本発明の実施形態に係る半導体装置、その製造方法、半導体装置を含んだ電子機器の順に図を参照しつつ説明する。

(1)半導体装置の構成

まず、本発明の実施形態に係る半導体装置の構成について、図1を用いて説明する。図1は、本発明の実施形態に係る半導体装置の断面図である。本実施形態に係る半導体装置100は、半導体基板10(以下、単に「基板10」ともいう。)を有している。基板10としては、例えばシリコン(Si)基板等が用いられる。また、基板10は、一方の面10a(以下、単に「表面10a」ともいう。)と、一方の面10aの反対側にある他方の面10b(以下、単に「裏面10b」ともいう。)とを有している。

【0015】

基板10の表面10a上には、第1絶縁膜20が形成されている。第1絶縁膜20としては、例えばシリコン酸化膜(SiO2膜)等が用いられる。

基板10及び第1絶縁膜20には、基板10及び第1絶縁膜20を貫通する貫通孔10cが形成されている。ここで、基板10に形成された貫通孔10cの内径は、第1絶縁膜20に形成された貫通孔10cの内径よりも大きくなっている。

【0016】

第1絶縁膜20上には、貫通孔10cに対応する位置に電解メッキ用シード層30(以下、単に「シード層30」ともいう。)が形成されている。シード層30の材料としては、例えばCuやAu等が用いられる。なお、図1に示すように、貫通孔10cを複数形成する場合には、シード層30をそれぞれ電気的に分断する。

シード層30上には、配線層40が形成されている。配線層40の材料としては、導電材料であれば良く、例えばアルミ(Al)等が用いられる。なお、配線層40は、実装する際にパッド電極として機能する。また、シード層30と同様に、貫通孔10cを複数形成する場合には、配線層40をそれぞれ電気的に分断する。

【0017】

貫通孔10cが形成された基板10及び第1絶縁膜20の壁面と、基板10の裏面10b上とには、第2絶縁膜50が形成されている。第2絶縁膜50としては、例えばSiO2膜等が用いられる。

貫通孔10cの内部には、第2絶縁膜50を介して貫通電極60が形成されている。その貫通電極60は、基板10の裏面10b上に形成された第2絶縁膜50上の一部にも連続して形成される。貫通電極60の材料としては、例えばCu等が用いられる。

なお、この貫通電極60は、シード層30を介して配線層40と電気的に接続される。

【0018】

また、図1に示すように、貫通電極60を複数形成する場合には、貫通電極60をそれぞれ電気的に分断する。

また、貫通電極60と第2絶縁膜50との間には、貫通電極60の材料が基板10に拡散することを防止する目的で拡散防止層(つまり、バリア層)を形成しても良い。この拡散防止層を形成することで、貫通電極60の材料が基板10に拡散することで生じる電流のリーク等を防止することができる。拡散防止層としては、例えばTiWやTi等を含んだ膜が用いられる。

【0019】

以上のように、上記態様であれば、シード層30上に形成された配線層40と、基板10の裏面10b側から基板10及び第1絶縁膜20を貫通してシード層30に接続する貫通電極60とを含んでいる。このため、端子ピッチが狭い場合であっても、貫通電極60と配線層40との間で導通をとることができる。よって、半導体装置100が小型化した場合であっても、その半導体装置を動作させることができる。

【0020】

(2)半導体装置の製造方法

次に、半導体装置100の製造方法について、図2を用いて説明する。図2(a)〜(h)は、半導体装置100の製造方法に含まれる各製造工程を示す概略断面図である。

以下、各製造工程について説明する。図2(a)は第1絶縁膜形成工程、シード層形成工程及び配線層形成工程を示す断面図である。そして、図3は、配線層形成工程後の能動面側から見た平面図である。

【0021】

(2.1)第1絶縁膜形成工程

まず、基板10の表面10a上に第1絶縁膜20を形成する第1絶縁膜形成工程を実施する。第1絶縁膜20の形成は、例えば基板10の表面10aを酸化する等の通常の半導体プロセスを用いて形成する。本実施形態では、通常の半導体プロセスを用いて、基板10の表面10a上に例えばSiO2膜を形成し、それを第1絶縁膜20とする。

【0022】

(2.2)シード層形成工程

次に、第1絶縁膜20上にシード層30を形成するシード層形成工程を実施する。本実施形態では、例えばCuやAuのスパッタや化学気相成長(CVD:Chemical Vapor Deposition)により、第1絶縁膜20上にCu層やAu層を形成し、それをシード層30とする。なお、シード層30は、後述する貫通電極60形成後に電気的に分断される。このため、図3に示すように、シード層30を分断しやすいように、予めパターニングして第1絶縁膜20上に形成することが望ましい。ただし、後工程にてシード層30の分断が可能であれば、第1絶縁膜20上の全面にシード層30を形成(いわゆる、全面ベタ形成)しても良い。なお、図3において破線で示された箇所は、貫通電極60が形成される位置60a(つまり、貫通孔10cが形成される位置)を示している。

【0023】

(2.3)配線層形成工程

次に、シード層30上に配線層40を形成する配線層形成工程を実施する。本実施形態では、例えばAl等を用いて配線層40を形成する。配線層40を形成する際、通常の半導体プロセスを用いることができる。なお、配線層40は、シード層30を介して、後述する貫通電極形成工程で形成する貫通電極60と電気的に接続されている。

【0024】

(2.4)貫通孔形成工程

次に、基板10及び第1絶縁膜20に貫通孔10cを形成する貫通孔形成工程を実施する。貫通孔形成工程では、図2(b)に示すように、基板10の裏面10b側にドライエッチング用マスク200(以下、単に「マスク200」ともいう。)をフォトレジストにより形成する。マスク200には、貫通孔10cの平面断面形状に対応する開口部200aが設けられている。そして、開口部200aから(つまり、裏面10b側から)基板10及び第1絶縁膜20をドライエッチングすることにより、基板10及び第1絶縁膜20を貫通してシード層30に達する貫通孔10cを形成する(図2(c)を参照)。

なお、本実施形態において、基板10の開口径(つまり、貫通孔10cの内径)は10μm〜30μm程度である。

【0025】

また、このドライエッチングに使用するガスとしては、基板10がSi基板であり、第1絶縁膜20がSiO2膜である場合には、例えばSF6とO2との混合ガス(SF6+O2)やC4F8とO2との混合ガス(C4F8+O2)等を用いることができる。

また、一種類のガスで基板10と第1絶縁膜20とをドライエッチングする場合には、基板10と第1絶縁膜20とのエッチングレートの違いにより、基板10に形成された貫通孔10cの内径は、第1絶縁膜20に形成された貫通孔10cの内径よりも大きくなる(図2(c)を参照)。

【0026】

(2.5)第2絶縁膜形成工程

次に、貫通孔10cの内部に第2絶縁膜を形成する第2絶縁膜形成工程を実施する。第2絶縁膜形成工程では、図2(d)に示すように、貫通孔10cの形成により露出した基板10の壁面及び第1絶縁膜20の壁面と、基板10の裏面10bとに第2絶縁膜50を形成する。つまり、シード層30上に第2絶縁膜50は形成されておらず、第2絶縁膜50は貫通孔10cの内部で露出した状態となっている。本実施形態では、例えばCVD法によりSiO2膜を形成し、そのSiO2膜を第2絶縁膜50としている。なお、図2(c)に示すように、第2絶縁膜形成工程を実施する前に、貫通孔形成工程で形成されたマスク200は除去される。

第2絶縁膜形成工程を実施することで、貫通孔形成工程において露出させたシード層30が第2絶縁膜50で再度覆われる場合もあるが、この場合には、貫通孔形成工程で用いたドライエッチングを再度実施することで、第2絶縁膜50で覆われたシード層30の表面を露出させることができる。

【0027】

(2.6)貫通電極形成工程

次に、貫通孔10cの内部に、第2絶縁膜50を介して貫通電極60を形成する貫通電極形成工程を実施する。貫通電極形成工程では、図2(e)に示すように、基板10の裏面10b側に形成された第2絶縁膜50上に電解メッキ用マスク300(以下、単に「マスク300」ともいう。)をフォトレジストにより形成する。この際、マスク300で貫通孔10cの開口部を塞がないようにマスク300を形成する。マスク300には、貫通孔10cの内径よりも大きな径を有する開口部300aが設けられている。

【0028】

次に、電解メッキにより、貫通孔10cの内部に貫通電極60を形成する。シード層30を例えばCu層で形成した場合、電解メッキすると、露出したCu層の表面からCuメッキが成長する。その結果、貫通孔10cの内部はCuメッキで充填され、この充填されたCuメッキが貫通電極60となる。

なお、メッキ時間は、メッキが貫通孔10cの内部を充填し、さらに裏面10b側に10μm〜20μm程度成長するまでとする。その後、電解メッキ用マスク300を除去して、裏面端子60bを含んだ貫通電極60を形成する(図2(f)を参照)。

【0029】

(2.7)分断工程

次に、シード層30を電気的に分断する分断工程を実施する。分断工程では、図2(g)に示すように、シード層30及び配線層40を覆うようにウェットエッチング用マスク400(以下、単に「マスク400」ともいう。)をフォトレジストにより形成する。次に、例えば過硫酸アンモニウム水溶液または過硫酸ナトリウム水溶液等でシード層30をウェットエッチングする。これにより、マスク400で覆われた部分以外のシード層30はエッチングされる。こうして、シード層30を電気的に分断する。

最後に、マスク400を除去して、図2(h)に示すように、貫通孔10cの内部に貫通電極60が形成された半導体装置100が完成する。

【0030】

以上のように、上記態様では、貫通孔10cは基板10の裏面10b側からシード層30に達するようにして形成されている。このため、貫通孔10cを微細化した場合であっても、ビア底においてシード層30を露出させることができる。その結果、電解メッキをした場合には、ビア底にあるシード層30の表面からメッキを成長させることができ、貫通孔10cの内部にメッキを充填することができる。その結果、貫通孔10cの内部に貫通電極60を形成することができる。ゆえに、微細ピッチ、微細な径に対応した導通電極の形状が可能となり、半導体装置の高精細化、小型化が可能となる。

【0031】

また、その他の作用・効果としては、高アスペクト比対応が可能であるので、薄膜化するリスクを回避することもできる。

なお、本実施形態では、シード層50の分断方法として、ウェットエッチングによる分断方法について説明したが、これに限定されるものではない。ウェットエッチングに代えて、例えばレーザーを用いて選択的にシード層50を分断しても良いし、ダイシング等を用いて個片化する際にシード層50を分断しても良い。

【0032】

そこで、以下、ダイシングによるシード層50の分断について説明する。図4は、ダイシングによるシード層50の分断工程を示す図である。図4(a)と(b)は、ダイシング前のシード層50とダイシング後のシード層50をそれぞれ示している。

図4(a)に示すように、ダイシング前、シード層50はダイシングライン500上で電気的に接続されている。そして、このダイシングライン500に沿って、ダイシングすることで、図4(b)に示すように、シード層30は電気的に分断される。

上記態様であれば、ダイシングライン500上で導通しているシード層50をダイシングライン500に沿ってダイシングするので、例えばウェットエッチング等の方法を用いることなくシード層50を電気的に絶縁することができる。よって、半導体装置100の製造を容易にすることができる。

【0033】

また、本実施形態では、第2絶縁膜としてSiO2膜を形成することについて説明したが、これに限定されるものではない。第2絶縁膜は、絶縁性が確保できるものであれば良く、無機材料、有機材料を問わない。

また、本実施形態では、第2絶縁膜形成工程後に貫通電極形成工程を実施することについて説明したが、これに限定されるものではない。例えば、第2絶縁膜形成工程後に、貫通電極60の材料が基板10に拡散することを防止する拡散防止層を形成する拡散防止層形成工程を実施しても良い。この拡散防止層を形成することで、貫通電極60の材料が基板10に拡散することで生じる電流のリーク等を防止することができる。拡散防止層としては、例えばTiWやTi等を含んだ膜が用いられる。

【0034】

(3)電子機器

本実施形態に係る電子機器は、上記態様の半導体装置100を含んだものである。このため、電子機器を小型化した場合であっても、半導体装置100を動作させることができる。よって、その電子機器を動作させることができる。

なお、上記態様の製造方法、上記態様の半導体装置及び上記態様の電子機器は、例えばCMOSやCCD等の各種センサー及びその製造方法への適用が可能である。

【符号の説明】

【0035】

10 半導体基板、10a 表面、10b 裏面、10c 貫通孔、20 第1絶縁膜、30 シード層、40 配線層、50 第2絶縁膜、60 貫通電極、60a 貫通電極が形成される位置、60b 裏面端子、100 半導体装置、200 マスク、200a 開口部、300 マスク、300a 開口部、400 マスク、500 ダイシングライン

【技術分野】

【0001】

本発明は、半導体装置の製造方法、半導体装置及び電子機器に関する。

【背景技術】

【0002】

近年、小型化、高精度化しているセンサーパッケージにおいて、配線を引きまわす際にTSV(Through Silicon Vias)を応用した形態が望まれている。そして、TSVにおいては接続配線の微細化が求められており、それに伴い貫通孔が微細化する傾向にある。

ところで、半導体基板に形成された貫通孔に電解メッキ法を用いて貫通電極を形成する場合、この貫通孔の内部に拡散防止層(例えばチタンタングステン(TiW)やチタン(Ti)を含んだ膜)やシード層を形成することは既に知られている(例えば、特許文献1を参照)。また、上記シード層は、例えば銅(Cu)や金(Au)等をスパッタすることで形成されることも既に知られている。

【0003】

以下、特許文献1に記載の貫通電極の製造方法を、図5を用いて簡単に説明する。前記製造方法は、図5(a)に示すように、まず半導体基板10の一方の面10aに第1絶縁膜20を形成する。そして、第1絶縁膜20上にパターニングされた配線層40を形成する。その後、半導体基板10の他方の面10b側から配線層40に達する貫通孔10cを形成する。次に、図5(b)に示すように、貫通孔10cが形成されて露出した半導体基板10及び第1絶縁膜20の壁面と、半導体基板10の他方の面10b上とに第2絶縁膜50を形成する。そして、第2絶縁膜50と配線層40とを覆うようにシード層30を形成する。最後に、図5(c)に示すように、電解メッキを実施して、貫通孔10cの内部に貫通電極60を形成する。この貫通電極60は、第2絶縁膜50及びシード層30を介して、貫通孔10cの内部にメッキを充填することで形成される。メッキを充填できる理由は、電解メッキを実施した場合、シード層30の表面からメッキが成長するからである。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−218689号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、近年の半導体装置の微細化により、端子ピッチは狭くなり、それに伴い貫通孔10cが微細化する傾向がある。微細化した貫通孔10cに上述した貫通電極の製造方法を用いると、以下のような方法となる。

まず、図6(a)に示すように、微細化した貫通孔10cの内部に第2絶縁膜50を形成する。その後、シード層50を形成する場合、例えばスパッタ法を用いると、図6(b)に示すように、半導体基板10の他方の面10b上及び貫通孔10cの開口部近傍にはシード層50は形成される。

【0006】

しかしながら、配線層40の近傍(いわゆる、ビア底)までシード層50を形成することは困難となる場合がある。このため、電解メッキ法を用いて電極を形成した場合、ビア底近傍においては電極が形成されない場合がある。ゆえに、貫通孔10cが微細化した場合には、電解メッキ法を用いて貫通孔10cの内部に貫通電極60を形成するのが困難となるといった課題がある。

【0007】

そこで、本発明は、このような事情に鑑みてなされたものであって、貫通孔を微細化した場合であっても、メッキで貫通孔の内部に貫通電極を形成することができる半導体装置の製造方法、その製造方法により製造された半導体装置及びその半導体装置を用いた電子機器を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題を解決するための本発明の一態様は、半導体基板の一方の面側にシード層を形成するシード層形成工程と、前記シード層形成工程後、前記シード層上に配線層を形成する配線層形成工程と、前記配線層形成工程後、前記半導体基板の他方の面から前記シード層に達する貫通孔を形成する貫通孔形成工程と、前記貫通孔形成工程後、前記貫通孔内にメッキで貫通電極を形成する貫通電極形成工程と、前記貫通電極形成工程後、前記シード層を複数に分断する分断工程とを含むことを特徴とする半導体装置の製造方法である。

【0009】

上記態様の製造方法は、シード層上に配線層を形成する工程と、半導体基板の他方の面からシード層に達する貫通孔を形成する工程とを含んでいる。つまり、半導体基板の一方の面側に予めシード層を形成し、その後、貫通孔を形成しているので、貫通孔に貫通電極をメッキで形成する際には、ビア底にあるシード層は表面が露出した状態となっている。このため、貫通孔が微細化した場合であっても、ビア底にあるシード層からメッキを成長させることができるので、貫通孔の内部をメッキで充填することができる。ゆえに、貫通孔の内部に貫通電極を形成することができ、その結果、貫通電極と配線層とを電気的に接続することができる。

【0010】

また、本発明の別の態様は、前記分断工程を、ダイシングライン上で導通しているシード層をダイシングラインに沿ってダイシングすることとしても良い。

上記態様の製造方法は、ダイシングライン上で導通しているシード層をダイシングラインに沿ってダイシングする工程を含んでいる。このため、例えばエッチング等の方法を用いることなくシード層を電気的に絶縁することができるので、半導体装置の製造を容易にすることができる。

【0011】

また、本発明の別の態様は、半導体基板と、前記半導体基板の一方の面側に形成されたシード層と、前記シード層上に形成された配線層と、前記半導体基板の他方の面から前記半導体基板を貫通して前記シード層に接続する貫通電極とを含むことを特徴とする半導体装置である。

上記態様の半導体装置は、シード層上に形成された配線層と、半導体基板の他方の面から半導体基板及び第1絶縁膜を貫通してシード層に接続する貫通電極とを含んでいる。このため、貫通孔が微細化した場合であっても、貫通電極と配線層とは導通をとることができる。よって、半導体装置が小型化した場合(つまり、端子ピッチが狭くなった場合)であっても、その半導体装置を動作させることができる。

【0012】

また、本発明の別の態様は、上記態様の半導体装置を含むことを特徴とする電子機器である。

上記態様の電子機器は、上記態様の半導体装置を含んでいる。このため、電子機器を小型化した場合であっても、半導体装置を動作させることができる。よって、その電子機器を動作させることができる。

【図面の簡単な説明】

【0013】

【図1】本発明の実施形態に係る半導体装置を示す断面図。

【図2】本発明の実施形態に係る半導体装置の製造方法を示す断面図。

【図3】配線層形成工程後の能動面側から見た平面図。

【図4】ダイシングによるシード層の分断を示す図。

【図5】従来の半導体装置の製造方法を示す断面図(その1)。

【図6】従来の半導体装置の製造方法を示す断面図(その2)。

【発明を実施するための形態】

【0014】

以下、本発明の実施形態に係る半導体装置、その製造方法、半導体装置を含んだ電子機器の順に図を参照しつつ説明する。

(1)半導体装置の構成

まず、本発明の実施形態に係る半導体装置の構成について、図1を用いて説明する。図1は、本発明の実施形態に係る半導体装置の断面図である。本実施形態に係る半導体装置100は、半導体基板10(以下、単に「基板10」ともいう。)を有している。基板10としては、例えばシリコン(Si)基板等が用いられる。また、基板10は、一方の面10a(以下、単に「表面10a」ともいう。)と、一方の面10aの反対側にある他方の面10b(以下、単に「裏面10b」ともいう。)とを有している。

【0015】

基板10の表面10a上には、第1絶縁膜20が形成されている。第1絶縁膜20としては、例えばシリコン酸化膜(SiO2膜)等が用いられる。

基板10及び第1絶縁膜20には、基板10及び第1絶縁膜20を貫通する貫通孔10cが形成されている。ここで、基板10に形成された貫通孔10cの内径は、第1絶縁膜20に形成された貫通孔10cの内径よりも大きくなっている。

【0016】

第1絶縁膜20上には、貫通孔10cに対応する位置に電解メッキ用シード層30(以下、単に「シード層30」ともいう。)が形成されている。シード層30の材料としては、例えばCuやAu等が用いられる。なお、図1に示すように、貫通孔10cを複数形成する場合には、シード層30をそれぞれ電気的に分断する。

シード層30上には、配線層40が形成されている。配線層40の材料としては、導電材料であれば良く、例えばアルミ(Al)等が用いられる。なお、配線層40は、実装する際にパッド電極として機能する。また、シード層30と同様に、貫通孔10cを複数形成する場合には、配線層40をそれぞれ電気的に分断する。

【0017】

貫通孔10cが形成された基板10及び第1絶縁膜20の壁面と、基板10の裏面10b上とには、第2絶縁膜50が形成されている。第2絶縁膜50としては、例えばSiO2膜等が用いられる。

貫通孔10cの内部には、第2絶縁膜50を介して貫通電極60が形成されている。その貫通電極60は、基板10の裏面10b上に形成された第2絶縁膜50上の一部にも連続して形成される。貫通電極60の材料としては、例えばCu等が用いられる。

なお、この貫通電極60は、シード層30を介して配線層40と電気的に接続される。

【0018】

また、図1に示すように、貫通電極60を複数形成する場合には、貫通電極60をそれぞれ電気的に分断する。

また、貫通電極60と第2絶縁膜50との間には、貫通電極60の材料が基板10に拡散することを防止する目的で拡散防止層(つまり、バリア層)を形成しても良い。この拡散防止層を形成することで、貫通電極60の材料が基板10に拡散することで生じる電流のリーク等を防止することができる。拡散防止層としては、例えばTiWやTi等を含んだ膜が用いられる。

【0019】

以上のように、上記態様であれば、シード層30上に形成された配線層40と、基板10の裏面10b側から基板10及び第1絶縁膜20を貫通してシード層30に接続する貫通電極60とを含んでいる。このため、端子ピッチが狭い場合であっても、貫通電極60と配線層40との間で導通をとることができる。よって、半導体装置100が小型化した場合であっても、その半導体装置を動作させることができる。

【0020】

(2)半導体装置の製造方法

次に、半導体装置100の製造方法について、図2を用いて説明する。図2(a)〜(h)は、半導体装置100の製造方法に含まれる各製造工程を示す概略断面図である。

以下、各製造工程について説明する。図2(a)は第1絶縁膜形成工程、シード層形成工程及び配線層形成工程を示す断面図である。そして、図3は、配線層形成工程後の能動面側から見た平面図である。

【0021】

(2.1)第1絶縁膜形成工程

まず、基板10の表面10a上に第1絶縁膜20を形成する第1絶縁膜形成工程を実施する。第1絶縁膜20の形成は、例えば基板10の表面10aを酸化する等の通常の半導体プロセスを用いて形成する。本実施形態では、通常の半導体プロセスを用いて、基板10の表面10a上に例えばSiO2膜を形成し、それを第1絶縁膜20とする。

【0022】

(2.2)シード層形成工程

次に、第1絶縁膜20上にシード層30を形成するシード層形成工程を実施する。本実施形態では、例えばCuやAuのスパッタや化学気相成長(CVD:Chemical Vapor Deposition)により、第1絶縁膜20上にCu層やAu層を形成し、それをシード層30とする。なお、シード層30は、後述する貫通電極60形成後に電気的に分断される。このため、図3に示すように、シード層30を分断しやすいように、予めパターニングして第1絶縁膜20上に形成することが望ましい。ただし、後工程にてシード層30の分断が可能であれば、第1絶縁膜20上の全面にシード層30を形成(いわゆる、全面ベタ形成)しても良い。なお、図3において破線で示された箇所は、貫通電極60が形成される位置60a(つまり、貫通孔10cが形成される位置)を示している。

【0023】

(2.3)配線層形成工程

次に、シード層30上に配線層40を形成する配線層形成工程を実施する。本実施形態では、例えばAl等を用いて配線層40を形成する。配線層40を形成する際、通常の半導体プロセスを用いることができる。なお、配線層40は、シード層30を介して、後述する貫通電極形成工程で形成する貫通電極60と電気的に接続されている。

【0024】

(2.4)貫通孔形成工程

次に、基板10及び第1絶縁膜20に貫通孔10cを形成する貫通孔形成工程を実施する。貫通孔形成工程では、図2(b)に示すように、基板10の裏面10b側にドライエッチング用マスク200(以下、単に「マスク200」ともいう。)をフォトレジストにより形成する。マスク200には、貫通孔10cの平面断面形状に対応する開口部200aが設けられている。そして、開口部200aから(つまり、裏面10b側から)基板10及び第1絶縁膜20をドライエッチングすることにより、基板10及び第1絶縁膜20を貫通してシード層30に達する貫通孔10cを形成する(図2(c)を参照)。

なお、本実施形態において、基板10の開口径(つまり、貫通孔10cの内径)は10μm〜30μm程度である。

【0025】

また、このドライエッチングに使用するガスとしては、基板10がSi基板であり、第1絶縁膜20がSiO2膜である場合には、例えばSF6とO2との混合ガス(SF6+O2)やC4F8とO2との混合ガス(C4F8+O2)等を用いることができる。

また、一種類のガスで基板10と第1絶縁膜20とをドライエッチングする場合には、基板10と第1絶縁膜20とのエッチングレートの違いにより、基板10に形成された貫通孔10cの内径は、第1絶縁膜20に形成された貫通孔10cの内径よりも大きくなる(図2(c)を参照)。

【0026】

(2.5)第2絶縁膜形成工程

次に、貫通孔10cの内部に第2絶縁膜を形成する第2絶縁膜形成工程を実施する。第2絶縁膜形成工程では、図2(d)に示すように、貫通孔10cの形成により露出した基板10の壁面及び第1絶縁膜20の壁面と、基板10の裏面10bとに第2絶縁膜50を形成する。つまり、シード層30上に第2絶縁膜50は形成されておらず、第2絶縁膜50は貫通孔10cの内部で露出した状態となっている。本実施形態では、例えばCVD法によりSiO2膜を形成し、そのSiO2膜を第2絶縁膜50としている。なお、図2(c)に示すように、第2絶縁膜形成工程を実施する前に、貫通孔形成工程で形成されたマスク200は除去される。

第2絶縁膜形成工程を実施することで、貫通孔形成工程において露出させたシード層30が第2絶縁膜50で再度覆われる場合もあるが、この場合には、貫通孔形成工程で用いたドライエッチングを再度実施することで、第2絶縁膜50で覆われたシード層30の表面を露出させることができる。

【0027】

(2.6)貫通電極形成工程

次に、貫通孔10cの内部に、第2絶縁膜50を介して貫通電極60を形成する貫通電極形成工程を実施する。貫通電極形成工程では、図2(e)に示すように、基板10の裏面10b側に形成された第2絶縁膜50上に電解メッキ用マスク300(以下、単に「マスク300」ともいう。)をフォトレジストにより形成する。この際、マスク300で貫通孔10cの開口部を塞がないようにマスク300を形成する。マスク300には、貫通孔10cの内径よりも大きな径を有する開口部300aが設けられている。

【0028】

次に、電解メッキにより、貫通孔10cの内部に貫通電極60を形成する。シード層30を例えばCu層で形成した場合、電解メッキすると、露出したCu層の表面からCuメッキが成長する。その結果、貫通孔10cの内部はCuメッキで充填され、この充填されたCuメッキが貫通電極60となる。

なお、メッキ時間は、メッキが貫通孔10cの内部を充填し、さらに裏面10b側に10μm〜20μm程度成長するまでとする。その後、電解メッキ用マスク300を除去して、裏面端子60bを含んだ貫通電極60を形成する(図2(f)を参照)。

【0029】

(2.7)分断工程

次に、シード層30を電気的に分断する分断工程を実施する。分断工程では、図2(g)に示すように、シード層30及び配線層40を覆うようにウェットエッチング用マスク400(以下、単に「マスク400」ともいう。)をフォトレジストにより形成する。次に、例えば過硫酸アンモニウム水溶液または過硫酸ナトリウム水溶液等でシード層30をウェットエッチングする。これにより、マスク400で覆われた部分以外のシード層30はエッチングされる。こうして、シード層30を電気的に分断する。

最後に、マスク400を除去して、図2(h)に示すように、貫通孔10cの内部に貫通電極60が形成された半導体装置100が完成する。

【0030】

以上のように、上記態様では、貫通孔10cは基板10の裏面10b側からシード層30に達するようにして形成されている。このため、貫通孔10cを微細化した場合であっても、ビア底においてシード層30を露出させることができる。その結果、電解メッキをした場合には、ビア底にあるシード層30の表面からメッキを成長させることができ、貫通孔10cの内部にメッキを充填することができる。その結果、貫通孔10cの内部に貫通電極60を形成することができる。ゆえに、微細ピッチ、微細な径に対応した導通電極の形状が可能となり、半導体装置の高精細化、小型化が可能となる。

【0031】

また、その他の作用・効果としては、高アスペクト比対応が可能であるので、薄膜化するリスクを回避することもできる。

なお、本実施形態では、シード層50の分断方法として、ウェットエッチングによる分断方法について説明したが、これに限定されるものではない。ウェットエッチングに代えて、例えばレーザーを用いて選択的にシード層50を分断しても良いし、ダイシング等を用いて個片化する際にシード層50を分断しても良い。

【0032】

そこで、以下、ダイシングによるシード層50の分断について説明する。図4は、ダイシングによるシード層50の分断工程を示す図である。図4(a)と(b)は、ダイシング前のシード層50とダイシング後のシード層50をそれぞれ示している。

図4(a)に示すように、ダイシング前、シード層50はダイシングライン500上で電気的に接続されている。そして、このダイシングライン500に沿って、ダイシングすることで、図4(b)に示すように、シード層30は電気的に分断される。

上記態様であれば、ダイシングライン500上で導通しているシード層50をダイシングライン500に沿ってダイシングするので、例えばウェットエッチング等の方法を用いることなくシード層50を電気的に絶縁することができる。よって、半導体装置100の製造を容易にすることができる。

【0033】

また、本実施形態では、第2絶縁膜としてSiO2膜を形成することについて説明したが、これに限定されるものではない。第2絶縁膜は、絶縁性が確保できるものであれば良く、無機材料、有機材料を問わない。

また、本実施形態では、第2絶縁膜形成工程後に貫通電極形成工程を実施することについて説明したが、これに限定されるものではない。例えば、第2絶縁膜形成工程後に、貫通電極60の材料が基板10に拡散することを防止する拡散防止層を形成する拡散防止層形成工程を実施しても良い。この拡散防止層を形成することで、貫通電極60の材料が基板10に拡散することで生じる電流のリーク等を防止することができる。拡散防止層としては、例えばTiWやTi等を含んだ膜が用いられる。

【0034】

(3)電子機器

本実施形態に係る電子機器は、上記態様の半導体装置100を含んだものである。このため、電子機器を小型化した場合であっても、半導体装置100を動作させることができる。よって、その電子機器を動作させることができる。

なお、上記態様の製造方法、上記態様の半導体装置及び上記態様の電子機器は、例えばCMOSやCCD等の各種センサー及びその製造方法への適用が可能である。

【符号の説明】

【0035】

10 半導体基板、10a 表面、10b 裏面、10c 貫通孔、20 第1絶縁膜、30 シード層、40 配線層、50 第2絶縁膜、60 貫通電極、60a 貫通電極が形成される位置、60b 裏面端子、100 半導体装置、200 マスク、200a 開口部、300 マスク、300a 開口部、400 マスク、500 ダイシングライン

【特許請求の範囲】

【請求項1】

半導体基板の一方の面側にシード層を形成するシード層形成工程と、

前記シード層形成工程後、前記シード層上に配線層を形成する配線層形成工程と、

前記配線層形成工程後、前記半導体基板の他方の面から前記シード層に達する貫通孔を形成する貫通孔形成工程と、

前記貫通孔形成工程後、前記貫通孔内にメッキで貫通電極を形成する貫通電極形成工程と、

前記貫通電極形成工程後、前記シード層を複数に分断する分断工程とを含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記分断工程は、ダイシングライン上で導通しているシード層をダイシングラインに沿ってダイシングすることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

半導体基板と、

前記半導体基板の一方の面側に形成されたシード層と、

前記シード層上に形成された配線層と、

前記半導体基板の他方の面から前記半導体基板を貫通して前記シード層に接続する貫通電極とを含むことを特徴とする半導体装置。

【請求項4】

請求項3に記載の半導体装置を含むことを特徴とする電子機器。

【請求項1】

半導体基板の一方の面側にシード層を形成するシード層形成工程と、

前記シード層形成工程後、前記シード層上に配線層を形成する配線層形成工程と、

前記配線層形成工程後、前記半導体基板の他方の面から前記シード層に達する貫通孔を形成する貫通孔形成工程と、

前記貫通孔形成工程後、前記貫通孔内にメッキで貫通電極を形成する貫通電極形成工程と、

前記貫通電極形成工程後、前記シード層を複数に分断する分断工程とを含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記分断工程は、ダイシングライン上で導通しているシード層をダイシングラインに沿ってダイシングすることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

半導体基板と、

前記半導体基板の一方の面側に形成されたシード層と、

前記シード層上に形成された配線層と、

前記半導体基板の他方の面から前記半導体基板を貫通して前記シード層に接続する貫通電極とを含むことを特徴とする半導体装置。

【請求項4】

請求項3に記載の半導体装置を含むことを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−98369(P2013−98369A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−240065(P2011−240065)

【出願日】平成23年11月1日(2011.11.1)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年11月1日(2011.11.1)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]