半導体装置の製造方法、半導体装置

【課題】Niシリサイドを用いてSiC上で信頼性の高い低抵抗の電極を低コストで得る。

【解決手段】n型SiC層11上にNi層12が形成される(図1(a))。熱処理を行うことによってNi層12のNiとn型SiC層11のSiとを反応させ、Niシリサイド層13を形成させる(図1(b))。この状態で酸化雰囲気中で熱処理を行う(図1(d))。還元雰囲気中で例えば300〜400℃で熱処理を行う(図1(f):還元処理工程)。これにより、酸化層15は還元され、Ni等で構成された還元層16となる。この還元層16は、ウェットエッチングで除去することができる(図1(g):エッチング工程)。その後、Niシリサイド層13の上に配線層となるTi/Al層30を形成する(図1(h))。

【解決手段】n型SiC層11上にNi層12が形成される(図1(a))。熱処理を行うことによってNi層12のNiとn型SiC層11のSiとを反応させ、Niシリサイド層13を形成させる(図1(b))。この状態で酸化雰囲気中で熱処理を行う(図1(d))。還元雰囲気中で例えば300〜400℃で熱処理を行う(図1(f):還元処理工程)。これにより、酸化層15は還元され、Ni等で構成された還元層16となる。この還元層16は、ウェットエッチングで除去することができる(図1(g):エッチング工程)。その後、Niシリサイド層13の上に配線層となるTi/Al層30を形成する(図1(h))。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、炭化珪素(SiC)を用いた半導体装置の製造方法、特に電極の形成方法に関する。また、この製造方法によって製造された半導体装置に関する。

【背景技術】

【0002】

炭化珪素(SiC)は、その禁制帯幅がシリコン等と比べて広いため、パワー素子等の材料として極めて有望である。これを用いてMOSFET(Metal Oxide Semiconductor Field Effect Transistor)や、そのショットキー接合が用いられたショットキーダイオード(SBD:Schottky Barrier Diode)等が実現されている。

【0003】

こうした素子を形成するに際しては、半導体材料であるSiC上に形成された電極を介してSiCに電流を流すことができる。この際の電極としては、SiCとの間の電流−電圧特性(I−V特性)に整流性のあるショットキー電極と、整流性がなくコンタクト抵抗の低いオーミック電極の2種類がある。一般に、これらの電極は金属材料で構成され、n型SiC、p型SiCのそれぞれに対して各種の材料が使用できることが知られている。

【0004】

このうち、n型SiCに対するオーミック電極は、MOSFETやSBD等の電極として広く用いられる。n型SiCに対して良好なオーミック特性をもつ(I−V特性に整流性がなくコンタクト抵抗が低い)電極の材料としては、例えば特許文献1に記載されるように、ニッケル(Ni)が知られている。ただし、良好なオーミック特性をもつのはNiとn型SiCとの間ではなく、正確にはNiとSiの化合物であるNiシリサイド(NixSiy)とn型SiCとの間である。Niシリサイドは、SiC表面にNiを形成した後に熱処理を行い、NiとSiCとの間の化学反応によって形成される。この化学反応式は(1)式で表される。

【0005】

【数1】

【0006】

ここで、(x、y)=(1、1)、(x、y)=(1、2)等である。この場合、NixSiyが形成されると同時に、SiCからC(炭素)単体が遊離する。このCは、Niシリサイド中を動き、その表面や内部で凝集し、グラファイトとして析出する。一方、Niシリサイドはオーミック電極として機能するものの、実際には配線となる他の金属材料(Au、Al等)をこの上に形成する必要がある。このため、例えばこの上にTi/Al等の配線材料が更に積層される。以上の工程を模式化して示した工程断面図が図5(a)〜(d)である。

【0007】

まず、n型SiC層11の清浄な表面に、Ni層12が蒸着やスパッタリング法によって形成される(図5(a))。その後、この状態で1000℃程度の熱処理を施すことにより、Niシリサイド層13が(1)式の反応によって形成される(図5(b))。なお、この図ではNi層12全体がNiシリサイド層13となっているように記載しているが、実際にはNi層12の最表面付近はシリサイド化されずに純Niの状態となっている場合もある。この場合には、残った純Ni層はウェットエッチング等によって選択的に除去でき、最終的に図5(b)の形態とすることができる。

【0008】

ここで、図5(b)の状態において、(1)式で示されたように、グラファイト14も同時に形成される。このグラファイト14は、Niシリサイド層13の内部や表面に分布する。次に、Ni層12を形成した場合と同様にして、この上に配線材料となるTi/Al層30(下層にチタン(Ti)、上層にアルミニウム(Al)を配した積層構造:配線層)が形成され、最終的な電極構造となる(図5(c))。この際に、Ti/Al層30のTiとNiシリサイド層13との間の密着性は良好であるものの、Tiとグラファイト14との間の密着性は低い。このため、図5(d)に示されるように、その後の工程、あるいはこの半導体素子の動作中において、Ti/Al層30とNiシリサイド層13の間で剥離が発生することがある。

【0009】

こうした剥離を抑制するために、特許文献1では、熱処理後にNiシリサイド層13の表面をプラズマエッチングによって除去することにより、表面のグラファイト14を除去している。また、特許文献2では、(1)非酸化性の熱処理を行うことによってNiシリサイド層13の内部のグラファイト14を表面に移動させ、その後でこれをエッチングで除去すること、(2)酸化性の雰囲気で熱処理を行うことによって、表面に移動したグラファイト14(C)を酸化してCO、CO2の状態で気体として除去すること、が記載されている。このうち、(2)の方法は、表面のみならずNiシリサイド層13内部のグラファイト14も効率的に除去できるため、極めて有効である。

【0010】

こうした製造方法を用いて、SiCに対するオーミック電極を、Ni(Niシリサイド)を用いて得ることができる。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2003−243323号公報

【特許文献2】特開2007−184571号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

特許文献1に記載の方法では、Niシリサイド層13の最表面のグラファイト14を除去することは可能である。しかしながら、Niシリサイド層13内部のグラファイト14を除去することは困難である。この内部のグラファイト14によってNiシリサイド層13の機械的強度は低下するため、やはり電極の信頼性の低下の原因となる。

【0013】

これに対して、特許文献2に記載の方法では、グラファイト14の除去はNiシリサイド層13の表面、内部両方において有効に行われる。しかしながら、これを酸化して気体化する熱処理において、酸化されるのはグラファイト14だけではなく、同時にNiシリサイド層13も酸化される。このため、Niシリサイド層13の最表面には、Niの酸化物を主成分とし、Si、C等の酸化物も含む酸化層が形成される。この主成分であるNiの酸化物(NiO)は絶縁性であるために、電極抵抗の増大の原因となる。また、グラファイト14と同様に、この酸化層自身がこの上のTi/Al層30等の剥離の原因となることもある。更に、例えばNiOは硫酸等の強酸によってもエッチングすることができず、NiO等を他の材料からの高い選択性をもってエッチングすることは、ウェットエッチング、ドライエッチングのいずれによっても困難である。このため、表面の酸化層を除去するためには、酸化層を除去すべき箇所以外の部分をフォトレジスト等のマスクでカバーした上でエッチング処理を行う等の作業が必要になる。このため、工程が複雑になる。

【0014】

このように、Niシリサイドを用いてSiC上で信頼性の高い低抵抗の電極を低コストで得ることは困難であった。

【0015】

本発明は、かかる問題点に鑑みてなされたものであり、上記問題点を解決する発明を提供することを目的とする。

【課題を解決するための手段】

【0016】

本発明は、上記課題を解決すべく、以下に掲げる構成とした。

本発明の半導体装置の製造方法は、ニッケル(Ni)シリサイドを用いた電極が炭化珪素(SiC)層に接続された構成を具備する半導体装置の製造方法であって、SiC層の表面にNi層を形成するNi形成工程と、熱処理を施すことにより、前記Ni層と前記SiC層とを反応させることによってNiシリサイド層を形成するシリサイド形成工程と、前記Niシリサイド層の形成後に酸化雰囲気で熱処理を行う酸化雰囲気熱処理工程と、当該酸化雰囲気熱処理工程の後で、還元雰囲気中で前記シリサイド形成工程における熱処理の温度よりも低い温度で熱処理を行う還元処理工程と、Niに対するエッチング処理を行うエッチング工程と、を具備することを特徴とする。

本発明の半導体装置の製造方法は、前記エッチング工程後に、前記Niシリサイド層と接触するように配線層を形成する配線形成工程を具備することを特徴とする。

本発明の半導体装置の製造方法は、前記還元処理工程における熱処理の温度を300〜400℃の範囲とすることを特徴とする。

本発明の半導体装置の製造方法は、前記シリサイド形成工程と前記酸化雰囲気熱処理工程との間に、非酸化雰囲気中で前記シリサイド形成工程における熱処理の温度よりも低い温度で熱処理を行う非酸化雰囲気熱処理工程を具備することを特徴とする。

本発明の半導体装置の製造方法は、前記エッチング工程において、超音波洗浄処理を行うことを特徴とする。

本発明の半導体装置の製造方法は、前記SiC層表面に絶縁層を形成し、当該絶縁層に開口部を形成した後に前記Ni形成工程を行うことを特徴とする。

本発明の半導体装置の製造方法において、前記半導体装置は、前記SiC層に対するショットキー電極が前記SiC層の一方の主面側に形成され、前記SiC層に対するオーミック電極が前記SiC層の他方の主面側に形成されたSBD(Schottky Barrier Diode)であり、前記Ni形成工程におけるNi層は前記他方の主面側に形成され、前記酸化雰囲気熱処理工程と、前記還元処理工程との間に、前記一方の主面側に前記ショットキー電極を形成するショットキー電極形成工程を具備することを特徴とする。

本発明の半導体装置は、前記半導体装置の製造方法によって製造されたことを特徴とする。

【発明の効果】

【0017】

本発明は以上のように構成されているので、Niシリサイドを用いてSiC上で信頼性の高い低抵抗の電極を低コストで得ることができる。

【図面の簡単な説明】

【0018】

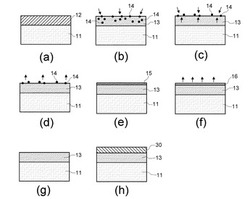

【図1】本発明の第1の実施の形態に係る半導体装置の製造方法の工程断面図である。

【図2】Niシリサイドを用いた電極とSiCとの間のI−V特性の還元処理温度依存性を示す図である。

【図3】本発明の第2の実施の形態に係る半導体装置の製造方法の工程断面図である。

【図4】本発明の第3の実施の形態に係る半導体装置の製造方法の工程断面図である。

【図5】Niシリサイドを電極に用いた従来の半導体装置の製造方法の一例を示す図である。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態となる半導体装置の製造方法につき説明する。ここで用いられる半導体装置を構成する材料は炭化珪素(SiC)であり、この製造方法は、その表面に電極を形成する方法である。この構造は、SiCが用いられる半導体装置全般、例えばMOSFET、SBD、MESFET等に用いられる。

【0020】

(第1の実施の形態)

第1の実施の形態となるこの製造方法は、n型SiCウェハの全面にNiシリサイドを用いたオーミック電極を形成する方法である。図1(a)〜(h)は、この半導体装置の製造方法を示す工程断面図である。ここでは、n型SiC上にNiシリサイドを用いた低抵抗のオーミック電極が形成される。一般に、Niシリサイドに直接ボンディング等を施すことは困難であるため、更にこの上には配線層となる他の電極材料が積層される。以下では、特にこの工程について説明する。

【0021】

まず、n型SiC層11上にNi層12が形成される(図1(a):Ni形成工程)。Ni層12は、蒸着(電子線加熱蒸着)やスパッタリング等、周知の成膜方法によって形成することができる。

【0022】

次に、熱処理を行うことによってNi層12のNiとn型SiC層11のSiとを反応させ、Niシリサイド層13を形成させる(図1(b):シリサイド形成工程)。この熱処理温度は900〜1200℃程度であり、これによって(1)式の反応が生じ、NixSiyからなるNiシリサイド層13が形成される。同時にグラファイト14も形成され、Niシリサイド層13の表面あるいは内部に析出する。なお、図1(b)ではNi層12全体がシリサイド化した場合について記載しているが、Ni層12が厚い場合には、最上部付近は未反応のNiが残存する場合もある。この場合においては、未反応のNiをウェットエッチングで除去することにより、図1(b)の形態となる。

【0023】

この状態において、低温での非酸化雰囲気熱処理を行う(図1(c):非酸化雰囲気熱処理工程)。この処理は、特許文献2に記載されたものと同様である。すなわち、特許文献2の段落番号0055に記載されるように、非酸化性ガス雰囲気中、100〜600℃の温度で熱処理を行う。これにより、Niシリサイド層13内部の炭素成分(グラファイト14)は表面に移動する。この工程においては、前記のシリサイド反応を発生させないために、その温度をシリサイド形成工程における熱処理の温度よりも低くする。

【0024】

次に、この状態で酸化雰囲気中で熱処理を行う(図1(d):酸化雰囲気熱処理工程)。この処理も、特許文献2に記載されたものと同様である。すなわち、表面の炭素成分(グラファイト14)は、CO、CO2となり、気体として除去される。従って、この工程により、炭素成分は除去される。

【0025】

以上の工程については、特許文献2に記載された従来の製造方法と同様である。

【0026】

この状態では、図1(e)に示されるように、グラファイト14の酸化と同時にNiシリサイド層13の表面も酸化し、その最表面には酸化層15が形成される。酸化層15は、NiOを主成分とし、SiO2等やC等が含まれる固体である。その主成分となるNiOは絶縁物であるために、Niシリサイド層13を電極として用いる際には、その電極抵抗の増大や剥離の原因となる。NiOは化学反応によって除去することが困難な材料である。特に、この酸化層15を他の材料からの高い選択性をもって化学的に除去することは困難である。

【0027】

本発明の実施の形態となる製造方法においては、この状態で、還元雰囲気(例えば0.1〜10%のH2が添加されたAr、N2雰囲気)中で例えば300〜400℃で熱処理を行う(図1(f):還元処理工程)。これにより、酸化層15は還元され、Ni等で構成された還元層16となる。なお、この熱処理温度が高いと、シリサイド反応が再度生じて再び炭素の析出が発生するため、この熱処理温度は前記のシリサイド形成工程よりも充分低い温度とする。具体例として、この還元処理工程を行わない場合と750℃で行った場合におけるNiシリサイド層13のコンタクト抵抗(I−V特性)を測定した結果を図2に示す。750℃の場合にはコンタクト抵抗が上昇していることが確認できる。一方、この温度が300℃よりも低いと還元の効果が小さくなる。このため、この熱処理温度は300〜400℃の範囲とすることが好ましい。

【0028】

この還元層16は、ウェットエッチングで除去することができる(図1(g):エッチング工程)。この場合には、純Niを他の物質に対して高い選択比でエッチングすることができる、硫酸やSPM(硫酸と過酸化水素水の混合)等を用いることができる。SiO2やC等は硫酸によってはエッチングされないが、これらは微粒子状となるため、超音波洗浄等、このウェットエッチング後の洗浄処理によって除去することが可能である。また、この時点で存在した炭素微粒子は酸には溶解しないため、特に超音波洗浄処理は有効である。このウェットエッチングにおいては、Ni、SiC、Niシリサイドの中で、特にNiに対する高い選択性が得られるため、フォトレジスト等によるマスキングは不要である。これにより、酸化層15が表面から除去されたNiシリサイド層13が得られる。

【0029】

なお、この工程においては残存したNiシリサイド層13の最表面が硫酸等によってやはり酸化されることがある。しかしながら、この場合に形成される酸化膜は前記の酸化層15と比べて非常に薄いため、これを除去するために、希フッ酸処理やプラズマ処理等によってこれを容易に除去することができる。

【0030】

その後、Niシリサイド層13の上に配線層となるTi/Al層30を形成する(図1(h):配線形成工程)。この際、グラファイト14は除去されており、Niシリサイド層13とTi/Al層30(特にTi)との間で良好な密着性が得られるため、剥離は発生しにくい。すなわち、信頼性の高い低抵抗の電極が得られる。

【0031】

上記の製造方法においては、還元処理工程とエッチング工程を行うことによって、酸化層15を除去している。この工程の際には、酸化層15を例えばドライエッチングで除去する場合のようなフォトレジストマスク等は不要である。このため、その上の剥離が発生せず信頼性の高い低抵抗の電極が用いられた半導体装置を低コストで得ることができる。

【0032】

(第2の実施の形態)

第1の実施の形態においては、SiCウェハの上面全面にNiシリサイド層を用いたオーミック電極を形成する例について記載した。しかしながら、実際には、絶縁層となるSiO2を形成し、その開口中で局所的にオーミック接続をとる必要がある場合が多い。この場合には、配線層を別途形成し、この配線層をこの開口中でNiシリサイド層に接触させた構造をとる。配線層は、ウェハ上の他の素子に接続された配線とされたり、ボンディングパッド等となるように、適宜パターニングされる。以下では、その場合の製造方法について記載する。図3(a)〜(g)は、この製造方法を示す工程断面図である。

【0033】

まず、n型SiC層11の上面にSiO2層41を形成し、その中に開口部を設ける(図3(a))。この開口部は、n型SiC層11に対してオーミック接続がなされる領域に対応する。SiO2層41はCVD法等によって成膜することができる。その後で、フォトリソグラフィ、エッチング(ウェットエッチング、ドライエッチング)を行うことにより、開口部を形成することができる。

【0034】

次に、この構造の開口部を含む上面全体にNi層12を形成する(図3(b):Ni形成工程)。この点については第1の実施の形態と同様である。Ni層12の厚さは、例えば50〜200nm程度とする。

【0035】

次に、熱処理を行い、Niシリサイド層13を形成する(図3(c):シリサイド形成工程)。この工程についても、第1の実施の形態と同様である。ただし、シリサイド反応はNi層12とn型SiC層11とが直接接する箇所でしか起こらないため、図3(c)に示されるように、Niシリサイド層13は開口部にのみ形成される。他の箇所(SiO2層41上)のNiは、そのまま未反応で残る。なお、第1の実施の形態と同様に、グラファイト14もNiシリサイド層13が形成された箇所において形成される。

【0036】

次に、この状態で酸化雰囲気中で熱処理を行う(図3(d):酸化雰囲気熱処理工程)。この工程も、第1の実施の形態と同様である。すなわち、これにより、グラファイト14が除去され、かつNiシリサイド層13の表面に酸化層15が形成される。また、SiO2層41上のNi層12も酸化され、酸化層15となる。

【0037】

次に、還元雰囲気中での熱処理を行う(図3(e):還元処理工程)。この工程も第1の実施の形態と同様である。これにより、Niシリサイド層13とSiO2層41上には還元されたNiを主成分とする還元層16が残される。

【0038】

次に、還元層16を、ウェットエッチングで除去する(図3(f):エッチング工程)。これにより、開口部においてNiシリサイド層13が露出し、かつSiO2層41上の還元層16も除去される。なお、酸化雰囲気熱処理工程において、SiO2層41上のNi層12全体が酸化されず、例えばその上部のみが酸化された場合においても、還元処理工程と酸化雰囲気熱処理工程を行うことにより、結局SiO2層41上のNiが全て除去される。これにより、SiO2層41上には導電性のNiは残らないため、この上に配線パターンを形成することが可能となる。

【0039】

次に、配線層となるTi/Al層30を、開口部中のNiシリサイド層13に接続されるように形成する(図3(g):配線形成工程)。この際、Ti/Al層30は、SiO2層41上の配線となるようなパターンとされる。これは、Ti/Al層30を全面に形成した後にフォトリソグラフィ、エッチングを行うことによって行われる。あるいは、フォトリソグラフィによってフォトレジストマスクを形成した後にTi/Al層30を形成し、リフトオフを行うことによってこのパターニングを行うことができる。

【0040】

上記の製造方法によって、SiCウェハにおいてNiシリサイドを用いて局所的にオーミック接合をとることが可能である。この上に、パターニングされた配線層を絶縁層を介して形成することができる。この場合においても、Niシリサイド層とその上の配線層との間の密着性を高くすることができ、信頼性の高い半導体装置を低コストで得ることができる。

【0041】

(第3の実施の形態)

第1、第2の実施の形態においては、n型SiCに対するNiシリサイドを用いたオーミック電極を形成する工程だけについて示されていた。これに対して、以下では、この製造方法を用いたSBD(Schottky Barrier Diode)の製造方法について説明する。このSBDにおいては、SiCウェハの上面(一方の主面)側にショットキー電極が形成され、下面(他方の主面)側に前記のNiシリサイドを用いたオーミック電極が形成される。この製造方法においては、Niシリサイド層表面に形成されたエッチング耐性の高い酸化層を保護膜として積極的に利用することができる。図4(a)〜(i)は、この製造方法を示す工程断面図である。

【0042】

まず、n型SiC層11(SiCウェハ)の上面側にSiO2層41、下面側にNi層12を形成する(図4(a):Ni形成工程)。SiO2層41は、CVD法等によって成膜することができ、Ni層12については前記と同様である。

【0043】

次に、前記のシリサイド形成工程を行う(図4(b))。この際の温度は前記の通り900〜1200℃程度である。ただし、この際には、雰囲気に少量のO2を混合させる。これにより、n型SiC層11近傍ではシリサイド反応が進みNiシリサイド層13が形成されると同時に、その表面(図中下側の面)は酸化される。なお、この際に、余剰炭素はCO、CO2となって気化する。このため、図1(e)と同様に、下面側においては、Niシリサイド層13の表面に酸化層14が形成される。

【0044】

次に、上面のSiO2層41に開口を形成する(図4(c):開口形成工程)。この開口によってSBDのショットキー接合面が規定される。また、この開口以外の箇所においては、ショットキー接合側の電極とn型SiC層11との間での絶縁が図られる。この開口は、フォトレジストをマスクとしたSiO2に対するウェットエッチング又はドライエッチングによって行うことができる。

【0045】

次に、ショットキー電極42をこの開口部を含む領域に形成する(図4(d):ショットキー電極形成工程)。ショットキー電極42は、n型SiC層11に対してショットキー接合を形成する、あるいは、この材料のシリサイドがn型SiCに対してショットキー接合を形成する材料が用いられ、例えばTiが用いられる。実際には、オーミック電極と同様に、この上にAl等が積層された積層構造が用いられる。ショットキー電極42のパターニングは、これを上面側全面に形成した後でフォトレジストをマスクとしたエッチングを行う、あるいはリフトオフ法を用いてパターニングすることができる。なお、良好なショットキー特性を得るために、前記のシリサイド形成工程における熱処理よりも低い温度での熱処理を行うこともできる。また、ショットキー電極42に接続された配線層をSiO2層41上に形成してもよい。

【0046】

ショットキー電極42とn型SiC層11との界面においては、SBDとしての動作が可能なようにショットキー障壁が形成されるが、このショットキー障壁は、この界面の状態、特に界面の反応によって変化する。このショットキー特性が良好に保たれるためには、ショットキー電極42が形成された以降の温度を400℃以下に保つことが必要である。このため、シリサイド化反応に高温を要するシリサイド形成工程はこの前に行うことが必要である。

【0047】

上記の工程において、開口形成工程やショットキー電極形成工程においては、複数回のフォトリソグラフィ(フォトレジストパターンの形成)、エッチングが行われる。この際には、SiCウェハの下面側と直接接触してその工程が行われる場合が多い。NiOを主成分とした酸化層14は、化学的に安定な材料であるため、こうした工程の際に、下面側におけるNiシリサイド層13の保護膜となる。すなわち、酸化雰囲気熱処理工程と還元処理工程との間にショットキー電極形成工程を行うことにより、ショットキー電極形成工程の際に酸化層14をそのままの状態で残しておくことができる。この際、オーミック電極の材料となるNiシリサイド層13が機械的、化学的に保護される。

【0048】

次に、この状態で前記の還元処理工程を行う(図4(e))。これにより、下面の酸化層14は、Niを主成分とする還元層15となる。また、この温度は、前記の通り300〜400℃であるため、上面側のショットキー接合に対して悪影響を与えない温度範囲である。

【0049】

次に、この構造における特にショットキー電極42等を保護するために、上面全体にフォトレジスト層50を形成する(図4(f))。

【0050】

この状態で、希フッ酸等を用いたウェットエッチングを行うことにより、Niを主成分とする還元層15は除去され、下面側にNiシリサイド層13が露出する(図4(g):エッチング工程)。フォトレジスト層50があるために、上面側のSiO2層41、ショットキー電極42等はこの影響を受けない。また、これらはフォトレジスト層50によって機械的にも保護される。この際には、希フッ酸の代わりに、Niをエッチングすることができ、かつフォトレジスト層50が耐性をもつ他のエッチング液を用いることもできる。

【0051】

次に、露出したNiシリサイド層13の表面に、配線層となるTi/Ni/Au層43を形成する(図4(h):配線形成工程)。

【0052】

次に、ウェット処理、アッシング処理等によってフォトレジスト層50を除去する(図4(i))。これにより、上面側にショットキー接合側、下面側にn型SiC側の電極が取り出された構成のSBDが得られる。このSBDを製造する際には、特に上面側の構造(ショットキー電極42等)を形成する際に、下面側に形成されている酸化層14がNiシリサイド層13の保護膜となる。このため、高い歩留まりで容易にこのSBDを製造することができる。また、Niシリサイド層13とTi/Ni/Au層43との間の密着性を高めることができることについては、第1、第2の実施の形態と同様である。

【0053】

なお、第3の実施の形態においても、n型SiC層11の下面にSiO2層を形成し、これに開口部を設けて第2の実施の形態と同様の工程を行うことができる。これにより、下面におけるオーミック接合を局所的にとり、これに接続された配線層を形成することも可能であり、この際にも酸化層を保護膜として用いることができる。

【0054】

なお、上記の例では、n型SiCに対してNiシリサイドを用いたオーミック電極を形成する場合について記載したが、n型以外(p型、半絶縁性)のSiCに対してNiシリサイドを用いた電極を形成する場合であっても、上記の製造方法が有効であることは明らかである。すなわち、この構造の電極は、SiCを用いたSBD、MOSFET、MESFET、pn接合ダイオード等、SiCに対して電気的接続をとることが必要な全ての半導体装置に対して有効である。このため、上記の製造方法も、これらの全ての半導体装置を製造する際に有効である。

【符号の説明】

【0055】

11 n型SiC層

12 Ni層

13 Niシリサイド層

14 グラファイト

15 酸化層

16 還元層

30 Ti/Al層(配線層)

41 SiO2層

42 ショットキー電極

43 Ti/Ni/Au層(配線層)

50 フォトレジスト層

【技術分野】

【0001】

本発明は、炭化珪素(SiC)を用いた半導体装置の製造方法、特に電極の形成方法に関する。また、この製造方法によって製造された半導体装置に関する。

【背景技術】

【0002】

炭化珪素(SiC)は、その禁制帯幅がシリコン等と比べて広いため、パワー素子等の材料として極めて有望である。これを用いてMOSFET(Metal Oxide Semiconductor Field Effect Transistor)や、そのショットキー接合が用いられたショットキーダイオード(SBD:Schottky Barrier Diode)等が実現されている。

【0003】

こうした素子を形成するに際しては、半導体材料であるSiC上に形成された電極を介してSiCに電流を流すことができる。この際の電極としては、SiCとの間の電流−電圧特性(I−V特性)に整流性のあるショットキー電極と、整流性がなくコンタクト抵抗の低いオーミック電極の2種類がある。一般に、これらの電極は金属材料で構成され、n型SiC、p型SiCのそれぞれに対して各種の材料が使用できることが知られている。

【0004】

このうち、n型SiCに対するオーミック電極は、MOSFETやSBD等の電極として広く用いられる。n型SiCに対して良好なオーミック特性をもつ(I−V特性に整流性がなくコンタクト抵抗が低い)電極の材料としては、例えば特許文献1に記載されるように、ニッケル(Ni)が知られている。ただし、良好なオーミック特性をもつのはNiとn型SiCとの間ではなく、正確にはNiとSiの化合物であるNiシリサイド(NixSiy)とn型SiCとの間である。Niシリサイドは、SiC表面にNiを形成した後に熱処理を行い、NiとSiCとの間の化学反応によって形成される。この化学反応式は(1)式で表される。

【0005】

【数1】

【0006】

ここで、(x、y)=(1、1)、(x、y)=(1、2)等である。この場合、NixSiyが形成されると同時に、SiCからC(炭素)単体が遊離する。このCは、Niシリサイド中を動き、その表面や内部で凝集し、グラファイトとして析出する。一方、Niシリサイドはオーミック電極として機能するものの、実際には配線となる他の金属材料(Au、Al等)をこの上に形成する必要がある。このため、例えばこの上にTi/Al等の配線材料が更に積層される。以上の工程を模式化して示した工程断面図が図5(a)〜(d)である。

【0007】

まず、n型SiC層11の清浄な表面に、Ni層12が蒸着やスパッタリング法によって形成される(図5(a))。その後、この状態で1000℃程度の熱処理を施すことにより、Niシリサイド層13が(1)式の反応によって形成される(図5(b))。なお、この図ではNi層12全体がNiシリサイド層13となっているように記載しているが、実際にはNi層12の最表面付近はシリサイド化されずに純Niの状態となっている場合もある。この場合には、残った純Ni層はウェットエッチング等によって選択的に除去でき、最終的に図5(b)の形態とすることができる。

【0008】

ここで、図5(b)の状態において、(1)式で示されたように、グラファイト14も同時に形成される。このグラファイト14は、Niシリサイド層13の内部や表面に分布する。次に、Ni層12を形成した場合と同様にして、この上に配線材料となるTi/Al層30(下層にチタン(Ti)、上層にアルミニウム(Al)を配した積層構造:配線層)が形成され、最終的な電極構造となる(図5(c))。この際に、Ti/Al層30のTiとNiシリサイド層13との間の密着性は良好であるものの、Tiとグラファイト14との間の密着性は低い。このため、図5(d)に示されるように、その後の工程、あるいはこの半導体素子の動作中において、Ti/Al層30とNiシリサイド層13の間で剥離が発生することがある。

【0009】

こうした剥離を抑制するために、特許文献1では、熱処理後にNiシリサイド層13の表面をプラズマエッチングによって除去することにより、表面のグラファイト14を除去している。また、特許文献2では、(1)非酸化性の熱処理を行うことによってNiシリサイド層13の内部のグラファイト14を表面に移動させ、その後でこれをエッチングで除去すること、(2)酸化性の雰囲気で熱処理を行うことによって、表面に移動したグラファイト14(C)を酸化してCO、CO2の状態で気体として除去すること、が記載されている。このうち、(2)の方法は、表面のみならずNiシリサイド層13内部のグラファイト14も効率的に除去できるため、極めて有効である。

【0010】

こうした製造方法を用いて、SiCに対するオーミック電極を、Ni(Niシリサイド)を用いて得ることができる。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2003−243323号公報

【特許文献2】特開2007−184571号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

特許文献1に記載の方法では、Niシリサイド層13の最表面のグラファイト14を除去することは可能である。しかしながら、Niシリサイド層13内部のグラファイト14を除去することは困難である。この内部のグラファイト14によってNiシリサイド層13の機械的強度は低下するため、やはり電極の信頼性の低下の原因となる。

【0013】

これに対して、特許文献2に記載の方法では、グラファイト14の除去はNiシリサイド層13の表面、内部両方において有効に行われる。しかしながら、これを酸化して気体化する熱処理において、酸化されるのはグラファイト14だけではなく、同時にNiシリサイド層13も酸化される。このため、Niシリサイド層13の最表面には、Niの酸化物を主成分とし、Si、C等の酸化物も含む酸化層が形成される。この主成分であるNiの酸化物(NiO)は絶縁性であるために、電極抵抗の増大の原因となる。また、グラファイト14と同様に、この酸化層自身がこの上のTi/Al層30等の剥離の原因となることもある。更に、例えばNiOは硫酸等の強酸によってもエッチングすることができず、NiO等を他の材料からの高い選択性をもってエッチングすることは、ウェットエッチング、ドライエッチングのいずれによっても困難である。このため、表面の酸化層を除去するためには、酸化層を除去すべき箇所以外の部分をフォトレジスト等のマスクでカバーした上でエッチング処理を行う等の作業が必要になる。このため、工程が複雑になる。

【0014】

このように、Niシリサイドを用いてSiC上で信頼性の高い低抵抗の電極を低コストで得ることは困難であった。

【0015】

本発明は、かかる問題点に鑑みてなされたものであり、上記問題点を解決する発明を提供することを目的とする。

【課題を解決するための手段】

【0016】

本発明は、上記課題を解決すべく、以下に掲げる構成とした。

本発明の半導体装置の製造方法は、ニッケル(Ni)シリサイドを用いた電極が炭化珪素(SiC)層に接続された構成を具備する半導体装置の製造方法であって、SiC層の表面にNi層を形成するNi形成工程と、熱処理を施すことにより、前記Ni層と前記SiC層とを反応させることによってNiシリサイド層を形成するシリサイド形成工程と、前記Niシリサイド層の形成後に酸化雰囲気で熱処理を行う酸化雰囲気熱処理工程と、当該酸化雰囲気熱処理工程の後で、還元雰囲気中で前記シリサイド形成工程における熱処理の温度よりも低い温度で熱処理を行う還元処理工程と、Niに対するエッチング処理を行うエッチング工程と、を具備することを特徴とする。

本発明の半導体装置の製造方法は、前記エッチング工程後に、前記Niシリサイド層と接触するように配線層を形成する配線形成工程を具備することを特徴とする。

本発明の半導体装置の製造方法は、前記還元処理工程における熱処理の温度を300〜400℃の範囲とすることを特徴とする。

本発明の半導体装置の製造方法は、前記シリサイド形成工程と前記酸化雰囲気熱処理工程との間に、非酸化雰囲気中で前記シリサイド形成工程における熱処理の温度よりも低い温度で熱処理を行う非酸化雰囲気熱処理工程を具備することを特徴とする。

本発明の半導体装置の製造方法は、前記エッチング工程において、超音波洗浄処理を行うことを特徴とする。

本発明の半導体装置の製造方法は、前記SiC層表面に絶縁層を形成し、当該絶縁層に開口部を形成した後に前記Ni形成工程を行うことを特徴とする。

本発明の半導体装置の製造方法において、前記半導体装置は、前記SiC層に対するショットキー電極が前記SiC層の一方の主面側に形成され、前記SiC層に対するオーミック電極が前記SiC層の他方の主面側に形成されたSBD(Schottky Barrier Diode)であり、前記Ni形成工程におけるNi層は前記他方の主面側に形成され、前記酸化雰囲気熱処理工程と、前記還元処理工程との間に、前記一方の主面側に前記ショットキー電極を形成するショットキー電極形成工程を具備することを特徴とする。

本発明の半導体装置は、前記半導体装置の製造方法によって製造されたことを特徴とする。

【発明の効果】

【0017】

本発明は以上のように構成されているので、Niシリサイドを用いてSiC上で信頼性の高い低抵抗の電極を低コストで得ることができる。

【図面の簡単な説明】

【0018】

【図1】本発明の第1の実施の形態に係る半導体装置の製造方法の工程断面図である。

【図2】Niシリサイドを用いた電極とSiCとの間のI−V特性の還元処理温度依存性を示す図である。

【図3】本発明の第2の実施の形態に係る半導体装置の製造方法の工程断面図である。

【図4】本発明の第3の実施の形態に係る半導体装置の製造方法の工程断面図である。

【図5】Niシリサイドを電極に用いた従来の半導体装置の製造方法の一例を示す図である。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態となる半導体装置の製造方法につき説明する。ここで用いられる半導体装置を構成する材料は炭化珪素(SiC)であり、この製造方法は、その表面に電極を形成する方法である。この構造は、SiCが用いられる半導体装置全般、例えばMOSFET、SBD、MESFET等に用いられる。

【0020】

(第1の実施の形態)

第1の実施の形態となるこの製造方法は、n型SiCウェハの全面にNiシリサイドを用いたオーミック電極を形成する方法である。図1(a)〜(h)は、この半導体装置の製造方法を示す工程断面図である。ここでは、n型SiC上にNiシリサイドを用いた低抵抗のオーミック電極が形成される。一般に、Niシリサイドに直接ボンディング等を施すことは困難であるため、更にこの上には配線層となる他の電極材料が積層される。以下では、特にこの工程について説明する。

【0021】

まず、n型SiC層11上にNi層12が形成される(図1(a):Ni形成工程)。Ni層12は、蒸着(電子線加熱蒸着)やスパッタリング等、周知の成膜方法によって形成することができる。

【0022】

次に、熱処理を行うことによってNi層12のNiとn型SiC層11のSiとを反応させ、Niシリサイド層13を形成させる(図1(b):シリサイド形成工程)。この熱処理温度は900〜1200℃程度であり、これによって(1)式の反応が生じ、NixSiyからなるNiシリサイド層13が形成される。同時にグラファイト14も形成され、Niシリサイド層13の表面あるいは内部に析出する。なお、図1(b)ではNi層12全体がシリサイド化した場合について記載しているが、Ni層12が厚い場合には、最上部付近は未反応のNiが残存する場合もある。この場合においては、未反応のNiをウェットエッチングで除去することにより、図1(b)の形態となる。

【0023】

この状態において、低温での非酸化雰囲気熱処理を行う(図1(c):非酸化雰囲気熱処理工程)。この処理は、特許文献2に記載されたものと同様である。すなわち、特許文献2の段落番号0055に記載されるように、非酸化性ガス雰囲気中、100〜600℃の温度で熱処理を行う。これにより、Niシリサイド層13内部の炭素成分(グラファイト14)は表面に移動する。この工程においては、前記のシリサイド反応を発生させないために、その温度をシリサイド形成工程における熱処理の温度よりも低くする。

【0024】

次に、この状態で酸化雰囲気中で熱処理を行う(図1(d):酸化雰囲気熱処理工程)。この処理も、特許文献2に記載されたものと同様である。すなわち、表面の炭素成分(グラファイト14)は、CO、CO2となり、気体として除去される。従って、この工程により、炭素成分は除去される。

【0025】

以上の工程については、特許文献2に記載された従来の製造方法と同様である。

【0026】

この状態では、図1(e)に示されるように、グラファイト14の酸化と同時にNiシリサイド層13の表面も酸化し、その最表面には酸化層15が形成される。酸化層15は、NiOを主成分とし、SiO2等やC等が含まれる固体である。その主成分となるNiOは絶縁物であるために、Niシリサイド層13を電極として用いる際には、その電極抵抗の増大や剥離の原因となる。NiOは化学反応によって除去することが困難な材料である。特に、この酸化層15を他の材料からの高い選択性をもって化学的に除去することは困難である。

【0027】

本発明の実施の形態となる製造方法においては、この状態で、還元雰囲気(例えば0.1〜10%のH2が添加されたAr、N2雰囲気)中で例えば300〜400℃で熱処理を行う(図1(f):還元処理工程)。これにより、酸化層15は還元され、Ni等で構成された還元層16となる。なお、この熱処理温度が高いと、シリサイド反応が再度生じて再び炭素の析出が発生するため、この熱処理温度は前記のシリサイド形成工程よりも充分低い温度とする。具体例として、この還元処理工程を行わない場合と750℃で行った場合におけるNiシリサイド層13のコンタクト抵抗(I−V特性)を測定した結果を図2に示す。750℃の場合にはコンタクト抵抗が上昇していることが確認できる。一方、この温度が300℃よりも低いと還元の効果が小さくなる。このため、この熱処理温度は300〜400℃の範囲とすることが好ましい。

【0028】

この還元層16は、ウェットエッチングで除去することができる(図1(g):エッチング工程)。この場合には、純Niを他の物質に対して高い選択比でエッチングすることができる、硫酸やSPM(硫酸と過酸化水素水の混合)等を用いることができる。SiO2やC等は硫酸によってはエッチングされないが、これらは微粒子状となるため、超音波洗浄等、このウェットエッチング後の洗浄処理によって除去することが可能である。また、この時点で存在した炭素微粒子は酸には溶解しないため、特に超音波洗浄処理は有効である。このウェットエッチングにおいては、Ni、SiC、Niシリサイドの中で、特にNiに対する高い選択性が得られるため、フォトレジスト等によるマスキングは不要である。これにより、酸化層15が表面から除去されたNiシリサイド層13が得られる。

【0029】

なお、この工程においては残存したNiシリサイド層13の最表面が硫酸等によってやはり酸化されることがある。しかしながら、この場合に形成される酸化膜は前記の酸化層15と比べて非常に薄いため、これを除去するために、希フッ酸処理やプラズマ処理等によってこれを容易に除去することができる。

【0030】

その後、Niシリサイド層13の上に配線層となるTi/Al層30を形成する(図1(h):配線形成工程)。この際、グラファイト14は除去されており、Niシリサイド層13とTi/Al層30(特にTi)との間で良好な密着性が得られるため、剥離は発生しにくい。すなわち、信頼性の高い低抵抗の電極が得られる。

【0031】

上記の製造方法においては、還元処理工程とエッチング工程を行うことによって、酸化層15を除去している。この工程の際には、酸化層15を例えばドライエッチングで除去する場合のようなフォトレジストマスク等は不要である。このため、その上の剥離が発生せず信頼性の高い低抵抗の電極が用いられた半導体装置を低コストで得ることができる。

【0032】

(第2の実施の形態)

第1の実施の形態においては、SiCウェハの上面全面にNiシリサイド層を用いたオーミック電極を形成する例について記載した。しかしながら、実際には、絶縁層となるSiO2を形成し、その開口中で局所的にオーミック接続をとる必要がある場合が多い。この場合には、配線層を別途形成し、この配線層をこの開口中でNiシリサイド層に接触させた構造をとる。配線層は、ウェハ上の他の素子に接続された配線とされたり、ボンディングパッド等となるように、適宜パターニングされる。以下では、その場合の製造方法について記載する。図3(a)〜(g)は、この製造方法を示す工程断面図である。

【0033】

まず、n型SiC層11の上面にSiO2層41を形成し、その中に開口部を設ける(図3(a))。この開口部は、n型SiC層11に対してオーミック接続がなされる領域に対応する。SiO2層41はCVD法等によって成膜することができる。その後で、フォトリソグラフィ、エッチング(ウェットエッチング、ドライエッチング)を行うことにより、開口部を形成することができる。

【0034】

次に、この構造の開口部を含む上面全体にNi層12を形成する(図3(b):Ni形成工程)。この点については第1の実施の形態と同様である。Ni層12の厚さは、例えば50〜200nm程度とする。

【0035】

次に、熱処理を行い、Niシリサイド層13を形成する(図3(c):シリサイド形成工程)。この工程についても、第1の実施の形態と同様である。ただし、シリサイド反応はNi層12とn型SiC層11とが直接接する箇所でしか起こらないため、図3(c)に示されるように、Niシリサイド層13は開口部にのみ形成される。他の箇所(SiO2層41上)のNiは、そのまま未反応で残る。なお、第1の実施の形態と同様に、グラファイト14もNiシリサイド層13が形成された箇所において形成される。

【0036】

次に、この状態で酸化雰囲気中で熱処理を行う(図3(d):酸化雰囲気熱処理工程)。この工程も、第1の実施の形態と同様である。すなわち、これにより、グラファイト14が除去され、かつNiシリサイド層13の表面に酸化層15が形成される。また、SiO2層41上のNi層12も酸化され、酸化層15となる。

【0037】

次に、還元雰囲気中での熱処理を行う(図3(e):還元処理工程)。この工程も第1の実施の形態と同様である。これにより、Niシリサイド層13とSiO2層41上には還元されたNiを主成分とする還元層16が残される。

【0038】

次に、還元層16を、ウェットエッチングで除去する(図3(f):エッチング工程)。これにより、開口部においてNiシリサイド層13が露出し、かつSiO2層41上の還元層16も除去される。なお、酸化雰囲気熱処理工程において、SiO2層41上のNi層12全体が酸化されず、例えばその上部のみが酸化された場合においても、還元処理工程と酸化雰囲気熱処理工程を行うことにより、結局SiO2層41上のNiが全て除去される。これにより、SiO2層41上には導電性のNiは残らないため、この上に配線パターンを形成することが可能となる。

【0039】

次に、配線層となるTi/Al層30を、開口部中のNiシリサイド層13に接続されるように形成する(図3(g):配線形成工程)。この際、Ti/Al層30は、SiO2層41上の配線となるようなパターンとされる。これは、Ti/Al層30を全面に形成した後にフォトリソグラフィ、エッチングを行うことによって行われる。あるいは、フォトリソグラフィによってフォトレジストマスクを形成した後にTi/Al層30を形成し、リフトオフを行うことによってこのパターニングを行うことができる。

【0040】

上記の製造方法によって、SiCウェハにおいてNiシリサイドを用いて局所的にオーミック接合をとることが可能である。この上に、パターニングされた配線層を絶縁層を介して形成することができる。この場合においても、Niシリサイド層とその上の配線層との間の密着性を高くすることができ、信頼性の高い半導体装置を低コストで得ることができる。

【0041】

(第3の実施の形態)

第1、第2の実施の形態においては、n型SiCに対するNiシリサイドを用いたオーミック電極を形成する工程だけについて示されていた。これに対して、以下では、この製造方法を用いたSBD(Schottky Barrier Diode)の製造方法について説明する。このSBDにおいては、SiCウェハの上面(一方の主面)側にショットキー電極が形成され、下面(他方の主面)側に前記のNiシリサイドを用いたオーミック電極が形成される。この製造方法においては、Niシリサイド層表面に形成されたエッチング耐性の高い酸化層を保護膜として積極的に利用することができる。図4(a)〜(i)は、この製造方法を示す工程断面図である。

【0042】

まず、n型SiC層11(SiCウェハ)の上面側にSiO2層41、下面側にNi層12を形成する(図4(a):Ni形成工程)。SiO2層41は、CVD法等によって成膜することができ、Ni層12については前記と同様である。

【0043】

次に、前記のシリサイド形成工程を行う(図4(b))。この際の温度は前記の通り900〜1200℃程度である。ただし、この際には、雰囲気に少量のO2を混合させる。これにより、n型SiC層11近傍ではシリサイド反応が進みNiシリサイド層13が形成されると同時に、その表面(図中下側の面)は酸化される。なお、この際に、余剰炭素はCO、CO2となって気化する。このため、図1(e)と同様に、下面側においては、Niシリサイド層13の表面に酸化層14が形成される。

【0044】

次に、上面のSiO2層41に開口を形成する(図4(c):開口形成工程)。この開口によってSBDのショットキー接合面が規定される。また、この開口以外の箇所においては、ショットキー接合側の電極とn型SiC層11との間での絶縁が図られる。この開口は、フォトレジストをマスクとしたSiO2に対するウェットエッチング又はドライエッチングによって行うことができる。

【0045】

次に、ショットキー電極42をこの開口部を含む領域に形成する(図4(d):ショットキー電極形成工程)。ショットキー電極42は、n型SiC層11に対してショットキー接合を形成する、あるいは、この材料のシリサイドがn型SiCに対してショットキー接合を形成する材料が用いられ、例えばTiが用いられる。実際には、オーミック電極と同様に、この上にAl等が積層された積層構造が用いられる。ショットキー電極42のパターニングは、これを上面側全面に形成した後でフォトレジストをマスクとしたエッチングを行う、あるいはリフトオフ法を用いてパターニングすることができる。なお、良好なショットキー特性を得るために、前記のシリサイド形成工程における熱処理よりも低い温度での熱処理を行うこともできる。また、ショットキー電極42に接続された配線層をSiO2層41上に形成してもよい。

【0046】

ショットキー電極42とn型SiC層11との界面においては、SBDとしての動作が可能なようにショットキー障壁が形成されるが、このショットキー障壁は、この界面の状態、特に界面の反応によって変化する。このショットキー特性が良好に保たれるためには、ショットキー電極42が形成された以降の温度を400℃以下に保つことが必要である。このため、シリサイド化反応に高温を要するシリサイド形成工程はこの前に行うことが必要である。

【0047】

上記の工程において、開口形成工程やショットキー電極形成工程においては、複数回のフォトリソグラフィ(フォトレジストパターンの形成)、エッチングが行われる。この際には、SiCウェハの下面側と直接接触してその工程が行われる場合が多い。NiOを主成分とした酸化層14は、化学的に安定な材料であるため、こうした工程の際に、下面側におけるNiシリサイド層13の保護膜となる。すなわち、酸化雰囲気熱処理工程と還元処理工程との間にショットキー電極形成工程を行うことにより、ショットキー電極形成工程の際に酸化層14をそのままの状態で残しておくことができる。この際、オーミック電極の材料となるNiシリサイド層13が機械的、化学的に保護される。

【0048】

次に、この状態で前記の還元処理工程を行う(図4(e))。これにより、下面の酸化層14は、Niを主成分とする還元層15となる。また、この温度は、前記の通り300〜400℃であるため、上面側のショットキー接合に対して悪影響を与えない温度範囲である。

【0049】

次に、この構造における特にショットキー電極42等を保護するために、上面全体にフォトレジスト層50を形成する(図4(f))。

【0050】

この状態で、希フッ酸等を用いたウェットエッチングを行うことにより、Niを主成分とする還元層15は除去され、下面側にNiシリサイド層13が露出する(図4(g):エッチング工程)。フォトレジスト層50があるために、上面側のSiO2層41、ショットキー電極42等はこの影響を受けない。また、これらはフォトレジスト層50によって機械的にも保護される。この際には、希フッ酸の代わりに、Niをエッチングすることができ、かつフォトレジスト層50が耐性をもつ他のエッチング液を用いることもできる。

【0051】

次に、露出したNiシリサイド層13の表面に、配線層となるTi/Ni/Au層43を形成する(図4(h):配線形成工程)。

【0052】

次に、ウェット処理、アッシング処理等によってフォトレジスト層50を除去する(図4(i))。これにより、上面側にショットキー接合側、下面側にn型SiC側の電極が取り出された構成のSBDが得られる。このSBDを製造する際には、特に上面側の構造(ショットキー電極42等)を形成する際に、下面側に形成されている酸化層14がNiシリサイド層13の保護膜となる。このため、高い歩留まりで容易にこのSBDを製造することができる。また、Niシリサイド層13とTi/Ni/Au層43との間の密着性を高めることができることについては、第1、第2の実施の形態と同様である。

【0053】

なお、第3の実施の形態においても、n型SiC層11の下面にSiO2層を形成し、これに開口部を設けて第2の実施の形態と同様の工程を行うことができる。これにより、下面におけるオーミック接合を局所的にとり、これに接続された配線層を形成することも可能であり、この際にも酸化層を保護膜として用いることができる。

【0054】

なお、上記の例では、n型SiCに対してNiシリサイドを用いたオーミック電極を形成する場合について記載したが、n型以外(p型、半絶縁性)のSiCに対してNiシリサイドを用いた電極を形成する場合であっても、上記の製造方法が有効であることは明らかである。すなわち、この構造の電極は、SiCを用いたSBD、MOSFET、MESFET、pn接合ダイオード等、SiCに対して電気的接続をとることが必要な全ての半導体装置に対して有効である。このため、上記の製造方法も、これらの全ての半導体装置を製造する際に有効である。

【符号の説明】

【0055】

11 n型SiC層

12 Ni層

13 Niシリサイド層

14 グラファイト

15 酸化層

16 還元層

30 Ti/Al層(配線層)

41 SiO2層

42 ショットキー電極

43 Ti/Ni/Au層(配線層)

50 フォトレジスト層

【特許請求の範囲】

【請求項1】

ニッケル(Ni)シリサイドを用いた電極が炭化珪素(SiC)層に接続された構成を具備する半導体装置の製造方法であって、

SiC層の表面にNi層を形成するNi形成工程と、

熱処理を施すことにより、前記Ni層と前記SiC層とを反応させることによってNiシリサイド層を形成するシリサイド形成工程と、

前記Niシリサイド層の形成後に酸化雰囲気で熱処理を行う酸化雰囲気熱処理工程と、

当該酸化雰囲気熱処理工程の後で、還元雰囲気中で前記シリサイド形成工程における熱処理の温度よりも低い温度で熱処理を行う還元処理工程と、

Niに対するエッチング処理を行うエッチング工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項2】

前記エッチング工程後に、

前記Niシリサイド層と接触するように配線層を形成する配線形成工程を具備することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記還元処理工程における熱処理の温度を300〜400℃の範囲とすることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記シリサイド形成工程と前記酸化雰囲気熱処理工程との間に、

非酸化雰囲気中で前記シリサイド形成工程における熱処理の温度よりも低い温度で熱処理を行う非酸化雰囲気熱処理工程を具備することを特徴とする請求項1から請求項3までのいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記エッチング工程において、超音波洗浄処理を行うことを特徴とする請求項1から請求項4までのいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記SiC層表面に絶縁層を形成し、当該絶縁層に開口部を形成した後に前記Ni形成工程を行うことを特徴とする請求項1から請求項5までのいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記半導体装置は、前記SiC層に対するショットキー電極が前記SiC層の一方の主面側に形成され、前記SiC層に対するオーミック電極が前記SiC層の他方の主面側に形成されたSBD(Schottky Barrier Diode)であり、

前記Ni形成工程におけるNi層は前記他方の主面側に形成され、

前記酸化雰囲気熱処理工程と、前記還元処理工程との間に、

前記一方の主面側に前記ショットキー電極を形成するショットキー電極形成工程を具備することを特徴とする請求項1から請求項6までのいずれか1項に記載の半導体装置の製造方法。

【請求項8】

請求項1から請求項7までのいずれか1項に記載の半導体装置の製造方法によって製造されたことを特徴とする半導体装置。

【請求項1】

ニッケル(Ni)シリサイドを用いた電極が炭化珪素(SiC)層に接続された構成を具備する半導体装置の製造方法であって、

SiC層の表面にNi層を形成するNi形成工程と、

熱処理を施すことにより、前記Ni層と前記SiC層とを反応させることによってNiシリサイド層を形成するシリサイド形成工程と、

前記Niシリサイド層の形成後に酸化雰囲気で熱処理を行う酸化雰囲気熱処理工程と、

当該酸化雰囲気熱処理工程の後で、還元雰囲気中で前記シリサイド形成工程における熱処理の温度よりも低い温度で熱処理を行う還元処理工程と、

Niに対するエッチング処理を行うエッチング工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項2】

前記エッチング工程後に、

前記Niシリサイド層と接触するように配線層を形成する配線形成工程を具備することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記還元処理工程における熱処理の温度を300〜400℃の範囲とすることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記シリサイド形成工程と前記酸化雰囲気熱処理工程との間に、

非酸化雰囲気中で前記シリサイド形成工程における熱処理の温度よりも低い温度で熱処理を行う非酸化雰囲気熱処理工程を具備することを特徴とする請求項1から請求項3までのいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記エッチング工程において、超音波洗浄処理を行うことを特徴とする請求項1から請求項4までのいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記SiC層表面に絶縁層を形成し、当該絶縁層に開口部を形成した後に前記Ni形成工程を行うことを特徴とする請求項1から請求項5までのいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記半導体装置は、前記SiC層に対するショットキー電極が前記SiC層の一方の主面側に形成され、前記SiC層に対するオーミック電極が前記SiC層の他方の主面側に形成されたSBD(Schottky Barrier Diode)であり、

前記Ni形成工程におけるNi層は前記他方の主面側に形成され、

前記酸化雰囲気熱処理工程と、前記還元処理工程との間に、

前記一方の主面側に前記ショットキー電極を形成するショットキー電極形成工程を具備することを特徴とする請求項1から請求項6までのいずれか1項に記載の半導体装置の製造方法。

【請求項8】

請求項1から請求項7までのいずれか1項に記載の半導体装置の製造方法によって製造されたことを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−190829(P2012−190829A)

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願番号】特願2011−50436(P2011−50436)

【出願日】平成23年3月8日(2011.3.8)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願日】平成23年3月8日(2011.3.8)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

[ Back to top ]