半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法、半導体装置に関し、詳しくは微細な配線を高精度に形成する技術に関する。

【背景技術】

【0002】

従来、基板に形成した半導体素子等の微細な配線材料として、アルミニウムやアルミニウム合金が用いられていた。しかし、アルミニウムは融点が低く、かつ耐マイグレーション性に劣るため、半導体素子の高集積化、高速化への対応が困難であった。

【0003】

このため、近年は配線材料として、銅が用いられるようになっている。銅はアルミニウムより融点が高く、かつ電気抵抗率も低いため、LSI配線材料として有力である。例えば、特許文献1には、絶縁層に溝を形成し、この溝の内部に銅を埋め込み、その後、溝からはみ出した余分な銅を除去することにより、微細な溝内に銅配線を形成する方法が提案されている。

【0004】

絶縁層などの基体に溝を形成する際に、この溝の底面に基体材料の自然酸化膜が形成されることがある。このような自然酸化膜を除去せず溝内に銅配線を形成すると、銅配線の導電率など電気的特性が劣化する懸念がある。このため、溝の内部に銅を埋め込む工程の前に、予め溝の底部に生じた酸化膜をスパッタリング法などによって除去することが行われている。

【0005】

しかしながら、溝の底部に生じた酸化膜をスパッタリング法などによって除去する際に、溝の頂面領域も削られてしまい、テーパー形状になってしまうことがあった。溝の頂面領域がテーパー形状になってしまうと、溝の内部に銅を埋め込んだ際に、形成された銅配線の内部に空洞が生じ、断線や導電率の低下をもたらすという課題があった。

【0006】

図6は、従来の半導体装置の製造方法の一例を示す断面図である。

基体100の一面100a側に微細な銅配線を形成する際には、まず、基体100の一面100aから所定深さの溝部101をドライエッチング等で形成する(図6(a)参照)。この時、溝部101の底面101aには、基体100の構成材料の酸化物からなる自然酸化膜102が形成される。

【0007】

次に、この溝部101の底面101aに生じた自然酸化膜102を除去するために、例えばArガスを用いたドライエッチングを行う(図6(b)参照)。この時、基体100の一面100a、即ち溝部101の頂面領域T1もドライエッチングによって角部が削り取られ、テーパー状(肩削れ形状)になってしまう。

【0008】

このように溝部101の頂面領域T1がテーパー状になった状態で、溝部101を埋める銅配線の構成材となるシード層103を形成すると、テーパー状の頂面領域T1によって斜め上方向にシード層103が過剰に堆積する(図6中のC部)。そして、溝部101の開口端付近が閉塞ないし狭められる(図6(c)参照)。この状態で、リフローによってシード層103を溶融させて溝部101に銅配線105を形成すると、銅配線105の内部に空洞Eが生じてしまう(図6(d)参照)。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特公平6−103681号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明は上記課題を解決するためになされたものであり、微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【課題を解決するための手段】

【0011】

上記課題を解決するために、本発明は次のような半導体装置の製造方法、半導体装置を提供する。

即ち、本発明の半導体装置の製造方法は、基体の一面から掘り込まれた溝部の一面にエッチングカバー層を形成するカバー層形成工程と、前記溝部の底面に堆積した前記基体の自然酸化膜を除去する酸化膜除去工程と、少なくとも該溝部の内壁面を覆うバリア層を形成するバリア層形成工程と、前記バリア層の内側領域に導電材料を埋め込む埋込工程と、を少なくとも備え、

前記エッチングカバー層はTaまたはTi、前記導電材料はCuからなることを特徴とする。

【0012】

前記カバー層形成工程および前記酸化膜除去工程は、同一の高周波スパッタリング装置を用いて、印加する高周波バイアス値を変化させることによって行うことを特徴とする。

また、前記埋込工程は、前記バリア層を覆う前記導電材料からなるシード層を形成し、該シード層をリフロー法によって溶融させる工程であることを特徴とする。

【0013】

前記埋込工程は、前記バリア層を覆うように前記導電材料をスパッタリング法によって積層させる工程であることを特徴とする。

前記バリア層は、Ta,Ti,W,Ru,V,Co,Nbのうち、少なくとも一種を含む材料からなることを特徴とする。

【0014】

前記基体は、半導体基板と、該半導体基板の一面に形成された絶縁層とからなることを特徴とする。

【0015】

本発明の半導体装置は、前記各項記載の半導体装置の製造方法を用いて製造したことを特徴とする。

【発明の効果】

【0016】

本発明の半導体装置の製造方法、半導体装置によれば、溝部の底面に形成された酸化膜を除去する際に、基体の一面、即ち溝部の頂面をエッチングカバー層で覆ったので、溝部の底面にある酸化膜だけが選択的に除去され、基体の一面がエッチングされることを防止できる。よって、酸化膜をエッチング除去する際に溝部の頂面がテーパー状に削られた、いわゆる肩崩れ形状になることを確実に防止する。

これにより、溝部の内側に空洞を生じさせること無く緻密に導電材料を埋め込むことができ、導電性に優れた配線を得ることが可能になる。

【図面の簡単な説明】

【0017】

【図1】本発明の半導体装置の一例を示す要部拡大断面図である。

【図2】本発明の半導体装置の製造方法を段階的に示した要部拡大断面図である。

【図3】本発明の半導体装置の製造方法を段階的に示した要部拡大断面図である。

【図4】成膜装置(スパッタリング装置)の一例を示す概略構成図である。

【図5】成膜装置のRFバイアスと成膜レートとの関係を示すグラフである。

【図6】従来の半導体装置の製造方法の一例を示す要部拡大断面図である。

【発明を実施するための形態】

【0018】

以下、本発明に係る半導体装置の製造方法、半導体装置について、図面に基づき説明する。なお、本実施形態は発明の趣旨をより良く理解させるために、一例を挙げて説明するものであり、特に指定のない限り、本発明を限定するものではない。また、以下の説明で用いる図面は、本発明の特徴をわかりやすくするために、便宜上、要部となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。

【0019】

(半導体装置)

図1は、本発明の半導体装置の一例を示す要部拡大断面図である。

半導体装置10は、基体11を備えている。基体11は、絶縁性基板、例えばガラス基板、樹脂基板などから構成される。なお、この基体11の一部に、例えば半導体素子等が形成されていてもよい。

【0020】

基体11の一面11aには、溝部(トレンチ)12が形成されている。溝部12は、例えば、基体11の一面11aから基体11の厚み方向に掘り下げられた幅が細く、かつ深い微細な溝からなる。溝部12の底部の幅Wは、例えば20nm〜50nm程度になるように形成される。また、溝部12の深さDは、例えば80nm〜200nm程度になるように形成される。このような溝部12の内側領域に、例えば半導体素子の回路配線を構成する導電体が形成される。

【0021】

溝部12には、内壁面を覆うように、バリア層(バリアメタル)13が形成されている。バリア層13は、例えば、Ta(タンタル)窒化物、Ta珪化物、Ta炭化物、Ti(チタン)窒化物、Ti珪化物、Ti炭化物、W(タングステン)窒化物、W珪化物、W炭化物、Ru(ルテニウム)、およびRu酸化物、V(バナジウム)酸化物、Co(コバルト)酸化物、Nb(ニオブ)酸化物などから構成される。

バリア層(バリアメタル)13は、厚みt1が例えば1nm〜3nm程度になるように形成される。

【0022】

溝部12におけるバリア層13の内側領域には、導電材料からなる導電体15が形成されている。導電体15は、Cu(銅)から構成されている。この導電体15は、バリア層13の内側にシード層16を形成し、このシード層16を溶融(リフロー)することによって、あるいはメッキ成長法によって、溝部12を埋め込む導電体15を形成する。あるいは、バリア層13の内側領域に、スパッタリング法によって導電材料を堆積させて導電体15を形成する。導電体15は、例えば、基体11に形成された半導体素子の回路配線となる。

【0023】

(半導体装置の製造方法)

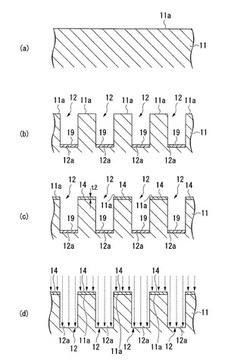

図2、図3は、本発明の半導体装置の製造方法を段階的に示した要部拡大断面図である。

本発明の半導体装置を製造する際には、まず、基体11を用意する(図2(a)参照)。基体11としては、絶縁性基板、半導体基板が用いられる。絶縁性基板として、例えば、ガラス基板、樹脂基板が挙げられる。また、半導体基板としては、例えば、シリコンウェーハ、SiCウェーハなどが挙げられる。基体11には、例えば、予め半導体素子(図示略)が形成されている。

【0024】

次に、この基体11の一面11aに、所定の深さの溝部12を形成する(図2(b)参照:溝部形成工程)。溝部12は、例えば、半導体素子の回路配線を象ったパターンとなるように形成される。基体11の一面11aに溝部12を形成する方法としては、例えば、フォトリソグラフィーによるエッチング加工や、レーザー光による加工を用いることができる。

【0025】

このような溝部12の底面12aには、基体11の構成材料が酸化された酸化膜(自然酸化膜)19が形成されることがある。このような酸化膜19をそのまま残した状態で溝部12に導電体を埋め込むと、導電特性が劣化したり導電体が酸化される原因となるため、後述する酸化膜除去工程で取り除く必要がある。

【0026】

次に、溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する(図2(c)参照:カバー層形成工程)。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。また、エッチングカバー層14は、厚みt2が例えば1nm〜5nm程度になるように形成される。

【0027】

図4は、エッチングカバー層の形成に用いるスパッタリング装置(成膜装置)の一例を示している。

スパッタリング装置(成膜装置)1は、真空槽2と、真空槽2内部にそれぞれ配置された基板ホルダ7およびターゲット5とを有している。

【0028】

真空槽2には真空排気系9とガス供給系4とが接続されており、真空槽2内部を真空排気し、真空排気しながらガス供給系4からスパッタガスと、化学構造中に窒素又は酸素を含む反応ガスを導入し(例えば反応ガスが酸素の場合、流量が0.1sccm以上5sccm以下)、真空槽2内部に大気圧よりも低い成膜雰囲気(例えば全圧が10−4Pa以上10−1Pa以下)を形成する。

【0029】

そして、基体11に溝部12が形成された一面11a側をターゲット5に向けた状態で基板ホルダ7に保持させておく。真空槽2の外部にはスパッタ電源8とバイアス電源6がそれぞれ配置され、ターゲット5はスパッタ電源8に、基板ホルダ7はバイアス電源6にそれぞれ接続されている。

【0030】

真空槽2の外部に磁界形成手段3が配置されており、真空槽2を接地電位に置き、真空槽2内部の成膜雰囲気を維持しながら、ターゲット5に負電圧を印加するとターゲット5はマグネトロンスパッタされる。ターゲット5は、上述したエッチングカバー層14の形成材料が主成分とされる。

そして、ターゲット5がマグネトロンスパッタされると、エッチングカバー層の形成材料、即ちTaやTiがスパッタ粒子として放出される。

【0031】

放出されたスパッタ粒子と、反応ガスは基体11の一面11a、即ち溝部12の頂面を覆うエッチングカバー層14が形成される。なお、スパッタリング装置1の成膜条件を適切に制御することによって、溝部12の内側、特に底面12aにはエッチングカバー層14が堆積されないようにすることができる。溝部12の内側にエッチングカバー層14を堆積させないためには、例えば、基板ホルダ7に接続されたバイアス電源6の投入電力をゼロにするなどの制御を行えばよい。

【0032】

次に、溝部12の底面12aに形成された酸化膜19を除去する(図2(d)参照:酸化膜除去工程)。酸化膜19を除去する方法としては、例えば、前工程であるカバー層形成工程で用いたスパッタリング装置(成膜装置)1を用いることができる。

【0033】

図5は、スパッタリング装置(成膜装置)において、印加するRFバイアスと成膜レートとの関係を示すグラフである。このグラフによれば、スパッタリング装置(成膜装置)1のRFバイアスが480W付近で成膜レートが0となり、それよりもRFバイアスを低くすることによって、成膜レートが上昇していく。一方、RFバイアスを480W付近よりも高くすることによって、成膜レートはマイナスに転じる。これは即ち、成膜対象物(基体)をエッチングすることになる。

このように、スパッタリング装置1のRFバイアスを変化させることによって、成膜対象物(基体)に成膜を行ったり、あるいは逆にエッチングを行うことができる。

【0034】

このように、スパッタリング装置(成膜装置)1を用いて、溝部12の底面12aに形成された酸化膜19をエッチング除去する際に、基体11の一面11a、即ち溝部12の頂面がエッチングカバー層14で覆われているために、溝部12の底面12aにある酸化膜19だけが選択的に除去され、基体11の一面11aがエッチングされることを防止する。

【0035】

基体11の一面11a、即ち溝部12の頂面をエッチングカバー層14で覆うことによって、酸化膜19をエッチング除去する際に溝部12の頂面がテーパー状に削られた、いわゆる肩崩れ形状になることを確実に防止できる。

【0036】

次に、溝部12の内壁面を含む基体11の一面11aに、所定の厚みのバリア層(バリアメタル)13を形成する(図3(a)参照:バリア層形成工程)。バリア層(バリアメタル)13は、例えば、Ta、Ti、W、Ru、V、Co、Nbのうちの少なくとも1種を含む材料を用いて形成する。バリア層13の形成は、例えば、スパッタリング法を用いることが好ましい。

【0037】

バリア層(バリアメタル)13は、スパッタリング法によって形成される。例えば、図4に示すスパッタリング装置(成膜装置)1を用いて、溝部12の内壁面を覆うように成膜する。バリア層(バリアメタル)13は、厚みt1が例えば1nm〜5nm程度になるように形成される。

【0038】

次に、バリア層(バリアメタル)13を覆うようにシード層16を形成する(図3(b)参照)。このシード層16は、次工程においてリフローされ、溝部12に埋め込まれる導電材料となる。シード層16は、Cuから構成される。シード層16は、例えば厚みが3nm〜8nm程度になるように形成される。

【0039】

このようなシード層16の形成にあたって、基体11の一面11a、即ち溝部12の頂面がエッチングカバー層14によって覆われて角部が肩崩れしていないので、溝部12の開口面付近にシード層16が過剰に堆積して溝部12の開口面付近を狭めたり閉塞してしまう懸念が無い。従って、溝部12の内部にほぼ均一な厚みでシード層16の形成することが可能になる。

【0040】

次に、シード層16を形成した基体11を、シード層16の溶融温度以上に加熱してリフローを行う(図3(c)参照:埋込工程)。これにより、シード層16は溶融して溝部12の内側、即ちバリア層(バリアメタル)13の内側領域がCuからなる導電材料Mによって埋め込まれる。

【0041】

このような埋込工程において、エッチングカバー層14によってシード層16が溝部12の内部にほぼ均一な厚みで形成されているため、溶融した導電材料Mの内部に空洞が残留することが無く、溝部12の内部に隙間無く導電材料Mを埋め込むことができる。

【0042】

この後、溝部12を除いた基体11の一面11aに積層されているエッチングカバー層14、バリア層13および導電材料Mを除去する(図3(d)参照)。これによって、それぞれの溝部12ごとに、溝部12を埋め込む導電体15、即ち回路配線が形成される。

【0043】

なお、溝部12の内側に導電材料を埋め込む埋込工程は、上述したように、シード層16を形成して、このシード層16をリフロー法によって溶融する以外にも、例えば、スパッタリング法やメッキ成長法によって導電材料を埋め込むこともできる。

スパッタリング法によって導電材料を埋め込む場合、図5に示すスパッタリング装置(成膜装置)を用いてターゲット5をCuとして、溝部12の内側領域を含む基体11の一面11a側にCuからなる導電材料を堆積させる。

【0044】

このようなスパッタリング法によって導電材料を埋め込む場合であっても、酸化膜19をエッチング除去する際にエッチングカバー層14によって溝部12の頂面がテーパー状に削られた、いわゆる肩崩れ形状になることを防止できるので、堆積されるCuを溝部12の内側に均一に空洞を生じさせること無く堆積させることが可能になる。

【符号の説明】

【0045】

10 半導体装置、11 基体、12 溝部(トレンチ)、13 バリア層(バリアメタル)、14 エッチングカバー層、15 導電体(回路配線)、16 シード層。

【技術分野】

【0001】

本発明は、半導体装置の製造方法、半導体装置に関し、詳しくは微細な配線を高精度に形成する技術に関する。

【背景技術】

【0002】

従来、基板に形成した半導体素子等の微細な配線材料として、アルミニウムやアルミニウム合金が用いられていた。しかし、アルミニウムは融点が低く、かつ耐マイグレーション性に劣るため、半導体素子の高集積化、高速化への対応が困難であった。

【0003】

このため、近年は配線材料として、銅が用いられるようになっている。銅はアルミニウムより融点が高く、かつ電気抵抗率も低いため、LSI配線材料として有力である。例えば、特許文献1には、絶縁層に溝を形成し、この溝の内部に銅を埋め込み、その後、溝からはみ出した余分な銅を除去することにより、微細な溝内に銅配線を形成する方法が提案されている。

【0004】

絶縁層などの基体に溝を形成する際に、この溝の底面に基体材料の自然酸化膜が形成されることがある。このような自然酸化膜を除去せず溝内に銅配線を形成すると、銅配線の導電率など電気的特性が劣化する懸念がある。このため、溝の内部に銅を埋め込む工程の前に、予め溝の底部に生じた酸化膜をスパッタリング法などによって除去することが行われている。

【0005】

しかしながら、溝の底部に生じた酸化膜をスパッタリング法などによって除去する際に、溝の頂面領域も削られてしまい、テーパー形状になってしまうことがあった。溝の頂面領域がテーパー形状になってしまうと、溝の内部に銅を埋め込んだ際に、形成された銅配線の内部に空洞が生じ、断線や導電率の低下をもたらすという課題があった。

【0006】

図6は、従来の半導体装置の製造方法の一例を示す断面図である。

基体100の一面100a側に微細な銅配線を形成する際には、まず、基体100の一面100aから所定深さの溝部101をドライエッチング等で形成する(図6(a)参照)。この時、溝部101の底面101aには、基体100の構成材料の酸化物からなる自然酸化膜102が形成される。

【0007】

次に、この溝部101の底面101aに生じた自然酸化膜102を除去するために、例えばArガスを用いたドライエッチングを行う(図6(b)参照)。この時、基体100の一面100a、即ち溝部101の頂面領域T1もドライエッチングによって角部が削り取られ、テーパー状(肩削れ形状)になってしまう。

【0008】

このように溝部101の頂面領域T1がテーパー状になった状態で、溝部101を埋める銅配線の構成材となるシード層103を形成すると、テーパー状の頂面領域T1によって斜め上方向にシード層103が過剰に堆積する(図6中のC部)。そして、溝部101の開口端付近が閉塞ないし狭められる(図6(c)参照)。この状態で、リフローによってシード層103を溶融させて溝部101に銅配線105を形成すると、銅配線105の内部に空洞Eが生じてしまう(図6(d)参照)。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特公平6−103681号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明は上記課題を解決するためになされたものであり、微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【課題を解決するための手段】

【0011】

上記課題を解決するために、本発明は次のような半導体装置の製造方法、半導体装置を提供する。

即ち、本発明の半導体装置の製造方法は、基体の一面から掘り込まれた溝部の一面にエッチングカバー層を形成するカバー層形成工程と、前記溝部の底面に堆積した前記基体の自然酸化膜を除去する酸化膜除去工程と、少なくとも該溝部の内壁面を覆うバリア層を形成するバリア層形成工程と、前記バリア層の内側領域に導電材料を埋め込む埋込工程と、を少なくとも備え、

前記エッチングカバー層はTaまたはTi、前記導電材料はCuからなることを特徴とする。

【0012】

前記カバー層形成工程および前記酸化膜除去工程は、同一の高周波スパッタリング装置を用いて、印加する高周波バイアス値を変化させることによって行うことを特徴とする。

また、前記埋込工程は、前記バリア層を覆う前記導電材料からなるシード層を形成し、該シード層をリフロー法によって溶融させる工程であることを特徴とする。

【0013】

前記埋込工程は、前記バリア層を覆うように前記導電材料をスパッタリング法によって積層させる工程であることを特徴とする。

前記バリア層は、Ta,Ti,W,Ru,V,Co,Nbのうち、少なくとも一種を含む材料からなることを特徴とする。

【0014】

前記基体は、半導体基板と、該半導体基板の一面に形成された絶縁層とからなることを特徴とする。

【0015】

本発明の半導体装置は、前記各項記載の半導体装置の製造方法を用いて製造したことを特徴とする。

【発明の効果】

【0016】

本発明の半導体装置の製造方法、半導体装置によれば、溝部の底面に形成された酸化膜を除去する際に、基体の一面、即ち溝部の頂面をエッチングカバー層で覆ったので、溝部の底面にある酸化膜だけが選択的に除去され、基体の一面がエッチングされることを防止できる。よって、酸化膜をエッチング除去する際に溝部の頂面がテーパー状に削られた、いわゆる肩崩れ形状になることを確実に防止する。

これにより、溝部の内側に空洞を生じさせること無く緻密に導電材料を埋め込むことができ、導電性に優れた配線を得ることが可能になる。

【図面の簡単な説明】

【0017】

【図1】本発明の半導体装置の一例を示す要部拡大断面図である。

【図2】本発明の半導体装置の製造方法を段階的に示した要部拡大断面図である。

【図3】本発明の半導体装置の製造方法を段階的に示した要部拡大断面図である。

【図4】成膜装置(スパッタリング装置)の一例を示す概略構成図である。

【図5】成膜装置のRFバイアスと成膜レートとの関係を示すグラフである。

【図6】従来の半導体装置の製造方法の一例を示す要部拡大断面図である。

【発明を実施するための形態】

【0018】

以下、本発明に係る半導体装置の製造方法、半導体装置について、図面に基づき説明する。なお、本実施形態は発明の趣旨をより良く理解させるために、一例を挙げて説明するものであり、特に指定のない限り、本発明を限定するものではない。また、以下の説明で用いる図面は、本発明の特徴をわかりやすくするために、便宜上、要部となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。

【0019】

(半導体装置)

図1は、本発明の半導体装置の一例を示す要部拡大断面図である。

半導体装置10は、基体11を備えている。基体11は、絶縁性基板、例えばガラス基板、樹脂基板などから構成される。なお、この基体11の一部に、例えば半導体素子等が形成されていてもよい。

【0020】

基体11の一面11aには、溝部(トレンチ)12が形成されている。溝部12は、例えば、基体11の一面11aから基体11の厚み方向に掘り下げられた幅が細く、かつ深い微細な溝からなる。溝部12の底部の幅Wは、例えば20nm〜50nm程度になるように形成される。また、溝部12の深さDは、例えば80nm〜200nm程度になるように形成される。このような溝部12の内側領域に、例えば半導体素子の回路配線を構成する導電体が形成される。

【0021】

溝部12には、内壁面を覆うように、バリア層(バリアメタル)13が形成されている。バリア層13は、例えば、Ta(タンタル)窒化物、Ta珪化物、Ta炭化物、Ti(チタン)窒化物、Ti珪化物、Ti炭化物、W(タングステン)窒化物、W珪化物、W炭化物、Ru(ルテニウム)、およびRu酸化物、V(バナジウム)酸化物、Co(コバルト)酸化物、Nb(ニオブ)酸化物などから構成される。

バリア層(バリアメタル)13は、厚みt1が例えば1nm〜3nm程度になるように形成される。

【0022】

溝部12におけるバリア層13の内側領域には、導電材料からなる導電体15が形成されている。導電体15は、Cu(銅)から構成されている。この導電体15は、バリア層13の内側にシード層16を形成し、このシード層16を溶融(リフロー)することによって、あるいはメッキ成長法によって、溝部12を埋め込む導電体15を形成する。あるいは、バリア層13の内側領域に、スパッタリング法によって導電材料を堆積させて導電体15を形成する。導電体15は、例えば、基体11に形成された半導体素子の回路配線となる。

【0023】

(半導体装置の製造方法)

図2、図3は、本発明の半導体装置の製造方法を段階的に示した要部拡大断面図である。

本発明の半導体装置を製造する際には、まず、基体11を用意する(図2(a)参照)。基体11としては、絶縁性基板、半導体基板が用いられる。絶縁性基板として、例えば、ガラス基板、樹脂基板が挙げられる。また、半導体基板としては、例えば、シリコンウェーハ、SiCウェーハなどが挙げられる。基体11には、例えば、予め半導体素子(図示略)が形成されている。

【0024】

次に、この基体11の一面11aに、所定の深さの溝部12を形成する(図2(b)参照:溝部形成工程)。溝部12は、例えば、半導体素子の回路配線を象ったパターンとなるように形成される。基体11の一面11aに溝部12を形成する方法としては、例えば、フォトリソグラフィーによるエッチング加工や、レーザー光による加工を用いることができる。

【0025】

このような溝部12の底面12aには、基体11の構成材料が酸化された酸化膜(自然酸化膜)19が形成されることがある。このような酸化膜19をそのまま残した状態で溝部12に導電体を埋め込むと、導電特性が劣化したり導電体が酸化される原因となるため、後述する酸化膜除去工程で取り除く必要がある。

【0026】

次に、溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する(図2(c)参照:カバー層形成工程)。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。また、エッチングカバー層14は、厚みt2が例えば1nm〜5nm程度になるように形成される。

【0027】

図4は、エッチングカバー層の形成に用いるスパッタリング装置(成膜装置)の一例を示している。

スパッタリング装置(成膜装置)1は、真空槽2と、真空槽2内部にそれぞれ配置された基板ホルダ7およびターゲット5とを有している。

【0028】

真空槽2には真空排気系9とガス供給系4とが接続されており、真空槽2内部を真空排気し、真空排気しながらガス供給系4からスパッタガスと、化学構造中に窒素又は酸素を含む反応ガスを導入し(例えば反応ガスが酸素の場合、流量が0.1sccm以上5sccm以下)、真空槽2内部に大気圧よりも低い成膜雰囲気(例えば全圧が10−4Pa以上10−1Pa以下)を形成する。

【0029】

そして、基体11に溝部12が形成された一面11a側をターゲット5に向けた状態で基板ホルダ7に保持させておく。真空槽2の外部にはスパッタ電源8とバイアス電源6がそれぞれ配置され、ターゲット5はスパッタ電源8に、基板ホルダ7はバイアス電源6にそれぞれ接続されている。

【0030】

真空槽2の外部に磁界形成手段3が配置されており、真空槽2を接地電位に置き、真空槽2内部の成膜雰囲気を維持しながら、ターゲット5に負電圧を印加するとターゲット5はマグネトロンスパッタされる。ターゲット5は、上述したエッチングカバー層14の形成材料が主成分とされる。

そして、ターゲット5がマグネトロンスパッタされると、エッチングカバー層の形成材料、即ちTaやTiがスパッタ粒子として放出される。

【0031】

放出されたスパッタ粒子と、反応ガスは基体11の一面11a、即ち溝部12の頂面を覆うエッチングカバー層14が形成される。なお、スパッタリング装置1の成膜条件を適切に制御することによって、溝部12の内側、特に底面12aにはエッチングカバー層14が堆積されないようにすることができる。溝部12の内側にエッチングカバー層14を堆積させないためには、例えば、基板ホルダ7に接続されたバイアス電源6の投入電力をゼロにするなどの制御を行えばよい。

【0032】

次に、溝部12の底面12aに形成された酸化膜19を除去する(図2(d)参照:酸化膜除去工程)。酸化膜19を除去する方法としては、例えば、前工程であるカバー層形成工程で用いたスパッタリング装置(成膜装置)1を用いることができる。

【0033】

図5は、スパッタリング装置(成膜装置)において、印加するRFバイアスと成膜レートとの関係を示すグラフである。このグラフによれば、スパッタリング装置(成膜装置)1のRFバイアスが480W付近で成膜レートが0となり、それよりもRFバイアスを低くすることによって、成膜レートが上昇していく。一方、RFバイアスを480W付近よりも高くすることによって、成膜レートはマイナスに転じる。これは即ち、成膜対象物(基体)をエッチングすることになる。

このように、スパッタリング装置1のRFバイアスを変化させることによって、成膜対象物(基体)に成膜を行ったり、あるいは逆にエッチングを行うことができる。

【0034】

このように、スパッタリング装置(成膜装置)1を用いて、溝部12の底面12aに形成された酸化膜19をエッチング除去する際に、基体11の一面11a、即ち溝部12の頂面がエッチングカバー層14で覆われているために、溝部12の底面12aにある酸化膜19だけが選択的に除去され、基体11の一面11aがエッチングされることを防止する。

【0035】

基体11の一面11a、即ち溝部12の頂面をエッチングカバー層14で覆うことによって、酸化膜19をエッチング除去する際に溝部12の頂面がテーパー状に削られた、いわゆる肩崩れ形状になることを確実に防止できる。

【0036】

次に、溝部12の内壁面を含む基体11の一面11aに、所定の厚みのバリア層(バリアメタル)13を形成する(図3(a)参照:バリア層形成工程)。バリア層(バリアメタル)13は、例えば、Ta、Ti、W、Ru、V、Co、Nbのうちの少なくとも1種を含む材料を用いて形成する。バリア層13の形成は、例えば、スパッタリング法を用いることが好ましい。

【0037】

バリア層(バリアメタル)13は、スパッタリング法によって形成される。例えば、図4に示すスパッタリング装置(成膜装置)1を用いて、溝部12の内壁面を覆うように成膜する。バリア層(バリアメタル)13は、厚みt1が例えば1nm〜5nm程度になるように形成される。

【0038】

次に、バリア層(バリアメタル)13を覆うようにシード層16を形成する(図3(b)参照)。このシード層16は、次工程においてリフローされ、溝部12に埋め込まれる導電材料となる。シード層16は、Cuから構成される。シード層16は、例えば厚みが3nm〜8nm程度になるように形成される。

【0039】

このようなシード層16の形成にあたって、基体11の一面11a、即ち溝部12の頂面がエッチングカバー層14によって覆われて角部が肩崩れしていないので、溝部12の開口面付近にシード層16が過剰に堆積して溝部12の開口面付近を狭めたり閉塞してしまう懸念が無い。従って、溝部12の内部にほぼ均一な厚みでシード層16の形成することが可能になる。

【0040】

次に、シード層16を形成した基体11を、シード層16の溶融温度以上に加熱してリフローを行う(図3(c)参照:埋込工程)。これにより、シード層16は溶融して溝部12の内側、即ちバリア層(バリアメタル)13の内側領域がCuからなる導電材料Mによって埋め込まれる。

【0041】

このような埋込工程において、エッチングカバー層14によってシード層16が溝部12の内部にほぼ均一な厚みで形成されているため、溶融した導電材料Mの内部に空洞が残留することが無く、溝部12の内部に隙間無く導電材料Mを埋め込むことができる。

【0042】

この後、溝部12を除いた基体11の一面11aに積層されているエッチングカバー層14、バリア層13および導電材料Mを除去する(図3(d)参照)。これによって、それぞれの溝部12ごとに、溝部12を埋め込む導電体15、即ち回路配線が形成される。

【0043】

なお、溝部12の内側に導電材料を埋め込む埋込工程は、上述したように、シード層16を形成して、このシード層16をリフロー法によって溶融する以外にも、例えば、スパッタリング法やメッキ成長法によって導電材料を埋め込むこともできる。

スパッタリング法によって導電材料を埋め込む場合、図5に示すスパッタリング装置(成膜装置)を用いてターゲット5をCuとして、溝部12の内側領域を含む基体11の一面11a側にCuからなる導電材料を堆積させる。

【0044】

このようなスパッタリング法によって導電材料を埋め込む場合であっても、酸化膜19をエッチング除去する際にエッチングカバー層14によって溝部12の頂面がテーパー状に削られた、いわゆる肩崩れ形状になることを防止できるので、堆積されるCuを溝部12の内側に均一に空洞を生じさせること無く堆積させることが可能になる。

【符号の説明】

【0045】

10 半導体装置、11 基体、12 溝部(トレンチ)、13 バリア層(バリアメタル)、14 エッチングカバー層、15 導電体(回路配線)、16 シード層。

【特許請求の範囲】

【請求項1】

基体の一面から掘り込まれた溝部の一面にエッチングカバー層を形成するカバー層形成工程と、

前記溝部の底面に堆積した前記基体の自然酸化膜を除去する酸化膜除去工程と、

少なくとも該溝部の内壁面を覆うバリア層を形成するバリア層形成工程と、

前記バリア層の内側領域に導電材料を埋め込む埋込工程と、を少なくとも備え、

前記エッチングカバー層はTaまたはTi、前記導電材料はCuからなることを特徴とする半導体装置の製造方法。

【請求項2】

前記カバー層形成工程および前記酸化膜除去工程は、同一の高周波スパッタリング装置を用いて、印加する高周波バイアス値を変化させることによって行うことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記埋込工程は、前記バリア層を覆う前記導電材料からなるシード層を形成し、該シード層をリフロー法によって溶融させる工程であることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項4】

前記埋込工程は、前記バリア層を覆うように前記導電材料をスパッタリング法によって積層させる工程であることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項5】

前記バリア層は、Ta,Ti,W,Ru,V,Co,Nbのうち、少なくとも一種を含む材料からなることを特徴とする請求項1ないし4いずれか1項記載の半導体装置の製造方法。

【請求項6】

前記基体は、半導体基板と、該半導体基板の一面に形成された絶縁層とからなることを特徴とする請求項1ないし5いずれか1項記載の半導体装置の製造方法。

【請求項7】

請求項1ないし6いずれか1項記載の半導体装置の製造方法を用いて製造したことを特徴とする半導体装置。

【請求項1】

基体の一面から掘り込まれた溝部の一面にエッチングカバー層を形成するカバー層形成工程と、

前記溝部の底面に堆積した前記基体の自然酸化膜を除去する酸化膜除去工程と、

少なくとも該溝部の内壁面を覆うバリア層を形成するバリア層形成工程と、

前記バリア層の内側領域に導電材料を埋め込む埋込工程と、を少なくとも備え、

前記エッチングカバー層はTaまたはTi、前記導電材料はCuからなることを特徴とする半導体装置の製造方法。

【請求項2】

前記カバー層形成工程および前記酸化膜除去工程は、同一の高周波スパッタリング装置を用いて、印加する高周波バイアス値を変化させることによって行うことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記埋込工程は、前記バリア層を覆う前記導電材料からなるシード層を形成し、該シード層をリフロー法によって溶融させる工程であることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項4】

前記埋込工程は、前記バリア層を覆うように前記導電材料をスパッタリング法によって積層させる工程であることを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項5】

前記バリア層は、Ta,Ti,W,Ru,V,Co,Nbのうち、少なくとも一種を含む材料からなることを特徴とする請求項1ないし4いずれか1項記載の半導体装置の製造方法。

【請求項6】

前記基体は、半導体基板と、該半導体基板の一面に形成された絶縁層とからなることを特徴とする請求項1ないし5いずれか1項記載の半導体装置の製造方法。

【請求項7】

請求項1ないし6いずれか1項記載の半導体装置の製造方法を用いて製造したことを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−77631(P2013−77631A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−215349(P2011−215349)

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000231464)株式会社アルバック (1,740)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000231464)株式会社アルバック (1,740)

【Fターム(参考)】

[ Back to top ]