半導体装置の製造方法、及び半導体装置

【課題】微細配線においてボイドの発生を確実に防ぐ。

【解決手段】層間絶縁膜102、103に形成された開口部12の底面及び側壁、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部に、第一の金属を含むシード膜を形成し、シード膜上にレジストを形成して、開口部12をレジストで埋め込んだ後、開口部12の底面上に形成されたシード膜にレジストを残しつつレジストの一部を除去して、開口部12の側壁202A、Bの上部からフィールド部203にわたって形成されたシード膜を露出させ、開口部12の側壁の上部、及び、フィールド部203に位置するシード膜上に、第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成した後、レジストを除去してシード膜を露出させ、露出させたシード膜に、第一の金属を含むめっき膜を形成するものである。

【解決手段】層間絶縁膜102、103に形成された開口部12の底面及び側壁、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部に、第一の金属を含むシード膜を形成し、シード膜上にレジストを形成して、開口部12をレジストで埋め込んだ後、開口部12の底面上に形成されたシード膜にレジストを残しつつレジストの一部を除去して、開口部12の側壁202A、Bの上部からフィールド部203にわたって形成されたシード膜を露出させ、開口部12の側壁の上部、及び、フィールド部203に位置するシード膜上に、第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成した後、レジストを除去してシード膜を露出させ、露出させたシード膜に、第一の金属を含むめっき膜を形成するものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法、及び半導体装置に関する。

【背景技術】

【0002】

近年、半導体装置の配線構造の形成方法として、例えば、特許文献1や非特許文献1に記載のものが知られている。

【0003】

特許文献1では、表面に凹部を有するウェハの少なくとも凹部の底部、及び、側壁部に、Cuシード膜を形成し、Cuシード膜上に、少なくとも凹部の底部に位置するCuシード膜の部分が露出しかつ凹部の側壁部に位置するCuシード膜の部分を覆うようにRu膜又はTEOS膜を形成し、Cuシード膜に電流を供給して、Ru膜の形成された凹部に埋め込まれるように電解めっき法によりCuめっき膜を形成し、Cuめっき膜に熱処理を施した後、Ru膜又はTEOS膜を選択的に除去することが記載されている。特許文献1では、かかる方法により、凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができるとされている。

【0004】

非特許文献1では、成膜促進剤と、高分子の成膜抑制剤とを用いて、高アスペクト比のトレンチをCuで埋め込む技術が記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−80525号公報

【非特許文献】

【0006】

【非特許文献1】Jon Reid and Jian Zhou, "Electrofill Challenges and Directions for Future Device Generations", Advanced Metallization Conference 2007 Japan/Asia Session, pp.26-27

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記非特許文献1の技術は、成膜促進剤や成膜抑制剤の副反応の処理が必要となり、工業生産には適さない。また、半導体の微細化が進みトレンチの開口寸法が小さくなると、トレンチの底面にCuを堆積させる前に開口が塞がり、ボイドが発生してしまう。

【0008】

また、特許文献1の技術は、開口部(凹部)の側壁全面に、Ru膜又はTEOS膜といっためっき抑制膜を形成しており、開口部の底面、及び、開口部の外のフィールド部には、シード膜が露出している。そのため、開口部の底面にめっき膜の成長速度と、フィールド部のめっき膜の成長速度が同じになる。しかしながら、フィールド部のめっき膜は等方的に進むため、開口部に迫り出すように成長が進む。このため、開口部のアスペクト比が高くなると、底面からのめっき成長が開口部の上端に到達する前に、フィールド部からのめっき成長が開口部に到達して、開口部の上端を閉塞させてしまい、やはり、ボイドの発生を防ぐことができない。

【0009】

したがって、ボイドの発生を確実に防ぐことができる、微細配線の形成技術が未だ望まれる。

【課題を解決するための手段】

【0010】

本発明によれば、

絶縁膜に形成された開口部の底面及び側壁、並びに、前記開口部以外の前記絶縁膜上に、第一の金属を含むシード膜を形成する工程と、

前記シード膜上にマスク膜を形成して、前記開口部を前記マスク膜で埋め込む工程と、

前記開口部の底面上に形成された前記シード膜に前記マスク膜を残しつつ前記マスク膜の一部を除去して、前記開口部の前記側壁の上部から、前記開口部以外の前記絶縁膜上にわたって形成された前記シード膜を露出させる工程と、

前記開口部の前記側壁の上部、及び、前記開口部以外の前記絶縁膜上に位置する前記シード膜上に、前記第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成する工程と、

前記カバー膜を形成した後、前記開口部に残した前記マスク膜を除去して、前記シード膜を露出させる工程と、

露出させた前記シード膜に、前記第一の金属を含むめっき膜を形成する工程と、

を含む、半導体装置の製造方法が提供される。

【0011】

また、本発明によれば、

絶縁膜に形成された開口部と、

第一の金属を主成分とし、前記開口部を埋め込む配線膜と、

を備える埋め込み配線を有し、

前記配線膜は、前記第一の金属よりも抵抗率の高い第二の金属をさらに含み、

前記開口部の上部における前記配線膜中の前記第二の金属の濃度が、前記開口部の下部における前記配線膜中の前記第二の金属の濃度よりも高い、半導体装置が提供される。

【0012】

この発明によれば、シード膜を形成した後、めっき膜の形成前にマスク膜で開口部を埋め込み、マスク膜を選択的に除去することにより、開口部の側壁の上部から開口部以外の前記絶縁膜上(フィールド部)にわたってカバー膜を形成する。これにより、開口部の側壁の上部及びフィールド部におけるめっき成長を抑制して、フィールド膜からのめっき成長が開口部に到達する前に、開口部の内部のめっき成長を開口部の上端に到達させることができる。したがって、ボイドの発生なく開口部を埋設して、微細な埋め込み配線を形成することが可能になる。

【発明の効果】

【0013】

本発明によれば、微細配線においてもボイドの発生を確実に防ぐことができるため、信頼性の高い半導体装置を提供することができる。

【図面の簡単な説明】

【0014】

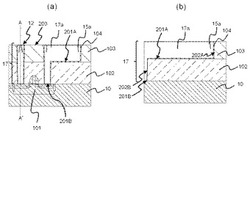

【図1】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図2】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図3】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図4】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図5】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図6】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図7】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図8】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図9】(a)が実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図10】(a)が実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図11】実施の形態に係る半導体装置を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図12】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図13】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図14】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図15】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図16】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図17】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図18】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図19】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図20】関連する技術を説明する図である。

【図21】実施の形態に係る半導体装置を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0016】

(第1の実施形態)

図1〜11は、本実施の形態の半導体装置の製造方法を説明する図である。図1〜11中、(a)が断面図であり、(b)が(a)のA−A'断面図である。

【0017】

本実施の形態の製造方法は、層間絶縁膜102、103に形成された開口部12の底面201A、201B及び側壁202、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部203に、第一の金属M1を含むシード膜13を形成する工程(図1)と、シード膜13上にレジスト14(マスク膜)を形成して、開口部12をレジスト14で埋め込む工程(図2)と、開口部12の底面201A、201B上に形成されたシード膜103にレジスト14を残しつつレジスト14の一部を除去して、開口部12の側壁202の上部からフィールド部203にわたって形成されたシード膜13を露出させる工程(図3)と、開口部12の側壁202の上部、及び、フィールド部203に位置するシード膜13上に、第一の金属M1よりも抵抗率が高い第二の金属M2を含むカバー膜15を形成する工程(図4)と、カバー膜15を形成した後、レジスト14を除去して、シード膜13を露出させる工程(図5)と、露出させたシード膜13に、第一の金属M1を含むめっき膜16を形成する工程(図6〜8)と、を含む。

【0018】

以下、本実施の形態の半導体装置の製造方法について、具体的に説明する。なお、本明細書においては、説明の都合上、上下方向は、半導体基板10に向かう方向を下とし、層間絶縁膜102、103の積層方向を上として記載する。半導体基板10として、例えばシリコン基板を用い、MOSトランジスタ101等の半導体素子等を形成する。ついで、例えば化学気相成長法(Chemical Vapor Deposition:CVD法)あるいは塗布法により層間絶縁膜102(第一の絶縁膜)と層間絶縁膜103(第二の絶縁膜)とをこの順で積層させる。層間絶縁膜102、103は、例えば、シリコン酸化膜等の低誘電率膜とすることができる。層間絶縁膜102、103は、それぞれ、単層であってもよいし、多層であってもよい。

【0019】

ついで、フォトリソグラフィ技術及びRIE(反応性イオンエッチング)法を用いて、開口部12を形成する。具体的には、層間絶縁膜103上にレジストパターンを形成し、レジストパターンをマスクとして、RIEにより層間絶縁膜102、103をエッチングし、層間絶縁膜102、103を貫通するように開口部12を形成する。これにより、層間絶縁膜103には、配線溝12Aが形成され、層間絶縁膜102には、配線溝12Aに接続したビア部12Bが形成される。ビア部12Bは、MOSトランジスタ101に接続している。その後、アッシング等によりレジストパターンを除去する。

【0020】

ここで、ビア部12Bは、アスペクト比を3以下とすることが好ましい。また、ビア部12Bは、テーパー状にすると好ましい。こうすることで、ビア部12Bにおけるボイドの発生をより確実に抑えることができる。

【0021】

その後、例えばスパッタ法あるいはCVD法により、開口部12の底面201A、201B、及び側壁202A、202Bにバリアメタル膜104を成膜する。バリアメタル膜104は、例えば、半導体で使用されている金属材料を用いて形成させることができ、例えば、Ta、TaN、Ti、Ru、Ir、W、これらを含む金属膜、並びにこれらの積層膜とすることができる。バリアメタル膜104の厚みは、例えば、1〜20nmとすることができる。

【0022】

ついで、バリアメタル膜104上に、例えばスパッタ法やCVD法によりシード膜13を成膜する。シード膜13は、開口部12の底面201A、201B、側壁202A、202B、フィールド部203上に形成される。シード膜13に含まれる第1の金属M1は、例えば、Cu、Al、Sn、Zn、TiとすることができるがCuを必須成分とすることが好ましく、Cuを主成分とすることがより好ましい。シード膜13は、Cuと他の金属(Al、Sn、Zn、Ti等)との合金から形成させてもよい。シード膜13の厚みは、10〜100nmとすることができる。(図1)。

【0023】

その後、レジスト14を塗布して開口部12を埋め込む(図2)。本実施の形態では、配線溝12A及びビア部12Bのすべてをレジスト14で埋め込む。開口部12の粗密によって埋め込み高さが変わる場合や、フィールド部203と開口部12との間に段差ができる場合には、レジスト14を二回に分けて塗布したり、レジスト14をエッチバックしてから再度埋め込んだりしてもよい。また、ここではレジスト14を用いたが、均一な埋め込み高さを実現できる材料であれば他の材料も可能である。また、塗布以外の方法を採用して、開口部12をレジスト14で埋め込んでもよい。

【0024】

ついで、酸素を含むガスを用いたプラズマを用いてレジスト14を選択的にエッチバックし、フィールド部203と、層間絶縁膜103内の側壁202Aに形成されたシード膜13の一部を露出させ、かつ、配線溝12Aの内部にレジスト14を残す。換言すれば、配線溝12Aの側壁202Aの上部に形成されたシード膜13を露出させ、かつ、配線溝12Aの内部にレジスト14を残す(図3)。本実施の形態では、このとき、配線溝12Aの側壁202Aの下部、及び、ビア部12Bの側壁202Bにわたって形成されたシード膜13は、露出させない。

具体的には、配線溝12Aの深さ全体の10〜50%の範囲にあるシード膜13が露出されていればよい。

なお、ここでは、酸素を含むガスを用いたプラズマを使用しているが開口部12に埋め込んだ材料に合わせて適宜変更可能であり、ガスやプラズマを使用しなくても良い。

【0025】

ついで、シード膜13が露出している箇所に、電界めっき等により第二の金属M2を堆積させて、カバー膜15を選択的に成膜する(図4)。第二の金属M2は、第一の金属M1とは異なる金属であり、第一の金属M1よりも抵抗率が高いものであればよいが、第一の金属M1よりも酸化されやすいものが好ましく、100〜400℃の熱処理で、シード膜13やめっき膜16を拡散できるものが好ましい。例えば、Ni、W、Ru、Ti、Mn、Al、Sn等を用いることができるが、第一の金属M1がCuのときは、Niが好ましい。また、カバー膜15は、シード膜13よりも抵抗率が高く、かつ、酸化されやすいように、これらの金属を組み合わせた合金としてもよい。また、第二の金属M1に加え、なお、第二の金属M2は、電界めっきではなく無電解めっきやCVD等の手法で選択的に堆積させても良い。カバー膜15の膜厚は、配線溝12Aの側壁202Aの上部、及び、フィールド部203のいずれも、0.5〜1原子層以上あればよい。

【0026】

ついで、レジスト14を有機剥離やプラズマ処理等により除去して、配線溝12Aの側壁202Aの下部及び底面201A、並びに、ビア部12Bの底面201B及び側壁202Bにそれぞれ形成されたシード膜13を露出させる(図5)。レジスト14のエッチバックは、幅依存性が少ないため、配線幅の依存なく選択的に除去することができる。除去後にシード膜13の表面に変質層が形成された場合には、シード膜13表面を洗浄液、例えば、シュウ酸や希釈されたフッ素酸、あるいは市販の洗浄液によって処理しても良い。また、無電解めっき等でシード膜13表面に選択的に第一の金属M1を成長して、シード膜13表面のダメージを回復しても良い。

【0027】

その後、シード膜13に電流を供給して、電界めっき法によりめっき膜16を形成し、開口部12を埋設する。めっき膜16は、第一の金属M1としてCuを含むことが好ましく、Cuを主成分とすることがより好ましい。また、めっき膜16の形成に使用されるめっき液としては、例えば、硫酸銅水溶液に、成膜促進剤や成膜抑制剤を添加させることができる。成膜促進剤としては、例えば、スルホン酸ナトリウム塩を用いることができる。成膜抑制剤としては、例えば、ポリエチレングリコールやポリプロピレングリコールの共重合体を用いることができる。

【0028】

カバー膜15は、第一の金属M1に比べて抵抗率が高い第二の金属M2を含むため、カバー膜15自体の抵抗率もシード膜13より高くなっている。また、カバー膜15とシード膜13とでは、表面電位が異なり、カバー膜15では、シード膜13よりも電流密度が低くなっている。また、カバー膜15は、シード膜13よりも酸化されやすいため、カバー膜15に形成された自然酸化膜の電位障壁により、めっき液中の第一の金属M1のイオンが電荷交換して第一の金属M1の原子となって堆積するのを妨げることができる。加えて、電荷交換した中性の第一の金属M1の原子は表面吸着しにくく、マイグレートしてシード膜13が露出した箇所で析出する。さらに、オストワルド腐食により、原子状態の第一の金属M1はある一定以上の体積がないとめっき液に溶解してしまう。カバー膜15上では、上記の理由でめっき成長が抑制されるため、めっき膜16は殆ど成膜されない。このカバー膜15の効果により、めっき膜16は、配線溝12Aの底面201A、及び、その近傍の側壁202A、並びにビア部12Bのみから成長する。そのため、めっき開始直後は、ビア部12Bはが従来のめっき成長をし、同時に配線溝12Aの底面201A及び側壁202Aにも若干めっき成膜される(図6)。

【0029】

ビア部12Bが埋め込まれると、配線溝12Aの底面201Aから配線溝12Aの上端に向かってめっき膜16が成長する(図7)。

【0030】

通常、配線溝12Aの埋め込み終了時においても、フィールド部203には、めっき膜16がほとんど成膜されない(図8)が、第二の金属M2及びめっきの電流密度の上限を最適化することで、フィールド部203には、めっき膜16が実質的に成膜されないようにすることができる。例えば、めっきの電流密度は、0.1〜10A/dm2程度とすることができる。フィールド部203からのめっき膜16の成長を確実に抑制することで、配線溝12Aが埋設される前に、フィールド部203のめっき成長が開口部12に到達するのを確実に防止することができる。なお、シード膜13にかける電流値は、電流密度と半導体基板10の面積と開口部12の開口率との積とすればよい。

【0031】

ついで、めっき膜16等に第一の熱処理(アニール)を施し、シード膜13及びめっき膜16の結晶を成長させる。熱処理条件は、例えば、100〜400℃、5分〜1時間とすることができる。これにより、シード膜13とめっき膜16とは一体的な膜となるので、以後、これを配線膜17aという。また、この第一の熱処理で、カバー膜15は、シード膜13及びめっき膜16中を拡散して、主にめっき膜16表面に偏析する(図9)。図9では、カバー膜15の形状が残存して、配線膜17a中に金属膜15aとして検出できる例を示しているが、図9中、金属膜15aを示す領域に、第二の金属M2の高濃度領域が設けられていてもよい。また、熱処理後も、カバー膜15が成膜されていた付近の第二の金属M2の濃度は相対的に高くなっている。また、図示する金属膜15aや、第二の金属M2の高濃度領域内でも、場所によっては第二の金属M2の濃度が異なるが、配線膜17aの他の領域に比較して一定以上、第二の金属M2の濃度が高い領域となっていればよい。なお、第二の金属M2の濃度が均一に拡散するまで、熱処理を加えることもできる。

【0032】

その後、化学機械研磨(Chemical Mechanical Polishing、CMP)によりフィールド部203上のシード膜13及びカバー膜15を除去する(図10)。本実施の形態では、フィールド部203へのめっき膜16の成膜が抑制されているため、かかるCMP工程を時短化することができる。また、研磨剤の使用量を削減して、製造コストを削減することができる。なお、カバー膜15を配線溝12Aの上端近傍に留まるように第一の熱処理をすることで、かかるCMP工程により開口部12の側壁上部に形成されたカバー膜15を完全に除去することもできる。

【0033】

ついで、さらに、第二の熱処理をすることで、銅などの第一の金属M1を主成分とする、デュアルダマシン構造の埋め込み配線17が形成される。かかる埋め込み配線17では、配線膜17aの表面、カバー膜15が成膜されていた領域、及び、これらの近傍に、第二の金属M2の濃度が高い状態が作られる(図11)。また、カバー膜15は配線抵抗を上昇させることがあるが、図11に示すように表面近傍に僅かに金属膜15aが残るように熱処理すれば、配線抵抗には影響しない。カバー膜15を構成する金属材料の最適化や、第一、第二の熱処理の条件の最適化により、配線溝12Aの内部のカバー膜15や第二の金属M2の高濃度領域は実質的に無くなり、埋め込み配線17の表面のみに高濃度領域を作成することができる。

【0034】

また、第一、第二の熱処理は、酸素や水分を含む雰囲気で行うこともできる。こうすることで、第一の金属M1の表面に酸化物を形成させることができるため、配線膜17a中に第二の金属M2の拡散を促進させることができる。さらに、第一の金属M1がCuであり、第二の金属M2がTiの場合は、アンモニアや窒素を含む雰囲気で行ってもよい。これにより、第二の金属M2の拡散を促進させるだけでなく、Cu表面にTiNを偏析させることができるため、信頼性を向上させることができる。熱処理中に配線膜17aの表面にこれらの雰囲気のプラズマを照射しても良い。

【0035】

その後、任意の工程を経て、半導体装置を完成させる。図21に示すように層間絶縁膜103上にさらに多層絶縁膜を成膜し、上記説明した方法を繰り返して、シングルダマシン構造の金属配線やデュアルダマシン構造の金属配線を形成させてもよい。

【0036】

こうして得られた半導体装置は、図11で示すように、層間絶縁膜102、103に形成された開口部12と、例えばCuなどの第一の金属M1を主成分とし、開口部12を埋め込む配線膜17aとを備える埋め込み配線17を有している。配線膜17aは、第一の金属M1よりも抵抗率の高い第二の金属M2をさらに含み、開口部12の上部における配線膜17a中の第二の金属M2の濃度が、開口部12の下部における配線膜17a中の第二の金属M2の濃度よりも高い。具体的には、開口部12の深さ中心よりも開口側の配線膜17aでは、底面側の配線膜17aに比較して、第二の金属M2の濃度が高い。また、第二の金属M2の濃度は、面方向で一定であってもよいし、不均一であってもよいが、不均一である場合は、上面視において、開口部12の周縁及び中心から所定範囲にある配線膜17aでは、開口部12の周縁又は中心の配線膜17aに比較して、第二の金属M2の濃度が高くなっている。

【0037】

図11に示す例では、埋め込み配線17は、MOSトランジスタ101に接続している。また、開口部12の上部の配線膜17a中に、第二の金属M2を含む金属膜15aが形成されているが、金属膜15aの示す部分が、開口部12の下部における配線膜17a中の第二の金属M2の濃度に比較して第二の金属M2を高濃度に含む領域であってもよい。

【0038】

また、前述のとおり、層間絶縁膜102と、層間絶縁膜103とがこの順で積層された多層絶縁膜を構成しており、開口部12が、層間絶縁膜102及び層間絶縁膜103を貫通して形成されている。層間絶縁膜103における開口部12内の第二の金属M2の濃度は、層間絶縁膜102における開口部12内の第二の金属M2の濃度よりも高くなっている。

【0039】

また、埋め込み配線17は、開口部12として、配線溝12A、及び、配線溝12Aと接続しているビア部12Bを備えており、配線膜17aにより配線溝12A及びビア部12Bが埋め込まれたデュアルダマシン構造を有している。配線溝12A内の第二の金属M2の濃度は、ビア部12B内の第二の金属M2の濃度よりも高くなっている。

【0040】

以上のような半導体装置によれば、ボイドなく開口部12が埋め込まれているため、配線信頼性の高い半導体装置とすることができる。

【0041】

つづいて、本実施の形態の効果について説明する。本実施の形態の技術によれば、シード膜13を形成した後、めっき膜16の形成前にレジスト14で開口部12を埋め込み、レジスト14を選択的に除去することにより、開口部12の側壁からフィールド部にわたってカバー膜を形成する。これにより、開口部12の側壁202の上部及びフィールド部203におけるめっき成長を抑制して、フィールド部203からのめっき成長が開口部12に到達する前に、開口部12の内部のめっき成長を開口部12の上端に到達させることができる。したがって、ボイドの発生なく開口部12を埋設して、微細な埋め込み配線17を形成することが可能になる。

【0042】

ここで、関連する技術について説明する。

近年の半導体装置においては配線での信号伝搬の遅延が素子動作を律速している。配線での遅延定数は配線抵抗と配線間容量との積で表されるので、配線材料に比抵抗値の小さいCuを用いることにより、配線抵抗を下げて素子動作を高速化させることが行われている。

【0043】

多層配線は、ダマシン(damascene)法で形成されることが一般的である。ダマシン法は、層間絶縁膜等の絶縁膜を加工して開口部を形成し、バリアメタル、シード膜を順に堆積させた後、シード膜を電解めっきのカソード電極とした配線金属の堆積により開口部を埋め込み、開口部を除く部分に堆積したバリアメタル及び配線金属のCMPによる除去し、バリア絶縁膜を堆積させる技術である。

【0044】

配線中にボイドと呼ばれる穴が存在すると、抵抗、信頼性、歩留等の電気特性が低下するため、開口部は、ボイドの無く、埋め込まれることが重要である。そこで、めっき液、例えばCuめっきには、硫酸銅の他に成膜促進剤と成膜抑制剤とが添加されて、開口部の底面での成膜速度が開口部の側壁よりも速くなるようにすることが行われる。これはボトムアップ埋設、あるいは、スーパーコンフォーマル埋設と呼ばれている。

【0045】

ボトムアップ成膜のメカニズムに関しては現在も詳細は不明であるが、一般に以下のように言われている。めっき液中にシードを浸漬すると、シードはめっき液中の成膜抑制剤及び成膜促進剤のそれぞれの濃度に応じた割合で、開口部の内部も外部も均一に覆われる。これにより、めっき成膜初期にはコンフォーマル成長して、開口部の内部も外部も全て同じ成膜速度で成膜される。しかしながら、吸着した成膜促進剤は脱離しないため、めっき成長が進むと開口部の底面での成膜促進剤の濃度が高くなり、底面の成膜速度が速くなる。こうしたボトムアップ成膜では、開口部の底面でのめっき成膜が、開口部の上端や側壁に比べて十分に速ければ、配線金属の堆積が閉塞する前に底面からの成長面が間口に到着して、ボイド無く埋め込むことができる。

【0046】

しかしながら、配線の微細化が進み開口部の開口寸法が小さくなると、従来のめっき液ではボトムアップ成長しなくなる。これは、寸法が小さいために成膜促進剤が底面で十分に高濃度化する前に、開口部の上端が閉塞してしまうためである。

【0047】

非特許文献1では、この対策としてめっき液中のCu、硫酸の高濃度化、成膜抑制剤、及び、ポリビニルピロリドン(polyvinylpyrollidone、PVP)の高分子化の手法が開示されている。非特許文献1には、硫酸の高濃度化により成膜促進剤が活性化され、Cuの高濃度化により析出確率が高くなり、ボトムアップ性が改善されることが説明されている。また、PVPを高分子化することでめっき液中での拡散速度が低下して、めっき成膜初期の開口部内への吸着量が少なくなり、開口部内の成膜促進剤の割合が高くなり、より微細な寸法でもボトムアップ可能となることも説明されている。

【0048】

しかしながら、本発明者の検討によれば、Cuや硫酸の高濃度化は硫酸銅析出によるパーティクルの発生やそれに伴う装置故障のリスクを増大させる。また、成膜抑制剤やPVPは使用中に分解するため、長期間使用すると効果が得られなくなる。これを防止するためには、頻繁にめっき液を交換すればよいが、コスト増加を招き、工業生産に適さない。さらに、非特許文献1の技術は、開口部内の成膜促進剤の効果を高めただけであり、ボトムアップのメカニズムは同じであるから、より微細な寸法ではボトムアップ成長しなくなってしまう。

【0049】

また、特許文献1に示す手法のように、開口部92aの側壁92cにのみ、めっき抑制膜95を形成すると、図20(a)に示すように、開口部92aの底面92b及び開口部92aの外のフィールド部92dからめっきは成長する。前述のように、シード膜93が開口部92aの底面92bも側壁92cも覆っている場合は、めっき膜96の成長が進むにつれて、めっき膜96上の開口部92aの底面の面積が減少して、めっき促進剤が濃縮され、底面の成膜は、側壁92cやフィールド部92dに比べて速くなっていく。しかし、側壁92cの全体をめっき抑制膜95で覆うと、めっきの成膜速度はフィールド部92dと同じ速さを保つことから、フィールド部92dのめっき膜96の成膜は等方的に進み、開口部92aの上端に迫り出す。このため、開口部92aのアスペクト比が0.5程度以上のパターンでは、ボトムアップ成長が開口部92aの上端に達する前に図20(b)に示すようにフィールド部92dからの成膜によって開口部92aが閉塞してしまう。一方、開口部92aのアスペクト比が0.5程度以下であると、ドライエッチチングの異方性が失われてくるために、数nmの厚さのめっき抑制膜95の側壁だけを残して除去するのは困難であり、めっき抑制膜95を開口部92aの側壁92cのみに選択的に形成させることができない。

【0050】

一方、本実施の形態では、レジスト14を塗布後にエッチバック等によって開口部12の底面201A、201Bのみを覆うように除去し、それをマスクとしてめっきを抑制するカバー膜15を選択的に成長することで、開口部12の底面201A、201B近傍のみでシード膜13を露出させている。これにより、配線幅に依らずに、開口部12の底面201A、201B近傍を除いた側壁202A、及び、フィールド部203にカバー膜15を成膜することができる。開口部12の側壁202の上部に堆積したカバー膜15は、シード膜13中の第一の金属M1よりも抵抗率の高い第二の金属M2を含むため、シード膜13と表面電位が異なっている。また、カバー膜15は、シード膜13よりも酸化されやすいため、表面が自然酸化されることで、還元反応が進行しにくいように構成されている。また、還元反応が進行する場合においても、シード膜13に比べて抵抗が高くなるように構成されているため、カバー膜15の電流密度を低くすることができる。このため、めっき膜16は、開口部12の側壁202の上部やフィールド部203には殆ど成膜されず開口部12の底面201A、201Bから優先的に成膜させることができる。これにより、開口部12が高アスペクト比になってもボトムアップ成膜が可能となり、配線幅のアスペクト比によらずに開口部12の底面201A、201B近傍からのみ、めっき膜を成長することが可能となる。このように、本実施の形態では、開口部12の側壁202Aや、フィールド部203からの成膜がないため、開口部12の埋設が完了する前に開口部12の上端が閉塞されることがない。したがって、ボイドの発生を低減させることができる。

【0051】

(第2の実施形態)

図12〜19は、本実施の形態の半導体装置の製造方法を説明する図である。図12〜19中、(a)が断面図であり、(b)が(a)のA−A'断面図である。本実施の形態では、第1の実施形態と異なる点のみ説明する。

【0052】

第1の実施形態で説明したように、半導体基板10上の層間絶縁膜102、103に形成された開口部12にバリアメタル膜104を成膜させた後、開口部12の底面201A、201B及び側壁202、並びに、開口部12以外の層間絶縁膜103の表面であるフィールド部203に、第一の金属M1を含むシード膜13を形成する。このとき、本実施の形態では、第1の実施形態とは異なり、ビア部12Bをシード膜301で埋設する(図12)。

【0053】

その後、第1の実施形態と同様に、シード膜301上にレジスト14を形成して、配線溝12Aをレジスト14で埋め込んだ後(図13)、レジスト14の一部を除去して、配線溝12Aの側壁202Aの上部、及び、フィールド部203にわたって形成されたシード膜301を露出させ(図14)、シード膜301が露出した配線溝12Aの側壁202Aの上部からフィールド部203にわたって、カバー膜15を形成する(図15)。ついで、レジスト14を除去して、シード膜13を露出させ(図16)、露出させたシード膜13にめっき膜16を形成し(図17、18)、開口部12を埋め込む(図19)。その後は、第1の実施の形態における説明、及び、図9〜11と同じである。

【0054】

本実施の形態の方法では、シード膜301にてビア部12Bがほぼ埋設されているため、第1の実施形態に比べて、ビア部12Bにボイドが発生するリスクをより確実に低減させることができる。

【0055】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。たとえば、実施の形態では、半導体基板にトランジスタが形成された構造を下地とする例を示したが、半導体基板に置き換えてトランジスタ上に形成された配線層を下地とすることもできる。

【符号の説明】

【0056】

10 半導体基板

12 開口部

12A 配線溝

12B ビア部

13 シード膜

14 レジスト

15 カバー膜

15a 金属膜

16 めっき膜

17a 配線膜

17 埋め込み配線

17B ビア部

101 MOSトランジスタ

102 層間絶縁膜

103 層間絶縁膜

104 バリアメタル膜

201A 底面

201B 底面

202 側壁

202A 側壁

202B 側壁

203 フィールド部

301 シード膜

90 ウェハ

902 層間絶縁膜

92 開口部

92a 開口部

92b 底面

92c 側壁

92d フィールド部

93 シード膜

95 めっき抑制膜

96 めっき膜

【技術分野】

【0001】

本発明は、半導体装置の製造方法、及び半導体装置に関する。

【背景技術】

【0002】

近年、半導体装置の配線構造の形成方法として、例えば、特許文献1や非特許文献1に記載のものが知られている。

【0003】

特許文献1では、表面に凹部を有するウェハの少なくとも凹部の底部、及び、側壁部に、Cuシード膜を形成し、Cuシード膜上に、少なくとも凹部の底部に位置するCuシード膜の部分が露出しかつ凹部の側壁部に位置するCuシード膜の部分を覆うようにRu膜又はTEOS膜を形成し、Cuシード膜に電流を供給して、Ru膜の形成された凹部に埋め込まれるように電解めっき法によりCuめっき膜を形成し、Cuめっき膜に熱処理を施した後、Ru膜又はTEOS膜を選択的に除去することが記載されている。特許文献1では、かかる方法により、凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができるとされている。

【0004】

非特許文献1では、成膜促進剤と、高分子の成膜抑制剤とを用いて、高アスペクト比のトレンチをCuで埋め込む技術が記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−80525号公報

【非特許文献】

【0006】

【非特許文献1】Jon Reid and Jian Zhou, "Electrofill Challenges and Directions for Future Device Generations", Advanced Metallization Conference 2007 Japan/Asia Session, pp.26-27

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記非特許文献1の技術は、成膜促進剤や成膜抑制剤の副反応の処理が必要となり、工業生産には適さない。また、半導体の微細化が進みトレンチの開口寸法が小さくなると、トレンチの底面にCuを堆積させる前に開口が塞がり、ボイドが発生してしまう。

【0008】

また、特許文献1の技術は、開口部(凹部)の側壁全面に、Ru膜又はTEOS膜といっためっき抑制膜を形成しており、開口部の底面、及び、開口部の外のフィールド部には、シード膜が露出している。そのため、開口部の底面にめっき膜の成長速度と、フィールド部のめっき膜の成長速度が同じになる。しかしながら、フィールド部のめっき膜は等方的に進むため、開口部に迫り出すように成長が進む。このため、開口部のアスペクト比が高くなると、底面からのめっき成長が開口部の上端に到達する前に、フィールド部からのめっき成長が開口部に到達して、開口部の上端を閉塞させてしまい、やはり、ボイドの発生を防ぐことができない。

【0009】

したがって、ボイドの発生を確実に防ぐことができる、微細配線の形成技術が未だ望まれる。

【課題を解決するための手段】

【0010】

本発明によれば、

絶縁膜に形成された開口部の底面及び側壁、並びに、前記開口部以外の前記絶縁膜上に、第一の金属を含むシード膜を形成する工程と、

前記シード膜上にマスク膜を形成して、前記開口部を前記マスク膜で埋め込む工程と、

前記開口部の底面上に形成された前記シード膜に前記マスク膜を残しつつ前記マスク膜の一部を除去して、前記開口部の前記側壁の上部から、前記開口部以外の前記絶縁膜上にわたって形成された前記シード膜を露出させる工程と、

前記開口部の前記側壁の上部、及び、前記開口部以外の前記絶縁膜上に位置する前記シード膜上に、前記第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成する工程と、

前記カバー膜を形成した後、前記開口部に残した前記マスク膜を除去して、前記シード膜を露出させる工程と、

露出させた前記シード膜に、前記第一の金属を含むめっき膜を形成する工程と、

を含む、半導体装置の製造方法が提供される。

【0011】

また、本発明によれば、

絶縁膜に形成された開口部と、

第一の金属を主成分とし、前記開口部を埋め込む配線膜と、

を備える埋め込み配線を有し、

前記配線膜は、前記第一の金属よりも抵抗率の高い第二の金属をさらに含み、

前記開口部の上部における前記配線膜中の前記第二の金属の濃度が、前記開口部の下部における前記配線膜中の前記第二の金属の濃度よりも高い、半導体装置が提供される。

【0012】

この発明によれば、シード膜を形成した後、めっき膜の形成前にマスク膜で開口部を埋め込み、マスク膜を選択的に除去することにより、開口部の側壁の上部から開口部以外の前記絶縁膜上(フィールド部)にわたってカバー膜を形成する。これにより、開口部の側壁の上部及びフィールド部におけるめっき成長を抑制して、フィールド膜からのめっき成長が開口部に到達する前に、開口部の内部のめっき成長を開口部の上端に到達させることができる。したがって、ボイドの発生なく開口部を埋設して、微細な埋め込み配線を形成することが可能になる。

【発明の効果】

【0013】

本発明によれば、微細配線においてもボイドの発生を確実に防ぐことができるため、信頼性の高い半導体装置を提供することができる。

【図面の簡単な説明】

【0014】

【図1】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図2】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図3】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図4】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図5】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図6】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図7】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図8】(a)が第1の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図9】(a)が実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図10】(a)が実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図11】実施の形態に係る半導体装置を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図12】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図13】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図14】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図15】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図16】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図17】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図18】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図19】(a)が第2の実施の形態に係る製造方法を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【図20】関連する技術を説明する図である。

【図21】実施の形態に係る半導体装置を模式的に示した断面図であり、(b)が(a)のA−A'断面図である。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0016】

(第1の実施形態)

図1〜11は、本実施の形態の半導体装置の製造方法を説明する図である。図1〜11中、(a)が断面図であり、(b)が(a)のA−A'断面図である。

【0017】

本実施の形態の製造方法は、層間絶縁膜102、103に形成された開口部12の底面201A、201B及び側壁202、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部203に、第一の金属M1を含むシード膜13を形成する工程(図1)と、シード膜13上にレジスト14(マスク膜)を形成して、開口部12をレジスト14で埋め込む工程(図2)と、開口部12の底面201A、201B上に形成されたシード膜103にレジスト14を残しつつレジスト14の一部を除去して、開口部12の側壁202の上部からフィールド部203にわたって形成されたシード膜13を露出させる工程(図3)と、開口部12の側壁202の上部、及び、フィールド部203に位置するシード膜13上に、第一の金属M1よりも抵抗率が高い第二の金属M2を含むカバー膜15を形成する工程(図4)と、カバー膜15を形成した後、レジスト14を除去して、シード膜13を露出させる工程(図5)と、露出させたシード膜13に、第一の金属M1を含むめっき膜16を形成する工程(図6〜8)と、を含む。

【0018】

以下、本実施の形態の半導体装置の製造方法について、具体的に説明する。なお、本明細書においては、説明の都合上、上下方向は、半導体基板10に向かう方向を下とし、層間絶縁膜102、103の積層方向を上として記載する。半導体基板10として、例えばシリコン基板を用い、MOSトランジスタ101等の半導体素子等を形成する。ついで、例えば化学気相成長法(Chemical Vapor Deposition:CVD法)あるいは塗布法により層間絶縁膜102(第一の絶縁膜)と層間絶縁膜103(第二の絶縁膜)とをこの順で積層させる。層間絶縁膜102、103は、例えば、シリコン酸化膜等の低誘電率膜とすることができる。層間絶縁膜102、103は、それぞれ、単層であってもよいし、多層であってもよい。

【0019】

ついで、フォトリソグラフィ技術及びRIE(反応性イオンエッチング)法を用いて、開口部12を形成する。具体的には、層間絶縁膜103上にレジストパターンを形成し、レジストパターンをマスクとして、RIEにより層間絶縁膜102、103をエッチングし、層間絶縁膜102、103を貫通するように開口部12を形成する。これにより、層間絶縁膜103には、配線溝12Aが形成され、層間絶縁膜102には、配線溝12Aに接続したビア部12Bが形成される。ビア部12Bは、MOSトランジスタ101に接続している。その後、アッシング等によりレジストパターンを除去する。

【0020】

ここで、ビア部12Bは、アスペクト比を3以下とすることが好ましい。また、ビア部12Bは、テーパー状にすると好ましい。こうすることで、ビア部12Bにおけるボイドの発生をより確実に抑えることができる。

【0021】

その後、例えばスパッタ法あるいはCVD法により、開口部12の底面201A、201B、及び側壁202A、202Bにバリアメタル膜104を成膜する。バリアメタル膜104は、例えば、半導体で使用されている金属材料を用いて形成させることができ、例えば、Ta、TaN、Ti、Ru、Ir、W、これらを含む金属膜、並びにこれらの積層膜とすることができる。バリアメタル膜104の厚みは、例えば、1〜20nmとすることができる。

【0022】

ついで、バリアメタル膜104上に、例えばスパッタ法やCVD法によりシード膜13を成膜する。シード膜13は、開口部12の底面201A、201B、側壁202A、202B、フィールド部203上に形成される。シード膜13に含まれる第1の金属M1は、例えば、Cu、Al、Sn、Zn、TiとすることができるがCuを必須成分とすることが好ましく、Cuを主成分とすることがより好ましい。シード膜13は、Cuと他の金属(Al、Sn、Zn、Ti等)との合金から形成させてもよい。シード膜13の厚みは、10〜100nmとすることができる。(図1)。

【0023】

その後、レジスト14を塗布して開口部12を埋め込む(図2)。本実施の形態では、配線溝12A及びビア部12Bのすべてをレジスト14で埋め込む。開口部12の粗密によって埋め込み高さが変わる場合や、フィールド部203と開口部12との間に段差ができる場合には、レジスト14を二回に分けて塗布したり、レジスト14をエッチバックしてから再度埋め込んだりしてもよい。また、ここではレジスト14を用いたが、均一な埋め込み高さを実現できる材料であれば他の材料も可能である。また、塗布以外の方法を採用して、開口部12をレジスト14で埋め込んでもよい。

【0024】

ついで、酸素を含むガスを用いたプラズマを用いてレジスト14を選択的にエッチバックし、フィールド部203と、層間絶縁膜103内の側壁202Aに形成されたシード膜13の一部を露出させ、かつ、配線溝12Aの内部にレジスト14を残す。換言すれば、配線溝12Aの側壁202Aの上部に形成されたシード膜13を露出させ、かつ、配線溝12Aの内部にレジスト14を残す(図3)。本実施の形態では、このとき、配線溝12Aの側壁202Aの下部、及び、ビア部12Bの側壁202Bにわたって形成されたシード膜13は、露出させない。

具体的には、配線溝12Aの深さ全体の10〜50%の範囲にあるシード膜13が露出されていればよい。

なお、ここでは、酸素を含むガスを用いたプラズマを使用しているが開口部12に埋め込んだ材料に合わせて適宜変更可能であり、ガスやプラズマを使用しなくても良い。

【0025】

ついで、シード膜13が露出している箇所に、電界めっき等により第二の金属M2を堆積させて、カバー膜15を選択的に成膜する(図4)。第二の金属M2は、第一の金属M1とは異なる金属であり、第一の金属M1よりも抵抗率が高いものであればよいが、第一の金属M1よりも酸化されやすいものが好ましく、100〜400℃の熱処理で、シード膜13やめっき膜16を拡散できるものが好ましい。例えば、Ni、W、Ru、Ti、Mn、Al、Sn等を用いることができるが、第一の金属M1がCuのときは、Niが好ましい。また、カバー膜15は、シード膜13よりも抵抗率が高く、かつ、酸化されやすいように、これらの金属を組み合わせた合金としてもよい。また、第二の金属M1に加え、なお、第二の金属M2は、電界めっきではなく無電解めっきやCVD等の手法で選択的に堆積させても良い。カバー膜15の膜厚は、配線溝12Aの側壁202Aの上部、及び、フィールド部203のいずれも、0.5〜1原子層以上あればよい。

【0026】

ついで、レジスト14を有機剥離やプラズマ処理等により除去して、配線溝12Aの側壁202Aの下部及び底面201A、並びに、ビア部12Bの底面201B及び側壁202Bにそれぞれ形成されたシード膜13を露出させる(図5)。レジスト14のエッチバックは、幅依存性が少ないため、配線幅の依存なく選択的に除去することができる。除去後にシード膜13の表面に変質層が形成された場合には、シード膜13表面を洗浄液、例えば、シュウ酸や希釈されたフッ素酸、あるいは市販の洗浄液によって処理しても良い。また、無電解めっき等でシード膜13表面に選択的に第一の金属M1を成長して、シード膜13表面のダメージを回復しても良い。

【0027】

その後、シード膜13に電流を供給して、電界めっき法によりめっき膜16を形成し、開口部12を埋設する。めっき膜16は、第一の金属M1としてCuを含むことが好ましく、Cuを主成分とすることがより好ましい。また、めっき膜16の形成に使用されるめっき液としては、例えば、硫酸銅水溶液に、成膜促進剤や成膜抑制剤を添加させることができる。成膜促進剤としては、例えば、スルホン酸ナトリウム塩を用いることができる。成膜抑制剤としては、例えば、ポリエチレングリコールやポリプロピレングリコールの共重合体を用いることができる。

【0028】

カバー膜15は、第一の金属M1に比べて抵抗率が高い第二の金属M2を含むため、カバー膜15自体の抵抗率もシード膜13より高くなっている。また、カバー膜15とシード膜13とでは、表面電位が異なり、カバー膜15では、シード膜13よりも電流密度が低くなっている。また、カバー膜15は、シード膜13よりも酸化されやすいため、カバー膜15に形成された自然酸化膜の電位障壁により、めっき液中の第一の金属M1のイオンが電荷交換して第一の金属M1の原子となって堆積するのを妨げることができる。加えて、電荷交換した中性の第一の金属M1の原子は表面吸着しにくく、マイグレートしてシード膜13が露出した箇所で析出する。さらに、オストワルド腐食により、原子状態の第一の金属M1はある一定以上の体積がないとめっき液に溶解してしまう。カバー膜15上では、上記の理由でめっき成長が抑制されるため、めっき膜16は殆ど成膜されない。このカバー膜15の効果により、めっき膜16は、配線溝12Aの底面201A、及び、その近傍の側壁202A、並びにビア部12Bのみから成長する。そのため、めっき開始直後は、ビア部12Bはが従来のめっき成長をし、同時に配線溝12Aの底面201A及び側壁202Aにも若干めっき成膜される(図6)。

【0029】

ビア部12Bが埋め込まれると、配線溝12Aの底面201Aから配線溝12Aの上端に向かってめっき膜16が成長する(図7)。

【0030】

通常、配線溝12Aの埋め込み終了時においても、フィールド部203には、めっき膜16がほとんど成膜されない(図8)が、第二の金属M2及びめっきの電流密度の上限を最適化することで、フィールド部203には、めっき膜16が実質的に成膜されないようにすることができる。例えば、めっきの電流密度は、0.1〜10A/dm2程度とすることができる。フィールド部203からのめっき膜16の成長を確実に抑制することで、配線溝12Aが埋設される前に、フィールド部203のめっき成長が開口部12に到達するのを確実に防止することができる。なお、シード膜13にかける電流値は、電流密度と半導体基板10の面積と開口部12の開口率との積とすればよい。

【0031】

ついで、めっき膜16等に第一の熱処理(アニール)を施し、シード膜13及びめっき膜16の結晶を成長させる。熱処理条件は、例えば、100〜400℃、5分〜1時間とすることができる。これにより、シード膜13とめっき膜16とは一体的な膜となるので、以後、これを配線膜17aという。また、この第一の熱処理で、カバー膜15は、シード膜13及びめっき膜16中を拡散して、主にめっき膜16表面に偏析する(図9)。図9では、カバー膜15の形状が残存して、配線膜17a中に金属膜15aとして検出できる例を示しているが、図9中、金属膜15aを示す領域に、第二の金属M2の高濃度領域が設けられていてもよい。また、熱処理後も、カバー膜15が成膜されていた付近の第二の金属M2の濃度は相対的に高くなっている。また、図示する金属膜15aや、第二の金属M2の高濃度領域内でも、場所によっては第二の金属M2の濃度が異なるが、配線膜17aの他の領域に比較して一定以上、第二の金属M2の濃度が高い領域となっていればよい。なお、第二の金属M2の濃度が均一に拡散するまで、熱処理を加えることもできる。

【0032】

その後、化学機械研磨(Chemical Mechanical Polishing、CMP)によりフィールド部203上のシード膜13及びカバー膜15を除去する(図10)。本実施の形態では、フィールド部203へのめっき膜16の成膜が抑制されているため、かかるCMP工程を時短化することができる。また、研磨剤の使用量を削減して、製造コストを削減することができる。なお、カバー膜15を配線溝12Aの上端近傍に留まるように第一の熱処理をすることで、かかるCMP工程により開口部12の側壁上部に形成されたカバー膜15を完全に除去することもできる。

【0033】

ついで、さらに、第二の熱処理をすることで、銅などの第一の金属M1を主成分とする、デュアルダマシン構造の埋め込み配線17が形成される。かかる埋め込み配線17では、配線膜17aの表面、カバー膜15が成膜されていた領域、及び、これらの近傍に、第二の金属M2の濃度が高い状態が作られる(図11)。また、カバー膜15は配線抵抗を上昇させることがあるが、図11に示すように表面近傍に僅かに金属膜15aが残るように熱処理すれば、配線抵抗には影響しない。カバー膜15を構成する金属材料の最適化や、第一、第二の熱処理の条件の最適化により、配線溝12Aの内部のカバー膜15や第二の金属M2の高濃度領域は実質的に無くなり、埋め込み配線17の表面のみに高濃度領域を作成することができる。

【0034】

また、第一、第二の熱処理は、酸素や水分を含む雰囲気で行うこともできる。こうすることで、第一の金属M1の表面に酸化物を形成させることができるため、配線膜17a中に第二の金属M2の拡散を促進させることができる。さらに、第一の金属M1がCuであり、第二の金属M2がTiの場合は、アンモニアや窒素を含む雰囲気で行ってもよい。これにより、第二の金属M2の拡散を促進させるだけでなく、Cu表面にTiNを偏析させることができるため、信頼性を向上させることができる。熱処理中に配線膜17aの表面にこれらの雰囲気のプラズマを照射しても良い。

【0035】

その後、任意の工程を経て、半導体装置を完成させる。図21に示すように層間絶縁膜103上にさらに多層絶縁膜を成膜し、上記説明した方法を繰り返して、シングルダマシン構造の金属配線やデュアルダマシン構造の金属配線を形成させてもよい。

【0036】

こうして得られた半導体装置は、図11で示すように、層間絶縁膜102、103に形成された開口部12と、例えばCuなどの第一の金属M1を主成分とし、開口部12を埋め込む配線膜17aとを備える埋め込み配線17を有している。配線膜17aは、第一の金属M1よりも抵抗率の高い第二の金属M2をさらに含み、開口部12の上部における配線膜17a中の第二の金属M2の濃度が、開口部12の下部における配線膜17a中の第二の金属M2の濃度よりも高い。具体的には、開口部12の深さ中心よりも開口側の配線膜17aでは、底面側の配線膜17aに比較して、第二の金属M2の濃度が高い。また、第二の金属M2の濃度は、面方向で一定であってもよいし、不均一であってもよいが、不均一である場合は、上面視において、開口部12の周縁及び中心から所定範囲にある配線膜17aでは、開口部12の周縁又は中心の配線膜17aに比較して、第二の金属M2の濃度が高くなっている。

【0037】

図11に示す例では、埋め込み配線17は、MOSトランジスタ101に接続している。また、開口部12の上部の配線膜17a中に、第二の金属M2を含む金属膜15aが形成されているが、金属膜15aの示す部分が、開口部12の下部における配線膜17a中の第二の金属M2の濃度に比較して第二の金属M2を高濃度に含む領域であってもよい。

【0038】

また、前述のとおり、層間絶縁膜102と、層間絶縁膜103とがこの順で積層された多層絶縁膜を構成しており、開口部12が、層間絶縁膜102及び層間絶縁膜103を貫通して形成されている。層間絶縁膜103における開口部12内の第二の金属M2の濃度は、層間絶縁膜102における開口部12内の第二の金属M2の濃度よりも高くなっている。

【0039】

また、埋め込み配線17は、開口部12として、配線溝12A、及び、配線溝12Aと接続しているビア部12Bを備えており、配線膜17aにより配線溝12A及びビア部12Bが埋め込まれたデュアルダマシン構造を有している。配線溝12A内の第二の金属M2の濃度は、ビア部12B内の第二の金属M2の濃度よりも高くなっている。

【0040】

以上のような半導体装置によれば、ボイドなく開口部12が埋め込まれているため、配線信頼性の高い半導体装置とすることができる。

【0041】

つづいて、本実施の形態の効果について説明する。本実施の形態の技術によれば、シード膜13を形成した後、めっき膜16の形成前にレジスト14で開口部12を埋め込み、レジスト14を選択的に除去することにより、開口部12の側壁からフィールド部にわたってカバー膜を形成する。これにより、開口部12の側壁202の上部及びフィールド部203におけるめっき成長を抑制して、フィールド部203からのめっき成長が開口部12に到達する前に、開口部12の内部のめっき成長を開口部12の上端に到達させることができる。したがって、ボイドの発生なく開口部12を埋設して、微細な埋め込み配線17を形成することが可能になる。

【0042】

ここで、関連する技術について説明する。

近年の半導体装置においては配線での信号伝搬の遅延が素子動作を律速している。配線での遅延定数は配線抵抗と配線間容量との積で表されるので、配線材料に比抵抗値の小さいCuを用いることにより、配線抵抗を下げて素子動作を高速化させることが行われている。

【0043】

多層配線は、ダマシン(damascene)法で形成されることが一般的である。ダマシン法は、層間絶縁膜等の絶縁膜を加工して開口部を形成し、バリアメタル、シード膜を順に堆積させた後、シード膜を電解めっきのカソード電極とした配線金属の堆積により開口部を埋め込み、開口部を除く部分に堆積したバリアメタル及び配線金属のCMPによる除去し、バリア絶縁膜を堆積させる技術である。

【0044】

配線中にボイドと呼ばれる穴が存在すると、抵抗、信頼性、歩留等の電気特性が低下するため、開口部は、ボイドの無く、埋め込まれることが重要である。そこで、めっき液、例えばCuめっきには、硫酸銅の他に成膜促進剤と成膜抑制剤とが添加されて、開口部の底面での成膜速度が開口部の側壁よりも速くなるようにすることが行われる。これはボトムアップ埋設、あるいは、スーパーコンフォーマル埋設と呼ばれている。

【0045】

ボトムアップ成膜のメカニズムに関しては現在も詳細は不明であるが、一般に以下のように言われている。めっき液中にシードを浸漬すると、シードはめっき液中の成膜抑制剤及び成膜促進剤のそれぞれの濃度に応じた割合で、開口部の内部も外部も均一に覆われる。これにより、めっき成膜初期にはコンフォーマル成長して、開口部の内部も外部も全て同じ成膜速度で成膜される。しかしながら、吸着した成膜促進剤は脱離しないため、めっき成長が進むと開口部の底面での成膜促進剤の濃度が高くなり、底面の成膜速度が速くなる。こうしたボトムアップ成膜では、開口部の底面でのめっき成膜が、開口部の上端や側壁に比べて十分に速ければ、配線金属の堆積が閉塞する前に底面からの成長面が間口に到着して、ボイド無く埋め込むことができる。

【0046】

しかしながら、配線の微細化が進み開口部の開口寸法が小さくなると、従来のめっき液ではボトムアップ成長しなくなる。これは、寸法が小さいために成膜促進剤が底面で十分に高濃度化する前に、開口部の上端が閉塞してしまうためである。

【0047】

非特許文献1では、この対策としてめっき液中のCu、硫酸の高濃度化、成膜抑制剤、及び、ポリビニルピロリドン(polyvinylpyrollidone、PVP)の高分子化の手法が開示されている。非特許文献1には、硫酸の高濃度化により成膜促進剤が活性化され、Cuの高濃度化により析出確率が高くなり、ボトムアップ性が改善されることが説明されている。また、PVPを高分子化することでめっき液中での拡散速度が低下して、めっき成膜初期の開口部内への吸着量が少なくなり、開口部内の成膜促進剤の割合が高くなり、より微細な寸法でもボトムアップ可能となることも説明されている。

【0048】

しかしながら、本発明者の検討によれば、Cuや硫酸の高濃度化は硫酸銅析出によるパーティクルの発生やそれに伴う装置故障のリスクを増大させる。また、成膜抑制剤やPVPは使用中に分解するため、長期間使用すると効果が得られなくなる。これを防止するためには、頻繁にめっき液を交換すればよいが、コスト増加を招き、工業生産に適さない。さらに、非特許文献1の技術は、開口部内の成膜促進剤の効果を高めただけであり、ボトムアップのメカニズムは同じであるから、より微細な寸法ではボトムアップ成長しなくなってしまう。

【0049】

また、特許文献1に示す手法のように、開口部92aの側壁92cにのみ、めっき抑制膜95を形成すると、図20(a)に示すように、開口部92aの底面92b及び開口部92aの外のフィールド部92dからめっきは成長する。前述のように、シード膜93が開口部92aの底面92bも側壁92cも覆っている場合は、めっき膜96の成長が進むにつれて、めっき膜96上の開口部92aの底面の面積が減少して、めっき促進剤が濃縮され、底面の成膜は、側壁92cやフィールド部92dに比べて速くなっていく。しかし、側壁92cの全体をめっき抑制膜95で覆うと、めっきの成膜速度はフィールド部92dと同じ速さを保つことから、フィールド部92dのめっき膜96の成膜は等方的に進み、開口部92aの上端に迫り出す。このため、開口部92aのアスペクト比が0.5程度以上のパターンでは、ボトムアップ成長が開口部92aの上端に達する前に図20(b)に示すようにフィールド部92dからの成膜によって開口部92aが閉塞してしまう。一方、開口部92aのアスペクト比が0.5程度以下であると、ドライエッチチングの異方性が失われてくるために、数nmの厚さのめっき抑制膜95の側壁だけを残して除去するのは困難であり、めっき抑制膜95を開口部92aの側壁92cのみに選択的に形成させることができない。

【0050】

一方、本実施の形態では、レジスト14を塗布後にエッチバック等によって開口部12の底面201A、201Bのみを覆うように除去し、それをマスクとしてめっきを抑制するカバー膜15を選択的に成長することで、開口部12の底面201A、201B近傍のみでシード膜13を露出させている。これにより、配線幅に依らずに、開口部12の底面201A、201B近傍を除いた側壁202A、及び、フィールド部203にカバー膜15を成膜することができる。開口部12の側壁202の上部に堆積したカバー膜15は、シード膜13中の第一の金属M1よりも抵抗率の高い第二の金属M2を含むため、シード膜13と表面電位が異なっている。また、カバー膜15は、シード膜13よりも酸化されやすいため、表面が自然酸化されることで、還元反応が進行しにくいように構成されている。また、還元反応が進行する場合においても、シード膜13に比べて抵抗が高くなるように構成されているため、カバー膜15の電流密度を低くすることができる。このため、めっき膜16は、開口部12の側壁202の上部やフィールド部203には殆ど成膜されず開口部12の底面201A、201Bから優先的に成膜させることができる。これにより、開口部12が高アスペクト比になってもボトムアップ成膜が可能となり、配線幅のアスペクト比によらずに開口部12の底面201A、201B近傍からのみ、めっき膜を成長することが可能となる。このように、本実施の形態では、開口部12の側壁202Aや、フィールド部203からの成膜がないため、開口部12の埋設が完了する前に開口部12の上端が閉塞されることがない。したがって、ボイドの発生を低減させることができる。

【0051】

(第2の実施形態)

図12〜19は、本実施の形態の半導体装置の製造方法を説明する図である。図12〜19中、(a)が断面図であり、(b)が(a)のA−A'断面図である。本実施の形態では、第1の実施形態と異なる点のみ説明する。

【0052】

第1の実施形態で説明したように、半導体基板10上の層間絶縁膜102、103に形成された開口部12にバリアメタル膜104を成膜させた後、開口部12の底面201A、201B及び側壁202、並びに、開口部12以外の層間絶縁膜103の表面であるフィールド部203に、第一の金属M1を含むシード膜13を形成する。このとき、本実施の形態では、第1の実施形態とは異なり、ビア部12Bをシード膜301で埋設する(図12)。

【0053】

その後、第1の実施形態と同様に、シード膜301上にレジスト14を形成して、配線溝12Aをレジスト14で埋め込んだ後(図13)、レジスト14の一部を除去して、配線溝12Aの側壁202Aの上部、及び、フィールド部203にわたって形成されたシード膜301を露出させ(図14)、シード膜301が露出した配線溝12Aの側壁202Aの上部からフィールド部203にわたって、カバー膜15を形成する(図15)。ついで、レジスト14を除去して、シード膜13を露出させ(図16)、露出させたシード膜13にめっき膜16を形成し(図17、18)、開口部12を埋め込む(図19)。その後は、第1の実施の形態における説明、及び、図9〜11と同じである。

【0054】

本実施の形態の方法では、シード膜301にてビア部12Bがほぼ埋設されているため、第1の実施形態に比べて、ビア部12Bにボイドが発生するリスクをより確実に低減させることができる。

【0055】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。たとえば、実施の形態では、半導体基板にトランジスタが形成された構造を下地とする例を示したが、半導体基板に置き換えてトランジスタ上に形成された配線層を下地とすることもできる。

【符号の説明】

【0056】

10 半導体基板

12 開口部

12A 配線溝

12B ビア部

13 シード膜

14 レジスト

15 カバー膜

15a 金属膜

16 めっき膜

17a 配線膜

17 埋め込み配線

17B ビア部

101 MOSトランジスタ

102 層間絶縁膜

103 層間絶縁膜

104 バリアメタル膜

201A 底面

201B 底面

202 側壁

202A 側壁

202B 側壁

203 フィールド部

301 シード膜

90 ウェハ

902 層間絶縁膜

92 開口部

92a 開口部

92b 底面

92c 側壁

92d フィールド部

93 シード膜

95 めっき抑制膜

96 めっき膜

【特許請求の範囲】

【請求項1】

絶縁膜に形成された開口部の底面及び側壁、並びに、前記開口部以外の前記絶縁膜上に、第一の金属を含むシード膜を形成する工程と、

前記シード膜上にマスク膜を形成して、前記開口部を前記マスク膜で埋め込む工程と、

前記開口部の底面上に形成された前記シード膜に前記マスク膜を残しつつ前記マスク膜の一部を除去して、前記開口部の前記側壁の上部から、前記開口部以外の前記絶縁膜上にわたって形成された前記シード膜を露出させる工程と、

前記開口部の前記側壁の上部、及び、前記開口部以外の前記絶縁膜上に位置する前記シード膜上に、前記第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成する工程と、

前記カバー膜を形成した後、前記開口部に残した前記マスク膜を除去して、前記シード膜を露出させる工程と、

露出させた前記シード膜に、前記第一の金属を含むめっき膜を形成する工程と、

を含む、半導体装置の製造方法。

【請求項2】

前記絶縁膜は、第一の絶縁膜と、第二の絶縁膜とがこの順で積層された多層絶縁膜であり、

前記開口部は、前記第一の絶縁膜と前記第二の絶縁膜とを貫通して形成されており、

前記シード膜を露出させる前記工程において、前記第二の絶縁膜内の前記側壁の上部に形成された前記シード膜を露出し、かつ、前記第二の絶縁膜内に前記マスク膜を残す、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記めっき膜を形成する前記工程の後、前記フィールド部に形成した前記カバー膜及び前記シード膜を除去する、請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記めっき膜を形成する前記工程の後に前記めっき膜を熱処理する工程をさらに含み、

前記めっき膜を熱処理する前記工程において、前記第二の金属を前記めっき膜中に拡散させて、前記第一の金属を主成分とする埋め込み配線を形成する、請求項1乃至3いずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記埋め込み配線がデュアルダマシン構造を有する、請求項4に記載の半導体装置の製造方法。

【請求項6】

前記開口部は、配線溝、及び、前記配線溝に接続しているビア部を備え、

前記シード膜を露出させる前記工程において、前記配線溝の前記側壁の上部に形成された前記シード膜を露出させ、かつ、前記配線溝の内部に前記マスク膜を残す、請求項1乃至5いずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記開口部を前記マスク膜で埋め込む前記工程において、前記ビア部を前記マスク膜で埋め込み、

前記シード膜を露出させる前記工程において、前記ビア部を前記マスク膜で埋め込んだ状態で、前記配線溝の前記側壁の上部に形成された前記シード膜を露出させる、請求項6に記載の半導体装置の製造方法。

【請求項8】

前記シード膜を形成する前記工程において、前記ビア部を前記シード膜で埋め込む、請求項6に記載の半導体装置の製造方法。

【請求項9】

前記第一の金属が銅である、請求項1乃至8いずれか1項に記載の半導体装置の製造方法。

【請求項10】

前記第二の金属がニッケルである、請求項1乃至9いずれか1項に記載の半導体装置の製造方法。

【請求項11】

絶縁膜に形成された開口部と、

第一の金属を主成分とし、前記開口部を埋め込む配線膜と、

を備える埋め込み配線を有し、

前記配線膜は、前記第一の金属よりも抵抗率の高い第二の金属をさらに含み、

前記開口部の上部における前記配線膜中の前記第二の金属の濃度が、前記開口部の下部における前記配線膜中の前記第二の金属の濃度よりも高い、半導体装置。

【請求項12】

前記開口部の上部において、前記配線膜中に、前記第二の金属を含む金属膜が形成されている、請求項11に記載の半導体装置。

【請求項13】

前記絶縁膜は、第一の絶縁膜と、第二の絶縁膜とがこの順で積層された多層絶縁膜であり、

前記開口部が前記第一の絶縁膜及び前記第二の絶縁膜に貫通して形成されており、

前記第二の絶縁膜における前記開口部内の前記第二の金属の濃度が、前記第一の絶縁膜における前記開口部内の前記第二の金属の濃度よりも高い、請求項11又は12に記載の半導体装置。

【請求項14】

前記埋め込み配線が、前記開口部として、配線溝、及び、前記配線溝に接続しているビア部を備え、前記配線膜により前記配線溝及び前記ビア部が埋め込まれたデュアルダマシン構造を有し、

前記配線溝内の第二の金属の濃度が、前記ビア部内の前記第二の金属の濃度よりも高い、請求項11又は12に記載の半導体装置。

【請求項15】

前記第一の金属が銅である、請求項11乃至14いずれか1項に記載の半導体装置。

【請求項16】

前記第二の金属がニッケルである、請求項11乃至15いずれか1項に記載の半導体装置。

【請求項1】

絶縁膜に形成された開口部の底面及び側壁、並びに、前記開口部以外の前記絶縁膜上に、第一の金属を含むシード膜を形成する工程と、

前記シード膜上にマスク膜を形成して、前記開口部を前記マスク膜で埋め込む工程と、

前記開口部の底面上に形成された前記シード膜に前記マスク膜を残しつつ前記マスク膜の一部を除去して、前記開口部の前記側壁の上部から、前記開口部以外の前記絶縁膜上にわたって形成された前記シード膜を露出させる工程と、

前記開口部の前記側壁の上部、及び、前記開口部以外の前記絶縁膜上に位置する前記シード膜上に、前記第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成する工程と、

前記カバー膜を形成した後、前記開口部に残した前記マスク膜を除去して、前記シード膜を露出させる工程と、

露出させた前記シード膜に、前記第一の金属を含むめっき膜を形成する工程と、

を含む、半導体装置の製造方法。

【請求項2】

前記絶縁膜は、第一の絶縁膜と、第二の絶縁膜とがこの順で積層された多層絶縁膜であり、

前記開口部は、前記第一の絶縁膜と前記第二の絶縁膜とを貫通して形成されており、

前記シード膜を露出させる前記工程において、前記第二の絶縁膜内の前記側壁の上部に形成された前記シード膜を露出し、かつ、前記第二の絶縁膜内に前記マスク膜を残す、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記めっき膜を形成する前記工程の後、前記フィールド部に形成した前記カバー膜及び前記シード膜を除去する、請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記めっき膜を形成する前記工程の後に前記めっき膜を熱処理する工程をさらに含み、

前記めっき膜を熱処理する前記工程において、前記第二の金属を前記めっき膜中に拡散させて、前記第一の金属を主成分とする埋め込み配線を形成する、請求項1乃至3いずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記埋め込み配線がデュアルダマシン構造を有する、請求項4に記載の半導体装置の製造方法。

【請求項6】

前記開口部は、配線溝、及び、前記配線溝に接続しているビア部を備え、

前記シード膜を露出させる前記工程において、前記配線溝の前記側壁の上部に形成された前記シード膜を露出させ、かつ、前記配線溝の内部に前記マスク膜を残す、請求項1乃至5いずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記開口部を前記マスク膜で埋め込む前記工程において、前記ビア部を前記マスク膜で埋め込み、

前記シード膜を露出させる前記工程において、前記ビア部を前記マスク膜で埋め込んだ状態で、前記配線溝の前記側壁の上部に形成された前記シード膜を露出させる、請求項6に記載の半導体装置の製造方法。

【請求項8】

前記シード膜を形成する前記工程において、前記ビア部を前記シード膜で埋め込む、請求項6に記載の半導体装置の製造方法。

【請求項9】

前記第一の金属が銅である、請求項1乃至8いずれか1項に記載の半導体装置の製造方法。

【請求項10】

前記第二の金属がニッケルである、請求項1乃至9いずれか1項に記載の半導体装置の製造方法。

【請求項11】

絶縁膜に形成された開口部と、

第一の金属を主成分とし、前記開口部を埋め込む配線膜と、

を備える埋め込み配線を有し、

前記配線膜は、前記第一の金属よりも抵抗率の高い第二の金属をさらに含み、

前記開口部の上部における前記配線膜中の前記第二の金属の濃度が、前記開口部の下部における前記配線膜中の前記第二の金属の濃度よりも高い、半導体装置。

【請求項12】

前記開口部の上部において、前記配線膜中に、前記第二の金属を含む金属膜が形成されている、請求項11に記載の半導体装置。

【請求項13】

前記絶縁膜は、第一の絶縁膜と、第二の絶縁膜とがこの順で積層された多層絶縁膜であり、

前記開口部が前記第一の絶縁膜及び前記第二の絶縁膜に貫通して形成されており、

前記第二の絶縁膜における前記開口部内の前記第二の金属の濃度が、前記第一の絶縁膜における前記開口部内の前記第二の金属の濃度よりも高い、請求項11又は12に記載の半導体装置。

【請求項14】

前記埋め込み配線が、前記開口部として、配線溝、及び、前記配線溝に接続しているビア部を備え、前記配線膜により前記配線溝及び前記ビア部が埋め込まれたデュアルダマシン構造を有し、

前記配線溝内の第二の金属の濃度が、前記ビア部内の前記第二の金属の濃度よりも高い、請求項11又は12に記載の半導体装置。

【請求項15】

前記第一の金属が銅である、請求項11乃至14いずれか1項に記載の半導体装置。

【請求項16】

前記第二の金属がニッケルである、請求項11乃至15いずれか1項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2012−195488(P2012−195488A)

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願番号】特願2011−59216(P2011−59216)

【出願日】平成23年3月17日(2011.3.17)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願日】平成23年3月17日(2011.3.17)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]