半導体装置の製造方法、製造システムおよび調整装置

【課題】製品の歩留まりを向上させることができる半導体装置の製造方法、製造システムおよび調整装置を提供すること。

【解決手段】実施形態にかかる半導体装置の製造方法は、成膜工程と、加工工程と、イオン注入工程と、アニール工程と、調整工程とを含む。成膜工程では、基板上に半導体の薄膜を成膜する。加工工程では、薄膜を所定の形状に加工する。イオン注入工程では、所定の形状に加工された薄膜に対してイオン注入処理を行う。アニール工程では、イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成する。調整工程では、成膜工程における薄膜の成膜条件および成膜結果と加工工程における薄膜の加工結果とのうち、少なくともいずれか1つに基づき、イオン注入工程におけるイオン注入処理の処理条件およびアニール工程におけるアニール処理の処理条件の双方または一方を調整する。

【解決手段】実施形態にかかる半導体装置の製造方法は、成膜工程と、加工工程と、イオン注入工程と、アニール工程と、調整工程とを含む。成膜工程では、基板上に半導体の薄膜を成膜する。加工工程では、薄膜を所定の形状に加工する。イオン注入工程では、所定の形状に加工された薄膜に対してイオン注入処理を行う。アニール工程では、イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成する。調整工程では、成膜工程における薄膜の成膜条件および成膜結果と加工工程における薄膜の加工結果とのうち、少なくともいずれか1つに基づき、イオン注入工程におけるイオン注入処理の処理条件およびアニール工程におけるアニール処理の処理条件の双方または一方を調整する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法、製造システムおよび調整装置に関する。

【背景技術】

【0002】

従来、基板上に半導体の薄膜を成膜する工程と成膜された薄膜を加工する工程とを繰り返して半導体装置を製造する半導体装置の製造方法が知られている。かかる半導体装置の製造方法では、各工程が終了する毎に薄膜の形状や特性を測定し、測定結果に基づいて各工程における処理条件をフィードバック制御することにより、次回薄膜の成膜や加工を行う際の成膜精度や加工精度を向上させていた。

【0003】

しかしながら、各工程における処理条件をフィードバック制御した場合、フィードバック制御による効果は、次回以降に成膜や加工が行われる薄膜に対して反映されるものであるため、今回成膜や加工が行われた製品の歩留まりが低下するという問題がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】再表2004/036639号公報

【特許文献2】特開2000−100973号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、製品の歩留まりを向上させることができる半導体装置の製造方法、製造システムおよび調整装置を提供することである。

【課題を解決するための手段】

【0006】

実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、成膜工程と、加工工程と、イオン注入工程と、アニール工程と、調整工程とを含む。成膜工程では、基板上に半導体の薄膜を成膜する。加工工程では、薄膜を所定の形状に加工する。イオン注入工程では、所定の形状に加工された薄膜に対してイオン注入処理を行う。アニール工程では、イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成する。調整工程では、成膜工程における薄膜の成膜条件および成膜結果と加工工程における薄膜の加工結果とのうち、少なくともいずれか1つに基づき、イオン注入工程におけるイオン注入処理の処理条件およびアニール工程におけるアニール処理の処理条件の双方または一方を調整する。

【図面の簡単な説明】

【0007】

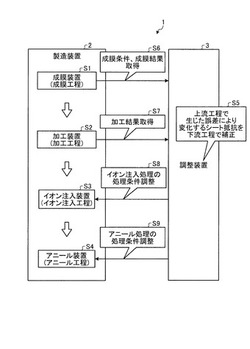

【図1】第1の実施形態にかかる製造システムによる製造方法を示す説明図。

【図2】第1の実施形態にかかる製造システムの構成を示す説明図。

【図3】第1の実施形態にかかる成膜装置を示す模式図。

【図4】第1の実施形態にかかる加工装置による寸法の計測位置を示す図。

【図5A】第1の実施形態にかかる膜厚関数情報の一例を示す説明図。

【図5B】第1の実施形態にかかる寸法関数情報の一例を示す説明図。

【図5C】第1の実施形態にかかる寸法関数情報の一例を示す説明図。

【図6】第1の実施形態にかかる炉内係数情報の一例を示す図。

【図7A】第1の実施形態にかかるドーズ量関数情報の一例を示す説明図。

【図7B】第1の実施形態にかかるアニール温度関数情報の一例を示す説明図。

【図8A】第1の実施形態にかかるイオン注入処理の処理条件を調整する手順を示す説明図。

【図8B】第1の実施形態にかかるアニール処理の処理条件を調整する手順を示す説明図。

【図9】第1の実施形態にかかる製造装置処理および調整装置処理の一例を示す図。

【図10】変形例1にかかる製造装置処理および調整装置処理の一例を示す図。

【図11】変形例2にかかる製造装置処理および調整装置処理の一例を示す図。

【図12】変形例3にかかる製造装置処理および調整装置処理の一例を示す図。

【図13】第2の実施形態にかかる製造システムの構成を示す説明図。

【図14】第2の実施形態にかかる成膜条件情報の一例を示す説明図。

【図15】第2の実施形態にかかるエッチング条件情報の一例を示す説明図。

【図16】第2の実施形態にかかる調整装置が実行する処理を示すフローチャート。

【発明を実施するための形態】

【0008】

以下に、添付図面を参照して、第1の実施形態および第2の実施形態にかかる半導体装置の製造方法、半導体装置の製造システムおよび調整装置を詳細に説明する。なお、以下に示す実施形態によって本発明が限定されるものではない。また、以下では、半導体装置の製造方法を単に「製造方法」と記載し、半導体装置の製造システムを単に「製造システム」と記載する。

【0009】

(第1の実施形態)

まず、第1の実施形態にかかる製造システムによる製造方法について、図1を用いて説明する。図1は、第1の実施形態にかかる製造システム1による製造方法を示す説明図である。なお、図1では、製造システム1の構成を簡略化して図示している。また、かかる製造システム1の詳細については、図2を用いて後述する。

【0010】

また、以下では、ポリシリコン等の半導体の薄膜抵抗素子(以下、「抵抗素子」と記載する)を生成する場合について説明する。また、製造システム1は、抵抗素子以外にコンデンサ等の受動素子やトランジスタ等の能動素子も生成することができる。

【0011】

また、以下では、説明を簡単にする観点から、第1の実施形態にかかる製造システム1に含まれる成膜装置、加工装置、イオン注入装置およびアニール装置を総称する場合、製造装置と呼ぶこととする。

【0012】

図1に示すように、製造システム1は、半導体装置を製造する製造装置2と製造装置2に含まれる複数の装置の動作を調整する調整装置3とを含む。そして、製造システム1では、ポリシリコンの抵抗素子を生成する場合、まず、シリコンウエハ等の基板上にポリシリコンの薄膜を成膜する成膜工程を成膜装置が行う(ステップS1)。

【0013】

続いて、製造装置2では、成膜された薄膜を所定の形状に加工する加工工程を加工装置が行う(ステップS2)。加工装置は、かかる加工工程によって薄膜を抵抗素子の形状に加工する。続いて、製造装置2では、イオン注入装置が抵抗素子の形状に加工された薄膜に対して不純物イオンのイオン注入処理を施すイオン注入工程を行う(ステップS3)。

【0014】

続いて、製造装置2では、不純物イオンが注入された薄膜に対してアニール処理を施すアニール工程をアニール装置が行う(ステップS4)。アニール装置は、かかるアニール工程により薄膜内の不純物イオンを活性化して抵抗素子を生成する。なお、かかる抵抗素子には、以後の工程によって抵抗素子の電極が設けられる。

【0015】

ところで、かかる製造装置2では、最終生成物である抵抗素子のシート抵抗を如何に所望の抵抗値へ近付けるかが重要である。ここで、製造装置2によって生成される抵抗素子のシート抵抗は、抵抗素子の膜厚、寸法、不純物イオン濃度、および不純物イオンの活性化率に依存する。

【0016】

そこで、製造システム1では、成膜工程や加工工程という上流工程で薄膜の膜厚や寸法に誤差が生じた場合、上流工程で生じた誤差により変化する最終的なシート抵抗をイオン注入工程やアニール工程という下流工程で調整装置3が補正する(ステップS5)。

【0017】

具体的には、調整装置3は、成膜装置によって薄膜が成膜されると、成膜装置から薄膜の成膜時に適用された成膜条件と、薄膜の成膜結果とを取得する(ステップS6)。たとえば、調整装置3は、成膜条件として成膜時における成膜炉内の温度を取得し、成膜結果として成膜された薄膜の膜厚を取得する。

【0018】

また、調整装置3は、加工装置によって薄膜の形状が加工されると、加工装置から薄膜の加工結果を取得する(ステップS7)。たとえば、調整装置3は、加工結果として、抵抗素子の形状に加工された薄膜の寸法を取得する。

【0019】

ここでの寸法とは、抵抗素子の形状に加工された薄膜の基板上における長さおよび幅である。なお、ここでの長さは、薄膜を抵抗素子として機能させた場合に電流が流れる方向の基板上における長さであり、幅は、電流が流れる方向と直交する方向の基板上における長さである。

【0020】

続いて、調整装置3は、取得した成膜条件、成膜結果および加工結果のうち、少なくともいずれか1つに基づき、イオン注入処理の処理条件を調整することで抵抗素子のシート抵抗を補正する(ステップS8)。

【0021】

たとえば、調整装置3は、取得した成膜条件、成膜結果および加工結果のうち、少なくともいずれか1つに基づき、抵抗素子のシート抵抗を予測する。そして、調整装置3は、予測したシート抵抗と予め定められた所望の抵抗値との差分を低減するように、イオン注入処理の処理時間や不純物イオンのドーズ量を調整する。なお、かかる調整の詳細については、図8Aを用いて後述する。

【0022】

続いて、調整装置3は、取得した成膜条件、成膜結果および加工結果のうち、少なくともいずれか1つに基づき、アニール処理の処理条件を調整することで抵抗素子のシート抵抗を補正する(ステップS9)。

【0023】

たとえば、調整装置3は、取得した成膜条件、成膜結果および加工結果のうち、少なくともいずれか1つに基づいて予測したシート抵抗と予め定められた所望の抵抗値との差分を低減するように、アニール処理の処理時間や処理温度を調整する。なお、かかる調整の詳細については、図8Bを用いて後述する。

【0024】

このように、調整装置3は、上流工程で生じた誤差により変化するシート抵抗の目的値からのズレを下流工程で補正する。これにより、製造システム1では、最終生成物である抵抗素子のシート抵抗を予め定められた抵抗値へ近付けることができるため、シート抵抗のバラツキを抑制することができる。したがって、製造システム1によれば、製品の歩留まりを向上させることができる。

【0025】

なお、ここでは、調整装置3がイオン注入処理の処理条件およびアニール処理の処理条件の双方を調整する場合について説明したが、調整装置3は、イオン注入処理の処理条件およびアニール処理の処理条件のいずれか一方を調整することもできる。なお、かかる点については、図11および図12を用いて後述する。

【0026】

次に、図2を用いて第1の実施形態にかかる製造システム1の構成について説明する。図2は、第1の実施形態にかかる製造システム1の構成を示す説明図である。図2に示すように、製造システム1は、製造装置2と、調整装置3とを含む。製造装置2は、成膜装置21、加工装置22、イオン注入装置23およびアニール装置24を含む。

【0027】

成膜装置21は、LP−CVD(Low Pressure―Chemical Vapor Deposition)を行うことでシリコンウエハ等の基板上に半導体の薄膜を成膜する装置である。ここで、図3を用いて成膜装置21について説明する。図3は、第1の実施形態にかかる成膜装置21を示す模式図である。

【0028】

図3に示すように、成膜装置21は、複数の基板26を収納して処理する成膜炉25を備えている。また、成膜炉25は、処理対象となる複数の基板26を縦方向に多段に収納する。

【0029】

また、成膜装置21には、成膜する薄膜の膜厚に応じて予め定められた複数種類の成膜条件が設定される。たとえば、成膜装置21には、成膜時における成膜炉25内の温度、成膜時間、成膜炉25に導入する原料ガスの流量、成膜炉25内の圧力等の成膜条件が設定される。

【0030】

そして、成膜装置21は、設定された複数種類の成膜条件に基づき、成膜炉25内でLP−CVDを行うことにより基板26上に半導体(ここでは、ポリシリコン)の薄膜を成膜する。

【0031】

かかる縦型の成膜装置21では、成膜炉25内における基板26の位置(以下、「炉内位置」と記載する)によって成膜される薄膜の膜質に差が生じる。たとえば、図3に示すような縦型の成膜炉25の場合、上下方向へ多段に収納した複数の基板26にポリシリコンの薄膜を成膜すると、ポリシリコンのグレインサイズは、成膜する基板26の炉内位置が成膜炉25内の上段へ行くほど大きくなる傾向にある。

【0032】

そして、グレインサイズが異なるポリシリコン膜に対して同一の処理条件でイオン注入処理およびアニール処理を行った場合、グレインサイズが大きなポリシリコン膜は、グレインサイズが小さなポリシリコン膜に比べシート抵抗が小さくなる。すなわち、ポリシリコンのグレインサイズにバラツキが生じた場合、抵抗素子のシート抵抗にもバラツキが生じる。

【0033】

そこで、製造システム1では、成膜炉25内の空間を縦方向について複数(ここでは、6つ)の炉内位置A、B、C、D、EおよびFに分け、最上段の炉内位置Aおよび最下段の炉内位置Fを除く炉内位置B、C、DおよびEで成膜された基板26を次の工程へ送る。

【0034】

また、成膜装置21は、各種成膜条件が設定された場合に、設定された成膜条件を調整装置3へ出力し、薄膜が完了すると、成膜した薄膜の膜厚を計測し、計測結果を成膜結果として調整装置3へ出力する。このとき成膜装置21は、膜厚を計測した基板26の炉内位置B、C、DおよびEと成膜結果とを対応付けて調整装置3へ出力する。

【0035】

図2の説明に戻り製造装置2の説明を続ける。加工装置22は、成膜装置21によって成膜された薄膜を所定形状に加工する装置である。ここでは、加工装置22は、設定された加工条件に基づいてポリシリコンの薄膜を抵抗素子の形状に加工する。

【0036】

具体的には、加工装置22は、ポリシリコンの薄膜上にフォトレジストを塗布し、フォトリソグラフィーによってフォトレジストに所定のパターニングを施すことでレジストマスクを形成する。続いて、加工装置22は、レジストマスクを用いてRIE(Reactive Ion Etching)を行うことによってポリシリコンの薄膜を抵抗素子の形状に加工する。

【0037】

そして、加工装置22は、各種加工条件が設定された場合に、設定された加工条件を調整装置3へ出力し、薄膜の形状を加工した場合に、加工した薄膜の寸法を計測し、計測結果を加工結果として調整装置3へ出力する。

【0038】

ここで、図4を用いて加工装置22による寸法の計測位置について説明する。図4は、第1の実施形態にかかる加工装置22による寸法の計測位置を示す図である。図4に示すように、加工装置22は、各基板26を中心からの距離に応じて複数(ここでは、3つ)の計測領域G、HおよびIに分割する。

【0039】

そして、加工装置22は、各計測領域G、HおよびI内で抵抗素子の形状に加工された薄膜の寸法、すなわち、基板26の面上における薄膜の長さおよび幅を計測し、計測結果を計測領域G、HおよびI毎に調整装置3へ出力する。

【0040】

図2の説明に戻り製造装置2の説明を続ける。イオン注入装置23は、所定形状に加工されたポリシリコンの薄膜に対して不純物イオンをイオン注入する装置である。かかるイオン注入装置23は、イオン注入処理を行った場合に、イオン注入処理の処理条件を調整装置3へ出力する。たとえば、イオン注入装置23は、イオン注入した不純物イオンのドーズ量や不純物イオンの注入時間等を処理条件として調整装置3へ出力する。

【0041】

アニール装置24は、不純物イオンがイオン注入されたポリシリコンの薄膜に対して熱処理を行うことにより、薄膜内の不純物イオンを活性化させて抵抗素子を生成する装置である。

【0042】

調整装置3は、製造装置2に含まれる成膜装置21、加工装置22、イオン注入装置23およびアニール装置24の各装置で実行される製造工程の内容を調整する装置であり、制御部4と記憶部5とを備えている。

【0043】

記憶部5は、成膜装置情報50、成膜結果情報51、加工装置情報52、加工結果情報53、膜厚関数情報54、寸法関数情報55aおよび55b、炉内位置係数情報56、ドーズ量関数情報57、アニール温度関数情報58、シート抵抗情報59を記憶する記憶デバイスである。

【0044】

成膜装置情報50は、成膜装置21に設定された各種成膜条件の設定履歴であり、具体的には、成膜時における成膜炉25内の温度、成膜時間、成膜炉25に導入する原料ガスの流量、成膜炉25内の圧力等の成膜条件に関する設定履歴である。成膜結果情報51は、成膜装置21によって成膜された薄膜の膜厚を測定した測定値である。

【0045】

加工装置情報52は、加工装置22に設定された各種加工条件の設定履歴であり、具体的には、フォトグラフィーの際に用いた露光マスクの種類や露光時における露光マスクの位置情報等に関する履歴である。加工結果情報53は、加工装置22によって加工された薄膜の寸法を測定した測定値である。

【0046】

膜厚関数情報54は、成膜工程で成膜された薄膜の膜厚と、成膜工程で成膜された薄膜に対してイオン注入処理およびアニール処理を施した場合の薄膜のシート抵抗との関係を示す関数である。

【0047】

また、寸法関数情報55aおよび55bは、加工工程で形状を加工された薄膜の寸法と、加工工程で形状を加工された薄膜に対してイオン注入およびアニール処理を施した場合の薄膜のシート抵抗との関係を示す関数である。

【0048】

ここで、図5A、図5B、図5Cを用いて膜厚関数情報54および寸法関数情報55a、55bの一例について説明する。図5Aは、第1の実施形態にかかる膜厚関数情報54の一例を示す説明図であり、図5Bおよび図5Cは、第1の実施形態にかかる寸法関数情報55a、55bの一例を示す説明図である。

【0049】

図5Aに示すように、膜厚関数情報54は、次式

シート抵抗=−a×(抵抗素子の膜厚)+b・・・式(1)

によって表わされるシート抵抗と薄膜の膜厚との関係を示す関数である。なお、式(1)におけるaおよびbは、薄膜の寸法、イオン注入処理およびアニール処理の処理条件から算出される正の定数である。同図に示すように、シート抵抗の抵抗値は、薄膜の膜厚が大きくなるほど低下する。

【0050】

なお、図5Aでは、膜厚関数情報54として1つの関数を例示しているが、記憶部5は、薄膜の寸法、イオン注入処理およびアニール処理の処理条件の組み合わせ毎に、複数の関数を記憶する。かかる膜厚関数情報54は、制御部4が成膜装置情報50や成膜結果情報51に基づいてシート抵抗を予測する際に用いられる。

【0051】

また、図5Bに示すように、寸法関数情報55aは、次式

シート抵抗=c×(抵抗素子の寸法)+d・・・式(2)

によって表わされるシート抵抗とシート抵抗の寸法(長さ)との関係を示す関数である。なお、式(2)におけるcおよびdは、薄膜の膜厚、イオン注入処理およびアニール処理の処理条件から算出される正の定数である。同図に示すように、シート抵抗の抵抗値は、薄膜の長さが大きくなるほど上昇する。

【0052】

また、図5Cに示すように、寸法関数情報55bは、シート抵抗とシート抵抗の寸法(幅)との関係を示す関数である。かかるシート抵抗の幅に関する寸法関数情報55bは、上記式(2)と同様に一次関数によって表わされる。

【0053】

ただし、シート抵抗の幅に関する寸法関数情報55bの場合、上記式(2)における定数cは、負の定数となる。すなわち、シート抵抗の抵抗値は、薄膜の幅が大きくなるほど低下する。

【0054】

なお、図5Bおよび図5Cでは、寸法関数情報55aおよび55bとして、それぞれ1つの関数を例示しているが、記憶部5は、薄膜の膜厚、イオン注入処理およびアニール処理の処理条件の組み合わせ毎に、複数の関数を記憶する。かかる寸法関数情報55aおよび55bは、制御部4が加工結果情報53に基づいてシート抵抗を予測する際に用いられる。

【0055】

図2の説明に戻り調整装置3の説明を続ける。炉内位置係数情報56は、成膜装置21から加工装置22へ送られる基板26の成膜炉25内における炉内位置B、C、DおよびEと所定の炉内位置係数とを対応付けた情報である。

【0056】

かかる炉内位置係数情報56は、制御部4が膜厚関数情報54に基づいて予測したシート抵抗を補正する際に用いられる。前述したように、成膜工程で成膜された薄膜は、成膜炉25内の炉内位置B、C、DおよびEによって膜質が異なり、かかる膜質の違いによって最終的なシート抵抗も薄膜が成膜された炉内位置B、C、DおよびEによって変わってくる。

【0057】

このため、膜厚関数情報54に基づいて予測されたシート抵抗は、炉内位置B、C、DおよびE毎に補正する必要がある。そこで、調整装置3では、成膜装置21から加工装置22へ送られる基板26の成膜炉25内における炉内位置B、C、DおよびEと所定の炉内位置係数とを対応付けた炉内位置係数情報56を記憶部5によって記憶している。

【0058】

ここで、図6を用いて炉内位置係数情報56の一例について説明する。図6は、第1の実施形態にかかる炉内位置係数情報56の一例を示す図である。なお、図6に示す炉内位置B、C、DおよびEは、図3に示す炉内位置B、C、DおよびEに対応する。

【0059】

前述したように、成膜装置21の成膜炉25では、成膜する基板26の炉内位置B、C、DおよびEが成膜炉25内の上段へ行くほどポリシリコンのグレインサイズが大きくなり、シート抵抗が小さくなる傾向がある。

【0060】

そこで、図6に示すように、炉内位置係数情報56では、各炉内位置B、C、DおよびEに対して、各炉内位置B、C、DおよびEが成膜炉25内で上段に行くほど小さくなる炉内位置係数α、β、γおよびδをそれぞれ対応付けている。

【0061】

そして、制御部4は、膜厚関数情報54に基づいて予測した薄膜のシート抵抗へ、薄膜が成膜された炉内位置B、C、DおよびEに対応した炉内位置係数α、β、γおよびδを乗算することで、炉内位置B、C、DおよびE毎に予測したシート抵抗を補正する。

【0062】

図2の説明に戻り、ドーズ量関数情報57は、薄膜へイオン注入する不純物イオンのドーズ量と抵抗素子のシート抵抗との関係を示す関数である。また、アニール温度関数情報58は、アニール処理における処理温度と薄膜のシート抵抗との関係を示す関数である。

【0063】

ここで、図7Aおよび図7Bを用いてドーズ量関数情報57およびアニール温度関数情報58の一例について説明する。図7Aは、第1の実施形態にかかるドーズ量関数情報57の一例を示す説明図であり、図7Bは、第1の実施形態にかかるアニール温度関数情報58の一例を示す説明図である。

【0064】

図7Aに示すように、ドーズ量関数情報57は、次式

ドーズ量=e×(シート抵抗)2−f×(シート抵抗)+g・・・式(3)

によって表わされる不純物イオンのドーズ量と抵抗素子のシート抵抗との関係を示す関数である。なお、式(3)におけるe、fおよびgは、薄膜の成膜条件、薄膜の膜厚および寸法から算出される正の定数である。同図に示すように、シート抵抗の抵抗値は、ドーズ量を増大するほど低下する。また、シート抵抗の低下率は、ドーズ量が増大するほど低くなる。

【0065】

なお、図7Aでは、ドーズ量関数情報57として1つの関数を例示しているが、記憶部5は、薄膜の成膜条件、薄膜の膜厚および寸法の組み合わせ毎に、複数の関数を記憶する。かかるドーズ量関数情報57は、制御部4がイオン注入処理の処理条件を調整する際に用いられる。

【0066】

また、図7Bに示すように、アニール温度関数情報58は、次式

シート抵抗=−h×(アニール温度)+i・・・式(4)

によって表わされるシート抵抗とアニール処理の処理温度との関係を示す関数である。なお、式(4)におけるhおよびiは、薄膜の成膜条件、薄膜の膜厚および寸法から算出される正の定数である。同図に示すように、シート抵抗の抵抗値は、アニール処理の処理温度が高くなるほど低下する。

【0067】

なお、図7Bでは、アニール温度関数情報58として1つの関数を例示しているが、記憶部5は、薄膜の成膜条件、薄膜の膜厚および寸法の組み合わせ毎に、複数の関数を記憶する。かかるアニール温度関数情報58は、制御部4がアニール処理の処理条件を調整する際に用いられる。

【0068】

なお、調整装置3は、アニール温度関数情報58に加え、アニール処理の処理時間とシート抵抗との関係を示す情報を記憶部5へ記憶させ、かかる情報に基づいて制御部4がアニール処理の処理条件を調整するように構成することもできる。また、シート抵抗情報59は、予め定められた抵抗素子のシート抵抗に関する目標値である。

【0069】

制御部4は、調整装置3全体の動作を統括制御する処理部であり、たとえば、CPU(Central Processing Unit)とROM(Read Only Memory)とRAM(Random Access Memory)とを有する情報処理装置である。

【0070】

かかる制御部4は、CPUがROMから各種プログラムを読出し、RAMを作業領域として使用して実行することにより機能する成膜補正部41、形状補正部42および調整部43を備えている。

【0071】

成膜補正部41は、成膜装置21に設定されている成膜条件を調整することによって成膜工程で成膜される薄膜の膜厚が予め設定された所望の膜厚となるように補正する処理部である。

【0072】

具体的には、成膜補正部41は、成膜装置21によって薄膜が成膜される毎に、成膜時における成膜炉25内の温度、成膜時間、成膜炉25に導入する原料ガスの流量、成膜炉25内の圧力等の成膜条件を成膜装置21から取得する。そして、成膜補正部41は、取得した各成膜条件を成膜装置情報50として記憶部5へ順次記憶させる。

【0073】

また、成膜補正部41は、成膜装置21によって薄膜が成膜される毎に、成膜された薄膜の膜厚の測定結果を成膜結果として取得し、取得した成膜結果を成膜結果情報51として記憶部5へ記憶させる。

【0074】

そして、成膜補正部41は、成膜装置情報50と成膜結果情報51とに基づいて、次回成膜される薄膜の膜厚と今回成膜された膜厚とが一致するように調整した成膜条件を成膜装置21へ出力して設定する。これにより、成膜工程で成膜される薄膜の膜厚が予め設定された所望の膜厚へ近付くように補正される。

【0075】

形状補正部42は、加工装置22に設定されている加工条件を調整することによって加工工程で加工される薄膜の寸法が予め設定された所望の寸法となるように補正する処理部である。

【0076】

具体的には、形状補正部42は、加工装置22によって薄膜の形状が加工される毎に、フォトグラフィーの際に用いた露光マスクの種類や露光時における露光マスクの位置情報等の加工条件を加工装置22から取得する。そして、形状補正部42は、取得した各加工条件を加工装置情報52として記憶部5へ順次記憶させる。

【0077】

また、形状補正部42は、加工装置22によって薄膜の形状が加工される毎に、加工された薄膜の寸法に関する測定結果を加工結果として取得し、取得した加工結果を加工結果情報53として記憶部5へ記憶させる。

【0078】

そして、形状補正部42は、加工装置情報52と加工結果情報53とに基づいて、次回加工される薄膜の寸法と今回加工された薄膜の寸法とが一致するように調整した加工条件を加工装置22へ出力して設定する。これにより、加工工程で成膜される薄膜の寸法が予め設定された所望の寸法へ近付くように補正される。

【0079】

調整部43は、記憶部5によって記憶されている各種情報に基づいて、イオン注入装置23によるイオン注入処理の処理条件およびアニール装置24によるアニール処理の処理条件を調整することによって抵抗素子のシート抵抗のバラツキを抑制する処理部である。

【0080】

かかる調整部43は、イオン注入処理およびアニール処理の処理条件を調整する場合、成膜工程によって成膜された薄膜を用いて生成される抵抗素子のシート抵抗および加工工程によって加工された薄膜を用いて生成される抵抗素子のシート抵抗を予測する。

【0081】

具体的には、調整部43は、成膜装置21によって薄膜が成膜されると、成膜装置情報50および成膜結果情報51を記憶部5から読み出し、読み出した成膜装置情報50および成膜結果情報51に基づき、成膜工程によって成膜された薄膜の膜厚を判別する。

【0082】

たとえば、調整部43は、記憶部5によって記憶されている成膜装置情報50から算出した膜厚と、成膜結果情報51として記憶部5に記憶されている膜厚とを平均化した膜厚を成膜工程によって成膜された薄膜の膜厚として判別する。

【0083】

なお、調整部43は、成膜装置情報50から算出した膜厚を成膜工程によって成膜された薄膜の膜厚として判別してもよく、成膜結果情報51として記憶部5に記憶されている膜厚を成膜工程によって成膜された薄膜の膜厚として判別してもよい。

【0084】

続いて、調整部43は、記憶部5から膜厚関数情報54を読み出し、読み出した膜厚関数情報54の式(1)へ判別した膜厚を代入することによってシート抵抗を算出する。このとき調整部43は、成膜炉25の炉内位置B、C、DおよびE毎にシート抵抗を算出する。

【0085】

続いて、調整部43は、炉内位置B、C、DおよびE毎に算出した各シート抵抗に対して対応する炉内位置係数情報56の炉内係数α、β、γおよびδをそれぞれ乗算することにより、成膜工程によって成膜された薄膜を用いて生成される抵抗素子のシート抵抗の予測値を算出する。これにより、調整部43は、炉内位置B、C、DおよびEを考慮したシート抵抗の予測値を精度よく算出することができる。

【0086】

また、調整部43は、加工装置22によって薄膜の形状が加工されると、加工工程によって加工された薄膜を用いて生成される抵抗素子のシート抵抗を予測する。具体的には、調整部43は、記憶部5から加工結果情報53および寸法関数情報55aおよび55bを読み出す。

【0087】

続いて、調整部43は、加工結果情報53における薄膜の寸法を寸法関数情報55aおよび55bの式(2)へ代入することでシート抵抗の予測値を算出する。このとき、調整部43は、寸法の計測領域G、HおよびI(図4参照)毎にシート抵抗の予測値を算出する。

【0088】

そして、調整部43は、算出したシート抵抗の予測値を用いてイオン注入処理およびアニール処理の処理条件を調整する。ここで、図8Aおよび図8Bを用いてイオン注入処理およびアニール処理の処理条件を調整する手順について説明する。

【0089】

図8Aは、第1の実施形態にかかるイオン注入処理の処理条件を調整する手順を示す説明図であり、図8Bは、第1の実施形態にかかるアニール処理の処理条件を調整する手順を示す説明図である。

【0090】

図8Aに示すように、調整部43は、イオン注入処理の処理条件を調整する場合、算出したシート抵抗の予測値Jとシート抵抗情報59として記憶されている目的値Kとを比較する。そして、調整部43は、シート抵抗の予測値Jがシート抵抗の目的値Kよりも大きい場合、イオン注入装置23に設定されているドーズ量の既定値Lをドーズ量関数情報57に基づいて調整値Mまで上昇させる。一方、調整部43は、シート抵抗の予測値Jがシート抵抗の目的値Kよりも小さい場合には、イオン注入装置23に設定されているドーズ量を低下させる。

【0091】

このように、調整部43は、上流工程で成膜した薄膜の膜厚や寸法と予め定められた所望の膜厚や寸法との間に誤差が生じた場合、下流工程でイオン注入処理の処理条件を調整することにより最終的な抵抗素子のシート抵抗を目的値Kへ近付けることができる。したがって、製造システム1によれば、抵抗素子のシート抵抗にバラツキが生じることを抑制することができる。

【0092】

また、図8Bに示すように、調整部43は、アニール処理の処理条件を調整する場合、算出したシート抵抗の予測値Oとシート抵抗情報59として記憶されている目的値Pとを比較する。そして、調整部43は、シート抵抗の予測値Oがシート抵抗の目的値Pよりも小さい場合、アニール装置24に設定されている処理温度の既定値Qをアニール温度関数情報58に基づいて調整値Rまで低下させる。一方、調整部43は、シート抵抗の予測値Oがシート抵抗の目的値Pよりも大きい場合、アニール装置24に設定されている処理温度を上昇させる。

【0093】

また、調整部43は、アニール処理の処理条件を調整する場合、加工結果情報53に基づき、薄膜の寸法が計測された計測領域G、H、I毎、すなわち、薄膜の基板26上における位置毎に処理条件を調整する。

【0094】

このように、調整部43は、上流工程で成膜した薄膜の膜厚や寸法と予め定められた所望の膜厚や寸法との間に誤差が生じた場合、下流工程でアニール処理の処理条件を薄膜の基板26上における位置毎に調整する。これにより、製造システム1では、最終的な抵抗素子のシート抵抗を目的値Pへ近付けることができるので、抵抗素子のシート抵抗にバラツキが生じることを抑制することができる。

【0095】

次に、図9を用いて第1の実施形態にかかる製造システム1で製造装置2が実行する製造装置処理および調整装置3が実行する調整装置処理について説明する。図9は、第1の実施形態にかかる製造装置処理および調整装置処理の一例を示す図である。

【0096】

図9に示すように、製造システム1では、成膜装置21がLP−CVDを行うことにより基板26上にポリシリコンの薄膜を形成する(ステップS101)。一方、調整装置3は、成膜装置21によって薄膜が成膜されると、調整装置3は、成膜装置21から成膜装置情報50および成膜結果情報51を取得する(ステップS201)。

【0097】

続いて、調整装置3は、取得した成膜装置情報50および成膜結果情報51に基づき、成膜装置21によって成膜された薄膜によって生成される抵抗素子のシート抵抗を予測する(ステップS202)。続いて、調整装置3は、予測したシート抵抗と予め定められた所望の抵抗値との差分を低減可能なイオン注入処理の処理条件を算出し(ステップS203)、算出した処理条件をイオン注入装置23へ設定する(ステップS204)。

【0098】

また、加工装置22は、成膜装置21によって薄膜が成膜された基板26が搬入されると、搬入された基板26に成膜されている薄膜をフォトリソグラフィーおよびRIEによって抵抗素子の形状に加工する(ステップS102)。

【0099】

続いて、イオン注入装置23は、加工装置22によって形状が加工された基板26が搬入されると、搬入された基板26に対し、調整装置3によって設定された処理条件で不純物イオンのイオン注入処理を行う(ステップS103)。

【0100】

一方、調整装置3は、加工装置22によって薄膜が抵抗素子の形状に加工されると、加工装置22から加工結果情報53を取得する(ステップS205)。続いて、調整装置3は、イオン注入装置23からイオン注入処理の処理結果を取得する(ステップS206)。

【0101】

続いて、調整装置3は、加工装置22から取得した加工結果情報53とイオン注入装置23から取得した処理結果とに基づいて抵抗素子の最終的なシート抵抗を予測する(ステップS207)。

【0102】

続いて、調整装置3は、予測したシート抵抗と予め定められた所望の抵抗値との差分を低減可能なアニール処理の処理条件を算出し(ステップS208)、算出した処理条件をアニール装置24へ設定する(ステップS209)。最後に、アニール装置24は、調整装置3によって設定された処理条件でアニール処理を行い(ステップS104)、抵抗素子を生成する。

【0103】

このように、上述した第1の実施形態では、製造システム1の調整装置3が、上流工程である成膜工程の処理条件および処理結果に基づき、下流工程であるイオン注入処理の処理条件を調整することによって上流工程で生じた誤差を下流工程で補正する。

【0104】

さらに、製造システム1では、調整装置3が上流工程である加工工程の加工結果と、調整後の処理条件で実行されたイオン注入処理の処理結果とに基づき、下流工程であるアニール処理の処理条件を調整することによって上流工程で生じた誤差を補正する。

【0105】

これにより、製造システム1では、仮に上流工程で誤差が生じた場合であっても、最終生成物となる抵抗素子のシート抵抗を予め定められた所望の抵抗値へ近付けることができるため、抵抗素子のシート抵抗にバラツキが生じることを抑制することができる。

【0106】

なお、製造装置処理および調整装置処理は、図9に示す処理に限定するものではない。以下では、図10〜図12を用いて第1の実施形態にかかる製造装置処理および調整装置処理の変形例1〜3について説明する。

【0107】

図10は、変形例1にかかる製造装置処理および調整装置処理の一例を示す図であり、図11は、変形例2にかかる製造装置処理および調整装置処理の一例を示す図であり、図12は、変形例3にかかる製造装置処理および調整装置処理の一例を示す図である。

【0108】

なお、図10〜図12では、図9に示す処理と同一の処理に対して同一のステップ番号を付している。図10に示すように、変形例1は、調整装置処理におけるステップS300およびステップS301だけが図9に示す処理と異なる。

【0109】

すなわち、変形例1にかかる調整装置3は、図9に示す処理と同様に、上流工程である成膜工程の処理条件および処理結果に基づき、下流工程であるイオン注入処理の処理条件を調整することによって上流工程で生じた誤差を下流工程で補正する。

【0110】

さらに、調整装置3は、加工装置22からの加工結果情報53の取得(ステップS205)およびイオン注入装置23からの処理結果の取得(ステップS206)を行った後、成膜装置情報50および成膜結果情報51を記憶部5から読み出す(ステップS300)。

【0111】

続いて、調整装置3は、加工結果情報53、イオン注入処理の処理結果、成膜装置情報50および成膜結果情報51に基づいて最終的なシート抵抗を予測する(ステップS301)。その後、予測したシート抵抗に基づいてアニール処理の処理条件を算出し(ステップS208)、処理条件をアニール装置24へ設定する(ステップS209)。

【0112】

このように、変形例1にかかる調整装置3は、加工結果情報53およびイオン注入処理の処理結果に加え、再度、成膜装置情報50および成膜結果情報51を考慮してアニール処理の処理条件を調整する。これにより、変形例1にかかる製造システムによれば、最終生成物となる抵抗素子のシート抵抗を予め定められた所望の抵抗値へ、より正確に近付けることができる。

【0113】

また、図11に示すように、変形例2は、イオン注入装置23が予め定められた処理条件でイオン注入処理を実行する(ステップS400)点および調整装置3が図9に示すステップS205〜209の処理を実行する点が図9に示す処理と異なる。

【0114】

また、図12に示すように、変形例3は、アニール装置24が予め設定された処理条件でアニール処理を実行する(ステップS500)点および調整装置3が図9に示すステップS201〜204の処理を実行する点が図9に示す処理と異なる。

【0115】

かかる変形例2および変形例3によっても、上流工程で誤差が生じた場合に、最終生成物となる抵抗素子のシート抵抗を予め定められた所望の抵抗値へ近付けることができるため、抵抗素子のシート抵抗にバラツキが生じることを抑制することができる。

【0116】

しかも、変形例2および変形例3によれば、調整装置3は、イオン注入処理またはアニール処理のいずれか一方の処理条件を算出して対応する装置へ設定するだけで済むため、処理負荷を低減しつつ、シート抵抗のバラツキを抑制することができる。

【0117】

なお、上述した第1の実施形態および変形例1〜3では、調整装置3がイオン注入処理のドーズ量を調整する場合について説明したが、調整装置3は、イオン注入処理のイオン注入時間を調整してもよい。また、調整装置3は、ドーズ量およびイオン注入時間の双方を調整してもよい。かかる構成とする場合、調整装置3は、処理時間が最短となるようにドーズ量およびイオン注入時間を調整する。

【0118】

また、上述した第1の実施形態および変形例1〜3では、調整装置3がアニール処理の処理温度を調整する場合について説明したが、調整装置3は、アニール処理の処理時間を調整してもよい。また、調整装置3は、アニール処理の処理温度および処理時間の双方を調整してもよい。かかる構成とする場合、調整装置3は、処理時間が最短となるように処理温度および処理時間を調整する。

【0119】

(第2の実施形態)

次に、第2の実施形態にかかる製造システムによる製造方法について説明する。図13は、第2の実施形態にかかる製造システム10の構成を示す説明図である。なお、図13には、製造システム10の特徴を説明するために必要な構成要素を図示しており、一般的な構成要素については図示を省略している。

【0120】

図13に示すように、製造システム10は、成膜装置11、エッチング装置12、膜厚測定装置13、調整装置14を備え、半導体の薄膜を成膜した後、薄膜をエッチングして膜厚を所望の膜厚(以下、「目標膜厚」と記載する)まで低減するシステムである。

【0121】

具体的には、成膜装置11は、シリコンウエハ等の基板や基板上にシリコン層等の半導体層が形成されたウエハを酸化させる酸化炉を備える。そして、成膜装置11は、酸化炉の内部で複数枚のウエハを熱処理することによってウエハ上に酸化させた半導体の薄膜(以下、「酸化膜」と記載する)を成膜する。

【0122】

かかる成膜装置11は、予め設定された所定の成膜条件の下で酸化膜の成膜工程を行う。なお、成膜条件は、成膜する酸化膜の用途等によって任意に設定変更される。そして、成膜装置11は、成膜条件の設定時、または酸化膜の成膜前、もしくは酸化膜の成膜後に、成膜条件を示す成膜条件情報16aを調整装置14へ出力する。かかる成膜条件情報16aの一例については、図14を参照して後述する。

【0123】

エッチング装置12は、成膜装置11によって成膜された酸化膜をウェットエッチングすることによって酸化膜の膜厚を目標膜厚まで低減する装置である。かかるエッチング装置12は、予め設定された所定のエッチング条件または調整装置14によって調整されたエッチング条件の下で酸化膜のエッチング工程を行う。

【0124】

また、エッチング装置12は、エッチングを行う前に、これから行うエッチング工程のエッチング条件を示すエッチング条件情報16bを調整装置14へ出力する。なお、エッチング条件情報16bの一例については、図15を参照して後述する。

【0125】

膜厚測定装置13は、成膜装置11によって成膜された酸化膜の膜厚およびエッチング装置12によってエッチングされた酸化膜の膜厚を測定する装置である。かかる膜厚測定装置13は、調整装置14から膜厚測定指示が入力された場合に、酸化膜の膜厚を測定し、測定結果を調整装置14へ出力する。

【0126】

調整装置14は、成膜装置11における酸化膜の成膜条件およびエッチング装置12におけるエッチング条件に基づいてエッチング装置12におけるエッチング条件を調整する装置である。具体的には、調整装置14は、調整部15と記憶部16とを備える。

【0127】

記憶部16は、成膜装置11から入力される成膜条件情報16aと、エッチング装置12から入力されるエッチング条件情報16bと、目標膜厚情報16cとを記憶する。なお、目標膜厚情報16cは、酸化膜の目標膜厚を示す情報であり、外部から任意に設定変更が可能な情報である。

【0128】

ここで、図14および図15を参照し、成膜条件情報16aおよびエッチング条件情報16bについて説明する。図14は、第2の実施形態にかかる成膜条件情報16aの一例を示す説明図であり、図15は、第2の実施形態にかかるエッチング条件情報16bの一例を示す説明図である。

【0129】

図14に示すように、成膜条件情報16aは、装置内位置、処理温度、処理圧力、ガス流量、処理時間のそれぞれを示す情報を含む。装置内位置は、酸化炉におけるウエハの載置位置を示す情報である。本実施形態では、酸化炉内部の各領域に対して1、2、3・・・というように装置内位置を示す番号を付している。

【0130】

また、処理温度は、酸化膜を成膜する際の酸化炉内部の温度であり、処理圧力は、酸化膜を成膜する際の酸化炉内部の気圧である。また、ガス流量は、酸化膜を成膜する際に酸化炉内部へ単位時間に導入される処理ガスの流量(容積)であり、処理時間は、酸化膜の成膜にかける処理時間である。

【0131】

ここで、図14におけるs、t、u、vは、成膜条件情報16aにおける処理温度、処理圧力、ガス流量、処理時間のそれぞれを示す数値である。なお、成膜条件情報16aとして、図14に示す情報に加え、例えば、処理ガスの種類や酸化炉内部における処理ガスの濃度を示す情報等を含めてもよい。

【0132】

また、図15に示すように、エッチング条件情報16bは、処理時間、処理回数、処理温度のそれぞれを示す情報を含む。処理時間は、酸化膜のウェットエッチングにかける処理時間であり、処理回数は、同じウエハに対して所定の単位時間内に繰り返しエッチングを行う処理回数であり、処理温度は、ウェットエッチングに使用するエッチャントの温度である。

【0133】

ここで、図15におけるw、x、yは、エッチング条件情報16bにおける処理時間、処理回数、処理温度のそれぞれを示す数値である。なお、エッチング条件情報16bとして、図15に示す情報に加え、例えば、エッチャントの種類や濃度を示す情報等を含めてもよい。

【0134】

次に、図13へ戻り調整部15について説明する。調整部15は、記憶部16によって記憶された各情報に基づき、エッチング装置12におけるエッチング条件を調整することによってエッチング後の酸化膜の膜厚を目標膜厚へ近付ける処理部である。

【0135】

具体的には、調整部15は、予測膜厚算出部15a、補正量算出部15b、膜厚測定指示部15cを備える。予測膜厚算出部15aは、記憶部16によって記憶された成膜条件情報16aおよびエッチング条件情報16bを用いてエッチング工程後における酸化膜の予測膜厚を算出して補正量算出部15bへ出力する処理部である。

【0136】

かかる予測膜厚算出部15aは、記憶部16から読出した成膜条件情報16aに含まれる各情報の数値と、記憶部16から読出したエッチング条件情報16bに対応するエッチング条件の下でエッチングを行った場合における酸化膜の膜厚の低減量とを次式

予測膜厚=j×(処理温度)+k×(処理時間)+l×(ガス流量)+m×(処理圧力)+n×(装置内位置)+o・・・式(5)

へ代入することによって予測膜厚を算出する。

【0137】

ここで、式(5)における処理温度は、成膜工程における処理温度であり、処理時間は、成膜工程における処理時間である。また、式(5)におけるjは、処理温度の変化に伴う酸化膜の膜厚の変化率を示す定数であり、kは、処理時間の変化に伴う酸化膜の膜厚の変化率を示す定数であり、lは、ガス流量の変化に伴う酸化膜の膜厚の変化率を示す定数である。

【0138】

また、式(5)におけるmは、処理圧力の変化に伴う酸化膜の膜厚の変化率を示す定数であり、nは、装置内位置の違いに伴う酸化膜の膜厚の変化率を示す定数である。また、式(5)におけるoは、記憶部16によって記憶されたエッチング条件情報16bに対応したエッチング条件の下でウェットエッチングを行った場合に低減される酸化膜の膜厚の低減量を示す負の数値である。

【0139】

これらの定数j、k、l、m、n、oは、成膜条件およびエッチング条件を変更して酸化膜の成膜およびエッチングを行う試験を繰り返し、試験の結果に基づいて予め算出された定数である。

【0140】

補正量算出部15bは、予測膜厚算出部15aから入力されるエッチング工程後における酸化膜の予測膜厚と、記憶部16に記憶されたエッチング条件情報16bおよび目標膜厚情報16cとに基づいてエッチング時間の補正量を算出する処理部である。

【0141】

かかる補正量算出部15bは、予測膜厚算出部15aから入力される予測膜厚、記憶部16から読出したエッチング条件情報16bを用いて算出したエッチングレート、目標膜厚情報16cに対応する目標膜厚を次式

エッチング時間の補正量={(予測膜厚)−(目標膜厚)}/(エッチングレート)・・・式(6)

へ代入することによってエッチング時間の補正量を算出する。

【0142】

ここで、エッチングレートは、記憶部16によって記憶されたエッチング条件情報16bにおける処理温度および処理回数でエッチングを行った場合に、所定の単位時間内でエッチングされる酸化膜のエッチング量である。

【0143】

かかるエッチングレートは、補正量算出部15bが次式

エッチングレート=p×(処理温度)+q×(処理回数)+r・・・式(7)

によって算出する。

【0144】

なお、式(7)における処理温度は、エッチング工程における処理温度である。また、式(7)における定数p、q、rは、エッチング条件を変更して酸化膜のエッチングを行う試験を繰り返し、試験の結果に基づいて予め算出された定数である。

【0145】

そして、補正量算出部15bは、算出したエッチング時間の補正量に基づいてエッチング装置12によるエッチング時間を補正し、補正後のエッチング時間をエッチング装置12へ出力してエッチング時間の設定変更を行う。

【0146】

すなわち、補正量算出部15bは、算出した補正量が正の場合、記憶部16に記憶されたエッチング条件情報16bにおける処理時間へ補正量を加算した時間を補正後のエッチング時間としてエッチング装置12へ出力する。

【0147】

一方、補正量算出部15bは、算出した補正量が負の場合、記憶部16に記憶されたエッチング条件情報16bにおける処理時間から補正量を減算した時間を補正後のエッチング時間としてエッチング装置12へ出力する。

【0148】

そして、エッチング装置12は、補正量算出部15bから補正後のエッチング時間が入力された場合、補正後のエッチング時間を調整装置14の記憶部16へ出力してエッチング条件情報16bを更新し、酸化膜を補正後のエッチング時間エッチングする。また、補正量算出部15bは、補正後のエッチング時間を膜厚測定指示部15cへ出力する。

【0149】

膜厚測定指示部15cは、補正量算出部15bから入力される補正後のエッチング時間が所定のエッチング条件を逸脱したか否かを判定し、逸脱したと判定した場合、酸化膜の膜厚測定指示を膜厚測定装置13へ出力する処理部である。

【0150】

例えば、膜厚測定指示部15cは、補正後のエッチング時間が予め定められた所定時間範囲の上限値を超えた場合、および下限値を下回った場合に、補正後のエッチング時間が所定のエッチング条件を逸脱したと判定する。

【0151】

そして、膜厚測定装置13は、膜厚測定指示部15cから膜厚測定指示が入力された場合に、成膜装置11によって成膜された酸化膜の膜厚と、エッチング装置12によってエッチングされた酸化膜の膜厚とを測定し、測定結果を膜厚測定指示部15cへ出力する。

【0152】

膜厚測定指示部15cは、測定結果が入力された場合に、次回のエッチング時間が所定のエッチング条件を逸脱しなくなるように、式(5)および式(6)における各定数の補正値を予測膜厚算出部15aと補正量算出部15bとへ出力する。そして、予測膜厚算出部15aおよび補正量算出部15bは、式(5)および式(6)における各定数を膜厚測定指示部15cから入力される補正値へ更新する。

【0153】

次に、図16を参照し、調整装置14が実行する処理について説明する。図16は、第2の実施形態にかかる調整装置14が実行する処理を示すフローチャートである。図16に示すように、調整装置14の予測膜厚算出部15aは、記憶部16へ成膜条件情報16aおよびエッチング条件情報16bが記憶された場合に、記憶部16から成膜条件情報16aおよびエッチング条件情報16bを読出す(ステップS601)。

【0154】

続いて、予測膜厚算出部15aは、記憶部16から読出した成膜条件情報16aおよびエッチング条件情報16bを用い、式(5)の演算処理を実行してエッチング工程後における酸化膜の予測膜厚を算出する(ステップS602)。そして、予測膜厚算出部15aは、算出した予測膜厚を補正量算出部15bへ出力する。

【0155】

補正量算出部15bは、予測膜厚算出部15aから予測膜厚が入力された場合、記憶部16からエッチング条件情報16bおよび目標膜厚情報16cを読出す(ステップS603)。続いて、補正量算出部15bは、記憶部16から読出したエッチング条件情報16bおよび目標膜厚情報16cを用い、式(6)および式(7)の演算処理を実行してエッチング条件の補正量(ここでは、エッチング時間の補正量)を算出する(ステップS604)。

【0156】

そして、補正量算出部15bは、算出した補正量を用いてエッチング装置12のエッチング条件(ここでは、エッチング時間)を補正し、補正後のエッチング条件をエッチング装置12および膜厚測定指示部15cへ出力する(ステップS605)。

【0157】

続いて、膜厚測定指示部15cは、補正量算出部15bから入力された補正後のエッチング条件が所定のエッチング条件を逸脱したか否かを判定する(ステップS606)。ここで、膜厚測定指示部15cは、補正後のエッチング条件が所定のエッチング条件を逸脱しないと判定した場合(ステップS606,No)、処理を終了する。

【0158】

一方、膜厚測定指示部15cは、補正後のエッチング条件が所定のエッチング条件を逸脱したと判定した場合(ステップS606,Yes)、膜厚測定装置13へ膜厚計測指示を出力する(ステップS607)。

【0159】

続いて、膜厚測定指示部15cは、膜厚測定装置13から入力される成膜工程後における酸化膜の膜厚およびエッチング工程後における酸化膜の膜厚の測定結果に基づき、予測膜厚およびエッチング条件の補正量の算出処理内容を補正する(ステップS608)。

【0160】

例えば、膜厚測定指示部15cは、次回のエッチング時間が所定のエッチング条件を逸脱しなくなるように、式(5)および式(6)における各定数の補正値を予測膜厚算出部15aと補正量算出部15bとへ出力して処理を終了する。

【0161】

上述したように、第2の実施形態にかかる半導体装置の製造方法は、基板上に半導体の薄膜を成膜する成膜工程と、成膜した薄膜をエッチングして薄膜の膜厚を低減するエッチング工程とを含む。さらに、第2の実施形態にかかる半導体装置の製造方法は、成膜工程における薄膜の成膜条件およびエッチング工程におけるエッチング条件に基づいてエッチング工程におけるエッチング条件を調整する調整工程とを含む。

【0162】

これにより、第2の実施形態にかかる半導体装置の製造方法によれば、エッチング条件を調整したことによる効果が今回エッチングされる薄膜から反映されるので、製品の歩留まりを向上させることができる。

【0163】

また、第2の実施形態にかかる半導体装置の製造方法における調整工程では、成膜装置11に設定された成膜条件およびエッチング装置12に設定されたエッチング条件に基づき、エッチング工程後における薄膜の膜厚を予測する。さらに、調整工程では、予測したエッチング工程後の膜厚と予め定められた目標とする薄膜の膜厚との差分が低減するようにエッチング条件を調整する。

【0164】

すなわち、第2の実施形態にかかる半導体装置の製造方法では、成膜工程後における薄膜の膜厚測定、およびエッチング工程後における薄膜の膜厚測定を行うことなく、エッチング条件の調整を行うことができる。

【0165】

これにより、第2の実施形態にかかる半導体装置の製造方法によれば、膜厚測定装置13による膜厚測定回数の低減、および膜厚測定時間の短縮が可能となるので、製品の製造時間を短縮することができる。

【0166】

また、第2の実施形態にかかる半導体装置の製造方法では、調整工程によって調整されたエッチング条件が所定のエッチング条件を逸脱した場合に、薄膜の膜厚を測定する測定工程をさらに含む。

【0167】

これにより、第2の実施形態にかかる半導体装置の製造方法では、調整後のエッチング条件が所定のエッチング条件を逸脱した場合に、実際の膜厚を測定した測定結果を用いて予測膜厚やエッチング条件の補正量の算出処理内容を補正することができる。したがって、第2の実施形態にかかる半導体装置の製造方法では、エッチング後の薄膜の膜厚を目標とする所望の膜厚へさらに精度よく近付けることができる。

【0168】

なお、第2の実施形態では、成膜装置11が酸化シリコン膜を成膜する装置である場合について説明したが、成膜装置11は、窒化シリコン膜やエピタキシャル成長によるシリコン膜等、任意の半導体の薄膜を成膜する装置であってもよい。

【0169】

また、第2の実施形態では、エッチング条件のうちエッチング時間を調整する場合について説明したが、調整するエッチング条件は、所定時間あたりのエッチング処理回数やエッチング工程における処理温度を調整してもよい。

【0170】

また、第2の実施形態では、エッチング装置12がウェットエッチングを行う装置である場合について説明したが、エッチング装置12は、ドライエッチングを行う装置であってもよい。また、エッチング装置12に代えて薄膜を研磨することによって膜厚を所望の膜厚まで低減する研磨装置を用いてもよい。かかる場合には、成膜条件と研磨装置へ設定される研磨条件に基づいて研磨装置へ設定する研磨条件を調整する。なお、研磨装置がCMP(Chemical Mechanical Polishing)を行う装置の場合、研磨条件は、研磨時間、研磨剤の粗さ等となる。

【0171】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0172】

1、10 製造システム、2 製造装置、21、11 成膜装置、22 加工装置、23 イオン注入装置、24 アニール装置、3、14 調整装置、4 制御部、41 成膜補正部、42 形状補正部、43、15 調整部、5、16 記憶部、50 成膜装置情報、51 成膜結果情報、52 加工装置情報、53 加工結果情報、54 膜厚関数情報、55a、55b 寸法関数情報、56 炉内位置係数情報、57 ドーズ量関数情報、58 アニール温度関数情報、59 シート抵抗情報、12 エッチング装置、13 膜厚測定装置、15a 予測膜厚算出部、15b 補正量算出部、15c 膜厚測定指示部、16a 成膜条件情報、16b エッチング条件情報、16c 目標膜厚情報

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法、製造システムおよび調整装置に関する。

【背景技術】

【0002】

従来、基板上に半導体の薄膜を成膜する工程と成膜された薄膜を加工する工程とを繰り返して半導体装置を製造する半導体装置の製造方法が知られている。かかる半導体装置の製造方法では、各工程が終了する毎に薄膜の形状や特性を測定し、測定結果に基づいて各工程における処理条件をフィードバック制御することにより、次回薄膜の成膜や加工を行う際の成膜精度や加工精度を向上させていた。

【0003】

しかしながら、各工程における処理条件をフィードバック制御した場合、フィードバック制御による効果は、次回以降に成膜や加工が行われる薄膜に対して反映されるものであるため、今回成膜や加工が行われた製品の歩留まりが低下するという問題がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】再表2004/036639号公報

【特許文献2】特開2000−100973号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、製品の歩留まりを向上させることができる半導体装置の製造方法、製造システムおよび調整装置を提供することである。

【課題を解決するための手段】

【0006】

実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、成膜工程と、加工工程と、イオン注入工程と、アニール工程と、調整工程とを含む。成膜工程では、基板上に半導体の薄膜を成膜する。加工工程では、薄膜を所定の形状に加工する。イオン注入工程では、所定の形状に加工された薄膜に対してイオン注入処理を行う。アニール工程では、イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成する。調整工程では、成膜工程における薄膜の成膜条件および成膜結果と加工工程における薄膜の加工結果とのうち、少なくともいずれか1つに基づき、イオン注入工程におけるイオン注入処理の処理条件およびアニール工程におけるアニール処理の処理条件の双方または一方を調整する。

【図面の簡単な説明】

【0007】

【図1】第1の実施形態にかかる製造システムによる製造方法を示す説明図。

【図2】第1の実施形態にかかる製造システムの構成を示す説明図。

【図3】第1の実施形態にかかる成膜装置を示す模式図。

【図4】第1の実施形態にかかる加工装置による寸法の計測位置を示す図。

【図5A】第1の実施形態にかかる膜厚関数情報の一例を示す説明図。

【図5B】第1の実施形態にかかる寸法関数情報の一例を示す説明図。

【図5C】第1の実施形態にかかる寸法関数情報の一例を示す説明図。

【図6】第1の実施形態にかかる炉内係数情報の一例を示す図。

【図7A】第1の実施形態にかかるドーズ量関数情報の一例を示す説明図。

【図7B】第1の実施形態にかかるアニール温度関数情報の一例を示す説明図。

【図8A】第1の実施形態にかかるイオン注入処理の処理条件を調整する手順を示す説明図。

【図8B】第1の実施形態にかかるアニール処理の処理条件を調整する手順を示す説明図。

【図9】第1の実施形態にかかる製造装置処理および調整装置処理の一例を示す図。

【図10】変形例1にかかる製造装置処理および調整装置処理の一例を示す図。

【図11】変形例2にかかる製造装置処理および調整装置処理の一例を示す図。

【図12】変形例3にかかる製造装置処理および調整装置処理の一例を示す図。

【図13】第2の実施形態にかかる製造システムの構成を示す説明図。

【図14】第2の実施形態にかかる成膜条件情報の一例を示す説明図。

【図15】第2の実施形態にかかるエッチング条件情報の一例を示す説明図。

【図16】第2の実施形態にかかる調整装置が実行する処理を示すフローチャート。

【発明を実施するための形態】

【0008】

以下に、添付図面を参照して、第1の実施形態および第2の実施形態にかかる半導体装置の製造方法、半導体装置の製造システムおよび調整装置を詳細に説明する。なお、以下に示す実施形態によって本発明が限定されるものではない。また、以下では、半導体装置の製造方法を単に「製造方法」と記載し、半導体装置の製造システムを単に「製造システム」と記載する。

【0009】

(第1の実施形態)

まず、第1の実施形態にかかる製造システムによる製造方法について、図1を用いて説明する。図1は、第1の実施形態にかかる製造システム1による製造方法を示す説明図である。なお、図1では、製造システム1の構成を簡略化して図示している。また、かかる製造システム1の詳細については、図2を用いて後述する。

【0010】

また、以下では、ポリシリコン等の半導体の薄膜抵抗素子(以下、「抵抗素子」と記載する)を生成する場合について説明する。また、製造システム1は、抵抗素子以外にコンデンサ等の受動素子やトランジスタ等の能動素子も生成することができる。

【0011】

また、以下では、説明を簡単にする観点から、第1の実施形態にかかる製造システム1に含まれる成膜装置、加工装置、イオン注入装置およびアニール装置を総称する場合、製造装置と呼ぶこととする。

【0012】

図1に示すように、製造システム1は、半導体装置を製造する製造装置2と製造装置2に含まれる複数の装置の動作を調整する調整装置3とを含む。そして、製造システム1では、ポリシリコンの抵抗素子を生成する場合、まず、シリコンウエハ等の基板上にポリシリコンの薄膜を成膜する成膜工程を成膜装置が行う(ステップS1)。

【0013】

続いて、製造装置2では、成膜された薄膜を所定の形状に加工する加工工程を加工装置が行う(ステップS2)。加工装置は、かかる加工工程によって薄膜を抵抗素子の形状に加工する。続いて、製造装置2では、イオン注入装置が抵抗素子の形状に加工された薄膜に対して不純物イオンのイオン注入処理を施すイオン注入工程を行う(ステップS3)。

【0014】

続いて、製造装置2では、不純物イオンが注入された薄膜に対してアニール処理を施すアニール工程をアニール装置が行う(ステップS4)。アニール装置は、かかるアニール工程により薄膜内の不純物イオンを活性化して抵抗素子を生成する。なお、かかる抵抗素子には、以後の工程によって抵抗素子の電極が設けられる。

【0015】

ところで、かかる製造装置2では、最終生成物である抵抗素子のシート抵抗を如何に所望の抵抗値へ近付けるかが重要である。ここで、製造装置2によって生成される抵抗素子のシート抵抗は、抵抗素子の膜厚、寸法、不純物イオン濃度、および不純物イオンの活性化率に依存する。

【0016】

そこで、製造システム1では、成膜工程や加工工程という上流工程で薄膜の膜厚や寸法に誤差が生じた場合、上流工程で生じた誤差により変化する最終的なシート抵抗をイオン注入工程やアニール工程という下流工程で調整装置3が補正する(ステップS5)。

【0017】

具体的には、調整装置3は、成膜装置によって薄膜が成膜されると、成膜装置から薄膜の成膜時に適用された成膜条件と、薄膜の成膜結果とを取得する(ステップS6)。たとえば、調整装置3は、成膜条件として成膜時における成膜炉内の温度を取得し、成膜結果として成膜された薄膜の膜厚を取得する。

【0018】

また、調整装置3は、加工装置によって薄膜の形状が加工されると、加工装置から薄膜の加工結果を取得する(ステップS7)。たとえば、調整装置3は、加工結果として、抵抗素子の形状に加工された薄膜の寸法を取得する。

【0019】

ここでの寸法とは、抵抗素子の形状に加工された薄膜の基板上における長さおよび幅である。なお、ここでの長さは、薄膜を抵抗素子として機能させた場合に電流が流れる方向の基板上における長さであり、幅は、電流が流れる方向と直交する方向の基板上における長さである。

【0020】

続いて、調整装置3は、取得した成膜条件、成膜結果および加工結果のうち、少なくともいずれか1つに基づき、イオン注入処理の処理条件を調整することで抵抗素子のシート抵抗を補正する(ステップS8)。

【0021】

たとえば、調整装置3は、取得した成膜条件、成膜結果および加工結果のうち、少なくともいずれか1つに基づき、抵抗素子のシート抵抗を予測する。そして、調整装置3は、予測したシート抵抗と予め定められた所望の抵抗値との差分を低減するように、イオン注入処理の処理時間や不純物イオンのドーズ量を調整する。なお、かかる調整の詳細については、図8Aを用いて後述する。

【0022】

続いて、調整装置3は、取得した成膜条件、成膜結果および加工結果のうち、少なくともいずれか1つに基づき、アニール処理の処理条件を調整することで抵抗素子のシート抵抗を補正する(ステップS9)。

【0023】

たとえば、調整装置3は、取得した成膜条件、成膜結果および加工結果のうち、少なくともいずれか1つに基づいて予測したシート抵抗と予め定められた所望の抵抗値との差分を低減するように、アニール処理の処理時間や処理温度を調整する。なお、かかる調整の詳細については、図8Bを用いて後述する。

【0024】

このように、調整装置3は、上流工程で生じた誤差により変化するシート抵抗の目的値からのズレを下流工程で補正する。これにより、製造システム1では、最終生成物である抵抗素子のシート抵抗を予め定められた抵抗値へ近付けることができるため、シート抵抗のバラツキを抑制することができる。したがって、製造システム1によれば、製品の歩留まりを向上させることができる。

【0025】

なお、ここでは、調整装置3がイオン注入処理の処理条件およびアニール処理の処理条件の双方を調整する場合について説明したが、調整装置3は、イオン注入処理の処理条件およびアニール処理の処理条件のいずれか一方を調整することもできる。なお、かかる点については、図11および図12を用いて後述する。

【0026】

次に、図2を用いて第1の実施形態にかかる製造システム1の構成について説明する。図2は、第1の実施形態にかかる製造システム1の構成を示す説明図である。図2に示すように、製造システム1は、製造装置2と、調整装置3とを含む。製造装置2は、成膜装置21、加工装置22、イオン注入装置23およびアニール装置24を含む。

【0027】

成膜装置21は、LP−CVD(Low Pressure―Chemical Vapor Deposition)を行うことでシリコンウエハ等の基板上に半導体の薄膜を成膜する装置である。ここで、図3を用いて成膜装置21について説明する。図3は、第1の実施形態にかかる成膜装置21を示す模式図である。

【0028】

図3に示すように、成膜装置21は、複数の基板26を収納して処理する成膜炉25を備えている。また、成膜炉25は、処理対象となる複数の基板26を縦方向に多段に収納する。

【0029】

また、成膜装置21には、成膜する薄膜の膜厚に応じて予め定められた複数種類の成膜条件が設定される。たとえば、成膜装置21には、成膜時における成膜炉25内の温度、成膜時間、成膜炉25に導入する原料ガスの流量、成膜炉25内の圧力等の成膜条件が設定される。

【0030】

そして、成膜装置21は、設定された複数種類の成膜条件に基づき、成膜炉25内でLP−CVDを行うことにより基板26上に半導体(ここでは、ポリシリコン)の薄膜を成膜する。

【0031】

かかる縦型の成膜装置21では、成膜炉25内における基板26の位置(以下、「炉内位置」と記載する)によって成膜される薄膜の膜質に差が生じる。たとえば、図3に示すような縦型の成膜炉25の場合、上下方向へ多段に収納した複数の基板26にポリシリコンの薄膜を成膜すると、ポリシリコンのグレインサイズは、成膜する基板26の炉内位置が成膜炉25内の上段へ行くほど大きくなる傾向にある。

【0032】

そして、グレインサイズが異なるポリシリコン膜に対して同一の処理条件でイオン注入処理およびアニール処理を行った場合、グレインサイズが大きなポリシリコン膜は、グレインサイズが小さなポリシリコン膜に比べシート抵抗が小さくなる。すなわち、ポリシリコンのグレインサイズにバラツキが生じた場合、抵抗素子のシート抵抗にもバラツキが生じる。

【0033】

そこで、製造システム1では、成膜炉25内の空間を縦方向について複数(ここでは、6つ)の炉内位置A、B、C、D、EおよびFに分け、最上段の炉内位置Aおよび最下段の炉内位置Fを除く炉内位置B、C、DおよびEで成膜された基板26を次の工程へ送る。

【0034】

また、成膜装置21は、各種成膜条件が設定された場合に、設定された成膜条件を調整装置3へ出力し、薄膜が完了すると、成膜した薄膜の膜厚を計測し、計測結果を成膜結果として調整装置3へ出力する。このとき成膜装置21は、膜厚を計測した基板26の炉内位置B、C、DおよびEと成膜結果とを対応付けて調整装置3へ出力する。

【0035】

図2の説明に戻り製造装置2の説明を続ける。加工装置22は、成膜装置21によって成膜された薄膜を所定形状に加工する装置である。ここでは、加工装置22は、設定された加工条件に基づいてポリシリコンの薄膜を抵抗素子の形状に加工する。

【0036】

具体的には、加工装置22は、ポリシリコンの薄膜上にフォトレジストを塗布し、フォトリソグラフィーによってフォトレジストに所定のパターニングを施すことでレジストマスクを形成する。続いて、加工装置22は、レジストマスクを用いてRIE(Reactive Ion Etching)を行うことによってポリシリコンの薄膜を抵抗素子の形状に加工する。

【0037】

そして、加工装置22は、各種加工条件が設定された場合に、設定された加工条件を調整装置3へ出力し、薄膜の形状を加工した場合に、加工した薄膜の寸法を計測し、計測結果を加工結果として調整装置3へ出力する。

【0038】

ここで、図4を用いて加工装置22による寸法の計測位置について説明する。図4は、第1の実施形態にかかる加工装置22による寸法の計測位置を示す図である。図4に示すように、加工装置22は、各基板26を中心からの距離に応じて複数(ここでは、3つ)の計測領域G、HおよびIに分割する。

【0039】

そして、加工装置22は、各計測領域G、HおよびI内で抵抗素子の形状に加工された薄膜の寸法、すなわち、基板26の面上における薄膜の長さおよび幅を計測し、計測結果を計測領域G、HおよびI毎に調整装置3へ出力する。

【0040】

図2の説明に戻り製造装置2の説明を続ける。イオン注入装置23は、所定形状に加工されたポリシリコンの薄膜に対して不純物イオンをイオン注入する装置である。かかるイオン注入装置23は、イオン注入処理を行った場合に、イオン注入処理の処理条件を調整装置3へ出力する。たとえば、イオン注入装置23は、イオン注入した不純物イオンのドーズ量や不純物イオンの注入時間等を処理条件として調整装置3へ出力する。

【0041】

アニール装置24は、不純物イオンがイオン注入されたポリシリコンの薄膜に対して熱処理を行うことにより、薄膜内の不純物イオンを活性化させて抵抗素子を生成する装置である。

【0042】

調整装置3は、製造装置2に含まれる成膜装置21、加工装置22、イオン注入装置23およびアニール装置24の各装置で実行される製造工程の内容を調整する装置であり、制御部4と記憶部5とを備えている。

【0043】

記憶部5は、成膜装置情報50、成膜結果情報51、加工装置情報52、加工結果情報53、膜厚関数情報54、寸法関数情報55aおよび55b、炉内位置係数情報56、ドーズ量関数情報57、アニール温度関数情報58、シート抵抗情報59を記憶する記憶デバイスである。

【0044】

成膜装置情報50は、成膜装置21に設定された各種成膜条件の設定履歴であり、具体的には、成膜時における成膜炉25内の温度、成膜時間、成膜炉25に導入する原料ガスの流量、成膜炉25内の圧力等の成膜条件に関する設定履歴である。成膜結果情報51は、成膜装置21によって成膜された薄膜の膜厚を測定した測定値である。

【0045】

加工装置情報52は、加工装置22に設定された各種加工条件の設定履歴であり、具体的には、フォトグラフィーの際に用いた露光マスクの種類や露光時における露光マスクの位置情報等に関する履歴である。加工結果情報53は、加工装置22によって加工された薄膜の寸法を測定した測定値である。

【0046】

膜厚関数情報54は、成膜工程で成膜された薄膜の膜厚と、成膜工程で成膜された薄膜に対してイオン注入処理およびアニール処理を施した場合の薄膜のシート抵抗との関係を示す関数である。

【0047】

また、寸法関数情報55aおよび55bは、加工工程で形状を加工された薄膜の寸法と、加工工程で形状を加工された薄膜に対してイオン注入およびアニール処理を施した場合の薄膜のシート抵抗との関係を示す関数である。

【0048】

ここで、図5A、図5B、図5Cを用いて膜厚関数情報54および寸法関数情報55a、55bの一例について説明する。図5Aは、第1の実施形態にかかる膜厚関数情報54の一例を示す説明図であり、図5Bおよび図5Cは、第1の実施形態にかかる寸法関数情報55a、55bの一例を示す説明図である。

【0049】

図5Aに示すように、膜厚関数情報54は、次式

シート抵抗=−a×(抵抗素子の膜厚)+b・・・式(1)

によって表わされるシート抵抗と薄膜の膜厚との関係を示す関数である。なお、式(1)におけるaおよびbは、薄膜の寸法、イオン注入処理およびアニール処理の処理条件から算出される正の定数である。同図に示すように、シート抵抗の抵抗値は、薄膜の膜厚が大きくなるほど低下する。

【0050】

なお、図5Aでは、膜厚関数情報54として1つの関数を例示しているが、記憶部5は、薄膜の寸法、イオン注入処理およびアニール処理の処理条件の組み合わせ毎に、複数の関数を記憶する。かかる膜厚関数情報54は、制御部4が成膜装置情報50や成膜結果情報51に基づいてシート抵抗を予測する際に用いられる。

【0051】

また、図5Bに示すように、寸法関数情報55aは、次式

シート抵抗=c×(抵抗素子の寸法)+d・・・式(2)

によって表わされるシート抵抗とシート抵抗の寸法(長さ)との関係を示す関数である。なお、式(2)におけるcおよびdは、薄膜の膜厚、イオン注入処理およびアニール処理の処理条件から算出される正の定数である。同図に示すように、シート抵抗の抵抗値は、薄膜の長さが大きくなるほど上昇する。

【0052】

また、図5Cに示すように、寸法関数情報55bは、シート抵抗とシート抵抗の寸法(幅)との関係を示す関数である。かかるシート抵抗の幅に関する寸法関数情報55bは、上記式(2)と同様に一次関数によって表わされる。

【0053】

ただし、シート抵抗の幅に関する寸法関数情報55bの場合、上記式(2)における定数cは、負の定数となる。すなわち、シート抵抗の抵抗値は、薄膜の幅が大きくなるほど低下する。

【0054】

なお、図5Bおよび図5Cでは、寸法関数情報55aおよび55bとして、それぞれ1つの関数を例示しているが、記憶部5は、薄膜の膜厚、イオン注入処理およびアニール処理の処理条件の組み合わせ毎に、複数の関数を記憶する。かかる寸法関数情報55aおよび55bは、制御部4が加工結果情報53に基づいてシート抵抗を予測する際に用いられる。

【0055】

図2の説明に戻り調整装置3の説明を続ける。炉内位置係数情報56は、成膜装置21から加工装置22へ送られる基板26の成膜炉25内における炉内位置B、C、DおよびEと所定の炉内位置係数とを対応付けた情報である。

【0056】

かかる炉内位置係数情報56は、制御部4が膜厚関数情報54に基づいて予測したシート抵抗を補正する際に用いられる。前述したように、成膜工程で成膜された薄膜は、成膜炉25内の炉内位置B、C、DおよびEによって膜質が異なり、かかる膜質の違いによって最終的なシート抵抗も薄膜が成膜された炉内位置B、C、DおよびEによって変わってくる。

【0057】

このため、膜厚関数情報54に基づいて予測されたシート抵抗は、炉内位置B、C、DおよびE毎に補正する必要がある。そこで、調整装置3では、成膜装置21から加工装置22へ送られる基板26の成膜炉25内における炉内位置B、C、DおよびEと所定の炉内位置係数とを対応付けた炉内位置係数情報56を記憶部5によって記憶している。

【0058】

ここで、図6を用いて炉内位置係数情報56の一例について説明する。図6は、第1の実施形態にかかる炉内位置係数情報56の一例を示す図である。なお、図6に示す炉内位置B、C、DおよびEは、図3に示す炉内位置B、C、DおよびEに対応する。

【0059】

前述したように、成膜装置21の成膜炉25では、成膜する基板26の炉内位置B、C、DおよびEが成膜炉25内の上段へ行くほどポリシリコンのグレインサイズが大きくなり、シート抵抗が小さくなる傾向がある。

【0060】

そこで、図6に示すように、炉内位置係数情報56では、各炉内位置B、C、DおよびEに対して、各炉内位置B、C、DおよびEが成膜炉25内で上段に行くほど小さくなる炉内位置係数α、β、γおよびδをそれぞれ対応付けている。

【0061】

そして、制御部4は、膜厚関数情報54に基づいて予測した薄膜のシート抵抗へ、薄膜が成膜された炉内位置B、C、DおよびEに対応した炉内位置係数α、β、γおよびδを乗算することで、炉内位置B、C、DおよびE毎に予測したシート抵抗を補正する。

【0062】

図2の説明に戻り、ドーズ量関数情報57は、薄膜へイオン注入する不純物イオンのドーズ量と抵抗素子のシート抵抗との関係を示す関数である。また、アニール温度関数情報58は、アニール処理における処理温度と薄膜のシート抵抗との関係を示す関数である。

【0063】

ここで、図7Aおよび図7Bを用いてドーズ量関数情報57およびアニール温度関数情報58の一例について説明する。図7Aは、第1の実施形態にかかるドーズ量関数情報57の一例を示す説明図であり、図7Bは、第1の実施形態にかかるアニール温度関数情報58の一例を示す説明図である。

【0064】

図7Aに示すように、ドーズ量関数情報57は、次式

ドーズ量=e×(シート抵抗)2−f×(シート抵抗)+g・・・式(3)

によって表わされる不純物イオンのドーズ量と抵抗素子のシート抵抗との関係を示す関数である。なお、式(3)におけるe、fおよびgは、薄膜の成膜条件、薄膜の膜厚および寸法から算出される正の定数である。同図に示すように、シート抵抗の抵抗値は、ドーズ量を増大するほど低下する。また、シート抵抗の低下率は、ドーズ量が増大するほど低くなる。

【0065】

なお、図7Aでは、ドーズ量関数情報57として1つの関数を例示しているが、記憶部5は、薄膜の成膜条件、薄膜の膜厚および寸法の組み合わせ毎に、複数の関数を記憶する。かかるドーズ量関数情報57は、制御部4がイオン注入処理の処理条件を調整する際に用いられる。

【0066】

また、図7Bに示すように、アニール温度関数情報58は、次式

シート抵抗=−h×(アニール温度)+i・・・式(4)

によって表わされるシート抵抗とアニール処理の処理温度との関係を示す関数である。なお、式(4)におけるhおよびiは、薄膜の成膜条件、薄膜の膜厚および寸法から算出される正の定数である。同図に示すように、シート抵抗の抵抗値は、アニール処理の処理温度が高くなるほど低下する。

【0067】

なお、図7Bでは、アニール温度関数情報58として1つの関数を例示しているが、記憶部5は、薄膜の成膜条件、薄膜の膜厚および寸法の組み合わせ毎に、複数の関数を記憶する。かかるアニール温度関数情報58は、制御部4がアニール処理の処理条件を調整する際に用いられる。

【0068】

なお、調整装置3は、アニール温度関数情報58に加え、アニール処理の処理時間とシート抵抗との関係を示す情報を記憶部5へ記憶させ、かかる情報に基づいて制御部4がアニール処理の処理条件を調整するように構成することもできる。また、シート抵抗情報59は、予め定められた抵抗素子のシート抵抗に関する目標値である。

【0069】

制御部4は、調整装置3全体の動作を統括制御する処理部であり、たとえば、CPU(Central Processing Unit)とROM(Read Only Memory)とRAM(Random Access Memory)とを有する情報処理装置である。

【0070】

かかる制御部4は、CPUがROMから各種プログラムを読出し、RAMを作業領域として使用して実行することにより機能する成膜補正部41、形状補正部42および調整部43を備えている。

【0071】

成膜補正部41は、成膜装置21に設定されている成膜条件を調整することによって成膜工程で成膜される薄膜の膜厚が予め設定された所望の膜厚となるように補正する処理部である。

【0072】

具体的には、成膜補正部41は、成膜装置21によって薄膜が成膜される毎に、成膜時における成膜炉25内の温度、成膜時間、成膜炉25に導入する原料ガスの流量、成膜炉25内の圧力等の成膜条件を成膜装置21から取得する。そして、成膜補正部41は、取得した各成膜条件を成膜装置情報50として記憶部5へ順次記憶させる。

【0073】

また、成膜補正部41は、成膜装置21によって薄膜が成膜される毎に、成膜された薄膜の膜厚の測定結果を成膜結果として取得し、取得した成膜結果を成膜結果情報51として記憶部5へ記憶させる。

【0074】

そして、成膜補正部41は、成膜装置情報50と成膜結果情報51とに基づいて、次回成膜される薄膜の膜厚と今回成膜された膜厚とが一致するように調整した成膜条件を成膜装置21へ出力して設定する。これにより、成膜工程で成膜される薄膜の膜厚が予め設定された所望の膜厚へ近付くように補正される。

【0075】

形状補正部42は、加工装置22に設定されている加工条件を調整することによって加工工程で加工される薄膜の寸法が予め設定された所望の寸法となるように補正する処理部である。

【0076】

具体的には、形状補正部42は、加工装置22によって薄膜の形状が加工される毎に、フォトグラフィーの際に用いた露光マスクの種類や露光時における露光マスクの位置情報等の加工条件を加工装置22から取得する。そして、形状補正部42は、取得した各加工条件を加工装置情報52として記憶部5へ順次記憶させる。

【0077】

また、形状補正部42は、加工装置22によって薄膜の形状が加工される毎に、加工された薄膜の寸法に関する測定結果を加工結果として取得し、取得した加工結果を加工結果情報53として記憶部5へ記憶させる。

【0078】

そして、形状補正部42は、加工装置情報52と加工結果情報53とに基づいて、次回加工される薄膜の寸法と今回加工された薄膜の寸法とが一致するように調整した加工条件を加工装置22へ出力して設定する。これにより、加工工程で成膜される薄膜の寸法が予め設定された所望の寸法へ近付くように補正される。

【0079】

調整部43は、記憶部5によって記憶されている各種情報に基づいて、イオン注入装置23によるイオン注入処理の処理条件およびアニール装置24によるアニール処理の処理条件を調整することによって抵抗素子のシート抵抗のバラツキを抑制する処理部である。

【0080】

かかる調整部43は、イオン注入処理およびアニール処理の処理条件を調整する場合、成膜工程によって成膜された薄膜を用いて生成される抵抗素子のシート抵抗および加工工程によって加工された薄膜を用いて生成される抵抗素子のシート抵抗を予測する。

【0081】

具体的には、調整部43は、成膜装置21によって薄膜が成膜されると、成膜装置情報50および成膜結果情報51を記憶部5から読み出し、読み出した成膜装置情報50および成膜結果情報51に基づき、成膜工程によって成膜された薄膜の膜厚を判別する。

【0082】

たとえば、調整部43は、記憶部5によって記憶されている成膜装置情報50から算出した膜厚と、成膜結果情報51として記憶部5に記憶されている膜厚とを平均化した膜厚を成膜工程によって成膜された薄膜の膜厚として判別する。

【0083】

なお、調整部43は、成膜装置情報50から算出した膜厚を成膜工程によって成膜された薄膜の膜厚として判別してもよく、成膜結果情報51として記憶部5に記憶されている膜厚を成膜工程によって成膜された薄膜の膜厚として判別してもよい。

【0084】

続いて、調整部43は、記憶部5から膜厚関数情報54を読み出し、読み出した膜厚関数情報54の式(1)へ判別した膜厚を代入することによってシート抵抗を算出する。このとき調整部43は、成膜炉25の炉内位置B、C、DおよびE毎にシート抵抗を算出する。

【0085】

続いて、調整部43は、炉内位置B、C、DおよびE毎に算出した各シート抵抗に対して対応する炉内位置係数情報56の炉内係数α、β、γおよびδをそれぞれ乗算することにより、成膜工程によって成膜された薄膜を用いて生成される抵抗素子のシート抵抗の予測値を算出する。これにより、調整部43は、炉内位置B、C、DおよびEを考慮したシート抵抗の予測値を精度よく算出することができる。

【0086】

また、調整部43は、加工装置22によって薄膜の形状が加工されると、加工工程によって加工された薄膜を用いて生成される抵抗素子のシート抵抗を予測する。具体的には、調整部43は、記憶部5から加工結果情報53および寸法関数情報55aおよび55bを読み出す。

【0087】

続いて、調整部43は、加工結果情報53における薄膜の寸法を寸法関数情報55aおよび55bの式(2)へ代入することでシート抵抗の予測値を算出する。このとき、調整部43は、寸法の計測領域G、HおよびI(図4参照)毎にシート抵抗の予測値を算出する。

【0088】

そして、調整部43は、算出したシート抵抗の予測値を用いてイオン注入処理およびアニール処理の処理条件を調整する。ここで、図8Aおよび図8Bを用いてイオン注入処理およびアニール処理の処理条件を調整する手順について説明する。

【0089】

図8Aは、第1の実施形態にかかるイオン注入処理の処理条件を調整する手順を示す説明図であり、図8Bは、第1の実施形態にかかるアニール処理の処理条件を調整する手順を示す説明図である。

【0090】

図8Aに示すように、調整部43は、イオン注入処理の処理条件を調整する場合、算出したシート抵抗の予測値Jとシート抵抗情報59として記憶されている目的値Kとを比較する。そして、調整部43は、シート抵抗の予測値Jがシート抵抗の目的値Kよりも大きい場合、イオン注入装置23に設定されているドーズ量の既定値Lをドーズ量関数情報57に基づいて調整値Mまで上昇させる。一方、調整部43は、シート抵抗の予測値Jがシート抵抗の目的値Kよりも小さい場合には、イオン注入装置23に設定されているドーズ量を低下させる。

【0091】

このように、調整部43は、上流工程で成膜した薄膜の膜厚や寸法と予め定められた所望の膜厚や寸法との間に誤差が生じた場合、下流工程でイオン注入処理の処理条件を調整することにより最終的な抵抗素子のシート抵抗を目的値Kへ近付けることができる。したがって、製造システム1によれば、抵抗素子のシート抵抗にバラツキが生じることを抑制することができる。

【0092】

また、図8Bに示すように、調整部43は、アニール処理の処理条件を調整する場合、算出したシート抵抗の予測値Oとシート抵抗情報59として記憶されている目的値Pとを比較する。そして、調整部43は、シート抵抗の予測値Oがシート抵抗の目的値Pよりも小さい場合、アニール装置24に設定されている処理温度の既定値Qをアニール温度関数情報58に基づいて調整値Rまで低下させる。一方、調整部43は、シート抵抗の予測値Oがシート抵抗の目的値Pよりも大きい場合、アニール装置24に設定されている処理温度を上昇させる。

【0093】

また、調整部43は、アニール処理の処理条件を調整する場合、加工結果情報53に基づき、薄膜の寸法が計測された計測領域G、H、I毎、すなわち、薄膜の基板26上における位置毎に処理条件を調整する。

【0094】

このように、調整部43は、上流工程で成膜した薄膜の膜厚や寸法と予め定められた所望の膜厚や寸法との間に誤差が生じた場合、下流工程でアニール処理の処理条件を薄膜の基板26上における位置毎に調整する。これにより、製造システム1では、最終的な抵抗素子のシート抵抗を目的値Pへ近付けることができるので、抵抗素子のシート抵抗にバラツキが生じることを抑制することができる。

【0095】

次に、図9を用いて第1の実施形態にかかる製造システム1で製造装置2が実行する製造装置処理および調整装置3が実行する調整装置処理について説明する。図9は、第1の実施形態にかかる製造装置処理および調整装置処理の一例を示す図である。

【0096】

図9に示すように、製造システム1では、成膜装置21がLP−CVDを行うことにより基板26上にポリシリコンの薄膜を形成する(ステップS101)。一方、調整装置3は、成膜装置21によって薄膜が成膜されると、調整装置3は、成膜装置21から成膜装置情報50および成膜結果情報51を取得する(ステップS201)。

【0097】

続いて、調整装置3は、取得した成膜装置情報50および成膜結果情報51に基づき、成膜装置21によって成膜された薄膜によって生成される抵抗素子のシート抵抗を予測する(ステップS202)。続いて、調整装置3は、予測したシート抵抗と予め定められた所望の抵抗値との差分を低減可能なイオン注入処理の処理条件を算出し(ステップS203)、算出した処理条件をイオン注入装置23へ設定する(ステップS204)。

【0098】

また、加工装置22は、成膜装置21によって薄膜が成膜された基板26が搬入されると、搬入された基板26に成膜されている薄膜をフォトリソグラフィーおよびRIEによって抵抗素子の形状に加工する(ステップS102)。

【0099】

続いて、イオン注入装置23は、加工装置22によって形状が加工された基板26が搬入されると、搬入された基板26に対し、調整装置3によって設定された処理条件で不純物イオンのイオン注入処理を行う(ステップS103)。

【0100】

一方、調整装置3は、加工装置22によって薄膜が抵抗素子の形状に加工されると、加工装置22から加工結果情報53を取得する(ステップS205)。続いて、調整装置3は、イオン注入装置23からイオン注入処理の処理結果を取得する(ステップS206)。

【0101】

続いて、調整装置3は、加工装置22から取得した加工結果情報53とイオン注入装置23から取得した処理結果とに基づいて抵抗素子の最終的なシート抵抗を予測する(ステップS207)。

【0102】

続いて、調整装置3は、予測したシート抵抗と予め定められた所望の抵抗値との差分を低減可能なアニール処理の処理条件を算出し(ステップS208)、算出した処理条件をアニール装置24へ設定する(ステップS209)。最後に、アニール装置24は、調整装置3によって設定された処理条件でアニール処理を行い(ステップS104)、抵抗素子を生成する。

【0103】

このように、上述した第1の実施形態では、製造システム1の調整装置3が、上流工程である成膜工程の処理条件および処理結果に基づき、下流工程であるイオン注入処理の処理条件を調整することによって上流工程で生じた誤差を下流工程で補正する。

【0104】

さらに、製造システム1では、調整装置3が上流工程である加工工程の加工結果と、調整後の処理条件で実行されたイオン注入処理の処理結果とに基づき、下流工程であるアニール処理の処理条件を調整することによって上流工程で生じた誤差を補正する。

【0105】

これにより、製造システム1では、仮に上流工程で誤差が生じた場合であっても、最終生成物となる抵抗素子のシート抵抗を予め定められた所望の抵抗値へ近付けることができるため、抵抗素子のシート抵抗にバラツキが生じることを抑制することができる。

【0106】

なお、製造装置処理および調整装置処理は、図9に示す処理に限定するものではない。以下では、図10〜図12を用いて第1の実施形態にかかる製造装置処理および調整装置処理の変形例1〜3について説明する。

【0107】

図10は、変形例1にかかる製造装置処理および調整装置処理の一例を示す図であり、図11は、変形例2にかかる製造装置処理および調整装置処理の一例を示す図であり、図12は、変形例3にかかる製造装置処理および調整装置処理の一例を示す図である。

【0108】

なお、図10〜図12では、図9に示す処理と同一の処理に対して同一のステップ番号を付している。図10に示すように、変形例1は、調整装置処理におけるステップS300およびステップS301だけが図9に示す処理と異なる。

【0109】

すなわち、変形例1にかかる調整装置3は、図9に示す処理と同様に、上流工程である成膜工程の処理条件および処理結果に基づき、下流工程であるイオン注入処理の処理条件を調整することによって上流工程で生じた誤差を下流工程で補正する。

【0110】

さらに、調整装置3は、加工装置22からの加工結果情報53の取得(ステップS205)およびイオン注入装置23からの処理結果の取得(ステップS206)を行った後、成膜装置情報50および成膜結果情報51を記憶部5から読み出す(ステップS300)。

【0111】

続いて、調整装置3は、加工結果情報53、イオン注入処理の処理結果、成膜装置情報50および成膜結果情報51に基づいて最終的なシート抵抗を予測する(ステップS301)。その後、予測したシート抵抗に基づいてアニール処理の処理条件を算出し(ステップS208)、処理条件をアニール装置24へ設定する(ステップS209)。

【0112】

このように、変形例1にかかる調整装置3は、加工結果情報53およびイオン注入処理の処理結果に加え、再度、成膜装置情報50および成膜結果情報51を考慮してアニール処理の処理条件を調整する。これにより、変形例1にかかる製造システムによれば、最終生成物となる抵抗素子のシート抵抗を予め定められた所望の抵抗値へ、より正確に近付けることができる。

【0113】

また、図11に示すように、変形例2は、イオン注入装置23が予め定められた処理条件でイオン注入処理を実行する(ステップS400)点および調整装置3が図9に示すステップS205〜209の処理を実行する点が図9に示す処理と異なる。

【0114】

また、図12に示すように、変形例3は、アニール装置24が予め設定された処理条件でアニール処理を実行する(ステップS500)点および調整装置3が図9に示すステップS201〜204の処理を実行する点が図9に示す処理と異なる。

【0115】

かかる変形例2および変形例3によっても、上流工程で誤差が生じた場合に、最終生成物となる抵抗素子のシート抵抗を予め定められた所望の抵抗値へ近付けることができるため、抵抗素子のシート抵抗にバラツキが生じることを抑制することができる。

【0116】

しかも、変形例2および変形例3によれば、調整装置3は、イオン注入処理またはアニール処理のいずれか一方の処理条件を算出して対応する装置へ設定するだけで済むため、処理負荷を低減しつつ、シート抵抗のバラツキを抑制することができる。

【0117】

なお、上述した第1の実施形態および変形例1〜3では、調整装置3がイオン注入処理のドーズ量を調整する場合について説明したが、調整装置3は、イオン注入処理のイオン注入時間を調整してもよい。また、調整装置3は、ドーズ量およびイオン注入時間の双方を調整してもよい。かかる構成とする場合、調整装置3は、処理時間が最短となるようにドーズ量およびイオン注入時間を調整する。

【0118】

また、上述した第1の実施形態および変形例1〜3では、調整装置3がアニール処理の処理温度を調整する場合について説明したが、調整装置3は、アニール処理の処理時間を調整してもよい。また、調整装置3は、アニール処理の処理温度および処理時間の双方を調整してもよい。かかる構成とする場合、調整装置3は、処理時間が最短となるように処理温度および処理時間を調整する。

【0119】

(第2の実施形態)

次に、第2の実施形態にかかる製造システムによる製造方法について説明する。図13は、第2の実施形態にかかる製造システム10の構成を示す説明図である。なお、図13には、製造システム10の特徴を説明するために必要な構成要素を図示しており、一般的な構成要素については図示を省略している。

【0120】

図13に示すように、製造システム10は、成膜装置11、エッチング装置12、膜厚測定装置13、調整装置14を備え、半導体の薄膜を成膜した後、薄膜をエッチングして膜厚を所望の膜厚(以下、「目標膜厚」と記載する)まで低減するシステムである。

【0121】

具体的には、成膜装置11は、シリコンウエハ等の基板や基板上にシリコン層等の半導体層が形成されたウエハを酸化させる酸化炉を備える。そして、成膜装置11は、酸化炉の内部で複数枚のウエハを熱処理することによってウエハ上に酸化させた半導体の薄膜(以下、「酸化膜」と記載する)を成膜する。

【0122】

かかる成膜装置11は、予め設定された所定の成膜条件の下で酸化膜の成膜工程を行う。なお、成膜条件は、成膜する酸化膜の用途等によって任意に設定変更される。そして、成膜装置11は、成膜条件の設定時、または酸化膜の成膜前、もしくは酸化膜の成膜後に、成膜条件を示す成膜条件情報16aを調整装置14へ出力する。かかる成膜条件情報16aの一例については、図14を参照して後述する。

【0123】

エッチング装置12は、成膜装置11によって成膜された酸化膜をウェットエッチングすることによって酸化膜の膜厚を目標膜厚まで低減する装置である。かかるエッチング装置12は、予め設定された所定のエッチング条件または調整装置14によって調整されたエッチング条件の下で酸化膜のエッチング工程を行う。

【0124】

また、エッチング装置12は、エッチングを行う前に、これから行うエッチング工程のエッチング条件を示すエッチング条件情報16bを調整装置14へ出力する。なお、エッチング条件情報16bの一例については、図15を参照して後述する。

【0125】

膜厚測定装置13は、成膜装置11によって成膜された酸化膜の膜厚およびエッチング装置12によってエッチングされた酸化膜の膜厚を測定する装置である。かかる膜厚測定装置13は、調整装置14から膜厚測定指示が入力された場合に、酸化膜の膜厚を測定し、測定結果を調整装置14へ出力する。

【0126】

調整装置14は、成膜装置11における酸化膜の成膜条件およびエッチング装置12におけるエッチング条件に基づいてエッチング装置12におけるエッチング条件を調整する装置である。具体的には、調整装置14は、調整部15と記憶部16とを備える。

【0127】

記憶部16は、成膜装置11から入力される成膜条件情報16aと、エッチング装置12から入力されるエッチング条件情報16bと、目標膜厚情報16cとを記憶する。なお、目標膜厚情報16cは、酸化膜の目標膜厚を示す情報であり、外部から任意に設定変更が可能な情報である。

【0128】

ここで、図14および図15を参照し、成膜条件情報16aおよびエッチング条件情報16bについて説明する。図14は、第2の実施形態にかかる成膜条件情報16aの一例を示す説明図であり、図15は、第2の実施形態にかかるエッチング条件情報16bの一例を示す説明図である。

【0129】

図14に示すように、成膜条件情報16aは、装置内位置、処理温度、処理圧力、ガス流量、処理時間のそれぞれを示す情報を含む。装置内位置は、酸化炉におけるウエハの載置位置を示す情報である。本実施形態では、酸化炉内部の各領域に対して1、2、3・・・というように装置内位置を示す番号を付している。

【0130】

また、処理温度は、酸化膜を成膜する際の酸化炉内部の温度であり、処理圧力は、酸化膜を成膜する際の酸化炉内部の気圧である。また、ガス流量は、酸化膜を成膜する際に酸化炉内部へ単位時間に導入される処理ガスの流量(容積)であり、処理時間は、酸化膜の成膜にかける処理時間である。

【0131】

ここで、図14におけるs、t、u、vは、成膜条件情報16aにおける処理温度、処理圧力、ガス流量、処理時間のそれぞれを示す数値である。なお、成膜条件情報16aとして、図14に示す情報に加え、例えば、処理ガスの種類や酸化炉内部における処理ガスの濃度を示す情報等を含めてもよい。

【0132】

また、図15に示すように、エッチング条件情報16bは、処理時間、処理回数、処理温度のそれぞれを示す情報を含む。処理時間は、酸化膜のウェットエッチングにかける処理時間であり、処理回数は、同じウエハに対して所定の単位時間内に繰り返しエッチングを行う処理回数であり、処理温度は、ウェットエッチングに使用するエッチャントの温度である。

【0133】

ここで、図15におけるw、x、yは、エッチング条件情報16bにおける処理時間、処理回数、処理温度のそれぞれを示す数値である。なお、エッチング条件情報16bとして、図15に示す情報に加え、例えば、エッチャントの種類や濃度を示す情報等を含めてもよい。

【0134】

次に、図13へ戻り調整部15について説明する。調整部15は、記憶部16によって記憶された各情報に基づき、エッチング装置12におけるエッチング条件を調整することによってエッチング後の酸化膜の膜厚を目標膜厚へ近付ける処理部である。

【0135】

具体的には、調整部15は、予測膜厚算出部15a、補正量算出部15b、膜厚測定指示部15cを備える。予測膜厚算出部15aは、記憶部16によって記憶された成膜条件情報16aおよびエッチング条件情報16bを用いてエッチング工程後における酸化膜の予測膜厚を算出して補正量算出部15bへ出力する処理部である。

【0136】

かかる予測膜厚算出部15aは、記憶部16から読出した成膜条件情報16aに含まれる各情報の数値と、記憶部16から読出したエッチング条件情報16bに対応するエッチング条件の下でエッチングを行った場合における酸化膜の膜厚の低減量とを次式

予測膜厚=j×(処理温度)+k×(処理時間)+l×(ガス流量)+m×(処理圧力)+n×(装置内位置)+o・・・式(5)

へ代入することによって予測膜厚を算出する。

【0137】

ここで、式(5)における処理温度は、成膜工程における処理温度であり、処理時間は、成膜工程における処理時間である。また、式(5)におけるjは、処理温度の変化に伴う酸化膜の膜厚の変化率を示す定数であり、kは、処理時間の変化に伴う酸化膜の膜厚の変化率を示す定数であり、lは、ガス流量の変化に伴う酸化膜の膜厚の変化率を示す定数である。

【0138】

また、式(5)におけるmは、処理圧力の変化に伴う酸化膜の膜厚の変化率を示す定数であり、nは、装置内位置の違いに伴う酸化膜の膜厚の変化率を示す定数である。また、式(5)におけるoは、記憶部16によって記憶されたエッチング条件情報16bに対応したエッチング条件の下でウェットエッチングを行った場合に低減される酸化膜の膜厚の低減量を示す負の数値である。

【0139】

これらの定数j、k、l、m、n、oは、成膜条件およびエッチング条件を変更して酸化膜の成膜およびエッチングを行う試験を繰り返し、試験の結果に基づいて予め算出された定数である。

【0140】

補正量算出部15bは、予測膜厚算出部15aから入力されるエッチング工程後における酸化膜の予測膜厚と、記憶部16に記憶されたエッチング条件情報16bおよび目標膜厚情報16cとに基づいてエッチング時間の補正量を算出する処理部である。

【0141】

かかる補正量算出部15bは、予測膜厚算出部15aから入力される予測膜厚、記憶部16から読出したエッチング条件情報16bを用いて算出したエッチングレート、目標膜厚情報16cに対応する目標膜厚を次式

エッチング時間の補正量={(予測膜厚)−(目標膜厚)}/(エッチングレート)・・・式(6)

へ代入することによってエッチング時間の補正量を算出する。

【0142】

ここで、エッチングレートは、記憶部16によって記憶されたエッチング条件情報16bにおける処理温度および処理回数でエッチングを行った場合に、所定の単位時間内でエッチングされる酸化膜のエッチング量である。

【0143】

かかるエッチングレートは、補正量算出部15bが次式

エッチングレート=p×(処理温度)+q×(処理回数)+r・・・式(7)

によって算出する。

【0144】

なお、式(7)における処理温度は、エッチング工程における処理温度である。また、式(7)における定数p、q、rは、エッチング条件を変更して酸化膜のエッチングを行う試験を繰り返し、試験の結果に基づいて予め算出された定数である。

【0145】

そして、補正量算出部15bは、算出したエッチング時間の補正量に基づいてエッチング装置12によるエッチング時間を補正し、補正後のエッチング時間をエッチング装置12へ出力してエッチング時間の設定変更を行う。

【0146】

すなわち、補正量算出部15bは、算出した補正量が正の場合、記憶部16に記憶されたエッチング条件情報16bにおける処理時間へ補正量を加算した時間を補正後のエッチング時間としてエッチング装置12へ出力する。

【0147】

一方、補正量算出部15bは、算出した補正量が負の場合、記憶部16に記憶されたエッチング条件情報16bにおける処理時間から補正量を減算した時間を補正後のエッチング時間としてエッチング装置12へ出力する。

【0148】

そして、エッチング装置12は、補正量算出部15bから補正後のエッチング時間が入力された場合、補正後のエッチング時間を調整装置14の記憶部16へ出力してエッチング条件情報16bを更新し、酸化膜を補正後のエッチング時間エッチングする。また、補正量算出部15bは、補正後のエッチング時間を膜厚測定指示部15cへ出力する。

【0149】

膜厚測定指示部15cは、補正量算出部15bから入力される補正後のエッチング時間が所定のエッチング条件を逸脱したか否かを判定し、逸脱したと判定した場合、酸化膜の膜厚測定指示を膜厚測定装置13へ出力する処理部である。

【0150】

例えば、膜厚測定指示部15cは、補正後のエッチング時間が予め定められた所定時間範囲の上限値を超えた場合、および下限値を下回った場合に、補正後のエッチング時間が所定のエッチング条件を逸脱したと判定する。

【0151】

そして、膜厚測定装置13は、膜厚測定指示部15cから膜厚測定指示が入力された場合に、成膜装置11によって成膜された酸化膜の膜厚と、エッチング装置12によってエッチングされた酸化膜の膜厚とを測定し、測定結果を膜厚測定指示部15cへ出力する。

【0152】

膜厚測定指示部15cは、測定結果が入力された場合に、次回のエッチング時間が所定のエッチング条件を逸脱しなくなるように、式(5)および式(6)における各定数の補正値を予測膜厚算出部15aと補正量算出部15bとへ出力する。そして、予測膜厚算出部15aおよび補正量算出部15bは、式(5)および式(6)における各定数を膜厚測定指示部15cから入力される補正値へ更新する。

【0153】

次に、図16を参照し、調整装置14が実行する処理について説明する。図16は、第2の実施形態にかかる調整装置14が実行する処理を示すフローチャートである。図16に示すように、調整装置14の予測膜厚算出部15aは、記憶部16へ成膜条件情報16aおよびエッチング条件情報16bが記憶された場合に、記憶部16から成膜条件情報16aおよびエッチング条件情報16bを読出す(ステップS601)。

【0154】

続いて、予測膜厚算出部15aは、記憶部16から読出した成膜条件情報16aおよびエッチング条件情報16bを用い、式(5)の演算処理を実行してエッチング工程後における酸化膜の予測膜厚を算出する(ステップS602)。そして、予測膜厚算出部15aは、算出した予測膜厚を補正量算出部15bへ出力する。

【0155】

補正量算出部15bは、予測膜厚算出部15aから予測膜厚が入力された場合、記憶部16からエッチング条件情報16bおよび目標膜厚情報16cを読出す(ステップS603)。続いて、補正量算出部15bは、記憶部16から読出したエッチング条件情報16bおよび目標膜厚情報16cを用い、式(6)および式(7)の演算処理を実行してエッチング条件の補正量(ここでは、エッチング時間の補正量)を算出する(ステップS604)。

【0156】

そして、補正量算出部15bは、算出した補正量を用いてエッチング装置12のエッチング条件(ここでは、エッチング時間)を補正し、補正後のエッチング条件をエッチング装置12および膜厚測定指示部15cへ出力する(ステップS605)。

【0157】

続いて、膜厚測定指示部15cは、補正量算出部15bから入力された補正後のエッチング条件が所定のエッチング条件を逸脱したか否かを判定する(ステップS606)。ここで、膜厚測定指示部15cは、補正後のエッチング条件が所定のエッチング条件を逸脱しないと判定した場合(ステップS606,No)、処理を終了する。

【0158】

一方、膜厚測定指示部15cは、補正後のエッチング条件が所定のエッチング条件を逸脱したと判定した場合(ステップS606,Yes)、膜厚測定装置13へ膜厚計測指示を出力する(ステップS607)。

【0159】

続いて、膜厚測定指示部15cは、膜厚測定装置13から入力される成膜工程後における酸化膜の膜厚およびエッチング工程後における酸化膜の膜厚の測定結果に基づき、予測膜厚およびエッチング条件の補正量の算出処理内容を補正する(ステップS608)。

【0160】

例えば、膜厚測定指示部15cは、次回のエッチング時間が所定のエッチング条件を逸脱しなくなるように、式(5)および式(6)における各定数の補正値を予測膜厚算出部15aと補正量算出部15bとへ出力して処理を終了する。

【0161】

上述したように、第2の実施形態にかかる半導体装置の製造方法は、基板上に半導体の薄膜を成膜する成膜工程と、成膜した薄膜をエッチングして薄膜の膜厚を低減するエッチング工程とを含む。さらに、第2の実施形態にかかる半導体装置の製造方法は、成膜工程における薄膜の成膜条件およびエッチング工程におけるエッチング条件に基づいてエッチング工程におけるエッチング条件を調整する調整工程とを含む。

【0162】

これにより、第2の実施形態にかかる半導体装置の製造方法によれば、エッチング条件を調整したことによる効果が今回エッチングされる薄膜から反映されるので、製品の歩留まりを向上させることができる。

【0163】

また、第2の実施形態にかかる半導体装置の製造方法における調整工程では、成膜装置11に設定された成膜条件およびエッチング装置12に設定されたエッチング条件に基づき、エッチング工程後における薄膜の膜厚を予測する。さらに、調整工程では、予測したエッチング工程後の膜厚と予め定められた目標とする薄膜の膜厚との差分が低減するようにエッチング条件を調整する。

【0164】

すなわち、第2の実施形態にかかる半導体装置の製造方法では、成膜工程後における薄膜の膜厚測定、およびエッチング工程後における薄膜の膜厚測定を行うことなく、エッチング条件の調整を行うことができる。

【0165】

これにより、第2の実施形態にかかる半導体装置の製造方法によれば、膜厚測定装置13による膜厚測定回数の低減、および膜厚測定時間の短縮が可能となるので、製品の製造時間を短縮することができる。

【0166】

また、第2の実施形態にかかる半導体装置の製造方法では、調整工程によって調整されたエッチング条件が所定のエッチング条件を逸脱した場合に、薄膜の膜厚を測定する測定工程をさらに含む。

【0167】

これにより、第2の実施形態にかかる半導体装置の製造方法では、調整後のエッチング条件が所定のエッチング条件を逸脱した場合に、実際の膜厚を測定した測定結果を用いて予測膜厚やエッチング条件の補正量の算出処理内容を補正することができる。したがって、第2の実施形態にかかる半導体装置の製造方法では、エッチング後の薄膜の膜厚を目標とする所望の膜厚へさらに精度よく近付けることができる。

【0168】

なお、第2の実施形態では、成膜装置11が酸化シリコン膜を成膜する装置である場合について説明したが、成膜装置11は、窒化シリコン膜やエピタキシャル成長によるシリコン膜等、任意の半導体の薄膜を成膜する装置であってもよい。

【0169】

また、第2の実施形態では、エッチング条件のうちエッチング時間を調整する場合について説明したが、調整するエッチング条件は、所定時間あたりのエッチング処理回数やエッチング工程における処理温度を調整してもよい。

【0170】

また、第2の実施形態では、エッチング装置12がウェットエッチングを行う装置である場合について説明したが、エッチング装置12は、ドライエッチングを行う装置であってもよい。また、エッチング装置12に代えて薄膜を研磨することによって膜厚を所望の膜厚まで低減する研磨装置を用いてもよい。かかる場合には、成膜条件と研磨装置へ設定される研磨条件に基づいて研磨装置へ設定する研磨条件を調整する。なお、研磨装置がCMP(Chemical Mechanical Polishing)を行う装置の場合、研磨条件は、研磨時間、研磨剤の粗さ等となる。

【0171】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0172】

1、10 製造システム、2 製造装置、21、11 成膜装置、22 加工装置、23 イオン注入装置、24 アニール装置、3、14 調整装置、4 制御部、41 成膜補正部、42 形状補正部、43、15 調整部、5、16 記憶部、50 成膜装置情報、51 成膜結果情報、52 加工装置情報、53 加工結果情報、54 膜厚関数情報、55a、55b 寸法関数情報、56 炉内位置係数情報、57 ドーズ量関数情報、58 アニール温度関数情報、59 シート抵抗情報、12 エッチング装置、13 膜厚測定装置、15a 予測膜厚算出部、15b 補正量算出部、15c 膜厚測定指示部、16a 成膜条件情報、16b エッチング条件情報、16c 目標膜厚情報

【特許請求の範囲】

【請求項1】

基板上に半導体の薄膜を成膜する成膜工程と、

前記薄膜を所定の形状に加工する加工工程と、

前記所定の形状に加工された薄膜に対してイオン注入処理を行うイオン注入工程と、

前記イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成するアニール工程と、

前記成膜工程における前記薄膜の成膜条件および成膜結果と前記加工工程における前記薄膜の加工結果とのうち、少なくともいずれか1つに基づき、前記イオン注入工程における前記イオン注入処理の処理条件および前記アニール工程におけるアニール処理の処理条件の双方または一方を調整する調整工程と

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記調整工程は、

前記成膜条件、前記成膜結果および前記加工結果のうち、少なくともいずれか1つに基づき、前記抵抗素子のシート抵抗を予測し、当該シート抵抗と予め定められたシート抵抗との差分が低減するように前記イオン注入処理の処理条件および前記アニール処理の処理条件の双方または一方を調整する

ことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記調整工程は、

前記アニール処理の処理条件となる処理温度を調整する場合、前記所定の形状に加工された薄膜の前記基板における位置毎に当該処理温度を調整する

ことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記調整工程は、

前記アニール処理の処理条件となる処理温度を調整する場合、前記イオン注入工程によってイオン注入されたイオンのドーズ量に基づいて当該処理温度を調整する

ことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項5】

基板上に半導体の薄膜を成膜する成膜工程と、

前記薄膜をエッチングして当該薄膜の膜厚を低減するエッチング工程と、

前記成膜工程における成膜条件および前記エッチング工程におけるエッチング条件に基づいて前記エッチング条件を調整する調整工程と

を含むことを特徴とする半導体装置の製造方法。

【請求項6】

前記調整工程は、

前記成膜条件および前記エッチング条件に基づき、前記エッチング工程後における前記薄膜の膜厚を予測し、当該膜厚と予め定められた前記薄膜の膜厚との差分が低減するように前記エッチング条件を調整する

ことを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記調整工程によって調整された前記エッチング条件が所定のエッチング条件を逸脱した場合に、前記薄膜の膜厚を測定する測定工程

をさらに含むことを特徴とする請求項5または請求項6に記載の半導体装置の製造方法。

【請求項8】

基板上に半導体の薄膜を成膜する成膜装置と、

前記薄膜を所定の形状に加工する加工装置と、

前記所定の形状に加工された薄膜に対してイオン注入処理を行うイオン注入装置と、

前記イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成するアニール装置と、

前記成膜装置における前記薄膜の成膜条件および成膜結果と前記加工装置における前記薄膜の加工結果とのうち、少なくともいずれか1つに基づき、前記イオン注入装置におけるイオン注入処理の処理条件および前記アニール装置におけるアニール処理の処理条件の双方または一方を調整する調整装置と

を備えることを特徴とする半導体装置の製造システム。

【請求項9】

基板上に半導体の薄膜を成膜する成膜装置と、

前記薄膜をエッチングして当該薄膜の膜厚を低減するエッチング装置と、

前記成膜装置における成膜条件および前記エッチング装置におけるエッチング条件に基づいて前記エッチング条件を調整する調整装置と

を備えることを特徴とする半導体装置の製造システム。

【請求項10】

基板上に半導体の薄膜を成膜する成膜装置における前記薄膜の成膜条件と前記薄膜の成膜結果と前記薄膜を所定の形状に加工する加工装置における前記薄膜の加工結果とのうち、少なくともいずれか1つの情報を記憶する記憶部と、

前記記憶部によって記憶された情報に基づき、前記所定の形状に加工された薄膜に対してイオン注入処理を行うイオン注入装置におけるイオン注入処理の処理条件、および前記イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成するアニール装置におけるアニール処理の処理条件の双方または一方を調整する調整部と

を備えることを特徴とする調整装置。

【請求項11】

基板上に半導体の薄膜を成膜する成膜装置における成膜条件と前記薄膜をエッチングして当該薄膜の膜厚を低減するエッチング装置におけるエッチング条件とを記憶する記憶部と、

前記記憶部によって記憶された前記成膜条件および前記エッチング条件に基づいて前記エッチング条件を調整する調整部と

を備えることを特徴とする調整装置。

【請求項1】

基板上に半導体の薄膜を成膜する成膜工程と、

前記薄膜を所定の形状に加工する加工工程と、

前記所定の形状に加工された薄膜に対してイオン注入処理を行うイオン注入工程と、

前記イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成するアニール工程と、

前記成膜工程における前記薄膜の成膜条件および成膜結果と前記加工工程における前記薄膜の加工結果とのうち、少なくともいずれか1つに基づき、前記イオン注入工程における前記イオン注入処理の処理条件および前記アニール工程におけるアニール処理の処理条件の双方または一方を調整する調整工程と

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記調整工程は、

前記成膜条件、前記成膜結果および前記加工結果のうち、少なくともいずれか1つに基づき、前記抵抗素子のシート抵抗を予測し、当該シート抵抗と予め定められたシート抵抗との差分が低減するように前記イオン注入処理の処理条件および前記アニール処理の処理条件の双方または一方を調整する

ことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記調整工程は、

前記アニール処理の処理条件となる処理温度を調整する場合、前記所定の形状に加工された薄膜の前記基板における位置毎に当該処理温度を調整する

ことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記調整工程は、

前記アニール処理の処理条件となる処理温度を調整する場合、前記イオン注入工程によってイオン注入されたイオンのドーズ量に基づいて当該処理温度を調整する

ことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項5】

基板上に半導体の薄膜を成膜する成膜工程と、

前記薄膜をエッチングして当該薄膜の膜厚を低減するエッチング工程と、

前記成膜工程における成膜条件および前記エッチング工程におけるエッチング条件に基づいて前記エッチング条件を調整する調整工程と

を含むことを特徴とする半導体装置の製造方法。

【請求項6】

前記調整工程は、

前記成膜条件および前記エッチング条件に基づき、前記エッチング工程後における前記薄膜の膜厚を予測し、当該膜厚と予め定められた前記薄膜の膜厚との差分が低減するように前記エッチング条件を調整する

ことを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記調整工程によって調整された前記エッチング条件が所定のエッチング条件を逸脱した場合に、前記薄膜の膜厚を測定する測定工程

をさらに含むことを特徴とする請求項5または請求項6に記載の半導体装置の製造方法。

【請求項8】

基板上に半導体の薄膜を成膜する成膜装置と、

前記薄膜を所定の形状に加工する加工装置と、

前記所定の形状に加工された薄膜に対してイオン注入処理を行うイオン注入装置と、

前記イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成するアニール装置と、

前記成膜装置における前記薄膜の成膜条件および成膜結果と前記加工装置における前記薄膜の加工結果とのうち、少なくともいずれか1つに基づき、前記イオン注入装置におけるイオン注入処理の処理条件および前記アニール装置におけるアニール処理の処理条件の双方または一方を調整する調整装置と

を備えることを特徴とする半導体装置の製造システム。

【請求項9】

基板上に半導体の薄膜を成膜する成膜装置と、

前記薄膜をエッチングして当該薄膜の膜厚を低減するエッチング装置と、

前記成膜装置における成膜条件および前記エッチング装置におけるエッチング条件に基づいて前記エッチング条件を調整する調整装置と

を備えることを特徴とする半導体装置の製造システム。

【請求項10】

基板上に半導体の薄膜を成膜する成膜装置における前記薄膜の成膜条件と前記薄膜の成膜結果と前記薄膜を所定の形状に加工する加工装置における前記薄膜の加工結果とのうち、少なくともいずれか1つの情報を記憶する記憶部と、

前記記憶部によって記憶された情報に基づき、前記所定の形状に加工された薄膜に対してイオン注入処理を行うイオン注入装置におけるイオン注入処理の処理条件、および前記イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成するアニール装置におけるアニール処理の処理条件の双方または一方を調整する調整部と

を備えることを特徴とする調整装置。

【請求項11】

基板上に半導体の薄膜を成膜する成膜装置における成膜条件と前記薄膜をエッチングして当該薄膜の膜厚を低減するエッチング装置におけるエッチング条件とを記憶する記憶部と、

前記記憶部によって記憶された前記成膜条件および前記エッチング条件に基づいて前記エッチング条件を調整する調整部と

を備えることを特徴とする調整装置。

【図1】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図6】

【図7A】

【図7B】

【図8A】

【図8B】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図6】

【図7A】

【図7B】

【図8A】

【図8B】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2012−212847(P2012−212847A)

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願番号】特願2011−233316(P2011−233316)

【出願日】平成23年10月24日(2011.10.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願日】平成23年10月24日(2011.10.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]