半導体装置の製造方法および半導体装置

【課題】複数の半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置およびその半導体装置を容易に製造することのできる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜6の上面上に、全面的に、3〜30nmの厚みのゲート電極用金属膜Mを形成する。次に、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分にのみ、全面的に、ゲート電極用金属膜Mとは異種材料の、10nm以下の厚みのn側キャップ層8Aを形成する。その上で、熱処理を行って、n側キャップ層8Aを、その直下のゲート電極用金属膜M内に拡散・反応させて、nFET領域Rn内にn側ゲート電極用金属膜MAを形成する。それ以降は、ポリSi層を堆積した上で、ゲート電極加工を施す。

【解決手段】ゲート絶縁膜6の上面上に、全面的に、3〜30nmの厚みのゲート電極用金属膜Mを形成する。次に、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分にのみ、全面的に、ゲート電極用金属膜Mとは異種材料の、10nm以下の厚みのn側キャップ層8Aを形成する。その上で、熱処理を行って、n側キャップ層8Aを、その直下のゲート電極用金属膜M内に拡散・反応させて、nFET領域Rn内にn側ゲート電極用金属膜MAを形成する。それ以降は、ポリSi層を堆積した上で、ゲート電極加工を施す。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、より詳細には、複数のゲート電極構造を有する半導体装置およびその製造方法に関する。

【背景技術】

【0002】

45nmノード以降のCMOSデバイスでは、ゲート電極をpoly−Siとし、ゲート絶縁膜をSiONとする構造に代わって、ゲート絶縁膜を高誘電率の絶縁膜(以下「high−k膜」という)とするゲートスタック構造の適用が始められている。その理由は、high−k膜は、SiO2膜などと比較して、物理的には膜厚が厚くても、電気的動作時においては膜厚が薄い膜として機能する、すなわち実効的な膜厚が薄いという性質を有するので、ゲートリーク電流を抑制するのに寄与し得るからである。

【0003】

このようなpoly−Si/high−k膜構造では、フェルミレベルピンニング(Fermi Level Pinning)という現象によって、特にpMOSFETに関してデバイス動作時の閾値電圧(Vth)が高くなるという問題がある。

【0004】

そこで、pMOSFETの閾値電圧(Vth)低減策として、ゲート絶縁膜の形成前にSi基板にフッ素(F)イオンを注入することが、提案されている(非特許文献1参照)。しかし、所望のデバイス特性を得るためには、Si基板にFイオンを多量に注入する必要性がある。このようにSi基板にFイオンを多量に注入すると、注入ダメージによってデバイス特性が劣化するという問題がある。

【0005】

また、nMOSFETの閾値電圧(Vth)低減策としては、ゲート絶縁膜の形成前にSi基板に窒素(N2)イオンを注入することが提案されているが、Si基板にN2イオンを多量に注入すると、やはり注入ダメージによってデバイス特性が劣化する。

【0006】

そこで、仕事関数はFETの閾値電圧(Vth)と直接的に関連性を有するので、閾値電圧(Vth)を低減するための解決策として、所望の仕事関数を有する金属材料をゲート電極として適用することが、提案されている。金属材料を最下層のゲート電極の材料として適用するときの第1の利点は、金属ゲート電極は、poly−Siゲート電極の場合のように空乏層を生じさせないので、空乏化によってデバイス動作時の実効的なゲート絶縁膜の膜厚が増加するという問題を解消して、高性能デバイスの実現が可能となる点にある。また第2の利点は、フェルミレベルピニングによる閾値電圧制御性の困難化の欠点を回避できる点にある。

【0007】

CMOSデバイスとしては、pMOSFETおよびnMOSFETのそれぞれに適した仕事関数を有する金属材料を用いることが好ましいことから、特許文献1〜3には、Si膜を最下層のゲート電極に用いてフルシリサイド化したゲート電極において、n/p−MOS間の材料および結晶相を制御する方法が、提案されている。また特許文献4には、n/p−MOSのメタルゲートにおいて、同種金属材料を用いた金属膜/金属窒化膜間での窒素拡散の制御によって金属ゲート電極の仕事関数を制御する方法が、提案されている。しかし、製造フローの複雑化および製造プロセスの困難化が問題となる。

【0008】

そこで、このような問題を回避する観点から、pMOSFETではpoly−Si/metal/high−k構造を備え、nMOSFETではpoly−Si/high−k構造を備えるハイブリッドメタルゲートCMOSデバイスの開発が進められている(非特許文献2参照)。

【0009】

また、pMOSFETおよびnMOSFETのそれぞれに適したゲート電極の作り分けは、製造プロセスが困難化することから、ゲート絶縁膜に対してキャッピングを行い、2種類のゲート絶縁膜を作りこむ手法が検討されている(たとえば非特許文献3参照)。

【0010】

【特許文献1】特開2007−242894号公報

【特許文献2】特開2007−141889号公報

【特許文献3】特開2005−294799号公報

【特許文献4】特開2007−142153号公報

【非特許文献1】M. Inoue et.al, IEDM Tech. Dig., (2005) p.425.

【非特許文献2】T. Hayashi et.al, IEDM Tech. Dig., (2006) p.247.

【非特許文献3】V. Narayanan et.al, VLSI Tech. Symp., (2006) p.224.

【発明の開示】

【発明が解決しようとする課題】

【0011】

上述の通り、CMOSデバイスを所望の閾値電圧(Vth)で動作させるためには、CMOSデバイスを構成するpMOSFETおよびnMOSFETのそれぞれに適した仕事関数を有する金属材料をゲート電極材料として用いることが好ましい。しかし、全く物性の異なる2種類以上の材料をpMOSFETとnMOSFETとで作り分けることは、フローを複雑化させるという問題を生じさせることが考えられる。この製造プロセスの困難化は、特許文献1〜4に記載されるように同種の材料を用いる場合でも避けられない。しかも、pMOSFETおよびnMOSFETのそれぞれに個別の金属材料を用いる場合には、同一チップ(ウェハ)上において、異種材料をドライエッチング法などによって同時に加工してゲート電極を形成することになるので、良好なゲート形状を得ることは困難である。これによって、所望のデバイス特性が得られないおそれがある。

【0012】

他方、上述の非特許文献2に記載のハイブリッドメタルゲート構造を採用する場合には、閾値電圧の制御範囲が狭く、またnMOSFETは、poly−Si/high−k構造となるので、実効的なゲート絶縁膜の膜厚が増加する。これによって、所望のデバイス特性が得られない可能性もあり、その点が課題とされている。しかも非特許文献2に記載のハイブリッドメタルゲート電極の形成方法では、片側のチャネル領域に所望の金属材料を堆積後に、別のチャネル領域上の金属層をウェットエッチングなどによって除去しなければならない。この金属層のエッチング工程は、ゲート絶縁膜の直上において行われるので、ゲート絶縁膜にダメージを与える可能性が高い。これによって、デバイスの信頼性が低下するおそれがある。

【0013】

また非特許文献3に記載されるゲート絶縁膜に対してキャッピングを行う手法では、ゲート絶縁膜上において、キャッピング層の形成および除去工程を繰り返すので、ゲート絶縁膜が劣化し、デバイスの信頼性が低下するおそれがある。

【0014】

本発明の目的は、CMOSデバイスのように複数の半導体素子を備える半導体装置であって、複数の半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置およびその半導体装置を容易に製造することのできる半導体装置の製造方法を提供することである。

【0015】

また本発明の他の目的は、CMOSデバイスを構成するpFETおよびnFETのように半導体装置を構成する複数の半導体素子のそれぞれに適した所望の仕事関数を有する金属材料をデュアルゲート電極材料として容易にかつ精度良く形成することが可能な半導体装置の製造方法を提供することである。

【0016】

また本発明の他の目的は、ゲート絶縁膜の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる半導体装置の製造方法および半導体装置を提供することである。

【課題を解決するための手段】

【0017】

本発明の半導体装置の製造方法は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置の製造方法であって、前記第1導電型半導体素子が形成される第1導電型素子領域と前記第2導電型半導体素子が形成される第2導電型素子領域とを互いに分離する素子分離膜を半導体基板に形成する工程と、前記半導体基板の主面上に配設されたゲート絶縁膜の表面上に、第1金属膜を形成する工程と、前記第1導電型素子領域に形成された前記第1金属膜上面上に、前記第1金属膜とは異種材料の第1キャップ層を形成する工程と、第1熱処理により前記第1キャップ層と前記第1導電型素子領域内の前記第1金属膜を反応させる工程と、前記第1導電型素子領域と前記第2導電型素子領域とで異なる組成を有するデュアルゲート電極構造を形成する工程とを備えることを特徴とする。

【0018】

また本発明の半導体装置の製造方法は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置の製造方法であって、第1導電型半導体素子が形成される第1導電型素子領域および第2導電型半導体素子が形成される第2導電型素子領域の半導体基板上に、絶縁性材料から成る絶縁層を形成する工程と、第1導電型素子領域および第2導電型素子領域の半導体基板と絶縁層との間、または第1導電型素子領域および第2導電型素子領域の絶縁層上に、第1の元素を含有する第1元素層を形成する工程と、第1導電型素子領域および第2導電型素子領域の第1元素層上に、導電性材料から成る電極用導電層を形成する工程と、第1導電型素子領域の電極用導電層上に、第1の元素とは異なる第2の元素を含有する第2元素層を形成する工程と、第1元素層および第2元素層とともに、絶縁層および電極用導電層を熱処理する工程とを備えることを特徴とする。

【0019】

また本発明の半導体装置の製造方法は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置の製造方法であって、第1導電型半導体素子が形成される第1導電型素子領域および第2導電型半導体素子が形成される第2導電型素子領域の半導体基板上に、絶縁性材料から成る絶縁層を形成する工程と、第1導電型素子領域および第2導電型素子領域の半導体基板と絶縁層との間、または第1導電型素子領域および第2導電型素子領域の絶縁層上に、第1の元素を含有する第1元素層を形成する工程と、第1導電型素子領域および第2導電型素子領域の第1元素層上に、導電性材料から成る電極用導電層を形成する工程と、第2導電型素子領域の電極用導電層上に、第1の元素とは異なる第2の元素の拡散を抑制または防止する拡散抑止層を形成する工程と、拡散抑止層上および第1導電型素子領域の電極用導電層上に、第2の元素を含有する第2元素層を形成する工程と、第1元素層および第2元素層とともに、絶縁層、電極用導電層および拡散抑止層を熱処理する工程とを含むことを特徴とする。

【0020】

また本発明の半導体装置の製造方法は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置の製造方法であって、第1導電型半導体素子が形成される第1導電型素子領域および第2導電型半導体素子が形成される第2導電型素子領域の半導体基板上に、絶縁性材料から成る絶縁層を形成する工程と、第1導電型素子領域および第2導電型素子領域の半導体基板と絶縁層との間、または第1導電型素子領域および第2導電型素子領域の絶縁層上に、第1の元素を含有する第1元素層を形成する工程と、第1導電型素子領域および第2導電型素子領域の第1元素層上に、導電性材料から成る電極用導電層を、第2導電型素子領域における厚み寸法の方が第1導電型素子領域における厚み寸法よりも大きくなるように形成する工程と、第1導電型素子領域および第2導電型素子領域の電極用導電層上に、第1の元素とは異なる第2の元素を含有する第2元素層を形成する工程と、第1元素層および第2元素層とともに、絶縁層および電極用導電層を熱処理する工程とを含むことを特徴とする。

【0021】

本発明の半導体装置は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置であって、第1導電型半導体素子は、半導体基板上に設けられ、絶縁性を有し、第1の元素および第1の元素とは異なる第2の元素を含有する第1元素添加絶縁層と、第1元素添加絶縁層上に設けられ、導電性を有し、第2の元素を含有する元素添加導電層とを備え、第2導電型半導体素子は、第1元素添加絶縁層が設けられる半導体基板上に第1元素添加絶縁層と並設して設けられ、絶縁性を有し、第1の元素を含有する第2元素添加絶縁層と、第2元素添加絶縁層上に設けられ、導電性を有する電極用導電層とを備えることを特徴とする。

【0022】

また本発明の半導体装置は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置であって、第1導電型半導体素子は、半導体基板上に設けられ、絶縁性を有し、第1の元素および第1の元素とは異なる第2の元素を含有する第1元素添加絶縁層と、第1元素添加絶縁層上に設けられ、導電性を有し、第2の元素を含有する第1元素添加導電層とを備え、第2導電型半導体素子は、第1元素添加絶縁層が設けられる半導体基板上に第1元素添加絶縁層と並設して設けられ、絶縁性を有し、第1の元素を含有する第2元素添加絶縁層と、第2元素添加絶縁層上に設けられ、導電性を有する電極用導電層と、電極用導電層上に設けられ、導電性を有し、第2の元素を含有する第2元素添加導電層と、第2元素添加導電層上に設けられ、導電性を有し、第2の元素を含有する、もう一つの第2元素添加導電層とを備えることを特徴とする。

【0023】

また本発明の半導体装置は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置であって、第1導電型半導体素子は、半導体基板上に設けられ、絶縁性を有し、第1の元素および第1の元素とは異なる第2の元素を含有する第1元素添加絶縁層と、第1元素添加絶縁層上に設けられ、導電性を有し、第2の元素を含有する第1元素添加導電層とを備え、第2導電型半導体素子は、第1元素添加絶縁層が設けられる半導体基板上に第1元素添加絶縁層と並設して設けられ、絶縁性を有し、第1の元素を含有する第2元素添加絶縁層と、第2元素添加絶縁層上に設けられ、導電性を有する電極用導電層と、電極用導電層上に設けられ、導電性を有し、第2の元素を含有する第2元素添加導電層とを備えることを特徴とする。

【0024】

また本発明の半導体装置は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置であって、第1導電型半導体素子は、半導体基板上に設けられ、絶縁性を有し、第1の元素および第1の元素とは異なる第2の元素を含有する第1元素添加絶縁層と、第1元素添加絶縁層上に設けられ、導電性を有し、第2の元素を含有する第1元素添加導電層とを備え、第2導電型半導体素子は、第1元素添加絶縁層が設けられる半導体基板上に第1元素添加絶縁層と並設して設けられ、絶縁性を有し、第1の元素を含有する第2元素添加絶縁層と、第2元素添加絶縁層上に設けられ、導電性を有する電極用導電層と、電極用導電層上に設けられ、導電性を有し、電極用導電層とは異なる材料から成る上部導電層とを備えることを特徴とする。

【発明の効果】

【0025】

本発明の半導体装置の製造方法によれば、第1導電型半導体素子のゲート電極の金属膜と第2導電型半導体素子のゲート電極の金属膜とが互いに異なる仕事関数を有するデュアルゲート電極構造を有することにより、第1導電型半導体素子、第2導電型半導体素子それぞれを所望の閾値電圧で動作可能な半導体装置を容易に形成することができる。特に、第1導電型半導体素子のゲート電極の金属膜の主材料と第2導電型半導体素子のゲート電極の金属膜の主材料とが同一であるので、ゲート電極の加工がより容易となり、微細ゲート電極の加工精度を向上させることができる。しかも、ゲート絶縁膜に対するダメージが製造工程中に生じることはなく、高い信頼性を有する半導体装置を実現することができる。このように本発明の半導体装置の製造方法によれば、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0026】

また本発明の半導体装置の製造方法によれば、第1導電型素子領域および第2導電型素子領域の半導体基板上に絶縁層が形成され、この絶縁層と半導体基板との間または絶縁層上に第1元素層および電極用導電層が順次形成される。形成された電極用導電層のうち、第1導電型素子領域の電極用導電層上に、第2元素層が形成される。形成された第1元素層および第2元素層とともに、絶縁層および電極用導電層が熱処理される。この熱処理によって、第1元素層に含有される第1の元素を、第1元素層の上方または下方の絶縁層に拡散させることができる。また第2元素層に含有される第2の元素を、第2元素層の下方の電極用導電層に拡散させ、さらに電極用導電層の下方の絶縁層に拡散させることができる。これによって、第1導電型素子領域では、第1および第2の元素を含有する絶縁層を形成し、第2導電型素子領域では、第1の元素を含有する絶縁層を形成することができるので、第1導電型半導体素子の閾値電圧および第2導電型半導体素子の閾値電圧をそれぞれ制御することができる。したがって、閾値電圧の制御範囲を広げることができる。

【0027】

また第2元素層は、電極用導電層上に形成されており、第2元素層と絶縁層との間には電極用導電層が介在するので、第1導電型素子領域に第2元素層を形成するために、たとえば第2元素層を第1導電型素子領域と第2導電型素子領域とにわたって形成した後、第2導電型素子領域の第2元素層を除去するときに、絶縁層が劣化することを防ぐことができる。これによって、劣化による絶縁層の信頼性の低下を防止することができるので、絶縁層の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。たとえば第1導電型半導体素子および第2導電型半導体素子が絶縁層をゲート絶縁膜とするMOSトランジスタである場合、ゲート絶縁膜の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0028】

また本発明の半導体装置の製造方法によれば、第1導電型素子領域および第2導電型素子領域の半導体基板上に絶縁層が形成され、この絶縁層と半導体基板との間または絶縁層上に第1元素層および電極用導電層が順次形成される。形成された電極用導電層のうち、第2導電型素子領域の電極用導電層上に拡散抑止層が形成され、この拡散抑止層上および第1導電型素子領域の電極用導電層上に、第2元素層が形成される。形成された第1元素層および第2元素層とともに、絶縁層、電極用導電層および拡散抑止層が熱処理される。

【0029】

この熱処理によって、第1元素層に含有される第1の元素を、第1元素層の上方または下方の絶縁層に拡散させることができる。また第1導電型素子領域では、第2元素層に含有される第2の元素を、第2元素層の下方の電極用導電層に拡散させ、さらに電極用導電層の下方の絶縁層に拡散させることができる。第2導電型素子領域では、第2元素層は拡散抑止層上に形成されるので、拡散抑止層によって、電極用導電層および絶縁層への第2の元素の拡散を抑制または防止することができる。これによって、第1導電型素子領域では、第1および第2の元素を含有する絶縁層を形成し、第2導電型素子領域では、第1の元素を含有する絶縁層を形成することができるので、第1導電型半導体素子の閾値電圧および第2導電型半導体素子の閾値電圧をそれぞれ制御することができる。したがって、閾値電圧の制御範囲を広げることができる。

【0030】

また第2元素層は、電極用導電層上に形成されており、第2元素層と絶縁層との間には電極用導電層が介在するので、第1導電型素子領域に第2元素層を形成するために、たとえば第2元素層を第1導電型素子領域と第2導電型素子領域とにわたって形成した後、第2導電型素子領域の第2元素層を除去するときに、絶縁層が劣化することを防ぐことができる。これによって、劣化による絶縁層の信頼性の低下を防止することができるので、絶縁層の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。たとえば第1導電型半導体素子および第2導電型半導体素子が絶縁層をゲート絶縁膜とするMOSトランジスタである場合、ゲート絶縁膜の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0031】

また本発明の半導体装置の製造方法によれば、第1導電型素子領域および第2導電型素子領域の半導体基板上に絶縁層が形成され、この絶縁層と半導体基板との間または絶縁層上に第1元素層および電極用導電層が順次形成される。電極用導電層は、第2導電型素子領域における厚み寸法の方が第1導電型素子領域における厚み寸法よりも大きく形成される。この電極用導電層上に、第1導電型素子領域および第2導電型素子領域にわたって、第2元素層が形成される。形成された第1元素層および第2元素層とともに、絶縁層および電極用導電層が熱処理される。この熱処理によって、第1元素層に含有される第1の元素を、第1元素層の上方または下方の絶縁層に拡散させることができる。また第2元素層に含有される第2の元素を、第2元素層の下方の電極用導電層に拡散させ、さらに電極用導電層の下方の絶縁層に拡散させることが可能である。

【0032】

電極用導電層は、第2導電型素子領域における厚み寸法の方が、第1導電型素子領域における厚み寸法よりも大きいので、第2導電型素子領域では、第1導電型素子領域に比べて、電極用導電層および絶縁層への第2の元素の拡散を抑制することができる。たとえば、第2の元素を、第2導電型素子領域では絶縁層まで拡散させ、第1導電型素子領域では絶縁層までは拡散しないようにすることができる。これによって、第1導電型素子領域では、第1および第2の元素を含有する絶縁層を形成し、第2導電型素子領域では、第1の元素を含有する絶縁層を形成することができるので、第1導電型半導体素子の閾値電圧および第2導電型半導体素子の閾値電圧をそれぞれ制御することができる。したがって、閾値電圧の制御範囲を広げることができる。

【0033】

また第2元素層は、電極用導電層上に形成されており、第2元素層と絶縁層との間には電極用導電層が介在するので、第2元素層を形成するときに絶縁層が劣化することを防ぐことができる。これによって、劣化による絶縁層の信頼性の低下を防止することができるので、絶縁層の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。たとえば第1導電型素子および第2導電型素子が絶縁層をゲート絶縁膜とするMOSトランジスタである場合、ゲート絶縁膜の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0034】

本発明の半導体装置によれば、第1導電型半導体素子は、第1元素添加絶縁層に第1および第2の元素を含有し、この第1元素添加絶縁層上の元素添加導電層に第2の元素を含有する。また第2導電型半導体素子は、第2元素添加絶縁層に第1の元素を含有し、この第2元素添加絶縁層上に電極用導電層を備える。これによって、それぞれに適した閾値電圧を有する第1導電型半導体素子および第2導電型半導体素子を実現することが可能である。また第1および第2元素添加絶縁層は、第1および第2元素添加絶縁層となる絶縁層上でエッチングを実施することなく形成することが可能であるので、製造過程における劣化が防止され、信頼性の低下が防止される。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を実現することが可能である。

【0035】

また本発明の半導体装置によれば、第1導電型半導体素子は、第1元素添加絶縁層に第1および第2の元素を含有し、この第1元素添加絶縁層上の第1元素添加導電層に第2の元素を含有する。また第2導電型半導体素子は、第2元素添加絶縁層に第1の元素を含有し、この第2元素添加絶縁層上に電極用導電層を備え、この電極用導電層上の第2元素添加導電層および、もう一つの第2元素添加導電層に第2の元素を含有する。これによって、それぞれに適した閾値電圧を有する第1導電型半導体素子および第2導電型半導体素子を実現することが可能である。また第1および第2元素添加絶縁層は、第1および第2元素添加絶縁層となる絶縁層上でエッチングを実施することなく形成することが可能であるので、製造過程における劣化が防止され、信頼性の低下が防止される。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を実現することが可能である。

【0036】

また本発明の半導体装置によれば、第1導電型半導体素子は、第1元素添加絶縁層に第1および第2の元素を含有し、この第1元素添加絶縁層上の第1元素添加導電層に第2の元素を含有する。また第2導電型半導体素子は、第2元素添加絶縁層に第1の元素を含有し、この第2元素添加絶縁層上に電極用導電層を備え、この電極用導電層上の第2元素添加導電層に第2の元素を含有する。これによって、それぞれに適した閾値電圧を有する第1導電型半導体素子および第2導電型半導体素子を実現することが可能である。また第1および第2元素添加絶縁層は、第1および第2元素添加絶縁層となる絶縁層上でエッチングを実施することなく形成することが可能であるので、製造過程における劣化が防止され、信頼性の低下が防止される。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を実現することが可能である。

【0037】

また本発明の半導体装置によれば、第1導電型半導体素子は、第1元素添加絶縁層に第1および第2の元素を含有し、この第1元素添加絶縁層上の第1元素添加導電層に第2の元素を含有する。また第2導電型半導体素子は、第2元素添加絶縁層に第1の元素を含有し、この第2元素添加絶縁層上に電極用導電層を備え、この電極用導電層上に電極用導電層とは異なる材料から成る上部導電層を備える。これによって、それぞれに適した閾値電圧を有する第1導電型半導体素子および第2導電型半導体素子を実現することが可能である。また第1および第2元素添加絶縁層は、第1および第2元素添加絶縁層となる絶縁層上でエッチングを実施することなく形成することが可能であるので、製造過程における劣化が防止され、信頼性の低下が防止される。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を実現することが可能である。

【発明を実施するための最良の形態】

【0038】

以下に、本発明を実施するための複数の形態について説明する。各実施の形態において、先行する実施の形態で説明している事項に対応する部分については同一の参照符を付して、重複する説明を省略する場合がある。構成の一部のみを説明している場合、構成の他の部分は、先行して説明している実施の形態と同様である。

【0039】

<第1の実施の形態>

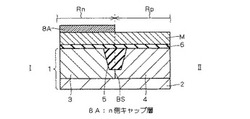

図1〜図4および図6〜図9は、本発明の第1の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。本実施の形態の半導体装置は、相補型MOS(Complementary Metal-Oxide Semiconductor;略称:CMOS)構造を有する半導体装置であり、具体的にはCMOSトランジスタである。図5は、第1の実施の形態の半導体装置における、後述するn側キャップ層8Aの形成領域を模式的に示す上面図である。なお、図5における断線I−IIに関する断面図が図4に相当している。CMOSトランジスタは、より詳細にはCMOS電界効果型トランジスタ(Field Effect Transistor;略称:FET)である。CMOSFETには、nチャネルのMOSトランジスタであるn型MOSトランジスタと、pチャネルのMOSトランジスタであるp型MOSトランジスタとが並設される。n型MOSトランジスタは、より詳細にはnMOSFET(以下「nFET」という場合がある)であり、p型MOSトランジスタは、より詳細にはpMOSFET(以下「pFET」という場合がある)である。このようにCMOSFETには、導電型が互いに異なるnMOSFETとpMOSFETとが並設される。nMOSFETは、第1導電型半導体素子に相当し、pMOSFETは、第2導電型半導体素子に相当する。

【0040】

まず、図1に示すように、従来のCMOS作製フローに則り、半導体基板であるシリコン(Si)基板1の主面よりp型半導体層2の内部に向けて延在したpウェル3およびnウェル4、並びに、素子分離膜である絶縁膜(以下「素子分離絶縁膜」という場合がある)5などを順次に形成する。ここで、素子分離絶縁膜5は、図5に例示するように、nMOSFETが形成されるnMOSFET領域(以下「nFET領域」という場合がある)Rnと、pMOSFETが形成されるpMOSFET領域(以下「pFET領域」という場合がある)Rpとを区分する絶縁膜であり、素子分離絶縁膜5の底面直下には、pウェル3およびnウェル4の境界面BSが形成されている。この境界面BSは、nFET領域RnとpFET領域Rpとの境界に相当する。このようにnFET領域RnとpFET領域Rpとは、素子分離絶縁膜5によって互いに分離される。nFET領域Rnは、第1導電型素子領域に相当し、pFET領域Rpは、第2導電型素子領域に相当する。また、Si基板1の主面よりp型半導体層2の内部に向けて延在した素子分離絶縁膜5を形成する工程は、素子分離膜を半導体基板に形成する工程に相当する。

【0041】

pウェル3、nウェル4および素子分離絶縁膜5の形成後は、Si基板1の上記主面上に、全面に亘って、high−k膜を成すゲート絶縁膜6として、たとえばハフニウムシリコンオキシナイトライド(HfSiON)を形成する。なお、ゲート絶縁膜6の材料はこれに限られるわけではなく、その他のゲート絶縁膜6の材料として、シリコン酸窒化膜(SiON)、または、ハフニウム(Hf)、ランタン(La)、アルミニウム(Al)などの酸化膜、酸窒化膜、もしくは酸窒化珪化膜を用いてもよい。

【0042】

次に、図2に示すように、ゲート絶縁膜6の上面上に、全面に亘って、第1金属膜に該当するゲート電極用金属膜Mを、スパッタ法などにより形成する。このときのゲート電極用金属膜Mの膜厚は、薄すぎると同膜Mの膜厚制御が困難になる一方、厚すぎると後述するn側キャップ層8Aの拡散が不充分となるため、経験的に、3nm〜30nmの範囲内の値に設定される。ゲート電極用金属膜Mの材料としては、チタン(Ti)、タンタル(Ta)、Hfおよびタングステン(W)のうちの少なくとも一つの元素を含んだ材料(第1材料)、あるいは、当該第1材料の窒化物(たとえばTiNなど)、炭化物(たとえばTaCなど)、珪化物(たとえばHfSiなど)、窒化珪化物(たとえばTaSiNなど)、もしくは炭窒化物(たとえばTaCNなど)のいずれかの材料を適用可能である。

【0043】

その上で、ゲート電極用金属膜Mの上面上にレジストを塗布してフォトレジストマスクを用いたフォトリソグラフィを実行することにより、図3に示すように、ゲート電極用金属膜Mの上面のうちでpFET領域Rp内に属する部分上に、全面的に、レジストパターン7を形成する。

【0044】

次に、レジストパターン7をマスクとして、スパッタ法などにより、図4および図5に例示するように、nFET領域Rnに形成されたゲート電極用金属膜Mの上面上に、本実施の形態では、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分上にのみ、全面的に、n側キャップ層(第1キャップ層に該当)8Aを形成する。その後、不要となったレジストパターン7を除去する。ここで、n側キャップ層8Aの膜厚は、経験的に、10nm以下に設定される。また、n側キャップ層8Aは、ゲート電極用金属膜Mとは異種材料で形成される。n側キャップ層8Aの材料としては、Hf、Ta、La、マグネシウム(Mg)、イッテルビウム(Yb)およびインジウム(In)のうちで少なくとも一つの元素を含む金属材料(第2材料)、または、当該第2材料の酸化物、窒化物、炭化物、珪化物、窒化珪化物、もしくは炭窒化物のいずれかの材料を用いることが、望ましい。

【0045】

なお、n側キャップ層8Aの他の形成方法として、図6に例示する方法を適用してもよい。すなわち、まず、キャップ層8APをゲート電極用金属膜Mの上面上に全面的に形成しておいた上で、その後、キャップ層8APの上面のうちでnFET領域Rnに属する部分上に全面的にレジストパターン7Aを形成し、レジストパターン7Aをマスクとしてウェットエッチングまたはドライエッチング法などを用いることにより、pFET領域Rp内に属するキャップ層8APの全部分を除去する。これにより、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分上にのみ、全面的に、n側キャップ層8Aが形成される。その後、不要となったレジストパターン7Aを除去する。

【0046】

n側キャップ層8Aの形成後は、熱処理を施して、n側キャップ層8AとnFET領域Rn内のゲート電極用金属膜M(すなわち、n側キャップ層8Aの直下に位置するゲート電極用金属膜Mの部分)を反応させ、n側キャップ層8Aの下に位置するゲート電極用金属膜M内にn側キャップ層8Aを拡散させることで、図7に示すように、nFET領域Rn内に、n側ゲート電極用金属膜MAを形成する。これにより、ゲート絶縁膜6の上面と接する最下層のゲート電極層は、pFET領域Rp内ではゲート電極用金属膜Mとなる一方、nFET領域Rn内ではn側ゲート電極用金属膜MAとなる。なお、拡散(反応)のための熱処理の温度は、キャップ層Aの材料に応じて定まる。このn側キャップ層8AをnFET領域Rn内のゲート電極用金属膜Mに拡散させて反応させるための熱処理は、第1熱処理に相当する。

【0047】

次に、図8に示すように、多結晶シリコン層(以下「ポリSi層」という場合がある)10Aを、30nm〜120nmの範囲内で、最下層のゲート電極層の上面上に全面的に堆積する。ここで、ポリSi層10Aを形成する利点は、その後の工程において従来通りのCMOS形成プロセスをそのまま適用できる点にある。なお、ポリSi層10Aを形成せずに、pFETおよびnFETの各々ゲート電極を、それぞれ、ゲート電極用金属膜Mおよびn側ゲート電極用金属膜MAのみから構成することとしてもよい。

【0048】

その後、ドライエッチング法などにより、pFETおよびnFETの各ゲート電極を形成するための加工を行う。このとき、nFETおよびpFETの各々のゲート電極の主材料が共に同じであるため、ゲート電極の加工が容易となる。これにより、図9に示すように、nFETのゲート電極GEはn側ゲート電極用金属膜MAとポリSi層10とのスタック構造であり、pFETのゲート電極GEはゲート電極用金属膜MとポリSi層10とのスタック構造という、デュアルゲート電極構造が形成される。このように、pFETおよびnFETの各ゲート電極を形成するための加工を行う工程は、nFET領域RnとpFET領域Rpとで異なる組成を有するデュアルゲート電極構造を形成する工程に相当する。

【0049】

その後は、通常のCMOS形成プロセスフローを順次に経ることにより、CMOSが完成される。このCMOS形成プロセスフローにおいて、図9に示すソースドレイン領域11およびサイドウォールスペーサ12が形成される。

【0050】

以上の記載により、本実施の形態によれば、nFETのゲート電極GEはn側ゲート電極用金属膜MA、pFETのゲート電極GEはゲート電極用金属膜Mという、互いに異なる仕事関数を有するデュアルゲート電極構造を有することにより、nFET、pFETそれぞれを所望の閾値電圧で動作可能なCMOSを容易にかつ精度良く形成することができる。特に、ゲート電極GEの主材料がnFETおよびpFET間で同じであるため、ドライエッチング法などによるゲート電極加工が容易となる。これによって、微細ゲート電極の加工精度を向上させることができる。また、従来のハイブリッドメタルゲート電極構造のように、片チャネル領域上のみのゲート電極を除去する工程がそもそも不必要になるため、ゲート絶縁膜6に対するダメージはなくなり、高信頼性デバイスを実現することが可能である。このように本実施の形態の半導体装置の製造方法によれば、nFETおよびpFETがそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0051】

<第2の実施の形態>

図10〜図12は、本発明の第2の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。本実施の形態では、第1の実施の形態と同じフローに従ってゲート電極用金属膜Mを形成した後に、フォトレジストマスクを用いる方法(図3参照)、または、ウェットエッチングもしくはドライエッチング法などを用いる方法(図6参照)により、図10の断面図に示すように、pFET領域Rpに形成されたゲート電極用金属膜Mの上面上に、本実施の形態では、ゲート電極用金属膜Mの上面のうちでpFET領域Rp内に属する部分上にのみ、p側キャップ層8Bを形成する。p側キャップ層(第1キャップ層に該当)8Bの膜厚は、経験的に、10nm以下とする。また、p側キャップ層8Bは、ゲート電極用金属膜Mとは異種材料で形成される。p側キャップ層8Bの材料としては、白金(Pt)、イリジウム(Ir)、ニッケル(Ni)、アルミニウム(Al)およびルテニウム(Ru)のうちの少なくとも一つを含む金属材料(第3材料)、または、当該第3材料の酸化物、窒化物、炭化物、珪化物、窒化珪化物、もしくは炭窒化物のいずれかの材料を用いることが、望ましい。

【0052】

その後、熱処理を施して、p側キャップ層8BとpFET領域Rp内のゲート電極用金属膜M(すなわち、p側キャップ層8Bの直下に位置するゲート電極用金属膜Mの部分)を反応させ、p側キャップ層8Bの下に位置するゲート電極用金属膜M内にp側キャップ層8Bを拡散させることで、図11に示すように、pFET領域Rp内に、p側ゲート電極用金属膜MBを形成する。なお、拡散のための上記熱処理の温度は、p側キャップ層8Bの材料次第で定まる。このp側キャップ層8BをpFET領域Rp内のゲート電極用金属膜Mに拡散させて反応させるための熱処理は、第1熱処理に相当する。

【0053】

その後は、第1の実施の形態と同様に、ポリSi層を30nm〜120nmの範囲内で堆積し、ドライエッチング法などにより、pFETおよびnFETの各ゲート電極の加工を行う。このとき、本実施の形態においても、nFETおよびpFET間でゲート電極の主材料が同じであるため、ゲート電極加工は容易となる。これにより、図12に示すように、nFETのゲート電極GEはゲート電極用金属膜MとポリSi層10とのスタック構造を有し、pFETのゲート電極GEはp側ゲート電極用金属膜MBとポリSi層10とのスタック構造を有するというデュアルゲート電極構造が、形成される。

【0054】

その後は、第1の実施の形態と同様に、通常のCMOS形成プロセスフローを順次に経ることにより、CMOSが完成される。

【0055】

なお、本実施の形態においても、ポリSi層10を形成しなくてもよい。

【0056】

以上の記載により、本実施の形態によれば、nFETのゲート電極GEはゲート電極用金属膜M、pFETのゲート電極GEはp側ゲート電極用金属膜MBという、互いに異なる仕事関数を有するデュアルゲート電極構造を有することにより、nFETおよびpFETそれぞれを所望の閾値電圧で動作可能なCMOSを容易にかつ精度良く形成することができる。特に、ゲート電極GEの主材料がnFETおよびpFET間で同じであるため、ドライエッチング法などによるゲート電極加工が容易となる。これによって、微細ゲート電極の加工精度を向上させることができる。また、従来のハイブリッドメタルゲート電極構造のように、片チャネル領域上のみのゲート電極を除去する工程がそもそも不必要になるため、ゲート絶縁膜6に対するダメージはなくなり、高信頼性デバイスを実現することが可能である。このように本実施の形態の半導体装置の製造方法によれば、nFETおよびpFETがそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0057】

<第3の実施の形態>

図13〜図17は、本発明の第3の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。本実施の形態の特徴点は、nFET領域Rn内にn側ゲート電極用金属膜MAを、および、pFET領域Rp内にp側ゲート電極用金属膜MCを、同一チップ上に形成する点にある。p側ゲート電極用金属膜MCは、第2の実施の形態におけるp側ゲート電極用金属膜MBに相当し、第2の実施の形態におけるp側ゲート電極用金属膜MBと同様にして形成される。

【0058】

まず、n側ゲート電極用金属膜MAおよびp側ゲート電極用金属膜MCを同一チップ上に形成する一つの方法について、記載する。すなわち、第1の実施の形態の図1〜図7に記載した方法と同一の方法によって、nFET領域Rn内にn側ゲート電極用金属膜MAを形成する。その上で、第1の実施の形態で既述した方法と同一の方法(図3または図6参照)を用いて、図13に示すように、pFET領域Rp内のゲート電極用金属膜Mの上面上にのみ、全面的に、第2p側キャップ層(第2キャップ層に該当)8Cを形成する。そして、第2p側キャップ層8Cの材料如何で定まる所定の温度で熱処理を行って、pFET領域Rp内のゲート電極用金属膜M内に第2p側キャップ層8Cを拡散させることで、図14に示すように、pFET領域Rp内にp側ゲート電極用金属膜MCを形成する。

【0059】

第2p側キャップ層8Cは、第2の実施の形態におけるp側キャップ層8Bに相当し、nFET領域Rn内にn側ゲート電極用金属膜MAが形成された後に形成されること以外は、第2の実施の形態におけるp側キャップ層8Bと同様にして形成される。第2p側キャップ層8Cは、ゲート電極用金属膜Mおよび第1キャップ層に相当するn側キャップ層8Aとは異種材料で形成される。第2p側キャップ層8Cの材料としては、白金(Pt)、イリジウム(Ir)、ニッケル(Ni)、アルミニウム(Al)およびルテニウム(Ru)のうちの少なくとも一つを含む金属材料(第3材料)、または、当該第3材料の酸化物、窒化物、炭化物、珪化物、窒化珪化物、もしくは炭窒化物のいずれかの材料を用いることが望ましい。第2p側キャップ層8CをpFET領域Rp内のゲート電極用金属膜Mに拡散させて反応させるための熱処理は、第2熱処理に相当する。

【0060】

次に、n側ゲート電極用金属膜MAおよびp側ゲート電極用金属膜MCを同一チップ上に形成する他の方法について記載する。すなわち、第1の実施の形態の図2の構造に対して、図15に示すように、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分上にのみn側キャップ層8Aを全面的に形成する一方で、ゲート電極用金属膜Mの上面のうちでpFET領域Rp内に属する部分上にのみ、異なる仕事関数を有する第2p側キャップ層8Cを全面的に形成する。そして、同一の温度で熱処理を行うことで、同時に、nFET領域Rn内のゲート電極用金属膜M内にn側キャップ層8Aを拡散させる一方で、pFET領域Rp内のゲート電極用金属膜M内に第2p側キャップ層8Cを拡散させる。このときの処理温度は、n側キャップ層8Aおよび第2p側キャップ層8Cの材料の選定次第で定まる。その結果、図14に示す構造が、同様に得られる。

【0061】

その後は、図16に示すように、n側ゲート電極用金属膜MAおよびp側ゲート電極用金属膜MCの上面上に全面的にポリSi層10Aを堆積する。それ以降の工程は、第1または第2の実施の形態と同様である。その結果、図17に示すように、nFETのゲート電極GEはn側ゲート電極用金属膜MAを有する一方、pFETのゲート電極GEはp側ゲート電極用金属膜MCを有するというデュアルゲート電極構造が、実現される。

【0062】

その後は、第1または第2の実施の形態と同様に、通常のCMOS形成プロセスフローを順次に経ることにより、CMOSが完成される。

【0063】

以上の記載により、本実施の形態によれば、nFETのゲート電極GEはn側ゲート電極用金属膜MA、pFETのゲート電極GEはp側ゲート電極用金属膜MCという、互いに異なる仕事関数を有するデュアルゲート電極構造を有することにより、nFETおよびpFETそれぞれを所望の閾値電圧で動作可能なCMOSを容易にかつ精度良く形成することができる。特に、ゲート電極GEの主材料がnFETおよびpFET間で同じであるため、ドライエッチング法などによるゲート電極加工が容易となる。これによって、微細ゲート電極の加工精度を向上させることができる。また、従来のハイブリッドメタルゲート電極構造のように、片チャネル領域上のみのゲート電極を除去する工程がそもそも不必要になるため、ゲート絶縁膜6に対するダメージはなくなり、高信頼性デバイスを実現することが可能である。このように本実施の形態の半導体装置の製造方法によれば、nFETおよびpFETがそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0064】

<第4の実施の形態>

図18〜図23は、本発明の第4の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。本実施の形態は、第1〜第3の実施の形態の各々に係る図2の構造において、ゲート電極用金属膜Mの膜厚が、既述したキャップ層の拡散を容易にするという観点から、3nm〜10nm程度と比較的薄く設定されている場合におけるCMOSの製造方法を提案する。なお、以下に記載する一例は、本実施の形態の技術的特徴点を第1の実施の形態に適用した場合であるが、勿論、本実施の形態の技術的特徴点をその他の第2および第3の実施の形態に適用してもよい。

【0065】

まず、図18に示すように、第1の実施の形態で既述した方法により、nFET領域Rn内のゲート電極用金属膜Mの上面上にのみ、n側キャップ層8Aを形成する。その上で、熱処理を施すことで、n側キャップ層8Aを、その直下のゲート電極用金属膜Mの部分内に拡散させて、図19に示すように、n側ゲート電極用金属膜MAをnFET領域Rn内に形成する。その後、図20に示すように、n側ゲート電極用金属膜MAおよびゲート電極用金属膜Mの上面上に、全面的に、第2ゲート電極用金属膜(第2金属膜に該当)Nを形成して、ゲート電極用金属膜の積層構造を得る。この場合の第2ゲート電極用金属膜Nの膜厚は、経験的観点から、5nm〜30nmの範囲内に設定される。

【0066】

あるいは、上記の製造方法に代えて、以下の製造方法を適用して上記のゲート電極用金属膜の積層構造を得てもよい。すなわち、図21に示すように、n側キャップ層8Aの形成後に、n側キャップ層8Aを被覆するように、ゲート電極用金属膜Mの上面上に、全面的に、5nm〜30nmの範囲内の膜厚を有する第2ゲート電極用金属膜(第2金属膜に該当)Nを形成する。次に、第2ゲート電極用金属膜N越しに図21の構造に対して熱処理を施して、n側キャップ層8Aをその直下のゲート電極用金属膜Mの部分内に拡散・反応させて、図20に示すように、n側ゲート電極用金属膜MAを、nFET領域Rn内に形成する。

【0067】

ここで、第2ゲート電極用金属膜Nの材料は、ゲート電極用金属膜Mと同種の材料であることが望ましいが、これに限られるわけではない。たとえば、Ti、Ta、HfおよびWのうちの少なくとも一つの元素を含んだ金属材料(第4材料)、または、当該第4材料の窒化物、炭化物、珪化物、窒化珪化物、もしくは炭窒化物のいずれかを、ゲート電極Nの材料として適用することができる。

【0068】

第2ゲート電極用金属膜Nの形成後は、図22に示すように、ポリSi層10Aを積層し(変形例として、ポリSi層10Aを形成しなくてもよい。)、第1の実施の形態で既述した通りのゲート電極加工を行い、図23に示す構造を得る。図23に示すように、nFETのゲート電極GEはn側ゲート電極用金属膜MAと第2ゲート電極用金属膜Nとの積層体およびポリSi層10から成る構造を有する一方、pFETのゲート電極GEはゲート電極用金属膜Mと第2ゲート電極用金属膜Nとの積層体およびポリSi層10から成る構造を有するという、デュアルゲート構造が、形成されている。

【0069】

その後は、前述と同様のCMOS形成プロセスフローを順次に経ることで、CMOSが完成される。

【0070】

なお、図24は、第3の実施の形態における図13および図14に示す方法、すなわちn側ゲート電極用金属膜MAの形成後に第2p側キャップ層8Cを形成して拡散させてp側ゲート電極用金属膜MCを形成する方法に対して本実施の形態を適用した場合の製造工程の状態を示す断面図である。また図25は、第3の実施の形態における図15に示す方法、すなわちn側キャップ層8Aおよび第2p側キャップ層8Cを共に拡散させて、n側ゲート電極用金属膜MAおよびp側ゲート電極用金属膜MCを形成する方法に対して本実施の形態を適用した場合の製造工程の状態を示す断面図である。

【0071】

第3の実施の形態における図13および図14に示す方法に対して本実施の形態を適用する場合、図14に示すようにn側ゲート電極用金属膜MAおよびp側ゲート電極用金属膜MCを形成した後に、図24に示すようにn側ゲート電極用金属膜MAの上面上およびp側ゲート電極用金属膜MCの上面上に、全面的に、第2ゲート電極用金属膜Nを形成する。

【0072】

第3の実施の形態における図15に示す方法に対して本実施の形態を適用する場合、図15に示すようにn側キャップ層8Aおよび第2p側キャップ層8Cを形成した後であって、n側キャップ層8Aおよび第2p側キャップ層8Cの拡散前に、図25に示すように、n側キャップ層8Aの上面上および第2p側キャップ層8Cの上面上に、全面的に、第2ゲート電極用金属膜Nを形成する。

【0073】

以上の記載により、本実施の形態によれば、以下の利点が得られる。第1に、ゲート電極用金属膜Mが比較的薄い膜である場合においても、同種または異種の材料から成る第2ゲート電極用金属膜Nを積層しているので、第2ゲート電極用金属膜NまたはポリSi層10の厚みを調整することにより、ゲート電極GEの高さを安定させることができる。第2に、同種または異種の材料の第2ゲート電極用金属膜Nを積層することにより、ゲート電極GEの金属膜を厚膜化することができるため、ゲート電極最上層のポリSi層10中からのSi拡散を抑制することができ、仕事関数の変動を防ぐことができる。

【0074】

<第5の実施の形態>

図26〜図28は、本発明の第5の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。本実施の形態においても、半導体装置として、相補型MOSFET(Complementary Metal-Oxide Semiconductor Field Effect Transistor;略称:CMOSFET)200を製造する。CMOSFET200には、nチャネルのMOSトランジスタであるn型MOSトランジスタと、pチャネルのMOSトランジスタであるp型MOSトランジスタとが並設される。n型MOSトランジスタは、より詳細にはnMOSFET120であり、p型MOSトランジスタは、より詳細にはpMOSFET121である。本実施の形態では、nMOSFET120が第1導電型半導体素子に相当し、pMOSFET121が第2導電型半導体素子に相当する。図26〜図28では、理解を容易にするために、前述の図1〜図25に示したp型半導体層2については、記載を省略している。

【0075】

図26は、第2絶縁膜用キャップ層109の形成が終了した段階の状態を示す断面図である。まず、図26に示すように、従来のCMOSFET作製フローに則り、半導体基板であるシリコン(Si)基板101の表面からSi基板101の内部に向けて延在した素子分離膜102、pウェル103およびnウェル104を順次に形成する。ここで、素子分離膜102は、第1導電型素子領域であるnMOSFET領域Rnと、第2導電型素子領域であるpMOSFET領域Rpとを区分する絶縁膜であり、nMOSFET領域Rnに形成されるpウェル103と、pMOSFET領域Rpに形成されるnウェル104との間に介在する。素子分離膜102の底面直下には、pウェル103およびnウェル104の境界面BSが形成されている。この境界面BSは、nMOSFET領域RnとpMOSFET領域Rpとの境界に相当する。

【0076】

次に、Si基板101上に、素子分離膜102、pウェル103およびnウェル104が形成された表面側から、全面にわたって界面層105を形成する。界面層105は、Si基板101と、後述するゲート絶縁膜用絶縁層106との界面反応を防止するために設けられ、たとえば絶縁性材料から成る。界面層105は、たとえば、シリコン酸化膜(SiO2)またはシリコン酸窒化膜(SiON)から成り、Si基板101を酸化または酸化および窒化することによって形成される。

【0077】

次に、界面層105上全面に、ゲート絶縁膜用絶縁層(以下、単に「絶縁層」という場合がある)106として、たとえばハフニウムシリコンオキシナイトライド(HfSiON)層を形成する。絶縁層106の材料としては、HfSiONに限らず、絶縁性材料、具体的には、ハフニウム(Hf)、ジルコニウム(Zr)などの、酸化物、酸窒化物または酸窒化珪化物などの高誘電率材料、すなわちhigh−k材料が挙げられる。絶縁層106の材料は、high−k材料に限らず、たとえばSiONなどのhigh−k材料以外の絶縁性材料でもよい。

【0078】

次に、絶縁層106上に、第1絶縁膜用キャップ層107として、たとえば膜厚が0.5nmのアルミニウム(Al)酸化膜を積層する。第1絶縁膜用キャップ層107の膜厚、すなわち厚み寸法は、0.1nm以上2nm以下に選ばれる。第1絶縁膜用キャップ層107は、絶縁層106上の全面にわたって、具体的にはnMOSFET領域RnとpMOSFET領域Rpとにわたって形成される。

【0079】

第1絶縁膜用キャップ層107の材料としては、元素としてAlを含有する材料が用いられる。第1絶縁膜用キャップ層107は第1元素層に相当し、Alは第1の元素に相当する。第1絶縁膜用キャップ層107の材料は、Alを含有する材料に限定されないが、Alを含有する材料であることが好ましい。本実施の形態のように、第1絶縁膜用キャップ層107の材料に、ゲート絶縁膜としての性質も持ち合わせた材料、たとえばAl酸化膜を選んだ場合には、本実施の形態とは異なるが、絶縁層106の下層に第1絶縁膜用キャップ層107を形成することも可能である。この場合、第1絶縁膜用キャップ層107は、絶縁層106を形成する前に、Si基板101上に形成される。

【0080】

第1絶縁膜用キャップ層107の形成後は、用途に応じて、酸素雰囲気または窒素雰囲気などで熱処理を行ってもよい。その後、第1絶縁膜用キャップ層107上に、スパッタ法などによって、全面にわたってゲート電極用金属膜108を形成する。ゲート電極用金属膜108の膜厚は、薄すぎるとゲート電極用金属膜108の膜厚制御が困難になり、また厚すぎると後述する第2絶縁膜用キャップ層109の材料の拡散が不充分となるので、経験的に、2nm〜30nmの範囲内の値に選ばれる。本実施の形態では、ゲート電極用金属膜108として、10nmの窒化チタン(TiN)膜を形成する。

【0081】

ゲート電極用金属膜108は、導電性材料から成り、電極用導電層に相当する。またゲート電極用金属膜108は、第1金属膜に相当し、前述の第1〜第4の実施の形態におけるゲート電極用金属膜Mに相当する。ゲート電極用金属膜108を構成する導電性材料としては、たとえばTiNが挙げられる。ゲート電極用金属膜108を構成する導電性材料としては、TiNに限らず、チタン(Ti)、タンタル(Ta)、Hfおよびタングステン(W)のうちの少なくとも1つの元素を含んだ材料(以下「第1材料」という)、具体的には、Ti、Ta、HfおよびWから選ばれる1種または2種以上から成る第1材料、ならびに第1材料の窒化物、第1材料の炭化物、第1材料の珪化物、第1材料の窒化珪化物、第1材料の炭窒化物が挙げられ、これらの材料から選ばれる1種または2種以上が用いられる。

【0082】

ゲート電極用金属膜108上には、第2絶縁膜用キャップ層109として、たとえばランタン(La)酸化膜を全面に堆積する。第2絶縁膜用キャップ層109の膜厚、すなわち厚み寸法は、0.1nm以上10nm以下に選ばれ、より詳細には、0.5nm以上2nm以下に選ばれる。その後、形成した第2絶縁膜用キャップ層109上のうち、nMOSFET領域Rnに属する部分上全面にフォトレジストマスクを形成し、このフォトレジストマスクをマスクとして、ウェットエッチング法またはドライエッチング法などを用いることによって、pMOSFET領域Rpに属する第2絶縁膜用キャップ層109の全ての部分を除去する。これによって、ゲート電極用金属膜108の上のうちで、nMOSFET領域Rnに属する部分上にのみ、全面に第2絶縁膜用キャップ層109が形成される。その後、不要となったフォトレジストマスクを除去する。

【0083】

第2絶縁膜用キャップ層109の材料としては、La酸化物などのLaを含有する材料が用いられる。第2絶縁膜用キャップ層109は第2元素層に相当し、Laは第2の元素に相当する。第2絶縁膜用キャップ層109は、第1キャップ層としても機能し、たとえば第1の実施の形態におけるn側キャップ層8Aとしても機能する。

【0084】

本実施の形態では、前述のように第1のキャップ層7に含有される第1の元素はAlであるので、第1絶縁膜用キャップ層107に含有される第1の元素と、第2絶縁膜用キャップ層109に含有される第2の元素とは異なる。第2の元素としては、Laに限定されず、周期律表の第2族元素および第3族元素のうち、少なくとも1種を用いることができる。周期律表の第2族元素(以下、単に「第2族元素」という場合がある)は、旧族名ではIIA族元素であり、アルカリ土類金属元素とも呼ばれる。周期律表の第3族元素(以下、単に「第3族元素」という場合がある)は、旧族名ではIIIA族元素であり、希土類元素とも呼ばれる。

【0085】

したがって第2絶縁膜用キャップ層109の材料としては、Laを含む材料に限定されず、La、ジスプロシウム(Dy)、イッテルビウム(Yb)、エルビウム(Er)などの少なくとも1つの希土類元素を含む材料および、マグネシウム(Mg)、ストロンチウム(Sr)などの少なくとも1つのアルカリ土類金属元素を含む材料が挙げられる。具体的には、希土類元素から成る材料およびその酸化物材料、ならびにアルカリ土類金属元素から成る材料およびその酸化物材料が挙げられ、これらの材料から選ばれる1種または2種以上を第2絶縁膜用キャップ層109の材料として用いてもよい。

【0086】

図27は、ゲート電極用金属膜108上および元素添加金属層110上への多結晶シリコン層113の形成が終了した段階の状態を示す断面図である。図26の第2絶縁膜用キャップ層109の形成後は、各層が形成されたSi基板101に熱処理を施して、第1および第2絶縁膜用キャップ層107,109とともに、絶縁層106およびゲート電極用金属膜108を熱処理する。これによって、第2絶縁膜用キャップ層109をゲート電極用金属膜108と反応させ、nMOSFET領域Rnに属するゲート電極用金属膜108内、すなわち第2絶縁膜用キャップ層109の直下に位置するゲート電極用金属膜108内に、第2絶縁膜用キャップ層109の材料を拡散させることで、図27に示すように、nMOSFET領域Rnに、ゲート電極用金属膜108に第2絶縁膜用キャップ層109の材料、具体的には第2絶縁膜用キャップ層109に含有される第2の元素が添加された元素添加金属層110を形成する。本実施の形態では、第2絶縁膜用キャップ層109に含有される第2の元素であるLaがゲート電極用金属膜108に拡散されて、Laが添加された元素添加金属層110が形成される。元素添加金属層110は、元素添加導電層に相当する。また第1および第2絶縁膜用キャップ層107,109、絶縁層106、ならびにゲート電極用金属膜108の熱処理は、第1熱処理に相当する。

【0087】

さらに第2絶縁膜用キャップ層109の材料は、第2絶縁膜用キャップ層109の下方に位置する絶縁層106、すなわちnMOSFET領域Rnに属する絶縁層106中にも拡散される。また第1絶縁膜用キャップ層107の材料は、第1絶縁膜用キャップ層107の直下に位置する絶縁層106、すなわちnMOSFET領域RnおよびpMOSFET領域Rpに属する絶縁層106に拡散される。そのため、nMOSFET領域Rnに属する絶縁層106は、第1および第2絶縁膜用キャップ層107,109の材料、具体的には第1絶縁膜用キャップ層107に含有される第1の元素および第2絶縁膜用キャップ層109に含有される第2の元素が添加されて第1元素添加絶縁層111となる。本実施の形態では、絶縁層106はHfSiON層であるので、第1元素添加絶縁層111として、第1絶縁膜用キャップ層107に含有される第1の元素であるAlと第2絶縁膜用キャップ層109に含有される第2の元素であるLaとが添加されたHfSiON層が形成される。

【0088】

元素添加金属層110および第1元素添加絶縁層111は、ゲート電極用金属膜108の膜厚、第2絶縁膜用キャップ層109の膜厚、熱処理を施すタイミング、ならびに熱処理温度および熱処理時間などの熱処理条件を制御することによって、所望の組成に制御できる。

【0089】

pMOSFET領域Rpに属する絶縁層106は、第1絶縁膜用キャップ層107の材料、具体的には第1絶縁膜用キャップ層107に含有される第1の元素が添加されて、第2元素添加絶縁層112となる。本実施の形態では、絶縁層106はHfSiON層であるので、第2元素添加絶縁層112として、第1絶縁膜用キャップ層107に含有される第1の元素であるAlが添加されたHfSiON層が形成される。

【0090】

pMOSFET領域Rpに属するゲート電極用金属膜108上には、第2絶縁膜用キャップ層109が設けられていないので、pMOSFET領域Rpでは、ゲート電極用金属膜108への第2絶縁膜用キャップ層109の材料の拡散は起こらず、ゲート電極用金属膜108がそのまま残存する。この残存するゲート電極用金属膜108が、電極用導電層に相当する。

【0091】

本実施の形態では、第1および第2絶縁膜用キャップ層107,109は、前述の第1〜第4の実施の形態におけるn側キャップ層8A、p側キャップ層8Bおよび第2p側キャップ層8Cと同様に、熱処理によって消失する。具体的に述べると、本実施の形態では、第1および第2絶縁膜用キャップ層107,109は、拡散させるべき量の材料によって形成される。したがって、熱処理によって第1および第2絶縁膜用キャップ層107,109を構成する材料の全てが拡散されて他の層と一体化し、第1および第2絶縁膜用キャップ層107,109自体は消失する。第1および第2絶縁膜用キャップ層107,109の消失によって、nMOSFET領域Rnでは、元素添加金属層110が露出し、第1元素添加絶縁層111の直上に元素添加金属層110が形成された状態となる。またpMOSFET領域Rpでは、第2元素添加絶縁層112の直上にゲート電極用金属膜108が形成された状態となる。

【0092】

その後、図27に示すように、多結晶シリコン(poly−Si)層113を、30nm〜120nmの範囲内で、ゲート電極用金属膜108上および元素添加金属層110上に堆積する。ここで、poly−Si層113を形成する利点は、その後の工程において従来通りのCMOSFET形成プロセスをそのまま適用できる点にある。

【0093】

図28は、CMOSFET200の形成が終了した段階の状態を示す断面図である。図27のpoly−Si層113の形成後は、ドライエッチング法などによって、nMOSFET120およびpMOSFET121の各ゲート電極を形成するための加工を行う。具体的には、ゲート電極の部分とその下層が残存するように、ゲート電極となるpoly−Si層113、元素添加金属層110およびゲート電極用金属膜108、ならびにその下層の第1元素添加絶縁層111、第2元素添加絶縁層112および界面層105をエッチングする。

【0094】

本実施の形態において、nMOSFET120のn側ゲート電極114は、poly−Si層113および元素添加金属層110によって構成され、n側ゲート絶縁膜116は、界面層105および第1元素添加絶縁層111によって構成される。したがってnMOSFET120は、poly−Si層113、元素添加金属層110、第1元素添加絶縁層111、界面層105およびpウェル103から成るゲートスタック構造となる。

【0095】

またpMOSFET121のp側ゲート電極115は、poly−Si層113およびゲート電極用金属膜108によって構成され、p側ゲート絶縁膜117は、界面層105および第2元素添加絶縁層112によって構成される。したがってpMOSFET121は、poly−Si層113、ゲート電極用金属膜108、第2元素添加絶縁層112、界面層105およびnウェル104から成るゲートスタック構造となる。

【0096】

n側ゲート電極114およびp側ゲート電極115の形成後は、通常のCMOSFET形成プロセスフローを順次に経ることによって、nMOSFET120およびpMOSFET121が形成され、CMOSFET200が形成される。具体的には、nMOSFET領域Rnにおいて、n側ゲート電極114およびn側ゲート絶縁膜の両側壁に、たとえばSiO2から成るサイドウォールスペーサ118を形成する。またpMOSFET領域Rpにおいて、p側ゲート電極115およびp側ゲート絶縁膜117の両側壁に、たとえばSiO2から成るサイドウォールスペーサ118を形成する。サイドウォールスペーサ118は、たとえば、化学気相成長(Chemical Vapor Deposition;略称:CVD)法などによってSiO2膜を形成した後、異方性エッチングを用いてエッチバックすることによって形成する。その後、イオン打込みなどによってソースドレイン領域119を形成することによって、CMOSFET200が形成される。

【0097】

このようにして形成される本実施の形態のCMOSFET200において、nMOSFET120のn側ゲート電極114の実効仕事関数は、4.0eV〜4.3eVであり、pMOSFET121のp側ゲート電極115の実効仕事関数は、4.9eV〜5.2eVである。ここで、「ゲート電極の実効仕事関数」とは、ゲート絶縁膜との界面におけるゲート電極の仕事関数のことであり、ゲート電極を構成する材料本来の「仕事関数」とは区別される。ゲート電極の実効仕事関数は、得られたnMOSFET120およびpMOSFET121におけるMOS型キャパシタのC−V特性、すなわち容量−ゲート電圧特性から求められるフラットバンド電圧から求められる。

【0098】

本実施の形態によれば、nMOSFET領域RnおよびpMOSFET領域RpのSi基板101上に、界面層105、絶縁層106、第1絶縁膜用キャップ層107およびゲート電極用金属膜108が順次形成される。形成されたゲート電極用金属膜108のうち、nMOSFET領域Rnのゲート電極用金属膜108上に、第2絶縁膜用キャップ層109が形成される。形成された第1絶縁膜用キャップ層107および第2絶縁膜用キャップ層109とともに、絶縁層106およびゲート電極用金属膜108が熱処理される。この熱処理によって、第1絶縁膜用キャップ層107に含有される第1の元素、具体的にはAlを、第1絶縁膜用キャップ層107の下方の絶縁層106に拡散させることができる。また第2絶縁膜用キャップ層109に含有される第2の元素、具体的にはLaを、第2絶縁膜用キャップ層109の下方のゲート電極用金属膜108に拡散させ、さらにゲート電極用金属膜108の下方の絶縁層106に拡散させることができる。

【0099】

これによって、nMOSFET領域Rnでは、第1および第2の元素、具体的にはAlおよびLaを含有する絶縁層106を形成し、pMOSFET領域Rpでは、第1の元素、具体的にはAlを含有する絶縁層106を形成することができるので、nMOSFET120の閾値電圧およびpMOSFET121の閾値電圧をそれぞれ制御することができる。したがって、閾値電圧の制御範囲を広げることができる。

【0100】

また本実施の形態では、第2絶縁膜用キャップ層109は、絶縁層106の表面上ではなく、ゲート電極用金属膜108の表面上に形成されており、第2絶縁膜用キャップ層109と絶縁層106との間にはゲート電極用金属膜108が介在するので、nMOSFET領域Rnのみに残存させるための第2絶縁膜用キャップ層109のエッチングは、ゲート電極用金属膜108の表面上で行われる。つまり、本実施の形態では、pMOSFET領域Rpに属する第2絶縁膜用キャップ層109をエッチングによって除去する作業を、絶縁層106の表面上ではなく、ゲート電極用金属膜108の表面上で行っている。したがって、エッチングによって絶縁層106が損傷することを防ぐことができるので、絶縁層106の劣化を防ぎ、n側ゲート絶縁膜116およびp側ゲート絶縁膜117の劣化を防ぐことができる。

【0101】

また本実施の形態では、nMOSFET領域Rnのゲート絶縁膜であるn側ゲート絶縁膜116とpMOSFET領域Rpのゲート絶縁膜であるp側ゲート絶縁膜117とを作り分けるために、片側のゲート電極を剥離するなどのプロセスを経る必要がないので、ゲート絶縁膜116,117の劣化が無い。

【0102】

したがって、劣化による絶縁層106の信頼性の低下を防止し、n側ゲート絶縁膜116およびp側ゲート絶縁膜117の信頼性の低下を防止することができるので、高信頼性デバイスが実現可能である。つまり本実施の形態では、絶縁層106の信頼性の低下、ひいてはn側ゲート絶縁膜116およびp側ゲート絶縁膜117の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。

【0103】

また本実施の形態では、nMOSFET120のn側ゲート電極114は、poly−Si層113および元素添加金属層110によって構成され、pMOSFET121のp側ゲート電極115は、poly−Si層113およびゲート電極用金属膜108によって構成される。このようにnMOSFET120およびpMOSFET121のそれぞれのゲート電極114,115は、上層は共にpoly−Si層113であり、また下層金属層の主材料は共に同じであるので、ゲート電極114,115の加工が容易となる。したがって、n側ゲート電極114とp側ゲート電極115とを一度に加工しても、所望の形状を有するn側およびp側ゲート電極114,115を形成することができる。

【0104】

以上のように本実施の形態によれば、nMOSFET120およびpMOSFET121がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置200を容易に製造することができる。

【0105】

また本実施の形態では、第1絶縁膜用キャップ層107は、Al酸化物などのAlを含有する材料で構成されており、第1の元素として、Alを含有するので、pMOSFET領域Rpのp側ゲート絶縁膜117には、Alが含有される。これによって、pMOSFET121に適した閾値電圧に制御することが可能となる。したがって第1絶縁膜用キャップ層107は、本実施の形態のように、Alを含有する材料で構成されることが好ましい。

【0106】

また本実施の形態では、第2絶縁膜用キャップ層109は、La酸化物などのLaを含有する材料で構成されている。つまり第2絶縁膜用キャップ層109は、Laなどの第3族元素を含有する材料で構成されており、第2の元素として、第3族元素を含有するので、nMOSFET領域Rnのn側ゲート絶縁膜116には、希土類系元素が含有される。これによって、nMOSFET120に適した閾値電圧に制御することが可能となる。第2絶縁膜用キャップ層109の材料として、第2族元素を含有する材料を用いた場合も同様の効果があり、nMOSFET120に適した閾値電圧に制御することが可能となる。したがって第2絶縁膜用キャップ層109は、第3族元素および第2族元素のうち、少なくとも1種を含有する材料で構成されることが好ましい。

【0107】

本実施の形態では、第1絶縁膜用キャップ層107は、Alを含有する材料で構成されており、第2絶縁膜用キャップ層109は、Laを含有する材料で構成されているので、nMOSFET領域Rnのn側ゲート絶縁膜116には、AlおよびLaが含有されることになる。したがって、第1絶縁膜用キャップ層107および第2絶縁膜用キャップ層109の厚み寸法、ならびに熱処理条件によって、n側ゲート絶縁膜116中のAlおよびLaの含有量を制御することができるので、nMOSFET120に特に適した閾値電圧に制御することが可能となる。

【0108】

また本実施の形態では、ゲート電極用金属膜108の材料は、チタン(Ti)、タンタル(Ta)、ハフニウム(Hf)およびタングステン(W)のうちの少なくとも1つの元素を含む第1材料、第1材料の窒化物、第1材料の炭化物、第1材料の珪化物、第1材料の窒化珪化物、または、第1材料の炭窒化物のいずれかの材料である。これらの材料から成るゲート電極用金属膜108には、前述の第2絶縁膜用キャップ層109の材料が拡散可能であるので、第2絶縁膜用キャップ層109の材料の拡散が、ゲート電極用金属膜108によって阻害されることを防ぐことができる。これによって、nMOSFET領域Rnの絶縁層106に第2絶縁膜用キャップ層109の材料を確実に拡散させることができるので、nMOSFET120に適した閾値電圧に制御することができる。

【0109】

また本実施の形態では、ゲート電極用金属膜108上および元素添加金属層110上には、poly−Si層113が形成される。これによって、その後の工程において従来通りのCMOSFET形成プロセスをそのまま適用することができるので、製造工程の煩雑化を招くことなく、nMOSFET120およびpMOSFET121の閾値電圧を、それぞれに適した閾値電圧に制御することができる。

【0110】

また本実施の形態では、第1絶縁膜用キャップ層107の厚み寸法は、0.1nm以上2nm以下である。これによって、第1絶縁膜用キャップ層107に含有される第1の元素、具体的にはAlを、適度な量でnMOSFET領域RnおよびpMOSFET領域Rpの絶縁層106に拡散させることができるので、nMOSFET120およびpMOSFET121の閾値電圧を、それぞれに適した閾値電圧により確実に制御することができる。

【0111】

また本実施の形態では、第2絶縁膜用キャップ層109の厚み寸法は、0.1nm以上10nm以下である。これによって、第2絶縁膜用キャップ層109に含有される第2の元素、具体的にはLaを、適度な量でnMOSFET領域Rnの絶縁層106に拡散させることができるので、nMOSFET120に適した閾値電圧にさらに確実に制御することができる。

【0112】

以上のようにして形成される本実施の形態のnMOSFET120は、n側ゲート絶縁膜116を構成する第1元素添加絶縁層111に、第1絶縁膜用キャップ層107由来の第1の元素であるAlおよび第2絶縁膜用キャップ層109由来の第2の元素であるLaを含有し、この第1元素添加絶縁層111上の元素添加金属層110に第2絶縁膜用キャップ層109由来の第2の元素であるLaを含有する。またpMOSFET121は、p側ゲート絶縁膜117を構成する第2元素添加絶縁層112に、第1絶縁膜用キャップ層107由来の第1の元素であるAlを含有し、この第2元素添加絶縁層112上に第1の元素であるAlおよび第2の元素であるLaが添加されていないゲート電極用金属膜108を備える。

【0113】

これによって、それぞれに適した実効仕事関数を有するゲート電極114,115を備えるnMOSFET120およびpMOSFET121を実現することができる。具体的には、nMOSFET120におけるn側ゲート電極114の実効仕事関数を4.0eV〜4.3eVとし、pMOSFET121におけるp側ゲート電極115の実効仕事関数を4.9eV〜5.2eVすることができる。したがって、それぞれに適した閾値電圧を有するnMOSFET120およびpMOSFET121を実現することが可能である。

【0114】

また第1および第2元素添加絶縁層111,112は、第1および第2元素添加絶縁層111,112となるゲート絶縁膜用絶縁層106上でエッチングを実施することなく形成することが可能であるので、製造過程における劣化が防止され、信頼性の低下が防止される。したがって、nMOSFET120およびpMOSFET121がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置200を実現することが可能である。

【0115】

以上に述べた本実施の形態では、第1絶縁膜用キャップ層107は、絶縁層106上に設けられるが、本実施の形態のように第1絶縁膜用キャップ層107の材料が、ゲート絶縁膜としての性質を持ち合わせた材料、たとえばAl酸化物膜である場合には、Si基板101と絶縁層106との間に設けられてもよい。この場合、第1絶縁膜用キャップ層107の材料は、熱処理によって、第1絶縁膜用キャップ層107の上方の絶縁層106に拡散される。

【0116】

また前述の第1および第2絶縁膜用キャップ層107,109に含有される元素を熱拡散させるための熱処理工程は、他の製造工程に組み入れてもよい。具体的には、第1および第2絶縁膜用キャップ層107,109に含有される元素は、多結晶シリコン層113を形成するときの熱を用いて拡散させたり、多結晶シリコン層113の形成後の工程、たとえば活性化アニール工程で拡散させたりしてもよい。これによって、熱拡散工程を省略することが可能である。しかし、熱拡散させる前に多結晶シリコン層113を形成して熱処理をすると、第2絶縁膜用キャップ層109の材料によっては、多結晶シリコン層113の方に極端に拡散してしまい、ゲート電極金属層8の方に拡散されない場合がある。したがって、本実施の形態のように、多結晶シリコン層113の形成前に、熱処理工程を行うことが好ましい。

【0117】

<第6の実施の形態>

次に、本発明の第6の実施の形態である半導体装置の製造方法について説明する。図29〜図33は、本発明の第6の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。本実施の形態においても、前述の第5の実施の形態と同様に、半導体装置として、CMOSFET210を製造する。図29は、保護層130の形成が終了した段階の状態を示す断面図である。図29〜図33では、理解を容易にするために、前述の図1〜図25に示したp型半導体層2については、記載を省略している。

【0118】

まず、前述の第5の実施の形態と同様に、Si基板101上に、素子分離膜102、pウェル103およびnウェル104が形成された表面側から、全面にわたって界面層105、絶縁層106、第1絶縁膜用キャップ層107、ゲート電極用金属膜108を順次に形成した後、ゲート電極用金属膜108上全面に、第2絶縁膜用キャップ層109を堆積する。第2絶縁膜用キャップ層109の材料としては、本実施の形態では、La酸化物などの希土類元素を含む材料(以下「希土類系材料」という)が用いられる。希土類系材料は潮解性を有しているので、第2絶縁膜用キャップ層109が希土類系材料を含む場合、水分または大気に触れると、特性が劣化してしまうおそれがある。

【0119】

そこで本実施の形態では、第2絶縁膜用キャップ層109の劣化を防ぐために、第2絶縁膜用キャップ層109の堆積後、第2絶縁膜用キャップ層109上全面に、保護層130として、窒化チタン(TiN)膜を形成する。この保護層130の形成は、第2絶縁膜用キャップ層109の劣化をより確実に防ぐためには、たとえば原子層化学気相成長(Atomic Layer Chemical Vapor Deposition;略称:ALCVD)法を用いて、第2絶縁膜用キャップ層109を堆積した時点から大気暴露せずに連続して行うことが望ましいが、その限りではない。

【0120】

保護層130の材料は、ゲート電極用金属膜108と同一材料でもよいし、異なる材料でもよい。本実施の形態では、保護層130とゲート電極用金属膜108とは、同一の材料、具体的にはTiNで構成される。保護層130の具体的な材料としては、TiNのほか、Ti、Ta、Hfおよびタングステン(W)のうち少なくとも1つの元素を含んだ第1材料、ならびに第1材料の窒化物、第1材料の炭化物、第1材料の珪化物、第1材料の窒化珪化物および第1材料の炭窒化物が挙げられる。また保護層130の材料は、シリコン(Si)でもよいし、絶縁材料でもよい。これらの材料から選ばれる1種または2種以上が用いられる。

【0121】

図30は、pMOSFET領域Rpの保護層130および第2絶縁膜用キャップ層109を除去する段階の状態を示す断面図である。保護層130の形成後は、フォトリソグラフィ技術を用いて、nMOSFET領域Rnの保護層130のみを残すようにパターニングし、残されたnMOSFET領域Rnの保護層130をマスクとして、ドライエッチングによって、pMOSFET領域Rpの第2絶縁膜用キャップ層109を除去する。本実施の形態とは異なるが、pMOSFET領域Rpの保護層130および第2絶縁膜用キャップ層109は、ウェットエッチングなどによって同時に除去してもよい。

【0122】

図31は、ゲート電極用金属膜108上および元素添加保護層131上へのpoly−Si層113の形成が終了した段階の状態を示す断面図である。pMOSFET領域Rpの保護層130および第2絶縁膜用キャップ層109を除去した後は、熱処理を施して、第2絶縁膜用キャップ層109をゲート電極用金属膜108と反応させ、nMOSFET領域Rnに属するゲート電極用金属膜108内、すなわち第2絶縁膜用キャップ層109の直下に位置するゲート電極用金属膜108内に、第2絶縁膜用キャップ層109の材料を拡散させることで、図31に示すように、nMOSFET領域Rnに、ゲート電極用金属膜108に第2絶縁膜用キャップ層109の材料が添加された元素添加金属層110を形成する。本実施の形態では、第2絶縁膜用キャップ層109の材料であるLaがゲート電極用金属膜108に拡散されて、Laが添加された元素添加金属層110が形成される。

【0123】

また第2絶縁膜用キャップ層109は保護層130とも反応する。これによって、nMOSFET領域Rnに属する保護層130内に、第2絶縁膜用キャップ層109の材料が拡散され、図31に示すように、nMOSFET領域Rnに、保護層130に第2絶縁膜用キャップ層109の材料が添加された元素添加保護層131が形成される。本実施の形態では、第2絶縁膜用キャップ層109の材料であるLaが保護層130に拡散されて、Laが添加された元素添加保護層131が形成される。本実施の形態では、保護層130は、ゲート電極用金属膜108と同一の材料、具体的にはTiNなどの導電性材料から成るので、元素添加保護層131は、導電性を有しており、もう一つの元素添加導電層に相当する。

【0124】

さらに第2絶縁膜用キャップ層109の材料は、前述の第5の実施の形態と同様に、第2絶縁膜用キャップ層109の下方に位置する絶縁層106、すなわちnMOSFET領域Rnに属する絶縁層106中にも拡散される。また第1絶縁膜用キャップ層107の材料は、第1絶縁膜用キャップ層107の直下に位置する絶縁層106、すなわちnMOSFET領域RnおよびpMOSFET領域Rpに属する絶縁層106に拡散される。これによって、nMOSFET領域Rnに属する絶縁層106は、第1および第2絶縁膜用キャップ層107,109の材料が添加されて第1元素添加絶縁層111となる。本実施の形態では、絶縁層106はHfSiONであるので、第1元素添加絶縁層111として、第1絶縁膜用キャップ層107の材料であるAlと第2絶縁膜用キャップ層109の材料であるLaとが添加されたHfSiON層が形成される。

【0125】

元素添加保護層131、元素添加金属層110および第1元素添加絶縁層111は、ゲート電極用金属膜108の膜厚、第2絶縁膜用キャップ層109の膜厚、熱処理を施すタイミング、ならびに熱処理温度および熱処理時間などの熱処理条件を制御することによって、所望の組成に制御できる。

【0126】

pMOSFET領域Rpに属する絶縁層106は、前述の第5の実施の形態と同様に、第1絶縁膜用キャップ層107の材料が添加されて、第2元素添加絶縁層112となる。本実施の形態では、絶縁層106はHfSiON層であるので、第2元素添加絶縁層112として、第1絶縁膜用キャップ層107の材料であるAlが添加されたHfSiON層が形成される。

【0127】

本実施の形態においても、前述の第5の実施の形態と同様に、第1および第2絶縁膜用キャップ層107,109は、拡散させるべき量の材料によって形成されるので、熱処理によって消失する。これによって、nMOSFET領域Rnでは、元素添加金属層110の直上に元素添加保護層131が形成され、第1元素添加絶縁層111の直上に元素添加金属層110が形成された状態となる。本実施の形態では、保護層130とゲート電極用金属膜108とは、同一の材料で構成されるので、元素添加保護層131と元素添加金属層110とは一体化して、1つの層を構成する。pMOSFET領域Rpでは、前述の第5の実施の形態と同様に、第2元素添加絶縁層112の直上にゲート電極用金属膜108が形成された状態となる。

【0128】

その後、図31に示すように、poly−Si層113を、30nm〜120nmの範囲内で、ゲート電極用金属膜108上および元素添加保護層131上に堆積する。本実施の形態でも、前述の第5の実施の形態と同様に、poly−Si層113の形成前に、熱処理工程を行うことが好ましい。

【0129】

図32は、CMOSFET210の形成が終了した段階の状態を示す断面図である。図31のpoly−Si層113の形成後は、前述の第5の実施の形態と同様に、ドライエッチング法などによって、nMOSFET120AおよびpMOSFET121の各ゲート電極を形成するための加工を行う。具体的には、ゲート電極の部分とその下層が残存するように、ゲート電極となるpoly−Si層113、元素添加保護層131、元素添加金属層110およびゲート電極用金属膜108、ならびにその下層の第1元素添加絶縁層111、第2元素添加絶縁層112および界面層105をエッチングする。

【0130】

本実施の形態において、nMOSFET120Aのn側ゲート電極114Aは、poly−Si層113、元素添加保護層131および元素添加金属層110によって構成され、n側ゲート絶縁膜116は、界面層105および第1元素添加絶縁層111によって構成される。したがってnMOSFET120Aは、poly−Si層113、元素添加保護層131、元素添加金属層110、第1元素添加絶縁層111、界面層105およびpウェル103から成るゲートスタック構造となる。またpMOSFET121は、図28に示す第5の実施の形態と同様に、poly−Si層113、ゲート電極用金属膜108、第2元素添加絶縁層112、界面層105およびnウェル104から成るゲートスタック構造となる。

【0131】

n側ゲート電極114Aおよびp側ゲート電極115の形成後は、前述の第5の実施の形態と同様に、通常のCMOSFET形成プロセスフローを順次に経ることによって、nMOSFET120AおよびpMOSFET121を形成し、CMOSFET210を形成する。具体的には、nMOSFET領域Rnにおいて、n側ゲート電極114Aおよびn側ゲート絶縁膜116の両側壁に、たとえばSiO2から成るサイドウォールスペーサ118を形成する。またpMOSFET領域Rpにおいて、p側ゲート電極115およびp側ゲート絶縁膜117の両側壁に、たとえばSiO2から成るサイドウォールスペーサ118を形成する。その後、イオン打込みなどによってソースドレイン領域119を形成することによって、CMOSFET210が形成される。

【0132】

このようにして形成される本実施の形態のCMOSFET210において、nMOSFET120Aのn側ゲート電極114Aの実効仕事関数は、4.0eV〜4.3eVであり、pMOSFET121のp側ゲート電極115の実効仕事関数は、4.9eV〜5.2eVである。ゲート電極の実効仕事関数は、得られたnMOSFET120AおよびpMOSFET121におけるMOS型キャパシタのC−V特性、すなわち容量−ゲート電圧特性から求められるフラットバンド電圧から求められる。

【0133】

本実施の形態では、第2絶縁膜用キャップ層109上に保護層130を形成するので、pMOSFET領域Rpの第2絶縁膜用キャップ層109のみを除去するときのリソグラフィ工程などによる第2絶縁膜用キャップ層109の劣化を防止することができる。これによって、その後の熱処理のときに、第2絶縁膜用キャップ層109の材料をゲート電極用金属膜108および絶縁層106に、より確実に拡散させることができるので、nMOSFET120Aの閾値電圧を、より確実に所望の値に制御することができる。

【0134】

このようにして形成される本実施の形態のnMOSFET120Aは、第1元素添加絶縁層111に第1の元素であるAlおよび第2の元素であるLaを含有し、第1元素添加絶縁層111上の元素添加金属層110に第2の元素であるLaを含有し、元素添加金属層110上の元素添加31に第2絶縁膜用キャップ層109由来の第2の元素であるLaを含有する。またpMOSFET121は、第2元素添加絶縁層112に第1の元素であるAlを含有し、この第2元素添加絶縁層112上に第1の元素であるAlおよび第2の元素であるLaが添加されていないゲート電極用金属膜108を備える。

【0135】

これによって、それぞれに適した実効仕事関数を有するゲート電極114A,115を備えるnMOSFET120AおよびpMOSFET121を実現することができる。具体的には、nMOSFET120Aにおけるn側ゲート電極114Aの実効仕事関数を4.0eV〜4.3eVとし、pMOSFET121におけるp側ゲート電極115の実効仕事関数を4.9eV〜5.2eVすることができる。したがって、それぞれに適した閾値電圧を有するnMOSFET120AおよびpMOSFET121を実現することが可能である。

【0136】

以上に述べた本実施の形態では、保護層130の材料は、金属材料であるTiNであるので、poly−Si層113の形成前に、元素添加保護層131を除去する必要はない。このように保護層130の材料が金属または不純物を添加したシリコンなどの導電性材料である場合は、poly−Si層113の形成前に、元素添加保護層131を除去する必要がないけれども、保護層130の材料が絶縁材料である場合は、poly−Si層113の形成前に、元素添加保護層131を除去する必要がある。この場合、nMOSFETのn側ゲート電極は、poly−Si層113および元素添加金属層110によって構成され、nMOSFETは、poly−Si層113、元素添加金属層110、第1元素添加絶縁層111、界面層105およびpウェル103から成るゲートスタック構造となる。

【0137】

また本実施の形態では、保護層130は、第2絶縁膜用キャップ層109の材料が拡散可能な材料、具体的にはゲート電極用金属膜108と同一の材料で構成されているが、これに限定されず、第2絶縁膜用キャップ層109の材料が拡散しない、または拡散しにくい材料で構成されてもよい。

【0138】

図33は、ゲート電極用金属膜108上および保護層130上へのpoly−Si層113の形成が終了した段階の状態を示す断面図である。図29に示すように、第2絶縁膜用キャップ層109上に形成される保護層130が、第2絶縁膜用キャップ層109の材料が拡散しない、または拡散しにくい材料で構成されている場合は、nMOSFET領域Rnに属する保護層130内に、第2絶縁膜用キャップ層109の材料が拡散して元素添加保護層131が形成される図31とは異なり、熱拡散工程では、保護層130内に第2絶縁膜用キャップ層109の材料が拡散されない。したがって保護層130は、そのまま残存する。第2絶縁膜用キャップ層109の直下に位置するゲート電極用金属膜108には、図31と同様に、第2絶縁膜用キャップ層109の材料が拡散され、ゲート電極用金属膜108に第2絶縁膜用キャップ層109の材料が添加された元素添加金属層110を形成する。図33では、第2絶縁膜用キャップ層109の材料であるLaがゲート電極用金属膜108に拡散されて、Laが添加された元素添加金属層110が形成される。

【0139】

保護層130の材料が金属または不純物を添加したシリコンなどの導電性材料である場合は、熱拡散後、前述の第5の実施の形態と同様にして、nMOSFET領域Rnに残存する保護層130上およびpMOSFET領域Rpのゲート電極用金属膜108上に、poly−Si層113が堆積される。その後、ゲート電極を形成するための加工を行うと、nMOSFET領域Rnでは、n側ゲート電極として、poly−Si層113、保護層130および元素添加金属層110によって構成されるゲート電極が形成される。したがってnMOSFETは、poly−Si層113、保護層130、元素添加金属層110、第1元素添加絶縁層111、界面層105およびpウェル103から成るゲートスタック構造となる。この場合、保護層130は、導電性を有し、元素添加金属層110とは異なる材料で構成されており、上部導電層に相当する。

【0140】

保護層130の材料が絶縁材料である場合は、poly−Si層113の形成前に、元素添加保護層131は除去される。この場合、nMOSFETのn側ゲート電極は、poly−Si層113および元素添加金属層110によって構成され、nMOSFETは、poly−Si層113、元素添加金属層110、第1元素添加絶縁層111、界面層105およびpウェル103から成るゲートスタック構造となる。

【0141】

<第7の実施の形態>

次に、本発明の第7の実施の形態である半導体装置の製造方法について説明する。図34〜図37は、本発明の第7の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。本実施の形態においても、前述の第5の実施の形態と同様に、半導体装置として、CMOSFET220を製造する。図34は、拡散抑止層140の形成が終了した段階の状態を示す断面図である。図34〜図37では、理解を容易にするために、前述の図1〜図25に示したp型半導体層2については、記載を省略している。

【0142】

本実施の形態では、前述の第5の実施の形態と同様に、Si基板101上に、素子分離膜102、pウェル103およびnウェル104が形成された表面側から、全面にわたって界面層105、絶縁層106、第1絶縁膜用キャップ層107、ゲート電極用金属膜108を順次に形成した後、ゲート電極用金属膜108上全面に、拡散抑止層140を形成する。拡散抑止層140は、この後に堆積する第2絶縁膜用キャップ層109の材料がゲート電極用金属膜108に拡散することを抑制または防止する機能を有する。拡散抑止層140の材料は、本実施の形態では、前述のゲート電極用金属膜108と同一の材料である。拡散抑止層140の形成後は、エッチングによって、pMOSFET領域Rpの拡散抑止層140のみを残して、nMOSFET領域Rnの拡散抑止層140を除去する。

【0143】

図35は、第2絶縁膜用キャップ層109の形成が終了した段階の状態を示す断面図である。nMOSFET領域Rnの拡散抑止層140を除去した後は、nMOSFET領域Rnのゲート電極用金属膜108上およびpMOSFET領域Rpの拡散抑止層140上に、第2絶縁膜用キャップ層109を形成する。nMOSFET領域Rnにおける第2絶縁膜用キャップ層109と第1絶縁膜用キャップ層107との距離と、pMOSFET領域Rpにおける第2絶縁膜用キャップ層109と第1絶縁膜用キャップ層107との距離との関係、すなわちnMOSFET領域Rnにおけるゲート電極用金属膜108の厚み寸法と、pMOSFET領域Rpにおける拡散抑止層140およびゲート電極用金属膜108の合計の厚み寸法との関係は、たとえば、厚みが大きい方、すなわちpMOSFET領域Rp側が20nmであり、厚みが小さい方、すなわちnMOSFET領域Rn側が10nmとなるように選ばれる。

【0144】

図36は、元素添加金属層110上、ならびに元素未添加金属層142および元素添加金属層141上へのpoly−Si層113の形成が終了した段階の状態を示す断面図である。第2絶縁膜用キャップ層109の形成後は、各層が形成されたSi基板101に熱処理を施して、第1および第2絶縁膜用キャップ層107,109とともに、絶縁層106、ゲート電極用金属膜108および拡散抑止層140を熱処理する。これによって、第2絶縁膜用キャップ層109をゲート電極用金属膜108と反応させ、nMOSFET領域Rnに属するゲート電極用金属膜108内に、第2絶縁膜用キャップ層109の材料を拡散させることで、図36に示すように、nMOSFET領域Rnに、ゲート電極用金属膜108に第2絶縁膜用キャップ層109の材料が添加された元素添加金属層110を形成する。本実施の形態では、第2絶縁膜用キャップ層109の材料であるLaがゲート電極用金属膜108に拡散されて、Laが添加された元素添加金属層110が形成される。

【0145】

また第2絶縁膜用キャップ層109の材料は、前述の第5の実施の形態と同様に、第2絶縁膜用キャップ層109の下方に位置する絶縁層106、すなわちnMOSFET領域Rnに属する絶縁層106中にも拡散される。また第1絶縁膜用キャップ層107の材料は、第1絶縁膜用キャップ層107の直下に位置する絶縁層106、すなわちnMOSFET領域RnおよびpMOSFET領域Rpに属する絶縁層106に拡散される。これによって、nMOSFET領域Rnに属する絶縁層106は、第1および第2絶縁膜用キャップ層107,109の材料が添加されて第1元素添加絶縁層111となる。本実施の形態では、絶縁層106はHfSiONであるので、第1元素添加絶縁層111として、第1絶縁膜用キャップ層107の材料であるAlと第2絶縁膜用キャップ層109の材料であるLaとが添加されたHfSiON層が形成される。

【0146】

pMOSFET領域Rpでは、pMOSFET領域Rpに属する拡散抑止層140内に、第2絶縁膜用キャップ層109の材料が拡散され、さらに拡散抑止層140の直下に位置するゲート電極用金属膜108のうち、拡散抑止層140寄りの一部分に、第2絶縁膜用キャップ層109の材料が拡散される。これによって、pMOSFET領域Rpには、図36に示すように、拡散抑止層140とゲート電極用金属膜108の一部とに第2絶縁膜用キャップ層109の材料であるLaが添加されて成る元素添加金属層141が形成される。また、ゲート電極用金属膜108のうち、第2絶縁膜用キャップ層109の材料が添加された部分を除く残余の部分は、第2絶縁膜用キャップ層109の材料が添加されていない元素未添加金属層142となる。

【0147】

元素未添加金属層142は、電極用導電層に相当する。また元素添加金属層141のうち、ゲート電極用金属膜108の一部に第2絶縁膜用キャップ層109の材料が添加されて成る部分が、第2元素添加導電層に相当し、拡散抑止層140に第2絶縁膜用キャップ層109の材料が添加されて成る部分が、もう一つの第2元素添加導電層に相当する。本実施の形態では、拡散抑止層140とゲート電極用金属膜108とは、同一の材料で構成されるので、拡散抑止層140とゲート電極用金属膜108の一部とが一体化して、前述の元素添加金属層141が形成される。

【0148】

pMOSFET領域Rpに属する絶縁層106は、前述の第5の実施の形態と同様に、第1絶縁膜用キャップ層107の材料が添加されて、第2元素添加絶縁層112となる。本実施の形態では、絶縁層106はHfSiON層であるので、第2元素添加絶縁層112として、第1絶縁膜用キャップ層107の材料であるAlが添加されたHfSiON層が形成される。

【0149】

本実施の形態においても、前述の第5の実施の形態と同様に、第1および第2絶縁膜用キャップ層107,109は、拡散させるべき量の材料によって形成されるので、熱処理によって消失する。これによって、nMOSFET領域Rnでは、前述の第5の実施の形態と同様に、元素添加金属層110が露出し、第1元素添加絶縁層111の直上に元素添加金属層110が形成された状態となる。pMOSFET領域Rpでは、第2元素添加絶縁層112の直上に元素未添加金属層142が形成された状態となる。また本実施の形態では、拡散抑止層140とゲート電極用金属膜108とは、同一の材料で構成されるので、pMOSFET領域Rpでは、拡散抑止層140とゲート電極用金属膜108の一部とが一体化して、前述の元素添加金属層141が形成される。

【0150】

その後、図36に示すように、poly−Si層113を、30nm〜120nmの範囲内で、元素添加金属層110上および元素添加金属層141上に堆積する。本実施の形態でも、前述の第5の実施の形態と同様に、poly−Si層113の形成前に、熱処理工程を行うことが好ましい。

【0151】

図37は、CMOSFET220形成が終了した段階の状態を示す断面図である。図36のpoly−Si層113の形成後は、前述の第5の実施の形態と同様に、ドライエッチング法などによって、nMOSFET120およびpMOSFET121Aの各ゲート電極を形成するための加工を行う。具体的には、ゲート電極の部分とその下層が残存するように、ゲート電極となるpoly−Si層113、元素添加金属層110、元素添加金属層141および元素未添加金属層142ならびにその下層の第1元素添加絶縁層111、第2元素添加絶縁層112および界面層105をエッチングする。

【0152】

本実施の形態において、nMOSFET120は、図28に示す第5の実施の形態と同様に、poly−Si層113、元素添加金属層110、第1元素添加絶縁層111、界面層105およびpウェル103から成るゲートスタック構造となる。

【0153】

またpMOSFET121Aのp側ゲート電極115Aは、poly−Si層113、元素添加金属層141および元素未添加金属層142によって構成され、p側ゲート絶縁膜117は、図28に示す第5の実施の形態と同様に、界面層105および第2元素添加絶縁層112によって構成される。したがってpMOSFET121Aは、poly−Si層113、元素添加金属層141、元素未添加金属層142、第2元素添加絶縁層112、界面層105およびnウェル104から成るゲートスタック構造となる。

【0154】

n側ゲート電極114およびp側ゲート電極115Aの形成後は、前述の第5の実施の形態と同様に、通常のCMOSFET形成プロセスフローを順次に経ることによって、nMOSFET120およびpMOSFET121Aを形成し、CMOSFET220を形成する。具体的には、nMOSFET領域Rnにおいて、n側ゲート電極114およびn側ゲート絶縁膜116の両側壁に、たとえばSiO2から成るサイドウォールスペーサ118を形成する。またpMOSFET領域Rpにおいて、p側ゲート電極115Aおよびp側ゲート絶縁膜117の両側壁に、たとえばSiO2から成るサイドウォールスペーサ118を形成する。その後、イオン打込みなどによってソースドレイン領域119を形成することによって、CMOSFET220が形成される。

【0155】

このようにして形成される本実施の形態のCMOSFET220において、nMOSFET120のn側ゲート電極114の実効仕事関数は、4.0eV〜4.3eVであり、pMOSFET121Aのp側ゲート電極115Aの実効仕事関数は、4.9eV〜5.2eVである。ゲート電極の実効仕事関数は、得られたnMOSFET120およびpMOSFET121AにおけるMOS型キャパシタのC−V特性、すなわち容量−ゲート電圧特性から求められるフラットバンド電圧から求められる。

【0156】

本実施の形態によれば、nMOSFET領域RnおよびpMOSFET領域RpのSi基板101上に界面層105および絶縁層106が順次形成され、この絶縁層106上に第1絶縁膜用キャップ層107およびゲート電極用金属膜108が順次形成される。形成されたゲート電極用金属膜108のうち、pMOSFET領域Rpのゲート電極用金属膜108上に拡散抑止層140が形成され、この拡散抑止層140上およびnMOSFET領域Rnのゲート電極用金属膜108上に、第2絶縁膜用キャップ層109が形成される。形成された第1絶縁膜用キャップ層107および第2絶縁膜用キャップ層109とともに、絶縁層106、ゲート電極用金属膜108および拡散抑止層140が熱処理される。この熱処理によって、第1絶縁膜用キャップ層107に含有されるAlを、第1絶縁膜用キャップ層107の下方の絶縁層106に拡散させることができる。またnMOSFET領域Rnでは、第2絶縁膜用キャップ層109に含有されるLaを、第2絶縁膜用キャップ層109の下方のゲート電極用金属膜108に拡散させ、さらにゲート電極用金属膜108の下方の絶縁層106に拡散させることができる。

【0157】

pMOSFET領域Rpでは、第2絶縁膜用キャップ層109は拡散抑止層140上に形成されるので、拡散抑止層140によって、ゲート電極用金属膜108および絶縁層106へのLaの拡散を抑制または防止することができる。これによって、nMOSFET領域Rnでは、AlおよびLaを含有する絶縁層106を形成し、pMOSFET領域Rpでは、Alを含有する絶縁層106を形成することができるので、nMOSFET120の閾値電圧およびpMOSFET121Aの閾値電圧をそれぞれ制御することができる。したがって、閾値電圧の制御範囲を広げることができる。

【0158】

また第2絶縁膜用キャップ層109は、ゲート電極用金属膜108上に形成されており、第2絶縁膜用キャップ層109と絶縁層106との間にはゲート電極用金属膜108が介在するので、nMOSFET領域Rnに第2絶縁膜用キャップ層109を形成するために、たとえば第2絶縁膜用キャップ層109をnMOSFET領域RnとpMOSFET領域Rpとにわたって形成した後、pMOSFET領域Rpの第2絶縁膜用キャップ層109を除去するときに、絶縁層106が劣化することを防ぐことができる。これによって、劣化による絶縁層106の信頼性の低下を防止し、n側ゲート絶縁膜116およびp側ゲート絶縁膜117の信頼性の低下を防止することができる。したがって、絶縁層106の信頼性の低下、ひいてはn側ゲート絶縁膜116およびp側ゲート絶縁膜117の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。

【0159】

以上のように本実施の形態によれば、nMOSFET120およびpMOSFET121Aがそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置220を容易に製造することができる。

【0160】

以上のようにして形成される本実施の形態のnMOSFET120は、第1元素添加絶縁層111に第1の元素であるAlおよび第2の元素であるLaを含有し、この第1元素添加絶縁層111上の元素添加金属層110に第2の元素であるLaを含有する。またpMOSFET121Aは、第2元素添加絶縁層112に第1の元素であるAlを含有し、この第2元素添加絶縁層112上に第1の元素であるAlおよび第2の元素であるLaが添加されていない元素未添加金属層142を備え、この元素未添加金属層142上の第2元素添加導電層および、もう一つの第2元素添加導電層である元素添加金属層141に第2の元素であるLaを含有する。

【0161】

これによって、それぞれに適した実効仕事関数を有するゲート電極114,115Aを備えるnMOSFET120およびpMOSFET121Aを実現することができる。具体的には、nMOSFET120におけるn側ゲート電極114の実効仕事関数を4.0eV〜4.3eVとし、pMOSFET121Aにおけるp側ゲート電極115Aの実効仕事関数を4.9eV〜5.2eVすることができる。したがって、それぞれに適した閾値電圧を有するnMOSFET120およびpMOSFET121Aを実現することが可能である。

【0162】

また第1および第2元素添加絶縁層111,112は、第1および第2元素添加絶縁層111,112となるゲート絶縁膜用絶縁層106上でエッチングを実施することなく形成することが可能であるので、製造過程における劣化が防止され、信頼性の低下が防止される。したがって、nMOSFET120およびpMOSFET121Aがそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置220を実現することが可能である。

【0163】

<第8の実施の形態>

次に、本発明の第8の実施の形態である半導体装置の製造方法について説明する。図38〜図41は、本発明の第8の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。本実施の形態においても、前述の第5の実施の形態と同様に、半導体装置として、CMOSFET230を製造する。図38は、nMOSFET領域Rnの第1絶縁膜用キャップ層107の一部を除去した段階の状態を示す断面図である。図38〜図41では、理解を容易にするために、前述の図1〜図25に示したp型半導体層2については、記載を省略している。

【0164】

本実施の形態では、前述の第5の実施の形態と同様にして、Si基板101上に、素子分離膜102、pウェル103およびnウェル104が形成された表面側から、全面にわたって界面層105、絶縁層106、第1絶縁膜用キャップ層107、ゲート電極用金属膜108Aを順次に形成した後、nMOSFET領域Rnの全体にわたって、ゲート電極用金属膜108Aの一部を、エッチバックなどによって厚み方向に除去する。

【0165】

図39は、第2絶縁膜用キャップ層109の形成が終了した段階の状態を示す断面図である。nMOSFET領域Rnのゲート電極用金属膜108Aの一部を除去した後は、nMOSFET領域RnおよびpMOSFET領域Rpのゲート電極用金属膜108A上に、第2絶縁膜用キャップ層109を形成する。

【0166】

図40は、nMOSFET領域RnおよびpMOSFET領域Rpの元素添加金属層110上へのpoly−Si層113の形成が終了した段階の状態を示す断面図である。第2絶縁膜用キャップ層109の形成後は、熱処理を施して、第2絶縁膜用キャップ層109をゲート電極用金属膜108Aと反応させ、nMOSFET領域Rnに属するゲート電極用金属膜108A内に、第2絶縁膜用キャップ層109の材料を拡散させることで、図40に示すように、nMOSFET領域Rnに、ゲート電極用金属膜108Aに第2絶縁膜用キャップ層109の材料が添加された元素添加金属層110を形成する。本実施の形態では、第2絶縁膜用キャップ層109の材料であるLaがゲート電極用金属膜108Aに拡散されて、Laが添加された元素添加金属層110が形成される。元素添加金属層110は、第1元素添加金属層に相当する。

【0167】

また第2絶縁膜用キャップ層109の材料は、前述の第5の実施の形態と同様に、第2絶縁膜用キャップ層109の下方に位置する絶縁層106、すなわちnMOSFET領域Rnに属する絶縁層106中にも拡散される。また第1絶縁膜用キャップ層107の材料は、第1絶縁膜用キャップ層107の直下に位置する絶縁層106、すなわちnMOSFET領域RnおよびpMOSFET領域Rpに属する絶縁層106に拡散される。これによって、nMOSFET領域Rnに属する絶縁層106は、第1および第2絶縁膜用キャップ層107,109の材料が添加されて第1元素添加絶縁層111となる。本実施の形態では、絶縁層106はHfSiONであるので、第1元素添加絶縁層111として、第1絶縁膜用キャップ層107の材料であるAlと第2絶縁膜用キャップ層109の材料であるLaとが添加されたHfSiON層が形成される。

【0168】

pMOSFET領域Rpでは、第2絶縁膜用キャップ層109の直下に位置するゲート電極用金属膜108Aのうち、第2絶縁膜用キャップ層109寄りの一部分に、第2絶縁膜用キャップ層109の材料が拡散される。これによって、pMOSFET領域Rpには、図40に示すように、ゲート電極用金属膜108Aの一部に第2絶縁膜用キャップ層109の材料であるLaが添加されて成る元素添加金属層110が形成される。また、ゲート電極用金属膜108Aのうち、第2絶縁膜用キャップ層109の材料が添加された部分を除く残余の部分は、第2絶縁膜用キャップ層109の材料が添加されていない元素未添加金属層142となる。元素添加金属層110は、第2元素添加導電層に相当し、元素未添加金属層142は、電極用導電層に相当する。

【0169】

pMOSFET領域Rpに属する絶縁層106は、前述の第5の実施の形態と同様に、第1絶縁膜用キャップ層107の材料が添加されて、第2元素添加絶縁層112となる。本実施の形態では、絶縁層106はHfSiON層であるので、第2元素添加絶縁層112として、第1絶縁膜用キャップ層107の材料であるAlが添加されたHfSiON層が形成される。

【0170】

本実施の形態においても、前述の第5の実施の形態と同様に、第1および第2絶縁膜用キャップ層107,109は、拡散させるべき量の材料によって形成されるので、熱処理によって消失する。これによって、nMOSFET領域Rnでは、元素添加金属層110が露出し、第1元素添加絶縁層111の直上に元素添加金属層110が形成された状態となる。pMOSFET領域Rpでは、元素添加金属層110が露出し、第2元素添加絶縁層112の直上に元素未添加金属層142が形成された状態となる。

【0171】

その後、図40に示すように、poly−Si層113を、30nm〜120nmの範囲内で、nMOSFET領域RnおよびpMOSFET領域Rpの元素添加金属層110上に堆積する。本実施の形態でも、前述の第5の実施の形態と同様に、poly−Si層113の形成前に、熱処理工程を行うことが好ましい。

【0172】

図41は、CMOSFET230形成が終了した段階の状態を示す断面図である。図40のpoly−Si層113の形成後は、前述の第5の実施の形態と同様に、ドライエッチング法などによって、nMOSFET120およびpMOSFET121Bの各ゲート電極を形成するための加工を行う。具体的には、ゲート電極の部分とその下層が残存するように、ゲート電極となるpoly−Si層113、元素添加金属層110、および元素未添加金属層142ならびにその下層の第1元素添加絶縁層111、第2元素添加絶縁層112および界面層105をエッチングする。

【0173】

本実施の形態において、nMOSFET120は、図28に示す第5の実施の形態と同様に、poly−Si層113、元素添加金属層110、第1元素添加絶縁層111、界面層105およびpウェル103から成るゲートスタック構造となる。

【0174】

またpMOSFET121Bのp側ゲート電極115Bは、poly−Si層113、元素添加金属層110および元素未添加金属層142によって構成され、p側ゲート絶縁膜117は、図28に示す第5の実施の形態と同様に、界面層105および第2元素添加絶縁層112によって構成される。したがってpMOSFET121Bは、poly−Si層113、元素添加金属層110、元素未添加金属層142、第2元素添加絶縁層112、界面層105およびnウェル104から成るゲートスタック構造となる。

【0175】

n側ゲート電極114およびp側ゲート電極115Bの形成後は、前述の第5の実施の形態と同様に、通常のCMOSFET形成プロセスフローを順次に経ることによって、nMOSFET120およびpMOSFET121Bを形成し、CMOSFET230を形成する。具体的には、nMOSFET領域Rnにおいて、n側ゲート電極114およびn側ゲート絶縁膜116の両側壁に、たとえばSiO2から成るサイドウォールスペーサ118を形成する。またpMOSFET領域Rpにおいて、p側ゲート電極115Bおよびp側ゲート絶縁膜117の両側壁に、たとえばSiO2から成るサイドウォールスペーサ118を形成する。その後、イオン打込みなどによってソースドレイン領域119を形成することによって、CMOSFET230が形成される。

【0176】

このようにして形成される本実施の形態のCMOSFET230において、nMOSFET120のn側ゲート電極114の実効仕事関数は、4.0eV〜4.3eVであり、pMOSFET121Bのp側ゲート電極115Bの実効仕事関数は、4.9eV〜5.2eVである。ゲート電極の実効仕事関数は、得られたnMOSFET120およびpMOSFET121BにおけるMOS型キャパシタのC−V特性、すなわち容量−ゲート電圧特性から求められるフラットバンド電圧から求められる。

【0177】

本実施の形態によれば、nMOSFET領域RnおよびpMOSFET領域RpのSi基板101上に界面層105および絶縁層106が順次形成され、この絶縁層106上に第1絶縁膜用キャップ層107およびゲート電極用金属膜108が順次形成される。ゲート電極用金属膜108は、pMOSFET領域Rpにおける厚み寸法の方がnMOSFET領域Rnにおける厚み寸法よりも大きく形成される。このゲート電極用金属膜108上に、nMOSFET領域RnおよびpMOSFET領域Rpにわたって、第2絶縁膜用キャップ層109が形成される。形成された第1絶縁膜用キャップ層107および第2絶縁膜用キャップ層109とともに、絶縁層106およびゲート電極用金属膜108が熱処理される。この熱処理によって、第1絶縁膜用キャップ層107に含有される第1の元素、具体的にはAlを、第1絶縁膜用キャップ層107の下方の絶縁層106に拡散させることができる。また第2絶縁膜用キャップ層109に含有される第2の元素、具体的にはLaを、第2絶縁膜用キャップ層109の下方のゲート電極用金属膜108に拡散させ、さらにゲート電極用金属膜108の下方の絶縁層106に拡散させることが可能である。

【0178】

ゲート電極用金属膜108は、pMOSFET領域Rpにおける厚み寸法の方が、nMOSFET領域Rnにおける厚み寸法よりも大きいので、pMOSFET領域Rpでは、nMOSFET領域Rnに比べて、ゲート電極用金属膜108および絶縁層106へのLaの拡散を抑制することができる。たとえば、Laを、pMOSFET領域Rpでは絶縁層106まで拡散させ、nMOSFET領域Rnでは絶縁層106までは拡散しないようにすることができる。これによって、nMOSFET領域Rnでは、AlおよびLaを含有する絶縁層106を形成し、pMOSFET領域Rpでは、Alを含有する絶縁層106を形成することができるので、nMOSFET120の閾値電圧およびpMOSFET121Bの閾値電圧をそれぞれ制御することができる。これによって、閾値電圧の制御範囲を広げることができる。

【0179】

また第2絶縁膜用キャップ層109は、ゲート電極用金属膜108上に形成されており、第2絶縁膜用キャップ層109と絶縁層106との間にはゲート電極用金属膜108が介在するので、第2絶縁膜用キャップ層109を形成するときに絶縁層106が劣化することを防ぐことができる。これによって、劣化による絶縁層106の信頼性の低下を防止することができる。したがって、絶縁層106の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。

【0180】

以上のように本実施の形態によれば、nMOSFET120およびpMOSFET121Bがそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置230を容易に製造することができる。

【0181】

以上のようにして形成される本実施の形態のnMOSFET120は、第1元素添加絶縁層111に第1の元素であるAlおよび第2の元素であるLaを含有し、この第1元素添加絶縁層111上の元素添加金属層110に第2の元素であるLaを含有する。またpMOSFET121Bは、第2元素添加絶縁層112に第1の元素であるAlを含有し、この第2元素添加絶縁層112上に第1の元素であるAlおよび第2の元素であるLaが添加されていない元素未添加金属層142を備え、この元素未添加金属層142上の元素添加金属層110に第2の元素であるLaを含有する。

【0182】

これによって、それぞれに適した実効仕事関数を有するゲート電極114,115Bを備えるnMOSFET120およびpMOSFET121Bを実現することができる。具体的には、nMOSFET120におけるn側ゲート電極114の実効仕事関数を4.0eV〜4.3eVとし、pMOSFET121Bにおけるp側ゲート電極115Bの実効仕事関数を4.9eV〜5.2eVすることができる。したがって、それぞれに適した閾値電圧を有するnMOSFET120およびpMOSFET121Bを実現することが可能である。

【0183】

また第1および第2元素添加絶縁層111,112は、第1および第2元素添加絶縁層111,112となるゲート絶縁膜用絶縁層106上でエッチングを実施することなく形成することが可能であるので、製造過程における劣化が防止され、信頼性の低下が防止される。したがって、nMOSFET120およびpMOSFET121Bがそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置230を実現することが可能である。

【0184】

<第9の実施の形態>

次に、本発明の第9の実施の形態である半導体装置の製造方法について説明する。図42〜図46は、本発明の第9の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。本実施の形態においても、前述の第5の実施の形態と同様に、半導体装置として、CMOSFET240を製造する。図42は、拡散抑止層140Aの形成が終了した段階の状態を示す断面図である。図42〜図46では、理解を容易にするために、前述の図1〜図25に示したp型半導体層2については、記載を省略している。

【0185】

本実施の形態では、前述の第5の実施の形態と同様に、Si基板101上に、素子分離膜102、pウェル103およびnウェル104が形成された表面側から、全面にわたって界面層105、絶縁層106、第1絶縁膜用キャップ層107、ゲート電極用金属膜108を順次に形成した後、ゲート電極用金属膜108上全面に、拡散抑止層140Aを形成する。拡散抑止層140Aは、この後に堆積する第2絶縁膜用キャップ層109の材料がゲート電極用金属膜108に拡散することを抑止する機能を有する。拡散抑止層140Aは、本実施の形態では、第2絶縁膜用キャップ層109の材料の拡散を抑止するように形成される。

【0186】

拡散抑止層140Aの材料は、本実施の形態では、前述のゲート電極用金属膜108と異なる材料である。拡散抑止層140Aが第2絶縁膜用キャップ層109の材料を拡散可能か否かは、拡散抑止層140Aの材料を構成する元素だけでなく、拡散抑止層140Aの成膜条件などによっても変化する。したがって、前述の「ゲート電極用金属膜108と異なる材料」とは、ゲート電極用金属膜108の材料と構成する元素が異なる場合だけでなく、ゲート電極用金属膜108の材料と構成する元素が同じであるが、成膜条件などが異なり、層の性質が異なる場合も含む。本実施の形態において、拡散抑止層140Aは、TiNによって構成される。拡散抑止層140Aの形成後は、エッチングによって、pMOSFET領域Rpの拡散抑止層140Aのみを残して、nMOSFET領域Rnの拡散抑止層140Aを除去する。

【0187】

図43は、第2絶縁膜用キャップ層109の形成が終了した段階の状態を示す断面図である。nMOSFET領域Rnの拡散抑止層140Aを除去した後は、nMOSFET領域Rnのゲート電極用金属膜108上およびpMOSFET領域Rpの拡散抑止層140A上に、第2絶縁膜用キャップ層109を形成する。

【0188】

図44は、pMOSFET領域Rpの第2絶縁膜用キャップ層109を除去する段階の状態を示す断面図である。第2絶縁膜用キャップ層109の形成後は、熱処理を施して、第2絶縁膜用キャップ層109をゲート電極用金属膜108と反応させ、nMOSFET領域Rnに属するゲート電極用金属膜108内に、第2絶縁膜用キャップ層109の材料を拡散させることで、図44に示すように、nMOSFET領域Rnに、ゲート電極用金属膜108に第2絶縁膜用キャップ層109の材料が添加された元素添加金属層110を形成する。本実施の形態では、第2絶縁膜用キャップ層109の材料であるLaがゲート電極用金属膜108に拡散されて、Laが添加された元素添加金属層110が形成される。

【0189】

また第2絶縁膜用キャップ層109の材料は、前述の第5の実施の形態と同様に、第2絶縁膜用キャップ層109の下方に位置する絶縁層106、すなわちnMOSFET領域Rnに属する絶縁層106中にも拡散される。また第1絶縁膜用キャップ層107の材料は、第1絶縁膜用キャップ層107の直下に位置する絶縁層106、すなわちnMOSFET領域RnおよびpMOSFET領域Rpに属する絶縁層106に拡散される。これによって、nMOSFET領域Rnに属する絶縁層106は、第1および第2絶縁膜用キャップ層107,109の材料が添加されて第1元素添加絶縁層111となる。本実施の形態では、絶縁層106はHfSiONであるので、第1元素添加絶縁層111として、第1絶縁膜用キャップ層107の材料であるAlと第2絶縁膜用キャップ層109の材料であるLaとが添加されたHfSiON層が形成される。

【0190】

pMOSFET領域Rpでは、第2絶縁膜用キャップ層109の材料と、拡散抑止層140Aとが反応しないので、第2絶縁膜用キャップ層109の材料は、pMOSFET領域Rpに属する拡散抑止層140A内に拡散されない。その結果、pMOSFET領域Rpにおいて、第2絶縁膜用キャップ層109の材料は、ゲート電極用金属膜108内にも拡散されない。したがってpMOSFET領域Rpでは、熱処理後においても、図44に示すように、拡散抑止層140Aとゲート電極用金属膜108とがそのまま残存する。この残存するゲート電極用金属膜108が、電極用導電層に相当する。拡散抑止層140Aは、ゲート電極用金属膜108とは異なる材料で構成されており、上部導電層に相当する。

【0191】

また、pMOSFET領域Rpに属する絶縁層106は、前述の第5の実施の形態と同様に、第1絶縁膜用キャップ層107の材料が添加されて、第2元素添加絶縁層112となる。本実施の形態では、絶縁層106はHfSiON層であるので、第2元素添加絶縁層112として、第1絶縁膜用キャップ層107の材料であるAlが添加されたHfSiON層が形成される。

【0192】

本実施の形態においても、前述の第5の実施の形態と同様に、第1および第2絶縁膜用キャップ層107,109は、拡散させるべき量の材料によって形成されるので、第1絶縁膜用キャップ層107は、熱処理によって消失する。第2絶縁膜用キャップ層109も、nMOSFET領域Rnでは消失する。pMOSFET領域Rpでは、第2絶縁膜用キャップ層109は拡散抑止層140上に形成されており、この拡散抑止層140Aは、本実施の形態では、第2絶縁膜用キャップ層109の材料の拡散を阻止するように形成されている。したがって、pMOSFET領域Rpでは、第2絶縁膜用キャップ層109が残存する。元素添加金属層110、第1および第2元素添加絶縁層111,112の形成後は、pMOSFET領域Rpの第2絶縁膜用キャップ層109を、ウェットエッチングなどによって除去する。

【0193】

図45は、拡散抑止層140A上および元素添加金属層110上へのpoly−Si層113の形成が終了した段階の状態を示す断面図である。pMOSFET領域Rpの第2絶縁膜用キャップ層109を除去した後は、図45に示すように、poly−Si層113を、30nm〜120nmの範囲内で、拡散抑止層140A上および元素添加金属層110上に堆積する。本実施の形態でも、前述の第5の実施の形態と同様に、poly−Si層113の形成前に、熱処理工程を行うことが好ましい。

【0194】

図46は、CMOSFET240形成が終了した段階の状態を示す断面図である。図45のpoly−Si層113の形成後は、前述の第5の実施の形態と同様に、ドライエッチング法などによって、nMOSFET120およびpMOSFET121Cの各ゲート電極を形成するための加工を行う。具体的には、ゲート電極の部分とその下層が残存するように、ゲート電極となるpoly−Si層113、元素添加金属層110、拡散抑止層140Aおよびゲート電極用金属膜108ならびにその下層の第1元素添加絶縁層111、第2元素添加絶縁層112および界面層105をエッチングする。

【0195】

本実施の形態において、nMOSFET120は、図28に示す第5の実施の形態と同様に、poly−Si層113、元素添加金属層110、第1元素添加絶縁層111、界面層105およびpウェル103から成るゲートスタック構造となる。

【0196】

またpMOSFET121Cのp側ゲート電極115Cは、poly−Si層113、拡散抑止層140Aおよびゲート電極用金属膜108によって構成され、p側ゲート絶縁膜117は、図28に示す第5の実施の形態と同様に、界面層105および第2元素添加絶縁層112によって構成される。したがってpMOSFET121Cは、poly−Si層113、拡散抑止層140A、ゲート電極用金属膜108、第2元素添加絶縁層112、界面層105およびnウェル104から成るゲートスタック構造となる。

【0197】

n側ゲート電極114およびp側ゲート電極115Cの形成後は、前述の第5の実施の形態と同様に、通常のCMOSFET形成プロセスフローを順次に経ることによって、nMOSFET120およびpMOSFET121Cを形成し、CMOSFET240を形成する。具体的には、nMOSFET領域Rnにおいて、n側ゲート電極114およびn側ゲート絶縁膜116の両側壁に、たとえばSiO2から成るサイドウォールスペーサ118を形成する。またpMOSFET領域Rpにおいて、p側ゲート電極115Cおよびp側ゲート絶縁膜117の両側壁に、たとえばSiO2から成るサイドウォールスペーサ118を形成する。その後、イオン打込みなどによってソースドレイン領域119を形成することによって、CMOSFET240が形成される。

【0198】

このようにして形成される本実施の形態のCMOSFET240において、nMOSFET120のn側ゲート電極114の実効仕事関数は、4.0eV〜4.3eVであり、pMOSFET121Cのp側ゲート電極115Cの実効仕事関数は、4.9eV〜5.2eVである。ゲート電極の実効仕事関数は、得られたnMOSFET120およびpMOSFET121CにおけるMOS型キャパシタのC−V特性、すなわち容量−ゲート電圧特性から求められるフラットバンド電圧から求められる。

【0199】

本実施の形態では、拡散抑止層140Aは、第2絶縁膜用キャップ層109の材料の拡散を防止するように形成される。本実施の形態のように、第2絶縁膜用キャップ層109が、たとえばLa酸化物などの希土類材料から成る場合、第2絶縁膜用キャップ層109は、潮解性を有するので、nMOSFET領域RnおよびpMOSFET領域Rpにわたって形成した後、片側領域のみを除去する方法で、一方の領域のみに第2絶縁膜用キャップ層109を形成することは困難である。

【0200】

本実施の形態では、拡散抑止層140Aを形成することによって、pMOSFET領域Rpの第2絶縁膜用キャップ層109を除去することなく、pMOSFET領域Rpにおける第2絶縁膜用キャップ層109の材料の拡散を防止することができる。したがって、第2絶縁膜用キャップ層109の片側領域を除去する工程を省くことができるので、製造フローを簡略化することができる。また片側領域の除去による第2絶縁膜用キャップ層109の劣化が無くなるので、その後の熱処理のときに、第2絶縁膜用キャップ層109の材料をnMOSFET領域Rnのゲート電極用金属膜108および絶縁層106に、より確実に拡散させることができる。これによって、nMOSFET120の閾値電圧を、より確実に所望の値に制御することができる。

【0201】

以上のようにして形成される本実施の形態のnMOSFET120は、第1元素添加絶縁層111に第1の元素であるAlおよび第2の元素であるLaを含有し、この第1元素添加絶縁層111上のnMOSFET領域Rnのゲート電極用金属膜108に第2の元素であるLaを含有する。またpMOSFET121Cは、第2元素添加絶縁層112に第1の元素であるAlを含有し、この第2元素添加絶縁層112上に第1の元素であるAlおよび第2の元素であるLaが添加されていないゲート電極用金属膜108を備え、このゲート電極用金属膜108上にゲート電極用金属膜108とは異なる材料から成る拡散抑止層140Aを備える。

【0202】

これによって、それぞれに適した実効仕事関数を有するゲート電極114,115Cを備えるnMOSFET120およびpMOSFET121Cを実現することができる。具体的には、nMOSFET120におけるn側ゲート電極114の実効仕事関数を4.0eV〜4.3eVとし、pMOSFET121Cにおけるp側ゲート電極115Cの実効仕事関数を4.9eV〜5.2eVすることができる。したがって、それぞれに適した閾値電圧を有するnMOSFET120およびpMOSFET121Cを実現することが可能である。

【0203】

また第1および第2元素添加絶縁層111,112は、第1および第2元素添加絶縁層111,112となるゲート絶縁膜用絶縁層106上でエッチングを実施することなく形成することが可能であるので、製造過程における劣化が防止され、信頼性の低下が防止される。したがって、nMOSFET120およびpMOSFET121Cがそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置240を実現することが可能である。

【0204】

<第10の実施の形態>

次に、本発明の第10の実施の形態である半導体装置の製造方法について説明する。図47〜図49は、本発明の第10の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。本実施の形態においても、前述の第5の実施の形態と同様に、半導体装置として、CMOSFET250を製造する。図47〜図49では、理解を容易にするために、前述の図1〜図25に示したp型半導体層2については、記載を省略している。

【0205】

図47は、熱処理が終了した段階の状態を示す断面図である。まず、前述の第5の実施の形態と同様にして、Si基板101に素子分離膜102、pウェル103およびnウェル104を形成し、さらにSi基板101上に界面層105、絶縁層106、第1絶縁膜用キャップ層107、ゲート電極用金属膜108および第2絶縁膜用キャップ層109を順次に形成した後、熱処理を施す。これによって、図47に示すように、nMOSFET領域Rnでは、第2絶縁膜用キャップ層109に含有される元素がゲート電極用金属膜108に添加されて元素添加金属層110が形成されるとともに、第1絶縁膜用キャップ層107に含有される元素および第2絶縁膜用キャップ層109に含有される元素が絶縁層106に添加されて第1元素添加絶縁層111が形成される。またpMOSFET領域Rpでは、第1絶縁膜用キャップ層107に含有される元素が絶縁層106に添加されて、第2元素添加絶縁層112が形成される。

【0206】

図48は、ゲート電極用金属膜108上および元素添加金属層110上への第2ゲート電極用金属膜150およびpoly−Si層113の形成が終了した段階の状態を示す断面図である。熱処理後、本実施の形態では、poly−Si層113を形成する前に、第2ゲート電極用金属膜150を、ゲート電極用金属膜108上および元素添加金属層110上に堆積する。第2ゲート電極用金属膜150は、第2金属膜に相当し、前述の第4の実施の形態における第2ゲート電極用金属膜Nに相当する。第2ゲート電極用金属膜150の膜厚、すなわち厚み寸法は、3nm以上20nm以下であることが好ましい。

【0207】

第2ゲート電極用金属膜150は、導電性材料から成る。第2ゲート電極用金属膜150の材料は、ゲート電極用金属膜108と同一材料でもよいし、異なる材料でもよい。本実施の形態では、第2ゲート電極用金属膜150とゲート電極用金属膜108とは、同一の材料、具体的にはTiNで構成される。第2ゲート電極用金属膜150を構成する導電性材料としては、TiNに限らず、ゲート電極用金属膜108を構成する導電性材料と同様のものが挙げられる。第2ゲート電極用金属膜150の形成後は、poly−Si層113を、30nm〜120nmの範囲内で、第2ゲート電極用金属膜150上に堆積する。

【0208】

図49は、CMOSFET250の形成が終了した段階の状態を示す断面図である。図48のpoly−Si層113の形成後は、前述の第5の実施の形態と同様に、ドライエッチング法などによって、nMOSFET120BおよびpMOSFET121Dの各ゲート電極を形成するための加工を行う。具体的には、ゲート電極の部分とその下層が残存するように、ゲート電極となるpoly−Si層113、第2ゲート電極用金属膜150、元素添加金属層110およびゲート電極用金属膜108、ならびにその下層の第1元素添加絶縁層111、第2元素添加絶縁層112および界面層105をエッチングする。

【0209】

本実施の形態において、nMOSFET120Bのn側ゲート電極114Bは、poly−Si層113、第2ゲート電極用金属膜150および元素添加金属層110によって構成され、n側ゲート絶縁膜116は、図28に示す第5の実施の形態と同様に、界面層105および第1元素添加絶縁層111によって構成される。したがってnMOSFET120Bは、poly−Si層113、第2ゲート電極用金属膜150、元素添加金属層110、第1元素添加絶縁層111、界面層105およびpウェル103から成るゲートスタック構造となる。

【0210】

またpMOSFET121Dのp側ゲート電極115Dは、poly−Si層113、第2ゲート電極用金属膜150およびゲート電極用金属膜108によって構成され、p側ゲート絶縁膜117は、図28に示す第5の実施の形態と同様に、界面層105および第2元素添加絶縁層112によって構成される。したがってpMOSFET121Dは、poly−Si層113、第2ゲート電極用金属膜150、ゲート電極用金属膜108、第2元素添加絶縁層112、界面層105およびnウェル104から成るゲートスタック構造となる。

【0211】

n側ゲート電極114Bおよびp側ゲート電極115Dの形成後は、前述の第5の実施の形態と同様に、通常のCMOSFET形成プロセスフローを順次に経ることによって、nMOSFET120BおよびpMOSFET121Dを形成し、CMOSFET250を形成する。

【0212】

このようにして形成される本実施の形態のCMOSFET250において、nMOSFET120Bのn側ゲート電極114Bの実効仕事関数は、4.0eV〜4.3eVであり、pMOSFET121Dのp側ゲート電極115Dの実効仕事関数は、4.9eV〜5.2eVである。ゲート電極の実効仕事関数は、得られたnMOSFET120BおよびpMOSFET121DにおけるMOS型キャパシタのC−V特性、すなわち容量−ゲート電圧特性から求められるフラットバンド電圧から求められる。

【0213】

以上のように本実施の形態によれば、poly−Si層113を形成する前に、ゲート電極用金属膜108上および元素添加金属層110上に第2ゲート電極用金属膜150が形成され、この第2ゲート電極用金属膜150上にpoly−Si層113が形成される。つまり、本実施の形態では、ゲート電極用金属膜108とpoly−Si層113との間、および元素添加金属層110とpoly−Si層113との間には、第2ゲート電極用金属膜150が設けられる。

【0214】

ゲート電極用金属膜108および元素添加金属層110が、たとえば10nm以下と薄いと、poly−Si層113の積層によって、ゲート電極114B,115Dの実効仕事関数が低下する弊害が起こる場合がある。

【0215】

本実施の形態のように第2ゲート電極用金属膜150を、ゲート電極用金属膜108とpoly−Si層113との間、および元素添加金属層110とpoly−Si層113との間に挿入することによって、ゲート電極用金属膜108および元素添加金属層110が薄い場合でも、poly−Si層113の積層の悪影響を抑え、ゲート電極114B,115Dの実効仕事関数が低下することを防ぐことができる。

【0216】

以上のように本実施の形態では、それぞれに適した実効仕事関数を有するゲート電極114B,115Dを備えるnMOSFET120BおよびpMOSFET121Dを実現することができる。具体的には、nMOSFET120Bにおけるn側ゲート電極114Bの実効仕事関数を4.0eV〜4.3eVとし、pMOSFET121Dにおけるp側ゲート電極115Dの実効仕事関数を4.9eV〜5.2eVすることができる。したがって、それぞれに適した閾値電圧を有するnMOSFET120BおよびpMOSFET121Dを実現することが可能である。

【0217】

本実施の形態のように第2ゲート電極用金属膜150を設ける場合、第1および第2絶縁膜用キャップ層107,109に含有される元素を熱拡散させるための熱処理は、本実施の形態のように第2ゲート電極用金属膜150およびpoly−Si層113を形成する前に行うことが好ましい。熱処理の前に第2ゲート電極用金属膜150、または第2ゲート電極用金属膜150およびpoly−Si層113を形成すると、前述の第5の実施の形態において熱処理の前にpoly−Si層113を形成する場合と同様に、第2絶縁膜用キャップ層109の材料によっては、第2ゲート電極用金属膜150およびpoly−Si層113の方に極端に拡散してしまい、ゲート電極金属層8の方に拡散されない場合がある。したがって、本実施の形態のように、第2ゲート電極用金属膜150およびpoly−Si層113の形成前に、熱処理工程を行うことが好ましい。

【0218】

以上のように本実施の形態では、前述の第5の実施の形態におけるpoly−Si層113の形成前に、第2ゲート電極用金属膜150を形成するが、前述の第6〜第9の実施の形態においても、本実施の形態と同様に、poly−Si層113を形成する前に、第2ゲート電極用金属膜150を形成してもよい。具体的には、第6の実施の形態では、ゲート電極用金属膜108上および元素添加保護層131上に第2ゲート電極用金属膜150を形成した後、第2ゲート電極用金属膜150上にpoly−Si層113を形成してもよい。

【0219】

また前述の第7の実施の形態では、元素添加金属層110上および元素添加金属層141上に第2ゲート電極用金属膜150を形成した後、第2ゲート電極用金属膜150上にpoly−Si層113を形成してもよい。

【0220】

また前述の第8の実施の形態では、nMOSFET領域RnおよびpMOSFET領域Rpの元素添加金属層110上に第2ゲート電極用金属膜150を形成した後、第2ゲート電極用金属膜150上にpoly−Si層113を形成してもよい。

【0221】

また前述の第9の実施の形態では、拡散抑止層140A上および元素添加金属層110上に第2ゲート電極用金属膜150を形成した後、第2ゲート電極用金属膜150上にpoly−Si層113を形成してもよい。

【0222】

また前述の第1〜第4の実施の形態では、前述の第5〜第10の実施の形態と同様に、Si基板1上に、素子分離膜5、pウェル3およびnウェル4が形成された表面側から、全面にわたって、絶縁性材料から成る界面層を形成してもよい。

【0223】

また前述の第5〜第10の実施の形態では、前述の第3の実施の形態と同様に、第1キャップ層として機能する第2絶縁膜用キャップ層109の拡散後または拡散前に、第2キャップ層を形成して、ゲート電極用金属膜108,108Aに拡散させてもよい。

【0224】

また前述の各実施の形態では、第1導電型をn型とし、第2導電型をp型としているが、第1導電型をp型とし、第2導電型をn型としてもよい。

【図面の簡単な説明】

【0225】

【図1】本発明の第1の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図2】本発明の第1の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図3】本発明の第1の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図4】本発明の第1の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図5】本発明の第1の実施の形態に係る半導体装置におけるn側キャップ層8Aの形成領域を模式的に示す上面図である。

【図6】本発明の第1の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図7】本発明の第1の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図8】本発明の第1の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図9】本発明の第1の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図10】本発明の第2の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図11】本発明の第2の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図12】本発明の第2の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図13】本発明の第3の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図14】本発明の第3の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図15】本発明の第3の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図16】本発明の第3の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図17】本発明の第3の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図18】本発明の第4の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図19】本発明の第4の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図20】本発明の第4の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図21】本発明の第4の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図22】本発明の第4の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図23】本発明の第4の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図24】本発明の第4の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図25】本発明の第4の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図26】本発明の第5の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図27】本発明の第5の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図28】本発明の第5の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図29】本発明の第6の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図30】本発明の第6の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図31】本発明の第6の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図32】本発明の第6の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図33】本発明の第6の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図34】本発明の第7の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図35】本発明の第7の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図36】本発明の第7の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図37】本発明の第7の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図38】本発明の第8の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図39】本発明の第8の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図40】本発明の第8の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図41】本発明の第8の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図42】本発明の第9の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図43】本発明の第9の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図44】本発明の第9の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図45】本発明の第9の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図46】本発明の第9の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図47】本発明の第10の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図48】本発明の第10の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【図49】本発明の第10の実施の形態である半導体装置の製造方法における各製造工程の状態を示す断面図である。

【符号の説明】

【0226】

1,101 シリコン基板、5,102 素子分離膜、3,103 pウェル、4,104 nウェル、6 ゲート絶縁膜、8A n側キャップ層、8B p側キャップ層、8C 第2p側キャップ層、105 界面層、106 ゲート絶縁膜用絶縁層、107 第1絶縁膜用キャップ層、108,108A ゲート電極用金属膜、109 第2絶縁膜用キャップ層、110,141 元素添加金属層、111 第1元素添加絶縁層、112 第2元素添加絶縁層、10,10A,113 多結晶シリコン層、114,114A,114B n側ゲート電極、115,115A,115B,115C,115D p側ゲート電極、116 n側ゲート絶縁膜、117 p側ゲート絶縁膜、120,120A,120B nMOSFET、121,121A,121B,121C,121D pMOSFET、130 保護層、131 元素添加保護層、140,140A 拡散抑止層、142 元素未添加金属層、150 第2ゲート電極用金属膜、200,210,220,230,240,250 CMOSFET、GE ゲート電極、M ゲート電極用金属膜、MA n側ゲート電極用金属膜、MB,MC p側ゲート電極用金属膜、N 第2ゲート電極用金属膜、Rn nMOSFET領域、Rp pMOSFET領域。

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、より詳細には、複数のゲート電極構造を有する半導体装置およびその製造方法に関する。

【背景技術】

【0002】

45nmノード以降のCMOSデバイスでは、ゲート電極をpoly−Siとし、ゲート絶縁膜をSiONとする構造に代わって、ゲート絶縁膜を高誘電率の絶縁膜(以下「high−k膜」という)とするゲートスタック構造の適用が始められている。その理由は、high−k膜は、SiO2膜などと比較して、物理的には膜厚が厚くても、電気的動作時においては膜厚が薄い膜として機能する、すなわち実効的な膜厚が薄いという性質を有するので、ゲートリーク電流を抑制するのに寄与し得るからである。

【0003】

このようなpoly−Si/high−k膜構造では、フェルミレベルピンニング(Fermi Level Pinning)という現象によって、特にpMOSFETに関してデバイス動作時の閾値電圧(Vth)が高くなるという問題がある。

【0004】

そこで、pMOSFETの閾値電圧(Vth)低減策として、ゲート絶縁膜の形成前にSi基板にフッ素(F)イオンを注入することが、提案されている(非特許文献1参照)。しかし、所望のデバイス特性を得るためには、Si基板にFイオンを多量に注入する必要性がある。このようにSi基板にFイオンを多量に注入すると、注入ダメージによってデバイス特性が劣化するという問題がある。

【0005】

また、nMOSFETの閾値電圧(Vth)低減策としては、ゲート絶縁膜の形成前にSi基板に窒素(N2)イオンを注入することが提案されているが、Si基板にN2イオンを多量に注入すると、やはり注入ダメージによってデバイス特性が劣化する。

【0006】

そこで、仕事関数はFETの閾値電圧(Vth)と直接的に関連性を有するので、閾値電圧(Vth)を低減するための解決策として、所望の仕事関数を有する金属材料をゲート電極として適用することが、提案されている。金属材料を最下層のゲート電極の材料として適用するときの第1の利点は、金属ゲート電極は、poly−Siゲート電極の場合のように空乏層を生じさせないので、空乏化によってデバイス動作時の実効的なゲート絶縁膜の膜厚が増加するという問題を解消して、高性能デバイスの実現が可能となる点にある。また第2の利点は、フェルミレベルピニングによる閾値電圧制御性の困難化の欠点を回避できる点にある。

【0007】

CMOSデバイスとしては、pMOSFETおよびnMOSFETのそれぞれに適した仕事関数を有する金属材料を用いることが好ましいことから、特許文献1〜3には、Si膜を最下層のゲート電極に用いてフルシリサイド化したゲート電極において、n/p−MOS間の材料および結晶相を制御する方法が、提案されている。また特許文献4には、n/p−MOSのメタルゲートにおいて、同種金属材料を用いた金属膜/金属窒化膜間での窒素拡散の制御によって金属ゲート電極の仕事関数を制御する方法が、提案されている。しかし、製造フローの複雑化および製造プロセスの困難化が問題となる。

【0008】

そこで、このような問題を回避する観点から、pMOSFETではpoly−Si/metal/high−k構造を備え、nMOSFETではpoly−Si/high−k構造を備えるハイブリッドメタルゲートCMOSデバイスの開発が進められている(非特許文献2参照)。

【0009】

また、pMOSFETおよびnMOSFETのそれぞれに適したゲート電極の作り分けは、製造プロセスが困難化することから、ゲート絶縁膜に対してキャッピングを行い、2種類のゲート絶縁膜を作りこむ手法が検討されている(たとえば非特許文献3参照)。

【0010】

【特許文献1】特開2007−242894号公報

【特許文献2】特開2007−141889号公報

【特許文献3】特開2005−294799号公報

【特許文献4】特開2007−142153号公報

【非特許文献1】M. Inoue et.al, IEDM Tech. Dig., (2005) p.425.

【非特許文献2】T. Hayashi et.al, IEDM Tech. Dig., (2006) p.247.

【非特許文献3】V. Narayanan et.al, VLSI Tech. Symp., (2006) p.224.

【発明の開示】

【発明が解決しようとする課題】

【0011】

上述の通り、CMOSデバイスを所望の閾値電圧(Vth)で動作させるためには、CMOSデバイスを構成するpMOSFETおよびnMOSFETのそれぞれに適した仕事関数を有する金属材料をゲート電極材料として用いることが好ましい。しかし、全く物性の異なる2種類以上の材料をpMOSFETとnMOSFETとで作り分けることは、フローを複雑化させるという問題を生じさせることが考えられる。この製造プロセスの困難化は、特許文献1〜4に記載されるように同種の材料を用いる場合でも避けられない。しかも、pMOSFETおよびnMOSFETのそれぞれに個別の金属材料を用いる場合には、同一チップ(ウェハ)上において、異種材料をドライエッチング法などによって同時に加工してゲート電極を形成することになるので、良好なゲート形状を得ることは困難である。これによって、所望のデバイス特性が得られないおそれがある。

【0012】

他方、上述の非特許文献2に記載のハイブリッドメタルゲート構造を採用する場合には、閾値電圧の制御範囲が狭く、またnMOSFETは、poly−Si/high−k構造となるので、実効的なゲート絶縁膜の膜厚が増加する。これによって、所望のデバイス特性が得られない可能性もあり、その点が課題とされている。しかも非特許文献2に記載のハイブリッドメタルゲート電極の形成方法では、片側のチャネル領域に所望の金属材料を堆積後に、別のチャネル領域上の金属層をウェットエッチングなどによって除去しなければならない。この金属層のエッチング工程は、ゲート絶縁膜の直上において行われるので、ゲート絶縁膜にダメージを与える可能性が高い。これによって、デバイスの信頼性が低下するおそれがある。

【0013】

また非特許文献3に記載されるゲート絶縁膜に対してキャッピングを行う手法では、ゲート絶縁膜上において、キャッピング層の形成および除去工程を繰り返すので、ゲート絶縁膜が劣化し、デバイスの信頼性が低下するおそれがある。

【0014】

本発明の目的は、CMOSデバイスのように複数の半導体素子を備える半導体装置であって、複数の半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置およびその半導体装置を容易に製造することのできる半導体装置の製造方法を提供することである。

【0015】

また本発明の他の目的は、CMOSデバイスを構成するpFETおよびnFETのように半導体装置を構成する複数の半導体素子のそれぞれに適した所望の仕事関数を有する金属材料をデュアルゲート電極材料として容易にかつ精度良く形成することが可能な半導体装置の製造方法を提供することである。

【0016】

また本発明の他の目的は、ゲート絶縁膜の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる半導体装置の製造方法および半導体装置を提供することである。

【課題を解決するための手段】

【0017】

本発明の半導体装置の製造方法は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置の製造方法であって、前記第1導電型半導体素子が形成される第1導電型素子領域と前記第2導電型半導体素子が形成される第2導電型素子領域とを互いに分離する素子分離膜を半導体基板に形成する工程と、前記半導体基板の主面上に配設されたゲート絶縁膜の表面上に、第1金属膜を形成する工程と、前記第1導電型素子領域に形成された前記第1金属膜上面上に、前記第1金属膜とは異種材料の第1キャップ層を形成する工程と、第1熱処理により前記第1キャップ層と前記第1導電型素子領域内の前記第1金属膜を反応させる工程と、前記第1導電型素子領域と前記第2導電型素子領域とで異なる組成を有するデュアルゲート電極構造を形成する工程とを備えることを特徴とする。

【0018】

また本発明の半導体装置の製造方法は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置の製造方法であって、第1導電型半導体素子が形成される第1導電型素子領域および第2導電型半導体素子が形成される第2導電型素子領域の半導体基板上に、絶縁性材料から成る絶縁層を形成する工程と、第1導電型素子領域および第2導電型素子領域の半導体基板と絶縁層との間、または第1導電型素子領域および第2導電型素子領域の絶縁層上に、第1の元素を含有する第1元素層を形成する工程と、第1導電型素子領域および第2導電型素子領域の第1元素層上に、導電性材料から成る電極用導電層を形成する工程と、第1導電型素子領域の電極用導電層上に、第1の元素とは異なる第2の元素を含有する第2元素層を形成する工程と、第1元素層および第2元素層とともに、絶縁層および電極用導電層を熱処理する工程とを備えることを特徴とする。

【0019】

また本発明の半導体装置の製造方法は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置の製造方法であって、第1導電型半導体素子が形成される第1導電型素子領域および第2導電型半導体素子が形成される第2導電型素子領域の半導体基板上に、絶縁性材料から成る絶縁層を形成する工程と、第1導電型素子領域および第2導電型素子領域の半導体基板と絶縁層との間、または第1導電型素子領域および第2導電型素子領域の絶縁層上に、第1の元素を含有する第1元素層を形成する工程と、第1導電型素子領域および第2導電型素子領域の第1元素層上に、導電性材料から成る電極用導電層を形成する工程と、第2導電型素子領域の電極用導電層上に、第1の元素とは異なる第2の元素の拡散を抑制または防止する拡散抑止層を形成する工程と、拡散抑止層上および第1導電型素子領域の電極用導電層上に、第2の元素を含有する第2元素層を形成する工程と、第1元素層および第2元素層とともに、絶縁層、電極用導電層および拡散抑止層を熱処理する工程とを含むことを特徴とする。

【0020】

また本発明の半導体装置の製造方法は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置の製造方法であって、第1導電型半導体素子が形成される第1導電型素子領域および第2導電型半導体素子が形成される第2導電型素子領域の半導体基板上に、絶縁性材料から成る絶縁層を形成する工程と、第1導電型素子領域および第2導電型素子領域の半導体基板と絶縁層との間、または第1導電型素子領域および第2導電型素子領域の絶縁層上に、第1の元素を含有する第1元素層を形成する工程と、第1導電型素子領域および第2導電型素子領域の第1元素層上に、導電性材料から成る電極用導電層を、第2導電型素子領域における厚み寸法の方が第1導電型素子領域における厚み寸法よりも大きくなるように形成する工程と、第1導電型素子領域および第2導電型素子領域の電極用導電層上に、第1の元素とは異なる第2の元素を含有する第2元素層を形成する工程と、第1元素層および第2元素層とともに、絶縁層および電極用導電層を熱処理する工程とを含むことを特徴とする。

【0021】

本発明の半導体装置は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置であって、第1導電型半導体素子は、半導体基板上に設けられ、絶縁性を有し、第1の元素および第1の元素とは異なる第2の元素を含有する第1元素添加絶縁層と、第1元素添加絶縁層上に設けられ、導電性を有し、第2の元素を含有する元素添加導電層とを備え、第2導電型半導体素子は、第1元素添加絶縁層が設けられる半導体基板上に第1元素添加絶縁層と並設して設けられ、絶縁性を有し、第1の元素を含有する第2元素添加絶縁層と、第2元素添加絶縁層上に設けられ、導電性を有する電極用導電層とを備えることを特徴とする。

【0022】

また本発明の半導体装置は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置であって、第1導電型半導体素子は、半導体基板上に設けられ、絶縁性を有し、第1の元素および第1の元素とは異なる第2の元素を含有する第1元素添加絶縁層と、第1元素添加絶縁層上に設けられ、導電性を有し、第2の元素を含有する第1元素添加導電層とを備え、第2導電型半導体素子は、第1元素添加絶縁層が設けられる半導体基板上に第1元素添加絶縁層と並設して設けられ、絶縁性を有し、第1の元素を含有する第2元素添加絶縁層と、第2元素添加絶縁層上に設けられ、導電性を有する電極用導電層と、電極用導電層上に設けられ、導電性を有し、第2の元素を含有する第2元素添加導電層と、第2元素添加導電層上に設けられ、導電性を有し、第2の元素を含有する、もう一つの第2元素添加導電層とを備えることを特徴とする。

【0023】

また本発明の半導体装置は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置であって、第1導電型半導体素子は、半導体基板上に設けられ、絶縁性を有し、第1の元素および第1の元素とは異なる第2の元素を含有する第1元素添加絶縁層と、第1元素添加絶縁層上に設けられ、導電性を有し、第2の元素を含有する第1元素添加導電層とを備え、第2導電型半導体素子は、第1元素添加絶縁層が設けられる半導体基板上に第1元素添加絶縁層と並設して設けられ、絶縁性を有し、第1の元素を含有する第2元素添加絶縁層と、第2元素添加絶縁層上に設けられ、導電性を有する電極用導電層と、電極用導電層上に設けられ、導電性を有し、第2の元素を含有する第2元素添加導電層とを備えることを特徴とする。

【0024】

また本発明の半導体装置は、導電型が互いに異なる第1導電型半導体素子と第2導電型半導体素子とが並設される半導体装置であって、第1導電型半導体素子は、半導体基板上に設けられ、絶縁性を有し、第1の元素および第1の元素とは異なる第2の元素を含有する第1元素添加絶縁層と、第1元素添加絶縁層上に設けられ、導電性を有し、第2の元素を含有する第1元素添加導電層とを備え、第2導電型半導体素子は、第1元素添加絶縁層が設けられる半導体基板上に第1元素添加絶縁層と並設して設けられ、絶縁性を有し、第1の元素を含有する第2元素添加絶縁層と、第2元素添加絶縁層上に設けられ、導電性を有する電極用導電層と、電極用導電層上に設けられ、導電性を有し、電極用導電層とは異なる材料から成る上部導電層とを備えることを特徴とする。

【発明の効果】

【0025】

本発明の半導体装置の製造方法によれば、第1導電型半導体素子のゲート電極の金属膜と第2導電型半導体素子のゲート電極の金属膜とが互いに異なる仕事関数を有するデュアルゲート電極構造を有することにより、第1導電型半導体素子、第2導電型半導体素子それぞれを所望の閾値電圧で動作可能な半導体装置を容易に形成することができる。特に、第1導電型半導体素子のゲート電極の金属膜の主材料と第2導電型半導体素子のゲート電極の金属膜の主材料とが同一であるので、ゲート電極の加工がより容易となり、微細ゲート電極の加工精度を向上させることができる。しかも、ゲート絶縁膜に対するダメージが製造工程中に生じることはなく、高い信頼性を有する半導体装置を実現することができる。このように本発明の半導体装置の製造方法によれば、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0026】

また本発明の半導体装置の製造方法によれば、第1導電型素子領域および第2導電型素子領域の半導体基板上に絶縁層が形成され、この絶縁層と半導体基板との間または絶縁層上に第1元素層および電極用導電層が順次形成される。形成された電極用導電層のうち、第1導電型素子領域の電極用導電層上に、第2元素層が形成される。形成された第1元素層および第2元素層とともに、絶縁層および電極用導電層が熱処理される。この熱処理によって、第1元素層に含有される第1の元素を、第1元素層の上方または下方の絶縁層に拡散させることができる。また第2元素層に含有される第2の元素を、第2元素層の下方の電極用導電層に拡散させ、さらに電極用導電層の下方の絶縁層に拡散させることができる。これによって、第1導電型素子領域では、第1および第2の元素を含有する絶縁層を形成し、第2導電型素子領域では、第1の元素を含有する絶縁層を形成することができるので、第1導電型半導体素子の閾値電圧および第2導電型半導体素子の閾値電圧をそれぞれ制御することができる。したがって、閾値電圧の制御範囲を広げることができる。

【0027】

また第2元素層は、電極用導電層上に形成されており、第2元素層と絶縁層との間には電極用導電層が介在するので、第1導電型素子領域に第2元素層を形成するために、たとえば第2元素層を第1導電型素子領域と第2導電型素子領域とにわたって形成した後、第2導電型素子領域の第2元素層を除去するときに、絶縁層が劣化することを防ぐことができる。これによって、劣化による絶縁層の信頼性の低下を防止することができるので、絶縁層の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。たとえば第1導電型半導体素子および第2導電型半導体素子が絶縁層をゲート絶縁膜とするMOSトランジスタである場合、ゲート絶縁膜の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0028】

また本発明の半導体装置の製造方法によれば、第1導電型素子領域および第2導電型素子領域の半導体基板上に絶縁層が形成され、この絶縁層と半導体基板との間または絶縁層上に第1元素層および電極用導電層が順次形成される。形成された電極用導電層のうち、第2導電型素子領域の電極用導電層上に拡散抑止層が形成され、この拡散抑止層上および第1導電型素子領域の電極用導電層上に、第2元素層が形成される。形成された第1元素層および第2元素層とともに、絶縁層、電極用導電層および拡散抑止層が熱処理される。

【0029】

この熱処理によって、第1元素層に含有される第1の元素を、第1元素層の上方または下方の絶縁層に拡散させることができる。また第1導電型素子領域では、第2元素層に含有される第2の元素を、第2元素層の下方の電極用導電層に拡散させ、さらに電極用導電層の下方の絶縁層に拡散させることができる。第2導電型素子領域では、第2元素層は拡散抑止層上に形成されるので、拡散抑止層によって、電極用導電層および絶縁層への第2の元素の拡散を抑制または防止することができる。これによって、第1導電型素子領域では、第1および第2の元素を含有する絶縁層を形成し、第2導電型素子領域では、第1の元素を含有する絶縁層を形成することができるので、第1導電型半導体素子の閾値電圧および第2導電型半導体素子の閾値電圧をそれぞれ制御することができる。したがって、閾値電圧の制御範囲を広げることができる。

【0030】

また第2元素層は、電極用導電層上に形成されており、第2元素層と絶縁層との間には電極用導電層が介在するので、第1導電型素子領域に第2元素層を形成するために、たとえば第2元素層を第1導電型素子領域と第2導電型素子領域とにわたって形成した後、第2導電型素子領域の第2元素層を除去するときに、絶縁層が劣化することを防ぐことができる。これによって、劣化による絶縁層の信頼性の低下を防止することができるので、絶縁層の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。たとえば第1導電型半導体素子および第2導電型半導体素子が絶縁層をゲート絶縁膜とするMOSトランジスタである場合、ゲート絶縁膜の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0031】

また本発明の半導体装置の製造方法によれば、第1導電型素子領域および第2導電型素子領域の半導体基板上に絶縁層が形成され、この絶縁層と半導体基板との間または絶縁層上に第1元素層および電極用導電層が順次形成される。電極用導電層は、第2導電型素子領域における厚み寸法の方が第1導電型素子領域における厚み寸法よりも大きく形成される。この電極用導電層上に、第1導電型素子領域および第2導電型素子領域にわたって、第2元素層が形成される。形成された第1元素層および第2元素層とともに、絶縁層および電極用導電層が熱処理される。この熱処理によって、第1元素層に含有される第1の元素を、第1元素層の上方または下方の絶縁層に拡散させることができる。また第2元素層に含有される第2の元素を、第2元素層の下方の電極用導電層に拡散させ、さらに電極用導電層の下方の絶縁層に拡散させることが可能である。

【0032】

電極用導電層は、第2導電型素子領域における厚み寸法の方が、第1導電型素子領域における厚み寸法よりも大きいので、第2導電型素子領域では、第1導電型素子領域に比べて、電極用導電層および絶縁層への第2の元素の拡散を抑制することができる。たとえば、第2の元素を、第2導電型素子領域では絶縁層まで拡散させ、第1導電型素子領域では絶縁層までは拡散しないようにすることができる。これによって、第1導電型素子領域では、第1および第2の元素を含有する絶縁層を形成し、第2導電型素子領域では、第1の元素を含有する絶縁層を形成することができるので、第1導電型半導体素子の閾値電圧および第2導電型半導体素子の閾値電圧をそれぞれ制御することができる。したがって、閾値電圧の制御範囲を広げることができる。

【0033】

また第2元素層は、電極用導電層上に形成されており、第2元素層と絶縁層との間には電極用導電層が介在するので、第2元素層を形成するときに絶縁層が劣化することを防ぐことができる。これによって、劣化による絶縁層の信頼性の低下を防止することができるので、絶縁層の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。たとえば第1導電型素子および第2導電型素子が絶縁層をゲート絶縁膜とするMOSトランジスタである場合、ゲート絶縁膜の信頼性の低下を防止するとともに、閾値電圧の制御範囲を広げることができる。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を容易に製造することができる。

【0034】

本発明の半導体装置によれば、第1導電型半導体素子は、第1元素添加絶縁層に第1および第2の元素を含有し、この第1元素添加絶縁層上の元素添加導電層に第2の元素を含有する。また第2導電型半導体素子は、第2元素添加絶縁層に第1の元素を含有し、この第2元素添加絶縁層上に電極用導電層を備える。これによって、それぞれに適した閾値電圧を有する第1導電型半導体素子および第2導電型半導体素子を実現することが可能である。また第1および第2元素添加絶縁層は、第1および第2元素添加絶縁層となる絶縁層上でエッチングを実施することなく形成することが可能であるので、製造過程における劣化が防止され、信頼性の低下が防止される。したがって、第1導電型半導体素子および第2導電型半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置を実現することが可能である。

【0035】