半導体装置の製造方法および半導体装置

【課題】貫通電極を有する3次元構造の半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間で、第1バンプ電極50が形成されていない領域に、スペーサ49と第2バンプ電極50aとを積層した支持部を形成することによって、ウエハW3のたわみを防いで、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔をウエハ面内で均一に保つ。これにより、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間の接着剤51の未充填箇所の生成を防ぐ。

【解決手段】ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間で、第1バンプ電極50が形成されていない領域に、スペーサ49と第2バンプ電極50aとを積層した支持部を形成することによって、ウエハW3のたわみを防いで、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔をウエハ面内で均一に保つ。これにより、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間の接着剤51の未充填箇所の生成を防ぐ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法および半導体装置に関し、特に3次元構造の半導体装置の製造方法および半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

3次元構造の半導体装置は、半導体活性層を多層に積み重ねた構造に3次元的に半導体素子を集積することにより、2次元構造の半導体装置が直面する種々の障壁、例えば微細化におけるリソグラフィ技術の限界、配線の微細化や配線長増大による配線抵抗の増大や寄生効果の増大、またそれに伴う動作速度の飽和傾向、素子寸法の微細化による高電界効果等を回避し、集積度の向上を維持する有力な構造として注目されている。

【0003】

3次元構造の半導体装置については、例えば特開平11−261000号公報(特許文献1)または特開2002−334967号公報(特許文献2)に記載があり、半導体素子が形成された半導体基板を貼り合せることにより3次元構造の半導体装置を製造する方法が開示されている。また、これらの文献には、所望の半導体基板の主裏面間を貫通する溝内に垂直相互接続体または埋込接続電極と称する貫通電極を形成し、半導体基板の主裏面間を導通可能なようにする構成が開示されている。

【0004】

また、特開2006−165025号公報(特許文献3)または特開2003−17558号公報(特許文献4)には、半導体基板中に貫通電極を備えた半導体装置および貫通電極の形成方法が開示されている。

【0005】

また、特開2007−281393号公報(特許文献5)には、導電性材料からなる突起電極と、突起電極よりも大きな高さをもつダミーの突起部とを基板上に有しており、突起部を利用して間隙を決定し、突起部の内側領域において電子部品の表面に付着された電気絶縁材によって所定の間隙を正確に保持する半導体装置が開示されている。

【特許文献1】特開平11−261000号公報

【特許文献2】特開2002−334967号公報

【特許文献3】特開2006−165025号公報

【特許文献4】特開2003−17558号公報

【特許文献5】特開2007−281393号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

複数枚のチップが積層されて構成される3次元構造の半導体装置では、上に位置するチップとこれに対向して下に位置するチップとの間において互いの信号を伝達する手段の一つとして貫通電極が用いられている。また、上に位置するチップとこれに対向して下に位置するチップとの間隔は、例えば5〜30μm程度であり、その間には、両チップを貼り合わせる接着剤として機能する樹脂が充填されている。

【0007】

しかしながら、貫通電極を有する3次元構造の半導体装置については、その製造過程において、以下に説明する種々の技術的課題が存在する。

【0008】

上記貫通電極は半導体装置の回路構成に依存して局在することから、多数の貫通電極が配置された領域と、貫通電極が配置されない領域とが存在する。貫通電極が配置された領域では、上に位置するウエハとこれに対向して下に位置するウエハとの間隔は貫通電極の長さで決まる。しかし、貫通電極が配置されていない領域では、上に位置するウエハの厚さが、例えば30μm程度と薄いため、上に位置するウエハがたわむことによって、上に位置するウエハとこれに対向して下に位置するウエハとの間隔が、貫通電極が配置された領域の上に位置するウエハとこれに対向して下に位置するウエハとの間隔よりも20%程度狭くなる。このため、上に位置するウエハとこれに対向して下に位置するウエハとの間隔にばらつきが生じてしまう。

【0009】

上に位置するウエハとこれに対向して下に位置するウエハとの間隔が狭いところでは樹脂が注入されにくくなり、上に位置するウエハとこれに対向して下に位置するウエハとの間に樹脂が充填されない箇所が形成されてしまう。複数枚のウエハを積層して貼り合わせた後に、積層した複数枚のウエハは、例えばダイシングにより個々の積層した複数枚のチップに個片化されて半導体装置が形成されるが、その時、樹脂が充填されない箇所では、上に位置するチップとこれに対向して下に位置するチップとが分離して、半導体装置が破壊するという問題が発生する。

【0010】

本発明の目的は、貫通電極を有する3次元構造の半導体装置の製造歩留まりを向上させることのできる技術を提供することにある。

【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの一実施の形態を簡単に説明すれば、次のとおりである。

【0013】

この実施の形態は、複数枚の半導体ウエハを貼り合わせ、各々の半導体ウエハの半導体チップに形成された集積回路同士を互いに電気的に接続することにより所望の集積回路を形成する半導体装置の製造方法である。まず、第2ウエハの主面上に最上層配線を覆う表面保護膜を形成した後、表面保護膜を加工して最上層配線の一部を露出させる。続いて、第2ウエハの主面上に絶縁膜を形成した後、この絶縁膜を加工して最上層配線が露出していない領域の表面保護膜上に絶縁膜からなるスペーサを形成する。続いて、同一工程で第2ウエハの主面上の露出した最上層配線上に第1バンプ電極を、スペーサ上に第2バンプ電極を形成する。その後、第2ウエハの主面上に形成された第1バンプ電極に、第1ウエハの裏面から突出する貫通電極を物理的に接触させ、さらに第1ウエハの裏面と第2ウエハの主面上の表面保護膜との間に樹脂を充填するものである。

【0014】

また、この実施の形態は、複数枚の半導体ウエハを貼り合わせ、各々の半導体ウエハの半導体チップに形成された集積回路同士を互いに電気的に接続することにより所望の集積回路を形成する半導体装置の製造方法である。まず、第2ウエハの主面上に最上層配線を覆う表面保護膜を形成した後、表面保護膜を加工して第1バンプ電極が形成される領域の表面保護膜の厚さを第1バンプ電極が形成されない領域の表面保護膜の厚さよりも薄くし、さらに表面保護膜を加工して第1バンプ電極が形成される領域の最上層配線の一部を露出させる。続いて、同一工程で第2ウエハの主面上の露出した最上層配線上に第1バンプ電極を最上層配線が露出していない表面保護膜上に第2バンプ電極を形成する。その後、第2ウエハの主面上に形成された第1バンプ電極に、第1ウエハの裏面から突出する貫通電極を物理的に接触させ、さらに第1ウエハの裏面と第2ウエハの主面上の表面保護膜との間に樹脂を充填するものである。

【0015】

また、この実施の形態は、複数枚の半導体チップが貼り合わされ、各々の半導体チップに形成された集積回路同士が互いに電気的に接続されてなる所望の集積回路を備える半導体装置である。この半導体装置は、主面上に形成された複数の第1集積回路と、裏面から突出する貫通電極とを含む第1チップと、主面上に形成された複数の第2集積回路と、複数の第2集積回路のいずれかに電気的に接続されて主面上に形成された複数層の配線と、最上層配線の一部を露出して主面上に形成された表面保護膜と、表面保護膜上に形成されたスペーサと、表面保護膜から露出する最上層配線と電気的に接続して形成された第1バンプ電極と、スペーサ上に形成された第2バンプ電極とを含む第2チップとを有し、第1チップの裏面から突出する貫通電極が第2チップの主面上の第1バンプ電極と物理的に接触しており、第1チップの裏面と第2チップの主面上の表面保護膜との間に樹脂が充填されているものである。

【0016】

また、この実施の形態は、複数枚の半導体チップが貼り合わされ、各々の半導体チップに形成された集積回路同士が互いに電気的に接続されてなる所望の集積回路を備える半導体装置である。この半導体装置は、主面上に形成された複数の第1集積回路と、裏面から突出する貫通電極とを含む第1チップと、主面上に形成された複数の第2集積回路と、複数の第2集積回路のいずれかに電気的に接続されて主面上に形成された複数層の配線と、最上層配線の一部を露出して主面上に形成された表面保護膜と、表面保護膜から露出する最上層配線と電気的に接続して形成された第1バンプ電極と、表面保護膜上に形成された第2バンプ電極とを含む第2チップとを有し、第1バンプ電極が形成された領域の表面保護膜の厚さは、第2バンプ電極が形成される領域の表面保護膜の厚さよりも薄く、第1チップの裏面から突出する貫通電極が第2チップの主面上の第1バンプ電極と物理的に接触しており、第1チップの裏面と第2チップの主面上の表面保護膜との間に樹脂が充填されているものである。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものの一実施の形態によって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

上に位置するウエハ(第1ウエハ)とこれに対向して下に位置するウエハ(第2ウエハ)との間隔をウエハ面内で均一に保つことができるので、上に位置するウエハとこれに対向して下に位置するウエハとの間に接着剤である樹脂を余すところなく充填することができる。これにより、積層した複数枚のウエハを積層した複数枚のチップに個片化して半導体装置を形成しても、積層されたチップの分離を防ぐことができるので、貫通電極を有する3次元構造の半導体装置の製造歩留まりを向上させることができる。

【発明を実施するための最良の形態】

【0019】

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0020】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0021】

また、以下の実施の形態で用いる図面においては、平面図であっても図面を見易くするためにハッチングを付す場合もある。また、以下の実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0022】

(実施の形態1)

本実施の形態1の半導体装置は、互いに異なる集積回路が形成された3枚の半導体チップ(以下、単にチップという)C1,C2,C3を積層して貼り合わせた3次元構造を有している。図1は、この半導体装置を配線基板1に実装してモールド樹脂2で封止したパッケージの一例を示す断面図である。

【0023】

配線基板1に実装された3枚のチップC1,C2,C3のうち、最下層のチップC1は、接着剤3を介して配線基板1に接着されている。また、中間層のチップC2は、接着剤3を介してチップC1に接着されており、最上層のチップC3は、接着剤3を介してチップC2に接着されている。後に詳しく説明するが、最下層のチップC1に形成された集積回路と中間層のチップC2に形成された集積回路は、チップC2に形成された複数の貫通電極4を介して電気的に接続され、中間層のチップC2に形成された集積回路と最上層のチップC3に形成された集積回路は、チップC3に形成された複数の貫通電極4を介して電気的に接続されている。すなわち、本実施の形態1の半導体装置は、チップC1,C2,C3に形成された集積回路を貫通電極4を介して互いに接続することによって、所望のシステムを実現している。

【0024】

上記チップC1,C2,C3と配線基板1は、最上層のチップC3に形成された複数のボンディングパッド5と配線基板1上に形成された複数の電極6との間にボンディングされた複数本の金(Au)ワイヤ7を介して電気的に接続されている。電極6は、配線基板1内の銅(Cu)配線8を介して、配線基板1の裏面の半田バンプ9に電気的に接続されている。半田バンプ9は、図1に示すパッケージをマザーボードなどに実装する際の外部接続端子を構成している。

【0025】

図2は、本実施の形態1の半導体装置の製造工程を示すフロー図である。この半導体装置の製造工程は、半導体ウエハ(以下、単にウエハという)W1,W2,W3に互いに異なる集積回路を形成し、ウエハW2,W3に導電部を形成する工程と、ウエハW1,W2にバンプ電極を形成する工程と、ウエハW3の裏面を研磨して導電部を露出させることによって貫通電極4を形成する工程と、ウエハW2,W3を貼り合わせ、ウエハW3に備わる貫通電極4とウエハW2に備わるバンプ電極とを介して集積回路同士を電気的に接続する工程と、ウエハW2,W3間に接着剤を注入する工程と、ウエハW2の裏面を研磨して導電部を露出させることによって貫通電極4を形成する工程と、ウエハW1,(W2+W3)を貼り合わせ、ウエハW2に備わる貫通電極4とウエハW1に備わるバンプ電極とを介して集積回路同士を電気的に接続する工程と、ウエハW1,(W2+W3)間に接着剤を注入する工程と、ウエハW1,W2,W3をダイシングすることによって、3次元構造のチップC1,C2,C3を形成する工程と、チップC1,C2,C3をパッケージング(基板実装、ワイヤボンディング、樹脂封止)する工程とに大別される。

【0026】

以下、3枚のウエハW1,W2,W3を用いた半導体装置の製造方法を工程順に説明する。

【0027】

まず、図3〜図21を用いて、ウエハに集積回路と導電部とを形成する工程およびウエハにバンプ電極を形成する工程について説明する。ここでの説明では、貼り合わせた時に中間に位置するウエハW2を用いる。

【0028】

図3に示すように、単結晶シリコンからなる厚さ780μm程度のウエハW2を用意する。そして、このウエハW2を熱処理してその主面(集積回路を形成する面)に厚さ10nm程度の薄い酸化シリコン膜20を形成し、続いて酸化シリコン膜20上にCVD(Chemical Vapor Deposition)法で窒化シリコン膜21を堆積した後、フォトレジスト膜(図示せず)をマスクにしたドライエッチングで素子分離溝形成領域の窒化シリコン膜21と酸化シリコン膜20とを除去する。ウエハW2と窒化シリコン膜21との間に形成する酸化シリコン膜20は、ウエハW2と窒化シリコン膜21との界面に生じる応力を緩和し、この応力に起因してウエハW2の表面に転位などの欠陥が発生するのを防ぐためのバッファ層である。

【0029】

次に、図4に示すように、窒化シリコン膜21をマスクにしたドライエッチングにより、素子分離溝形成領域のウエハW2に深さ350nm程度の素子分離溝22を形成し、後に貫通電極4を形成する領域の近傍のウエハW2に深さ350nm程度の溝23を形成する。溝23の平面形状は、例えば図5に示すような四角枠状とする。

【0030】

次に、図6に示すように、ウエハW2を熱処理することによって、素子分離溝22および溝23の内壁に酸化シリコン膜24aを形成した後、ウエハW2の主面上にCVD法で酸化シリコン膜24を堆積し、続いて素子分離溝22および溝23のそれぞれの外部の酸化シリコン膜24をCMP(Chemical Mechanical Polishing)法で研磨、除去することによって、素子分離溝22の内部および溝23の内部に酸化シリコン膜24を残す。

【0031】

次に、窒化シリコン膜21をエッチングして除去した後、図7に示すように、ウエハW2の主面上にCVD法で窒化シリコン膜25を堆積する。続いて、フォトレジスト膜(図示せず)をマスクにしたドライエッチングで溝23の上部の窒化シリコン膜25、溝23の内部の酸化シリコン膜24および溝23の下方のウエハW2を順次エッチングすることにより、溝23の内側に、例えば深さ40μm程度の絶縁溝26Aを形成する。図8に示すように、絶縁溝26Aは、溝23に沿って形成し、その幅を溝23の幅よりも狭くする。絶縁溝26Aの幅は、例えば2μm程度である。

【0032】

次に、図9に示すように、ウエハW2を1000℃程度で熱処理することによって、絶縁溝26Aの内壁に酸化シリコン膜27を形成する。続いて、図10に示すように、ウエハW2の主面上にCVD法で多結晶シリコン膜28を堆積した後、絶縁溝26Aの外部の多結晶シリコン膜28をエッチバックで除去することにより、絶縁溝26Aの内部に多結晶シリコン膜28を残す。このとき、絶縁溝26Aの内部の多結晶シリコン膜28は、その表面の高さをウエハW2の表面よりも低くする。

【0033】

次に、ウエハW2の主面上にCVD法で酸化シリコン膜を堆積した後、絶縁溝26Aの外部の酸化シリコン膜をCMP法で研磨、除去することにより、図11に示すように、絶縁溝26Aの内部の多結晶シリコン膜28上に酸化シリコン膜からなるキャップ絶縁膜29を形成する。ここまでの工程により、多結晶シリコン膜28の周囲を酸化シリコン膜27とキャップ絶縁膜29とで囲んだ絶縁部26Cが完成する。絶縁部26Cは、後の工程でウエハW2の主面に形成する集積回路素子と導電部(貫通電極4)とを電気的に分離するために形成する。また、絶縁溝26Aの内壁に酸化シリコン膜27を形成する際には、ウエハW2を1000℃程度で熱処理するので、絶縁部26Cは、集積回路素子よりも先に形成しておくことが望ましい。

【0034】

次に、窒化シリコン膜25をエッチングして除去した後、図12に示すように、ウエハW2の素子形成領域にn型不純物とp型不純物とをイオン注入することによって、n型ウエル30とp型ウエル31とを形成する。

【0035】

次に、ウエハW2の表面をウエットエッチングして酸化シリコン膜20を除去し、続いてウエハW2を熱処理してその表面にゲート絶縁膜32を形成した後、図13に示すように、周知のMIS(Metal Insulator Semiconductor)トランジスタ形成プロセスに従ってp型ウエル31にnチャネル型MISトランジスタQnを形成し、n型ウエル30にpチャネル型MISトランジスタQpを形成する。

【0036】

nチャネル型MISトランジスタQnは、主としてゲート絶縁膜32、ゲート電極33およびn型半導体領域(ソース、ドレイン)34で構成され、pチャネル型MISトランジスタQpは、主としてゲート絶縁膜32、ゲート電極33およびp型半導体領域(ソース、ドレイン)35で構成される。nチャネル型MISトランジスタQnのゲート電極33は、例えばゲート絶縁膜32上にCVD法でn型多結晶シリコン膜を堆積した後、フォトレジスト膜(図示せず)をマスクにしたドライエッチングでn型多結晶シリコン膜をパターニングすることによって形成する。同様に、pチャネル型MISトランジスタQpのゲート電極33は、例えばゲート絶縁膜32上にCVD法でp型多結晶シリコン膜を堆積した後、フォトレジスト膜(図示せず)をマスクにしたドライエッチングでp型多結晶シリコン膜をパターニングすることによって形成する。n型半導体領域(ソース、ドレイン)34は、p型ウエル31にn型不純物(例えばリン(P))をイオン注入して形成し、p型半導体領域(ソース、ドレイン)35は、n型ウエル30にp型不純物(例えばホウ素(B))をイオン注入して形成する。

【0037】

次に、図14に示すように、ウエハW2の主面上にCVD法で酸化シリコン膜36を堆積し、続いて酸化シリコン膜36をCMP法で研磨してその表面を平坦化した後、フォトレジスト膜(図示せず)をマスクにして酸化シリコン膜36とその下部のウエハW2とをドライエッチングすることにより、絶縁部26Cから離間してその内側に、絶縁部26Cに取り囲まれるように導電溝4Aを形成する。導電溝4Aの内部には、後の工程で貫通電極4が形成される。ウエハW2の主面から導電溝4Aの底部までの深さは、絶縁溝26Aのそれとほぼ同じ(40μm程度)である。

【0038】

図15に示すように、導電溝4Aの平面形状は長方形であり、その長辺は、例えば5.6μm程度、短辺は、例えば1.7μm程度である。この場合、導電溝4Aの短辺方向におけるアスペクト比は20以上となる。導電溝4Aは、ウエハW2から得られるチップ(C2)1個当たり数千個ずつ形成される。また、特に限定はされないが、本実施の形態1では、このような長方形の導電溝4Aを1個の絶縁部26Cの内側に2個ずつ並べて配置し、これら2個の導電溝4Aを同一の集積回路に接続する構成を採用している。

【0039】

次に、図16に示すように、ウエハW2の主面上にスパッタリング法で厚さ100nm程度の窒化チタン(TiN)膜40を堆積する。窒化チタン膜40は酸化シリコン膜36と導電膜との接着性を向上させる機能がある。続いて、導電溝4Aの内部を含むウエハW2の主面上にCVD法で厚さ20〜30nm程度の窒化チタン膜42を堆積する。窒化チタン膜42は、次の工程で堆積するタングステン(W)膜とウエハW2(シリコン(Si))との反応を防ぐバリア層として機能する。次に、窒化チタン膜42上にCVD法でタングステン膜43を堆積して、導電溝4Aの内部にタングステン膜43を埋め込む。その後、エッチバック法またはCMP法で導電溝4Aの外側のタングステン膜43および窒化チタン膜42を除去して、図17に示すように、導電溝4Aの内部にタングステンを主成分とする導電膜(窒化チタン膜42およびタングステン膜43)が充填された導電部4Cを形成する。

【0040】

次に、図18に示すように、酸化シリコン膜36上にCVD法で酸化シリコン膜37を形成した後、酸化シリコン膜37上にnチャネル型MISトランジスタQnとpチャネル型MISトランジスタQpとを接続する第1層アルミニウム(Al)配線38を形成する。また同時に、導電溝4Aの内部のタングステン膜43とMISトランジスタの一部(例えばpチャネル型MISトランジスタQp)とを接続する第1層アルミニウム配線39を形成する。第1層アルミニウム配線38、39を形成するには、酸化シリコン膜37上にスパッタリング法でアルミニウム合金膜を堆積した後、フォトレジスト膜(図示せず)をマスクにしたドライエッチング法でアルミニウム合金膜をパターニングする。

【0041】

次に、図19に示すように、第1層アルミニウム配線38、39の上層に酸化シリコン膜からなる第1層間絶縁膜44、第2層アルミニウム配線45、酸化シリコン膜からなる第2層間絶縁膜46、第3層アルミニウム配線47、酸化シリコン膜と窒化シリコン膜との積層膜からなる表面保護膜48を順次形成する。続いて、フォトレジスト膜(図示せず)をマスクにしたドライエッチング法で表面保護膜48パターニングして、第3層アルミニウム配線47の一部を露出させる。

【0042】

次に、図20に示すように、ウエハW2の主面上に有機絶縁膜、例えばポリイミド樹脂膜を塗布した後、有機絶縁膜をパターニングして、第3層アルミニウム配線47が露出していない表面保護膜48上に有機絶縁膜からなるスペーサ49を形成する。スペーサ49は、ウエハW2の主面上の表面保護膜48と後の製造工程でウエハW2の主面上に積層されるウエハW3の裏面との間隔とがウエハ面内で均一となるように上記間隔を調整するために設けられる。すなわち、このスペーサ49の厚さは、ウエハW2の主面上の表面保護膜48と後の製造工程でウエハW2の主面上に積層されるウエハW3の裏面との間隔、ウエハ3の裏面から突出する貫通電極4の長さ、および後の製造工程で第3層アルミニウム配線47に接続して形成される第1バンプ電極の厚さなどによって決めることができる。

【0043】

次に、図21に示すように、露出した第3層アルミニウム配線47に接続する第1バンプ電極50を形成する。第1バンプ電極50は、例えばマスク蒸着法で形成され、主にインジウム半田等の低硬度の材料、あるいは温度などの条件により低硬度となりうる金属または合金膜によって構成されて下層の配線と電気的に接続されている。同時に、スペーサ49上にも第2バンプ電極50aを形成する。この第2バンプ電極50aは、ウエハW2に形成された素子とは電気的に接続されておらず、素子の動作には何ら寄与しない。

【0044】

次に、図22〜図26を用いて、ウエハW3の裏面を研磨する工程、ウエハW2,W3を貼り合わせる工程、ウエハW2,W3間に接着剤を注入する工程およびウエハW2の裏面を研磨する工程について説明する。

【0045】

上記と同様の方法で集積回路および導電部4C等が形成されたウエハW3を準備する。但し、ウエハW3は最上層に位置することから、第1バンプ電極50は形成されていない。

【0046】

次に、図22に示すように、ウエハW3の裏面を、例えばCMP法などにより研磨して所定の厚さまで薄く加工する。研磨を実施したこの段階では、導電溝4Aおよび絶縁溝26AはウエハW3の裏面には露出させない。これは、研磨により導電溝4Aの内部に充填した導電膜(窒化チタン膜42およびタングステン膜43)が破壊されるのを防ぐためと、ウエハW3に物理的なダメージ層が残留しないように、後の製造工程で非物理的な方法によりウエハW3を薄く加工する余裕を残すためである。

【0047】

次に、図23に示すように、ウエハW3の裏面を、例えばフッ酸と硝酸との混合溶液、またはそれに類するシリコンエッチング溶液を用いたウエットエッチング法により、エッチングする。ウエットエッチング法に代えてドライエッチング法によりウエハW3の裏面を選択的にエッチングしてもよい。これにより、ウエハW3の厚さを、例えば30μm程度とし、ウエハW3の裏面から導電部4Cを突出させて貫通電極4を形成し、絶縁部26Cを突出させて貫通分離部26を形成する。

【0048】

次に、図24に示すように、ウエハW2とウエハW3とを接近させて、ウエハW3に形成された貫通電極4とウエハW2に形成された第1バンプ電極50とを物理的に接触させる。この際、第1バンプ電極50に貫通電極4を刺すことにより、ウエハW2に形成された素子とウエハW3形成された素子との電気的接続を確保する。また、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間で、貫通電極4が形成されていない領域には、スペーサ49上に第2バンプ電極50aが積層された支持部が形成されている。スペーサ49と第2バンプ電極50aとを積層した厚さが、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔とほぼ同じになるようにスペーサ49の厚さは設定されているので、貫通電極4が形成されていない領域であってもウエハW3がたわむことがなく、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔をウエハ面内で均一に保つことができる。

【0049】

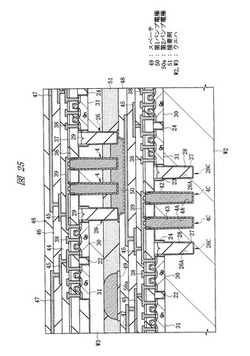

次に、図25に示すように、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間に、充填材としての機能も有する接着剤51を充填し、ウエハW2とウエハW3とを固定する。ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔がウエハ面内で均一であることから、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間に接着剤51が入りやすく、接着剤51の未充填箇所の形成を防ぐことができるので、物理的な強度を確保することができる。接着剤51には絶縁性を持つ樹脂、例えばエポキシ樹脂などの熱硬化樹脂などを用いることができるが、これと同等の接着性、強度および絶縁性を有する材料であれば材質は問わない。

【0050】

次に、図26に示すように、ウエハW2の裏面を前述したウエハW3と同様にして研磨することにより、ウエハW2の厚さを、例えば30μm程度とし、ウエハW2の裏面から導電部4Cを突出させて貫通電極4を形成し、絶縁部26Cを突出させて貫通分離部26を形成する。

【0051】

次に、図27を用いて、ウエハW1とウエハW2,W3を貼り合わせる工程およびウエハW1,W2間に接着剤を注入する工程について説明する。

【0052】

上記と同様の方法で集積回路および第1バンプ電極50が形成されたウエハW1を準備する。ウエハW1は最下層に位置することから、導電部4Cは形成されていない。

【0053】

さらに、図27に示すように、上記と同様の方法でウエハW1の主面上に、すでに積層して貼り合わせてあるウエハW2,W3を接近させて、ウエハW2に形成された貫通電極4とウエハW1に形成された第1バンプ電極50とを物理的に接触させる。続いて、ウエハ1の主面上の表面保護膜48とウエハW2の裏面との間に充填材としての機能も有する接着剤51を充填し、ウエハW1とウエハW2,W3とを固定する。その後、これらのウエハW1,W2,W3をダイシングして3次元構造のチップC1,C2,C3に個片化し、これを配線基板1に実装してモールド樹脂2で封止することにより、前記図1に示すパッケージが完成する。

【0054】

なお、本実施の形態1では、1つのスペーサ49上に1つの第2バンプ電極50aを形成したが、これに限定されるものではなく、例えば1つのスペーサ49上に複数の第2バンプ電極50aを形成してもよく、または2つ以上のスペーサ49に跨って1つの第2バンプ電極50aを形成してもよい。

【0055】

このように、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間で、ウエハW1の第3層アルミニウム配線47に接続する第1バンプ電極50が形成されていない領域に、スペーサ49と第2バンプ電極50aとを積層した支持部を形成することにより、ウエハW2のたわみを防いで、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間隔をウエハ面内で均一に保つことができる。同様にして、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔をウエハ面内で均一に保つことができる。これによって、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間またはウエハW2の主面上の表面保護膜48とウエハW3の裏面との間に接着剤51を余すところなく充填できるので、ウエハW1,W2,W3を積層して貼り合わせた後に、積層したウエハW1,W2,W3を積層したチップC1,C2,C3に個片化して半導体装置を形成しても、積層したチップC1,C2,C3の分離を防ぐことができる。

【0056】

(実施の形態2)

本発明の実施の形態2による半導体装置を示す半導体ウエハの要部断面図を図28に示す。

【0057】

前述した実施の形態1では、例えばウエハW1(下に位置するウエハ)とウエハW2(上に位置するウエハ)とを積層して貼り合わせた場合、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間で、ウエハW1の第3層アルミニウム配線47に接続する第1バンプ電極50が形成されていない領域に、スペーサ49と第2バンプ電極50aとを積層した支持部を形成することにより、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間隔をウエハ面内で均一に保っている。

【0058】

しかしながら、本実施の形態2では、ウエハW1とウエハW2とを積層して貼り合わせた場合、ウエハW1の第3層アルミニウム配線47に接続する第1バンプ電極50が形成されていない領域に、ウエハW1の第3層アルミニウム配線47に接続する第1バンプ電極50が形成されている領域よりも厚い表面保護膜48をウエハW1に形成し、さらにウエハW1の第3層アルミニウム配線47に接続する第1バンプ電極50が形成されていない領域の表面保護膜48上に第2バンプ電極50aを形成する。これによって、ウエハW2の裏面から貫通電極4が突出していない領域に、相対的に厚い表面保護膜48と第2バンプ電極50aとを積層した支持部を形成することができるので、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間隔をウエハ面内で均一に保つことができる。また、本実施の形態2では、前述した実施の形態1で用いたスペーサ49を形成する必要がないので、前述した実施の形態1よりも製造コストを低減することができる。

【0059】

膜厚が厚い領域と膜厚が薄い領域とを有する上記表面保護膜48は、例えば第3層アルミニウム配線47が形成されたウエハW1の主面上にCVD法で表面保護膜48を形成し、第1バンプ電極50が形成される領域の表面保護膜48を薄く加工した後、第1バンプ電極50が形成される領域の第3層アルミニウム配線47が露出するように表面保護膜48を加工することにより形成することができる。あるいは、第1バンプ電極50が形成される領域の第3層アルミニウム配線47が露出するように、表面保護膜48を加工した後、第1バンプ電極50が形成される領域の表面保護膜48を薄く加工してもよい。

【0060】

(実施の形態3)

本発明の実施の形態3による半導体装置を示す半導体ウエハの要部断面図を図29に示す。ここでは、積層して貼り合わせたウエハW1とウエハW2とを用いて説明する。

【0061】

前述した実施の形態1では、貫通電極4から離間した位置に貫通電極4を取り囲むように、貫通分離部26を形成している。

【0062】

しかしながら、本実施の形態3では、貫通分離部26の内部に多結晶シリコン膜28を貫通してタングステンを主成分とする導電膜からなる貫通電極4が形成されている。貫通分離部26は、貫通孔26aの側面を覆うように形成された酸化シリコン膜27と、この酸化シリコン膜27の側面を覆うように形成された多結晶シリコン膜28と、この多結晶シリコン膜28の上面を覆うように形成されたキャップ絶縁膜29とを有している。貫通電極4は、導電溝4Aの内側に形成された窒化チタン膜42およびタングステン膜43とを有している。貫通分離部26の内部に貫通電極4を形成することにより、貫通分離部26を用いてウエハW2と貫通電極4との電気的な絶縁を行うことができ、かつ、貫通電極4を構成する導電膜からの汚染の拡散を抑えて素子の電気的特性の劣化を防止することができる。

【0063】

このように貫通分離部26の内部に貫通電極4が形成された構造であっても、前述した実施の形態1と同様に、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間で、貫通電極4が形成されていない領域に、スペーサ49と第2バンプ電極50aとが積層された支持部を形成することにより、ウエハW2のたわみを防いで、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間隔をウエハ面内で均一に保つことができる。

【0064】

貫通分離部26の内部に形成される貫通電極4は、例えば以下に説明する製造方法により形成することができる。

【0065】

まず、図30に示すように、ウエハW2の主面に素子分離溝22および溝23を形成した後、素子分離溝22および溝23の内部に酸化シリコン膜24を埋め込む。

【0066】

次に、図31に示すように、ウエハW2の主面上に絶縁膜、例えば窒化シリコン膜25をCVD法で堆積した後、レジストパターン(図示は省略)をマスクとして、そこから露出する窒化シリコン膜25、酸化シリコン膜24およびウエハW2を順にエッチング除去することにより、ウエハW2の主面に絶縁溝26Aを形成する。この絶縁溝26Aは、前述した貫通孔26aを形成することになる溝であり、ウエハW2の主面からウエハW2の厚さ方向の途中の位置であって溝23の深さよりも深い位置まで延びるように形成されている。

【0067】

続いて、ウエハW2に対して熱酸化処理を施すことにより、絶縁溝26Aの内壁(側面および底面)のウエハW2の露出面に絶縁膜、例えば酸化シリコン膜27を形成する。この絶縁膜は、熱酸化処理により形成された酸化シリコン膜27に限定されるものではなく、例えばCVD法で形成される酸化シリコン、窒化シリコン、酸窒化シリコンなどを絶縁膜に用いることもできる。

【0068】

続いて、ウエハW2の主面上に、絶縁溝26Aが充填されるように埋込膜、例えば多結晶シリコン膜28をCVD法で堆積する。続いて、多結晶シリコン膜28を異方性のドライエッチング法によってエッチバックすることにより、絶縁溝26Aの外部の余分な多結晶シリコン膜28を除去し、絶縁溝26A内のみに多結晶シリコン膜28を残すようにする。

【0069】

続いて、ウエハW2の主面上に、多結晶シリコン膜28の上部の窪みが埋め込まれるように、例えば酸化シリコンからなるキャップ絶縁膜29をCVD法で堆積する。続いて、キャップ絶縁膜29をCMP法で研磨することにより、多結晶シリコン膜28の上部の窪みの外部の余分なキャップ絶縁膜29を除去し、多結晶シリコン膜28の上部の窪み内のみにキャップ絶縁膜29を残すようにする。このようにして多結晶シリコン膜28の上面をキャップ絶縁膜29により覆う。その後、窒化シリコン膜25をウエットエッチング法によって除去する。

【0070】

次に、図32に示すように、ウエハW2の主面の素子形成領域に集積回路素子を形成する。集積回路を構成する集積回路素子の例としては、MISトランジスタ、バイポーラトランジスタやダイオード等のような能動素子がある。また、上記集積回路素子の他の例としては、抵抗、キャパシタおよびインダクタ等のような受動素子がある。ここでは、素子として、nチャネル型MISトランジスタが例示されており、前述した実施の形態1に例示したnチャネル型MISトランジスタQnと同様の製造方法により形成することができる。

【0071】

次に、図33に示すように、ウエハW2の主面上に酸化シリコン膜36をCVD法で堆積した後、レジストパターン(図示は省略)をマスクとして、そこから露出する酸化シリコン膜36、キャップ絶縁膜29および多結晶シリコン膜28を順にエッチング除去する。これにより、ウエハW2の主面に導電溝4Aを形成する。この導電溝4Aは、ウエハW2の主面の酸化シリコン膜36の上面からウエハW2の厚さ方向に、絶縁溝26A内の底面の酸化シリコン膜27まで延びるように形成されている。

【0072】

続いて、ウエハW2の主面上に窒化チタン膜42をスパッタリング法で堆積した後、タングステン膜43をCVD法で堆積し、窒化チタン膜42およびタングステン膜43により導電溝4Aを埋め込む。続いて、タングステン膜43および窒化チタン膜42をCMP法で研磨することにより、導電溝4Aの外部の余分なタングステン膜43および窒化チタン膜42を除去し、導電溝4A内のみにタングステン膜43および窒化チタン膜42を残すようにする。このようにして導電溝4A内にタングステン膜43および窒化チタン膜42が埋め込まれて導電部4Cを形成する。導電部4Cは貫通電極4を形成する部分であり、この導電部4Cの構成はウエハW2の主裏面間を貫通していないことを除いて貫通電極4と同じである。

【0073】

次に、図34に示すように、配線層を形成する。ここでは、配線層として、3層配線構成の配線層が例示されており、前述した実施の形態1に例示した配線層と同様の製造方法により形成することができる。さらに、前述した実施の形態1と同様にして、表面保護膜48上にスペーサ49を形成し、続いて露出した第3層アルミニウム配線47に接続する第1バンプ電極50を形成し、スペーサ49上に第2バンプ電極50aを形成する。

【0074】

次に、図35に示すように、ウエハW2の裏面を、例えばCMP法で研磨して所定の厚さまで薄く加工した後、ウエハW2の裏面を、例えばフッ酸と硝酸との混合溶液、またはそれに類するシリコンエッチング溶液を用いたウエットエッチング法により、エッチングする。ウエットエッチング法に代えてドライエッチング法によりウエハW2の裏面を選択的にエッチングしてもよい。エッチングを実施したこの段階では、酸化シリコン膜27は露出しているが、導電部4Cは酸化シリコン膜27により覆われている。続いて、露出した酸化シリコン膜27をエッチング法により除去する。これにより、貫通孔26aの側面を覆う酸化シリコン膜27、多結晶シリコン膜28およびキャップ絶縁膜29からなる貫通分離部26が形成され、さらにその内部に形成されて裏面から突出する貫通電極4を形成する。

【0075】

なお、本実施の形態3は、前述した実施の形態1で説明したスペーサ49と第2バンプ電極50aとを積層した支持部を有する半導体装置に適用した場合について説明したが、前述した実施の形態2で説明した相対的に厚く形成された表面保護膜48上に第2バンプ電極50aを積層した支持部を有する半導体装置にも適用できることは言うまでもない。

【0076】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0077】

本発明は、複数枚のチップを積層して貼り合わせた3次元構造の半導体装置に適用することができる。

【図面の簡単な説明】

【0078】

【図1】本発明の実施の形態1による半導体装置を配線基板に実装して樹脂封止したパッケージの一例を示す断面図である。

【図2】本発明の実施の形態1による半導体装置の製造工程を示すフロー図である。

【図3】本発明の実施の形態1による半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図4】図3に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図5】溝の平面形状を示す半導体ウエハの要部平面図である。

【図6】図4に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図7】図6に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図8】絶縁溝の平面形状を示す半導体ウエハの要部平面図である。

【図9】図7に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図10】図9に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図11】図10に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図12】図11に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図13】図12に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図14】図13に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図15】導電溝の平面形状を示す半導体ウエハの要部平面図である。

【図16】図14に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図17】図16に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図18】図17に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図19】図18に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図20】図19に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図21】図20に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図22】図21に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図23】図22に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図24】図23に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図25】図24に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図26】図25に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図27】図26に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図28】本発明の実施の形態2による半導体装置を示す半導体ウエハの要部断面図である。

【図29】本発明の実施の形態3による半導体装置を示す半導体ウエハの要部断面図である。

【図30】本発明の実施の形態3による半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図31】図30に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図32】図31に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図33】図32に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図34】図33に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図35】図34に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【符号の説明】

【0079】

1 配線基板

2 モールド樹脂

3 接着剤

4 貫通電極

4A 導電溝

4C 導電部

5 ボンディングパッド

6 電極

7 ワイヤ

8 配線

9 半田バンプ

20 酸化シリコン膜

21 窒化シリコン膜

22 素子分離溝

23 溝

24,24a 酸化シリコン膜

25 窒化シリコン膜

26 貫通分離部

26A 絶縁溝

26C 絶縁部

26a 貫通孔

27 酸化シリコン膜

28 多結晶シリコン膜

29 キャップ絶縁膜

30 n型ウエル

31 p型ウエル

32 ゲート絶縁膜

33 ゲート電極

34 n型半導体領域(ソース、ドレイン)

35 p型半導体領域(ソース、ドレイン)

36,37 酸化シリコン膜

38,39 第1層アルミニウム配線

40 窒化チタン膜

42 窒化チタン膜

43 タングステン膜

44 第1層間絶縁膜

45 第2層アルミニウム配線

46 第2層間絶縁膜

47 第3層アルミニウム配線

48 表面保護膜

49 スペーサ

50 第1バンプ電極

50a 第2バンプ電極

51 接着剤

C1,C2,C3 半導体チップ

Qn nチャネル型MISトランジスタ

Qp pチャネル型MISトランジスタ

W1,W2,W3 半導体ウエハ

【技術分野】

【0001】

本発明は、半導体装置の製造方法および半導体装置に関し、特に3次元構造の半導体装置の製造方法および半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

3次元構造の半導体装置は、半導体活性層を多層に積み重ねた構造に3次元的に半導体素子を集積することにより、2次元構造の半導体装置が直面する種々の障壁、例えば微細化におけるリソグラフィ技術の限界、配線の微細化や配線長増大による配線抵抗の増大や寄生効果の増大、またそれに伴う動作速度の飽和傾向、素子寸法の微細化による高電界効果等を回避し、集積度の向上を維持する有力な構造として注目されている。

【0003】

3次元構造の半導体装置については、例えば特開平11−261000号公報(特許文献1)または特開2002−334967号公報(特許文献2)に記載があり、半導体素子が形成された半導体基板を貼り合せることにより3次元構造の半導体装置を製造する方法が開示されている。また、これらの文献には、所望の半導体基板の主裏面間を貫通する溝内に垂直相互接続体または埋込接続電極と称する貫通電極を形成し、半導体基板の主裏面間を導通可能なようにする構成が開示されている。

【0004】

また、特開2006−165025号公報(特許文献3)または特開2003−17558号公報(特許文献4)には、半導体基板中に貫通電極を備えた半導体装置および貫通電極の形成方法が開示されている。

【0005】

また、特開2007−281393号公報(特許文献5)には、導電性材料からなる突起電極と、突起電極よりも大きな高さをもつダミーの突起部とを基板上に有しており、突起部を利用して間隙を決定し、突起部の内側領域において電子部品の表面に付着された電気絶縁材によって所定の間隙を正確に保持する半導体装置が開示されている。

【特許文献1】特開平11−261000号公報

【特許文献2】特開2002−334967号公報

【特許文献3】特開2006−165025号公報

【特許文献4】特開2003−17558号公報

【特許文献5】特開2007−281393号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

複数枚のチップが積層されて構成される3次元構造の半導体装置では、上に位置するチップとこれに対向して下に位置するチップとの間において互いの信号を伝達する手段の一つとして貫通電極が用いられている。また、上に位置するチップとこれに対向して下に位置するチップとの間隔は、例えば5〜30μm程度であり、その間には、両チップを貼り合わせる接着剤として機能する樹脂が充填されている。

【0007】

しかしながら、貫通電極を有する3次元構造の半導体装置については、その製造過程において、以下に説明する種々の技術的課題が存在する。

【0008】

上記貫通電極は半導体装置の回路構成に依存して局在することから、多数の貫通電極が配置された領域と、貫通電極が配置されない領域とが存在する。貫通電極が配置された領域では、上に位置するウエハとこれに対向して下に位置するウエハとの間隔は貫通電極の長さで決まる。しかし、貫通電極が配置されていない領域では、上に位置するウエハの厚さが、例えば30μm程度と薄いため、上に位置するウエハがたわむことによって、上に位置するウエハとこれに対向して下に位置するウエハとの間隔が、貫通電極が配置された領域の上に位置するウエハとこれに対向して下に位置するウエハとの間隔よりも20%程度狭くなる。このため、上に位置するウエハとこれに対向して下に位置するウエハとの間隔にばらつきが生じてしまう。

【0009】

上に位置するウエハとこれに対向して下に位置するウエハとの間隔が狭いところでは樹脂が注入されにくくなり、上に位置するウエハとこれに対向して下に位置するウエハとの間に樹脂が充填されない箇所が形成されてしまう。複数枚のウエハを積層して貼り合わせた後に、積層した複数枚のウエハは、例えばダイシングにより個々の積層した複数枚のチップに個片化されて半導体装置が形成されるが、その時、樹脂が充填されない箇所では、上に位置するチップとこれに対向して下に位置するチップとが分離して、半導体装置が破壊するという問題が発生する。

【0010】

本発明の目的は、貫通電極を有する3次元構造の半導体装置の製造歩留まりを向上させることのできる技術を提供することにある。

【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの一実施の形態を簡単に説明すれば、次のとおりである。

【0013】

この実施の形態は、複数枚の半導体ウエハを貼り合わせ、各々の半導体ウエハの半導体チップに形成された集積回路同士を互いに電気的に接続することにより所望の集積回路を形成する半導体装置の製造方法である。まず、第2ウエハの主面上に最上層配線を覆う表面保護膜を形成した後、表面保護膜を加工して最上層配線の一部を露出させる。続いて、第2ウエハの主面上に絶縁膜を形成した後、この絶縁膜を加工して最上層配線が露出していない領域の表面保護膜上に絶縁膜からなるスペーサを形成する。続いて、同一工程で第2ウエハの主面上の露出した最上層配線上に第1バンプ電極を、スペーサ上に第2バンプ電極を形成する。その後、第2ウエハの主面上に形成された第1バンプ電極に、第1ウエハの裏面から突出する貫通電極を物理的に接触させ、さらに第1ウエハの裏面と第2ウエハの主面上の表面保護膜との間に樹脂を充填するものである。

【0014】

また、この実施の形態は、複数枚の半導体ウエハを貼り合わせ、各々の半導体ウエハの半導体チップに形成された集積回路同士を互いに電気的に接続することにより所望の集積回路を形成する半導体装置の製造方法である。まず、第2ウエハの主面上に最上層配線を覆う表面保護膜を形成した後、表面保護膜を加工して第1バンプ電極が形成される領域の表面保護膜の厚さを第1バンプ電極が形成されない領域の表面保護膜の厚さよりも薄くし、さらに表面保護膜を加工して第1バンプ電極が形成される領域の最上層配線の一部を露出させる。続いて、同一工程で第2ウエハの主面上の露出した最上層配線上に第1バンプ電極を最上層配線が露出していない表面保護膜上に第2バンプ電極を形成する。その後、第2ウエハの主面上に形成された第1バンプ電極に、第1ウエハの裏面から突出する貫通電極を物理的に接触させ、さらに第1ウエハの裏面と第2ウエハの主面上の表面保護膜との間に樹脂を充填するものである。

【0015】

また、この実施の形態は、複数枚の半導体チップが貼り合わされ、各々の半導体チップに形成された集積回路同士が互いに電気的に接続されてなる所望の集積回路を備える半導体装置である。この半導体装置は、主面上に形成された複数の第1集積回路と、裏面から突出する貫通電極とを含む第1チップと、主面上に形成された複数の第2集積回路と、複数の第2集積回路のいずれかに電気的に接続されて主面上に形成された複数層の配線と、最上層配線の一部を露出して主面上に形成された表面保護膜と、表面保護膜上に形成されたスペーサと、表面保護膜から露出する最上層配線と電気的に接続して形成された第1バンプ電極と、スペーサ上に形成された第2バンプ電極とを含む第2チップとを有し、第1チップの裏面から突出する貫通電極が第2チップの主面上の第1バンプ電極と物理的に接触しており、第1チップの裏面と第2チップの主面上の表面保護膜との間に樹脂が充填されているものである。

【0016】

また、この実施の形態は、複数枚の半導体チップが貼り合わされ、各々の半導体チップに形成された集積回路同士が互いに電気的に接続されてなる所望の集積回路を備える半導体装置である。この半導体装置は、主面上に形成された複数の第1集積回路と、裏面から突出する貫通電極とを含む第1チップと、主面上に形成された複数の第2集積回路と、複数の第2集積回路のいずれかに電気的に接続されて主面上に形成された複数層の配線と、最上層配線の一部を露出して主面上に形成された表面保護膜と、表面保護膜から露出する最上層配線と電気的に接続して形成された第1バンプ電極と、表面保護膜上に形成された第2バンプ電極とを含む第2チップとを有し、第1バンプ電極が形成された領域の表面保護膜の厚さは、第2バンプ電極が形成される領域の表面保護膜の厚さよりも薄く、第1チップの裏面から突出する貫通電極が第2チップの主面上の第1バンプ電極と物理的に接触しており、第1チップの裏面と第2チップの主面上の表面保護膜との間に樹脂が充填されているものである。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものの一実施の形態によって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

上に位置するウエハ(第1ウエハ)とこれに対向して下に位置するウエハ(第2ウエハ)との間隔をウエハ面内で均一に保つことができるので、上に位置するウエハとこれに対向して下に位置するウエハとの間に接着剤である樹脂を余すところなく充填することができる。これにより、積層した複数枚のウエハを積層した複数枚のチップに個片化して半導体装置を形成しても、積層されたチップの分離を防ぐことができるので、貫通電極を有する3次元構造の半導体装置の製造歩留まりを向上させることができる。

【発明を実施するための最良の形態】

【0019】

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0020】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0021】

また、以下の実施の形態で用いる図面においては、平面図であっても図面を見易くするためにハッチングを付す場合もある。また、以下の実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0022】

(実施の形態1)

本実施の形態1の半導体装置は、互いに異なる集積回路が形成された3枚の半導体チップ(以下、単にチップという)C1,C2,C3を積層して貼り合わせた3次元構造を有している。図1は、この半導体装置を配線基板1に実装してモールド樹脂2で封止したパッケージの一例を示す断面図である。

【0023】

配線基板1に実装された3枚のチップC1,C2,C3のうち、最下層のチップC1は、接着剤3を介して配線基板1に接着されている。また、中間層のチップC2は、接着剤3を介してチップC1に接着されており、最上層のチップC3は、接着剤3を介してチップC2に接着されている。後に詳しく説明するが、最下層のチップC1に形成された集積回路と中間層のチップC2に形成された集積回路は、チップC2に形成された複数の貫通電極4を介して電気的に接続され、中間層のチップC2に形成された集積回路と最上層のチップC3に形成された集積回路は、チップC3に形成された複数の貫通電極4を介して電気的に接続されている。すなわち、本実施の形態1の半導体装置は、チップC1,C2,C3に形成された集積回路を貫通電極4を介して互いに接続することによって、所望のシステムを実現している。

【0024】

上記チップC1,C2,C3と配線基板1は、最上層のチップC3に形成された複数のボンディングパッド5と配線基板1上に形成された複数の電極6との間にボンディングされた複数本の金(Au)ワイヤ7を介して電気的に接続されている。電極6は、配線基板1内の銅(Cu)配線8を介して、配線基板1の裏面の半田バンプ9に電気的に接続されている。半田バンプ9は、図1に示すパッケージをマザーボードなどに実装する際の外部接続端子を構成している。

【0025】

図2は、本実施の形態1の半導体装置の製造工程を示すフロー図である。この半導体装置の製造工程は、半導体ウエハ(以下、単にウエハという)W1,W2,W3に互いに異なる集積回路を形成し、ウエハW2,W3に導電部を形成する工程と、ウエハW1,W2にバンプ電極を形成する工程と、ウエハW3の裏面を研磨して導電部を露出させることによって貫通電極4を形成する工程と、ウエハW2,W3を貼り合わせ、ウエハW3に備わる貫通電極4とウエハW2に備わるバンプ電極とを介して集積回路同士を電気的に接続する工程と、ウエハW2,W3間に接着剤を注入する工程と、ウエハW2の裏面を研磨して導電部を露出させることによって貫通電極4を形成する工程と、ウエハW1,(W2+W3)を貼り合わせ、ウエハW2に備わる貫通電極4とウエハW1に備わるバンプ電極とを介して集積回路同士を電気的に接続する工程と、ウエハW1,(W2+W3)間に接着剤を注入する工程と、ウエハW1,W2,W3をダイシングすることによって、3次元構造のチップC1,C2,C3を形成する工程と、チップC1,C2,C3をパッケージング(基板実装、ワイヤボンディング、樹脂封止)する工程とに大別される。

【0026】

以下、3枚のウエハW1,W2,W3を用いた半導体装置の製造方法を工程順に説明する。

【0027】

まず、図3〜図21を用いて、ウエハに集積回路と導電部とを形成する工程およびウエハにバンプ電極を形成する工程について説明する。ここでの説明では、貼り合わせた時に中間に位置するウエハW2を用いる。

【0028】

図3に示すように、単結晶シリコンからなる厚さ780μm程度のウエハW2を用意する。そして、このウエハW2を熱処理してその主面(集積回路を形成する面)に厚さ10nm程度の薄い酸化シリコン膜20を形成し、続いて酸化シリコン膜20上にCVD(Chemical Vapor Deposition)法で窒化シリコン膜21を堆積した後、フォトレジスト膜(図示せず)をマスクにしたドライエッチングで素子分離溝形成領域の窒化シリコン膜21と酸化シリコン膜20とを除去する。ウエハW2と窒化シリコン膜21との間に形成する酸化シリコン膜20は、ウエハW2と窒化シリコン膜21との界面に生じる応力を緩和し、この応力に起因してウエハW2の表面に転位などの欠陥が発生するのを防ぐためのバッファ層である。

【0029】

次に、図4に示すように、窒化シリコン膜21をマスクにしたドライエッチングにより、素子分離溝形成領域のウエハW2に深さ350nm程度の素子分離溝22を形成し、後に貫通電極4を形成する領域の近傍のウエハW2に深さ350nm程度の溝23を形成する。溝23の平面形状は、例えば図5に示すような四角枠状とする。

【0030】

次に、図6に示すように、ウエハW2を熱処理することによって、素子分離溝22および溝23の内壁に酸化シリコン膜24aを形成した後、ウエハW2の主面上にCVD法で酸化シリコン膜24を堆積し、続いて素子分離溝22および溝23のそれぞれの外部の酸化シリコン膜24をCMP(Chemical Mechanical Polishing)法で研磨、除去することによって、素子分離溝22の内部および溝23の内部に酸化シリコン膜24を残す。

【0031】

次に、窒化シリコン膜21をエッチングして除去した後、図7に示すように、ウエハW2の主面上にCVD法で窒化シリコン膜25を堆積する。続いて、フォトレジスト膜(図示せず)をマスクにしたドライエッチングで溝23の上部の窒化シリコン膜25、溝23の内部の酸化シリコン膜24および溝23の下方のウエハW2を順次エッチングすることにより、溝23の内側に、例えば深さ40μm程度の絶縁溝26Aを形成する。図8に示すように、絶縁溝26Aは、溝23に沿って形成し、その幅を溝23の幅よりも狭くする。絶縁溝26Aの幅は、例えば2μm程度である。

【0032】

次に、図9に示すように、ウエハW2を1000℃程度で熱処理することによって、絶縁溝26Aの内壁に酸化シリコン膜27を形成する。続いて、図10に示すように、ウエハW2の主面上にCVD法で多結晶シリコン膜28を堆積した後、絶縁溝26Aの外部の多結晶シリコン膜28をエッチバックで除去することにより、絶縁溝26Aの内部に多結晶シリコン膜28を残す。このとき、絶縁溝26Aの内部の多結晶シリコン膜28は、その表面の高さをウエハW2の表面よりも低くする。

【0033】

次に、ウエハW2の主面上にCVD法で酸化シリコン膜を堆積した後、絶縁溝26Aの外部の酸化シリコン膜をCMP法で研磨、除去することにより、図11に示すように、絶縁溝26Aの内部の多結晶シリコン膜28上に酸化シリコン膜からなるキャップ絶縁膜29を形成する。ここまでの工程により、多結晶シリコン膜28の周囲を酸化シリコン膜27とキャップ絶縁膜29とで囲んだ絶縁部26Cが完成する。絶縁部26Cは、後の工程でウエハW2の主面に形成する集積回路素子と導電部(貫通電極4)とを電気的に分離するために形成する。また、絶縁溝26Aの内壁に酸化シリコン膜27を形成する際には、ウエハW2を1000℃程度で熱処理するので、絶縁部26Cは、集積回路素子よりも先に形成しておくことが望ましい。

【0034】

次に、窒化シリコン膜25をエッチングして除去した後、図12に示すように、ウエハW2の素子形成領域にn型不純物とp型不純物とをイオン注入することによって、n型ウエル30とp型ウエル31とを形成する。

【0035】

次に、ウエハW2の表面をウエットエッチングして酸化シリコン膜20を除去し、続いてウエハW2を熱処理してその表面にゲート絶縁膜32を形成した後、図13に示すように、周知のMIS(Metal Insulator Semiconductor)トランジスタ形成プロセスに従ってp型ウエル31にnチャネル型MISトランジスタQnを形成し、n型ウエル30にpチャネル型MISトランジスタQpを形成する。

【0036】

nチャネル型MISトランジスタQnは、主としてゲート絶縁膜32、ゲート電極33およびn型半導体領域(ソース、ドレイン)34で構成され、pチャネル型MISトランジスタQpは、主としてゲート絶縁膜32、ゲート電極33およびp型半導体領域(ソース、ドレイン)35で構成される。nチャネル型MISトランジスタQnのゲート電極33は、例えばゲート絶縁膜32上にCVD法でn型多結晶シリコン膜を堆積した後、フォトレジスト膜(図示せず)をマスクにしたドライエッチングでn型多結晶シリコン膜をパターニングすることによって形成する。同様に、pチャネル型MISトランジスタQpのゲート電極33は、例えばゲート絶縁膜32上にCVD法でp型多結晶シリコン膜を堆積した後、フォトレジスト膜(図示せず)をマスクにしたドライエッチングでp型多結晶シリコン膜をパターニングすることによって形成する。n型半導体領域(ソース、ドレイン)34は、p型ウエル31にn型不純物(例えばリン(P))をイオン注入して形成し、p型半導体領域(ソース、ドレイン)35は、n型ウエル30にp型不純物(例えばホウ素(B))をイオン注入して形成する。

【0037】

次に、図14に示すように、ウエハW2の主面上にCVD法で酸化シリコン膜36を堆積し、続いて酸化シリコン膜36をCMP法で研磨してその表面を平坦化した後、フォトレジスト膜(図示せず)をマスクにして酸化シリコン膜36とその下部のウエハW2とをドライエッチングすることにより、絶縁部26Cから離間してその内側に、絶縁部26Cに取り囲まれるように導電溝4Aを形成する。導電溝4Aの内部には、後の工程で貫通電極4が形成される。ウエハW2の主面から導電溝4Aの底部までの深さは、絶縁溝26Aのそれとほぼ同じ(40μm程度)である。

【0038】

図15に示すように、導電溝4Aの平面形状は長方形であり、その長辺は、例えば5.6μm程度、短辺は、例えば1.7μm程度である。この場合、導電溝4Aの短辺方向におけるアスペクト比は20以上となる。導電溝4Aは、ウエハW2から得られるチップ(C2)1個当たり数千個ずつ形成される。また、特に限定はされないが、本実施の形態1では、このような長方形の導電溝4Aを1個の絶縁部26Cの内側に2個ずつ並べて配置し、これら2個の導電溝4Aを同一の集積回路に接続する構成を採用している。

【0039】

次に、図16に示すように、ウエハW2の主面上にスパッタリング法で厚さ100nm程度の窒化チタン(TiN)膜40を堆積する。窒化チタン膜40は酸化シリコン膜36と導電膜との接着性を向上させる機能がある。続いて、導電溝4Aの内部を含むウエハW2の主面上にCVD法で厚さ20〜30nm程度の窒化チタン膜42を堆積する。窒化チタン膜42は、次の工程で堆積するタングステン(W)膜とウエハW2(シリコン(Si))との反応を防ぐバリア層として機能する。次に、窒化チタン膜42上にCVD法でタングステン膜43を堆積して、導電溝4Aの内部にタングステン膜43を埋め込む。その後、エッチバック法またはCMP法で導電溝4Aの外側のタングステン膜43および窒化チタン膜42を除去して、図17に示すように、導電溝4Aの内部にタングステンを主成分とする導電膜(窒化チタン膜42およびタングステン膜43)が充填された導電部4Cを形成する。

【0040】

次に、図18に示すように、酸化シリコン膜36上にCVD法で酸化シリコン膜37を形成した後、酸化シリコン膜37上にnチャネル型MISトランジスタQnとpチャネル型MISトランジスタQpとを接続する第1層アルミニウム(Al)配線38を形成する。また同時に、導電溝4Aの内部のタングステン膜43とMISトランジスタの一部(例えばpチャネル型MISトランジスタQp)とを接続する第1層アルミニウム配線39を形成する。第1層アルミニウム配線38、39を形成するには、酸化シリコン膜37上にスパッタリング法でアルミニウム合金膜を堆積した後、フォトレジスト膜(図示せず)をマスクにしたドライエッチング法でアルミニウム合金膜をパターニングする。

【0041】

次に、図19に示すように、第1層アルミニウム配線38、39の上層に酸化シリコン膜からなる第1層間絶縁膜44、第2層アルミニウム配線45、酸化シリコン膜からなる第2層間絶縁膜46、第3層アルミニウム配線47、酸化シリコン膜と窒化シリコン膜との積層膜からなる表面保護膜48を順次形成する。続いて、フォトレジスト膜(図示せず)をマスクにしたドライエッチング法で表面保護膜48パターニングして、第3層アルミニウム配線47の一部を露出させる。

【0042】

次に、図20に示すように、ウエハW2の主面上に有機絶縁膜、例えばポリイミド樹脂膜を塗布した後、有機絶縁膜をパターニングして、第3層アルミニウム配線47が露出していない表面保護膜48上に有機絶縁膜からなるスペーサ49を形成する。スペーサ49は、ウエハW2の主面上の表面保護膜48と後の製造工程でウエハW2の主面上に積層されるウエハW3の裏面との間隔とがウエハ面内で均一となるように上記間隔を調整するために設けられる。すなわち、このスペーサ49の厚さは、ウエハW2の主面上の表面保護膜48と後の製造工程でウエハW2の主面上に積層されるウエハW3の裏面との間隔、ウエハ3の裏面から突出する貫通電極4の長さ、および後の製造工程で第3層アルミニウム配線47に接続して形成される第1バンプ電極の厚さなどによって決めることができる。

【0043】

次に、図21に示すように、露出した第3層アルミニウム配線47に接続する第1バンプ電極50を形成する。第1バンプ電極50は、例えばマスク蒸着法で形成され、主にインジウム半田等の低硬度の材料、あるいは温度などの条件により低硬度となりうる金属または合金膜によって構成されて下層の配線と電気的に接続されている。同時に、スペーサ49上にも第2バンプ電極50aを形成する。この第2バンプ電極50aは、ウエハW2に形成された素子とは電気的に接続されておらず、素子の動作には何ら寄与しない。

【0044】

次に、図22〜図26を用いて、ウエハW3の裏面を研磨する工程、ウエハW2,W3を貼り合わせる工程、ウエハW2,W3間に接着剤を注入する工程およびウエハW2の裏面を研磨する工程について説明する。

【0045】

上記と同様の方法で集積回路および導電部4C等が形成されたウエハW3を準備する。但し、ウエハW3は最上層に位置することから、第1バンプ電極50は形成されていない。

【0046】

次に、図22に示すように、ウエハW3の裏面を、例えばCMP法などにより研磨して所定の厚さまで薄く加工する。研磨を実施したこの段階では、導電溝4Aおよび絶縁溝26AはウエハW3の裏面には露出させない。これは、研磨により導電溝4Aの内部に充填した導電膜(窒化チタン膜42およびタングステン膜43)が破壊されるのを防ぐためと、ウエハW3に物理的なダメージ層が残留しないように、後の製造工程で非物理的な方法によりウエハW3を薄く加工する余裕を残すためである。

【0047】

次に、図23に示すように、ウエハW3の裏面を、例えばフッ酸と硝酸との混合溶液、またはそれに類するシリコンエッチング溶液を用いたウエットエッチング法により、エッチングする。ウエットエッチング法に代えてドライエッチング法によりウエハW3の裏面を選択的にエッチングしてもよい。これにより、ウエハW3の厚さを、例えば30μm程度とし、ウエハW3の裏面から導電部4Cを突出させて貫通電極4を形成し、絶縁部26Cを突出させて貫通分離部26を形成する。

【0048】

次に、図24に示すように、ウエハW2とウエハW3とを接近させて、ウエハW3に形成された貫通電極4とウエハW2に形成された第1バンプ電極50とを物理的に接触させる。この際、第1バンプ電極50に貫通電極4を刺すことにより、ウエハW2に形成された素子とウエハW3形成された素子との電気的接続を確保する。また、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間で、貫通電極4が形成されていない領域には、スペーサ49上に第2バンプ電極50aが積層された支持部が形成されている。スペーサ49と第2バンプ電極50aとを積層した厚さが、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔とほぼ同じになるようにスペーサ49の厚さは設定されているので、貫通電極4が形成されていない領域であってもウエハW3がたわむことがなく、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔をウエハ面内で均一に保つことができる。

【0049】

次に、図25に示すように、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間に、充填材としての機能も有する接着剤51を充填し、ウエハW2とウエハW3とを固定する。ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔がウエハ面内で均一であることから、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間に接着剤51が入りやすく、接着剤51の未充填箇所の形成を防ぐことができるので、物理的な強度を確保することができる。接着剤51には絶縁性を持つ樹脂、例えばエポキシ樹脂などの熱硬化樹脂などを用いることができるが、これと同等の接着性、強度および絶縁性を有する材料であれば材質は問わない。

【0050】

次に、図26に示すように、ウエハW2の裏面を前述したウエハW3と同様にして研磨することにより、ウエハW2の厚さを、例えば30μm程度とし、ウエハW2の裏面から導電部4Cを突出させて貫通電極4を形成し、絶縁部26Cを突出させて貫通分離部26を形成する。

【0051】

次に、図27を用いて、ウエハW1とウエハW2,W3を貼り合わせる工程およびウエハW1,W2間に接着剤を注入する工程について説明する。

【0052】

上記と同様の方法で集積回路および第1バンプ電極50が形成されたウエハW1を準備する。ウエハW1は最下層に位置することから、導電部4Cは形成されていない。

【0053】

さらに、図27に示すように、上記と同様の方法でウエハW1の主面上に、すでに積層して貼り合わせてあるウエハW2,W3を接近させて、ウエハW2に形成された貫通電極4とウエハW1に形成された第1バンプ電極50とを物理的に接触させる。続いて、ウエハ1の主面上の表面保護膜48とウエハW2の裏面との間に充填材としての機能も有する接着剤51を充填し、ウエハW1とウエハW2,W3とを固定する。その後、これらのウエハW1,W2,W3をダイシングして3次元構造のチップC1,C2,C3に個片化し、これを配線基板1に実装してモールド樹脂2で封止することにより、前記図1に示すパッケージが完成する。

【0054】

なお、本実施の形態1では、1つのスペーサ49上に1つの第2バンプ電極50aを形成したが、これに限定されるものではなく、例えば1つのスペーサ49上に複数の第2バンプ電極50aを形成してもよく、または2つ以上のスペーサ49に跨って1つの第2バンプ電極50aを形成してもよい。

【0055】

このように、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間で、ウエハW1の第3層アルミニウム配線47に接続する第1バンプ電極50が形成されていない領域に、スペーサ49と第2バンプ電極50aとを積層した支持部を形成することにより、ウエハW2のたわみを防いで、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間隔をウエハ面内で均一に保つことができる。同様にして、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔をウエハ面内で均一に保つことができる。これによって、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間またはウエハW2の主面上の表面保護膜48とウエハW3の裏面との間に接着剤51を余すところなく充填できるので、ウエハW1,W2,W3を積層して貼り合わせた後に、積層したウエハW1,W2,W3を積層したチップC1,C2,C3に個片化して半導体装置を形成しても、積層したチップC1,C2,C3の分離を防ぐことができる。

【0056】

(実施の形態2)

本発明の実施の形態2による半導体装置を示す半導体ウエハの要部断面図を図28に示す。

【0057】

前述した実施の形態1では、例えばウエハW1(下に位置するウエハ)とウエハW2(上に位置するウエハ)とを積層して貼り合わせた場合、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間で、ウエハW1の第3層アルミニウム配線47に接続する第1バンプ電極50が形成されていない領域に、スペーサ49と第2バンプ電極50aとを積層した支持部を形成することにより、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間隔をウエハ面内で均一に保っている。

【0058】

しかしながら、本実施の形態2では、ウエハW1とウエハW2とを積層して貼り合わせた場合、ウエハW1の第3層アルミニウム配線47に接続する第1バンプ電極50が形成されていない領域に、ウエハW1の第3層アルミニウム配線47に接続する第1バンプ電極50が形成されている領域よりも厚い表面保護膜48をウエハW1に形成し、さらにウエハW1の第3層アルミニウム配線47に接続する第1バンプ電極50が形成されていない領域の表面保護膜48上に第2バンプ電極50aを形成する。これによって、ウエハW2の裏面から貫通電極4が突出していない領域に、相対的に厚い表面保護膜48と第2バンプ電極50aとを積層した支持部を形成することができるので、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間隔をウエハ面内で均一に保つことができる。また、本実施の形態2では、前述した実施の形態1で用いたスペーサ49を形成する必要がないので、前述した実施の形態1よりも製造コストを低減することができる。

【0059】

膜厚が厚い領域と膜厚が薄い領域とを有する上記表面保護膜48は、例えば第3層アルミニウム配線47が形成されたウエハW1の主面上にCVD法で表面保護膜48を形成し、第1バンプ電極50が形成される領域の表面保護膜48を薄く加工した後、第1バンプ電極50が形成される領域の第3層アルミニウム配線47が露出するように表面保護膜48を加工することにより形成することができる。あるいは、第1バンプ電極50が形成される領域の第3層アルミニウム配線47が露出するように、表面保護膜48を加工した後、第1バンプ電極50が形成される領域の表面保護膜48を薄く加工してもよい。

【0060】

(実施の形態3)

本発明の実施の形態3による半導体装置を示す半導体ウエハの要部断面図を図29に示す。ここでは、積層して貼り合わせたウエハW1とウエハW2とを用いて説明する。

【0061】

前述した実施の形態1では、貫通電極4から離間した位置に貫通電極4を取り囲むように、貫通分離部26を形成している。

【0062】

しかしながら、本実施の形態3では、貫通分離部26の内部に多結晶シリコン膜28を貫通してタングステンを主成分とする導電膜からなる貫通電極4が形成されている。貫通分離部26は、貫通孔26aの側面を覆うように形成された酸化シリコン膜27と、この酸化シリコン膜27の側面を覆うように形成された多結晶シリコン膜28と、この多結晶シリコン膜28の上面を覆うように形成されたキャップ絶縁膜29とを有している。貫通電極4は、導電溝4Aの内側に形成された窒化チタン膜42およびタングステン膜43とを有している。貫通分離部26の内部に貫通電極4を形成することにより、貫通分離部26を用いてウエハW2と貫通電極4との電気的な絶縁を行うことができ、かつ、貫通電極4を構成する導電膜からの汚染の拡散を抑えて素子の電気的特性の劣化を防止することができる。

【0063】

このように貫通分離部26の内部に貫通電極4が形成された構造であっても、前述した実施の形態1と同様に、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間で、貫通電極4が形成されていない領域に、スペーサ49と第2バンプ電極50aとが積層された支持部を形成することにより、ウエハW2のたわみを防いで、ウエハW1の主面上の表面保護膜48とウエハW2の裏面との間隔をウエハ面内で均一に保つことができる。

【0064】

貫通分離部26の内部に形成される貫通電極4は、例えば以下に説明する製造方法により形成することができる。

【0065】

まず、図30に示すように、ウエハW2の主面に素子分離溝22および溝23を形成した後、素子分離溝22および溝23の内部に酸化シリコン膜24を埋め込む。

【0066】

次に、図31に示すように、ウエハW2の主面上に絶縁膜、例えば窒化シリコン膜25をCVD法で堆積した後、レジストパターン(図示は省略)をマスクとして、そこから露出する窒化シリコン膜25、酸化シリコン膜24およびウエハW2を順にエッチング除去することにより、ウエハW2の主面に絶縁溝26Aを形成する。この絶縁溝26Aは、前述した貫通孔26aを形成することになる溝であり、ウエハW2の主面からウエハW2の厚さ方向の途中の位置であって溝23の深さよりも深い位置まで延びるように形成されている。

【0067】

続いて、ウエハW2に対して熱酸化処理を施すことにより、絶縁溝26Aの内壁(側面および底面)のウエハW2の露出面に絶縁膜、例えば酸化シリコン膜27を形成する。この絶縁膜は、熱酸化処理により形成された酸化シリコン膜27に限定されるものではなく、例えばCVD法で形成される酸化シリコン、窒化シリコン、酸窒化シリコンなどを絶縁膜に用いることもできる。

【0068】

続いて、ウエハW2の主面上に、絶縁溝26Aが充填されるように埋込膜、例えば多結晶シリコン膜28をCVD法で堆積する。続いて、多結晶シリコン膜28を異方性のドライエッチング法によってエッチバックすることにより、絶縁溝26Aの外部の余分な多結晶シリコン膜28を除去し、絶縁溝26A内のみに多結晶シリコン膜28を残すようにする。

【0069】

続いて、ウエハW2の主面上に、多結晶シリコン膜28の上部の窪みが埋め込まれるように、例えば酸化シリコンからなるキャップ絶縁膜29をCVD法で堆積する。続いて、キャップ絶縁膜29をCMP法で研磨することにより、多結晶シリコン膜28の上部の窪みの外部の余分なキャップ絶縁膜29を除去し、多結晶シリコン膜28の上部の窪み内のみにキャップ絶縁膜29を残すようにする。このようにして多結晶シリコン膜28の上面をキャップ絶縁膜29により覆う。その後、窒化シリコン膜25をウエットエッチング法によって除去する。

【0070】

次に、図32に示すように、ウエハW2の主面の素子形成領域に集積回路素子を形成する。集積回路を構成する集積回路素子の例としては、MISトランジスタ、バイポーラトランジスタやダイオード等のような能動素子がある。また、上記集積回路素子の他の例としては、抵抗、キャパシタおよびインダクタ等のような受動素子がある。ここでは、素子として、nチャネル型MISトランジスタが例示されており、前述した実施の形態1に例示したnチャネル型MISトランジスタQnと同様の製造方法により形成することができる。

【0071】

次に、図33に示すように、ウエハW2の主面上に酸化シリコン膜36をCVD法で堆積した後、レジストパターン(図示は省略)をマスクとして、そこから露出する酸化シリコン膜36、キャップ絶縁膜29および多結晶シリコン膜28を順にエッチング除去する。これにより、ウエハW2の主面に導電溝4Aを形成する。この導電溝4Aは、ウエハW2の主面の酸化シリコン膜36の上面からウエハW2の厚さ方向に、絶縁溝26A内の底面の酸化シリコン膜27まで延びるように形成されている。

【0072】

続いて、ウエハW2の主面上に窒化チタン膜42をスパッタリング法で堆積した後、タングステン膜43をCVD法で堆積し、窒化チタン膜42およびタングステン膜43により導電溝4Aを埋め込む。続いて、タングステン膜43および窒化チタン膜42をCMP法で研磨することにより、導電溝4Aの外部の余分なタングステン膜43および窒化チタン膜42を除去し、導電溝4A内のみにタングステン膜43および窒化チタン膜42を残すようにする。このようにして導電溝4A内にタングステン膜43および窒化チタン膜42が埋め込まれて導電部4Cを形成する。導電部4Cは貫通電極4を形成する部分であり、この導電部4Cの構成はウエハW2の主裏面間を貫通していないことを除いて貫通電極4と同じである。

【0073】

次に、図34に示すように、配線層を形成する。ここでは、配線層として、3層配線構成の配線層が例示されており、前述した実施の形態1に例示した配線層と同様の製造方法により形成することができる。さらに、前述した実施の形態1と同様にして、表面保護膜48上にスペーサ49を形成し、続いて露出した第3層アルミニウム配線47に接続する第1バンプ電極50を形成し、スペーサ49上に第2バンプ電極50aを形成する。

【0074】

次に、図35に示すように、ウエハW2の裏面を、例えばCMP法で研磨して所定の厚さまで薄く加工した後、ウエハW2の裏面を、例えばフッ酸と硝酸との混合溶液、またはそれに類するシリコンエッチング溶液を用いたウエットエッチング法により、エッチングする。ウエットエッチング法に代えてドライエッチング法によりウエハW2の裏面を選択的にエッチングしてもよい。エッチングを実施したこの段階では、酸化シリコン膜27は露出しているが、導電部4Cは酸化シリコン膜27により覆われている。続いて、露出した酸化シリコン膜27をエッチング法により除去する。これにより、貫通孔26aの側面を覆う酸化シリコン膜27、多結晶シリコン膜28およびキャップ絶縁膜29からなる貫通分離部26が形成され、さらにその内部に形成されて裏面から突出する貫通電極4を形成する。

【0075】

なお、本実施の形態3は、前述した実施の形態1で説明したスペーサ49と第2バンプ電極50aとを積層した支持部を有する半導体装置に適用した場合について説明したが、前述した実施の形態2で説明した相対的に厚く形成された表面保護膜48上に第2バンプ電極50aを積層した支持部を有する半導体装置にも適用できることは言うまでもない。

【0076】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0077】

本発明は、複数枚のチップを積層して貼り合わせた3次元構造の半導体装置に適用することができる。

【図面の簡単な説明】

【0078】

【図1】本発明の実施の形態1による半導体装置を配線基板に実装して樹脂封止したパッケージの一例を示す断面図である。

【図2】本発明の実施の形態1による半導体装置の製造工程を示すフロー図である。

【図3】本発明の実施の形態1による半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図4】図3に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図5】溝の平面形状を示す半導体ウエハの要部平面図である。

【図6】図4に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図7】図6に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図8】絶縁溝の平面形状を示す半導体ウエハの要部平面図である。

【図9】図7に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図10】図9に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図11】図10に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図12】図11に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図13】図12に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図14】図13に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図15】導電溝の平面形状を示す半導体ウエハの要部平面図である。

【図16】図14に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図17】図16に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図18】図17に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図19】図18に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図20】図19に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図21】図20に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図22】図21に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図23】図22に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図24】図23に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図25】図24に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図26】図25に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図27】図26に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図28】本発明の実施の形態2による半導体装置を示す半導体ウエハの要部断面図である。

【図29】本発明の実施の形態3による半導体装置を示す半導体ウエハの要部断面図である。

【図30】本発明の実施の形態3による半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図31】図30に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図32】図31に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図33】図32に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図34】図33に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【図35】図34に続く半導体装置の製造工程を示す半導体ウエハの要部断面図である。

【符号の説明】

【0079】

1 配線基板

2 モールド樹脂

3 接着剤

4 貫通電極

4A 導電溝

4C 導電部

5 ボンディングパッド

6 電極

7 ワイヤ

8 配線

9 半田バンプ

20 酸化シリコン膜

21 窒化シリコン膜

22 素子分離溝

23 溝

24,24a 酸化シリコン膜

25 窒化シリコン膜

26 貫通分離部

26A 絶縁溝

26C 絶縁部

26a 貫通孔

27 酸化シリコン膜

28 多結晶シリコン膜

29 キャップ絶縁膜

30 n型ウエル

31 p型ウエル

32 ゲート絶縁膜

33 ゲート電極

34 n型半導体領域(ソース、ドレイン)

35 p型半導体領域(ソース、ドレイン)

36,37 酸化シリコン膜

38,39 第1層アルミニウム配線

40 窒化チタン膜

42 窒化チタン膜

43 タングステン膜

44 第1層間絶縁膜

45 第2層アルミニウム配線

46 第2層間絶縁膜

47 第3層アルミニウム配線

48 表面保護膜

49 スペーサ

50 第1バンプ電極

50a 第2バンプ電極

51 接着剤

C1,C2,C3 半導体チップ

Qn nチャネル型MISトランジスタ

Qp pチャネル型MISトランジスタ

W1,W2,W3 半導体ウエハ

【特許請求の範囲】

【請求項1】

第1面上に集積回路が形成され、前記第1面と反対側の第2面から突出する貫通電極が形成された第1ウエハと、第1面上に集積回路が形成され、最上層配線に電気的に接続して第1バンプ電極が形成された第2ウエハとを積層して貼り合わせる工程を有する半導体装置の製造方法であって、

(a)前記第2ウエハの前記第1面上に前記最上層配線を覆う表面保護膜を形成する工程と、

(b)前記表面保護膜を加工して前記最上層配線の一部を露出させる工程と、

(c)前記(b)工程の後、前記第2ウエハの前記第1面上に絶縁膜を形成する工程と、

(d)前記第2ウエハの前記第1面上に形成された前記第1バンプ電極に、前記第1ウエハの前記第2面から突出する前記貫通電極を物理的に接触させる工程と、

(e)前記第1ウエハの前記第2面と前記第2ウエハの前記第1面上の前記表面保護膜との間に樹脂を充填する工程とからなるプロセスにおいて、

(f)前記(c)工程の前記絶縁膜を加工して前記最上層配線が露出していない領域の前記表面保護膜上に前記絶縁膜からなるスペーサを形成する工程と、

(g)前記(f)工程の後、同一工程で前記第2ウエハの前記第1面上の露出した前記最上層配線上に前記第1バンプ電極を形成し、前記スペーサ上に第2バンプ電極を形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項2】

請求項1記載の半導体装置の製造方法において、前記絶縁膜はポリイミド樹脂膜であることを特徴とする半導体装置の製造方法。

【請求項3】

請求項1記載の半導体装置の製造方法において、1つの前記スペーサ上に1つまたは2つ以上の前記第2バンプ電極を形成することを特徴とする半導体装置の製造方法。

【請求項4】

請求項1記載の半導体装置の製造方法において、2つ以上の前記スペーサ上に1つの前記第2バンプ電極を形成することを特徴とする半導体装置の製造方法。

【請求項5】

請求項1記載の半導体装置の製造方法において、前記スペーサと前記第2バンプ電極とを積層した厚さは、前記第1ウエハの前記第2面と前記第2ウエハの前記第1面上の前記表面保護膜との間隔とほぼ同じであることを特徴とする半導体装置の製造方法。

【請求項6】

第1面上に集積回路が形成され、前記第1面と反対側の第2面から突出する貫通電極が形成された第1ウエハと、第1面上に集積回路が形成され、最上層配線に電気的に接続して第1バンプ電極が形成された第2ウエハとを積層して貼り合わせる工程を有する半導体装置の製造方法であって、

(a)前記第2ウエハの前記第1面上に前記最上層配線を覆う表面保護膜を形成する工程と、

(b)前記表面保護膜を加工して前記第1バンプ電極が形成される領域の前記最上層配線の一部を露出させる工程と、

(c)前記第2ウエハの前記第1面上に形成された前記第1バンプ電極に、前記第1ウエハの前記第2面から突出する前記貫通電極を物理的に接触させる工程と、

(d)前記第1ウエハの前記第2面と前記第2ウエハの前記第1面上の前記表面保護膜との間に樹脂を充填する工程とからなるプロセスにおいて、

(e)前記(a)工程の前記表面保護膜を加工して前記第1バンプ電極が形成される領域の前記表面保護膜の厚さを前記第1バンプ電極が形成されない領域の前記表面保護膜の厚さよりも薄くする工程と、

(f)同一工程で前記第2ウエハの前記第1面上の露出した前記最上層配線上に前記第1バンプ電極を形成し、前記最上層配線が露出していない領域の前記表面保護膜上に第2バンプ電極を形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項7】

請求項1または6記載の半導体装置の製造方法において、前記第1ウエハの前記第2面と前記第2ウエハの前記第1面上の前記表面保護膜との間隔は5〜30μmであることを特徴とする半導体装置の製造方法。

【請求項8】

請求項1または6記載の半導体装置の製造方法において、前記表面保護膜は、酸化シリコン膜、窒化シリコン膜、または酸化シリコン膜上に窒化シリコン膜を形成した積層膜からなることを特徴とする半導体装置の製造方法。

【請求項9】

第1面上に形成された複数の第1集積回路と、前記第1面と反対側の第2面から突出する貫通電極とを含む第1チップと、

第1面上に形成された複数の第2集積回路と、前記複数の第2集積回路のいずれかに電気的に接続されて前記第1面上に形成された複数層の配線と、最上層配線の一部を露出して前記第1面上に形成された表面保護膜と、前記表面保護膜上に形成されたスペーサと、前記表面保護膜から露出する前記最上層配線と電気的に接続して形成された第1バンプ電極と、前記スペーサ上に形成された第2バンプ電極とを含む第2チップとを有し、

前記第1チップの前記第2面から突出する前記貫通電極が前記第2チップの前記第1面上の前記第1バンプ電極と物理的に接触しており、前記第1チップの前記第2面と前記第2チップの前記第1面上の前記表面保護膜との間に樹脂が充填されていることを特徴とする半導体装置。

【請求項10】

第1面上に形成された複数の第1集積回路と、前記第1面と反対側の第2面から突出する貫通電極とを含む第1チップと、

第1面上に形成された複数の第2集積回路と、前記複数の第2集積回路のいずれかに電気的に接続されて前記第1面上に形成された複数層の配線と、最上層配線の一部を露出して前記第1面上に形成された表面保護膜と、前記表面保護膜から露出する前記最上層配線と電気的に接続して形成された第1バンプ電極と、前記表面保護膜上に形成された第2バンプ電極とを含む第2チップとを有し、

前記第1バンプ電極が形成された領域の前記表面保護膜の厚さは、前記第2バンプ電極が形成された領域の前記表面保護膜の厚さよりも薄く、

前記第1チップの前記第2面から突出する前記貫通電極が前記第2チップの前記第1バンプ電極と物理的に接触しており、前記第1チップの前記第2面と前記第2チップの前記第1面上の前記表面保護膜との間に樹脂が充填されていることを特徴とする半導体装置。

【請求項1】

第1面上に集積回路が形成され、前記第1面と反対側の第2面から突出する貫通電極が形成された第1ウエハと、第1面上に集積回路が形成され、最上層配線に電気的に接続して第1バンプ電極が形成された第2ウエハとを積層して貼り合わせる工程を有する半導体装置の製造方法であって、

(a)前記第2ウエハの前記第1面上に前記最上層配線を覆う表面保護膜を形成する工程と、

(b)前記表面保護膜を加工して前記最上層配線の一部を露出させる工程と、

(c)前記(b)工程の後、前記第2ウエハの前記第1面上に絶縁膜を形成する工程と、

(d)前記第2ウエハの前記第1面上に形成された前記第1バンプ電極に、前記第1ウエハの前記第2面から突出する前記貫通電極を物理的に接触させる工程と、

(e)前記第1ウエハの前記第2面と前記第2ウエハの前記第1面上の前記表面保護膜との間に樹脂を充填する工程とからなるプロセスにおいて、

(f)前記(c)工程の前記絶縁膜を加工して前記最上層配線が露出していない領域の前記表面保護膜上に前記絶縁膜からなるスペーサを形成する工程と、

(g)前記(f)工程の後、同一工程で前記第2ウエハの前記第1面上の露出した前記最上層配線上に前記第1バンプ電極を形成し、前記スペーサ上に第2バンプ電極を形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項2】

請求項1記載の半導体装置の製造方法において、前記絶縁膜はポリイミド樹脂膜であることを特徴とする半導体装置の製造方法。

【請求項3】

請求項1記載の半導体装置の製造方法において、1つの前記スペーサ上に1つまたは2つ以上の前記第2バンプ電極を形成することを特徴とする半導体装置の製造方法。

【請求項4】

請求項1記載の半導体装置の製造方法において、2つ以上の前記スペーサ上に1つの前記第2バンプ電極を形成することを特徴とする半導体装置の製造方法。

【請求項5】

請求項1記載の半導体装置の製造方法において、前記スペーサと前記第2バンプ電極とを積層した厚さは、前記第1ウエハの前記第2面と前記第2ウエハの前記第1面上の前記表面保護膜との間隔とほぼ同じであることを特徴とする半導体装置の製造方法。

【請求項6】

第1面上に集積回路が形成され、前記第1面と反対側の第2面から突出する貫通電極が形成された第1ウエハと、第1面上に集積回路が形成され、最上層配線に電気的に接続して第1バンプ電極が形成された第2ウエハとを積層して貼り合わせる工程を有する半導体装置の製造方法であって、

(a)前記第2ウエハの前記第1面上に前記最上層配線を覆う表面保護膜を形成する工程と、

(b)前記表面保護膜を加工して前記第1バンプ電極が形成される領域の前記最上層配線の一部を露出させる工程と、

(c)前記第2ウエハの前記第1面上に形成された前記第1バンプ電極に、前記第1ウエハの前記第2面から突出する前記貫通電極を物理的に接触させる工程と、

(d)前記第1ウエハの前記第2面と前記第2ウエハの前記第1面上の前記表面保護膜との間に樹脂を充填する工程とからなるプロセスにおいて、

(e)前記(a)工程の前記表面保護膜を加工して前記第1バンプ電極が形成される領域の前記表面保護膜の厚さを前記第1バンプ電極が形成されない領域の前記表面保護膜の厚さよりも薄くする工程と、

(f)同一工程で前記第2ウエハの前記第1面上の露出した前記最上層配線上に前記第1バンプ電極を形成し、前記最上層配線が露出していない領域の前記表面保護膜上に第2バンプ電極を形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項7】

請求項1または6記載の半導体装置の製造方法において、前記第1ウエハの前記第2面と前記第2ウエハの前記第1面上の前記表面保護膜との間隔は5〜30μmであることを特徴とする半導体装置の製造方法。

【請求項8】

請求項1または6記載の半導体装置の製造方法において、前記表面保護膜は、酸化シリコン膜、窒化シリコン膜、または酸化シリコン膜上に窒化シリコン膜を形成した積層膜からなることを特徴とする半導体装置の製造方法。

【請求項9】

第1面上に形成された複数の第1集積回路と、前記第1面と反対側の第2面から突出する貫通電極とを含む第1チップと、

第1面上に形成された複数の第2集積回路と、前記複数の第2集積回路のいずれかに電気的に接続されて前記第1面上に形成された複数層の配線と、最上層配線の一部を露出して前記第1面上に形成された表面保護膜と、前記表面保護膜上に形成されたスペーサと、前記表面保護膜から露出する前記最上層配線と電気的に接続して形成された第1バンプ電極と、前記スペーサ上に形成された第2バンプ電極とを含む第2チップとを有し、

前記第1チップの前記第2面から突出する前記貫通電極が前記第2チップの前記第1面上の前記第1バンプ電極と物理的に接触しており、前記第1チップの前記第2面と前記第2チップの前記第1面上の前記表面保護膜との間に樹脂が充填されていることを特徴とする半導体装置。

【請求項10】

第1面上に形成された複数の第1集積回路と、前記第1面と反対側の第2面から突出する貫通電極とを含む第1チップと、

第1面上に形成された複数の第2集積回路と、前記複数の第2集積回路のいずれかに電気的に接続されて前記第1面上に形成された複数層の配線と、最上層配線の一部を露出して前記第1面上に形成された表面保護膜と、前記表面保護膜から露出する前記最上層配線と電気的に接続して形成された第1バンプ電極と、前記表面保護膜上に形成された第2バンプ電極とを含む第2チップとを有し、

前記第1バンプ電極が形成された領域の前記表面保護膜の厚さは、前記第2バンプ電極が形成された領域の前記表面保護膜の厚さよりも薄く、

前記第1チップの前記第2面から突出する前記貫通電極が前記第2チップの前記第1バンプ電極と物理的に接触しており、前記第1チップの前記第2面と前記第2チップの前記第1面上の前記表面保護膜との間に樹脂が充填されていることを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【公開番号】特開2010−114350(P2010−114350A)

【公開日】平成22年5月20日(2010.5.20)

【国際特許分類】

【出願番号】特願2008−287478(P2008−287478)

【出願日】平成20年11月10日(2008.11.10)

【出願人】(000005108)株式会社日立製作所 (27,607)

【出願人】(000005326)本田技研工業株式会社 (23,863)

【Fターム(参考)】

【公開日】平成22年5月20日(2010.5.20)

【国際特許分類】

【出願日】平成20年11月10日(2008.11.10)

【出願人】(000005108)株式会社日立製作所 (27,607)

【出願人】(000005326)本田技研工業株式会社 (23,863)

【Fターム(参考)】

[ Back to top ]