半導体装置の製造方法および半導体装置

【課題】容易に製造できる半導体装置を提供する。

【解決手段】半導体装置は、PMOSトランジスタのゲート電極1pの仕事関数値が、High-kゲート絶縁膜16(16a)、及び、High-kゲート絶縁膜16・酸化シリコン膜15界面へのAlの拡散により調整されており、NMOSトランジスタのゲート電極1nの仕事関数値が、High-kゲート絶縁膜16・金属ゲート膜19間に挿入された、数原子層程度のAl層18により調整されている構成を有する。

【解決手段】半導体装置は、PMOSトランジスタのゲート電極1pの仕事関数値が、High-kゲート絶縁膜16(16a)、及び、High-kゲート絶縁膜16・酸化シリコン膜15界面へのAlの拡散により調整されており、NMOSトランジスタのゲート電極1nの仕事関数値が、High-kゲート絶縁膜16・金属ゲート膜19間に挿入された、数原子層程度のAl層18により調整されている構成を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法と半導体装置とに関する。

【背景技術】

【0002】

従来、MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor:以下、

MOSトランジスタ又はMOSと略記する)のゲート絶縁膜としては、酸化シリコン(SiO2)膜が用いられていたが、MOSトランジスタの微細化/集積化のためにゲート絶縁膜を薄くすると、リーク電流が増えてしまう。従って、酸化シリコンよりも比誘電率が高いHf系酸化物をゲート絶縁膜として用いることが検討されている。Hf系酸化物膜上にポリシリコン電極やシリサイド電極を直接形成したのでは、Fermi Level pinningのた

めに、NMOS/PMOSトランジスタのゲート電極の実効的仕事関数の値を制御できない。

【0003】

そのため、図12に示したように、NMOS側のゲート絶縁膜56上と、PMOS側のゲート絶縁膜56上とに、仕事関数値の異なる金属ゲート膜59a、59bを形成するプロセス(以下、デュアルメタルプロセスと表記する)により、各ゲート電極の仕事関数値を制御することが提案されている。なお、図12及び図13において、絶縁膜56下に形成されている膜55は、酸化シリコン膜であり、金属ゲート膜59a、59b、59上に形成されている膜60は、ポリシリコン膜である。

【0004】

また、各ゲート電極の仕事関数値を制御できるプロセスとして、デュアルHigh-kプロセスと一般に呼ばれているプロセスも知られている。

【0005】

このデュアルHigh-kプロセスでは、図13に示したように、PMOS側の絶縁膜56と金属ゲート膜59との間にAl2O3等からなるキャップ層58aを設けておくと共に、NMOS側の絶縁膜56と金属ゲート膜59との間にLa2O3等からなるキャップ層58cを設けておく。そして、続く熱処理工程で各キャップ層58a(例えばAl膜)、58c(例えばLa膜)を拡散させて絶縁膜58の組成を変える(絶縁膜56を絶縁膜56a、56cに変える)と共に、絶縁膜56a、56cと酸化シリコン膜55の界面に、Hf−O−Al結合、Hf−O−La結合を生成することによって、各ゲート電極の仕事関数値を制御する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特表2008−507149号公報

【特許文献2】特開2008−16798号公報

【特許文献3】特表2008−515190号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

開示の技術の課題は、半導体装置を容易に製造できる半導体装置の製造方法を提供することにある。

【0008】

また、開示の技術の他の課題は、製造が容易な構成/構造を有する半導体装置を提供することにある。

【課題を解決するための手段】

【0009】

上記課題を解決するために、開示の技術の一態様では、半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、前記絶縁膜上にAl含有膜を形成する工程と、前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にAl膜を形成する工程と、前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程とにより、半導体装置が製造される。

【発明の効果】

【0010】

以上の工程によれば、半導体装置を容易に製造できることになる。

【図面の簡単な説明】

【0011】

【図1A】実効的仕事関数値が第一原理計算法により算出された構造の説明図(その1)。

【図1B】実効的仕事関数値が第一原理計算法により算出された構造の説明図(その2)。

【図1C】実効的仕事関数値が第一原理計算法により算出された構造の説明図(その3)。

【図1D】実効的仕事関数値が第一原理計算法により算出された構造の説明図(その4)。

【図2】実効的仕事関数値の算出結果の説明図。

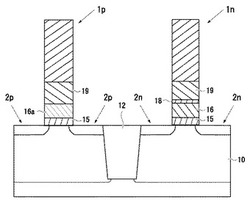

【図3】第1実施形態に係る製造方法により製造される半導体装置の基本構成の説明図。

【図4A】第1実施形態に係る製造方法を説明するための工程図(その1)。

【図4B】第1実施形態に係る製造方法を説明するための工程図(その2)。

【図4C】第1実施形態に係る製造方法を説明するための工程図(その3)。

【図4D】第1実施形態に係る製造方法を説明するための工程図(その4)。

【図4E】第1実施形態に係る製造方法を説明するための工程図(その5)。

【図4F】第1実施形態に係る製造方法を説明するための工程図(その6)。

【図4G】第1実施形態に係る製造方法を説明するための工程図(その7)。

【図4H】第1実施形態に係る製造方法を説明するための工程図(その8)。

【図4I】第1実施形態に係る製造方法を説明するための工程図(その9)。

【図4J】第1実施形態に係る製造方法を説明するための工程図(その10)。

【図4K】第1実施形態に係る製造方法を説明するための工程図(その11)。

【図5A】第2実施形態に係る製造方法を説明するための工程図(その1)。

【図5B】第2実施形態に係る製造方法を説明するための工程図(その2)。

【図5C】第2実施形態に係る製造方法を説明するための工程図(その3)。

【図5D】第2実施形態に係る製造方法を説明するための工程図(その4)。

【図5E】第2実施形態に係る製造方法を説明するための工程図(その5)。

【図5F】第2実施形態に係る製造方法を説明するための工程図(その6)。

【図6A】第3実施形態に係る製造方法を説明するための工程図(その1)。

【図6B】第3実施形態に係る製造方法を説明するための工程図(その2)。

【図6C】第3実施形態に係る製造方法を説明するための工程図(その3)。

【図6D】第3実施形態に係る製造方法を説明するための工程図(その4)。

【図6E】第3実施形態に係る製造方法を説明するための工程図(その5)。

【図6F】第3実施形態に係る製造方法を説明するための工程図(その6)。

【図6G】第3実施形態に係る製造方法を説明するための工程図(その7)。

【図6H】第3実施形態に係る製造方法を説明するための工程図(その8)。

【図6I】第3実施形態に係る製造方法を説明するための工程図(その9)。

【図6J】第3実施形態に係る製造方法を説明するための工程図(その10)。

【図7A】第4実施形態に係る製造方法を説明するための工程図(その1)。

【図7B】第4実施形態に係る製造方法を説明するための工程図(その2)。

【図8】第5実施形態に係る製造方法により製造される半導体装置の基本構成の説明図。

【図9A】第5実施形態に係る製造方法を説明するための工程図(その1)。

【図9B】第5実施形態に係る製造方法を説明するための工程図(その2)。

【図9C】第5実施形態に係る製造方法を説明するための工程図(その3)。

【図10】第6実施形態に係る製造方法により製造される半導体装置の基本構成の説明図。

【図11A】第6実施形態に係る製造方法を説明するための工程図(その1)。

【図11B】第6実施形態に係る製造方法を説明するための工程図(その2)。

【図12】デュアルHigh-kプロセスの説明図。

【図13】デュアルメタルプロセスの説明図。

【発明を実施するための形態】

【0012】

以下、図面を参照して一実施形態に係る半導体装置の製造方法について説明する。なお、以下で説明する各実施形態(第1〜第6実施形態)は、あくまで製造方法の一形態/一例であり、本発明は、以下の説明における特定の技術事項に限定されるものではない。

【0013】

第1〜第6実施形態に係る半導体装置の製造方法(以下、単に製造方法とも表記する)の詳細説明を行う前に、まず、各製造方法の概要説明を行う。

【0014】

以下で説明する各製造方法は、発明者らが鋭意研究することによって得られた、『或る材料からなる、数原子層程度の厚さの界面膜をHigh-k膜・金属ゲート膜間に設ければ、当該材料の仕事関数値近傍の値にゲート電極の仕事関数値を制御できる』という知見に基づき、開発されたものである。

【0015】

具体的には、既に説明したように、デュアルHigh-kプロセス(図13)では、La2O3等からなるキャップ層58cとAl2O3等からなるキャップ層58aとを形成するが、キャップ層58c材料として使用可能な材料(La2O3等)は、一般に、剥離(除去)が比較的に困難な材料となっている。

【0016】

一方、PMOSトランジスタ側のキャップ層58a材料として使用されているAlは、剥離が簡単に行える材料である。しかも、Alは、仕事関数値が小さい材料であるため、High-kゲート絶縁膜上へのAl膜の形成によりNMOS側のゲート電極の仕事関数値を制御できる場合には、La2O3膜等の剥離が不要となり、半導体装置の製造に要する物質数が減る結果として、High-kゲート絶縁膜を備えた半導体装置をより容易に製造できることになる。

【0017】

そのため、発明者らは、図1A〜図1Dに示した構造を有するゲート電極等の実効的仕

事関数値WFeffを、第一原理計算法により算出した。

【0018】

すなわち、発明者らは、シリコン基板上に、0.88nm厚の酸化シリコン膜と2.2nm厚

のHf02膜とAl膜とがこの順で積層された構造を有するゲート電極(図1A)のWFeffと、当該ゲート電極のAl膜部分を化学量論組成のTiN膜を置き換えた構造を有す

るゲート電極(図1B)のWFeffとを算出した。また、発明者らは、Hf02膜と化学

量論組成のTiN膜間との間に、1、2原子層分のAl膜が挿入された構造を有するゲート電極(図1C、図1D)のWFeffも算出した。さらに、発明者らは、Hf02膜上に

TiN0.75膜(非化学量論組成のTiN膜)が形成された構造を有するゲート電極(図示略)のWFeffも算出した。

【0019】

その結果、図2に示したように、Hf02膜・TiN膜間に1原子層分のAl膜を挿入しただけ(Al1/TiN(st))でも、ゲート電極のWFeffが低下し、2原子層程

度の厚さのAl膜をHf02膜・TiN膜間に形成すれば(Al2/TiN(st))、ゲート電極のWFeffが、Alの仕事関数値近くまで低下することが、分かった。なお、

この図2に示した各算出結果は、シリコン基板の表層側の1.5nm厚の部分からAl膜/TiN膜の下層側の0.96nmの部分までの構造(図1A参照)を対象として、当該構造を緩和してから、第一原理計算法により算出したものである。すなわち、各算出結果は、エネルギー的に最も安定な原子配列を各構造について見つけてから、第一原理計算法により算出したものとなっている。

【0020】

WFeffについての、このシミュレーション結果は、『或る材料からなる、薄い界面膜

をHigh-k膜・金属ゲート膜間に設ければ、当該材料の仕事関数値近傍の値にゲート電極の仕事関数値を制御できる』ということを意味するものである。

【0021】

そして、“金属ゲート膜/界面膜/High-k膜”構造をNMOSトランジスタ側のゲート電極に採用しておけば、上記したように、デュアルHigh-kプロセス(図13)により製造したものと同性能を有する半導体装置をより容易に製造できることになる。また、“金属ゲート膜/界面膜/High-k膜”構造を、一方のMOSトランジスタ側のゲート電極に採用しておけば、デュアルメタルプロセス(図12)により製造されるものと同性能の半導体装置を、NMOSトランジスタ側とPMOSトランジスタ側とに別材料で金属ゲート膜を形成する必要がない形で、製造できることにもなる。

【0022】

ただし、界面膜の形成後に、ハロゲンランプ等による活性化アニールが行われる手順/内容のプロセスでは、界面膜が拡散しまうため、“金属ゲート膜/界面膜/High-k膜”構造を有するゲート電極を実現することは出来ない。そのため、以下で説明する各実施形態に係る製造方法を開発したのである。

【0023】

《第1実施形態》

以下、第1実施形態に係る半導体装置の製造方法の内容を、詳細に説明する。

【0024】

まず、図3を用いて、本実施形態に係る製造方法により製造される半導体装置(以下、第1実施形態に係る半導体装置と表記する)の基本構成を説明する。

【0025】

図3に示してあるように、第1実施形態に係る半導体装置は、半導体基板10上の、素子分離領域12によって区画された各領域上に、PMOSトランジスタのゲート電極1p及びソースドレイン電極2pと、NMOSトランジスタのゲート電極1n及びソースドレイン電極2nとが形成されている半導体装置である。

【0026】

そして、第1実施形態に係る半導体装置は、仕事関数値の調整のためにAlが添加され

た絶縁膜16aを有するゲート電極1pと、絶縁膜16と金属ゲート膜19との間に、仕事関数値を調整するために、Al膜である界面膜18が挿入されたゲート電極1nとを備えたものとなっている。

【0027】

次に、図4A〜図4Kを用いて、本実施形態に係る製造方法による半導体装置の製造手順を具体的に説明する。

【0028】

本実施形態に係る製造方法による半導体装置の製造時には、まず(図4A参照)、Nウェル11、Pウェル13及び素子分離領域12をシリコンウェハー上に形成した半導体基板10が用意される。なお、素子分離領域12は、シリコンウェハー上のNMOS/PMOSトランジスタを形成する各領域の境界位置に、例えばシャロートレンチアイソレーション(STI)で形成される。Nウェル11は、シリコンウェハー上のPMOSトランジスタを形成する各領域にN型不純物イオンを注入することにより形成される。また、Pウェル13は、シリコンウェハー上のNMOSトランジスタを形成する各領域にP型不純物イオンを注入することにより形成される。

【0029】

その後、半導体基板10上に、1nm程度の厚さの酸化シリコン膜15が形成される。この酸化シリコン膜15は、例えば半導体基板10の熱酸化によって形成される。次いで、必要に応じて熱酸化膜に窒素を導入し、続いて絶縁膜16(High-kゲート絶縁膜)として2nm程度の厚さのハフニウム系酸化物膜(HfO2、HfSiOx、HfZrOx、等)が、MOCVD(Metal Organic Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法により形成され、続くプラズマチッ化プロセス等で窒素を導入してHfON、HfSiONを形成する場合もある。

【0030】

そして、形成した絶縁膜16中の酸素欠陥等を低減をさせるために半導体基板10は、例えば、800℃〜1000℃程度のO2/N2雰囲気中でアニールされる。同時に絶縁膜16は膜種により結晶化する。

【0031】

その後、Al含有膜17として、0.5nm程度の厚さのAl酸化物膜やAl膜が、CVD法、スパッタ法等により形成される。なお、半導体装置の製造コストを低減するという観点からは、このAl含有膜17と、界面膜18(Al膜:図4D参照)とが同一の装置により形成されるようにしておくことが、望ましい。

【0032】

Al含有膜17の形成後には、Al含有膜17のPMOS側(Nウェル11側)の部分のみを覆う形状のレジストパターン30が形成される(図4A)。そして、レジストパターン30をマスクとして、Al含有膜17のNMOS側(Pウェル13側)の部分が、希フッ化水素酸、希塩酸等により除去されてから、レジストパターン30が除去される。

【0033】

その後、上記した一連の工程を経た半導体基板10(図4B)を、例えば、N2雰囲気中、1050℃程度の温度で、5秒間程度、アニールするアニール処理が、行われる。

【0034】

このアニール処理が行われると、Al含有膜17中のAlが絶縁膜16内に拡散し、絶縁膜16のPMOS側の部分が、形成時とは組成の異なる絶縁膜16a(図4C)に変わる。また、Alが酸化シリコン膜15内まで拡散することにより、酸化シリコン膜15・絶縁膜16a間の界面部分にHf−O−Al結合が生成され、その結果として、製造中の半導体装置のPMOS側のゲート電極の仕事関数値が、適切な値に調整されることになる。

【0035】

なお、このアニール処理でも、絶縁膜16は結晶化する。そのため、上記した絶縁膜16形成直後のアニールを省略することも出来る。ただし、絶縁膜16を結晶化していれば

、Al含有膜17のパターニング時、つまり希フッ化水素酸等によるNMOS側部分の除去時に絶縁膜16に対して選択比を高くすることが出来る。従って、絶縁膜16形成直後にもアニールを行うようにしておくことが、望ましい。

【0036】

アニール処理後には、図4Dに示したように、絶縁膜16及び16a上に、界面膜18として、数原子層程度の厚さのAl膜がALD法等により形成される。次いで、界面膜18のNMOS側の部分のみを覆う形状のレジストパターン31が形成される。そして、レジストパターン31をマスクとして界面膜18のNMOS側の部分が希フッ化水素等により除去されてから、レジストパターン31が除去される(図4E)。

【0037】

その後、図4Fに示してあるように、金属ゲート膜(以下、MG膜と表記する)19として、例えば10nm程度の厚さのTiN膜が、スパッタ法等により形成される。さらに、50nm程度の厚さのポリシリコン膜20が、例えば熱CVD法により形成される。

【0038】

そして、酸化シリコン膜15からポリシリコン膜20までの部分を、図4Hに示すようなゲート形状に加工するゲートパターニングが行われる。

【0039】

このゲートパターニングは、例えば、以下の手順で行われる。まず、図4Gに示したように、ポリシリコン膜20上に、50nm程度の厚さのSiN(窒化シリコン)膜33と、70nm程度の厚さのBARC(bottom anti-reflection coating)膜34とが、順次、形成される。その後、ArFエキシマ・レーザ用のレジストを用いて、BARC膜34上に、240nm程度の厚さの、目的とするゲート形状に応じた形状(各部のサイズが目的とするサイズより大きな形状)を有するレジストパターン35が形成される。

【0040】

次いで、各種ガスを用いた反応性イオンエッチングにより、レジストパターン35をマスクとしてBARC膜34をエッチングし、レジストパターン35とパターン化されたBARC膜34とを所望サイズとなるようにトリミングし、トリミングしたレジストパターン35等をマスクとしてSiN膜33をパターン化する処理が、行われる。

【0041】

その後、パターン化したSiN膜33をマスクとしてポリシリコン膜20以下の膜が、例えばCl2/CH4ガスを用いて除去される。そして、SiN膜33がフッ化水素酸等により除去されて(図4H)、ゲートパターニングが完了する。

【0042】

続いて、ポリシリコン膜20等をマスクとして、NMOS側に、ポケットイオン、エクステンションイオンが注入される。NMOS側へのポケットイオン、エクステンションイオンとしては、それぞれ、In等のp型不純物イオン、As等のn型不純物イオンが注入される。後の工程にある活性化アニールはミリ秒アニールプロセスを使用するため、エクステンションとゲートのオーバーラップを考慮してチルト角注入(0−45°でチューニング)を対称的な4方向から行う。

【0043】

ポリシリコン膜20等をマスクとして、PMOS側に、ポケットイオン、エクステンションイオンを注入する処理も行われる。なお、この際に注入されるポケットイオン、エクステンションイオンは、それぞれ、n型不純物(例えば、Sb)イオン、p型不純物(例えば、Ge及びB)イオンであり、NMOSと同様にチルト注入で行う。

【0044】

その後、注入した各イオンを、Al膜18中のAlを拡散させることなく活性化するために、ミリ秒アニールが行われる。ここで、ミリ秒アニールとは、レーザーやフラッシュランプにより、ミリ秒単位の加熱を行うプロセスのことである。

【0045】

なお、ミリ秒アニールを行えば、Al膜18中のAlを拡散させることなく注入イオン

を活性化できる。ただし、ミリ秒アニールを行った場合、注入イオンも殆ど拡散しないことになる。そのため、本製造方法は、上記した各イオンの注入を、ハロゲンランプ等による活性化アニールが行われる場合とは異なる、ミリ秒アニール後の不純物プロファイルが所望のものとなるように決定した角度で、行うものとなっている。

【0046】

ミリ秒アニール後には、図4Jに示したように、サイドウォール22用のSi酸化膜を全面に堆積し、このSi酸化膜の全面を異方性エッチングすることにより、Si酸化膜を各ゲート電極の側面にのみ残してサイドウォール22が形成される。

【0047】

サイドウォール22の形成後には、歪を発生させることによりPMOSトランジスタのチャネル領域のホールの移動度を上げるためのストレッサ膜25が、形成される。このストレッサ膜25は、例えば、公知の手法/手順により、PMOS側の各活性領域(ソース/ドレイン領域)をリセスした後、リセスした部分に、例えば、450℃〜500℃程度の減圧熱CVDでSiより格子定数の大きい物質、例えばB添加Si−Ge等を選択成長させることにより、形成される。

【0048】

さらに、サイドウォール22の形成後には、サイドウォール22をマスクとしてNMOSトランジスタの各活性領域にn型不純物(例えば、AsやP)イオンを注入する処理や、注入イオンを活性化するためのミリ秒アニールも行われる。このミリ秒アニール処理によって、不純物をほとんど拡散させずにRTAでは得られなかった高い活性化率で不純物を活性化し、イオン注入に生じた結晶のダメージ回復もできると考えられる。

【0049】

その後、本実施形態に係る製造方法では、半導体基板10上の各所に、CoSi2、NiSi等のシリサイド膜26を形成するためのシリサイドプロセスが行われる。そして、図4Kに示した構成を有する半導体装置が製造される。すなわち、絶縁膜16とMG膜19との間に薄い界面膜18を挿入することによって仕事関数値を調整したゲート電極1n、及び、ソースドレイン電極2nを有するNMOSトランジスタと、Alの拡散により仕事関数値を調整したゲート電極1p、及び、ソースドレイン電極2pを有するNMOSトランジスタとを備えた半導体装置が製造される。

【0050】

以上、説明したように、本実施形態に係る製造方法は、注入イオンの活性化が、サーマルバジェットの少ないミリ秒アニールで行われるものとなっている。そのため、この製造方法によれば、“MG膜19/界面膜18/絶縁膜16”構造を有するPMOS側のゲート電極1pを備えた半導体装置を確実に製造できることになる。

【0051】

そして、そのような構造を有するゲート電極1pは、図2を用いて説明したように、デュアルHigh-kプロセスにより製造されるPMOS側のゲート電極と同性能のものとなる。従って、本実施形態に係る製造方法によれば、デュアルHigh-kプロセスにより製造される半導体装置と同性能の半導体装置を、より容易に製造できることになる。

【0052】

また、本実施形態に係る製造方法により製造される半導体装置は、NMOS側のゲート電極の仕事関数値制御、PMOS側のゲート電極の仕事関数値制御の双方に、Alが利用されたものとなっている。従って、本実施形態に係る製造方法は、半導体装置の製造に必要とされる物質数が少ない分、安価に、半導体装置を製造できる方法となっていることにもなる。

【0053】

《第2実施形態》

以下、図5A〜図5Fを用いて、第2実施形態に係る製造方法(半導体装置の製造方法)の内容を、第1実施形態に係る製造方法と異なる部分を中心に、説明する。なお、本実施形態及び後述する第3、第4実施形態に係る各製造方法により製造される半導体装置は

、第1実施形態に係る半導体装置と同じ基本構成(図3)を有するものである。

【0054】

第2実施形態に係る製造方法では、図5Aに示してあるように、まず、Nウェル11、Pウェル13及び素子分離領域12が形成されている半導体基板10上に、1nm程度の厚さの酸化シリコン膜15が、例えば半導体基板10の熱酸化により形成される。

【0055】

次いで、絶縁膜16(図4A、図5B参照)ではなく、0.5nm程度の厚さのAl含有膜17(Al酸化物膜等)が、CVD法、スパッタ法等により形成される。

【0056】

Al含有膜17の形成後には、Al含有膜17のPMOS側の部分のみを覆う形状のレジストパターン30が形成される。その後、レジストパターン30をマスクとして、Al含有膜17のNMOS側の部分が、希フッ化水素酸、希塩酸等により除去される。

【0057】

そして、不要となったレジストパターン30が除去されてから、図5Bに示してあるように、2nm程度の厚さのハフニウム系酸化物膜が、絶縁膜16として、MOCVD法やALD法により形成される。

【0058】

その後、絶縁膜16を結晶化させると共に、Al含有膜17中のAlを絶縁膜16及び酸化シリコン膜15中に拡散させるためのアニール処理が、行われる。このアニール処理としては、第1実施形態と同様に、半導体基板10を、1050℃程度の不活性ガス(例えば、N2)雰囲気中で5秒間程度アニールする処理が、行われる。

【0059】

アニール処理が行われると、Al含有膜17中のAlが絶縁膜16側へ拡散し、絶縁膜16のPMOS側の部分が、形成時とは組成の異なる絶縁膜16a(図5C)に変わることになる。また、酸化シリコン膜15側にAlが拡散することにより、酸化シリコン膜15・絶縁膜16間の界面部分にHf−O−Al結合が生成され、その結果として、製造中の半導体装置のPMOS側のゲート電極の仕事関数値が、適切な値に調整されることになる。

【0060】

絶縁膜16及び絶縁膜16a上には、図5Dに示したように、数原子層程度の厚さの界面膜18がALD法等により形成される。次いで、界面膜18のNMOS側の部分のみを覆う形状のレジストパターン31が形成される。そして、レジストパターン31をマスクとして界面膜18のNMOS側の部分が希フッ化水素等により除去されてから、レジストパターン31が除去される(図5E)。

【0061】

その後、図5Fに示したように、絶縁膜16a及び界面膜18上に、MG膜(金属ゲート膜)19として、例えば、10nm程度の厚さのTiN膜がスパッタ法等により形成される。さらに、50nm程度の厚さのポリシリコン膜20が、例えば熱CVD法により形成される。

【0062】

この後、本実施形態に係る製造方法では、図4H〜図4Kを用いて説明したものと同内容のプロセスが行われる。そして、図4Kに示したものと本質的には同構成の半導体装置が製造される。

【0063】

以上の説明から明らかなように、本実施形態に係る製造方法は、酸化シリコン膜15及び絶縁膜16へのAlの供給源として機能するAl含有膜17の形成位置のみが、第1実施形態に係る製造方法と異なったものとなっている。従って、この製造方法によっても、デュアルHigh-kプロセスにより製造される半導体装置と同性能の半導体装置を、より容易かつ安価に、製造できることになる。

【0064】

《第3実施形態》

以下、図6A〜図6Jを用いて、第3実施形態に係る製造方法(半導体装置の製造方法)の内容を説明する。

【0065】

本実施形態に係る製造方法による半導体装置の製造時には、まず、第1実施形態に係る製造方法と同じ手順で、半導体基板10上に、図6Aに示した構造、つまり、図4Bに示したものと同じ構造が形成される。次いで、上記したものと同内容のアニール処理が、行われる。

【0066】

その後、第3実施形態に係る製造方法では、図6Bに示したように、界面膜18やMG膜19ではなく、60nm程度の厚さのポリシリコン膜27が、例えばCVD法により形成される。

【0067】

その後、ポリシリコン膜27を形成した半導体基板10に対して、図4G〜図4Kを用いて説明したものと同内容のプロセス、又は、当該プロセス中のミリ秒アニールをハロゲンランプアニール等に変えたプロセスが、行われる。

【0068】

そして、その結果として、半導体基板10上/内に、図6Cに示した構造が形成される。すなわち、ゲート電極1p(図4K参照)に相当する部分が、酸化シリコン膜15、絶縁膜16a、ポリシリコン膜20の積層体となっていること、及び、ゲート電極1nに相当する部分が、酸化シリコン膜15、絶縁膜16、ポリシリコン膜20の積層体となっていることを除けば、図4Kに示したものと同じ構造が、半導体基板10上/内に形成される。

【0069】

この後、本実施形態に係る製造方法では、図6Dに示したように、60nm程度の厚さの層間絶縁膜28が形成される。この層間絶縁膜28としては、例えば酸化シリコン膜が、CVD等により形成される。

【0070】

次いで、CMP(Chemical and Mechanical Polishing)法により、層間絶縁膜28が、

ポリシリコン膜20の上面が露出するまで研磨される。そして、図6Eに示したように、ポリシリコン膜20が、例えばTMAH(テトラメチルアンモニウムハイドロオキサイド)を用いて除去される。

【0071】

ポリシリコン膜20の除去後には、図6Fに示したように、半導体基板10の全面(層間絶縁膜28上、サイドウォール22等によって形成されている凹部内)に、数原子層程度の厚さのAl膜である界面膜18が、ALD法等により形成される。そして、レジストパターンの形成を含む一連の処理により、界面膜18のPMOS側の部分のみが希フッ化水素等により除去される(図6G)。

【0072】

その後、図6Hに示したように、MG膜19として、例えば、10nm程度の厚さのTiN膜がスパッタ法等により形成される。次いで、半導体基板10の全面に、サイドウォール22等によって形成されている凹部を完全に埋める厚さのTiAl膜29が、下層側の方がTiリッチとなるように膜を積層する形で、蒸着法、スパッタ法等により形成される。

【0073】

その後、TiAl膜29等が、CMP法により、層間絶縁膜28が露出するまで研磨される。そして、図6Jに示したように、絶縁膜16とMG膜19との間に薄い界面膜18を挿入することによって仕事関数値を調整したゲート電極1n、及び、ソースドレイン電極2nを有するNMOSトランジスタと、Alの拡散により仕事関数値を調整したゲート電極1p、及び、ソースドレイン電極2pを有するNMOSトランジスタとを備えた半導

体装置が製造される。

【0074】

以上、説明したように、本実施形態に係る製造方法は、半導体基板10に注入したイオンを活性化した後に、界面膜18を形成するものとなっている。従って、この製造方法によっても、“MG膜19/界面膜18/絶縁膜16”構造を有するPMOS側のゲート電極1pを備えた半導体装置を製造できる。そして、その結果として、本実施形態に係る製造方法によれば、High-kゲート絶縁膜が用いられた半導体装置を製造できることになる。

【0075】

《第4実施形態》

以下、第4実施形態に係る製造方法(半導体装置の製造方法)の内容を、第3実施形態に係る製造方法と異なる部分を中心に、説明する。

【0076】

第4実施形態に係る製造方法では、まず、第2実施形態に係る製造方法と同じ手順で、半導体基板10上に、図7Aに示した構造、つまり図5Bに示したものと同じ構造が形成される。

【0077】

そして、絶縁膜16を結晶化させると共に、Al含有膜17中のAlを絶縁膜16及び酸化シリコン膜15中に拡散させるためのアニール処理が行われてから、図7Bに示したように、酸化シリコン等からなる、60nm程度の厚さの層間絶縁膜28が形成される。

【0078】

この後、第4実施形態に係る製造方法では、第3実施形態に係る製造方法と同内容のプロセス(図6B〜図6J参照)が行われる。そして、図6Jに示したものと本質的には同構成の半導体装置が製造される。

【0079】

以上の説明から明らかなように、本実施形態に係る製造方法は、酸化シリコン膜15及び絶縁膜16へのAlの供給源として機能するAl膜18の形成位置のみが、第3実施形態に係る製造方法と異なったものとなっている。従って、この製造方法によってもHigh-kゲート絶縁膜が用いられた半導体装置を製造できることになる。

【0080】

《第5実施形態》

まず、図8を用いて、第5実施形態に係る製造方法(半導体装置の製造方法)により製造される半導体装置(以下、第5実施形態に係る半導体装置と表記する)の基本構成を説明する。

【0081】

図8に示してあるように、第5実施形態に係る半導体装置は、ゲート電極1p及びソースドレイン電極2pを有するPMOSトランジスタと、ゲート電極1n及びソースドレイン電極2nを有するNMOSトランジスタとが、半導体基板10上の素子分離領域12によって区画された領域に形成されている装置である。そして、第5実施形態に係る半導体装置は、各MOSトランジスタのゲート電極として、絶縁膜16上に直接MG膜19a(詳細は後述)が形成されているゲート電極1pと、絶縁膜16上に、Al膜である界面膜18を介してMG膜19aが形成されているゲート電極1nとを、備えたものとなっている。

【0082】

次に、本実施形態に係る製造方法を説明する。

【0083】

上記構成を有する半導体装置を製造するために、本実施形態に係る製造方法では、まず、図9Aに示してあるように、半導体基板10上に、酸化シリコン膜15、絶縁膜16、MG膜19aが、順次、形成される。

【0084】

この際、酸化シリコン膜15としては、1nm程度の厚さのものが、例えば半導体基板

10の熱酸化によって形成される。また、絶縁膜16としては、2nm程度の厚さのハフニウム系酸化物膜が、MOCVD法やALD法により形成される。そして、MG膜19aとしては、仕事関数値の調整を行わなくてもPMOSトランジスタ用のゲート電極を実現できる材料(例えば、TiN)からなる、10nm程度の厚さの膜が、形成される。

【0085】

その後、図9Bに示したように、MG膜19aのPMOS側の部分のみを覆う形状のレジストパターン40が、形成される。そして、レジストパターン40をマスクとして、MG膜19aのNMOS側の部分のみに、Alイオンが注入される。このイオン注入は、MG膜19a・絶縁膜16界面に到達し得る加速エネルギー、例えばMG膜19の厚さが10nmである場合は、30kV〜40kVで、ドーズ量が2x1017/cm2程度となるよ

うに、行われる。

【0086】

Alイオンの注入後には、レジストパターン40が除去される。次いで、レジストパターン40除去後の半導体基板10を、Alの融点よりも少なくとも100℃低い温度、例えば360℃〜560℃の不活性ガス(例えば、N2)中で、2分〜10分程度、アニールする回復アニール処理が行われる。

【0087】

Alは、MG膜19a(TiN膜等)内に存在する場合よりも、酸素と結合している場合の方がエネルギー的に安定となる物質である。そのため、上記内容の回復アニール処理が行われると、図9Cに示したように、MG膜19a・絶縁膜16界面のNMOS側の部分に、数原子層分の界面膜18(Al膜)が形成されることになる。

【0088】

この後、本実施形態に係る製造方法では、図3F〜図3Kを用いて説明したものと同内容のプロセスが行われる。そして、その基本構成が図8に示したものとなっている半導体装置が製造される。

【0089】

以上の説明から明らかなように、この第5実施形態に係る製造方法は、いわば、デュアルメタルプロセスにより製造される半導体装置(図12参照)相当のものを、NMOSトランジスタ側とPMOSトランジスタ側とに別材料で金属ゲート膜を形成する必要がない形で製造できるものとなっている。

【0090】

従って、本実施形態に係る製造方法によれば、デュアルメタルプロセスにより製造される半導体装置と同性能の半導体装置を、金属ゲート膜の作り分けが不要な形で製造できることになる。

【0091】

《第6実施形態》

図10に、第6実施形態に係る製造方法(半導体装置の製造方法)により製造される半導体装置(以下、第6実施形態に係る半導体装置と表記する)の基本構成を示す。

【0092】

この図10から明らかなように、第6実施形態に係る半導体装置は、絶縁膜16上にMG膜19bが積層されているゲート電極1nを有するNMOSトランジスタと、絶縁膜16とMG膜19bとの間に界面膜18aが挿入されているゲート電極1pを有するPMOSトランジスタを備えた半導体装置である。

【0093】

この半導体装置の各ゲート電極1p、1n内のMG膜19bは、ハフニウム系酸化物を用いた絶縁膜16上に形成すると、仕事関数値の調整を行わなくてもNMOSトランジスタ用のゲート電極を実現できる材料、例えば、TiCやTaCからなる、10nm程度の厚さの膜である。また、ゲート電極1p内にのみ含まれる界面膜18aは、5eV程度の仕事関数値を有する材料、例えば、Ptからなる、数原子層程度の厚さの膜である。

【0094】

そして、第6実施形態に係る製造方法は、上記構成を有する半導体装置を以下の手順で製造するものとなっている。

【0095】

本実施形態に係る製造方法による半導体装置の製造時には、図11Aに示してあるように、半導体基板10上に、1nm程度の厚さの酸化シリコン膜15、絶縁膜16、MG膜19bが、順次、形成されてから、MG膜19bのPMOS側の部分のみを覆う形状のレジストパターン41が、形成される。

【0096】

その後、レジストパターン41をマスクとして、MG膜19bのPMOS側の部分のみに、例えば、Ptイオンが注入される。このイオン注入は、MG膜19b・絶縁膜16界面に到達し得る加速エネルギーで、ドーズ量が2x1017/cm2程度となるように、行わ

れる。

【0097】

Ptイオンの注入後には、レジストパターン41が除去される。その後、Ptを、MG膜19b・絶縁膜16界面に偏析させるための回復アニール処理が行われて、図12Bに示したように、MG膜19b・絶縁膜16界面のPMOS側の部分に、Ptからなる薄い界面膜18aが形成される。

【0098】

この後、本実施形態に係る製造方法では、図3F〜図3Kを用いて説明したものと同内容のプロセスが行われる。そして、その基本構成が図10に示したものとなっている半導体装置が製造される。

【0099】

以上の説明から明らかなように、この第5実施形態に係る製造方法も、いわば、デュアルメタルプロセスにより製造される半導体装置(図12参照)相当のものを、2種の金属ゲート膜を作り分けが不要な形で製造できるものとなっている。

【0100】

従って、本実施形態に係る製造方法によっても、デュアルメタルプロセスにより製造される半導体装置と同性能の半導体装置を、金属ゲート膜を作り分けが不要な形製造できることになる。

【0101】

《変形形態》

上記した各実施形態に係る製造方法は、各種の変形を行うことが出来る。例えば、第1〜第4実施形態に係る製造方法を、Alイオンの打ち込みと回復アニール処理により界面膜18を形成する方法に変形することが出来る。第3、第4実施形態に係る製造方法を、絶縁膜16の形成後(図5B)のアニール、Al含有膜17のエッチング後(図6A)のアニールが行われない方法、つまり注入イオンの活性化時にAlを拡散させる方法に変形することも出来る。第5、第6実施形態に係る製造方法を、いわゆるゲートラストプロセスが採用されているものに変形することも出来る。

【0102】

また、各実施形態に係る製造方法を、界面膜18、18a、18bと直接関係しない部分の構成が上記したものとは異なる半導体装置、例えばSOS(silicon on sapphire)

基板が用いられた半導体装置、ストレッサ膜26を備えない半導体装置、ゲート電極1nのポリシリコン膜20にAsイオン等が打ち込まれている半導体装置等を製造するものに変形しても良いことは当然のことである。

【0103】

以上、開示した技術に関し、更に以下の付記を開示する。

【0104】

(付記1) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記NMSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

を有する半導体装置の製造方法。

【0105】

(付記2) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Si酸化物を含む第1絶縁膜を形成する工程と、

前記第1絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にHf酸化物を含む第2絶縁膜を形成する工程と、

前記第2絶縁膜上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

を有する半導体装置の製造方法。

【0106】

(付記3) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にSi層を形成する工程と、

前記Si層をパターニングして、前記PMOSトランジスタ形成領域に第1パターン電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2パターン電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1パターン電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2パターン電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記第1ソースドレイン電極および前記第2ソースドレイン電極を形成する工程の後、前記第1パターン電極、前記第2パターン電極、第1ソースドレインおよび電極第2ソースドレイン電極上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を研磨し、前記第1パターン電極及び前記第2パターン電極の上面を露出させる工程と、

前記層間絶縁膜の研磨の後、前記第1パターン電極及び前記第2パターン電極の上面を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上およびNMOSトランジスタ形成領域上に金属膜を形成する工程と

を有する半導体装置の製造方法。

【0107】

(付記4) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Si酸化物を含む第1絶縁膜を形成する工程と、

前記第1絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上にHf酸化物を含む第2絶縁膜を形成する工程と、

前記第2絶縁膜上にSi層を形成する工程と、

前記Si層をパターニングして、前記PMOSトランジスタ形成領域に第1パターン電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2パターン電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1パターン電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2パターン電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記第1ソースドレイン電極および前記第2ソースドレイン電極を形成する工程の後、前記第1パターン電極、前記第2パターン電極、第1ソースドレインおよび電極第2ソースドレイン電極上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を研磨し、前記第1パターン電極及び第2パターン電極の上面を露出させる工程と、

前記層間絶縁膜の研磨の後、前記第1パターン電極及び第2パターン電極の上面を除去する工程と、

前記第1パターン電極および前記第2パターン電極を除去する工程の後、PMOSトランジスタ形成領域上およびNMOSトランジスタ形成領域上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する

工程と、

を有する半導体装置の製造方法。

【0108】

(付記5) 前記金属層はTiN層であることを特徴とする、付記1乃至付記4のいずれか1項に記載の半導体装置の製造方法。

【0109】

(付記6) 前記PMOSトランジスタ形成領域上のAl含有膜を第1マスク層で覆い、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記Al膜を形成する工程の前に、熱処理により、前記PMOSトランジスタ形成領域上の前記Al含有膜のAlを前記絶縁膜中に拡散させることを特徴とする、付記1又は付記3に記載の半導体装置の製造方法。

【0110】

(付記7) 前記第2絶縁膜を形成する工程の後、前記Al膜を形成する工程の前に、

熱処理により、前記PMOSトランジスタ形成領域上の前記Al含有膜のAlを前記第1絶縁膜中に拡散させることを特徴とする、付記2又は付記4に記載の半導体装置の製造方法。

【0111】

(付記8) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記金属膜を形成する工程と前記金属膜をパターニングする工程との間に行われる、前記金属膜上の前記NMOSトランジスタ形成領域上の部分に、前記金属膜と前記絶縁膜との界面に偏析させることにより前記第1ゲート電極の仕事関数値を調整するためのイオンを打ち込む工程と、

を有する半導体装置の製造方法。

【0112】

(付記9) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記金属膜を形成する工程と前記金属膜をパターニングする工程との間に行われる、前記金属膜上の前記PMOSトランジスタ形成領域上の部分に、前記金属膜と前記絶縁膜との界面に偏析させることにより前記第2ゲート電極の仕事関数値を調整するためのイオンを打ち込む工程と、

を有する半導体装置の製造方法。

【0113】

(付記10) 半導体基板上にPMOSトランジスタとNMOSトランジスタとが形成

されている半導体装置であって、

前記PMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に金属ゲート膜が設けられているゲート電極を有し、

前記NMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上にAl膜を介して金属ゲート膜が設けられているゲート電極を有する

ことを特徴とする半導体装置。

【0114】

(付記11) 熱処理により、仕事関数値を調整するために打ち込まれた前記イオンを前記金属膜と前記絶縁膜との界面に偏析させる工程をさらに含むことを特徴とする、付記8又は付記9に記載の半導体装置の製造方法。

【0115】

(付記12) 前記第1不純物注入及び前記第2不純物注入により注入された不純物を活性化するための活性化アニールとして、ミリ秒アニールを行うことを特徴とする、付記1又は付記2に記載の半導体装置の製造方法。

【0116】

(付記13) 半導体基板上にPMOSトランジスタとNMOSトランジスタとが形成されている半導体装置であって、

前記PMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に界面膜を介して金属ゲート膜が設けられているゲート電極を有し、

前記NMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に金属ゲート膜が設けられているゲート電極を有し、

その仕事関数値が、前記界面膜を設けずに形成した前記PMOSトランジスタのゲート電極の仕事関数値よりも小さい材料により、前記界面膜が形成されている

ことを特徴とする半導体装置。

【0117】

(付記14) 半導体基板上にPMOSトランジスタとNMOSトランジスタとが形成されている半導体装置であって、

前記PMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に金属ゲート膜が設けられているゲート電極を有し、

前記NMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に界面膜を介して金属ゲート膜が設けられているゲート電極を有し、

その仕事関数値が、前記界面膜を設けずに形成した前記NMOSトランジスタのゲート電極の仕事関数値よりも小さい材料により、前記界面膜が形成されている

ことを特徴とする半導体装置。

【符号の説明】

【0118】

1p、1n ゲート電極

2p、2n ソースドレイン電極

10 半導体基板

11 Nウェル

12 素子分離領域

13 Pウェル

15 酸化シリコン膜

16、16a 絶縁膜

17 Al含有膜

18 界面膜

19、19a、19b 金属ゲート膜(MG膜)

20、27 ポリシリコン膜

22 サイドウォール

25 ストレッサ膜

26 シリサイド膜

28 層間絶縁膜

29 TiAl膜

【技術分野】

【0001】

本発明は、半導体装置の製造方法と半導体装置とに関する。

【背景技術】

【0002】

従来、MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor:以下、

MOSトランジスタ又はMOSと略記する)のゲート絶縁膜としては、酸化シリコン(SiO2)膜が用いられていたが、MOSトランジスタの微細化/集積化のためにゲート絶縁膜を薄くすると、リーク電流が増えてしまう。従って、酸化シリコンよりも比誘電率が高いHf系酸化物をゲート絶縁膜として用いることが検討されている。Hf系酸化物膜上にポリシリコン電極やシリサイド電極を直接形成したのでは、Fermi Level pinningのた

めに、NMOS/PMOSトランジスタのゲート電極の実効的仕事関数の値を制御できない。

【0003】

そのため、図12に示したように、NMOS側のゲート絶縁膜56上と、PMOS側のゲート絶縁膜56上とに、仕事関数値の異なる金属ゲート膜59a、59bを形成するプロセス(以下、デュアルメタルプロセスと表記する)により、各ゲート電極の仕事関数値を制御することが提案されている。なお、図12及び図13において、絶縁膜56下に形成されている膜55は、酸化シリコン膜であり、金属ゲート膜59a、59b、59上に形成されている膜60は、ポリシリコン膜である。

【0004】

また、各ゲート電極の仕事関数値を制御できるプロセスとして、デュアルHigh-kプロセスと一般に呼ばれているプロセスも知られている。

【0005】

このデュアルHigh-kプロセスでは、図13に示したように、PMOS側の絶縁膜56と金属ゲート膜59との間にAl2O3等からなるキャップ層58aを設けておくと共に、NMOS側の絶縁膜56と金属ゲート膜59との間にLa2O3等からなるキャップ層58cを設けておく。そして、続く熱処理工程で各キャップ層58a(例えばAl膜)、58c(例えばLa膜)を拡散させて絶縁膜58の組成を変える(絶縁膜56を絶縁膜56a、56cに変える)と共に、絶縁膜56a、56cと酸化シリコン膜55の界面に、Hf−O−Al結合、Hf−O−La結合を生成することによって、各ゲート電極の仕事関数値を制御する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特表2008−507149号公報

【特許文献2】特開2008−16798号公報

【特許文献3】特表2008−515190号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

開示の技術の課題は、半導体装置を容易に製造できる半導体装置の製造方法を提供することにある。

【0008】

また、開示の技術の他の課題は、製造が容易な構成/構造を有する半導体装置を提供することにある。

【課題を解決するための手段】

【0009】

上記課題を解決するために、開示の技術の一態様では、半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、前記絶縁膜上にAl含有膜を形成する工程と、前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にAl膜を形成する工程と、前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程とにより、半導体装置が製造される。

【発明の効果】

【0010】

以上の工程によれば、半導体装置を容易に製造できることになる。

【図面の簡単な説明】

【0011】

【図1A】実効的仕事関数値が第一原理計算法により算出された構造の説明図(その1)。

【図1B】実効的仕事関数値が第一原理計算法により算出された構造の説明図(その2)。

【図1C】実効的仕事関数値が第一原理計算法により算出された構造の説明図(その3)。

【図1D】実効的仕事関数値が第一原理計算法により算出された構造の説明図(その4)。

【図2】実効的仕事関数値の算出結果の説明図。

【図3】第1実施形態に係る製造方法により製造される半導体装置の基本構成の説明図。

【図4A】第1実施形態に係る製造方法を説明するための工程図(その1)。

【図4B】第1実施形態に係る製造方法を説明するための工程図(その2)。

【図4C】第1実施形態に係る製造方法を説明するための工程図(その3)。

【図4D】第1実施形態に係る製造方法を説明するための工程図(その4)。

【図4E】第1実施形態に係る製造方法を説明するための工程図(その5)。

【図4F】第1実施形態に係る製造方法を説明するための工程図(その6)。

【図4G】第1実施形態に係る製造方法を説明するための工程図(その7)。

【図4H】第1実施形態に係る製造方法を説明するための工程図(その8)。

【図4I】第1実施形態に係る製造方法を説明するための工程図(その9)。

【図4J】第1実施形態に係る製造方法を説明するための工程図(その10)。

【図4K】第1実施形態に係る製造方法を説明するための工程図(その11)。

【図5A】第2実施形態に係る製造方法を説明するための工程図(その1)。

【図5B】第2実施形態に係る製造方法を説明するための工程図(その2)。

【図5C】第2実施形態に係る製造方法を説明するための工程図(その3)。

【図5D】第2実施形態に係る製造方法を説明するための工程図(その4)。

【図5E】第2実施形態に係る製造方法を説明するための工程図(その5)。

【図5F】第2実施形態に係る製造方法を説明するための工程図(その6)。

【図6A】第3実施形態に係る製造方法を説明するための工程図(その1)。

【図6B】第3実施形態に係る製造方法を説明するための工程図(その2)。

【図6C】第3実施形態に係る製造方法を説明するための工程図(その3)。

【図6D】第3実施形態に係る製造方法を説明するための工程図(その4)。

【図6E】第3実施形態に係る製造方法を説明するための工程図(その5)。

【図6F】第3実施形態に係る製造方法を説明するための工程図(その6)。

【図6G】第3実施形態に係る製造方法を説明するための工程図(その7)。

【図6H】第3実施形態に係る製造方法を説明するための工程図(その8)。

【図6I】第3実施形態に係る製造方法を説明するための工程図(その9)。

【図6J】第3実施形態に係る製造方法を説明するための工程図(その10)。

【図7A】第4実施形態に係る製造方法を説明するための工程図(その1)。

【図7B】第4実施形態に係る製造方法を説明するための工程図(その2)。

【図8】第5実施形態に係る製造方法により製造される半導体装置の基本構成の説明図。

【図9A】第5実施形態に係る製造方法を説明するための工程図(その1)。

【図9B】第5実施形態に係る製造方法を説明するための工程図(その2)。

【図9C】第5実施形態に係る製造方法を説明するための工程図(その3)。

【図10】第6実施形態に係る製造方法により製造される半導体装置の基本構成の説明図。

【図11A】第6実施形態に係る製造方法を説明するための工程図(その1)。

【図11B】第6実施形態に係る製造方法を説明するための工程図(その2)。

【図12】デュアルHigh-kプロセスの説明図。

【図13】デュアルメタルプロセスの説明図。

【発明を実施するための形態】

【0012】

以下、図面を参照して一実施形態に係る半導体装置の製造方法について説明する。なお、以下で説明する各実施形態(第1〜第6実施形態)は、あくまで製造方法の一形態/一例であり、本発明は、以下の説明における特定の技術事項に限定されるものではない。

【0013】

第1〜第6実施形態に係る半導体装置の製造方法(以下、単に製造方法とも表記する)の詳細説明を行う前に、まず、各製造方法の概要説明を行う。

【0014】

以下で説明する各製造方法は、発明者らが鋭意研究することによって得られた、『或る材料からなる、数原子層程度の厚さの界面膜をHigh-k膜・金属ゲート膜間に設ければ、当該材料の仕事関数値近傍の値にゲート電極の仕事関数値を制御できる』という知見に基づき、開発されたものである。

【0015】

具体的には、既に説明したように、デュアルHigh-kプロセス(図13)では、La2O3等からなるキャップ層58cとAl2O3等からなるキャップ層58aとを形成するが、キャップ層58c材料として使用可能な材料(La2O3等)は、一般に、剥離(除去)が比較的に困難な材料となっている。

【0016】

一方、PMOSトランジスタ側のキャップ層58a材料として使用されているAlは、剥離が簡単に行える材料である。しかも、Alは、仕事関数値が小さい材料であるため、High-kゲート絶縁膜上へのAl膜の形成によりNMOS側のゲート電極の仕事関数値を制御できる場合には、La2O3膜等の剥離が不要となり、半導体装置の製造に要する物質数が減る結果として、High-kゲート絶縁膜を備えた半導体装置をより容易に製造できることになる。

【0017】

そのため、発明者らは、図1A〜図1Dに示した構造を有するゲート電極等の実効的仕

事関数値WFeffを、第一原理計算法により算出した。

【0018】

すなわち、発明者らは、シリコン基板上に、0.88nm厚の酸化シリコン膜と2.2nm厚

のHf02膜とAl膜とがこの順で積層された構造を有するゲート電極(図1A)のWFeffと、当該ゲート電極のAl膜部分を化学量論組成のTiN膜を置き換えた構造を有す

るゲート電極(図1B)のWFeffとを算出した。また、発明者らは、Hf02膜と化学

量論組成のTiN膜間との間に、1、2原子層分のAl膜が挿入された構造を有するゲート電極(図1C、図1D)のWFeffも算出した。さらに、発明者らは、Hf02膜上に

TiN0.75膜(非化学量論組成のTiN膜)が形成された構造を有するゲート電極(図示略)のWFeffも算出した。

【0019】

その結果、図2に示したように、Hf02膜・TiN膜間に1原子層分のAl膜を挿入しただけ(Al1/TiN(st))でも、ゲート電極のWFeffが低下し、2原子層程

度の厚さのAl膜をHf02膜・TiN膜間に形成すれば(Al2/TiN(st))、ゲート電極のWFeffが、Alの仕事関数値近くまで低下することが、分かった。なお、

この図2に示した各算出結果は、シリコン基板の表層側の1.5nm厚の部分からAl膜/TiN膜の下層側の0.96nmの部分までの構造(図1A参照)を対象として、当該構造を緩和してから、第一原理計算法により算出したものである。すなわち、各算出結果は、エネルギー的に最も安定な原子配列を各構造について見つけてから、第一原理計算法により算出したものとなっている。

【0020】

WFeffについての、このシミュレーション結果は、『或る材料からなる、薄い界面膜

をHigh-k膜・金属ゲート膜間に設ければ、当該材料の仕事関数値近傍の値にゲート電極の仕事関数値を制御できる』ということを意味するものである。

【0021】

そして、“金属ゲート膜/界面膜/High-k膜”構造をNMOSトランジスタ側のゲート電極に採用しておけば、上記したように、デュアルHigh-kプロセス(図13)により製造したものと同性能を有する半導体装置をより容易に製造できることになる。また、“金属ゲート膜/界面膜/High-k膜”構造を、一方のMOSトランジスタ側のゲート電極に採用しておけば、デュアルメタルプロセス(図12)により製造されるものと同性能の半導体装置を、NMOSトランジスタ側とPMOSトランジスタ側とに別材料で金属ゲート膜を形成する必要がない形で、製造できることにもなる。

【0022】

ただし、界面膜の形成後に、ハロゲンランプ等による活性化アニールが行われる手順/内容のプロセスでは、界面膜が拡散しまうため、“金属ゲート膜/界面膜/High-k膜”構造を有するゲート電極を実現することは出来ない。そのため、以下で説明する各実施形態に係る製造方法を開発したのである。

【0023】

《第1実施形態》

以下、第1実施形態に係る半導体装置の製造方法の内容を、詳細に説明する。

【0024】

まず、図3を用いて、本実施形態に係る製造方法により製造される半導体装置(以下、第1実施形態に係る半導体装置と表記する)の基本構成を説明する。

【0025】

図3に示してあるように、第1実施形態に係る半導体装置は、半導体基板10上の、素子分離領域12によって区画された各領域上に、PMOSトランジスタのゲート電極1p及びソースドレイン電極2pと、NMOSトランジスタのゲート電極1n及びソースドレイン電極2nとが形成されている半導体装置である。

【0026】

そして、第1実施形態に係る半導体装置は、仕事関数値の調整のためにAlが添加され

た絶縁膜16aを有するゲート電極1pと、絶縁膜16と金属ゲート膜19との間に、仕事関数値を調整するために、Al膜である界面膜18が挿入されたゲート電極1nとを備えたものとなっている。

【0027】

次に、図4A〜図4Kを用いて、本実施形態に係る製造方法による半導体装置の製造手順を具体的に説明する。

【0028】

本実施形態に係る製造方法による半導体装置の製造時には、まず(図4A参照)、Nウェル11、Pウェル13及び素子分離領域12をシリコンウェハー上に形成した半導体基板10が用意される。なお、素子分離領域12は、シリコンウェハー上のNMOS/PMOSトランジスタを形成する各領域の境界位置に、例えばシャロートレンチアイソレーション(STI)で形成される。Nウェル11は、シリコンウェハー上のPMOSトランジスタを形成する各領域にN型不純物イオンを注入することにより形成される。また、Pウェル13は、シリコンウェハー上のNMOSトランジスタを形成する各領域にP型不純物イオンを注入することにより形成される。

【0029】

その後、半導体基板10上に、1nm程度の厚さの酸化シリコン膜15が形成される。この酸化シリコン膜15は、例えば半導体基板10の熱酸化によって形成される。次いで、必要に応じて熱酸化膜に窒素を導入し、続いて絶縁膜16(High-kゲート絶縁膜)として2nm程度の厚さのハフニウム系酸化物膜(HfO2、HfSiOx、HfZrOx、等)が、MOCVD(Metal Organic Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法により形成され、続くプラズマチッ化プロセス等で窒素を導入してHfON、HfSiONを形成する場合もある。

【0030】

そして、形成した絶縁膜16中の酸素欠陥等を低減をさせるために半導体基板10は、例えば、800℃〜1000℃程度のO2/N2雰囲気中でアニールされる。同時に絶縁膜16は膜種により結晶化する。

【0031】

その後、Al含有膜17として、0.5nm程度の厚さのAl酸化物膜やAl膜が、CVD法、スパッタ法等により形成される。なお、半導体装置の製造コストを低減するという観点からは、このAl含有膜17と、界面膜18(Al膜:図4D参照)とが同一の装置により形成されるようにしておくことが、望ましい。

【0032】

Al含有膜17の形成後には、Al含有膜17のPMOS側(Nウェル11側)の部分のみを覆う形状のレジストパターン30が形成される(図4A)。そして、レジストパターン30をマスクとして、Al含有膜17のNMOS側(Pウェル13側)の部分が、希フッ化水素酸、希塩酸等により除去されてから、レジストパターン30が除去される。

【0033】

その後、上記した一連の工程を経た半導体基板10(図4B)を、例えば、N2雰囲気中、1050℃程度の温度で、5秒間程度、アニールするアニール処理が、行われる。

【0034】

このアニール処理が行われると、Al含有膜17中のAlが絶縁膜16内に拡散し、絶縁膜16のPMOS側の部分が、形成時とは組成の異なる絶縁膜16a(図4C)に変わる。また、Alが酸化シリコン膜15内まで拡散することにより、酸化シリコン膜15・絶縁膜16a間の界面部分にHf−O−Al結合が生成され、その結果として、製造中の半導体装置のPMOS側のゲート電極の仕事関数値が、適切な値に調整されることになる。

【0035】

なお、このアニール処理でも、絶縁膜16は結晶化する。そのため、上記した絶縁膜16形成直後のアニールを省略することも出来る。ただし、絶縁膜16を結晶化していれば

、Al含有膜17のパターニング時、つまり希フッ化水素酸等によるNMOS側部分の除去時に絶縁膜16に対して選択比を高くすることが出来る。従って、絶縁膜16形成直後にもアニールを行うようにしておくことが、望ましい。

【0036】

アニール処理後には、図4Dに示したように、絶縁膜16及び16a上に、界面膜18として、数原子層程度の厚さのAl膜がALD法等により形成される。次いで、界面膜18のNMOS側の部分のみを覆う形状のレジストパターン31が形成される。そして、レジストパターン31をマスクとして界面膜18のNMOS側の部分が希フッ化水素等により除去されてから、レジストパターン31が除去される(図4E)。

【0037】

その後、図4Fに示してあるように、金属ゲート膜(以下、MG膜と表記する)19として、例えば10nm程度の厚さのTiN膜が、スパッタ法等により形成される。さらに、50nm程度の厚さのポリシリコン膜20が、例えば熱CVD法により形成される。

【0038】

そして、酸化シリコン膜15からポリシリコン膜20までの部分を、図4Hに示すようなゲート形状に加工するゲートパターニングが行われる。

【0039】

このゲートパターニングは、例えば、以下の手順で行われる。まず、図4Gに示したように、ポリシリコン膜20上に、50nm程度の厚さのSiN(窒化シリコン)膜33と、70nm程度の厚さのBARC(bottom anti-reflection coating)膜34とが、順次、形成される。その後、ArFエキシマ・レーザ用のレジストを用いて、BARC膜34上に、240nm程度の厚さの、目的とするゲート形状に応じた形状(各部のサイズが目的とするサイズより大きな形状)を有するレジストパターン35が形成される。

【0040】

次いで、各種ガスを用いた反応性イオンエッチングにより、レジストパターン35をマスクとしてBARC膜34をエッチングし、レジストパターン35とパターン化されたBARC膜34とを所望サイズとなるようにトリミングし、トリミングしたレジストパターン35等をマスクとしてSiN膜33をパターン化する処理が、行われる。

【0041】

その後、パターン化したSiN膜33をマスクとしてポリシリコン膜20以下の膜が、例えばCl2/CH4ガスを用いて除去される。そして、SiN膜33がフッ化水素酸等により除去されて(図4H)、ゲートパターニングが完了する。

【0042】

続いて、ポリシリコン膜20等をマスクとして、NMOS側に、ポケットイオン、エクステンションイオンが注入される。NMOS側へのポケットイオン、エクステンションイオンとしては、それぞれ、In等のp型不純物イオン、As等のn型不純物イオンが注入される。後の工程にある活性化アニールはミリ秒アニールプロセスを使用するため、エクステンションとゲートのオーバーラップを考慮してチルト角注入(0−45°でチューニング)を対称的な4方向から行う。

【0043】

ポリシリコン膜20等をマスクとして、PMOS側に、ポケットイオン、エクステンションイオンを注入する処理も行われる。なお、この際に注入されるポケットイオン、エクステンションイオンは、それぞれ、n型不純物(例えば、Sb)イオン、p型不純物(例えば、Ge及びB)イオンであり、NMOSと同様にチルト注入で行う。

【0044】

その後、注入した各イオンを、Al膜18中のAlを拡散させることなく活性化するために、ミリ秒アニールが行われる。ここで、ミリ秒アニールとは、レーザーやフラッシュランプにより、ミリ秒単位の加熱を行うプロセスのことである。

【0045】

なお、ミリ秒アニールを行えば、Al膜18中のAlを拡散させることなく注入イオン

を活性化できる。ただし、ミリ秒アニールを行った場合、注入イオンも殆ど拡散しないことになる。そのため、本製造方法は、上記した各イオンの注入を、ハロゲンランプ等による活性化アニールが行われる場合とは異なる、ミリ秒アニール後の不純物プロファイルが所望のものとなるように決定した角度で、行うものとなっている。

【0046】

ミリ秒アニール後には、図4Jに示したように、サイドウォール22用のSi酸化膜を全面に堆積し、このSi酸化膜の全面を異方性エッチングすることにより、Si酸化膜を各ゲート電極の側面にのみ残してサイドウォール22が形成される。

【0047】

サイドウォール22の形成後には、歪を発生させることによりPMOSトランジスタのチャネル領域のホールの移動度を上げるためのストレッサ膜25が、形成される。このストレッサ膜25は、例えば、公知の手法/手順により、PMOS側の各活性領域(ソース/ドレイン領域)をリセスした後、リセスした部分に、例えば、450℃〜500℃程度の減圧熱CVDでSiより格子定数の大きい物質、例えばB添加Si−Ge等を選択成長させることにより、形成される。

【0048】

さらに、サイドウォール22の形成後には、サイドウォール22をマスクとしてNMOSトランジスタの各活性領域にn型不純物(例えば、AsやP)イオンを注入する処理や、注入イオンを活性化するためのミリ秒アニールも行われる。このミリ秒アニール処理によって、不純物をほとんど拡散させずにRTAでは得られなかった高い活性化率で不純物を活性化し、イオン注入に生じた結晶のダメージ回復もできると考えられる。

【0049】

その後、本実施形態に係る製造方法では、半導体基板10上の各所に、CoSi2、NiSi等のシリサイド膜26を形成するためのシリサイドプロセスが行われる。そして、図4Kに示した構成を有する半導体装置が製造される。すなわち、絶縁膜16とMG膜19との間に薄い界面膜18を挿入することによって仕事関数値を調整したゲート電極1n、及び、ソースドレイン電極2nを有するNMOSトランジスタと、Alの拡散により仕事関数値を調整したゲート電極1p、及び、ソースドレイン電極2pを有するNMOSトランジスタとを備えた半導体装置が製造される。

【0050】

以上、説明したように、本実施形態に係る製造方法は、注入イオンの活性化が、サーマルバジェットの少ないミリ秒アニールで行われるものとなっている。そのため、この製造方法によれば、“MG膜19/界面膜18/絶縁膜16”構造を有するPMOS側のゲート電極1pを備えた半導体装置を確実に製造できることになる。

【0051】

そして、そのような構造を有するゲート電極1pは、図2を用いて説明したように、デュアルHigh-kプロセスにより製造されるPMOS側のゲート電極と同性能のものとなる。従って、本実施形態に係る製造方法によれば、デュアルHigh-kプロセスにより製造される半導体装置と同性能の半導体装置を、より容易に製造できることになる。

【0052】

また、本実施形態に係る製造方法により製造される半導体装置は、NMOS側のゲート電極の仕事関数値制御、PMOS側のゲート電極の仕事関数値制御の双方に、Alが利用されたものとなっている。従って、本実施形態に係る製造方法は、半導体装置の製造に必要とされる物質数が少ない分、安価に、半導体装置を製造できる方法となっていることにもなる。

【0053】

《第2実施形態》

以下、図5A〜図5Fを用いて、第2実施形態に係る製造方法(半導体装置の製造方法)の内容を、第1実施形態に係る製造方法と異なる部分を中心に、説明する。なお、本実施形態及び後述する第3、第4実施形態に係る各製造方法により製造される半導体装置は

、第1実施形態に係る半導体装置と同じ基本構成(図3)を有するものである。

【0054】

第2実施形態に係る製造方法では、図5Aに示してあるように、まず、Nウェル11、Pウェル13及び素子分離領域12が形成されている半導体基板10上に、1nm程度の厚さの酸化シリコン膜15が、例えば半導体基板10の熱酸化により形成される。

【0055】

次いで、絶縁膜16(図4A、図5B参照)ではなく、0.5nm程度の厚さのAl含有膜17(Al酸化物膜等)が、CVD法、スパッタ法等により形成される。

【0056】

Al含有膜17の形成後には、Al含有膜17のPMOS側の部分のみを覆う形状のレジストパターン30が形成される。その後、レジストパターン30をマスクとして、Al含有膜17のNMOS側の部分が、希フッ化水素酸、希塩酸等により除去される。

【0057】

そして、不要となったレジストパターン30が除去されてから、図5Bに示してあるように、2nm程度の厚さのハフニウム系酸化物膜が、絶縁膜16として、MOCVD法やALD法により形成される。

【0058】

その後、絶縁膜16を結晶化させると共に、Al含有膜17中のAlを絶縁膜16及び酸化シリコン膜15中に拡散させるためのアニール処理が、行われる。このアニール処理としては、第1実施形態と同様に、半導体基板10を、1050℃程度の不活性ガス(例えば、N2)雰囲気中で5秒間程度アニールする処理が、行われる。

【0059】

アニール処理が行われると、Al含有膜17中のAlが絶縁膜16側へ拡散し、絶縁膜16のPMOS側の部分が、形成時とは組成の異なる絶縁膜16a(図5C)に変わることになる。また、酸化シリコン膜15側にAlが拡散することにより、酸化シリコン膜15・絶縁膜16間の界面部分にHf−O−Al結合が生成され、その結果として、製造中の半導体装置のPMOS側のゲート電極の仕事関数値が、適切な値に調整されることになる。

【0060】

絶縁膜16及び絶縁膜16a上には、図5Dに示したように、数原子層程度の厚さの界面膜18がALD法等により形成される。次いで、界面膜18のNMOS側の部分のみを覆う形状のレジストパターン31が形成される。そして、レジストパターン31をマスクとして界面膜18のNMOS側の部分が希フッ化水素等により除去されてから、レジストパターン31が除去される(図5E)。

【0061】

その後、図5Fに示したように、絶縁膜16a及び界面膜18上に、MG膜(金属ゲート膜)19として、例えば、10nm程度の厚さのTiN膜がスパッタ法等により形成される。さらに、50nm程度の厚さのポリシリコン膜20が、例えば熱CVD法により形成される。

【0062】

この後、本実施形態に係る製造方法では、図4H〜図4Kを用いて説明したものと同内容のプロセスが行われる。そして、図4Kに示したものと本質的には同構成の半導体装置が製造される。

【0063】

以上の説明から明らかなように、本実施形態に係る製造方法は、酸化シリコン膜15及び絶縁膜16へのAlの供給源として機能するAl含有膜17の形成位置のみが、第1実施形態に係る製造方法と異なったものとなっている。従って、この製造方法によっても、デュアルHigh-kプロセスにより製造される半導体装置と同性能の半導体装置を、より容易かつ安価に、製造できることになる。

【0064】

《第3実施形態》

以下、図6A〜図6Jを用いて、第3実施形態に係る製造方法(半導体装置の製造方法)の内容を説明する。

【0065】

本実施形態に係る製造方法による半導体装置の製造時には、まず、第1実施形態に係る製造方法と同じ手順で、半導体基板10上に、図6Aに示した構造、つまり、図4Bに示したものと同じ構造が形成される。次いで、上記したものと同内容のアニール処理が、行われる。

【0066】

その後、第3実施形態に係る製造方法では、図6Bに示したように、界面膜18やMG膜19ではなく、60nm程度の厚さのポリシリコン膜27が、例えばCVD法により形成される。

【0067】

その後、ポリシリコン膜27を形成した半導体基板10に対して、図4G〜図4Kを用いて説明したものと同内容のプロセス、又は、当該プロセス中のミリ秒アニールをハロゲンランプアニール等に変えたプロセスが、行われる。

【0068】

そして、その結果として、半導体基板10上/内に、図6Cに示した構造が形成される。すなわち、ゲート電極1p(図4K参照)に相当する部分が、酸化シリコン膜15、絶縁膜16a、ポリシリコン膜20の積層体となっていること、及び、ゲート電極1nに相当する部分が、酸化シリコン膜15、絶縁膜16、ポリシリコン膜20の積層体となっていることを除けば、図4Kに示したものと同じ構造が、半導体基板10上/内に形成される。

【0069】

この後、本実施形態に係る製造方法では、図6Dに示したように、60nm程度の厚さの層間絶縁膜28が形成される。この層間絶縁膜28としては、例えば酸化シリコン膜が、CVD等により形成される。

【0070】

次いで、CMP(Chemical and Mechanical Polishing)法により、層間絶縁膜28が、

ポリシリコン膜20の上面が露出するまで研磨される。そして、図6Eに示したように、ポリシリコン膜20が、例えばTMAH(テトラメチルアンモニウムハイドロオキサイド)を用いて除去される。

【0071】

ポリシリコン膜20の除去後には、図6Fに示したように、半導体基板10の全面(層間絶縁膜28上、サイドウォール22等によって形成されている凹部内)に、数原子層程度の厚さのAl膜である界面膜18が、ALD法等により形成される。そして、レジストパターンの形成を含む一連の処理により、界面膜18のPMOS側の部分のみが希フッ化水素等により除去される(図6G)。

【0072】

その後、図6Hに示したように、MG膜19として、例えば、10nm程度の厚さのTiN膜がスパッタ法等により形成される。次いで、半導体基板10の全面に、サイドウォール22等によって形成されている凹部を完全に埋める厚さのTiAl膜29が、下層側の方がTiリッチとなるように膜を積層する形で、蒸着法、スパッタ法等により形成される。

【0073】

その後、TiAl膜29等が、CMP法により、層間絶縁膜28が露出するまで研磨される。そして、図6Jに示したように、絶縁膜16とMG膜19との間に薄い界面膜18を挿入することによって仕事関数値を調整したゲート電極1n、及び、ソースドレイン電極2nを有するNMOSトランジスタと、Alの拡散により仕事関数値を調整したゲート電極1p、及び、ソースドレイン電極2pを有するNMOSトランジスタとを備えた半導

体装置が製造される。

【0074】

以上、説明したように、本実施形態に係る製造方法は、半導体基板10に注入したイオンを活性化した後に、界面膜18を形成するものとなっている。従って、この製造方法によっても、“MG膜19/界面膜18/絶縁膜16”構造を有するPMOS側のゲート電極1pを備えた半導体装置を製造できる。そして、その結果として、本実施形態に係る製造方法によれば、High-kゲート絶縁膜が用いられた半導体装置を製造できることになる。

【0075】

《第4実施形態》

以下、第4実施形態に係る製造方法(半導体装置の製造方法)の内容を、第3実施形態に係る製造方法と異なる部分を中心に、説明する。

【0076】

第4実施形態に係る製造方法では、まず、第2実施形態に係る製造方法と同じ手順で、半導体基板10上に、図7Aに示した構造、つまり図5Bに示したものと同じ構造が形成される。

【0077】

そして、絶縁膜16を結晶化させると共に、Al含有膜17中のAlを絶縁膜16及び酸化シリコン膜15中に拡散させるためのアニール処理が行われてから、図7Bに示したように、酸化シリコン等からなる、60nm程度の厚さの層間絶縁膜28が形成される。

【0078】

この後、第4実施形態に係る製造方法では、第3実施形態に係る製造方法と同内容のプロセス(図6B〜図6J参照)が行われる。そして、図6Jに示したものと本質的には同構成の半導体装置が製造される。

【0079】

以上の説明から明らかなように、本実施形態に係る製造方法は、酸化シリコン膜15及び絶縁膜16へのAlの供給源として機能するAl膜18の形成位置のみが、第3実施形態に係る製造方法と異なったものとなっている。従って、この製造方法によってもHigh-kゲート絶縁膜が用いられた半導体装置を製造できることになる。

【0080】

《第5実施形態》

まず、図8を用いて、第5実施形態に係る製造方法(半導体装置の製造方法)により製造される半導体装置(以下、第5実施形態に係る半導体装置と表記する)の基本構成を説明する。

【0081】

図8に示してあるように、第5実施形態に係る半導体装置は、ゲート電極1p及びソースドレイン電極2pを有するPMOSトランジスタと、ゲート電極1n及びソースドレイン電極2nを有するNMOSトランジスタとが、半導体基板10上の素子分離領域12によって区画された領域に形成されている装置である。そして、第5実施形態に係る半導体装置は、各MOSトランジスタのゲート電極として、絶縁膜16上に直接MG膜19a(詳細は後述)が形成されているゲート電極1pと、絶縁膜16上に、Al膜である界面膜18を介してMG膜19aが形成されているゲート電極1nとを、備えたものとなっている。

【0082】

次に、本実施形態に係る製造方法を説明する。

【0083】

上記構成を有する半導体装置を製造するために、本実施形態に係る製造方法では、まず、図9Aに示してあるように、半導体基板10上に、酸化シリコン膜15、絶縁膜16、MG膜19aが、順次、形成される。

【0084】

この際、酸化シリコン膜15としては、1nm程度の厚さのものが、例えば半導体基板

10の熱酸化によって形成される。また、絶縁膜16としては、2nm程度の厚さのハフニウム系酸化物膜が、MOCVD法やALD法により形成される。そして、MG膜19aとしては、仕事関数値の調整を行わなくてもPMOSトランジスタ用のゲート電極を実現できる材料(例えば、TiN)からなる、10nm程度の厚さの膜が、形成される。

【0085】

その後、図9Bに示したように、MG膜19aのPMOS側の部分のみを覆う形状のレジストパターン40が、形成される。そして、レジストパターン40をマスクとして、MG膜19aのNMOS側の部分のみに、Alイオンが注入される。このイオン注入は、MG膜19a・絶縁膜16界面に到達し得る加速エネルギー、例えばMG膜19の厚さが10nmである場合は、30kV〜40kVで、ドーズ量が2x1017/cm2程度となるよ

うに、行われる。

【0086】

Alイオンの注入後には、レジストパターン40が除去される。次いで、レジストパターン40除去後の半導体基板10を、Alの融点よりも少なくとも100℃低い温度、例えば360℃〜560℃の不活性ガス(例えば、N2)中で、2分〜10分程度、アニールする回復アニール処理が行われる。

【0087】

Alは、MG膜19a(TiN膜等)内に存在する場合よりも、酸素と結合している場合の方がエネルギー的に安定となる物質である。そのため、上記内容の回復アニール処理が行われると、図9Cに示したように、MG膜19a・絶縁膜16界面のNMOS側の部分に、数原子層分の界面膜18(Al膜)が形成されることになる。

【0088】

この後、本実施形態に係る製造方法では、図3F〜図3Kを用いて説明したものと同内容のプロセスが行われる。そして、その基本構成が図8に示したものとなっている半導体装置が製造される。

【0089】

以上の説明から明らかなように、この第5実施形態に係る製造方法は、いわば、デュアルメタルプロセスにより製造される半導体装置(図12参照)相当のものを、NMOSトランジスタ側とPMOSトランジスタ側とに別材料で金属ゲート膜を形成する必要がない形で製造できるものとなっている。

【0090】

従って、本実施形態に係る製造方法によれば、デュアルメタルプロセスにより製造される半導体装置と同性能の半導体装置を、金属ゲート膜の作り分けが不要な形で製造できることになる。

【0091】

《第6実施形態》

図10に、第6実施形態に係る製造方法(半導体装置の製造方法)により製造される半導体装置(以下、第6実施形態に係る半導体装置と表記する)の基本構成を示す。

【0092】

この図10から明らかなように、第6実施形態に係る半導体装置は、絶縁膜16上にMG膜19bが積層されているゲート電極1nを有するNMOSトランジスタと、絶縁膜16とMG膜19bとの間に界面膜18aが挿入されているゲート電極1pを有するPMOSトランジスタを備えた半導体装置である。

【0093】

この半導体装置の各ゲート電極1p、1n内のMG膜19bは、ハフニウム系酸化物を用いた絶縁膜16上に形成すると、仕事関数値の調整を行わなくてもNMOSトランジスタ用のゲート電極を実現できる材料、例えば、TiCやTaCからなる、10nm程度の厚さの膜である。また、ゲート電極1p内にのみ含まれる界面膜18aは、5eV程度の仕事関数値を有する材料、例えば、Ptからなる、数原子層程度の厚さの膜である。

【0094】

そして、第6実施形態に係る製造方法は、上記構成を有する半導体装置を以下の手順で製造するものとなっている。

【0095】

本実施形態に係る製造方法による半導体装置の製造時には、図11Aに示してあるように、半導体基板10上に、1nm程度の厚さの酸化シリコン膜15、絶縁膜16、MG膜19bが、順次、形成されてから、MG膜19bのPMOS側の部分のみを覆う形状のレジストパターン41が、形成される。

【0096】

その後、レジストパターン41をマスクとして、MG膜19bのPMOS側の部分のみに、例えば、Ptイオンが注入される。このイオン注入は、MG膜19b・絶縁膜16界面に到達し得る加速エネルギーで、ドーズ量が2x1017/cm2程度となるように、行わ

れる。

【0097】

Ptイオンの注入後には、レジストパターン41が除去される。その後、Ptを、MG膜19b・絶縁膜16界面に偏析させるための回復アニール処理が行われて、図12Bに示したように、MG膜19b・絶縁膜16界面のPMOS側の部分に、Ptからなる薄い界面膜18aが形成される。

【0098】

この後、本実施形態に係る製造方法では、図3F〜図3Kを用いて説明したものと同内容のプロセスが行われる。そして、その基本構成が図10に示したものとなっている半導体装置が製造される。

【0099】

以上の説明から明らかなように、この第5実施形態に係る製造方法も、いわば、デュアルメタルプロセスにより製造される半導体装置(図12参照)相当のものを、2種の金属ゲート膜を作り分けが不要な形で製造できるものとなっている。

【0100】

従って、本実施形態に係る製造方法によっても、デュアルメタルプロセスにより製造される半導体装置と同性能の半導体装置を、金属ゲート膜を作り分けが不要な形製造できることになる。

【0101】

《変形形態》

上記した各実施形態に係る製造方法は、各種の変形を行うことが出来る。例えば、第1〜第4実施形態に係る製造方法を、Alイオンの打ち込みと回復アニール処理により界面膜18を形成する方法に変形することが出来る。第3、第4実施形態に係る製造方法を、絶縁膜16の形成後(図5B)のアニール、Al含有膜17のエッチング後(図6A)のアニールが行われない方法、つまり注入イオンの活性化時にAlを拡散させる方法に変形することも出来る。第5、第6実施形態に係る製造方法を、いわゆるゲートラストプロセスが採用されているものに変形することも出来る。

【0102】

また、各実施形態に係る製造方法を、界面膜18、18a、18bと直接関係しない部分の構成が上記したものとは異なる半導体装置、例えばSOS(silicon on sapphire)

基板が用いられた半導体装置、ストレッサ膜26を備えない半導体装置、ゲート電極1nのポリシリコン膜20にAsイオン等が打ち込まれている半導体装置等を製造するものに変形しても良いことは当然のことである。

【0103】

以上、開示した技術に関し、更に以下の付記を開示する。

【0104】

(付記1) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記NMSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

を有する半導体装置の製造方法。

【0105】

(付記2) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Si酸化物を含む第1絶縁膜を形成する工程と、

前記第1絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にHf酸化物を含む第2絶縁膜を形成する工程と、

前記第2絶縁膜上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

を有する半導体装置の製造方法。

【0106】

(付記3) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にSi層を形成する工程と、

前記Si層をパターニングして、前記PMOSトランジスタ形成領域に第1パターン電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2パターン電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1パターン電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2パターン電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記第1ソースドレイン電極および前記第2ソースドレイン電極を形成する工程の後、前記第1パターン電極、前記第2パターン電極、第1ソースドレインおよび電極第2ソースドレイン電極上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を研磨し、前記第1パターン電極及び前記第2パターン電極の上面を露出させる工程と、

前記層間絶縁膜の研磨の後、前記第1パターン電極及び前記第2パターン電極の上面を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上およびNMOSトランジスタ形成領域上に金属膜を形成する工程と

を有する半導体装置の製造方法。

【0107】

(付記4) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Si酸化物を含む第1絶縁膜を形成する工程と、

前記第1絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上にHf酸化物を含む第2絶縁膜を形成する工程と、

前記第2絶縁膜上にSi層を形成する工程と、

前記Si層をパターニングして、前記PMOSトランジスタ形成領域に第1パターン電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2パターン電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1パターン電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2パターン電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記第1ソースドレイン電極および前記第2ソースドレイン電極を形成する工程の後、前記第1パターン電極、前記第2パターン電極、第1ソースドレインおよび電極第2ソースドレイン電極上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を研磨し、前記第1パターン電極及び第2パターン電極の上面を露出させる工程と、

前記層間絶縁膜の研磨の後、前記第1パターン電極及び第2パターン電極の上面を除去する工程と、

前記第1パターン電極および前記第2パターン電極を除去する工程の後、PMOSトランジスタ形成領域上およびNMOSトランジスタ形成領域上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する

工程と、

を有する半導体装置の製造方法。

【0108】

(付記5) 前記金属層はTiN層であることを特徴とする、付記1乃至付記4のいずれか1項に記載の半導体装置の製造方法。

【0109】

(付記6) 前記PMOSトランジスタ形成領域上のAl含有膜を第1マスク層で覆い、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記Al膜を形成する工程の前に、熱処理により、前記PMOSトランジスタ形成領域上の前記Al含有膜のAlを前記絶縁膜中に拡散させることを特徴とする、付記1又は付記3に記載の半導体装置の製造方法。

【0110】

(付記7) 前記第2絶縁膜を形成する工程の後、前記Al膜を形成する工程の前に、

熱処理により、前記PMOSトランジスタ形成領域上の前記Al含有膜のAlを前記第1絶縁膜中に拡散させることを特徴とする、付記2又は付記4に記載の半導体装置の製造方法。

【0111】

(付記8) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記金属膜を形成する工程と前記金属膜をパターニングする工程との間に行われる、前記金属膜上の前記NMOSトランジスタ形成領域上の部分に、前記金属膜と前記絶縁膜との界面に偏析させることにより前記第1ゲート電極の仕事関数値を調整するためのイオンを打ち込む工程と、

を有する半導体装置の製造方法。

【0112】

(付記9) 半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記金属膜を形成する工程と前記金属膜をパターニングする工程との間に行われる、前記金属膜上の前記PMOSトランジスタ形成領域上の部分に、前記金属膜と前記絶縁膜との界面に偏析させることにより前記第2ゲート電極の仕事関数値を調整するためのイオンを打ち込む工程と、

を有する半導体装置の製造方法。

【0113】

(付記10) 半導体基板上にPMOSトランジスタとNMOSトランジスタとが形成

されている半導体装置であって、

前記PMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に金属ゲート膜が設けられているゲート電極を有し、

前記NMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上にAl膜を介して金属ゲート膜が設けられているゲート電極を有する

ことを特徴とする半導体装置。

【0114】

(付記11) 熱処理により、仕事関数値を調整するために打ち込まれた前記イオンを前記金属膜と前記絶縁膜との界面に偏析させる工程をさらに含むことを特徴とする、付記8又は付記9に記載の半導体装置の製造方法。

【0115】

(付記12) 前記第1不純物注入及び前記第2不純物注入により注入された不純物を活性化するための活性化アニールとして、ミリ秒アニールを行うことを特徴とする、付記1又は付記2に記載の半導体装置の製造方法。

【0116】

(付記13) 半導体基板上にPMOSトランジスタとNMOSトランジスタとが形成されている半導体装置であって、

前記PMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に界面膜を介して金属ゲート膜が設けられているゲート電極を有し、

前記NMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に金属ゲート膜が設けられているゲート電極を有し、

その仕事関数値が、前記界面膜を設けずに形成した前記PMOSトランジスタのゲート電極の仕事関数値よりも小さい材料により、前記界面膜が形成されている

ことを特徴とする半導体装置。

【0117】

(付記14) 半導体基板上にPMOSトランジスタとNMOSトランジスタとが形成されている半導体装置であって、

前記PMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に金属ゲート膜が設けられているゲート電極を有し、

前記NMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に界面膜を介して金属ゲート膜が設けられているゲート電極を有し、

その仕事関数値が、前記界面膜を設けずに形成した前記NMOSトランジスタのゲート電極の仕事関数値よりも小さい材料により、前記界面膜が形成されている

ことを特徴とする半導体装置。

【符号の説明】

【0118】

1p、1n ゲート電極

2p、2n ソースドレイン電極

10 半導体基板

11 Nウェル

12 素子分離領域

13 Pウェル

15 酸化シリコン膜

16、16a 絶縁膜

17 Al含有膜

18 界面膜

19、19a、19b 金属ゲート膜(MG膜)

20、27 ポリシリコン膜

22 サイドウォール

25 ストレッサ膜

26 シリサイド膜

28 層間絶縁膜

29 TiAl膜

【特許請求の範囲】

【請求項1】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記NMSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

を有する半導体装置の製造方法。

【請求項2】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Si酸化物を含む第1絶縁膜を形成する工程と、

前記第1絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にHf酸化物を含む第2絶縁膜を形成する工程と、

前記第2絶縁膜上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

を有する半導体装置の製造方法。

【請求項3】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にSi層を形成する工程と、

前記Si層をパターニングして、前記PMOSトランジスタ形成領域に第1パターン電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2パターン電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1パターン電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2パターン電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記第1ソースドレイン電極および前記第2ソースドレイン電極を形成する工程の後、前記第1パターン電極、前記第2パターン電極、第1ソースドレインおよび電極第2ソースドレイン電極上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を研磨し、前記第1パターン電極及び前記第2パターン電極の上面を露出させる工程と、

前記層間絶縁膜の研磨の後、前記第1パターン電極及び前記第2パターン電極の上面を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上およびNMOSトランジスタ形成領域上に金属膜を形成する工程と

を有する半導体装置の製造方法。

【請求項4】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Si酸化物を含む第1絶縁膜を形成する工程と、

前記第1絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上にHf酸化物を含む第2絶縁膜を形成する工程と、

前記第2絶縁膜上にSi層を形成する工程と、

前記Si層をパターニングして、前記PMOSトランジスタ形成領域に第1パターン電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2パターン電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1パターン電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2パターン電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記第1ソースドレイン電極および前記第2ソースドレイン電極を形成する工程の後、前記第1パターン電極、前記第2パターン電極、第1ソースドレインおよび電極第2ソースドレイン電極上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を研磨し、前記第1パターン電極及び第2パターン電極の上面を露出させる工程と、

前記層間絶縁膜の研磨の後、前記第1パターン電極及び第2パターン電極の上面を除去する工程と、

前記第1パターン電極および前記第2パターン電極を除去する工程の後、PMOSトラ

ンジスタ形成領域上およびNMOSトランジスタ形成領域上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、

を有する半導体装置の製造方法。

【請求項5】

前記金属層はTiN層であることを特徴とする、請求項1乃至請求項4のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記PMOSトランジスタ形成領域上のAl含有膜を第1マスク層で覆い、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記Al膜を形成する工程の前に、熱処理により、前記PMOSトランジスタ形成領域上の前記Al含有膜のAlを前記絶縁膜中に拡散させることを特徴とする、請求項1又は請求項3に記載の半導体装置の製造方法。

【請求項7】

前記第2絶縁膜を形成する工程の後、前記Al膜を形成する工程の前に、

熱処理により、前記PMOSトランジスタ形成領域上の前記Al含有膜のAlを前記第1絶縁膜中に拡散させることを特徴とする、請求項2又は請求項4に記載の半導体装置の製造方法。

【請求項8】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記金属膜を形成する工程と前記金属膜をパターニングする工程との間に行われる、前記金属膜上の前記NMOSトランジスタ形成領域上の部分に、前記金属膜と前記絶縁膜との界面に偏析させることにより前記第1ゲート電極の仕事関数値を調整するためのイオンを打ち込む工程と、

を有する半導体装置の製造方法。

【請求項9】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記金属膜を形成する工程と前記金属膜をパターニングする工程との間に行われる、前記金属膜上の前記PMOSトランジスタ形成領域上の部分に、前記金属膜と前記絶縁膜と

の界面に偏析させることにより前記第2ゲート電極の仕事関数値を調整するためのイオンを打ち込む工程と、

を有する半導体装置の製造方法。

【請求項10】

半導体基板上にPMOSトランジスタとNMOSトランジスタとが形成されている半導体装置であって、

前記PMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に金属ゲート膜が設けられているゲート電極を有し、

前記NMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上にAl膜を介して金属ゲート膜が設けられているゲート電極を有する

ことを特徴とする半導体装置。

【請求項1】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記NMSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

を有する半導体装置の製造方法。

【請求項2】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Si酸化物を含む第1絶縁膜を形成する工程と、

前記第1絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にHf酸化物を含む第2絶縁膜を形成する工程と、

前記第2絶縁膜上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

を有する半導体装置の製造方法。

【請求項3】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上及び前記NMOSトランジスタ形成領域上にSi層を形成する工程と、

前記Si層をパターニングして、前記PMOSトランジスタ形成領域に第1パターン電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2パターン電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1パターン電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2パターン電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記第1ソースドレイン電極および前記第2ソースドレイン電極を形成する工程の後、前記第1パターン電極、前記第2パターン電極、第1ソースドレインおよび電極第2ソースドレイン電極上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を研磨し、前記第1パターン電極及び前記第2パターン電極の上面を露出させる工程と、

前記層間絶縁膜の研磨の後、前記第1パターン電極及び前記第2パターン電極の上面を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上およびNMOSトランジスタ形成領域上に金属膜を形成する工程と

を有する半導体装置の製造方法。

【請求項4】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Si酸化物を含む第1絶縁膜を形成する工程と、

前記第1絶縁膜上にAl含有膜を形成する工程と、

前記PMOSトランジスタ形成領域上の前記Al含有膜を第1マスク層で覆い、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程と、

前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上にHf酸化物を含む第2絶縁膜を形成する工程と、

前記第2絶縁膜上にSi層を形成する工程と、

前記Si層をパターニングして、前記PMOSトランジスタ形成領域に第1パターン電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2パターン電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1パターン電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2パターン電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記第1ソースドレイン電極および前記第2ソースドレイン電極を形成する工程の後、前記第1パターン電極、前記第2パターン電極、第1ソースドレインおよび電極第2ソースドレイン電極上に層間絶縁膜を形成する工程と、

前記層間絶縁膜を研磨し、前記第1パターン電極及び第2パターン電極の上面を露出させる工程と、

前記層間絶縁膜の研磨の後、前記第1パターン電極及び第2パターン電極の上面を除去する工程と、

前記第1パターン電極および前記第2パターン電極を除去する工程の後、PMOSトラ

ンジスタ形成領域上およびNMOSトランジスタ形成領域上にAl膜を形成する工程と、

前記NMOSトランジスタ形成領域上の前記Al膜を第2マスク層で覆い、前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程と、

前記PMOSトランジスタ形成領域上の前記Al膜を除去する工程の後、前記PMOSトランジスタ形成領域上および前記NMOSトランジスタ形成領域上に金属膜を形成する工程と、

を有する半導体装置の製造方法。

【請求項5】

前記金属層はTiN層であることを特徴とする、請求項1乃至請求項4のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記PMOSトランジスタ形成領域上のAl含有膜を第1マスク層で覆い、前記NMOSトランジスタ形成領域上の前記Al含有膜を除去する工程の後、前記Al膜を形成する工程の前に、熱処理により、前記PMOSトランジスタ形成領域上の前記Al含有膜のAlを前記絶縁膜中に拡散させることを特徴とする、請求項1又は請求項3に記載の半導体装置の製造方法。

【請求項7】

前記第2絶縁膜を形成する工程の後、前記Al膜を形成する工程の前に、

熱処理により、前記PMOSトランジスタ形成領域上の前記Al含有膜のAlを前記第1絶縁膜中に拡散させることを特徴とする、請求項2又は請求項4に記載の半導体装置の製造方法。

【請求項8】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記金属膜を形成する工程と前記金属膜をパターニングする工程との間に行われる、前記金属膜上の前記NMOSトランジスタ形成領域上の部分に、前記金属膜と前記絶縁膜との界面に偏析させることにより前記第1ゲート電極の仕事関数値を調整するためのイオンを打ち込む工程と、

を有する半導体装置の製造方法。

【請求項9】

半導体基板のPMOSトランジスタ形成領域およびNMOSトランジスタ形成領域上に、Hf酸化物を含む絶縁膜を形成する工程と、

前記絶縁膜上に金属膜を形成する工程と、

前記金属膜をパターニングして、前記PMOSトランジスタ形成領域にPMOSトランジスタの第1ゲート電極を形成し、前記NMOSトランジスタ形成領域にNMOSトランジスタの第2ゲート電極を形成する工程と、

前記PMOSトランジスタ形成領域に、前記第1ゲート電極をマスクとして第1不純物注入を行い、PMOSトランジスタの第1ソースドレイン電極を形成する工程と、

前記NMOSトランジスタ形成領域に、前記第2ゲート電極をマスクとして第2不純物注入を行い、NMOSトランジスタの第2ソースドレイン電極を形成する工程と、

前記金属膜を形成する工程と前記金属膜をパターニングする工程との間に行われる、前記金属膜上の前記PMOSトランジスタ形成領域上の部分に、前記金属膜と前記絶縁膜と

の界面に偏析させることにより前記第2ゲート電極の仕事関数値を調整するためのイオンを打ち込む工程と、

を有する半導体装置の製造方法。

【請求項10】

半導体基板上にPMOSトランジスタとNMOSトランジスタとが形成されている半導体装置であって、

前記PMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上に金属ゲート膜が設けられているゲート電極を有し、

前記NMOSトランジスタが、Hf系酸化物からなるゲート絶縁膜上にAl膜を介して金属ゲート膜が設けられているゲート電極を有する

ことを特徴とする半導体装置。

【図1A】

【図1B】

【図1C】

【図1D】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図4G】

【図4H】

【図4I】

【図4J】

【図4K】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図5F】

【図6A】

【図6B】

【図6C】

【図6D】

【図6E】

【図6F】

【図6G】

【図6H】

【図6I】

【図6J】

【図7A】

【図7B】

【図8】

【図9A】

【図9B】

【図9C】

【図10】

【図11A】

【図11B】

【図12】

【図13】

【図1B】

【図1C】

【図1D】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図4G】

【図4H】

【図4I】

【図4J】

【図4K】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図5F】

【図6A】

【図6B】

【図6C】

【図6D】

【図6E】

【図6F】

【図6G】

【図6H】

【図6I】

【図6J】

【図7A】

【図7B】

【図8】

【図9A】

【図9B】

【図9C】

【図10】

【図11A】

【図11B】

【図12】

【図13】

【公開番号】特開2011−29296(P2011−29296A)

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願番号】特願2009−171752(P2009−171752)

【出願日】平成21年7月23日(2009.7.23)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願日】平成21年7月23日(2009.7.23)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]