半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を製造する。また、スループットを向上させ、製造コストを低減する。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法および半導体装置に関し、特に、Cu−Ni配線を有する半導体装置の製造方法、およびCu−Ni配線を有する半導体装置の構成に適用して有効な技術に関する。

【背景技術】

【0002】

半導体装置は、半導体基板上に形成されたMISFETなどの半導体素子と、この半導体素子の上方に形成された多層の配線を有する。そして、最上層配線上には、例えば、Cu−Ni配線よりなる再配線が形成される。この再配線の一端は、最上層配線と接続される接続部となり、再配線の他端はパッド領域となる。このように、再配線は、最上層配線の端部と半導体チップの所定の位置のパッド領域とを接続する役割を果たす。

【0003】

例えば、下記特許文献1(特開2005−38932号公報)には、再配線層を有する半導体装置が開示され、この再配線層の形成に際し、次のような(1)〜(5)に示す工程を有する半導体装置の製造技術が開示されている(特に、特許文献1の[0072]〜[0077]段落参照)。

【0004】

(1)下地金属層[6b]上に第1の感光性樹脂を塗布し、露光および現像により、主導体層[6a]形成部分を除く部分に第1の感光性レジスト[11a]を形成する[図2(d)]。第1の感光性レジスト[11a]の形成後、仮硬化を行う[図2(e)]。

【0005】

(2)第1の感光性レジスト[11a]を利用して、主導体層[6a]を形成する。具体的には、第1の感光性レジスト[11a]の開口部に、例えば、硫酸銅からなる銅メッキ液を用いて電解メッキを行うことにより、Cuからなる主導体層[6a]を形成する[図2(f)]。その後、感光性レジスト[11a]を除去する[図2(g)]。

【0006】

(3)主導体層[6a]上に、第2の感光性樹脂を塗布し、露光および現像により、金属柱[9]を形成するために露出される主導体層[6a]の一部分を除く主導体層[6a]の上面、もしくは表面のみが露出されるように、第2の感光性レジスト[11b]を形成する。その後、仮硬化を行う[図2(h)]。

【0007】

(4)そして、第2の感光性レジスト[11b]を利用して、金属層[7]を形成する。具体的には、第2の感光性レジスト[11b]の開口部に、例えば、電解メッキ法により膜厚1μm〜3μmのNi層を形成する。その後、剥離液により第2の感光性レジスト[11b]を除去する[図3(i)]。

【0008】

(5)次に、例えば、過硫酸アンモニウムを主成分とするエッチング液、および、過酸化水素水や無機アンモニアを主成分とし、望ましくは主導体層[6a]に表面保護層を一時的に形成しエッチング液から保護する役割を有する添加剤を含むエッチング液を用いて、次の処理を行う。再配線層部分以外、すなわち、金属層[7]が形成されていない部分の下地金属層[6b]およびこの部分の下に位置するバリアメタル層[5]をエッチングにより除去する[図3(j)]。なお、[カッコ]内は、特許文献1中に記載の符号または図面番号である。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2005−38932号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明者は、上記のような再配線を有する半導体装置の研究・開発に従事している。この再配線として、下層に銅膜(Cu)を、その上層にニッケル膜(Ni)を用いたCu−Ni再配線を採用し、これらの金属膜をメッキ法により形成している。

【0011】

しかしながら、追って詳細に説明するように、金属膜のメッキ法による成膜時に形成されるCuシード層のエッチングの際、Cu−Ni再配線のNi膜がエッチングされ、Ni膜の膜減りが生じるという問題が生じた。

【0012】

さらに、Ni膜の膜べりを考慮して、あらかじめNi膜を厚く形成した場合、Ni膜の応力により基板(半導体装置)に歪みが生じ、製造工程における不具合や、素子特性に与える影響が懸念されるという問題があった。

【0013】

そこで、本発明の目的は、特性の良好な半導体装置の製造方法を提供することにある。また、半導体装置の製造工程のスループットを向上させることにある。また、製造コストを低減することができる半導体装置の製造方法を提供することにある。

【0014】

また、本発明の他の目的は、特性の良好な半導体装置を提供することにある。また、製造コストを低減することができる半導体装置を提供することにある。

【0015】

本発明の上記目的およびその他の目的と新規な特徴は、本願明細書の記載および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0016】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0017】

本願において開示される発明のうち、代表的な実施の形態に示される半導体装置の製造方法は、次の(a)〜(f)の工程を有する。(a)は、基板の上方に導電性膜よりなる第1配線を形成する工程である。(b)は、上記第1配線上に、上記第1配線の第1領域を露出する第1絶縁膜を形成する工程である。(c)は、上記第1配線の上記第1領域から上記第1絶縁膜上に延在する第2配線を形成する工程である。また、この(c)工程は、(c1)上記第1領域および上記第1絶縁膜上に銅を主成分とする第1銅膜を形成する工程と、(c2)上記第1銅膜上に、上記第2配線の形成領域を開口した第1マスク膜を形成する工程と、を有する。さらに、(c3)上記第2配線の形成領域の上記第1銅膜上に、メッキ成長により銅を主成分とする第2銅膜を形成する工程と、(c4)上記第2銅膜上に、ニッケルを主成分とする第1ニッケル膜を形成する工程と、を有し、これにより、上記第1銅膜、上記第2銅膜および上記ニッケル膜よりなる上記第2配線を形成する工程である。(d)は、上記第2配線上のパッド領域に金を主成分とする金膜を形成する工程である。(e)は、上記(d)工程の後、上記第1マスク膜を除去し、上記第1ニッケル膜に不動態化処理を施すことにより、上記第1ニッケル膜の表面にニッケルの不動態化膜を形成する工程である。(f)は、上記(e)工程の後、前記第1銅膜をエッチングする工程である。

【0018】

本願において開示される発明のうち、代表的な実施の形態に示される半導体装置の製造方法は、次の(a)〜(g)の工程を有する。(a)は、基板の上方に第1導電性膜を形成する工程である。(b)は、上記第1導電性膜上に、上記第1導電性膜の第1領域を露出する第1絶縁膜を形成する工程である。(c)は、上記第1導電性膜の第1領域および上記第1絶縁膜上に位置する第2導電性膜を形成する工程である。また、この(c)工程は、(c1)上記第1領域および上記第1絶縁膜上に銅を主成分とする第1銅膜を形成する工程と、(c2)上記第1銅膜上に、上記第2導電性膜の形成領域を開口した第1マスク膜を形成する工程と、を有する。さらに、(c3)上記第2導電性膜の形成領域の上記第1銅膜上に、メッキ成長により銅を主成分とする第2銅膜を形成する工程と、(c4)上記第2銅膜上に、ニッケルを主成分とするニッケル膜を形成する工程と、を有し、これにより、上記第1銅膜、上記第2銅膜および上記ニッケル膜よりなる上記第2導電性膜を形成する工程である。(d)は、上記(c)工程の後、上記第1マスク膜を除去し、上記ニッケル膜に不動態化処理を施すことにより、上記ニッケル膜の表面にニッケルの不動態化膜を形成する工程である。(e)は、上記(d)工程の後、上記第1銅膜をエッチングする工程である。(f)は、上記第2導電性膜のパッド領域上の上記不動態化膜を除去する工程である。(g)は、上記(f)工程の後、上記パッド領域に、金を主成分とする金膜を形成する工程である。

【0019】

本願において開示される発明のうち、代表的な実施の形態に示される半導体装置は、次の(a)〜(e)の構成を有する。(a)は、基板の上方に配置された導電性膜よりなる第1配線である。(b)は、上記第1配線上に配置され、上記第1配線の第1領域を露出する開口部を有する第1絶縁膜である。(c)は、上記導電性膜の第1領域から上記第1絶縁膜上に延在する第2配線であって、(c1)銅を主成分とする銅膜と、(c2)上記銅膜上に配置され、ニッケルを主成分とする第1ニッケル膜とを有する第2配線である。(d)は、上記第2配線のパッド領域上であって、上記第1ニッケル膜上に配置された金を主成分とする金膜である。(e)は、上記第2配線の上記第1ニッケル膜上に配置されたニッケルの不動態化膜である。そして、上記第1ニッケル膜の表面に上記不動態膜と上記金膜とが形成されている。

【0020】

本願において開示される発明のうち、代表的な実施の形態に示される半導体装置は、次の(a)〜(f)の構成を有する。(a)は、基板の上方に配置された第1導電性膜である。(b)は、上記第1導電性膜上に配置され、上記第1導電性膜の第1領域を露出する開口部を有する第1絶縁膜である。(c)は、上記第1導電性膜の第1領域および上記第1絶縁膜上に配置された第2導電性膜であって、(c1)銅を主成分とする銅膜と、(c2)上記銅膜上に配置され、ニッケルを主成分とするニッケル膜とを有する上記第2導電性膜である。(d)は、上記第2導電性膜のパッド領域を開口する第2絶縁膜である。(e)は、上記第2導電性膜のパッド領域上であって、上記ニッケル膜の上方に配置されたバンプ電極である。(f)は、上記ニッケル膜と上記第2絶縁膜とに挟まれた領域に配置されたニッケルの不動態化膜である。

【発明の効果】

【0021】

本願において開示される発明のうち、以下に示す代表的な実施の形態に示される半導体装置によれば、半導体装置の特性を向上させることができる。また、半導体装置の製造コストを低減することができる。

【0022】

本願において開示される発明のうち、以下に示す代表的な実施の形態に示される半導体装置の製造方法によれば、特性の良好な半導体装置を製造することができる。また、半導体装置の製造工程において、スループットを向上させることができる。また、半導体装置の製造工程において、製造コストを低減することができる。

【図面の簡単な説明】

【0023】

【図1】実施の形態1の半導体装置の構成を示す要部断面図である。

【図2】実施の形態1の半導体装置の製造工程を示す要部断面図である。

【図3】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図2に続く工程を示す要部断面図である。

【図4】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図3に続く工程を示す要部断面図である。

【図5】実施の形態1の半導体装置の製造工程を示す要部平面図である。

【図6】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図4に続く工程を示す要部断面図である。

【図7】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図6に続く工程を示す要部断面図である。

【図8】実施の形態1の半導体装置の製造工程を示す要部平面図である。

【図9】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図7に続く工程を示す要部断面図である。

【図10】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図9に続く工程を示す要部断面図である。

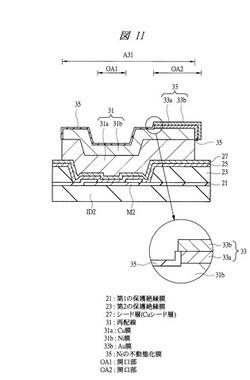

【図11】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図10に続く工程を示す要部断面図である。

【図12】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図11に続く工程を示す要部断面図である。

【図13】実施の形態2の半導体装置の構成を示す要部断面図である。

【図14】実施の形態2の半導体装置の製造工程を示す要部断面図である。

【図15】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図14に続く工程を示す要部断面図である。

【図16】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図15に続く工程を示す要部断面図である。

【図17】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図16に続く工程を示す要部断面図である。

【図18】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図17に続く工程を示す要部断面図である。

【図19】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図18に続く工程を示す要部断面図である。

【図20】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図19に続く工程を示す要部断面図である。

【図21】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図20に続く工程を示す要部断面図である。

【図22】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図21に続く工程を示す要部断面図である。

【図23】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図22に続く工程を示す要部断面図である。

【図24】実施の形態2の半導体装置の他の構成を示す要部断面図である。

【図25】実施の形態3の半導体装置の製造工程を示す要部断面図である。

【図26】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図25に続く工程を示す要部断面図である。

【図27】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図26に続く工程を示す要部断面図である。

【図28】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図27に続く工程を示す要部断面図である。

【図29】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図28に続く工程を示す要部断面図である。

【図30】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図29に続く工程を示す要部断面図である。

【発明を実施するための形態】

【0024】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、応用例、詳細説明、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

【0025】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数等(個数、数値、量、範囲等を含む)についても同様である。

【0026】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一または関連する符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0027】

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。

【0028】

(実施の形態1)

以下、図面を参照しながら本実施の形態の半導体装置の構成と製造方法について詳細に説明する。図1は、本実施の形態の半導体装置の構成を示す要部断面図である。図2〜図12は、本実施の形態の半導体装置の製造工程を示す要部断面図または要部平面図である。

【0029】

[構造説明]

まず、図1を参照しながら本実施の形態の半導体装置の特徴的な構成について説明する。

【0030】

図1に示すように、本実施の形態の半導体装置は、半導体基板(基板)1上に形成された半導体素子として、例えばpチャネル型MISFETQpおよびnチャネル型MISFETQnを有する。かかるMISFETの他、他の素子、例えば、容量素子、抵抗素子やメモリセルなど、種々の素子を有していてもよい。

【0031】

これらMISFET(Metal Insulator Semiconductor Field Effect Transistor、電界効果トランジスタ)上には、層間絶縁膜ID1が配置されている。また、上記MISFETのソース・ドレイン領域(3n、3p)上には、プラグP1を介して第1層配線M1が配置されている。さらに、第1層配線M1上には、第2層配線M2が形成されている。第1層配線M1と第2層配線M2との間は、プラグP2により電気的に接続され、プラグP2以外の領域は層間絶縁膜ID2により電気的に絶縁されている。

【0032】

第1層配線M1および第2層配線M2は、アルミニウム(Alを主成分とする導電性膜)よりなる配線である。主成分とは、少なくとも50%以上の組成比で混合されている成分をいう。

【0033】

この第2層配線(最上層配線)M2上には保護絶縁膜(21、23、絶縁膜)が形成され、保護絶縁膜の開口部(ここでは、第1の保護絶縁膜21の開口部)OA1から第2層配線(Al膜)M2が露出している。

【0034】

この露出部(開口部OA1、第1パッド領域)から保護絶縁膜(21、23)上に再配線31が配置されている。この再配線31は、上記露出部(開口部OA1、第1パッド領域)を半導体基板(半導体チップ)上の所望の領域まで引き回す役割を果たす。このように、再配線31を用い、再配線31の端部をパッド領域Pd(開口部OA2、第2パッド領域)とすることで、配線基板などの外部接続端子と半導体基板(半導体チップ)との電気的接続を容易に図ることができる。

【0035】

この再配線31は、銅膜(Cuを主成分とする導電性膜)31aと、ニッケル膜(Niを主成分とする導電性膜)31bとの積層膜(Cu−Ni配線)よりなる。Cu膜31aは、下層のシード層である銅薄膜よりメッキ成長された膜であり、Cu膜31aの下層にはシード層(図1においては図示せず。図12参照)が配置されている。また、シード層の下部には、バリア膜(図1においては図示せず。図12参照)が配置されている。なお、Ni膜31bは、上記Cu膜31a上にメッキ成長された膜である。なお、以降、シード層(シード膜)27をCuシード層27ということがある。また、このCuシード層および上記バリア膜も導電性を有するため、再配線31に含まれると考えることができる。

【0036】

また、上記再配線31の端部上には、パッドパターン33が配置されている。パッドパターン33は、ワイヤWとの接続を図るための下地層(パッド領域の下地層)であり、このパッドパターン33の表面が、パッド領域(ワイヤとの接続部、外部接続端子との接続部)Pdとなる。このパッドパターン33は、ニッケル膜(Niを主成分とする導電性膜)33aと金膜(Auを主成分とする導電性膜)33bの積層膜よりなる。

【0037】

このパッドパターン33の形成領域は、再配線31の端部領域より大きく、再配線31の端部領域の外周を含む領域である(図8参照)。よって、パッドパターン33は、再配線31の端部領域の上面のみならず、その側面を覆うように配置される(図1参照)。かかる構成により、再配線31とパッドパターン33の接触面積が大きくなり、パッドパターン33の剥がれを低減することができる。

【0038】

ここで、本実施の形態の半導体装置の特徴的な構成として、再配線31を構成するNi膜31bの表面のうち、パッドパターン33(パッド領域Pd、開口部OA2)の形成領域以外の領域に、Niの不動態化膜35が配置されている。また、パッドパターン33を構成するNi膜33aの表面のうち、Au膜33bで覆われていない領域、即ち、Ni膜33aの側面(露出領域、露出面)にも、Niの不動態化膜35が配置されている。

【0039】

Niの不動態化膜35とは、Niの酸化膜(NixOy)であり、不動態化処理により形成される膜である。不動態化処理としては、例えば、ニッケル膜と酸化性の溶液とを接触させる処理によりなされる。酸化性の溶液は、例えば、過酸化水素水を含有する溶液(処理液)であり、より具体的には、アンモニアと過酸化水素水を含有する溶液(アンモニア過水)が、ニッケルの不動態化処理液として好適に用いられる。また、ニッケル膜を酸化性雰囲気中でプラズマ処理することによってニッケル膜を不動態化することができる。

【0040】

上記Niの不動態化膜は、酸化膜であるが、Niの自然酸化膜とは異なり、緻密で安定な膜である。よって、Niの自然酸化膜は、Niの不動態化膜よりエッチングされやすく、例えば、上記アンモニア過水をエッチング液として用いてエッチングした場合、Niの自然酸化膜のエッチングレート(エッチング速度)は、Niの不動態化膜のエッチングレートの100倍以上である。即ち、Niの不動態化膜のエッチングレートは、Niの自然酸化膜のエッチングレートの100分の1以下である。また、上記Niの不動態化膜は、Niの自然酸化膜とは異なり、緻密で安定な膜であるため、硫酸や塩酸等の強い酸を用いても溶解し難い。

【0041】

このように、Niの不動態化膜35を配置することで、Ni膜31bの耐食性が高まる。また、後述の製造工程で詳細に説明するように、Cuシード層27をエッチングする際のNi膜31bの膜減りを低減することができる。よって、Ni膜31bをあらかじめ薄く形成することができ、下層の配線や素子(MISFET)等に加わる応力を低減することができる。

【0042】

また、パッドパターン33(パッド領域Pd)上には、後述する配線基板の外部接続端子との電気的接続を図るためのワイヤ(導電性部材)Wが配置されている。

【0043】

[製造方法説明]

次いで、図1〜図12を参照しながら、本実施の形態の半導体装置の製造工程を説明するとともに、当該半導体装置の構成をより明確にする。

【0044】

まず、図1に示すような半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の上方に複数の配線(M1、M2)が形成された半導体基板1を準備する。

【0045】

[Qn、Qp形成工程]

半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の形成方法に制限はないが、例えば、以下に示す工程により、これらを形成することができる(図1参照)。

【0046】

例えばp型の単結晶シリコンからなる半導体基板1をエッチングすることにより溝を形成し、溝の内部に絶縁膜として例えば酸化シリコン膜を埋め込むことにより素子分離領域2を形成する。この素子分離領域2により、nチャネル型MISFETQnが形成される活性領域およびpチャネル型MISFETQpが形成される活性領域が区画される。

【0047】

次いで、半導体基板1のnチャネル型MISFETQnが形成される活性領域にp型不純物をイオン打ち込みした後、熱処理により不純物を拡散させることにより、p型ウエルを形成する。また、半導体基板1のpチャネル型MISFETQpが形成される活性領域にn型不純物をイオン打ち込みした後、熱処理により不純物を拡散させることにより、n型ウエルを形成する。次いで、例えば、半導体基板1(p型ウエルおよびn型ウエル)の表面を熱酸化することにより、ゲート絶縁膜を形成する。

【0048】

次いで、ゲート絶縁膜上に、例えば導電性膜として、不純物をドープした多結晶シリコン膜を堆積し、さらに、その上部に、絶縁膜として例えば窒化シリコン膜を堆積する。次いで、窒化シリコン膜をエッチングした後、この窒化シリコン膜をマスクとして多結晶シリコン膜をエッチングすることにより、ゲート電極Gを形成する。このように、所望の形状の膜(マスク膜、フォトレジスト膜)をマスクとして、下層の膜を選択的に除去する工程を「パターニング」という。

【0049】

次いで、ゲート電極Gの両側のp型ウエルにn型不純物をイオン打ち込みすることによってn−型半導体領域を形成し、ゲート電極Gの両側のn型ウエルにp型不純物をイオン打ち込みすることによってp−型半導体領域を形成する。

【0050】

次いで、半導体基板1の全面上に絶縁膜として例えば窒化シリコン膜を堆積した後、異方的にエッチングすることによって、ゲート電極Gの側壁にサイドウォールスペーサを形成する。

【0051】

次いで、ゲート電極Gおよびサイドウォールスペーサをマスクにp型ウエルにn型不純物をイオン打ち込みすることによってn−型半導体領域よりも不純物濃度の高いn+型半導体領域を形成し、ゲート電極Gおよびサイドウォールスペーサをマスクにn型ウエルにp型不純物をイオン打ち込みすることによってp−型半導体領域よりも不純物濃度の高いp+型半導体領域を形成する。

【0052】

以上の工程により、n−型半導体領域およびn+型半導体領域よりなるLDD(Lightly Doped Drain)構造のソース・ドレイン領域3nを備えたnチャネル型MISFETQn、およびp−型半導体領域およびp+型半導体領域よりなるLDD構造のソース・ドレイン領域3pを備えたpチャネル型MISFETQpが形成される(図1参照)。

【0053】

[M1、M2形成工程]

複数の配線(M1、M2)の形成方法に制限はないが、例えば、以下に示す工程により、これらを形成することができる(図1参照)。

【0054】

まず、図1に示すnチャネル型MISFETQnおよびpチャネル型MISFETQp上に、絶縁膜として例えば酸化シリコン膜をCVD(Chemical Vapor deposition)法などで堆積する。その後、必要に応じて、酸化シリコン膜の表面を化学的機械研磨(CMP;Chemical Mechanical Polishing)法などで研磨してその表面を平坦化することによって層間絶縁膜ID1を形成する。

【0055】

次いで、層間絶縁膜ID1をパターニングすることにより、ソース・ドレイン領域3n、3p上に、それぞれコンタクトホール(接続孔)を形成する。次いで、コンタクトホール内を含む層間絶縁膜ID1上に、導電性膜として例えば、タングステン(W)膜をCVD法などで堆積し、このW膜を層間絶縁膜ID1が露出するまでCMP法などにより研磨することによって、コンタクトホール内に導電性膜を埋め込む。この工程により、プラグ(接続部、コンタクトプラグ)P1が形成される。なお、W膜の下層に、例えば窒化チタン(TiN)膜またはチタン(Ti)膜等よりなる単層膜又はこれらの積層膜からなるバリア膜を設けてもよい。

【0056】

次いで、プラグP1上を含む層間絶縁膜ID1上に、バリア膜(図示せず)として例えばTiN膜をスパッタリング法などにより形成する。次いで、バリア膜上に、Al膜をスパッタリング法などにより形成する。次いで、Al膜上に、反射防止膜(図示せず)としてTiN膜をスパッタリング法などにより形成する。

【0057】

次いで、バリア膜、Al膜および反射防止膜の積層膜をパターニングすることにより、第1層配線M1を形成する。なお、上記コンタクトホールを形成後、コンタクトホール内を含む層間絶縁膜ID1上に、上記積層膜を形成した後、パターニングすることにより、プラグP1と第1層配線M1を同時に形成してもよい。上記工程により、Alを主成分とする第1層配線M1が形成される。なお、TiN膜は、導電性を有するため、TiN膜/Al膜/TiN膜の積層膜を第1層配線M1として扱ってもよい。

【0058】

次いで、第1層配線M1上に、絶縁膜として例えば酸化シリコン膜をCVD法などで堆積し、その後、必要に応じて、酸化シリコン膜の表面を研磨することによって層間絶縁膜ID2を形成する。

【0059】

次いで、層間絶縁膜ID2をエッチングすることにより、第1層配線M1上にコンタクトホールを形成する。次いで、プラグP1と同様に、コンタクトホール内に導電性膜を埋め込むことにより、プラグP2を形成する。

【0060】

次いで、プラグP2上を含む層間絶縁膜ID2上に、第1層配線M1と同様に、TiN膜/Al膜/TiN膜の積層膜を形成し、パターニングすることにより第2層配線M2を形成する。

【0061】

[保護絶縁膜、再配線およびパッドパターン形成工程]

次いで、第2層配線M2上に保護絶縁膜(21、23、絶縁膜)および再配線31等を形成する。この工程を、図2〜図12を参照しながら説明する。図2〜図12においては、図1に示す半導体装置の最上層配線(ここでは、第2層配線M2)および再配線31の開口部OA1の近傍の領域を詳細に示してある。なお図2〜図12においては、図面を見やすくするため、第2層配線M2を、図1に示す第2層配線M2より短く表示してある。

【0062】

まず、図2に示すように、第2層配線M2および層間絶縁膜ID2上に、第1の保護絶縁膜21として、例えば、酸化シリコン膜および窒化シリコン膜の積層膜を形成する。例えば、酸化シリコン膜をCVD法などで堆積した後、酸化シリコン膜の上部に窒化シリコン膜をCVD法などで堆積することにより、上記積層膜を形成することができる。

【0063】

次いで、第1の保護絶縁膜21上にフォトレジスト膜(図示せず)を塗布し、このフォトレジスト膜を、露光・現像することにより開口部OA1のフォトレジスト膜を除去する。次いで、残存するフォトレジスト膜をマスクに、第1の保護絶縁膜(酸化シリコン膜および窒化シリコン膜の積層膜)21をエッチングすることにより、第1の保護絶縁膜21に開口部OA1を形成する。なお、開口部OA1に位置する反射防止膜もエッチングすることが好ましい。よって、この開口部(第1パッド領域)OA1からは、第2層配線M2を構成するAl膜が露出する。

【0064】

このように、上記開口部OA1は、第2層配線(Al膜)M2の露出部(露出領域)と対応し、第2層配線(Al膜)M2と再配線31との接続部(接続領域)となる。

【0065】

次いで、上記フォトレジスト膜を除去した後、開口部OA1上を含む第1の保護絶縁膜21上に、第2の保護絶縁膜23として、例えば、感光性ポリイミド膜(PIQ膜:Polyimide- isoindoloquinazolinedion膜)を塗布する。次いで、感光性ポリイミド膜を、露光・現像することにより少なくとも開口部OA1を含む領域の感光性ポリイミド膜を除去する。この工程により、開口部OA1から第2層配線(Al膜)M2が再び露出する。次いで、熱処理(キュア処理)を施すことにより、感光性ポリイミド膜を硬化させる。

【0066】

次いで、図3に示すように、上記開口部OA1上を含む第2の保護絶縁膜23上に、例えばクロム(Cr)膜からなるバリア膜25をスパッタリング法などにより堆積し、さらに、バリア膜25上に、電解メッキ用のCuシード層27として銅の薄膜(銅膜)をスパッタリング法などで形成する。

【0067】

次いで、図4に示すように、Cuシード層27上にフォトレジスト膜PR1を塗布し、フォトレジスト膜PR1を、露光・現像することにより再配線形成領域A31のフォトレジスト膜PR1を除去する。図5に示すように、再配線形成領域A31は、幅W1で長さLの略矩形の形状である。この再配線形成領域A31は、開口部OA1を含む領域である。次いで、残存するフォトレジスト膜(マスク膜)PR1の内部、即ち、再配線形成領域A31のCuシード層27上に、Cu膜(銅膜)31aを電解メッキ法により形成する。次いで、上記フォトレジスト膜PR1の内部、即ち、再配線形成領域A31のCu膜31a上に、Ni膜(ニッケル膜)31bを電解メッキ法により形成する。その結果、図6に示すように、Cu膜31aとNi膜31bとの積層膜が形成される。なお、Cu膜31aの膜厚は、例えば、8.0μm程度である。また、Ni膜31bの膜厚は、例えば、10nm〜3.5μm程度より好ましくは3.0μm以下である。

【0068】

Cuは低抵抗であり、Cu膜31aを再配線31に用いて好適である。また、Ni膜31bをCu膜31a上に形成することで、Cu膜31aを保護でき、Cu膜31aの耐食性を向上することができる。また、Cu膜31aのエレクトロマイグレーションを低減することができる。

【0069】

次いで、図7〜図9に示すように、再配線31の端部上に、パッドパターン33を形成する。パッドパターン33は、例えば、次の工程で形成する。まず、図7に示すように、再配線形成領域A31を含むフォトレジスト膜PR1上にフォトレジスト膜(マスク膜)PR2を塗布し、フォトレジスト膜PR2を、露光・現像することによりのパッドパターン形成領域OA2のフォトレジスト膜PR2を除去する。この際、パッドパターン形成領域(開口部)OA2において、フォトレジスト膜PR2の下層のフォトレジスト膜PR1も除去される。

【0070】

即ち、図8に示すように、パッドパターン形成領域(パッド領域)OA2は、再配線形成領域A31の端部領域上に配置される。再配線形成領域A31の端部領域を幅W1および長さL1の領域(図8の斜線部)とすると、パッドパターン形成領域OA2は、端部領域より一回り大きい。具体的には、略矩形状の上記端部領域の3辺において幅α分だけ広く設定されている。言い換えれば、上記端部領域とその外周(幅α分)を含み、幅が、(W1+2α)で、長さが、(L1+α)の領域となっている。

【0071】

次いで、図9に示すように、残存するフォトレジスト膜PR2の内部、即ち、パッドパターン形成領域OA2のNi膜31b上(その表面のみならず、側面も含む)に、Ni膜(ニッケル膜)33aを電解メッキ法により形成する。次いで、上記フォトレジスト膜PR2の内部、即ち、パッドパターン形成領域A33のNi膜33a上(その表面のみならず、側面も含む)に、Au膜33bを電解メッキ法により形成する。Ni膜33aの膜厚は、例えば、0.1〜1μm程度である。また、Au膜33bの膜厚は、例えば、1〜3μm程度である。

【0072】

このように、パッドパターン形成領域OA2を、再配線形成領域A31の端部領域より一回り大きく形成することで(図8参照)、パッドパターン形成領域A33において、再配線形成領域A31の端部領域の3辺に接する側面(側壁)がパッドパターン33により覆われる(図8および図9参照)。よって、再配線31とパッドパターン33の接触面積が大きくなり、これらの密着性が向上する。言い変えれば、パッドパターン33の剥離を低減することができる。

【0073】

次いで、図10に示すように、フォトレジスト膜PR1、PR2を除去する。その結果、再配線形成領域A31およびパッドパターン形成領域OA2においては、Ni膜31bおよびAu膜33bの表面と、Cu膜31a、Ni膜31b、Au膜33bおよびNi膜33aの側面とが露出する。また、再配線形成領域A31以外の領域において、Cuシード層27が露出する。

【0074】

次いで、図11に示すように、再配線31およびパッドパターン33を構成するNi膜(31b、33a)に対し、不動態化処理を施す。例えば、半導体基板1をアンモニアと過酸化水素水とを含有する処理液(アンモニア過水)に浸漬し、Ni膜(31b、33a)と処理液とを接触させることにより、Ni膜(31b、33a)の露出面において不動態化反応(酸化反応)を生じさせ、Niの不動態化膜35を形成する。この際、処理液を室温(25℃)以上に加熱する、より好ましくは50℃以上に加熱すれば、不動態化反応を促進させることができ好適である。

【0075】

不動態化処理のための処理液としては、アンモニア過水以外の過水(過酸化水素水を含有する処理液)を用いても良い。他の過水として、硫酸過水(硫酸と過酸化水素水とを含有する処理液)を用いてもよい。但し、硫酸過水は、Cu膜(31a)をエッチングし得るため、アンモニア過水を用いる方がより好ましい。

【0076】

また、不動態化処理として、プラズマ酸化法を用いてもよい。即ち、酸化性雰囲気(例えば、酸素を含有する雰囲気)中でプラズマを生じさせ、その内部に半導体基板1を配置し、酸素プラズマ(酸素ラジカル)とNi膜(31b、33a)とを反応させることにより、Ni膜(31b、33a)の露出面に、Niの不動態化膜35を形成してもよい。また、酸素を含んだ雰囲気中(窒素の中に酸素が微量(1%以下)に含まれた雰囲気)で150℃〜400℃の範囲で酸化アニールし不動態化膜35を形成してもよい。

【0077】

次いで、図12に示すように、ウエットエッチングにより、再配線形成領域A31以外の領域のCuシード層27と、その下層のバリア膜(Cr膜)25とを順次除去する。

【0078】

Cuシード層27のエッチングは、例えば、硫酸過水(硫酸と過酸化水素水とを含有する溶液)または硝酸過水(硝酸と過酸化水素水とを含有する溶液)を含有するエッチング液を用いて行われる。Cuシード層27を除去した後、バリア膜(Cr膜)25を、例えば、過マンガン酸カリウムを含有する溶液を用いてエッチングする。なお、バリア膜としてTi系の膜(TiN膜またはTi膜よりなる単層膜又はこれらの積層膜)を用いた場合には、アンモニア過水によりエッチングすることができる。

【0079】

ここで、上記Cuシード層27のエッチング液としては、硫酸過水または硝酸過水などが使用され、Cuのみならず、Niも溶解してしまう。しかしながら、本実施の形態おいては、Ni膜(31b、33a)の表面に、Niの不動態化膜35が形成されているため、Ni膜(31b、33a)のエッチング(膜減り)を防止することができる。

【0080】

その結果、次の効果を奏する。

【0081】

(1)Ni膜(31b、33a)のエッチングを防止することで、Ni膜(31b、33a)を当初から薄く成膜することができ、コストを抑えることができる。

【0082】

(2)Ni膜(31b、33a)の膜減り(例えば、本発明者の検討によれば、0.8μm程度)を考慮して、Ni膜(31b、33a)を厚く(例えば、1.0μm程度)形成した場合、当該膜の応力(膜応力)が大きくなり、半導体基板1に歪みが生じる。その結果、Ni膜31bの成膜から上記Cuシード層27のエッチング工程までの間の、露光工程などの処理工程や、処理装置間の搬送工程などにおいて、半導体基板1の固定や搬送にエラーが生じる。その結果、製造工程のスループット(throughput、単位時間あたりの処理能力)が低下する。また、歪みが大きい場合には、不良となり、製造歩留まりが低下する。また、下層の半導体素子(例えば、Qn、Qpなど)の特性の劣化や、配線(例えば、M1、M2)の断線などにも繋がり得る。これに対し、本実施の形態においては、上記のとおり、Ni膜(31b、33a)をあらかじめ薄く成膜することができるため、上記不具合を回避することができる。

【0083】

また、エッチングばらつきなどを考慮して、膜減り量を多めに設定する場合においては、Cuシード層27のエッチング工程の後において残存するNi膜の膜厚も所望の膜厚より大きくなる。その結果として、以降の工程においても、膜応力が大きい状態が継続する。よって、以降の工程、例えば、後述するプローブテスト工程やレーザー救済工程(ヒューズプログラミング工程)において、半導体基板1の固定(例えば、吸着固定)や搬送にエラーが生じ得る。このような場合も、製造工程のスループットが低下する。

【0084】

これに対し、本実施の形態においては、Ni膜(31b、33a)の膜厚を最適化することが可能であり、製造工程のスループットを向上させることができ、また、Ni膜(31b、33a)の膜応力を低減することにより、半導体装置の特性を向上させることができる。

【0085】

(3)また、パッドパターン33の側面にもNiの不動態化膜35が形成されているため(図11参照)、Ni膜33aのサイドエッチングを低減することができる。即ち、Niの不動態化膜35が形成されていない場合には、パッドパターン33のNi膜33aの側面が硫酸過水または硝酸過水に晒されるため、上記側面からNi膜のエッチング(侵食)が進行する。この侵食部が基点となりパッドパターン33が剥がれやすくなる。特に、パッドパターン33は、パターン面積が小さいため剥がれやすい。これに対し、本実施の形態においては、Ni膜33aのサイドエッチングを低減することができ、パッドパターン33の剥がれを低減することができる。

【0086】

[プローブテストおよびヒューズプログラミング工程]

この後、必要に応じて、パッドパターン33を利用して、半導体装置の動作テストを行う。このように、半導体装置の製造工程の前工程(ダイシング前、ウエハ状態)において、半導体装置(集積回路)などの良否を判定することを「ウエハテスト」と言う。

【0087】

このウエハテストとして、例えば、パッドパターン33に対応したプローブ針が設けられたプローブカードを用いて行う、「プローブテスト」がある。このプローブ針を介してパッドパターン33に電気的信号を印加し、また、パッドパターン33から得られる信号を検知することにより、半導体装置の電気的特性を確認することができる。このテスト結果により、半導体装置(集積回路)の良否を判断することができる。

【0088】

次いで、必要に応じて、ヒューズ素子のプログラミングを行う。例えば、配線(M1またはM2)と同層において、同じ導電性部材で形成されたヒューズ素子(図示せず)が設けられる。このヒューズ素子上の層間絶縁膜(ID1、ID2)や保護絶縁膜(21、23)をエッチングにより薄膜化する。この後、切断対象のヒューズ素子に対し、例えば、レーザーなどの高エネルギー線を照射することによりヒューズ素子を切断する。このように、ヒューズ素子の切断の有無によるプログラミングを行うことにより、例えば、上記プローブテストの結果に基づく欠陥の救済(冗長救済)や、半導体装置の仕様(周波数や対応電圧)に対応した回路の切り替えなどを行うことができる。

【0089】

上記プローブテスト工程やヒューズプログラミング工程においても、本実施の形態においては、半導体基板1の歪みが低減されているため、半導体基板1の固定(例えば、吸着固定)や搬送のエラーが低減される。

【0090】

[実装工程]

次いで、半導体基板(ウエハ)1を切断(ダイシング)して複数の半導体チップに分離(個片化)する。なお、ダイシングの前に、半導体基板(ウエハ)1の裏面研削を行い、半導体基板1を薄膜化してもよい。次いで、配線基板(実装基板)上に半導体チップを搭載(接着)する(ダイボンディング)。この配線基板のチップ搭載面側には外部接続端子(外部端子、端子)が形成されている。次いで、半導体チップ上のパッドパターン33と、配線基板に形成されている外部接続端子とを、金線などからなるワイヤ(導線、導電性部材)Wで接続する(ワイヤボンディング)。

【0091】

その後、必要に応じて、半導体チップやワイヤを覆うように封止樹脂(モールド樹脂)などで封止する。

【0092】

なお、本実施の形態においては、パッドパターン33をNi膜33aとAu膜33bとの積層膜で構成したが、Ni膜33aを省略してもよい。即ち、フォトレジスト膜PR2の内部、言い換えれば、パッドパターン形成領域OA2のNi膜31b上(その表面のみならず、側面も含む)に、直接、Au膜33bを電解メッキ法により形成してもよい。

【0093】

但し、Au膜33bの下層にNi膜33aを設け、連続して電解メッキ処理を行った方が、Au膜33bとNi膜33aとの密着性が向上し、Au膜33bの剥離を低減することができる。

【0094】

また、パッドパターン33を電解メッキ法を用いて形成したが、無電解メッキ法を用いて形成してもよい。但し、Au膜33bの膜厚が比較的大きい場合には、電解メッキ法を用いて好適である。

【0095】

(実施の形態2)

実施の形態1においては、再配線31の端部上にパッドパターン33を設け、パッドパターン33と配線基板などの外部接続端子とをワイヤWで接続したが(図1参照)、再配線31の端部上にバンプ電極BPを設け(図13参照)、このバンプ電極BPと配線基板などの外部接続端子とを接続してもよい。

【0096】

以下、図面を参照しながら本実施の形態の半導体装置の構成と製造方法について詳細に説明する。図13は、本実施の形態の半導体装置の構成を示す要部断面図である。図14〜図23は、本実施の形態の半導体装置の製造工程を示す要部断面図である。

【0097】

[構造説明]

まず、図13を参照しながら本実施の形態の半導体装置の特徴的な構成について説明する。

【0098】

図13に示すように、本実施の形態の半導体装置においても、実施の形態1の場合と同様に、半導体基板(基板)1上に形成された半導体素子として、例えばpチャネル型MISFETQpおよびnチャネル型MISFETQnを有する。かかるMISFETの他、他の素子、例えば、容量素子、抵抗素子やメモリセルなど、種々の素子を有していてもよい。これらMISFET上には、層間絶縁膜ID1が配置されている。また、上記MISFETのソース・ドレイン領域(3n、3p)上には、プラグP1を介して第1層配線M1が配置されている。

【0099】

この第1層配線M1上には、複数の配線層(第2層配線M2〜第4層配線M4)が配置されている。各配線層間は、プラグP2〜プラグP4により電気的に接続され、それ以外の領域は層間絶縁膜ID2〜ID4により電気的に絶縁されている。第1層配線M1〜第4層配線M4は、Cuを主成分とする導電性膜よりなるCu配線であり、いわゆるダマシン(damascene)配線である。

【0100】

最上層配線である第5層配線M5は、Alを主成分とする導電性膜よりなるAl配線である。なお、第1層配線M1〜第4層配線M4をAl配線としてもよい。

【0101】

この第5層配線(最上層配線)M5上には保護絶縁膜(21、23、24、絶縁膜)が形成され、保護絶縁膜の開口部(ここでは、第3の保護絶縁膜24の開口部)OA1から第5層配線(Al膜)M5が露出している。

【0102】

この露出部(開口部OA1、第1パッド領域)から保護絶縁膜(21、23、24)上に再配線31が配置されている。この再配線31は、上記露出部(開口部OA1、第1パッド領域)を半導体基板(半導体チップ)上の所望の領域まで引き回す役割を果たす。このように、再配線31を用い、再配線31の端部をパッド領域(開口部OA2、第2パッド領域)Pdとすることで、配線基板などの外部接続端子と半導体基板(半導体チップ)との電気的接続を容易に図ることができる。

【0103】

この再配線31は、銅膜(Cuを主成分とする導電性膜)31aと、ニッケル膜(Niを主成分とする導電性膜)31bとの積層膜よりなる。Cu膜31aは、下層のシード層である銅薄膜よりメッキ成長された膜であり、Cu膜31aの下層にはCuシード層(図13においては図示せず。図23参照)が配置されている。また、シード層の下部には、バリア膜(図13においては図示せず。図23参照)が配置されている。なお、Ni膜31bは、上記Cu膜31a上にメッキ成長された膜である。なお、以降、シード層(シード膜)27をCuシード層27ということがある。また、このCuシード層および上記バリア膜も導電性を有するため、再配線31に含まれると考えることができる。

【0104】

また、上記再配線31(Ni膜31b)上には表面保護絶縁膜(41、絶縁膜)が配置され、表面保護絶縁膜41の開口部OA2から再配線31が露出している。この開口部OA2内には、Au膜(図13においては、図示せず、図23参照)が形成されている。この開口部OA2が、パッド領域Pdとなる。このパッド領域Pd上には、バンプ電極(突起電極)BPが配置され、このバンプ電極BPを介して後述する配線基板などの外部接続端子と半導体装置との電気的接続が図られる。

【0105】

ここで、本実施の形態の半導体装置の特徴的な構成として、再配線31を構成するNi膜31bの表面のうち、開口部OA2以外の領域に、Niの不動態化膜35が配置されている。言い換えれば、Ni膜31bと表面保護絶縁膜(41、絶縁膜)とに挟まれた領域に、Niの不動態化膜35が配置されている。

【0106】

このように、Niの不動態化膜35を配置することで、Ni膜31bの耐食性が高まる。また、後述の製造工程で詳細に説明するように、Cuシード層27をエッチングする際のNi膜31bの膜減りを低減することができる。よって、Ni膜31bをあらかじめ薄く形成することができ、下層の配線や素子(MISFET)等に加わる応力を低減することができる。

【0107】

[製造方法説明]

次いで、図13〜図23を参照しながら、本実施の形態の半導体装置の製造工程を説明するとともに、当該半導体装置の構成をより明確にする。

【0108】

まず、図13に示すような半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の上方に複数の配線(M1〜M5)が形成された半導体基板1を準備する。

【0109】

[Qn、Qp形成工程]

半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の形成方法に制限はないが、例えば、実施の形態1で説明した工程により、nチャネル型MISFETQnおよびpチャネル型MISFETQpを形成することができる(図13、図1参照)。

【0110】

[M1〜M4形成工程]

複数の配線(M1〜M4)の形成方法に制限はないが、例えば、以下に示す工程により、これらを形成することができる(図13参照)。

【0111】

まず、前述の図13に示すnチャネル型MISFETQnおよびpチャネル型MISFETQp上に、絶縁膜として例えば酸化シリコン膜をCVD法で堆積する。その後、必要に応じて、酸化シリコン膜の表面を化学的機械研磨法で研磨してその表面を平坦化することによって層間絶縁膜ID1aを形成する。

【0112】

次いで、層間絶縁膜ID1aをエッチングすることにより、ソース・ドレイン領域3n、3p上に、それぞれコンタクトホール(接続孔)を形成する。次いで、コンタクトホール内を含む層間絶縁膜ID1a上に、導電性膜として例えば、W膜をCVD法で堆積し、このW膜を層間絶縁膜ID1aが露出するまでCMP法により研磨することによって、コンタクトホール内に導電性膜を埋め込む。この工程により、プラグ(接続部、コンタクトプラグ)P1が形成される。なお、W膜の下層に、例えばTiN膜、Ti膜等の単層膜又はこれらの積層膜からなるバリア膜を設けてもよい。

【0113】

次いで、層間絶縁膜ID1aおよびプラグP1上に、絶縁膜として例えば窒化シリコン膜および酸化シリコン膜をCVD法により順次堆積し、これらの積層膜から成る配線溝用絶縁膜ID1bを形成する。なお、窒化シリコン膜は、エッチングストッパー膜となる。また、上記層間絶縁膜ID1aと配線溝用絶縁膜ID1bとを併せて層間絶縁膜ID1と言うことがある(ID2〜ID4についても同様である)。

【0114】

次いで、配線溝用絶縁膜ID1bをエッチングすることにより配線溝を形成する。次いで、配線溝内を含む配線溝用絶縁膜ID1b上に、例えば窒化チタンからなるバリア膜(図示せず)をスパッタ法により堆積し、さらに、バリア膜上に、電解メッキ用のCuシード層(図示せず)として例えば銅の薄膜をスパッタ法もしくはCVD法で形成する。次いで、Cuシード層上に、導電性膜として例えば銅膜を電解メッキ法により形成する。

【0115】

次いで、配線溝以外の銅膜およびバリア膜をCMP法により除去することにより第1層配線M1を形成する。このように、配線溝の内部に導電性膜を埋め込む方法をダマシン法といい、特に、プラグと配線とを別工程で形成する方法をシングルダマシン法と言う。また、後述する第2層配線M2〜第4層配線M4のように、コンタクトホールおよび配線溝内に同時に導電性膜を埋め込むことにより、一度にプラグと配線とを形成する方法をデュアルダマシン法と言う。

【0116】

次いで、デュアルダマシン法を用いて第2層配線M2〜第4層配線M4を形成する。まず、第1層配線M1および配線溝用絶縁膜ID1b上に、例えば絶縁膜として窒化シリコン膜、酸化シリコン膜、窒化シリコン膜および酸化シリコン膜を順次CVD法により堆積することにより層間絶縁膜ID2を形成する。これらの膜のうち、下層の窒化シリコン膜は、第1層配線M1を構成する銅の拡散を防止する機能を有する。また、この下層の窒化シリコン膜は、後述するコンタクトホールを形成する際のエッチングストッパーとして、また、上層の窒化シリコン膜は、後述する配線溝を形成する際のエッチングストッパーとして利用される。

【0117】

次いで、層間絶縁膜ID2のうち、上から2層の絶縁膜である酸化シリコン膜および窒化シリコン膜の積層膜ID2bをエッチングすることにより、配線溝を形成する。次いで、配線溝内を含む層間絶縁膜ID2上に、第1フォトレジスト膜(図示せず)を堆積し、エッチバックすることにより配線溝を第1フォトレジスト膜で埋め込む。さらに、第1フォトレジスト膜上に後述するプラグP2の形成領域が開口した第2フォトレジスト膜(図示せず)を形成し、この第2フォトレジスト膜をマスクに、第1フォトレジスト膜と、下から2層の酸化シリコン膜および窒化シリコン膜の積層膜ID2aを、エッチングすることにより、コンタクトホールを形成する。

【0118】

なお、ここでは、配線溝を形成した後、コンタクトホールを形成したが、プラグP2の形成領域の層間絶縁膜ID2(4層の膜、ID2aおよびID2b)をエッチングすることによりコンタクトホールを形成した後、上から2層の絶縁膜である酸化シリコン膜および窒化シリコン膜の積層膜ID2bをエッチングすることにより、配線溝を形成してもよい。

【0119】

次いで、上記コンタクトホールおよび配線溝内を含む層間絶縁膜ID2上に、例えば窒化チタンからなるバリア膜(図示せず)をスパッタ法により堆積し、さらに、バリア膜上に、電解メッキ用のCuシード層(図示せず)として例えば銅の薄膜をスパッタ法もしくはCVD法で形成する。次いで、Cuシード層上に、導電性膜として例えば銅膜を電解メッキ法により形成する。

【0120】

次いで、配線溝以外の銅膜およびバリア膜をCMP法により除去することによりプラグP2および第2層配線M2を形成する。

【0121】

次いで、層間絶縁膜ID2(ID2a、ID2b)、プラグP2および第2層配線M2と同様に、層間絶縁膜ID3(ID3a、ID3b)、プラグP3および第3層配線M3を形成する。さらに、層間絶縁膜ID2(ID2a、ID2b)、プラグP2および第2層配線M2と同様に、層間絶縁膜ID4(ID4a、ID4b)、プラグP4および第4層配線M4を形成する。

【0122】

次いで、第4層配線M4上に、層間絶縁膜ID5を、例えば、層間絶縁膜ID1aと同様に形成し、この層間絶縁膜ID5中にプラグP5をプラグP1と同様に形成する。さらに、層間絶縁膜ID5およびプラグP5上に、第5層配線(Al配線)M5を形成する。

【0123】

例えば、層間絶縁膜ID5およびプラグP5上に、バリア膜(図示せず)として、例えば、TiN膜をスパッタリング法などで成膜し、次いで、バリア膜上に、Al膜をスパッタリング法により成膜し、さらに、Al膜上に、反射防止膜(図示せず)としてTiN膜をスパッタリング法などにより形成する。

【0124】

次いで、バリア膜、Al膜および反射防止膜の積層膜をパターニングすることにより、第5層配線M5を形成する。なお、上記コンタクトホールを形成後、コンタクトホール内を含む層間絶縁膜ID5上に、上記積層膜を形成した後、パターニングすることにより、プラグP5と第5層配線M5を同時に形成してもよい。上記工程により、Alを主成分とする第5層配線M5が形成される。なお、TiN膜は、導電性を有するため、TiN膜/Al膜/TiN膜の積層膜を第5層配線M5として扱ってもよい。

【0125】

[保護絶縁膜、再配線およびパッドパターン形成工程等]

次いで、第5層配線M5上に保護絶縁膜(21、23、24、絶縁膜)および再配線31等を形成する。この工程を、図14〜図23を参照しながら説明する。図14〜図23においては、図1に示す半導体装置の最上層配線(ここでは、第5層配線M5)および再配線31の開口部OA1の近傍の領域を詳細に示してある。なお図14〜図23においては、図面を見やすくするため、第5層配線M5を、図13に示す第5層配線M5より短く表示してある。

【0126】

まず、図14に示すように、第5層配線M5および層間絶縁膜ID5上に、第1の保護絶縁膜21として、例えば、酸化シリコン膜および窒化シリコン膜の積層膜を形成する。例えば、酸化シリコン膜をCVD法などで堆積した後、酸化シリコン膜の上部に窒化シリコン膜をCVD法などで堆積することにより、上記積層膜を形成することができる。

【0127】

次いで、第1の保護絶縁膜21をパターニングすることにより開口部OA1aを形成する。なお、開口部OA1aに位置する反射防止膜もエッチングすることが好ましい。よって、この開口部OA1aからは、第5層配線M5を構成するAl膜が露出する。

【0128】

次いで、開口部OA1a上を含む第1の保護絶縁膜21上に、第2の保護絶縁膜23として、例えば、感光性ポリイミド膜を塗布する。次いで、感光性ポリイミド膜を、露光・現像することにより開口部OA1aを含む領域の感光性ポリイミド膜を除去する。この工程により、開口部OA1aから第5層配線(Al膜)M5が再び露出する。

【0129】

次いで、図15に示すように、開口部OA1a上を含む第1および第2の保護絶縁膜(21、23)上に、第3の保護絶縁膜24として、例えば、感光性ポリイミド膜を塗布する。次いで、感光性ポリイミド膜を、露光・現像することにより開口部OA1a内の感光性ポリイミド膜を除去することにより、開口部OA1を形成する。この工程により、開口部OA1から第5層配線(Al膜)M5が再び露出する。次いで、熱処理(キュア処理)を施すことにより、感光性ポリイミド膜(23、24)を硬化させる。なお、上記工程においては、開口部OA1aをOA1より大きく形成したが、開口部OA1aを開口部OA1と同程度に形成してもよい。即ち、保護絶縁膜(21、23、24)の所望の領域が開口され第5層配線(Al膜)M5が露出する構成となればよい。この所望の領域(図15においては、開口部OA1)が、第5層配線(Al膜)M5と再配線31との接続部(接続領域)となる。

【0130】

次いで、図16に示すように、上記開口部OA1上を含む第3の保護絶縁膜24上に、例えばCr膜またはTi/TiN/Tiの積層膜(Ti系の膜)からなるバリア膜25をスパッタリング法などにより堆積し、さらに、バリア膜25上に、電解メッキ用のCuシード層27として銅の薄膜(銅膜)をスパッタリング法などで形成する。

【0131】

次いで、図17に示すように、Cuシード層27上にフォトレジスト膜PR1を塗布し、フォトレジスト膜PR1を、露光・現像することにより再配線形成領域A31のフォトレジスト膜PR1を除去する。この再配線形成領域A31は、開口部OA1を含む領域である。

【0132】

次いで、図18に示すように、残存するフォトレジスト膜(マスク膜)PR1の内部、即ち、再配線形成領域A31のCuシード層27上に、Cu膜(銅膜)31aを電解メッキ法により形成する。次いで、上記フォトレジスト膜PR1の内部、即ち、再配線形成領域A31のCu膜31a上に、Ni膜(ニッケル膜)31bを電解メッキ法により形成する。Cu膜31aの膜厚は、例えば、4〜7μm程度である。また、Ni膜31bの膜厚は、2〜4μm程度である。

【0133】

Cuは低抵抗であり、Cu膜31aを再配線31に用いて好適である。また、Ni膜31bをCu膜31a上に形成することで、Cu膜31aを保護でき、Cu膜31aの耐食性を向上することができる。また、Cu膜31aのエレクトロマイグレーションを低減することができる。

【0134】

次いで、図19に示すように、フォトレジスト膜PR1を除去する。その結果、再配線形成領域A31において、Ni膜31bの上面と、Cu膜31aおよびNi膜31bの側面とが露出し、再配線形成領域A31以外の領域において、Cuシード層27が露出する。

【0135】

次いで、図20に示すように、再配線31を構成するNi膜31bに対し、不動態化処理を施す。例えば、半導体基板1をアンモニアと過酸化水素水とを含有する処理液(アンモニア過水)に浸漬し、Ni膜31bと処理液とを接触させることにより、Ni膜31bの露出面において不動態化反応(酸化反応)を生じさせ、Niの不動態化膜35を形成する。これにより、Ni膜31bの上面と側面に、Niの不動態化膜35が形成される。この際、処理液を室温(25℃)以上に加熱する、より好ましくは50℃以上に加熱すれば、不動態化反応を促進させることができ好適である。

【0136】

不動態化処理のための処理液としては、アンモニア過水以外の過水(過酸化水素水を含有する処理液)を用いても良い。他の過水として、硫酸過水(硫酸と過酸化水素水とを含有する処理液)を用いてもよい。但し、硫酸過水は、Cu膜(31a)をエッチングし得るため、アンモニア過水を用いる方がより好ましい。

【0137】

また、不動態化処理として、プラズマ酸化法を用いてもよい。即ち、酸化性雰囲気(例えば、酸素を含有する雰囲気)中でプラズマを生じさせ、その内部に半導体基板1を配置し、酸素プラズマ(酸素ラジカル)とNi膜31bとを反応させることにより、Ni膜31bの露出面に、Niの不動態化膜35を形成してもよい。

【0138】

次いで、図21に示すように、ウエットエッチングにより、再配線形成領域A31以外の領域のCuシード層(Cu膜)27とバリア膜(Cr膜)25とを順次除去する。

【0139】

Cuシード層27のエッチングは、例えば、硫酸過水(硫酸と過酸化水素水とを含有する溶液)または硝酸過水(硝酸と過酸化水素水とを含有する溶液)を含有するエッチング液を用いて行われる。次いで、Cuシード層27を除去した後、バリア膜(Cr膜)25を、例えば、過マンガン酸カリウムを含有する溶液を用いてエッチングする。なお、バリア膜として上記Ti系の膜(TiN膜またはTi膜よりなる単層膜又はこれらの積層膜)を用いた場合には、アンモニア過水によりエッチングすることができる。

【0140】

ここで、上記Cuシード層27のエッチング液としては、硫酸過水または硝酸過水が使用され、Cuのみならず、Niも溶解してしまう。このようにCuのエッチング液はNiも溶解してしまうものが多い。しかしながら、本実施の形態おいては、Ni膜31bの表面に、Niの不動態化膜35が形成されているため、Ni膜31bのエッチング(膜減り)を防止することができる。

【0141】

その結果、次の効果を奏する。

【0142】

(1)Ni膜31bのエッチングを防止することで、Ni膜31bを当初から薄く成膜することができ、コストを抑えることができる。

【0143】

(2)Ni膜31bの膜減りを考慮して、Ni膜31bを厚く形成した場合、当該膜の応力(膜応力)が大きくなり、半導体基板1に歪みが生じる。その結果、Ni膜31bの成膜から上記Cuシード層27のエッチング工程までの間の、露光工程などの処理工程や、処理装置間の搬送工程などにおいて、半導体基板1の固定や搬送にエラーが生じる。その結果、製造工程のスループットが低下する。また、歪みが大きい場合には、不良となり、製造歩留まりが低下する。また、下層の半導体素子(例えば、Qn、Qpなど)の特性の劣化や、配線(例えば、M1〜M5)の断線などにも繋がり得る。これに対し、本実施の形態においては、上記のとおり、Ni膜31bをあらかじめ薄く成膜することができるため、上記不具合を回避することができる。

【0144】

また、エッチングばらつきなどを考慮して、膜減り量を多めに設定する場合においては、Cuシード層27のエッチング工程の後において残存するNi膜の膜厚も所望の膜厚より大きくなる。その結果として、以降の工程においても、膜応力が大きい状態が継続する。よって、以降の工程、例えば、後述するプローブテスト工程やレーザー救済工程(ヒューズプログラミング工程)において、半導体基板1の固定(例えば、吸着固定)や搬送にエラーが生じ得る。このような場合も、製造工程のスループットが低下する。

【0145】

これに対し、本実施の形態においては、Ni膜31bの膜厚を最適化することが可能であり、製造工程のスループットを向上させることができ、また、Ni膜31bの膜応力を低減することにより、半導体装置の特性を向上させることができる。

【0146】

(3)また、再配線31を構成するNi膜31bの側面にもNiの不動態化膜35が形成されているため、Ni膜31bのサイドエッチングを低減することができる。即ち、Niの不動態化膜35が形成されていない場合には、再配線31のNi膜31bの側面が硫酸過水または硝酸過水に晒されるため、上記側面からNi膜のエッチング(侵食)が進行する。かかるNi膜31bのサイドエッチングが進行すると、下層のCu膜31aのサイドエッチングも促進され得る。実施の形態1のパッドパターン(33)と比較し再配線31のパターン面積は大きいため、上記Ni膜31bおよびCu膜31aのサイドエッチングによる問題は小さいものの、配線の低抵抗化や、配線幅の微細化などに対応するためには、上記サイドエッチングの量は少ない方が好ましい。このように、本実施の形態においては、Ni膜31bのサイドエッチングを低減でき、また、Cu膜31aのサイドエッチングを低減できる(なお、当該効果は実施の形態1においても同様である)。

【0147】

次いで、再配線形成領域A31以外の領域のCuシード層(Cu膜)27とバリア膜(Cr膜)25とを除去した後、図21に示すように、Niの不動態化膜35上を含む第3の保護絶縁膜24上に、表面保護絶縁膜41として、例えば、感光性ポリイミド膜を塗布する。次いで、感光性ポリイミド膜を、露光・現像することにより感光性ポリイミド膜を選択的に除去することにより、開口部OA2を形成する。この開口部OA2は、再配線31の上部に位置し、パッド領域Pdと対応する。

【0148】

次いで、図22に示すように、表面保護絶縁膜41の開口部OA2から露出したNiの不動態化膜35を除去する。Niの不動態化膜35の除去は、還元性雰囲気におけるプラズマ処理により行うことができる。例えば、水素(H2)を含有する雰囲気中で、プラズマを生じさせ、水素プラズマ(水素ラジカル)とNiの不動態化膜(Niの酸化膜)35とを反応させることにより、Niの不動態化膜35を還元する。これにより、Niの不動態化膜35が除去され、表面保護絶縁膜41の開口部OA2からNi膜31bが露出する。上記水素雰囲気中でのプラズマ処理(水素プラズマ処理)に代えて、アンモニアプラズマ処理を行ってもよい。この場合、アンモニア(NH3)を含有する雰囲気中で、プラズマを生じさせ、水素ラジカルや窒化水素ラジカルとNiの不動態化膜(Niの酸化膜)35とを反応させる。

【0149】

次いで、図23に示すように、表面保護絶縁膜41の開口部OA2の内部のNi膜31b上に、Au膜33bを無電解メッキ法(置換メッキ法)により形成する。Au膜33bの膜厚は、10〜200nm程度である。このAu膜33bの表面が、パッド領域(バンプ電極形成領域)Pdとなる。

【0150】

この後、パッド領域Pdに、バンプ電極BPを形成する。例えば、Au膜33b(パッド領域Pd)上に、半田ボールをフラックスなどで仮固定し、半田リフロー処理(リフロー処理、熱処理)を行って半田を溶融、再固化することで、パッド領域Pd上に、半田よりなるバンプ電極BPを形成する。半田ボールの代わりに印刷法などにより半田ペーストをパッド領域Pd上に供給して、固化することにより半田よりなるバンプ電極BPを形成してもよい。また、半田よりなるバンプ電極BPの形成の際には、比較的薄い上記Au膜33bは、半田の内部に溶け込み、最終構造としてAu膜33bが認識できなくなる場合がある(図1参照)。

【0151】

[実装工程]

次いで、必要に応じて、プローブテストおよびヒューズプログラミング工程を行った後、半導体基板(ウエハ)1を切断(ダイシング)して複数の半導体チップに分離(個片化)する。なお、ダイシングの前に、半導体基板(ウエハ)1の裏面研削を行い、半導体基板1を薄膜化してもよい。次いで、配線基板上に半導体チップを搭載する。この配線基板のチップ搭載面側には外部接続端子(外部端子、端子)が形成されている。よって、搭載に際しては、半導体チップのバンプ電極BPと配線基板の外部接続端子とを位置合わせして搭載する(フェイスダウンボンディング)。次いで、バンプ電極BPを加熱リフローした後、半導体チップと配線基板との間を樹脂などで固定する。

【0152】

なお、本実施の形態においては、再配線形成領域A31内に開口部OA2を配置し、開口部OA2内部にAu膜33bを形成したが、開口部OA2を再配線31の端部領域より大きくしてもよい。図24は、本実施の形態の半導体装置の他の構成を示す要部断面図である。

【0153】

例えば、実施の形態1の図8に示すように、再配線31の端部領域の外周を含む領域を開口部OA2とし、その内部にAu膜33bを形成してもよい。その結果、図24に示すように、Au膜33bが、再配線31の端部領域の上面のみならず、その側面を覆うように配置されるため、再配線31とAu膜33bの接触面積が大きくなり、Au膜33bの剥がれを低減することができる。

【0154】

(実施の形態3)

実施の形態2においては、Cu膜31aおよびNi膜31bの積層膜よりなる再配線31の端部上にバンプ電極BPを形成したが、最上層配線である第5層配線M5の開口部OA1の直上にバンプ電極BPを形成してもよい。この際、バンプ電極BPの下層に、パッドパターン30として、Cu膜30aおよびNi膜30bの積層膜を配置してもよい。

【0155】

以下、図面を参照しながら本実施の形態の半導体装置の構成と製造方法について詳細に説明する。図25〜図30は、本実施の形態の半導体装置の製造工程を示す要部断面図である。

【0156】

[構造説明]

まず、本実施の形態の半導体装置の製造工程を示す要部断面図の最終工程図である図30を参照しながら本実施の形態の半導体装置の特徴的な構成について説明する。本実施の形態においては、実施の形態2と比較して、実施の形態2の再配線31に代えて、パッドパターン30を配置している点で相違するが、他の構成は、実施の形態2と同様であるため、パッドパターン30の構成について詳細に説明する。

【0157】

本実施の形態の半導体装置においても、実施の形態2と同様に、半導体基板(基板)1上に形成された半導体素子として、例えばpチャネル型MISFETQpおよびnチャネル型MISFETQnを有する(図13参照)。かかるMISFETの他、他の素子、例えば、容量素子、抵抗素子やメモリセルなど、種々の素子を有していてもよい。

【0158】

これらMISFET上には、層間絶縁膜ID1が配置されている。また、上記MISFETのソース・ドレイン領域(3n、3p)上には、プラグP1を介して第1層配線M1が配置されている。

【0159】

さらに、本実施の形態の半導体装置においても、実施の形態2と同様に、第1層配線M1上には、複数の配線層(第2層配線M2〜第4層配線M4)が形成されている。各配線層間は、プラグP2〜プラグP4により電気的に接続され、それ以外の領域は層間絶縁膜ID2〜ID4により電気的に絶縁されている。

【0160】

第1層配線M1〜第4層配線M4は、Cuを主成分とする導電性膜よりなるCu配線であり、いわゆるダマシン配線である。最上層配線である第5層配線M5は、Alを主成分とする導電性膜よりなるAl配線である。なお、第1層配線M1〜第4層配線M4をAl配線としてもよい。

【0161】

この第5層配線(最上層配線)M5上には保護絶縁膜(21、23、24、絶縁膜)が形成され、保護絶縁膜の開口部(ここでは、第3の保護絶縁膜24の開口部)OA1から第5層配線(Al膜)M5が露出している。

【0162】

この露出部(開口部OA1、第1パッド領域)より一回り大きく、その外周が保護絶縁膜(21、23、24)上にかかるように、パッドパターン30が配置されている。パッドパターン30は、銅膜(Cuを主成分とする導電性膜)30aと、ニッケル膜(Niを主成分とする導電性膜)30bとの積層膜よりなる。Cu膜30aは、下層のシード層である銅薄膜よりメッキ成長された膜であり、Cu膜31aの下層にはシード層27が配置されている。また、Cuシード層27の下部には、バリア膜25が配置されている。なお、Ni膜30bは、上記Cu膜30a上にメッキ成長された膜である。また、上記シード層27および上記バリア膜25も導電性を有するため、パッドパターン30に含まれると考えることができる。

【0163】

また、上記パッドパターン30(Ni膜30b)上には表面保護絶縁膜(41、絶縁膜)が形成され、表面保護絶縁膜41の開口部OA2からパッドパターン30が露出している。この開口部OA2内には、Au膜33bが配置されている。この開口部OA2が、パッド領域Pdとなる。パッド領域Pd上には、バンプ電極BPが配置され、このバンプ電極BPを介して後述する配線基板などの外部接続端子と半導体装置の電気的接続が図られる。

【0164】

ここで、本実施の形態の半導体装置の特徴的な構成として、パッドパターン30を構成するNi膜30bの表面のうち、開口部OA2以外の領域に、Niの不動態化膜35が配置されている。言い換えれば、Ni膜30bと表面保護絶縁膜(41、絶縁膜)とに挟まれた領域に、Niの不動態化膜35が配置されている。

【0165】

このように、Niの不動態化膜35を配置することで、Ni膜30bの耐食性が高まる。また、後述の製造工程で詳細に説明するように、Cuシード層27をエッチングする際のNi膜30bの膜減りを低減することができる。

【0166】

[製造方法説明]

次いで、図25〜図30を参照しながら、本実施の形態の半導体装置の製造工程を説明するとともに、当該半導体装置の構成をより明確にする。

【0167】

まず、実施の形態2と同様に、半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の上方に複数の配線(M1〜M5)が形成された半導体基板1を準備する。半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の形成工程および第1層配線M1〜第5層配線M5の形成工程は、実施の形態2と同様であるためその説明を省略する。

【0168】

[保護絶縁膜、再配線およびパッドパターン形成工程等]

図25に示すように、第5層配線M5の形成後、第1の保護絶縁膜21、第2の保護絶縁膜23および第3の保護絶縁膜24を形成する。これら保護絶縁膜(21、23、24)の積層膜は、開口部OA1を有し、開口部OA1から第5層配線(Al膜)M5が露出している。保護絶縁膜(21、23、24)および開口部OA1は、実施の形態2と同様の工程で形成することができる。

【0169】

次いで、上記開口部OA1上を含む第3の保護絶縁膜24上に、例えばCr膜またはTi/TiN/Tiの積層膜(Ti系の膜)からなるバリア膜25をスパッタリング法などにより堆積し、さらに、バリア膜25上に、電解メッキ用のCuシード層27として銅の薄膜(銅膜)をスパッタリング法などで形成する。

【0170】

次いで、Cuシード層27上にフォトレジスト膜PR1を塗布し、フォトレジスト膜PR1を、露光・現像することによりパッドパターン形成領域A30のフォトレジスト膜PR1を除去する。このパッドパターン形成領域A30は、開口部OA1を含む領域である。

【0171】

次いで、図26に示すように、残存するフォトレジスト膜(マスク膜)PR1の内部、即ち、パッドパターン形成領域A30のCuシード層27上に、Cu膜(銅膜)30aを電解メッキ法により形成する。次いで、上記フォトレジスト膜PR1の内部、即ち、パッドパターン形成領域A30のCu膜30a上に、Ni膜(ニッケル膜)30bを電解メッキ法により形成する。Cu膜30aの膜厚は、例えば、4〜7μm程度である。また、Ni膜30bの膜厚は、2〜4μm程度である。

【0172】

Cuは低抵抗であり、Cu膜30aをパッドパターン30に用いて好適である。また、Ni膜30bをCu膜30a上に形成することで、Cu膜30aを保護でき、Cu膜30aの耐食性を向上することができる。

【0173】

次いで、図27に示すように、フォトレジスト膜PR1を除去する。その結果、パッドパターン形成領域A30において、Ni膜30bの表面と、Cu膜30aおよびNi膜30bの側面とが露出し、パッドパターン形成領域A30以外の領域において、Cuシード層27が露出する。

【0174】

次いで、パッドパターン30を構成するNi膜30bに対し、実施の形態2と同様の処理を施し、Niの不動態化膜35を形成する。

【0175】

次いで、図28に示すように、実施の形態2と同様のウエットエッチングにより、パッドパターン形成領域A30以外の領域のCuシード層27とバリア膜(Cr膜)25とを順次除去する。

【0176】

ここで、上記Cuの薄膜よりなるCuシード層27のエッチング液としては、実施の形態2で詳細に説明したように、硫酸過水または硝酸過水が使用され、Cuのみならず、Niも溶解してしまう。しかしながら、本実施の形態おいては、Ni膜30bの表面および側面に、Niの不動態化膜35が形成されているため、Ni膜30bのエッチング(膜減り)を防止することができる。

【0177】

その結果、次の効果を奏する。

【0178】

(1)Ni膜30bのエッチングを防止することで、Ni膜30bを当初から薄く成膜することができ、コストを抑えることができる。

【0179】

(2)Ni膜30bの膜減りを考慮して、Ni膜30bを厚く形成した場合、実施の形態2で説明したように、当該膜の応力が大きくなるのに対し、膜応力を低減でき、搬送エラーなどの低減や、半導体装置の特性を向上させることができる。

【0180】

(3)また、パッドパターン30の側面にもNiの不動態化膜35が形成されているため、Ni膜30bのサイドエッチングを低減することができる。即ち、Niの不動態化膜35が形成されていない場合には、パッドパターン30のNi膜30bの側面が硫酸過水または硝酸過水に晒されるため、上記側面からNi膜30bのエッチング(侵食)が進行する。この侵食部が基点となりパッドパターン30が剥がれやすくなる。特に、パッドパターン30は、パターン面積が小さいため剥がれやすい。これに対し、本実施の形態においては、Ni膜30bのサイドエッチングを低減することができ、パッドパターン30の剥がれを低減することができる。

【0181】

次いで、パッドパターン形成領域A30以外の領域のCuシード層27とバリア膜(Cr膜)25とを除去した後、図29に示すように、Niの不動態化膜35上を含む第3の保護絶縁膜24上に、表面保護絶縁膜41として、例えば、感光性ポリイミド膜を塗布する。次いで、感光性ポリイミド膜を、露光・現像することにより感光性ポリイミド膜を選択的に除去することにより、開口部OA2を形成する。この開口部OA2は、パッドパターン30の上部に位置し、パッド領域(Pd)と対応する。

【0182】

次いで、開口部OA2から露出したNiの不動態化膜35を除去する。不動態化膜35の除去は、実施の形態2で説明した還元性雰囲気におけるプラズマ処理により行うことができる。

【0183】

次いで、図30に示すように、開口部OA2の内部のNi膜31b上に、Au膜33bを無電解メッキ法(置換メッキ法)により形成する。Au膜33bの膜厚は、10〜200nm程度である。このAu膜33bの表面が、パッド領域(バンプ電極形成領域)Pdとなる。

【0184】

この後、図示は省略するが、実施の形態2と同様に、パッド領域Pdに、バンプ電極BPを形成する。例えば、Au膜33b(パッド領域Pd)上に、半田ボールをフラックスなどで仮固定し、半田リフロー処理(リフロー処理、熱処理)を行って半田を溶融、再固化することで、パッド領域Pd上に、半田よりなるバンプ電極BPを形成する(図13参照)。

【0185】

[実装工程]

次いで、必要に応じて、プローブテストおよびヒューズプログラミング工程を行った後、実施の形態2と同様に、半導体基板(ウエハ)1を切断し、配線基板上にフェイスダウンボンディングする。

【0186】

以上、本発明者によってなされた発明をその実施の形態1〜3に基づき具体的に説明したが、本発明は上記実施の形態1〜3に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0187】

例えば、実施の形態1では2層の配線層(M1、M2)を、実施の形態2および3では、5層の配線層(M1〜M5)を形成したが、配線層の数に制限はなく、また、配線を構成する導電性材料も適宜変更可能である。

【産業上の利用可能性】

【0188】

本発明は、半導体装置の製造方法および半導体装置に関し、特に、Cu−Ni配線を有する半導体装置の製造方法、およびCu−Ni配線を有する半導体装置の構成に適用して好適なものである。

【符号の説明】

【0189】

1 半導体基板

2 素子分離領域

3n ソース・ドレイン領域

3p ソース・ドレイン領域

21 第1の保護絶縁膜

23 第2の保護絶縁膜

24 第3の保護絶縁膜

25 バリア膜

27 シード層(Cuシード層)

30 パッドパターン

30a Cu膜

30b Ni膜

31 再配線

31a Cu膜

31b Ni膜

33 パッドパターン

33a Ni膜

33b Au膜、

35 Niの不動態化膜

41 表面保護絶縁膜

A30 パッドパターン形成領域

A31 再配線形成領域

A33 パッドパターン形成領域

BP バンプ電極

G ゲート電極

ID1 層間絶縁膜

ID1a 層間絶縁膜

ID1b 配線溝用絶縁膜

ID2 層間絶縁膜

ID2a 積層膜

ID2b 積層膜

ID3(ID3a、ID3b) 層間絶縁膜

ID4(ID4a、ID4b) 層間絶縁膜

ID5 層間絶縁膜

L 長さ

L1 長さ

M1 第1層配線

M2 第2層配線

M3 第3層配線

M4 第4層配線

M5 第5層配線

OA1 開口部

OA1a 開口部

OA2 開口部(パッドパターン形成領域)

P1 プラグ

P2 プラグ

P3 プラグ

P4 プラグ

P5 プラグ

PR1 フォトレジスト膜

PR2 フォトレジスト膜

Pd パッド領域

Qn nチャネル型MISFET

Qp pチャネル型MISFET

W ワイヤ

W1 幅

α 幅

【技術分野】

【0001】

本発明は、半導体装置の製造方法および半導体装置に関し、特に、Cu−Ni配線を有する半導体装置の製造方法、およびCu−Ni配線を有する半導体装置の構成に適用して有効な技術に関する。

【背景技術】

【0002】

半導体装置は、半導体基板上に形成されたMISFETなどの半導体素子と、この半導体素子の上方に形成された多層の配線を有する。そして、最上層配線上には、例えば、Cu−Ni配線よりなる再配線が形成される。この再配線の一端は、最上層配線と接続される接続部となり、再配線の他端はパッド領域となる。このように、再配線は、最上層配線の端部と半導体チップの所定の位置のパッド領域とを接続する役割を果たす。

【0003】

例えば、下記特許文献1(特開2005−38932号公報)には、再配線層を有する半導体装置が開示され、この再配線層の形成に際し、次のような(1)〜(5)に示す工程を有する半導体装置の製造技術が開示されている(特に、特許文献1の[0072]〜[0077]段落参照)。

【0004】

(1)下地金属層[6b]上に第1の感光性樹脂を塗布し、露光および現像により、主導体層[6a]形成部分を除く部分に第1の感光性レジスト[11a]を形成する[図2(d)]。第1の感光性レジスト[11a]の形成後、仮硬化を行う[図2(e)]。

【0005】

(2)第1の感光性レジスト[11a]を利用して、主導体層[6a]を形成する。具体的には、第1の感光性レジスト[11a]の開口部に、例えば、硫酸銅からなる銅メッキ液を用いて電解メッキを行うことにより、Cuからなる主導体層[6a]を形成する[図2(f)]。その後、感光性レジスト[11a]を除去する[図2(g)]。

【0006】

(3)主導体層[6a]上に、第2の感光性樹脂を塗布し、露光および現像により、金属柱[9]を形成するために露出される主導体層[6a]の一部分を除く主導体層[6a]の上面、もしくは表面のみが露出されるように、第2の感光性レジスト[11b]を形成する。その後、仮硬化を行う[図2(h)]。

【0007】

(4)そして、第2の感光性レジスト[11b]を利用して、金属層[7]を形成する。具体的には、第2の感光性レジスト[11b]の開口部に、例えば、電解メッキ法により膜厚1μm〜3μmのNi層を形成する。その後、剥離液により第2の感光性レジスト[11b]を除去する[図3(i)]。

【0008】

(5)次に、例えば、過硫酸アンモニウムを主成分とするエッチング液、および、過酸化水素水や無機アンモニアを主成分とし、望ましくは主導体層[6a]に表面保護層を一時的に形成しエッチング液から保護する役割を有する添加剤を含むエッチング液を用いて、次の処理を行う。再配線層部分以外、すなわち、金属層[7]が形成されていない部分の下地金属層[6b]およびこの部分の下に位置するバリアメタル層[5]をエッチングにより除去する[図3(j)]。なお、[カッコ]内は、特許文献1中に記載の符号または図面番号である。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2005−38932号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明者は、上記のような再配線を有する半導体装置の研究・開発に従事している。この再配線として、下層に銅膜(Cu)を、その上層にニッケル膜(Ni)を用いたCu−Ni再配線を採用し、これらの金属膜をメッキ法により形成している。

【0011】

しかしながら、追って詳細に説明するように、金属膜のメッキ法による成膜時に形成されるCuシード層のエッチングの際、Cu−Ni再配線のNi膜がエッチングされ、Ni膜の膜減りが生じるという問題が生じた。

【0012】

さらに、Ni膜の膜べりを考慮して、あらかじめNi膜を厚く形成した場合、Ni膜の応力により基板(半導体装置)に歪みが生じ、製造工程における不具合や、素子特性に与える影響が懸念されるという問題があった。

【0013】

そこで、本発明の目的は、特性の良好な半導体装置の製造方法を提供することにある。また、半導体装置の製造工程のスループットを向上させることにある。また、製造コストを低減することができる半導体装置の製造方法を提供することにある。

【0014】

また、本発明の他の目的は、特性の良好な半導体装置を提供することにある。また、製造コストを低減することができる半導体装置を提供することにある。

【0015】

本発明の上記目的およびその他の目的と新規な特徴は、本願明細書の記載および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0016】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0017】

本願において開示される発明のうち、代表的な実施の形態に示される半導体装置の製造方法は、次の(a)〜(f)の工程を有する。(a)は、基板の上方に導電性膜よりなる第1配線を形成する工程である。(b)は、上記第1配線上に、上記第1配線の第1領域を露出する第1絶縁膜を形成する工程である。(c)は、上記第1配線の上記第1領域から上記第1絶縁膜上に延在する第2配線を形成する工程である。また、この(c)工程は、(c1)上記第1領域および上記第1絶縁膜上に銅を主成分とする第1銅膜を形成する工程と、(c2)上記第1銅膜上に、上記第2配線の形成領域を開口した第1マスク膜を形成する工程と、を有する。さらに、(c3)上記第2配線の形成領域の上記第1銅膜上に、メッキ成長により銅を主成分とする第2銅膜を形成する工程と、(c4)上記第2銅膜上に、ニッケルを主成分とする第1ニッケル膜を形成する工程と、を有し、これにより、上記第1銅膜、上記第2銅膜および上記ニッケル膜よりなる上記第2配線を形成する工程である。(d)は、上記第2配線上のパッド領域に金を主成分とする金膜を形成する工程である。(e)は、上記(d)工程の後、上記第1マスク膜を除去し、上記第1ニッケル膜に不動態化処理を施すことにより、上記第1ニッケル膜の表面にニッケルの不動態化膜を形成する工程である。(f)は、上記(e)工程の後、前記第1銅膜をエッチングする工程である。

【0018】

本願において開示される発明のうち、代表的な実施の形態に示される半導体装置の製造方法は、次の(a)〜(g)の工程を有する。(a)は、基板の上方に第1導電性膜を形成する工程である。(b)は、上記第1導電性膜上に、上記第1導電性膜の第1領域を露出する第1絶縁膜を形成する工程である。(c)は、上記第1導電性膜の第1領域および上記第1絶縁膜上に位置する第2導電性膜を形成する工程である。また、この(c)工程は、(c1)上記第1領域および上記第1絶縁膜上に銅を主成分とする第1銅膜を形成する工程と、(c2)上記第1銅膜上に、上記第2導電性膜の形成領域を開口した第1マスク膜を形成する工程と、を有する。さらに、(c3)上記第2導電性膜の形成領域の上記第1銅膜上に、メッキ成長により銅を主成分とする第2銅膜を形成する工程と、(c4)上記第2銅膜上に、ニッケルを主成分とするニッケル膜を形成する工程と、を有し、これにより、上記第1銅膜、上記第2銅膜および上記ニッケル膜よりなる上記第2導電性膜を形成する工程である。(d)は、上記(c)工程の後、上記第1マスク膜を除去し、上記ニッケル膜に不動態化処理を施すことにより、上記ニッケル膜の表面にニッケルの不動態化膜を形成する工程である。(e)は、上記(d)工程の後、上記第1銅膜をエッチングする工程である。(f)は、上記第2導電性膜のパッド領域上の上記不動態化膜を除去する工程である。(g)は、上記(f)工程の後、上記パッド領域に、金を主成分とする金膜を形成する工程である。

【0019】

本願において開示される発明のうち、代表的な実施の形態に示される半導体装置は、次の(a)〜(e)の構成を有する。(a)は、基板の上方に配置された導電性膜よりなる第1配線である。(b)は、上記第1配線上に配置され、上記第1配線の第1領域を露出する開口部を有する第1絶縁膜である。(c)は、上記導電性膜の第1領域から上記第1絶縁膜上に延在する第2配線であって、(c1)銅を主成分とする銅膜と、(c2)上記銅膜上に配置され、ニッケルを主成分とする第1ニッケル膜とを有する第2配線である。(d)は、上記第2配線のパッド領域上であって、上記第1ニッケル膜上に配置された金を主成分とする金膜である。(e)は、上記第2配線の上記第1ニッケル膜上に配置されたニッケルの不動態化膜である。そして、上記第1ニッケル膜の表面に上記不動態膜と上記金膜とが形成されている。

【0020】

本願において開示される発明のうち、代表的な実施の形態に示される半導体装置は、次の(a)〜(f)の構成を有する。(a)は、基板の上方に配置された第1導電性膜である。(b)は、上記第1導電性膜上に配置され、上記第1導電性膜の第1領域を露出する開口部を有する第1絶縁膜である。(c)は、上記第1導電性膜の第1領域および上記第1絶縁膜上に配置された第2導電性膜であって、(c1)銅を主成分とする銅膜と、(c2)上記銅膜上に配置され、ニッケルを主成分とするニッケル膜とを有する上記第2導電性膜である。(d)は、上記第2導電性膜のパッド領域を開口する第2絶縁膜である。(e)は、上記第2導電性膜のパッド領域上であって、上記ニッケル膜の上方に配置されたバンプ電極である。(f)は、上記ニッケル膜と上記第2絶縁膜とに挟まれた領域に配置されたニッケルの不動態化膜である。

【発明の効果】

【0021】

本願において開示される発明のうち、以下に示す代表的な実施の形態に示される半導体装置によれば、半導体装置の特性を向上させることができる。また、半導体装置の製造コストを低減することができる。

【0022】

本願において開示される発明のうち、以下に示す代表的な実施の形態に示される半導体装置の製造方法によれば、特性の良好な半導体装置を製造することができる。また、半導体装置の製造工程において、スループットを向上させることができる。また、半導体装置の製造工程において、製造コストを低減することができる。

【図面の簡単な説明】

【0023】

【図1】実施の形態1の半導体装置の構成を示す要部断面図である。

【図2】実施の形態1の半導体装置の製造工程を示す要部断面図である。

【図3】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図2に続く工程を示す要部断面図である。

【図4】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図3に続く工程を示す要部断面図である。

【図5】実施の形態1の半導体装置の製造工程を示す要部平面図である。

【図6】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図4に続く工程を示す要部断面図である。

【図7】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図6に続く工程を示す要部断面図である。

【図8】実施の形態1の半導体装置の製造工程を示す要部平面図である。

【図9】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図7に続く工程を示す要部断面図である。

【図10】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図9に続く工程を示す要部断面図である。

【図11】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図10に続く工程を示す要部断面図である。

【図12】実施の形態1の半導体装置の製造工程を示す要部断面図であって、図11に続く工程を示す要部断面図である。

【図13】実施の形態2の半導体装置の構成を示す要部断面図である。

【図14】実施の形態2の半導体装置の製造工程を示す要部断面図である。

【図15】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図14に続く工程を示す要部断面図である。

【図16】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図15に続く工程を示す要部断面図である。

【図17】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図16に続く工程を示す要部断面図である。

【図18】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図17に続く工程を示す要部断面図である。

【図19】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図18に続く工程を示す要部断面図である。

【図20】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図19に続く工程を示す要部断面図である。

【図21】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図20に続く工程を示す要部断面図である。

【図22】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図21に続く工程を示す要部断面図である。

【図23】実施の形態2の半導体装置の製造工程を示す要部断面図であって、図22に続く工程を示す要部断面図である。

【図24】実施の形態2の半導体装置の他の構成を示す要部断面図である。

【図25】実施の形態3の半導体装置の製造工程を示す要部断面図である。

【図26】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図25に続く工程を示す要部断面図である。

【図27】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図26に続く工程を示す要部断面図である。

【図28】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図27に続く工程を示す要部断面図である。

【図29】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図28に続く工程を示す要部断面図である。

【図30】実施の形態3の半導体装置の製造工程を示す要部断面図であって、図29に続く工程を示す要部断面図である。

【発明を実施するための形態】

【0024】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、応用例、詳細説明、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

【0025】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数等(個数、数値、量、範囲等を含む)についても同様である。

【0026】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一または関連する符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0027】

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。

【0028】

(実施の形態1)

以下、図面を参照しながら本実施の形態の半導体装置の構成と製造方法について詳細に説明する。図1は、本実施の形態の半導体装置の構成を示す要部断面図である。図2〜図12は、本実施の形態の半導体装置の製造工程を示す要部断面図または要部平面図である。

【0029】

[構造説明]

まず、図1を参照しながら本実施の形態の半導体装置の特徴的な構成について説明する。

【0030】

図1に示すように、本実施の形態の半導体装置は、半導体基板(基板)1上に形成された半導体素子として、例えばpチャネル型MISFETQpおよびnチャネル型MISFETQnを有する。かかるMISFETの他、他の素子、例えば、容量素子、抵抗素子やメモリセルなど、種々の素子を有していてもよい。

【0031】

これらMISFET(Metal Insulator Semiconductor Field Effect Transistor、電界効果トランジスタ)上には、層間絶縁膜ID1が配置されている。また、上記MISFETのソース・ドレイン領域(3n、3p)上には、プラグP1を介して第1層配線M1が配置されている。さらに、第1層配線M1上には、第2層配線M2が形成されている。第1層配線M1と第2層配線M2との間は、プラグP2により電気的に接続され、プラグP2以外の領域は層間絶縁膜ID2により電気的に絶縁されている。

【0032】

第1層配線M1および第2層配線M2は、アルミニウム(Alを主成分とする導電性膜)よりなる配線である。主成分とは、少なくとも50%以上の組成比で混合されている成分をいう。

【0033】

この第2層配線(最上層配線)M2上には保護絶縁膜(21、23、絶縁膜)が形成され、保護絶縁膜の開口部(ここでは、第1の保護絶縁膜21の開口部)OA1から第2層配線(Al膜)M2が露出している。

【0034】

この露出部(開口部OA1、第1パッド領域)から保護絶縁膜(21、23)上に再配線31が配置されている。この再配線31は、上記露出部(開口部OA1、第1パッド領域)を半導体基板(半導体チップ)上の所望の領域まで引き回す役割を果たす。このように、再配線31を用い、再配線31の端部をパッド領域Pd(開口部OA2、第2パッド領域)とすることで、配線基板などの外部接続端子と半導体基板(半導体チップ)との電気的接続を容易に図ることができる。

【0035】

この再配線31は、銅膜(Cuを主成分とする導電性膜)31aと、ニッケル膜(Niを主成分とする導電性膜)31bとの積層膜(Cu−Ni配線)よりなる。Cu膜31aは、下層のシード層である銅薄膜よりメッキ成長された膜であり、Cu膜31aの下層にはシード層(図1においては図示せず。図12参照)が配置されている。また、シード層の下部には、バリア膜(図1においては図示せず。図12参照)が配置されている。なお、Ni膜31bは、上記Cu膜31a上にメッキ成長された膜である。なお、以降、シード層(シード膜)27をCuシード層27ということがある。また、このCuシード層および上記バリア膜も導電性を有するため、再配線31に含まれると考えることができる。

【0036】

また、上記再配線31の端部上には、パッドパターン33が配置されている。パッドパターン33は、ワイヤWとの接続を図るための下地層(パッド領域の下地層)であり、このパッドパターン33の表面が、パッド領域(ワイヤとの接続部、外部接続端子との接続部)Pdとなる。このパッドパターン33は、ニッケル膜(Niを主成分とする導電性膜)33aと金膜(Auを主成分とする導電性膜)33bの積層膜よりなる。

【0037】

このパッドパターン33の形成領域は、再配線31の端部領域より大きく、再配線31の端部領域の外周を含む領域である(図8参照)。よって、パッドパターン33は、再配線31の端部領域の上面のみならず、その側面を覆うように配置される(図1参照)。かかる構成により、再配線31とパッドパターン33の接触面積が大きくなり、パッドパターン33の剥がれを低減することができる。

【0038】

ここで、本実施の形態の半導体装置の特徴的な構成として、再配線31を構成するNi膜31bの表面のうち、パッドパターン33(パッド領域Pd、開口部OA2)の形成領域以外の領域に、Niの不動態化膜35が配置されている。また、パッドパターン33を構成するNi膜33aの表面のうち、Au膜33bで覆われていない領域、即ち、Ni膜33aの側面(露出領域、露出面)にも、Niの不動態化膜35が配置されている。

【0039】

Niの不動態化膜35とは、Niの酸化膜(NixOy)であり、不動態化処理により形成される膜である。不動態化処理としては、例えば、ニッケル膜と酸化性の溶液とを接触させる処理によりなされる。酸化性の溶液は、例えば、過酸化水素水を含有する溶液(処理液)であり、より具体的には、アンモニアと過酸化水素水を含有する溶液(アンモニア過水)が、ニッケルの不動態化処理液として好適に用いられる。また、ニッケル膜を酸化性雰囲気中でプラズマ処理することによってニッケル膜を不動態化することができる。

【0040】

上記Niの不動態化膜は、酸化膜であるが、Niの自然酸化膜とは異なり、緻密で安定な膜である。よって、Niの自然酸化膜は、Niの不動態化膜よりエッチングされやすく、例えば、上記アンモニア過水をエッチング液として用いてエッチングした場合、Niの自然酸化膜のエッチングレート(エッチング速度)は、Niの不動態化膜のエッチングレートの100倍以上である。即ち、Niの不動態化膜のエッチングレートは、Niの自然酸化膜のエッチングレートの100分の1以下である。また、上記Niの不動態化膜は、Niの自然酸化膜とは異なり、緻密で安定な膜であるため、硫酸や塩酸等の強い酸を用いても溶解し難い。

【0041】

このように、Niの不動態化膜35を配置することで、Ni膜31bの耐食性が高まる。また、後述の製造工程で詳細に説明するように、Cuシード層27をエッチングする際のNi膜31bの膜減りを低減することができる。よって、Ni膜31bをあらかじめ薄く形成することができ、下層の配線や素子(MISFET)等に加わる応力を低減することができる。

【0042】

また、パッドパターン33(パッド領域Pd)上には、後述する配線基板の外部接続端子との電気的接続を図るためのワイヤ(導電性部材)Wが配置されている。

【0043】

[製造方法説明]

次いで、図1〜図12を参照しながら、本実施の形態の半導体装置の製造工程を説明するとともに、当該半導体装置の構成をより明確にする。

【0044】

まず、図1に示すような半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の上方に複数の配線(M1、M2)が形成された半導体基板1を準備する。

【0045】

[Qn、Qp形成工程]

半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の形成方法に制限はないが、例えば、以下に示す工程により、これらを形成することができる(図1参照)。

【0046】

例えばp型の単結晶シリコンからなる半導体基板1をエッチングすることにより溝を形成し、溝の内部に絶縁膜として例えば酸化シリコン膜を埋め込むことにより素子分離領域2を形成する。この素子分離領域2により、nチャネル型MISFETQnが形成される活性領域およびpチャネル型MISFETQpが形成される活性領域が区画される。

【0047】

次いで、半導体基板1のnチャネル型MISFETQnが形成される活性領域にp型不純物をイオン打ち込みした後、熱処理により不純物を拡散させることにより、p型ウエルを形成する。また、半導体基板1のpチャネル型MISFETQpが形成される活性領域にn型不純物をイオン打ち込みした後、熱処理により不純物を拡散させることにより、n型ウエルを形成する。次いで、例えば、半導体基板1(p型ウエルおよびn型ウエル)の表面を熱酸化することにより、ゲート絶縁膜を形成する。

【0048】

次いで、ゲート絶縁膜上に、例えば導電性膜として、不純物をドープした多結晶シリコン膜を堆積し、さらに、その上部に、絶縁膜として例えば窒化シリコン膜を堆積する。次いで、窒化シリコン膜をエッチングした後、この窒化シリコン膜をマスクとして多結晶シリコン膜をエッチングすることにより、ゲート電極Gを形成する。このように、所望の形状の膜(マスク膜、フォトレジスト膜)をマスクとして、下層の膜を選択的に除去する工程を「パターニング」という。

【0049】

次いで、ゲート電極Gの両側のp型ウエルにn型不純物をイオン打ち込みすることによってn−型半導体領域を形成し、ゲート電極Gの両側のn型ウエルにp型不純物をイオン打ち込みすることによってp−型半導体領域を形成する。

【0050】

次いで、半導体基板1の全面上に絶縁膜として例えば窒化シリコン膜を堆積した後、異方的にエッチングすることによって、ゲート電極Gの側壁にサイドウォールスペーサを形成する。

【0051】

次いで、ゲート電極Gおよびサイドウォールスペーサをマスクにp型ウエルにn型不純物をイオン打ち込みすることによってn−型半導体領域よりも不純物濃度の高いn+型半導体領域を形成し、ゲート電極Gおよびサイドウォールスペーサをマスクにn型ウエルにp型不純物をイオン打ち込みすることによってp−型半導体領域よりも不純物濃度の高いp+型半導体領域を形成する。

【0052】

以上の工程により、n−型半導体領域およびn+型半導体領域よりなるLDD(Lightly Doped Drain)構造のソース・ドレイン領域3nを備えたnチャネル型MISFETQn、およびp−型半導体領域およびp+型半導体領域よりなるLDD構造のソース・ドレイン領域3pを備えたpチャネル型MISFETQpが形成される(図1参照)。

【0053】

[M1、M2形成工程]

複数の配線(M1、M2)の形成方法に制限はないが、例えば、以下に示す工程により、これらを形成することができる(図1参照)。

【0054】

まず、図1に示すnチャネル型MISFETQnおよびpチャネル型MISFETQp上に、絶縁膜として例えば酸化シリコン膜をCVD(Chemical Vapor deposition)法などで堆積する。その後、必要に応じて、酸化シリコン膜の表面を化学的機械研磨(CMP;Chemical Mechanical Polishing)法などで研磨してその表面を平坦化することによって層間絶縁膜ID1を形成する。

【0055】

次いで、層間絶縁膜ID1をパターニングすることにより、ソース・ドレイン領域3n、3p上に、それぞれコンタクトホール(接続孔)を形成する。次いで、コンタクトホール内を含む層間絶縁膜ID1上に、導電性膜として例えば、タングステン(W)膜をCVD法などで堆積し、このW膜を層間絶縁膜ID1が露出するまでCMP法などにより研磨することによって、コンタクトホール内に導電性膜を埋め込む。この工程により、プラグ(接続部、コンタクトプラグ)P1が形成される。なお、W膜の下層に、例えば窒化チタン(TiN)膜またはチタン(Ti)膜等よりなる単層膜又はこれらの積層膜からなるバリア膜を設けてもよい。

【0056】

次いで、プラグP1上を含む層間絶縁膜ID1上に、バリア膜(図示せず)として例えばTiN膜をスパッタリング法などにより形成する。次いで、バリア膜上に、Al膜をスパッタリング法などにより形成する。次いで、Al膜上に、反射防止膜(図示せず)としてTiN膜をスパッタリング法などにより形成する。

【0057】

次いで、バリア膜、Al膜および反射防止膜の積層膜をパターニングすることにより、第1層配線M1を形成する。なお、上記コンタクトホールを形成後、コンタクトホール内を含む層間絶縁膜ID1上に、上記積層膜を形成した後、パターニングすることにより、プラグP1と第1層配線M1を同時に形成してもよい。上記工程により、Alを主成分とする第1層配線M1が形成される。なお、TiN膜は、導電性を有するため、TiN膜/Al膜/TiN膜の積層膜を第1層配線M1として扱ってもよい。

【0058】

次いで、第1層配線M1上に、絶縁膜として例えば酸化シリコン膜をCVD法などで堆積し、その後、必要に応じて、酸化シリコン膜の表面を研磨することによって層間絶縁膜ID2を形成する。

【0059】

次いで、層間絶縁膜ID2をエッチングすることにより、第1層配線M1上にコンタクトホールを形成する。次いで、プラグP1と同様に、コンタクトホール内に導電性膜を埋め込むことにより、プラグP2を形成する。

【0060】

次いで、プラグP2上を含む層間絶縁膜ID2上に、第1層配線M1と同様に、TiN膜/Al膜/TiN膜の積層膜を形成し、パターニングすることにより第2層配線M2を形成する。

【0061】

[保護絶縁膜、再配線およびパッドパターン形成工程]

次いで、第2層配線M2上に保護絶縁膜(21、23、絶縁膜)および再配線31等を形成する。この工程を、図2〜図12を参照しながら説明する。図2〜図12においては、図1に示す半導体装置の最上層配線(ここでは、第2層配線M2)および再配線31の開口部OA1の近傍の領域を詳細に示してある。なお図2〜図12においては、図面を見やすくするため、第2層配線M2を、図1に示す第2層配線M2より短く表示してある。

【0062】

まず、図2に示すように、第2層配線M2および層間絶縁膜ID2上に、第1の保護絶縁膜21として、例えば、酸化シリコン膜および窒化シリコン膜の積層膜を形成する。例えば、酸化シリコン膜をCVD法などで堆積した後、酸化シリコン膜の上部に窒化シリコン膜をCVD法などで堆積することにより、上記積層膜を形成することができる。

【0063】

次いで、第1の保護絶縁膜21上にフォトレジスト膜(図示せず)を塗布し、このフォトレジスト膜を、露光・現像することにより開口部OA1のフォトレジスト膜を除去する。次いで、残存するフォトレジスト膜をマスクに、第1の保護絶縁膜(酸化シリコン膜および窒化シリコン膜の積層膜)21をエッチングすることにより、第1の保護絶縁膜21に開口部OA1を形成する。なお、開口部OA1に位置する反射防止膜もエッチングすることが好ましい。よって、この開口部(第1パッド領域)OA1からは、第2層配線M2を構成するAl膜が露出する。

【0064】

このように、上記開口部OA1は、第2層配線(Al膜)M2の露出部(露出領域)と対応し、第2層配線(Al膜)M2と再配線31との接続部(接続領域)となる。

【0065】

次いで、上記フォトレジスト膜を除去した後、開口部OA1上を含む第1の保護絶縁膜21上に、第2の保護絶縁膜23として、例えば、感光性ポリイミド膜(PIQ膜:Polyimide- isoindoloquinazolinedion膜)を塗布する。次いで、感光性ポリイミド膜を、露光・現像することにより少なくとも開口部OA1を含む領域の感光性ポリイミド膜を除去する。この工程により、開口部OA1から第2層配線(Al膜)M2が再び露出する。次いで、熱処理(キュア処理)を施すことにより、感光性ポリイミド膜を硬化させる。

【0066】

次いで、図3に示すように、上記開口部OA1上を含む第2の保護絶縁膜23上に、例えばクロム(Cr)膜からなるバリア膜25をスパッタリング法などにより堆積し、さらに、バリア膜25上に、電解メッキ用のCuシード層27として銅の薄膜(銅膜)をスパッタリング法などで形成する。

【0067】

次いで、図4に示すように、Cuシード層27上にフォトレジスト膜PR1を塗布し、フォトレジスト膜PR1を、露光・現像することにより再配線形成領域A31のフォトレジスト膜PR1を除去する。図5に示すように、再配線形成領域A31は、幅W1で長さLの略矩形の形状である。この再配線形成領域A31は、開口部OA1を含む領域である。次いで、残存するフォトレジスト膜(マスク膜)PR1の内部、即ち、再配線形成領域A31のCuシード層27上に、Cu膜(銅膜)31aを電解メッキ法により形成する。次いで、上記フォトレジスト膜PR1の内部、即ち、再配線形成領域A31のCu膜31a上に、Ni膜(ニッケル膜)31bを電解メッキ法により形成する。その結果、図6に示すように、Cu膜31aとNi膜31bとの積層膜が形成される。なお、Cu膜31aの膜厚は、例えば、8.0μm程度である。また、Ni膜31bの膜厚は、例えば、10nm〜3.5μm程度より好ましくは3.0μm以下である。

【0068】

Cuは低抵抗であり、Cu膜31aを再配線31に用いて好適である。また、Ni膜31bをCu膜31a上に形成することで、Cu膜31aを保護でき、Cu膜31aの耐食性を向上することができる。また、Cu膜31aのエレクトロマイグレーションを低減することができる。

【0069】

次いで、図7〜図9に示すように、再配線31の端部上に、パッドパターン33を形成する。パッドパターン33は、例えば、次の工程で形成する。まず、図7に示すように、再配線形成領域A31を含むフォトレジスト膜PR1上にフォトレジスト膜(マスク膜)PR2を塗布し、フォトレジスト膜PR2を、露光・現像することによりのパッドパターン形成領域OA2のフォトレジスト膜PR2を除去する。この際、パッドパターン形成領域(開口部)OA2において、フォトレジスト膜PR2の下層のフォトレジスト膜PR1も除去される。

【0070】

即ち、図8に示すように、パッドパターン形成領域(パッド領域)OA2は、再配線形成領域A31の端部領域上に配置される。再配線形成領域A31の端部領域を幅W1および長さL1の領域(図8の斜線部)とすると、パッドパターン形成領域OA2は、端部領域より一回り大きい。具体的には、略矩形状の上記端部領域の3辺において幅α分だけ広く設定されている。言い換えれば、上記端部領域とその外周(幅α分)を含み、幅が、(W1+2α)で、長さが、(L1+α)の領域となっている。

【0071】

次いで、図9に示すように、残存するフォトレジスト膜PR2の内部、即ち、パッドパターン形成領域OA2のNi膜31b上(その表面のみならず、側面も含む)に、Ni膜(ニッケル膜)33aを電解メッキ法により形成する。次いで、上記フォトレジスト膜PR2の内部、即ち、パッドパターン形成領域A33のNi膜33a上(その表面のみならず、側面も含む)に、Au膜33bを電解メッキ法により形成する。Ni膜33aの膜厚は、例えば、0.1〜1μm程度である。また、Au膜33bの膜厚は、例えば、1〜3μm程度である。

【0072】

このように、パッドパターン形成領域OA2を、再配線形成領域A31の端部領域より一回り大きく形成することで(図8参照)、パッドパターン形成領域A33において、再配線形成領域A31の端部領域の3辺に接する側面(側壁)がパッドパターン33により覆われる(図8および図9参照)。よって、再配線31とパッドパターン33の接触面積が大きくなり、これらの密着性が向上する。言い変えれば、パッドパターン33の剥離を低減することができる。

【0073】

次いで、図10に示すように、フォトレジスト膜PR1、PR2を除去する。その結果、再配線形成領域A31およびパッドパターン形成領域OA2においては、Ni膜31bおよびAu膜33bの表面と、Cu膜31a、Ni膜31b、Au膜33bおよびNi膜33aの側面とが露出する。また、再配線形成領域A31以外の領域において、Cuシード層27が露出する。

【0074】

次いで、図11に示すように、再配線31およびパッドパターン33を構成するNi膜(31b、33a)に対し、不動態化処理を施す。例えば、半導体基板1をアンモニアと過酸化水素水とを含有する処理液(アンモニア過水)に浸漬し、Ni膜(31b、33a)と処理液とを接触させることにより、Ni膜(31b、33a)の露出面において不動態化反応(酸化反応)を生じさせ、Niの不動態化膜35を形成する。この際、処理液を室温(25℃)以上に加熱する、より好ましくは50℃以上に加熱すれば、不動態化反応を促進させることができ好適である。

【0075】

不動態化処理のための処理液としては、アンモニア過水以外の過水(過酸化水素水を含有する処理液)を用いても良い。他の過水として、硫酸過水(硫酸と過酸化水素水とを含有する処理液)を用いてもよい。但し、硫酸過水は、Cu膜(31a)をエッチングし得るため、アンモニア過水を用いる方がより好ましい。

【0076】

また、不動態化処理として、プラズマ酸化法を用いてもよい。即ち、酸化性雰囲気(例えば、酸素を含有する雰囲気)中でプラズマを生じさせ、その内部に半導体基板1を配置し、酸素プラズマ(酸素ラジカル)とNi膜(31b、33a)とを反応させることにより、Ni膜(31b、33a)の露出面に、Niの不動態化膜35を形成してもよい。また、酸素を含んだ雰囲気中(窒素の中に酸素が微量(1%以下)に含まれた雰囲気)で150℃〜400℃の範囲で酸化アニールし不動態化膜35を形成してもよい。

【0077】

次いで、図12に示すように、ウエットエッチングにより、再配線形成領域A31以外の領域のCuシード層27と、その下層のバリア膜(Cr膜)25とを順次除去する。

【0078】

Cuシード層27のエッチングは、例えば、硫酸過水(硫酸と過酸化水素水とを含有する溶液)または硝酸過水(硝酸と過酸化水素水とを含有する溶液)を含有するエッチング液を用いて行われる。Cuシード層27を除去した後、バリア膜(Cr膜)25を、例えば、過マンガン酸カリウムを含有する溶液を用いてエッチングする。なお、バリア膜としてTi系の膜(TiN膜またはTi膜よりなる単層膜又はこれらの積層膜)を用いた場合には、アンモニア過水によりエッチングすることができる。

【0079】

ここで、上記Cuシード層27のエッチング液としては、硫酸過水または硝酸過水などが使用され、Cuのみならず、Niも溶解してしまう。しかしながら、本実施の形態おいては、Ni膜(31b、33a)の表面に、Niの不動態化膜35が形成されているため、Ni膜(31b、33a)のエッチング(膜減り)を防止することができる。

【0080】

その結果、次の効果を奏する。

【0081】

(1)Ni膜(31b、33a)のエッチングを防止することで、Ni膜(31b、33a)を当初から薄く成膜することができ、コストを抑えることができる。

【0082】

(2)Ni膜(31b、33a)の膜減り(例えば、本発明者の検討によれば、0.8μm程度)を考慮して、Ni膜(31b、33a)を厚く(例えば、1.0μm程度)形成した場合、当該膜の応力(膜応力)が大きくなり、半導体基板1に歪みが生じる。その結果、Ni膜31bの成膜から上記Cuシード層27のエッチング工程までの間の、露光工程などの処理工程や、処理装置間の搬送工程などにおいて、半導体基板1の固定や搬送にエラーが生じる。その結果、製造工程のスループット(throughput、単位時間あたりの処理能力)が低下する。また、歪みが大きい場合には、不良となり、製造歩留まりが低下する。また、下層の半導体素子(例えば、Qn、Qpなど)の特性の劣化や、配線(例えば、M1、M2)の断線などにも繋がり得る。これに対し、本実施の形態においては、上記のとおり、Ni膜(31b、33a)をあらかじめ薄く成膜することができるため、上記不具合を回避することができる。

【0083】

また、エッチングばらつきなどを考慮して、膜減り量を多めに設定する場合においては、Cuシード層27のエッチング工程の後において残存するNi膜の膜厚も所望の膜厚より大きくなる。その結果として、以降の工程においても、膜応力が大きい状態が継続する。よって、以降の工程、例えば、後述するプローブテスト工程やレーザー救済工程(ヒューズプログラミング工程)において、半導体基板1の固定(例えば、吸着固定)や搬送にエラーが生じ得る。このような場合も、製造工程のスループットが低下する。

【0084】

これに対し、本実施の形態においては、Ni膜(31b、33a)の膜厚を最適化することが可能であり、製造工程のスループットを向上させることができ、また、Ni膜(31b、33a)の膜応力を低減することにより、半導体装置の特性を向上させることができる。

【0085】

(3)また、パッドパターン33の側面にもNiの不動態化膜35が形成されているため(図11参照)、Ni膜33aのサイドエッチングを低減することができる。即ち、Niの不動態化膜35が形成されていない場合には、パッドパターン33のNi膜33aの側面が硫酸過水または硝酸過水に晒されるため、上記側面からNi膜のエッチング(侵食)が進行する。この侵食部が基点となりパッドパターン33が剥がれやすくなる。特に、パッドパターン33は、パターン面積が小さいため剥がれやすい。これに対し、本実施の形態においては、Ni膜33aのサイドエッチングを低減することができ、パッドパターン33の剥がれを低減することができる。

【0086】

[プローブテストおよびヒューズプログラミング工程]

この後、必要に応じて、パッドパターン33を利用して、半導体装置の動作テストを行う。このように、半導体装置の製造工程の前工程(ダイシング前、ウエハ状態)において、半導体装置(集積回路)などの良否を判定することを「ウエハテスト」と言う。

【0087】

このウエハテストとして、例えば、パッドパターン33に対応したプローブ針が設けられたプローブカードを用いて行う、「プローブテスト」がある。このプローブ針を介してパッドパターン33に電気的信号を印加し、また、パッドパターン33から得られる信号を検知することにより、半導体装置の電気的特性を確認することができる。このテスト結果により、半導体装置(集積回路)の良否を判断することができる。

【0088】

次いで、必要に応じて、ヒューズ素子のプログラミングを行う。例えば、配線(M1またはM2)と同層において、同じ導電性部材で形成されたヒューズ素子(図示せず)が設けられる。このヒューズ素子上の層間絶縁膜(ID1、ID2)や保護絶縁膜(21、23)をエッチングにより薄膜化する。この後、切断対象のヒューズ素子に対し、例えば、レーザーなどの高エネルギー線を照射することによりヒューズ素子を切断する。このように、ヒューズ素子の切断の有無によるプログラミングを行うことにより、例えば、上記プローブテストの結果に基づく欠陥の救済(冗長救済)や、半導体装置の仕様(周波数や対応電圧)に対応した回路の切り替えなどを行うことができる。

【0089】

上記プローブテスト工程やヒューズプログラミング工程においても、本実施の形態においては、半導体基板1の歪みが低減されているため、半導体基板1の固定(例えば、吸着固定)や搬送のエラーが低減される。

【0090】

[実装工程]

次いで、半導体基板(ウエハ)1を切断(ダイシング)して複数の半導体チップに分離(個片化)する。なお、ダイシングの前に、半導体基板(ウエハ)1の裏面研削を行い、半導体基板1を薄膜化してもよい。次いで、配線基板(実装基板)上に半導体チップを搭載(接着)する(ダイボンディング)。この配線基板のチップ搭載面側には外部接続端子(外部端子、端子)が形成されている。次いで、半導体チップ上のパッドパターン33と、配線基板に形成されている外部接続端子とを、金線などからなるワイヤ(導線、導電性部材)Wで接続する(ワイヤボンディング)。

【0091】

その後、必要に応じて、半導体チップやワイヤを覆うように封止樹脂(モールド樹脂)などで封止する。

【0092】

なお、本実施の形態においては、パッドパターン33をNi膜33aとAu膜33bとの積層膜で構成したが、Ni膜33aを省略してもよい。即ち、フォトレジスト膜PR2の内部、言い換えれば、パッドパターン形成領域OA2のNi膜31b上(その表面のみならず、側面も含む)に、直接、Au膜33bを電解メッキ法により形成してもよい。

【0093】

但し、Au膜33bの下層にNi膜33aを設け、連続して電解メッキ処理を行った方が、Au膜33bとNi膜33aとの密着性が向上し、Au膜33bの剥離を低減することができる。

【0094】

また、パッドパターン33を電解メッキ法を用いて形成したが、無電解メッキ法を用いて形成してもよい。但し、Au膜33bの膜厚が比較的大きい場合には、電解メッキ法を用いて好適である。

【0095】

(実施の形態2)

実施の形態1においては、再配線31の端部上にパッドパターン33を設け、パッドパターン33と配線基板などの外部接続端子とをワイヤWで接続したが(図1参照)、再配線31の端部上にバンプ電極BPを設け(図13参照)、このバンプ電極BPと配線基板などの外部接続端子とを接続してもよい。

【0096】

以下、図面を参照しながら本実施の形態の半導体装置の構成と製造方法について詳細に説明する。図13は、本実施の形態の半導体装置の構成を示す要部断面図である。図14〜図23は、本実施の形態の半導体装置の製造工程を示す要部断面図である。

【0097】

[構造説明]

まず、図13を参照しながら本実施の形態の半導体装置の特徴的な構成について説明する。

【0098】

図13に示すように、本実施の形態の半導体装置においても、実施の形態1の場合と同様に、半導体基板(基板)1上に形成された半導体素子として、例えばpチャネル型MISFETQpおよびnチャネル型MISFETQnを有する。かかるMISFETの他、他の素子、例えば、容量素子、抵抗素子やメモリセルなど、種々の素子を有していてもよい。これらMISFET上には、層間絶縁膜ID1が配置されている。また、上記MISFETのソース・ドレイン領域(3n、3p)上には、プラグP1を介して第1層配線M1が配置されている。

【0099】

この第1層配線M1上には、複数の配線層(第2層配線M2〜第4層配線M4)が配置されている。各配線層間は、プラグP2〜プラグP4により電気的に接続され、それ以外の領域は層間絶縁膜ID2〜ID4により電気的に絶縁されている。第1層配線M1〜第4層配線M4は、Cuを主成分とする導電性膜よりなるCu配線であり、いわゆるダマシン(damascene)配線である。

【0100】

最上層配線である第5層配線M5は、Alを主成分とする導電性膜よりなるAl配線である。なお、第1層配線M1〜第4層配線M4をAl配線としてもよい。

【0101】

この第5層配線(最上層配線)M5上には保護絶縁膜(21、23、24、絶縁膜)が形成され、保護絶縁膜の開口部(ここでは、第3の保護絶縁膜24の開口部)OA1から第5層配線(Al膜)M5が露出している。

【0102】

この露出部(開口部OA1、第1パッド領域)から保護絶縁膜(21、23、24)上に再配線31が配置されている。この再配線31は、上記露出部(開口部OA1、第1パッド領域)を半導体基板(半導体チップ)上の所望の領域まで引き回す役割を果たす。このように、再配線31を用い、再配線31の端部をパッド領域(開口部OA2、第2パッド領域)Pdとすることで、配線基板などの外部接続端子と半導体基板(半導体チップ)との電気的接続を容易に図ることができる。

【0103】

この再配線31は、銅膜(Cuを主成分とする導電性膜)31aと、ニッケル膜(Niを主成分とする導電性膜)31bとの積層膜よりなる。Cu膜31aは、下層のシード層である銅薄膜よりメッキ成長された膜であり、Cu膜31aの下層にはCuシード層(図13においては図示せず。図23参照)が配置されている。また、シード層の下部には、バリア膜(図13においては図示せず。図23参照)が配置されている。なお、Ni膜31bは、上記Cu膜31a上にメッキ成長された膜である。なお、以降、シード層(シード膜)27をCuシード層27ということがある。また、このCuシード層および上記バリア膜も導電性を有するため、再配線31に含まれると考えることができる。

【0104】

また、上記再配線31(Ni膜31b)上には表面保護絶縁膜(41、絶縁膜)が配置され、表面保護絶縁膜41の開口部OA2から再配線31が露出している。この開口部OA2内には、Au膜(図13においては、図示せず、図23参照)が形成されている。この開口部OA2が、パッド領域Pdとなる。このパッド領域Pd上には、バンプ電極(突起電極)BPが配置され、このバンプ電極BPを介して後述する配線基板などの外部接続端子と半導体装置との電気的接続が図られる。

【0105】

ここで、本実施の形態の半導体装置の特徴的な構成として、再配線31を構成するNi膜31bの表面のうち、開口部OA2以外の領域に、Niの不動態化膜35が配置されている。言い換えれば、Ni膜31bと表面保護絶縁膜(41、絶縁膜)とに挟まれた領域に、Niの不動態化膜35が配置されている。

【0106】

このように、Niの不動態化膜35を配置することで、Ni膜31bの耐食性が高まる。また、後述の製造工程で詳細に説明するように、Cuシード層27をエッチングする際のNi膜31bの膜減りを低減することができる。よって、Ni膜31bをあらかじめ薄く形成することができ、下層の配線や素子(MISFET)等に加わる応力を低減することができる。

【0107】

[製造方法説明]

次いで、図13〜図23を参照しながら、本実施の形態の半導体装置の製造工程を説明するとともに、当該半導体装置の構成をより明確にする。

【0108】

まず、図13に示すような半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の上方に複数の配線(M1〜M5)が形成された半導体基板1を準備する。

【0109】

[Qn、Qp形成工程]

半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の形成方法に制限はないが、例えば、実施の形態1で説明した工程により、nチャネル型MISFETQnおよびpチャネル型MISFETQpを形成することができる(図13、図1参照)。

【0110】

[M1〜M4形成工程]

複数の配線(M1〜M4)の形成方法に制限はないが、例えば、以下に示す工程により、これらを形成することができる(図13参照)。

【0111】

まず、前述の図13に示すnチャネル型MISFETQnおよびpチャネル型MISFETQp上に、絶縁膜として例えば酸化シリコン膜をCVD法で堆積する。その後、必要に応じて、酸化シリコン膜の表面を化学的機械研磨法で研磨してその表面を平坦化することによって層間絶縁膜ID1aを形成する。

【0112】

次いで、層間絶縁膜ID1aをエッチングすることにより、ソース・ドレイン領域3n、3p上に、それぞれコンタクトホール(接続孔)を形成する。次いで、コンタクトホール内を含む層間絶縁膜ID1a上に、導電性膜として例えば、W膜をCVD法で堆積し、このW膜を層間絶縁膜ID1aが露出するまでCMP法により研磨することによって、コンタクトホール内に導電性膜を埋め込む。この工程により、プラグ(接続部、コンタクトプラグ)P1が形成される。なお、W膜の下層に、例えばTiN膜、Ti膜等の単層膜又はこれらの積層膜からなるバリア膜を設けてもよい。

【0113】

次いで、層間絶縁膜ID1aおよびプラグP1上に、絶縁膜として例えば窒化シリコン膜および酸化シリコン膜をCVD法により順次堆積し、これらの積層膜から成る配線溝用絶縁膜ID1bを形成する。なお、窒化シリコン膜は、エッチングストッパー膜となる。また、上記層間絶縁膜ID1aと配線溝用絶縁膜ID1bとを併せて層間絶縁膜ID1と言うことがある(ID2〜ID4についても同様である)。

【0114】

次いで、配線溝用絶縁膜ID1bをエッチングすることにより配線溝を形成する。次いで、配線溝内を含む配線溝用絶縁膜ID1b上に、例えば窒化チタンからなるバリア膜(図示せず)をスパッタ法により堆積し、さらに、バリア膜上に、電解メッキ用のCuシード層(図示せず)として例えば銅の薄膜をスパッタ法もしくはCVD法で形成する。次いで、Cuシード層上に、導電性膜として例えば銅膜を電解メッキ法により形成する。

【0115】

次いで、配線溝以外の銅膜およびバリア膜をCMP法により除去することにより第1層配線M1を形成する。このように、配線溝の内部に導電性膜を埋め込む方法をダマシン法といい、特に、プラグと配線とを別工程で形成する方法をシングルダマシン法と言う。また、後述する第2層配線M2〜第4層配線M4のように、コンタクトホールおよび配線溝内に同時に導電性膜を埋め込むことにより、一度にプラグと配線とを形成する方法をデュアルダマシン法と言う。

【0116】

次いで、デュアルダマシン法を用いて第2層配線M2〜第4層配線M4を形成する。まず、第1層配線M1および配線溝用絶縁膜ID1b上に、例えば絶縁膜として窒化シリコン膜、酸化シリコン膜、窒化シリコン膜および酸化シリコン膜を順次CVD法により堆積することにより層間絶縁膜ID2を形成する。これらの膜のうち、下層の窒化シリコン膜は、第1層配線M1を構成する銅の拡散を防止する機能を有する。また、この下層の窒化シリコン膜は、後述するコンタクトホールを形成する際のエッチングストッパーとして、また、上層の窒化シリコン膜は、後述する配線溝を形成する際のエッチングストッパーとして利用される。

【0117】

次いで、層間絶縁膜ID2のうち、上から2層の絶縁膜である酸化シリコン膜および窒化シリコン膜の積層膜ID2bをエッチングすることにより、配線溝を形成する。次いで、配線溝内を含む層間絶縁膜ID2上に、第1フォトレジスト膜(図示せず)を堆積し、エッチバックすることにより配線溝を第1フォトレジスト膜で埋め込む。さらに、第1フォトレジスト膜上に後述するプラグP2の形成領域が開口した第2フォトレジスト膜(図示せず)を形成し、この第2フォトレジスト膜をマスクに、第1フォトレジスト膜と、下から2層の酸化シリコン膜および窒化シリコン膜の積層膜ID2aを、エッチングすることにより、コンタクトホールを形成する。

【0118】

なお、ここでは、配線溝を形成した後、コンタクトホールを形成したが、プラグP2の形成領域の層間絶縁膜ID2(4層の膜、ID2aおよびID2b)をエッチングすることによりコンタクトホールを形成した後、上から2層の絶縁膜である酸化シリコン膜および窒化シリコン膜の積層膜ID2bをエッチングすることにより、配線溝を形成してもよい。

【0119】

次いで、上記コンタクトホールおよび配線溝内を含む層間絶縁膜ID2上に、例えば窒化チタンからなるバリア膜(図示せず)をスパッタ法により堆積し、さらに、バリア膜上に、電解メッキ用のCuシード層(図示せず)として例えば銅の薄膜をスパッタ法もしくはCVD法で形成する。次いで、Cuシード層上に、導電性膜として例えば銅膜を電解メッキ法により形成する。

【0120】

次いで、配線溝以外の銅膜およびバリア膜をCMP法により除去することによりプラグP2および第2層配線M2を形成する。

【0121】

次いで、層間絶縁膜ID2(ID2a、ID2b)、プラグP2および第2層配線M2と同様に、層間絶縁膜ID3(ID3a、ID3b)、プラグP3および第3層配線M3を形成する。さらに、層間絶縁膜ID2(ID2a、ID2b)、プラグP2および第2層配線M2と同様に、層間絶縁膜ID4(ID4a、ID4b)、プラグP4および第4層配線M4を形成する。

【0122】

次いで、第4層配線M4上に、層間絶縁膜ID5を、例えば、層間絶縁膜ID1aと同様に形成し、この層間絶縁膜ID5中にプラグP5をプラグP1と同様に形成する。さらに、層間絶縁膜ID5およびプラグP5上に、第5層配線(Al配線)M5を形成する。

【0123】

例えば、層間絶縁膜ID5およびプラグP5上に、バリア膜(図示せず)として、例えば、TiN膜をスパッタリング法などで成膜し、次いで、バリア膜上に、Al膜をスパッタリング法により成膜し、さらに、Al膜上に、反射防止膜(図示せず)としてTiN膜をスパッタリング法などにより形成する。

【0124】

次いで、バリア膜、Al膜および反射防止膜の積層膜をパターニングすることにより、第5層配線M5を形成する。なお、上記コンタクトホールを形成後、コンタクトホール内を含む層間絶縁膜ID5上に、上記積層膜を形成した後、パターニングすることにより、プラグP5と第5層配線M5を同時に形成してもよい。上記工程により、Alを主成分とする第5層配線M5が形成される。なお、TiN膜は、導電性を有するため、TiN膜/Al膜/TiN膜の積層膜を第5層配線M5として扱ってもよい。

【0125】

[保護絶縁膜、再配線およびパッドパターン形成工程等]

次いで、第5層配線M5上に保護絶縁膜(21、23、24、絶縁膜)および再配線31等を形成する。この工程を、図14〜図23を参照しながら説明する。図14〜図23においては、図1に示す半導体装置の最上層配線(ここでは、第5層配線M5)および再配線31の開口部OA1の近傍の領域を詳細に示してある。なお図14〜図23においては、図面を見やすくするため、第5層配線M5を、図13に示す第5層配線M5より短く表示してある。

【0126】

まず、図14に示すように、第5層配線M5および層間絶縁膜ID5上に、第1の保護絶縁膜21として、例えば、酸化シリコン膜および窒化シリコン膜の積層膜を形成する。例えば、酸化シリコン膜をCVD法などで堆積した後、酸化シリコン膜の上部に窒化シリコン膜をCVD法などで堆積することにより、上記積層膜を形成することができる。

【0127】

次いで、第1の保護絶縁膜21をパターニングすることにより開口部OA1aを形成する。なお、開口部OA1aに位置する反射防止膜もエッチングすることが好ましい。よって、この開口部OA1aからは、第5層配線M5を構成するAl膜が露出する。

【0128】

次いで、開口部OA1a上を含む第1の保護絶縁膜21上に、第2の保護絶縁膜23として、例えば、感光性ポリイミド膜を塗布する。次いで、感光性ポリイミド膜を、露光・現像することにより開口部OA1aを含む領域の感光性ポリイミド膜を除去する。この工程により、開口部OA1aから第5層配線(Al膜)M5が再び露出する。

【0129】

次いで、図15に示すように、開口部OA1a上を含む第1および第2の保護絶縁膜(21、23)上に、第3の保護絶縁膜24として、例えば、感光性ポリイミド膜を塗布する。次いで、感光性ポリイミド膜を、露光・現像することにより開口部OA1a内の感光性ポリイミド膜を除去することにより、開口部OA1を形成する。この工程により、開口部OA1から第5層配線(Al膜)M5が再び露出する。次いで、熱処理(キュア処理)を施すことにより、感光性ポリイミド膜(23、24)を硬化させる。なお、上記工程においては、開口部OA1aをOA1より大きく形成したが、開口部OA1aを開口部OA1と同程度に形成してもよい。即ち、保護絶縁膜(21、23、24)の所望の領域が開口され第5層配線(Al膜)M5が露出する構成となればよい。この所望の領域(図15においては、開口部OA1)が、第5層配線(Al膜)M5と再配線31との接続部(接続領域)となる。

【0130】

次いで、図16に示すように、上記開口部OA1上を含む第3の保護絶縁膜24上に、例えばCr膜またはTi/TiN/Tiの積層膜(Ti系の膜)からなるバリア膜25をスパッタリング法などにより堆積し、さらに、バリア膜25上に、電解メッキ用のCuシード層27として銅の薄膜(銅膜)をスパッタリング法などで形成する。

【0131】

次いで、図17に示すように、Cuシード層27上にフォトレジスト膜PR1を塗布し、フォトレジスト膜PR1を、露光・現像することにより再配線形成領域A31のフォトレジスト膜PR1を除去する。この再配線形成領域A31は、開口部OA1を含む領域である。

【0132】

次いで、図18に示すように、残存するフォトレジスト膜(マスク膜)PR1の内部、即ち、再配線形成領域A31のCuシード層27上に、Cu膜(銅膜)31aを電解メッキ法により形成する。次いで、上記フォトレジスト膜PR1の内部、即ち、再配線形成領域A31のCu膜31a上に、Ni膜(ニッケル膜)31bを電解メッキ法により形成する。Cu膜31aの膜厚は、例えば、4〜7μm程度である。また、Ni膜31bの膜厚は、2〜4μm程度である。

【0133】

Cuは低抵抗であり、Cu膜31aを再配線31に用いて好適である。また、Ni膜31bをCu膜31a上に形成することで、Cu膜31aを保護でき、Cu膜31aの耐食性を向上することができる。また、Cu膜31aのエレクトロマイグレーションを低減することができる。

【0134】

次いで、図19に示すように、フォトレジスト膜PR1を除去する。その結果、再配線形成領域A31において、Ni膜31bの上面と、Cu膜31aおよびNi膜31bの側面とが露出し、再配線形成領域A31以外の領域において、Cuシード層27が露出する。

【0135】

次いで、図20に示すように、再配線31を構成するNi膜31bに対し、不動態化処理を施す。例えば、半導体基板1をアンモニアと過酸化水素水とを含有する処理液(アンモニア過水)に浸漬し、Ni膜31bと処理液とを接触させることにより、Ni膜31bの露出面において不動態化反応(酸化反応)を生じさせ、Niの不動態化膜35を形成する。これにより、Ni膜31bの上面と側面に、Niの不動態化膜35が形成される。この際、処理液を室温(25℃)以上に加熱する、より好ましくは50℃以上に加熱すれば、不動態化反応を促進させることができ好適である。

【0136】

不動態化処理のための処理液としては、アンモニア過水以外の過水(過酸化水素水を含有する処理液)を用いても良い。他の過水として、硫酸過水(硫酸と過酸化水素水とを含有する処理液)を用いてもよい。但し、硫酸過水は、Cu膜(31a)をエッチングし得るため、アンモニア過水を用いる方がより好ましい。

【0137】

また、不動態化処理として、プラズマ酸化法を用いてもよい。即ち、酸化性雰囲気(例えば、酸素を含有する雰囲気)中でプラズマを生じさせ、その内部に半導体基板1を配置し、酸素プラズマ(酸素ラジカル)とNi膜31bとを反応させることにより、Ni膜31bの露出面に、Niの不動態化膜35を形成してもよい。

【0138】

次いで、図21に示すように、ウエットエッチングにより、再配線形成領域A31以外の領域のCuシード層(Cu膜)27とバリア膜(Cr膜)25とを順次除去する。

【0139】

Cuシード層27のエッチングは、例えば、硫酸過水(硫酸と過酸化水素水とを含有する溶液)または硝酸過水(硝酸と過酸化水素水とを含有する溶液)を含有するエッチング液を用いて行われる。次いで、Cuシード層27を除去した後、バリア膜(Cr膜)25を、例えば、過マンガン酸カリウムを含有する溶液を用いてエッチングする。なお、バリア膜として上記Ti系の膜(TiN膜またはTi膜よりなる単層膜又はこれらの積層膜)を用いた場合には、アンモニア過水によりエッチングすることができる。

【0140】

ここで、上記Cuシード層27のエッチング液としては、硫酸過水または硝酸過水が使用され、Cuのみならず、Niも溶解してしまう。このようにCuのエッチング液はNiも溶解してしまうものが多い。しかしながら、本実施の形態おいては、Ni膜31bの表面に、Niの不動態化膜35が形成されているため、Ni膜31bのエッチング(膜減り)を防止することができる。

【0141】

その結果、次の効果を奏する。

【0142】

(1)Ni膜31bのエッチングを防止することで、Ni膜31bを当初から薄く成膜することができ、コストを抑えることができる。

【0143】

(2)Ni膜31bの膜減りを考慮して、Ni膜31bを厚く形成した場合、当該膜の応力(膜応力)が大きくなり、半導体基板1に歪みが生じる。その結果、Ni膜31bの成膜から上記Cuシード層27のエッチング工程までの間の、露光工程などの処理工程や、処理装置間の搬送工程などにおいて、半導体基板1の固定や搬送にエラーが生じる。その結果、製造工程のスループットが低下する。また、歪みが大きい場合には、不良となり、製造歩留まりが低下する。また、下層の半導体素子(例えば、Qn、Qpなど)の特性の劣化や、配線(例えば、M1〜M5)の断線などにも繋がり得る。これに対し、本実施の形態においては、上記のとおり、Ni膜31bをあらかじめ薄く成膜することができるため、上記不具合を回避することができる。

【0144】

また、エッチングばらつきなどを考慮して、膜減り量を多めに設定する場合においては、Cuシード層27のエッチング工程の後において残存するNi膜の膜厚も所望の膜厚より大きくなる。その結果として、以降の工程においても、膜応力が大きい状態が継続する。よって、以降の工程、例えば、後述するプローブテスト工程やレーザー救済工程(ヒューズプログラミング工程)において、半導体基板1の固定(例えば、吸着固定)や搬送にエラーが生じ得る。このような場合も、製造工程のスループットが低下する。

【0145】

これに対し、本実施の形態においては、Ni膜31bの膜厚を最適化することが可能であり、製造工程のスループットを向上させることができ、また、Ni膜31bの膜応力を低減することにより、半導体装置の特性を向上させることができる。

【0146】

(3)また、再配線31を構成するNi膜31bの側面にもNiの不動態化膜35が形成されているため、Ni膜31bのサイドエッチングを低減することができる。即ち、Niの不動態化膜35が形成されていない場合には、再配線31のNi膜31bの側面が硫酸過水または硝酸過水に晒されるため、上記側面からNi膜のエッチング(侵食)が進行する。かかるNi膜31bのサイドエッチングが進行すると、下層のCu膜31aのサイドエッチングも促進され得る。実施の形態1のパッドパターン(33)と比較し再配線31のパターン面積は大きいため、上記Ni膜31bおよびCu膜31aのサイドエッチングによる問題は小さいものの、配線の低抵抗化や、配線幅の微細化などに対応するためには、上記サイドエッチングの量は少ない方が好ましい。このように、本実施の形態においては、Ni膜31bのサイドエッチングを低減でき、また、Cu膜31aのサイドエッチングを低減できる(なお、当該効果は実施の形態1においても同様である)。

【0147】

次いで、再配線形成領域A31以外の領域のCuシード層(Cu膜)27とバリア膜(Cr膜)25とを除去した後、図21に示すように、Niの不動態化膜35上を含む第3の保護絶縁膜24上に、表面保護絶縁膜41として、例えば、感光性ポリイミド膜を塗布する。次いで、感光性ポリイミド膜を、露光・現像することにより感光性ポリイミド膜を選択的に除去することにより、開口部OA2を形成する。この開口部OA2は、再配線31の上部に位置し、パッド領域Pdと対応する。

【0148】

次いで、図22に示すように、表面保護絶縁膜41の開口部OA2から露出したNiの不動態化膜35を除去する。Niの不動態化膜35の除去は、還元性雰囲気におけるプラズマ処理により行うことができる。例えば、水素(H2)を含有する雰囲気中で、プラズマを生じさせ、水素プラズマ(水素ラジカル)とNiの不動態化膜(Niの酸化膜)35とを反応させることにより、Niの不動態化膜35を還元する。これにより、Niの不動態化膜35が除去され、表面保護絶縁膜41の開口部OA2からNi膜31bが露出する。上記水素雰囲気中でのプラズマ処理(水素プラズマ処理)に代えて、アンモニアプラズマ処理を行ってもよい。この場合、アンモニア(NH3)を含有する雰囲気中で、プラズマを生じさせ、水素ラジカルや窒化水素ラジカルとNiの不動態化膜(Niの酸化膜)35とを反応させる。

【0149】

次いで、図23に示すように、表面保護絶縁膜41の開口部OA2の内部のNi膜31b上に、Au膜33bを無電解メッキ法(置換メッキ法)により形成する。Au膜33bの膜厚は、10〜200nm程度である。このAu膜33bの表面が、パッド領域(バンプ電極形成領域)Pdとなる。

【0150】

この後、パッド領域Pdに、バンプ電極BPを形成する。例えば、Au膜33b(パッド領域Pd)上に、半田ボールをフラックスなどで仮固定し、半田リフロー処理(リフロー処理、熱処理)を行って半田を溶融、再固化することで、パッド領域Pd上に、半田よりなるバンプ電極BPを形成する。半田ボールの代わりに印刷法などにより半田ペーストをパッド領域Pd上に供給して、固化することにより半田よりなるバンプ電極BPを形成してもよい。また、半田よりなるバンプ電極BPの形成の際には、比較的薄い上記Au膜33bは、半田の内部に溶け込み、最終構造としてAu膜33bが認識できなくなる場合がある(図1参照)。

【0151】

[実装工程]

次いで、必要に応じて、プローブテストおよびヒューズプログラミング工程を行った後、半導体基板(ウエハ)1を切断(ダイシング)して複数の半導体チップに分離(個片化)する。なお、ダイシングの前に、半導体基板(ウエハ)1の裏面研削を行い、半導体基板1を薄膜化してもよい。次いで、配線基板上に半導体チップを搭載する。この配線基板のチップ搭載面側には外部接続端子(外部端子、端子)が形成されている。よって、搭載に際しては、半導体チップのバンプ電極BPと配線基板の外部接続端子とを位置合わせして搭載する(フェイスダウンボンディング)。次いで、バンプ電極BPを加熱リフローした後、半導体チップと配線基板との間を樹脂などで固定する。

【0152】

なお、本実施の形態においては、再配線形成領域A31内に開口部OA2を配置し、開口部OA2内部にAu膜33bを形成したが、開口部OA2を再配線31の端部領域より大きくしてもよい。図24は、本実施の形態の半導体装置の他の構成を示す要部断面図である。

【0153】

例えば、実施の形態1の図8に示すように、再配線31の端部領域の外周を含む領域を開口部OA2とし、その内部にAu膜33bを形成してもよい。その結果、図24に示すように、Au膜33bが、再配線31の端部領域の上面のみならず、その側面を覆うように配置されるため、再配線31とAu膜33bの接触面積が大きくなり、Au膜33bの剥がれを低減することができる。

【0154】

(実施の形態3)

実施の形態2においては、Cu膜31aおよびNi膜31bの積層膜よりなる再配線31の端部上にバンプ電極BPを形成したが、最上層配線である第5層配線M5の開口部OA1の直上にバンプ電極BPを形成してもよい。この際、バンプ電極BPの下層に、パッドパターン30として、Cu膜30aおよびNi膜30bの積層膜を配置してもよい。

【0155】

以下、図面を参照しながら本実施の形態の半導体装置の構成と製造方法について詳細に説明する。図25〜図30は、本実施の形態の半導体装置の製造工程を示す要部断面図である。

【0156】

[構造説明]

まず、本実施の形態の半導体装置の製造工程を示す要部断面図の最終工程図である図30を参照しながら本実施の形態の半導体装置の特徴的な構成について説明する。本実施の形態においては、実施の形態2と比較して、実施の形態2の再配線31に代えて、パッドパターン30を配置している点で相違するが、他の構成は、実施の形態2と同様であるため、パッドパターン30の構成について詳細に説明する。

【0157】

本実施の形態の半導体装置においても、実施の形態2と同様に、半導体基板(基板)1上に形成された半導体素子として、例えばpチャネル型MISFETQpおよびnチャネル型MISFETQnを有する(図13参照)。かかるMISFETの他、他の素子、例えば、容量素子、抵抗素子やメモリセルなど、種々の素子を有していてもよい。

【0158】

これらMISFET上には、層間絶縁膜ID1が配置されている。また、上記MISFETのソース・ドレイン領域(3n、3p)上には、プラグP1を介して第1層配線M1が配置されている。

【0159】

さらに、本実施の形態の半導体装置においても、実施の形態2と同様に、第1層配線M1上には、複数の配線層(第2層配線M2〜第4層配線M4)が形成されている。各配線層間は、プラグP2〜プラグP4により電気的に接続され、それ以外の領域は層間絶縁膜ID2〜ID4により電気的に絶縁されている。

【0160】

第1層配線M1〜第4層配線M4は、Cuを主成分とする導電性膜よりなるCu配線であり、いわゆるダマシン配線である。最上層配線である第5層配線M5は、Alを主成分とする導電性膜よりなるAl配線である。なお、第1層配線M1〜第4層配線M4をAl配線としてもよい。

【0161】

この第5層配線(最上層配線)M5上には保護絶縁膜(21、23、24、絶縁膜)が形成され、保護絶縁膜の開口部(ここでは、第3の保護絶縁膜24の開口部)OA1から第5層配線(Al膜)M5が露出している。

【0162】

この露出部(開口部OA1、第1パッド領域)より一回り大きく、その外周が保護絶縁膜(21、23、24)上にかかるように、パッドパターン30が配置されている。パッドパターン30は、銅膜(Cuを主成分とする導電性膜)30aと、ニッケル膜(Niを主成分とする導電性膜)30bとの積層膜よりなる。Cu膜30aは、下層のシード層である銅薄膜よりメッキ成長された膜であり、Cu膜31aの下層にはシード層27が配置されている。また、Cuシード層27の下部には、バリア膜25が配置されている。なお、Ni膜30bは、上記Cu膜30a上にメッキ成長された膜である。また、上記シード層27および上記バリア膜25も導電性を有するため、パッドパターン30に含まれると考えることができる。

【0163】

また、上記パッドパターン30(Ni膜30b)上には表面保護絶縁膜(41、絶縁膜)が形成され、表面保護絶縁膜41の開口部OA2からパッドパターン30が露出している。この開口部OA2内には、Au膜33bが配置されている。この開口部OA2が、パッド領域Pdとなる。パッド領域Pd上には、バンプ電極BPが配置され、このバンプ電極BPを介して後述する配線基板などの外部接続端子と半導体装置の電気的接続が図られる。

【0164】

ここで、本実施の形態の半導体装置の特徴的な構成として、パッドパターン30を構成するNi膜30bの表面のうち、開口部OA2以外の領域に、Niの不動態化膜35が配置されている。言い換えれば、Ni膜30bと表面保護絶縁膜(41、絶縁膜)とに挟まれた領域に、Niの不動態化膜35が配置されている。

【0165】

このように、Niの不動態化膜35を配置することで、Ni膜30bの耐食性が高まる。また、後述の製造工程で詳細に説明するように、Cuシード層27をエッチングする際のNi膜30bの膜減りを低減することができる。

【0166】

[製造方法説明]

次いで、図25〜図30を参照しながら、本実施の形態の半導体装置の製造工程を説明するとともに、当該半導体装置の構成をより明確にする。

【0167】

まず、実施の形態2と同様に、半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の上方に複数の配線(M1〜M5)が形成された半導体基板1を準備する。半導体素子(nチャネル型MISFETQnおよびpチャネル型MISFETQp)の形成工程および第1層配線M1〜第5層配線M5の形成工程は、実施の形態2と同様であるためその説明を省略する。

【0168】

[保護絶縁膜、再配線およびパッドパターン形成工程等]

図25に示すように、第5層配線M5の形成後、第1の保護絶縁膜21、第2の保護絶縁膜23および第3の保護絶縁膜24を形成する。これら保護絶縁膜(21、23、24)の積層膜は、開口部OA1を有し、開口部OA1から第5層配線(Al膜)M5が露出している。保護絶縁膜(21、23、24)および開口部OA1は、実施の形態2と同様の工程で形成することができる。

【0169】

次いで、上記開口部OA1上を含む第3の保護絶縁膜24上に、例えばCr膜またはTi/TiN/Tiの積層膜(Ti系の膜)からなるバリア膜25をスパッタリング法などにより堆積し、さらに、バリア膜25上に、電解メッキ用のCuシード層27として銅の薄膜(銅膜)をスパッタリング法などで形成する。

【0170】

次いで、Cuシード層27上にフォトレジスト膜PR1を塗布し、フォトレジスト膜PR1を、露光・現像することによりパッドパターン形成領域A30のフォトレジスト膜PR1を除去する。このパッドパターン形成領域A30は、開口部OA1を含む領域である。

【0171】

次いで、図26に示すように、残存するフォトレジスト膜(マスク膜)PR1の内部、即ち、パッドパターン形成領域A30のCuシード層27上に、Cu膜(銅膜)30aを電解メッキ法により形成する。次いで、上記フォトレジスト膜PR1の内部、即ち、パッドパターン形成領域A30のCu膜30a上に、Ni膜(ニッケル膜)30bを電解メッキ法により形成する。Cu膜30aの膜厚は、例えば、4〜7μm程度である。また、Ni膜30bの膜厚は、2〜4μm程度である。

【0172】

Cuは低抵抗であり、Cu膜30aをパッドパターン30に用いて好適である。また、Ni膜30bをCu膜30a上に形成することで、Cu膜30aを保護でき、Cu膜30aの耐食性を向上することができる。

【0173】

次いで、図27に示すように、フォトレジスト膜PR1を除去する。その結果、パッドパターン形成領域A30において、Ni膜30bの表面と、Cu膜30aおよびNi膜30bの側面とが露出し、パッドパターン形成領域A30以外の領域において、Cuシード層27が露出する。

【0174】

次いで、パッドパターン30を構成するNi膜30bに対し、実施の形態2と同様の処理を施し、Niの不動態化膜35を形成する。

【0175】

次いで、図28に示すように、実施の形態2と同様のウエットエッチングにより、パッドパターン形成領域A30以外の領域のCuシード層27とバリア膜(Cr膜)25とを順次除去する。

【0176】

ここで、上記Cuの薄膜よりなるCuシード層27のエッチング液としては、実施の形態2で詳細に説明したように、硫酸過水または硝酸過水が使用され、Cuのみならず、Niも溶解してしまう。しかしながら、本実施の形態おいては、Ni膜30bの表面および側面に、Niの不動態化膜35が形成されているため、Ni膜30bのエッチング(膜減り)を防止することができる。

【0177】

その結果、次の効果を奏する。

【0178】

(1)Ni膜30bのエッチングを防止することで、Ni膜30bを当初から薄く成膜することができ、コストを抑えることができる。

【0179】

(2)Ni膜30bの膜減りを考慮して、Ni膜30bを厚く形成した場合、実施の形態2で説明したように、当該膜の応力が大きくなるのに対し、膜応力を低減でき、搬送エラーなどの低減や、半導体装置の特性を向上させることができる。

【0180】

(3)また、パッドパターン30の側面にもNiの不動態化膜35が形成されているため、Ni膜30bのサイドエッチングを低減することができる。即ち、Niの不動態化膜35が形成されていない場合には、パッドパターン30のNi膜30bの側面が硫酸過水または硝酸過水に晒されるため、上記側面からNi膜30bのエッチング(侵食)が進行する。この侵食部が基点となりパッドパターン30が剥がれやすくなる。特に、パッドパターン30は、パターン面積が小さいため剥がれやすい。これに対し、本実施の形態においては、Ni膜30bのサイドエッチングを低減することができ、パッドパターン30の剥がれを低減することができる。

【0181】

次いで、パッドパターン形成領域A30以外の領域のCuシード層27とバリア膜(Cr膜)25とを除去した後、図29に示すように、Niの不動態化膜35上を含む第3の保護絶縁膜24上に、表面保護絶縁膜41として、例えば、感光性ポリイミド膜を塗布する。次いで、感光性ポリイミド膜を、露光・現像することにより感光性ポリイミド膜を選択的に除去することにより、開口部OA2を形成する。この開口部OA2は、パッドパターン30の上部に位置し、パッド領域(Pd)と対応する。

【0182】

次いで、開口部OA2から露出したNiの不動態化膜35を除去する。不動態化膜35の除去は、実施の形態2で説明した還元性雰囲気におけるプラズマ処理により行うことができる。

【0183】

次いで、図30に示すように、開口部OA2の内部のNi膜31b上に、Au膜33bを無電解メッキ法(置換メッキ法)により形成する。Au膜33bの膜厚は、10〜200nm程度である。このAu膜33bの表面が、パッド領域(バンプ電極形成領域)Pdとなる。

【0184】

この後、図示は省略するが、実施の形態2と同様に、パッド領域Pdに、バンプ電極BPを形成する。例えば、Au膜33b(パッド領域Pd)上に、半田ボールをフラックスなどで仮固定し、半田リフロー処理(リフロー処理、熱処理)を行って半田を溶融、再固化することで、パッド領域Pd上に、半田よりなるバンプ電極BPを形成する(図13参照)。

【0185】

[実装工程]

次いで、必要に応じて、プローブテストおよびヒューズプログラミング工程を行った後、実施の形態2と同様に、半導体基板(ウエハ)1を切断し、配線基板上にフェイスダウンボンディングする。

【0186】

以上、本発明者によってなされた発明をその実施の形態1〜3に基づき具体的に説明したが、本発明は上記実施の形態1〜3に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0187】

例えば、実施の形態1では2層の配線層(M1、M2)を、実施の形態2および3では、5層の配線層(M1〜M5)を形成したが、配線層の数に制限はなく、また、配線を構成する導電性材料も適宜変更可能である。

【産業上の利用可能性】

【0188】

本発明は、半導体装置の製造方法および半導体装置に関し、特に、Cu−Ni配線を有する半導体装置の製造方法、およびCu−Ni配線を有する半導体装置の構成に適用して好適なものである。

【符号の説明】

【0189】

1 半導体基板

2 素子分離領域

3n ソース・ドレイン領域

3p ソース・ドレイン領域

21 第1の保護絶縁膜

23 第2の保護絶縁膜

24 第3の保護絶縁膜

25 バリア膜

27 シード層(Cuシード層)

30 パッドパターン

30a Cu膜

30b Ni膜

31 再配線

31a Cu膜

31b Ni膜

33 パッドパターン

33a Ni膜

33b Au膜、

35 Niの不動態化膜

41 表面保護絶縁膜

A30 パッドパターン形成領域

A31 再配線形成領域

A33 パッドパターン形成領域

BP バンプ電極

G ゲート電極

ID1 層間絶縁膜

ID1a 層間絶縁膜

ID1b 配線溝用絶縁膜

ID2 層間絶縁膜

ID2a 積層膜

ID2b 積層膜

ID3(ID3a、ID3b) 層間絶縁膜

ID4(ID4a、ID4b) 層間絶縁膜

ID5 層間絶縁膜

L 長さ

L1 長さ

M1 第1層配線

M2 第2層配線

M3 第3層配線

M4 第4層配線

M5 第5層配線

OA1 開口部

OA1a 開口部

OA2 開口部(パッドパターン形成領域)

P1 プラグ

P2 プラグ

P3 プラグ

P4 プラグ

P5 プラグ

PR1 フォトレジスト膜

PR2 フォトレジスト膜

Pd パッド領域

Qn nチャネル型MISFET

Qp pチャネル型MISFET

W ワイヤ

W1 幅

α 幅

【特許請求の範囲】

【請求項1】

(a)基板の上方に導電性膜よりなる第1配線を形成する工程と、

(b)前記第1配線上に、前記第1配線の第1領域を露出する第1絶縁膜を形成する工程と、

(c)前記第1配線の前記第1領域から前記第1絶縁膜上に延在する第2配線を形成する工程であって、

(c1)前記第1領域および前記第1絶縁膜上に銅を主成分とする第1銅膜を形成する工程と、

(c2)前記第1銅膜上に、前記第2配線の形成領域を開口した第1マスク膜を形成する工程と、

(c3)前記第2配線の形成領域の前記第1銅膜上に、メッキ成長により銅を主成分とする第2銅膜を形成する工程と、

(c4)前記第2銅膜上に、ニッケルを主成分とする第1ニッケル膜を形成する工程と、

により、前記第1銅膜、前記第2銅膜および前記ニッケル膜よりなる前記第2配線を形成する工程と、

(d)前記第2配線上のパッド領域に金を主成分とする金膜を形成する工程と、

(e)前記(d)工程の後、前記第1マスク膜を除去し、前記第1ニッケル膜に不動態化処理を施すことにより、前記第1ニッケル膜の表面にニッケルの不動態化膜を形成する工程と、

(f)前記(e)工程の後、前記第1銅膜をエッチングする工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記(c)工程と、前記(d)工程との間に、

(g)工程であって、

(g1)前記第1ニッケル膜および前記第1マスク膜上に、前記第2配線上に位置する前記パッド領域を開口した第2マスク膜を形成する工程と、

(g2)前記パッド領域に、メッキ成長によりニッケルを主成分とする第2ニッケル膜を形成する工程と、を有し、

前記(d)工程は、前記第2ニッケル膜上に、前記金膜を形成する工程であり、

前記(e)工程は、前記(d)工程の後、前記第1マスク膜および前記第2マスク膜を除去し、前記第1ニッケル膜および前記第2ニッケル膜に不動態化処理を施すことにより、前記第1ニッケル膜の表面および前記第2ニッケル膜の側面にニッケルの不動態化膜を形成する工程である、

ことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記パッド領域は、前記第2配線の端部およびその外周を含む領域であることを特徴とする請求項2記載の半導体装置の製造方法。

【請求項4】

前記(e)工程の不動態化処理は、前記第1ニッケル膜と、過酸化水素水を含有する処理液とを接触させて行われることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項5】

前記処理液は、アンモニアと前記過酸化水素水とを含有する処理液であることを特徴とする請求項4記載の半導体装置の製造方法。

【請求項6】

前記処理液は、25℃以上に加熱して用いられることを特徴とする請求項5記載の半導体装置の製造方法。

【請求項7】

前記(e)工程の不動態化処理は、前記第1ニッケル膜を酸化性雰囲気中でプラズマ処理することにより行われることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項8】

前記(f)工程のエッチングは、硫酸と過酸化水素水とを含有する液または硝酸と過酸化水素水とを含有する液を用いて行われることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項9】

前記(c1)工程は、前記第1領域および前記第1絶縁膜上に、バリア膜を形成した後、前記バリア膜上に、前記第1銅膜を形成する工程であることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項10】

前記バリア膜は、クロムを主成分とするクロム膜、もしくは、チタンと主成分とするチタン膜を有することを特徴とする請求項9記載の半導体装置の製造方法。

【請求項11】

前記第1配線は、アルミニウムを主成分とするアルミニウム膜を有する配線であることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項12】

(h)前記パッド領域の金膜と、実装基板の外部端子とを導線を介して接続する工程を有することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項13】

(a)基板の上方に第1導電性膜を形成する工程と、

(b)前記第1導電性膜上に、前記第1導電性膜の第1領域を露出する第1絶縁膜を形成する工程と、

(c)前記第1導電性膜の第1領域および前記第1絶縁膜上に位置する第2導電性膜を形成する工程であって、

(c1)前記第1領域および前記第1絶縁膜上に銅を主成分とする第1銅膜を形成する工程と、

(c2)前記第1銅膜上に、前記第2導電性膜の形成領域を開口した第1マスク膜を形成する工程と、

(c3)前記第2導電性膜の形成領域の前記第1銅膜上に、メッキ成長により銅を主成分とする第2銅膜を形成する工程と、

(c4)前記第2銅膜上に、ニッケルを主成分とするニッケル膜を形成する工程と、

により、前記第1銅膜、前記第2銅膜および前記ニッケル膜よりなる前記第2導電性膜を形成する工程と、

(d)前記(c)工程の後、前記第1マスク膜を除去し、前記ニッケル膜に不動態化処理を施すことにより、前記ニッケル膜の表面にニッケルの不動態化膜を形成する工程と、