半導体装置の製造方法および半導体装置

【目的】配線間のコンタクト配置において配線間距離をより小さく形成する。

【構成】実施形態の半導体装置は、第1と第2の配線と、第1の絶縁膜と、第2の絶縁膜と、第1のコンタクトと、第2のコンタクトと、を備えている。第1と第2の配線は、基板上に互いに並行するように形成される。第1の絶縁膜は、第1と第2の配線を覆うように形成される。第2の絶縁膜は、第1と第2の制御ゲート線間の所定位置で第1と第2の配線と並行して延びるように形成され、第1の絶縁膜と材料が異なる。第1のコンタクトは、第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成される。第2のコンタクトは、前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成される。

【構成】実施形態の半導体装置は、第1と第2の配線と、第1の絶縁膜と、第2の絶縁膜と、第1のコンタクトと、第2のコンタクトと、を備えている。第1と第2の配線は、基板上に互いに並行するように形成される。第1の絶縁膜は、第1と第2の配線を覆うように形成される。第2の絶縁膜は、第1と第2の制御ゲート線間の所定位置で第1と第2の配線と並行して延びるように形成され、第1の絶縁膜と材料が異なる。第1のコンタクトは、第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成される。第2のコンタクトは、前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法および半導体装置に関する。

【背景技術】

【0002】

半導体装置、特に、半導体記憶装置の開発において、大容量化等を達成すべく、チップサイズの縮小化が進められている。例えば、NAND型フラッシュメモリ装置等のフローティングゲート構造を搭載した半導体記憶装置において、メモリセル部のピッチサイズの縮小化が進められてきた。従来、チップサイズ縮小のために、かかるメモリセル部のピッチサイズの縮小を重要視していたが、昨今のさらなる縮小の要望に対して、これを実現するためには今後は隣り合うブロック同士で向かい合うセレクトゲート(配線)間の縮小も欠かすことのできない項目となってくる。よって、セレクトゲート間に配置されるビットラインコンタクトに関して、隣り合うセレクトゲート間のピッチサイズの縮小が望まれている。ビットライン間のピッチの縮小については、例えば、ビットラインコンタクト形成用のホールをセレクトゲートに沿って千鳥状に交互に配置することでビットライン間のピッチの縮小を図る方法が検討されている。

【0003】

しかしながら、千鳥配置のようにセレクトゲート間の幅寸法方向にずらして配置するビットラインコンタクトでは、セレクトゲート間の幅サイズ方向に対して実質的にホールが複数配置されることになる。そのため、セレクトゲート間の幅が拡大してしまう。例えば、千鳥配置のビットラインコンタクトにおいて、セレクトゲート間を縮小させる為には、コンタクトホール径の縮小或いはコンタクトホール間(背合わせ)距離の縮小が必要となる。

【0004】

しかしながら、コンタクトホール径の縮小及びコンタクトホール間の縮小はリソグラフィにとって非常に困難になる。なぜなら、ホール径を小さくしすぎると未開口のホールが発生し、コンタクトできないといった問題が発生するからである。また、ホール間距離を縮小させるとホール同士が近づきすぎて開口部の位置が重なってしまい、コンタクト同士がショートしてしまうといった問題が発生してしまう。上述したように、チップサイズ縮小にはホール径縮小又はホール間距離を縮小させることが重要であるが、すでに解像限界ギリギリでパターニングしているため、上記記載のように未開口や開口部の重なりなどの問題点を考えると、リソグラフィ技術でこれ以上のサイズ縮小は非常に困難になっている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−313970号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の実施形態は、上述した問題点を克服し、配線間のコンタクト配置において配線間距離をより小さく形成することが可能な半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

実施形態の半導体装置は、第1と第2の配線と、第1の絶縁膜と、第2の絶縁膜と、第1のコンタクトと、第2のコンタクトと、を備えている。第1と第2の配線は、基板上に互いに並行するように形成される。第1の絶縁膜は、前記第1と第2の配線を覆うように形成される。第2の絶縁膜は、前記第1と第2の制御ゲート線間の所定位置で前記第1と第2の配線と並行して延びるように形成され、第1の絶縁膜と材料が異なる。第1のコンタクトは、前記第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成される。第2のコンタクトは、前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成される。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。

【図2】第1の実施形態における半導体装置の製造方法を示す工程断面図である。

【図3】第1の実施形態におけるゲートとアクティブエリアの配置構成の一例を示す上面図である。

【図4】第1の実施形態における半導体装置の製造方法を示す工程断面図である。

【図5】第1の実施形態における半導体装置の製造方法を示す工程断面図である。

【図6】第1の実施形態における半導体装置の製造方法を示す上面図および工程断面図である。

【図7】第1の実施形態における半導体装置の製造方法を示す工程断面図である。

【図8】第1の実施形態における半導体装置の製造方法を示す工程断面図である。

【図9】第1の実施形態におけるビットラインコンタクトが形成された半導体装置の一例とその比較例とを示す上面図である。

【図10】第2の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。

【図11】第2の実施形態における半導体装置の製造方法を示す工程断面図である。

【図12】第2の実施形態における半導体装置の製造方法を示す工程断面図である。

【図13】第3の実施形態における半導体装置の製造方法の一工程断面を示す図である。

【図14】第3の実施形態におけるビットラインコンタクトが形成された半導体装置の一例を示す上面図である。

【発明を実施するための形態】

【0009】

(第1の実施形態)

第1の実施形態では、半導体装置の一例として、不揮発性のNAND型フラッシュメモリ装置の製造方法について説明する。第1の実施形態について、以下、図面を用いて説明する。

【0010】

図1は、第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャートである。図1において、第1の実施形態における半導体装置の製造方法では、素子分離工程を含むゲート形成工程(S102)と、イオン注入工程(S104)と、コンフォーマル絶縁膜A形成工程(S106)と、絶縁膜B形成工程(S112)と、研磨工程(S114)と、アモルファスシリコン(a−Si)膜形成工程(S116)と、レジストパターン形成工程(S118)と、ハードマスク形成工程(S120)と、ホール形成工程(S122)と、導電性材料埋め込み工程(S124)と、研磨工程(S126)といった一連の工程を実施する。

【0011】

図2では、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図2では、図1のゲート形成工程(S102)からイオン注入工程(S104)までを示している。それ以降の工程は後述する。

【0012】

図2(a)において、ゲート形成工程(S102)として、半導体基板200上に、まず、絶縁膜210を例えば2〜20nmの膜厚で形成する。絶縁膜210は、トンネル絶縁膜として機能する。形成方法は、例えば、酸素雰囲気中での加熱処理(熱酸化処理)により形成すると好適である。絶縁膜210として、例えば、酸化シリコン(SiO2)膜が用いられる。また、半導体基板200として、例えば、直径300ミリのシリコンウェハからなるp型シリコン基板が用いられる。

【0013】

そして、絶縁膜210上に、例えば、CVD法を用いて、ポリシリコン膜220を例えば50nmの膜厚で形成する。ポリシリコン膜220は、電荷蓄積層(FG:フローティングゲート)として機能する。そして、その後、ポリシリコン膜220上から半導体基板200の途中まで溝状の複数の開口部を形成し、かかる開口部を絶縁膜で埋め込むことで図示しない素子分離を行う。

【0014】

次に、ポリシリコン膜220上に、例えば、CVD法を用いて、絶縁膜230を例えば2〜20nmの膜厚で形成する。絶縁膜230は、電極間絶縁膜として機能する。

【0015】

そして、絶縁膜230上に、例えば、CVD法を用いて、ポリシリコン膜240を例えば50nmの膜厚で形成する。ポリシリコン膜240は、制御電極(GC:制御ゲート)の一部として機能する。また、ポリシリコン膜240上に、例えば、CVD法を用いて、金属膜250を例えば50nmの膜厚で形成する。金属膜250は、制御電極(GC:制御ゲート)の残りの一部として機能する。すなわち、制御電極は、ポリシリコン膜240と金属膜250とが積層されてなる積層構造を有する。ポリシリコン膜240と金属膜250との積層膜は、NAND型フラッシュメモリ装置におけるメモリ素子においてはワード線(配線の一例)として、セレクトゲートにおいてはセレクトゲート線(配線の一例)として機能する。

【0016】

図2(b)において、図示しないリソグラフィ工程とドライエッチング工程でゲート部分の両側に溝構造である開口部160,162,164を金属膜250とポリシリコン膜240と絶縁膜230とポリシリコン膜220内に形成する。図示していないレジスト塗布工程、露光工程等のリソグラフィ工程を経て金属膜250の上にレジスト膜が形成された半導体基板200に対し、露出した金属膜250とその下層に位置するポリシリコン膜240と絶縁膜230とポリシリコン膜220を異方性エッチング法により除去することで、半導体基板200の表面に対し、略垂直に開口部160,162,164を形成することができる。例えば、一例として、反応性イオンエッチング法により開口部160,162,164を形成すればよい。言い換えれば、ゲート領域に金属膜250とポリシリコン膜240と絶縁膜230とポリシリコン膜220とが残る(存在する)ように、エッチングにより、金属膜250とポリシリコン膜240と絶縁膜230とポリシリコン膜220とを貫通する開口部160,162,164を形成する。開口部164を介して並ぶ金属膜250とポリシリコン膜240と絶縁膜230とポリシリコン膜220との積層膜の1つずつがNAND型フラッシュメモリの各セルと対応する。例えば、幅25nmの開口部154をピッチ50nmで形成する。その結果、ゲート部分と開口部164との幅寸法が共に25nmずつとなる1:1のゲート11a,11b・・・を形成できる。また、1つのブロックを構成するゲート11a,11b・・・の端部には、セレクトゲート21を形成できる。また、隣り合うブロックにも、同様に、1:1のゲート13a,13b・・・を形成できる。また、かかるブロックを構成するゲート13a,13b・・・の端部には、セレクトゲート23を形成できる。ブロック間では、開口部160の間隔を有しながらセレクトゲート21,23が互いに並行するように形成される。

【0017】

次に、イオン注入工程(S104)として、各ゲート部分の両側の領域であって、p型の半導体基板200表面にn型不純物をイオン注入して、n型半導体領域を形成する。かかるn型半導体領域は、ソース・ドレイン領域として機能する。また、n型半導体領域に挟まれたp型半導体領域は、上部にゲート領域が形成されるチャネル領域として機能する。よって、開口部160,162,164の底面の絶縁膜210が露出した領域が、ソース部分或いはドレイン部分となる。ここでは、隣り合うセルの一方のソース部分と他方のドレイン部分とを共有する複数のセルが直列接続されたNANDストリング構造が形成される。

【0018】

図3は、第1の実施の形態におけるゲートとアクティブエリアの配置構成の一例を示す上面図である。図3では、セレクトゲート21のセレクトゲート線20(第1の配線)より左側にブロックAが、セレクトゲート23のセレクトゲート線22(第2の配線)より右側にブロックBが形成される。このように、基板上には、セレクトゲート線20,22が互いに並行するように形成される。

【0019】

ブロックAには、各ページのワード線10a,10b・・・が形成される。同様に、ブロックBには、各ページのワード線12a,12b・・・が形成される。なお、1つのブロック内で同じワード線に接続される複数のメモリセルにより1つのページが構成される。すなわち、ワード線10aには、図面の奥側に向かって複数のゲート11aが接続され、ワード線10bには、図面の奥側に向かって複数のゲート11bが接続される。ワード線12aには、図面の奥側に向かって複数のゲート13aが接続され、ワード線12bには、図面の奥側に向かって複数のゲート13bが接続される。そして、ワード線に直交する方向に複数のアクティブエリア30(活性領域)がそれぞれ素子分離領域32を挟んで形成される。アクティブエリア30は、各メモリセルのソース部分或いはドレイン部分となる。

【0020】

また、セレクトゲート線20の長手方向には、素子分離領域32を挟んで複数のセレクトゲート21が配置される。同様に、セレクトゲート線22の長手方向には、素子分離領域32を挟んで複数のセレクトゲート23が配置される。そして、セレクトゲート線20,22間に位置する各アクティブエリア30上に例えば1つのビットラインコンタクトが形成されることになる。以下、ビットラインコンタクトの形成プロセスについて説明する。

【0021】

図4には、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図4では、図1のコンフォーマル絶縁膜A形成工程(S106)から研磨工程(S114)までを示している。それ以降の工程は後述する。

【0022】

図4(a)において、コンフォーマル絶縁膜A形成工程(S106)として、トンネル絶縁膜を含む半導体基板202上に、ゲートを含む各ワード線10とセレクトゲートを含むセレクトゲート線20,22とを覆うように、絶縁膜260(絶縁膜A:第1の絶縁膜)をコンフォーマルに形成する。例えば、化学気相成長(CVD)法で形成すればよい。ここでは、セレクトゲート線20とセレクトゲート線22との間の空間が完全に埋め込まれることなく、セレクトゲート線20,22間にスペース151(くぼみ部分)が残るようにコンフォーマルに形成する。スペース151を形成するためには、絶縁膜260の膜厚をセレクトゲート線20,22間距離(開口部160の溝幅)の2分の1以下の膜厚にすることで達成できる。これにより、セレクトゲート線20,22の側面と平行する方向(セレクトゲート線20,22が延びる長手方向)に沿って、溝状のスペース151が形成される。絶縁膜260としては、例えば、SiO2膜が好適である。スペース151の幅としては、例えば、10nm〜100nmが好適である。

【0023】

図4(b)において、絶縁膜B形成工程(S112)として、絶縁膜260をコンフォーマルに形成することによって生じたセレクトゲート線20,22間のスペース151を埋め込むように、絶縁膜260上に絶縁膜260と材料の異なる絶縁膜262(絶縁膜B:第2の絶縁膜)を形成する。例えば、CVD法で形成すればよい。絶縁膜262の材料としては、絶縁膜260の材料に対してエッチング耐性が高い材料を用いるとよい。言い換えれば、絶縁膜260の材料としては、絶縁膜262の材料よりもエッチング加工の選択比が高い材料を用いるとよい。絶縁膜262の材料として、例えば、窒化シリコン窒化(SiN)、或いはアモルファスシリコン(a−Si)等が好適である。ここでは、例えば、SiN膜を形成する。

【0024】

図4(c)において、研磨工程(S114)として、化学機械研磨(CMP)法を用いて、絶縁膜260が露出するまで絶縁膜262を研磨除去する。言い換えれば、スペース151からはみ出た余分な絶縁膜262が研磨除去されるまで絶縁膜262の上面を後退させて、絶縁膜260を露出させる。その際、ゲート上の絶縁層として所望の膜厚に調整すればよい。なお、絶縁膜262の上面を後退させるに当って、ドライエッチング法を用いたエッチバックを行ってもよい。

【0025】

図5には、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図5では、図1のアモルファスシリコン(a−Si)膜形成工程(S116)を示している。それ以降の工程は後述する。

【0026】

図5において、アモルファスシリコン(a−Si)膜形成工程(S116)として、露出した絶縁膜260上およびスペース151に埋め込まれた絶縁膜262上に、コンタクトホール形成のためのハードマスク材となるa−Si膜270を形成する。

【0027】

ここで、絶縁膜262の材料をa−Siにした場合には、a−Si膜270の代わりに、SiN膜とすればよい。

【0028】

図6には、第1の実施形態における半導体装置の製造方法の上面図および工程断面図が示されている。図6では、図1のレジストパターン形成工程(S118)を示している。それ以降の工程は後述する。

【0029】

図6(b)において、レジストパターン形成工程(S118)として、まず、a−Si膜270上にレジスト膜280を形成後、リソグラフィ技術を用いて、セレクトゲート線20,22間に配置されるビットラインコンタクト用の複数のコンタクトホールパターン152,154が開口したレジストパターンを形成する。図6(a)に示すように、ここでは、セレクトゲート線20,22の長手方向に沿って並ぶ複数のアクティブエリア上に千鳥状に複数のコンタクトホールパターン152a,152b,152c,152d,152e,152f,・・・,154a,154b,154c,154d,154e,154f,・・・を形成する。コンタクトホールパターン152は、セレクトゲート線20,22に沿ってかつセレクトゲート線20側に寄せて、アクティブエリアを1つずつ飛ばしながらアクティブエリア上に形成され、コンタクトホールパターン154は、セレクトゲート線20,22に沿ってかつセレクトゲート線22側に寄せて、コンタクトホールパターン152が飛ばしたアクティブエリア上に形成される。すなわち、コンタクトホールパターン152,154は、アクティブエリアを1つおき互いにずらしながらセレクトゲート線20,22に沿ってそれぞれ形成されることで、千鳥配置に形成される。さらに言い換えれば、コンタクトホールパターン152,154は、複数のコンタクトホールパターン154の隣り合う2つのホールパターン間にコンタクトホールパターン152のうちの1つが位置し、複数のコンタクトホールパターン152の隣り合う2つのホールパターン間にコンタクトホールパターン154のうちの1つが位置するように、セレクトゲート線20,22の延びる方向に沿って互いに位置をずらして形成される。

【0030】

なお、コンタクトホールパターン152は、上方から見てコンタクトホールパターン152の一部(ここでは左側の一部)に絶縁膜262が重なる位置にパターニングされる。一方、コンタクトホールパターン154は、上方から見てコンタクトホールパターン154の一部(ここでは右側の一部)に絶縁膜262が重なる位置にパターニングされる。

【0031】

また、ここでは、コンタクトホールパターン152,154として、楕円形のパターンを示しているが、これに限るものではなく、円形でも正方形や長方形といった矩形等でも構わない。もちろん、その他の多角形でもよい。

【0032】

図7には、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図7では、図1のハードマスク形成工程(S120)を示している。それ以降の工程は後述する。

【0033】

図7において、ハードマスク形成工程(S120)として、形成されたレジストパターンをマスクとしてa−Si膜270をエッチングして、a−Si膜270にコンタクトホールパターン152,154を形成する。かかるエッチングによって、a−Si膜270のハードマスクが形成され、このハードマスクに開口したコンタクトホールパターン152,154は底部の径が上面の径よりも細くなるため、コンタクトホール径を小さくできる。よって、リソグラフィの解像限界のパターン径で露光した場合でも、ハードマスクに開口されたコンタクトホール底の径を解像限界の径寸法よりも小さく形成できる。例えば、露光時のパターン径が50〜60nmの場合に、ハードマスクに開口されたコンタクトホール底の径を20nm程度に小さくできる。

【0034】

図8には、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図8では、図1のホール形成工程(S122)から研磨工程(S126)までを示している。

【0035】

図8(a)において、ホール形成工程(S122)として、コンタクトホールパターン152,154が開口したa−Si膜270をハードマスクとして用いたエッチングにより、絶縁膜260に、絶縁膜262におけるセレクトゲート線20側の一方の側面が側壁の一部に含まれるコンタクトホール153(第1のホール)と、絶縁膜262におけるセレクトゲート線22側の他方の側面が側壁の一部に含まれるコンタクトホール155(第2のホール)と、を形成する。ここでは、1つおきのアクティブエリアと対応するようにセレクトゲート線20,22の延びる方向に沿って互いに位置をずらしつつ、複数のコンタクトホール153(第1のホール)と複数のコンタクトホール155(第2のホール)とが、それぞれスペースに残った絶縁膜262に対してセレクトゲート線20(第1の配線)およびセレクトゲート線22(第2の配線)側に形成される。

【0036】

次に、導電性材料埋め込み工程(S124)として、複数のコンタクトホール153と複数のコンタクトホール155とが埋め込まれるように導電性材料を堆積させる。導電性材料として、例えば、ポリシリコン、アルミニウム(Al)、タングステン(W)、或いは銅(Cu)等が好適である。

【0037】

そして、図8(b)に示すように、研磨工程(S126)として、各コンタクトホール153,155からはみ出た余分な導電性材料をCMP法により研磨除去することで、千鳥配置されたビットラインコンタクト40(第1のコンタクト)とビットラインコンタクト42(第2のコンタクト)が形成される。また、絶縁膜262は、ビットラインコンタクト40,42と接触する箇所以外の箇所で底面と両側面で絶縁膜260と接触することになる。そして、以降の図示しないプロセスにおいて、各ビットラインコンタクト40,42上にそれぞれ図示しないビットラインを形成すればよい。

【0038】

図9は、第1の実施形態におけるビットラインコンタクトが形成された半導体装置の一例とその比較例とを示す上面図である。図9(b)では、第1の実施形態におけるビットラインコンタクトを形成した場合を示している。第1の実施形態では、セレクトゲート線20,22間における絶縁膜を通して貫通するように形成されたビットラインコンタクト40が、絶縁膜262の両側面のうちの一方(ここでは、右側面)に接触する。また、セレクトゲート線20,22間における絶縁膜を通して貫通するように形成されたビットラインコンタクト42が、絶縁膜262の両側面のうちの他方(ここでは、左側面)に接触する。さらに、セレクトゲート線20,22の延びる方向に沿ってビットラインコンタクト40,42間で互いに位置をずらして配置される。

【0039】

一方、図9(a)では、絶縁膜262を間に挟まずに、千鳥配置でビットラインコンタクト用のコンタクトホールのパターニングを行ってビットラインコンタクトを形成した場合を示している。絶縁膜262を間に挟まずに、千鳥配置でコンタクトホールのパターニングを行う場合、実際背合わせの距離を近づけすぎると背合わせ距離のバラツキや、コンタクトホール間の重なりが発生してリソマージンの低下が起こる。そのため、図9(a)に示すように、隣り合うビットラインコンタクト44,46間距離D(背合わせ距離)を大きくしなければならない。例えば、かかる問題を回避する為60nm程度の背合わせ距離が必要となってくる。また、ビットラインコンタクト44,46間距離Dを小さくするためホール径を小さくすると未開口のホールが形成されコンタクトができなくなってしまう場合もある。その結果、セレクトゲート線間距離L1が大きくなってしまう。

【0040】

これに対して、第1の実施形態では、図9(b)に示すように、セレクトゲート線20,22間の所定位置に配置された絶縁膜262を間に挟んで、その両側にそれぞれ絶縁膜262と一部が重なるようにコンタクトホールのパターニングを行うことで、開口されない絶縁膜262がホールの分離膜として機能し、コンタクトホール同士を限りなく近づけても隣り合うコンタクトホール同士の重なりを防止できる。各コンタクトホールが絶縁膜262の両側にはみ出すようにパターニングされなければよい。これにより、ビットラインコンタクト40,42間距離を小さくできる。よって、最終的に形成されるビットラインコンタクト40,42間距離は絶縁膜262の幅まで小さくできる。例えば、10nm程度にすることができる。また、絶縁膜262によって、コンタクトホールパターンの開口面積の一部が塞がれるため、実際に形成されるホール径を小さくすることもできる。その結果、セレクトゲート線20,22間距離L2を小さくできる。すなわち、セレクトゲート間幅を狭くできる。

なお、ここでは、絶縁膜262の両側でビットラインコンタクト40,42ともに絶縁膜262と接触する場合を示したが、例えばコンタクトホールのパターニングの際の合わせずれなどにより、ビットラインコンタクト40,42の少なくとも一方が絶縁膜262とは離隔して形成されてもよい。すなわち、セレクトゲート線20,22間において絶縁膜を通して形成されるビットラインコンタクト40,42は、絶縁膜262の両側にはみ出すことなく絶縁膜262に対してそれぞれセレクトゲート線20,22側にセレクトゲート線20,22と接触しないように位置させればよく、絶縁膜262とは接触してもしなくてもよい。

【0041】

以上のように、第1の実施形態によれば、ゲート間のコンタクト配置においてゲート間距離をより小さく形成できる。よって、チップサイズの縮小化ができる。その結果、解像限界以下のパターンのビットラインコンタクトが望まれる場合でもホール径やホール間の距離を広げることなく、パターンを形成することが可能である。

【0042】

(第2の実施形態)

第1の実施形態では、コンフォーマルに絶縁膜260を形成することで、セレクトゲート線20,22間にスペース151を形成したが、スペースの形成の手法はこれに限るものではない。

【0043】

図10は、第2の実施形態における半導体装置の製造方法の要部工程を示すフローチャートである。図10において、第2の実施形態における半導体装置の製造方法では、コンフォーマル絶縁膜A形成工程(S106)の代わりに、絶縁膜A形成工程(S108)と開口部形成工程(S110)とを追加した点以外は、図1と同様である。また、以下、特に説明する点以外の内容は、第1の実施形態と同様である。

【0044】

素子分離工程を含むゲート形成工程(S102)からイオン注入工程(S104)までは、第1の実施形態と同様である。

【0045】

図11には、第2の実施形態における半導体装置の製造方法の工程断面図が示されている。図11では、図10の絶縁膜A形成工程(S108)から絶縁膜B形成工程(S112)までを示している。

【0046】

図11(a)において、絶縁膜A形成工程(S108)として、トンネル絶縁膜を含む半導体基板202上に、ゲートを含む各ワード線10とセレクトゲートを含むセレクトゲート線20,22とを覆うように、絶縁膜260(第1の絶縁膜)を形成する。例えば、化学気相成長(CVD)法で形成すればよい。ここでは、セレクトゲート線20とセレクトゲート線22との間が埋め込まれるように絶縁膜260を形成する。絶縁膜260としては、例えば、SiO2膜が好適である。

【0047】

図11(b)において、開口部形成工程(S110)として、図示しないリソグラフィ法とエッチング法により、セレクトゲート線20,22間の位置で絶縁膜260に溝状のスペース161(溝、或いは開口部の一例)を形成する。ここでは、セレクトゲート線20,22の延びる方向(長手方向)と並行する溝を開口する。ここでは、絶縁膜260を貫通しているが、貫通させずに途中までに留めておいても構わない。スペース161の幅としては、例えば、10nm〜100nmが好適である。

【0048】

図11(c)において、絶縁膜B形成工程(S112)として、絶縁膜260のスペース161を埋め込むように、絶縁膜260上に絶縁膜262(第2の絶縁膜)を形成する。

【0049】

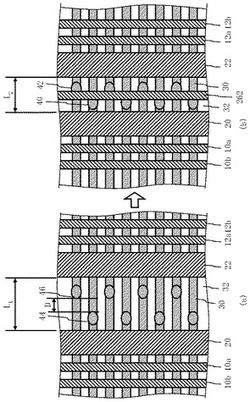

図12には、第2の実施形態における半導体装置の製造方法の工程断面図が示されている。図12では、図10の研磨工程(S114)から研磨工程(S126)までを示している。

【0050】

そして、第1の実施形態と同様、図12(a)に示すように、研磨工程(S114)として絶縁膜260が露出するまで絶縁膜262を研磨除去し、以下、第1の実施形態と同様の各工程を行って、図12(b)に示すように、千鳥配置されたビットラインコンタクト40(第1のコンタクト)とビットラインコンタクト42(第2のコンタクト)が形成される。

【0051】

以上のように、第2の実施形態のように、エッチングにより絶縁膜262を埋め込むためのスペース161を形成しても、第1の実施形態と同様の効果を発揮できる。また、リソグラフィ法とエッチング法を用いることで、スペース161の幅を調整し易くできる。

【0052】

(第3の実施形態)

上述した実施形態では、ビットライン方向に対して2か所の配置位置をアクティブエリア毎に順に交互に配置する2段の千鳥配置でコンタクトホールを形成したが、これに限るものではない。ビットライン方向に対してnか所(n>2)の配置位置をアクティブエリア毎に順にずらしながら配置することを繰り返してコンタクトホールを形成してもよい。第3の実施形態における半導体装置の製造方法は、以下の点を除いて上述した第2の実施形態と同様である。

【0053】

図13は、第3の実施形態における半導体装置の製造方法の一工程断面を示す図12(a)相当図である。図13において、セレクトゲート線20,22間には、絶縁膜262がセレクトゲート線20,22の延びる方向(長手方向)に並行して複数箇所に配置される。これを実現するために、開口部形成工程(S110)において、セレクトゲート線20,22間の絶縁膜260にスペース161を形成する際に、複数のスペースを形成する。そして、絶縁膜B形成工程(S112)において、絶縁膜260の各スペース161を埋め込むように、絶縁膜260上に絶縁膜262を形成する。

【0054】

図14は、第3の実施形態におけるビットラインコンタクトが形成された半導体装置の一例を示す上面図である。図14では、一例として、3段の配置位置をアクティブエリア毎に順にずらしながら配置することを繰り返す複数のコンタクトホールを開口して、ビットラインコンタクト40,42,44を形成した例を示している。nか所(n>2)の配置位置にずらす場合には、配置位置数よりも1つ少ない数の分離膜を形成すればよく、ここでは、分離膜として、絶縁膜262a,262bを形成している。

【0055】

以上のように、ビットライン方向に対してnか所(n>2)の配置位置をアクティブエリア毎に順にずらしながら配置することを繰り返して複数のコンタクトホールを形成する場合でも、第3の実施形態によれば、ゲート間のコンタクト配置においてコンタクト間距離を小さくでき、その結果、ゲート間距離をより小さく形成できる。よって、チップサイズの縮小化ができる。

【0056】

以上、具体例を参照しつつ実施形態について説明した。しかし、本発明は、これらの具体例に限定されるものではない。

【0057】

また、各膜の膜厚や、開口部のサイズ、形状、数などについても、半導体集積回路や各種の半導体素子において必要とされるものを適宜選択して用いることができる。

【0058】

その他、本発明の要素を具備し、当業者が適宜設計変更しうる全ての半導体装置および半導体装置の製造方法は、本発明の範囲に包含される。

【0059】

また、説明の簡便化のために、半導体産業で通常用いられる手法、例えば、フォトリソグラフィプロセス、処理前後のクリーニング等は省略しているが、それらの手法が含まれ得ることは言うまでもない。

【符号の説明】

【0060】

20,22 セレクトゲート線、21,23 セレクトゲート、40,42,44 ビットラインコンタクト、151,161 スペース、153,155 コンタクトホール、260,262 絶縁膜

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法および半導体装置に関する。

【背景技術】

【0002】

半導体装置、特に、半導体記憶装置の開発において、大容量化等を達成すべく、チップサイズの縮小化が進められている。例えば、NAND型フラッシュメモリ装置等のフローティングゲート構造を搭載した半導体記憶装置において、メモリセル部のピッチサイズの縮小化が進められてきた。従来、チップサイズ縮小のために、かかるメモリセル部のピッチサイズの縮小を重要視していたが、昨今のさらなる縮小の要望に対して、これを実現するためには今後は隣り合うブロック同士で向かい合うセレクトゲート(配線)間の縮小も欠かすことのできない項目となってくる。よって、セレクトゲート間に配置されるビットラインコンタクトに関して、隣り合うセレクトゲート間のピッチサイズの縮小が望まれている。ビットライン間のピッチの縮小については、例えば、ビットラインコンタクト形成用のホールをセレクトゲートに沿って千鳥状に交互に配置することでビットライン間のピッチの縮小を図る方法が検討されている。

【0003】

しかしながら、千鳥配置のようにセレクトゲート間の幅寸法方向にずらして配置するビットラインコンタクトでは、セレクトゲート間の幅サイズ方向に対して実質的にホールが複数配置されることになる。そのため、セレクトゲート間の幅が拡大してしまう。例えば、千鳥配置のビットラインコンタクトにおいて、セレクトゲート間を縮小させる為には、コンタクトホール径の縮小或いはコンタクトホール間(背合わせ)距離の縮小が必要となる。

【0004】

しかしながら、コンタクトホール径の縮小及びコンタクトホール間の縮小はリソグラフィにとって非常に困難になる。なぜなら、ホール径を小さくしすぎると未開口のホールが発生し、コンタクトできないといった問題が発生するからである。また、ホール間距離を縮小させるとホール同士が近づきすぎて開口部の位置が重なってしまい、コンタクト同士がショートしてしまうといった問題が発生してしまう。上述したように、チップサイズ縮小にはホール径縮小又はホール間距離を縮小させることが重要であるが、すでに解像限界ギリギリでパターニングしているため、上記記載のように未開口や開口部の重なりなどの問題点を考えると、リソグラフィ技術でこれ以上のサイズ縮小は非常に困難になっている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−313970号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の実施形態は、上述した問題点を克服し、配線間のコンタクト配置において配線間距離をより小さく形成することが可能な半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

実施形態の半導体装置は、第1と第2の配線と、第1の絶縁膜と、第2の絶縁膜と、第1のコンタクトと、第2のコンタクトと、を備えている。第1と第2の配線は、基板上に互いに並行するように形成される。第1の絶縁膜は、前記第1と第2の配線を覆うように形成される。第2の絶縁膜は、前記第1と第2の制御ゲート線間の所定位置で前記第1と第2の配線と並行して延びるように形成され、第1の絶縁膜と材料が異なる。第1のコンタクトは、前記第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成される。第2のコンタクトは、前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成される。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。

【図2】第1の実施形態における半導体装置の製造方法を示す工程断面図である。

【図3】第1の実施形態におけるゲートとアクティブエリアの配置構成の一例を示す上面図である。

【図4】第1の実施形態における半導体装置の製造方法を示す工程断面図である。

【図5】第1の実施形態における半導体装置の製造方法を示す工程断面図である。

【図6】第1の実施形態における半導体装置の製造方法を示す上面図および工程断面図である。

【図7】第1の実施形態における半導体装置の製造方法を示す工程断面図である。

【図8】第1の実施形態における半導体装置の製造方法を示す工程断面図である。

【図9】第1の実施形態におけるビットラインコンタクトが形成された半導体装置の一例とその比較例とを示す上面図である。

【図10】第2の実施形態における半導体装置の製造方法の要部工程を示すフローチャート図である。

【図11】第2の実施形態における半導体装置の製造方法を示す工程断面図である。

【図12】第2の実施形態における半導体装置の製造方法を示す工程断面図である。

【図13】第3の実施形態における半導体装置の製造方法の一工程断面を示す図である。

【図14】第3の実施形態におけるビットラインコンタクトが形成された半導体装置の一例を示す上面図である。

【発明を実施するための形態】

【0009】

(第1の実施形態)

第1の実施形態では、半導体装置の一例として、不揮発性のNAND型フラッシュメモリ装置の製造方法について説明する。第1の実施形態について、以下、図面を用いて説明する。

【0010】

図1は、第1の実施形態における半導体装置の製造方法の要部工程を示すフローチャートである。図1において、第1の実施形態における半導体装置の製造方法では、素子分離工程を含むゲート形成工程(S102)と、イオン注入工程(S104)と、コンフォーマル絶縁膜A形成工程(S106)と、絶縁膜B形成工程(S112)と、研磨工程(S114)と、アモルファスシリコン(a−Si)膜形成工程(S116)と、レジストパターン形成工程(S118)と、ハードマスク形成工程(S120)と、ホール形成工程(S122)と、導電性材料埋め込み工程(S124)と、研磨工程(S126)といった一連の工程を実施する。

【0011】

図2では、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図2では、図1のゲート形成工程(S102)からイオン注入工程(S104)までを示している。それ以降の工程は後述する。

【0012】

図2(a)において、ゲート形成工程(S102)として、半導体基板200上に、まず、絶縁膜210を例えば2〜20nmの膜厚で形成する。絶縁膜210は、トンネル絶縁膜として機能する。形成方法は、例えば、酸素雰囲気中での加熱処理(熱酸化処理)により形成すると好適である。絶縁膜210として、例えば、酸化シリコン(SiO2)膜が用いられる。また、半導体基板200として、例えば、直径300ミリのシリコンウェハからなるp型シリコン基板が用いられる。

【0013】

そして、絶縁膜210上に、例えば、CVD法を用いて、ポリシリコン膜220を例えば50nmの膜厚で形成する。ポリシリコン膜220は、電荷蓄積層(FG:フローティングゲート)として機能する。そして、その後、ポリシリコン膜220上から半導体基板200の途中まで溝状の複数の開口部を形成し、かかる開口部を絶縁膜で埋め込むことで図示しない素子分離を行う。

【0014】

次に、ポリシリコン膜220上に、例えば、CVD法を用いて、絶縁膜230を例えば2〜20nmの膜厚で形成する。絶縁膜230は、電極間絶縁膜として機能する。

【0015】

そして、絶縁膜230上に、例えば、CVD法を用いて、ポリシリコン膜240を例えば50nmの膜厚で形成する。ポリシリコン膜240は、制御電極(GC:制御ゲート)の一部として機能する。また、ポリシリコン膜240上に、例えば、CVD法を用いて、金属膜250を例えば50nmの膜厚で形成する。金属膜250は、制御電極(GC:制御ゲート)の残りの一部として機能する。すなわち、制御電極は、ポリシリコン膜240と金属膜250とが積層されてなる積層構造を有する。ポリシリコン膜240と金属膜250との積層膜は、NAND型フラッシュメモリ装置におけるメモリ素子においてはワード線(配線の一例)として、セレクトゲートにおいてはセレクトゲート線(配線の一例)として機能する。

【0016】

図2(b)において、図示しないリソグラフィ工程とドライエッチング工程でゲート部分の両側に溝構造である開口部160,162,164を金属膜250とポリシリコン膜240と絶縁膜230とポリシリコン膜220内に形成する。図示していないレジスト塗布工程、露光工程等のリソグラフィ工程を経て金属膜250の上にレジスト膜が形成された半導体基板200に対し、露出した金属膜250とその下層に位置するポリシリコン膜240と絶縁膜230とポリシリコン膜220を異方性エッチング法により除去することで、半導体基板200の表面に対し、略垂直に開口部160,162,164を形成することができる。例えば、一例として、反応性イオンエッチング法により開口部160,162,164を形成すればよい。言い換えれば、ゲート領域に金属膜250とポリシリコン膜240と絶縁膜230とポリシリコン膜220とが残る(存在する)ように、エッチングにより、金属膜250とポリシリコン膜240と絶縁膜230とポリシリコン膜220とを貫通する開口部160,162,164を形成する。開口部164を介して並ぶ金属膜250とポリシリコン膜240と絶縁膜230とポリシリコン膜220との積層膜の1つずつがNAND型フラッシュメモリの各セルと対応する。例えば、幅25nmの開口部154をピッチ50nmで形成する。その結果、ゲート部分と開口部164との幅寸法が共に25nmずつとなる1:1のゲート11a,11b・・・を形成できる。また、1つのブロックを構成するゲート11a,11b・・・の端部には、セレクトゲート21を形成できる。また、隣り合うブロックにも、同様に、1:1のゲート13a,13b・・・を形成できる。また、かかるブロックを構成するゲート13a,13b・・・の端部には、セレクトゲート23を形成できる。ブロック間では、開口部160の間隔を有しながらセレクトゲート21,23が互いに並行するように形成される。

【0017】

次に、イオン注入工程(S104)として、各ゲート部分の両側の領域であって、p型の半導体基板200表面にn型不純物をイオン注入して、n型半導体領域を形成する。かかるn型半導体領域は、ソース・ドレイン領域として機能する。また、n型半導体領域に挟まれたp型半導体領域は、上部にゲート領域が形成されるチャネル領域として機能する。よって、開口部160,162,164の底面の絶縁膜210が露出した領域が、ソース部分或いはドレイン部分となる。ここでは、隣り合うセルの一方のソース部分と他方のドレイン部分とを共有する複数のセルが直列接続されたNANDストリング構造が形成される。

【0018】

図3は、第1の実施の形態におけるゲートとアクティブエリアの配置構成の一例を示す上面図である。図3では、セレクトゲート21のセレクトゲート線20(第1の配線)より左側にブロックAが、セレクトゲート23のセレクトゲート線22(第2の配線)より右側にブロックBが形成される。このように、基板上には、セレクトゲート線20,22が互いに並行するように形成される。

【0019】

ブロックAには、各ページのワード線10a,10b・・・が形成される。同様に、ブロックBには、各ページのワード線12a,12b・・・が形成される。なお、1つのブロック内で同じワード線に接続される複数のメモリセルにより1つのページが構成される。すなわち、ワード線10aには、図面の奥側に向かって複数のゲート11aが接続され、ワード線10bには、図面の奥側に向かって複数のゲート11bが接続される。ワード線12aには、図面の奥側に向かって複数のゲート13aが接続され、ワード線12bには、図面の奥側に向かって複数のゲート13bが接続される。そして、ワード線に直交する方向に複数のアクティブエリア30(活性領域)がそれぞれ素子分離領域32を挟んで形成される。アクティブエリア30は、各メモリセルのソース部分或いはドレイン部分となる。

【0020】

また、セレクトゲート線20の長手方向には、素子分離領域32を挟んで複数のセレクトゲート21が配置される。同様に、セレクトゲート線22の長手方向には、素子分離領域32を挟んで複数のセレクトゲート23が配置される。そして、セレクトゲート線20,22間に位置する各アクティブエリア30上に例えば1つのビットラインコンタクトが形成されることになる。以下、ビットラインコンタクトの形成プロセスについて説明する。

【0021】

図4には、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図4では、図1のコンフォーマル絶縁膜A形成工程(S106)から研磨工程(S114)までを示している。それ以降の工程は後述する。

【0022】

図4(a)において、コンフォーマル絶縁膜A形成工程(S106)として、トンネル絶縁膜を含む半導体基板202上に、ゲートを含む各ワード線10とセレクトゲートを含むセレクトゲート線20,22とを覆うように、絶縁膜260(絶縁膜A:第1の絶縁膜)をコンフォーマルに形成する。例えば、化学気相成長(CVD)法で形成すればよい。ここでは、セレクトゲート線20とセレクトゲート線22との間の空間が完全に埋め込まれることなく、セレクトゲート線20,22間にスペース151(くぼみ部分)が残るようにコンフォーマルに形成する。スペース151を形成するためには、絶縁膜260の膜厚をセレクトゲート線20,22間距離(開口部160の溝幅)の2分の1以下の膜厚にすることで達成できる。これにより、セレクトゲート線20,22の側面と平行する方向(セレクトゲート線20,22が延びる長手方向)に沿って、溝状のスペース151が形成される。絶縁膜260としては、例えば、SiO2膜が好適である。スペース151の幅としては、例えば、10nm〜100nmが好適である。

【0023】

図4(b)において、絶縁膜B形成工程(S112)として、絶縁膜260をコンフォーマルに形成することによって生じたセレクトゲート線20,22間のスペース151を埋め込むように、絶縁膜260上に絶縁膜260と材料の異なる絶縁膜262(絶縁膜B:第2の絶縁膜)を形成する。例えば、CVD法で形成すればよい。絶縁膜262の材料としては、絶縁膜260の材料に対してエッチング耐性が高い材料を用いるとよい。言い換えれば、絶縁膜260の材料としては、絶縁膜262の材料よりもエッチング加工の選択比が高い材料を用いるとよい。絶縁膜262の材料として、例えば、窒化シリコン窒化(SiN)、或いはアモルファスシリコン(a−Si)等が好適である。ここでは、例えば、SiN膜を形成する。

【0024】

図4(c)において、研磨工程(S114)として、化学機械研磨(CMP)法を用いて、絶縁膜260が露出するまで絶縁膜262を研磨除去する。言い換えれば、スペース151からはみ出た余分な絶縁膜262が研磨除去されるまで絶縁膜262の上面を後退させて、絶縁膜260を露出させる。その際、ゲート上の絶縁層として所望の膜厚に調整すればよい。なお、絶縁膜262の上面を後退させるに当って、ドライエッチング法を用いたエッチバックを行ってもよい。

【0025】

図5には、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図5では、図1のアモルファスシリコン(a−Si)膜形成工程(S116)を示している。それ以降の工程は後述する。

【0026】

図5において、アモルファスシリコン(a−Si)膜形成工程(S116)として、露出した絶縁膜260上およびスペース151に埋め込まれた絶縁膜262上に、コンタクトホール形成のためのハードマスク材となるa−Si膜270を形成する。

【0027】

ここで、絶縁膜262の材料をa−Siにした場合には、a−Si膜270の代わりに、SiN膜とすればよい。

【0028】

図6には、第1の実施形態における半導体装置の製造方法の上面図および工程断面図が示されている。図6では、図1のレジストパターン形成工程(S118)を示している。それ以降の工程は後述する。

【0029】

図6(b)において、レジストパターン形成工程(S118)として、まず、a−Si膜270上にレジスト膜280を形成後、リソグラフィ技術を用いて、セレクトゲート線20,22間に配置されるビットラインコンタクト用の複数のコンタクトホールパターン152,154が開口したレジストパターンを形成する。図6(a)に示すように、ここでは、セレクトゲート線20,22の長手方向に沿って並ぶ複数のアクティブエリア上に千鳥状に複数のコンタクトホールパターン152a,152b,152c,152d,152e,152f,・・・,154a,154b,154c,154d,154e,154f,・・・を形成する。コンタクトホールパターン152は、セレクトゲート線20,22に沿ってかつセレクトゲート線20側に寄せて、アクティブエリアを1つずつ飛ばしながらアクティブエリア上に形成され、コンタクトホールパターン154は、セレクトゲート線20,22に沿ってかつセレクトゲート線22側に寄せて、コンタクトホールパターン152が飛ばしたアクティブエリア上に形成される。すなわち、コンタクトホールパターン152,154は、アクティブエリアを1つおき互いにずらしながらセレクトゲート線20,22に沿ってそれぞれ形成されることで、千鳥配置に形成される。さらに言い換えれば、コンタクトホールパターン152,154は、複数のコンタクトホールパターン154の隣り合う2つのホールパターン間にコンタクトホールパターン152のうちの1つが位置し、複数のコンタクトホールパターン152の隣り合う2つのホールパターン間にコンタクトホールパターン154のうちの1つが位置するように、セレクトゲート線20,22の延びる方向に沿って互いに位置をずらして形成される。

【0030】

なお、コンタクトホールパターン152は、上方から見てコンタクトホールパターン152の一部(ここでは左側の一部)に絶縁膜262が重なる位置にパターニングされる。一方、コンタクトホールパターン154は、上方から見てコンタクトホールパターン154の一部(ここでは右側の一部)に絶縁膜262が重なる位置にパターニングされる。

【0031】

また、ここでは、コンタクトホールパターン152,154として、楕円形のパターンを示しているが、これに限るものではなく、円形でも正方形や長方形といった矩形等でも構わない。もちろん、その他の多角形でもよい。

【0032】

図7には、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図7では、図1のハードマスク形成工程(S120)を示している。それ以降の工程は後述する。

【0033】

図7において、ハードマスク形成工程(S120)として、形成されたレジストパターンをマスクとしてa−Si膜270をエッチングして、a−Si膜270にコンタクトホールパターン152,154を形成する。かかるエッチングによって、a−Si膜270のハードマスクが形成され、このハードマスクに開口したコンタクトホールパターン152,154は底部の径が上面の径よりも細くなるため、コンタクトホール径を小さくできる。よって、リソグラフィの解像限界のパターン径で露光した場合でも、ハードマスクに開口されたコンタクトホール底の径を解像限界の径寸法よりも小さく形成できる。例えば、露光時のパターン径が50〜60nmの場合に、ハードマスクに開口されたコンタクトホール底の径を20nm程度に小さくできる。

【0034】

図8には、第1の実施形態における半導体装置の製造方法の工程断面図が示されている。図8では、図1のホール形成工程(S122)から研磨工程(S126)までを示している。

【0035】

図8(a)において、ホール形成工程(S122)として、コンタクトホールパターン152,154が開口したa−Si膜270をハードマスクとして用いたエッチングにより、絶縁膜260に、絶縁膜262におけるセレクトゲート線20側の一方の側面が側壁の一部に含まれるコンタクトホール153(第1のホール)と、絶縁膜262におけるセレクトゲート線22側の他方の側面が側壁の一部に含まれるコンタクトホール155(第2のホール)と、を形成する。ここでは、1つおきのアクティブエリアと対応するようにセレクトゲート線20,22の延びる方向に沿って互いに位置をずらしつつ、複数のコンタクトホール153(第1のホール)と複数のコンタクトホール155(第2のホール)とが、それぞれスペースに残った絶縁膜262に対してセレクトゲート線20(第1の配線)およびセレクトゲート線22(第2の配線)側に形成される。

【0036】

次に、導電性材料埋め込み工程(S124)として、複数のコンタクトホール153と複数のコンタクトホール155とが埋め込まれるように導電性材料を堆積させる。導電性材料として、例えば、ポリシリコン、アルミニウム(Al)、タングステン(W)、或いは銅(Cu)等が好適である。

【0037】

そして、図8(b)に示すように、研磨工程(S126)として、各コンタクトホール153,155からはみ出た余分な導電性材料をCMP法により研磨除去することで、千鳥配置されたビットラインコンタクト40(第1のコンタクト)とビットラインコンタクト42(第2のコンタクト)が形成される。また、絶縁膜262は、ビットラインコンタクト40,42と接触する箇所以外の箇所で底面と両側面で絶縁膜260と接触することになる。そして、以降の図示しないプロセスにおいて、各ビットラインコンタクト40,42上にそれぞれ図示しないビットラインを形成すればよい。

【0038】

図9は、第1の実施形態におけるビットラインコンタクトが形成された半導体装置の一例とその比較例とを示す上面図である。図9(b)では、第1の実施形態におけるビットラインコンタクトを形成した場合を示している。第1の実施形態では、セレクトゲート線20,22間における絶縁膜を通して貫通するように形成されたビットラインコンタクト40が、絶縁膜262の両側面のうちの一方(ここでは、右側面)に接触する。また、セレクトゲート線20,22間における絶縁膜を通して貫通するように形成されたビットラインコンタクト42が、絶縁膜262の両側面のうちの他方(ここでは、左側面)に接触する。さらに、セレクトゲート線20,22の延びる方向に沿ってビットラインコンタクト40,42間で互いに位置をずらして配置される。

【0039】

一方、図9(a)では、絶縁膜262を間に挟まずに、千鳥配置でビットラインコンタクト用のコンタクトホールのパターニングを行ってビットラインコンタクトを形成した場合を示している。絶縁膜262を間に挟まずに、千鳥配置でコンタクトホールのパターニングを行う場合、実際背合わせの距離を近づけすぎると背合わせ距離のバラツキや、コンタクトホール間の重なりが発生してリソマージンの低下が起こる。そのため、図9(a)に示すように、隣り合うビットラインコンタクト44,46間距離D(背合わせ距離)を大きくしなければならない。例えば、かかる問題を回避する為60nm程度の背合わせ距離が必要となってくる。また、ビットラインコンタクト44,46間距離Dを小さくするためホール径を小さくすると未開口のホールが形成されコンタクトができなくなってしまう場合もある。その結果、セレクトゲート線間距離L1が大きくなってしまう。

【0040】

これに対して、第1の実施形態では、図9(b)に示すように、セレクトゲート線20,22間の所定位置に配置された絶縁膜262を間に挟んで、その両側にそれぞれ絶縁膜262と一部が重なるようにコンタクトホールのパターニングを行うことで、開口されない絶縁膜262がホールの分離膜として機能し、コンタクトホール同士を限りなく近づけても隣り合うコンタクトホール同士の重なりを防止できる。各コンタクトホールが絶縁膜262の両側にはみ出すようにパターニングされなければよい。これにより、ビットラインコンタクト40,42間距離を小さくできる。よって、最終的に形成されるビットラインコンタクト40,42間距離は絶縁膜262の幅まで小さくできる。例えば、10nm程度にすることができる。また、絶縁膜262によって、コンタクトホールパターンの開口面積の一部が塞がれるため、実際に形成されるホール径を小さくすることもできる。その結果、セレクトゲート線20,22間距離L2を小さくできる。すなわち、セレクトゲート間幅を狭くできる。

なお、ここでは、絶縁膜262の両側でビットラインコンタクト40,42ともに絶縁膜262と接触する場合を示したが、例えばコンタクトホールのパターニングの際の合わせずれなどにより、ビットラインコンタクト40,42の少なくとも一方が絶縁膜262とは離隔して形成されてもよい。すなわち、セレクトゲート線20,22間において絶縁膜を通して形成されるビットラインコンタクト40,42は、絶縁膜262の両側にはみ出すことなく絶縁膜262に対してそれぞれセレクトゲート線20,22側にセレクトゲート線20,22と接触しないように位置させればよく、絶縁膜262とは接触してもしなくてもよい。

【0041】

以上のように、第1の実施形態によれば、ゲート間のコンタクト配置においてゲート間距離をより小さく形成できる。よって、チップサイズの縮小化ができる。その結果、解像限界以下のパターンのビットラインコンタクトが望まれる場合でもホール径やホール間の距離を広げることなく、パターンを形成することが可能である。

【0042】

(第2の実施形態)

第1の実施形態では、コンフォーマルに絶縁膜260を形成することで、セレクトゲート線20,22間にスペース151を形成したが、スペースの形成の手法はこれに限るものではない。

【0043】

図10は、第2の実施形態における半導体装置の製造方法の要部工程を示すフローチャートである。図10において、第2の実施形態における半導体装置の製造方法では、コンフォーマル絶縁膜A形成工程(S106)の代わりに、絶縁膜A形成工程(S108)と開口部形成工程(S110)とを追加した点以外は、図1と同様である。また、以下、特に説明する点以外の内容は、第1の実施形態と同様である。

【0044】

素子分離工程を含むゲート形成工程(S102)からイオン注入工程(S104)までは、第1の実施形態と同様である。

【0045】

図11には、第2の実施形態における半導体装置の製造方法の工程断面図が示されている。図11では、図10の絶縁膜A形成工程(S108)から絶縁膜B形成工程(S112)までを示している。

【0046】

図11(a)において、絶縁膜A形成工程(S108)として、トンネル絶縁膜を含む半導体基板202上に、ゲートを含む各ワード線10とセレクトゲートを含むセレクトゲート線20,22とを覆うように、絶縁膜260(第1の絶縁膜)を形成する。例えば、化学気相成長(CVD)法で形成すればよい。ここでは、セレクトゲート線20とセレクトゲート線22との間が埋め込まれるように絶縁膜260を形成する。絶縁膜260としては、例えば、SiO2膜が好適である。

【0047】

図11(b)において、開口部形成工程(S110)として、図示しないリソグラフィ法とエッチング法により、セレクトゲート線20,22間の位置で絶縁膜260に溝状のスペース161(溝、或いは開口部の一例)を形成する。ここでは、セレクトゲート線20,22の延びる方向(長手方向)と並行する溝を開口する。ここでは、絶縁膜260を貫通しているが、貫通させずに途中までに留めておいても構わない。スペース161の幅としては、例えば、10nm〜100nmが好適である。

【0048】

図11(c)において、絶縁膜B形成工程(S112)として、絶縁膜260のスペース161を埋め込むように、絶縁膜260上に絶縁膜262(第2の絶縁膜)を形成する。

【0049】

図12には、第2の実施形態における半導体装置の製造方法の工程断面図が示されている。図12では、図10の研磨工程(S114)から研磨工程(S126)までを示している。

【0050】

そして、第1の実施形態と同様、図12(a)に示すように、研磨工程(S114)として絶縁膜260が露出するまで絶縁膜262を研磨除去し、以下、第1の実施形態と同様の各工程を行って、図12(b)に示すように、千鳥配置されたビットラインコンタクト40(第1のコンタクト)とビットラインコンタクト42(第2のコンタクト)が形成される。

【0051】

以上のように、第2の実施形態のように、エッチングにより絶縁膜262を埋め込むためのスペース161を形成しても、第1の実施形態と同様の効果を発揮できる。また、リソグラフィ法とエッチング法を用いることで、スペース161の幅を調整し易くできる。

【0052】

(第3の実施形態)

上述した実施形態では、ビットライン方向に対して2か所の配置位置をアクティブエリア毎に順に交互に配置する2段の千鳥配置でコンタクトホールを形成したが、これに限るものではない。ビットライン方向に対してnか所(n>2)の配置位置をアクティブエリア毎に順にずらしながら配置することを繰り返してコンタクトホールを形成してもよい。第3の実施形態における半導体装置の製造方法は、以下の点を除いて上述した第2の実施形態と同様である。

【0053】

図13は、第3の実施形態における半導体装置の製造方法の一工程断面を示す図12(a)相当図である。図13において、セレクトゲート線20,22間には、絶縁膜262がセレクトゲート線20,22の延びる方向(長手方向)に並行して複数箇所に配置される。これを実現するために、開口部形成工程(S110)において、セレクトゲート線20,22間の絶縁膜260にスペース161を形成する際に、複数のスペースを形成する。そして、絶縁膜B形成工程(S112)において、絶縁膜260の各スペース161を埋め込むように、絶縁膜260上に絶縁膜262を形成する。

【0054】

図14は、第3の実施形態におけるビットラインコンタクトが形成された半導体装置の一例を示す上面図である。図14では、一例として、3段の配置位置をアクティブエリア毎に順にずらしながら配置することを繰り返す複数のコンタクトホールを開口して、ビットラインコンタクト40,42,44を形成した例を示している。nか所(n>2)の配置位置にずらす場合には、配置位置数よりも1つ少ない数の分離膜を形成すればよく、ここでは、分離膜として、絶縁膜262a,262bを形成している。

【0055】

以上のように、ビットライン方向に対してnか所(n>2)の配置位置をアクティブエリア毎に順にずらしながら配置することを繰り返して複数のコンタクトホールを形成する場合でも、第3の実施形態によれば、ゲート間のコンタクト配置においてコンタクト間距離を小さくでき、その結果、ゲート間距離をより小さく形成できる。よって、チップサイズの縮小化ができる。

【0056】

以上、具体例を参照しつつ実施形態について説明した。しかし、本発明は、これらの具体例に限定されるものではない。

【0057】

また、各膜の膜厚や、開口部のサイズ、形状、数などについても、半導体集積回路や各種の半導体素子において必要とされるものを適宜選択して用いることができる。

【0058】

その他、本発明の要素を具備し、当業者が適宜設計変更しうる全ての半導体装置および半導体装置の製造方法は、本発明の範囲に包含される。

【0059】

また、説明の簡便化のために、半導体産業で通常用いられる手法、例えば、フォトリソグラフィプロセス、処理前後のクリーニング等は省略しているが、それらの手法が含まれ得ることは言うまでもない。

【符号の説明】

【0060】

20,22 セレクトゲート線、21,23 セレクトゲート、40,42,44 ビットラインコンタクト、151,161 スペース、153,155 コンタクトホール、260,262 絶縁膜

【特許請求の範囲】

【請求項1】

基板上に、互いに並行する第1と第2の配線を形成する工程と、

前記第1と第2の配線を覆うように、第1の絶縁膜をコンフォーマルに形成する工程と、

前記第1の絶縁膜をコンフォーマルに形成することによって生じた前記第1と第2の配線間のくぼみ部分を埋め込むように、前記第1の絶縁膜上に第2の絶縁膜を形成する工程と、

前記第1の絶縁膜が露出するまで前記第2の絶縁膜の上面を後退させる工程と、

前記第1の絶縁膜に、前記第1と第2の配線が延びる方向に沿って互いに位置をずらしつつ、前記くぼみ部分に残った前記第2の絶縁膜に対して前記第1の配線側に位置する第1のホールと、前記くぼみ部分に残った前記第2の絶縁膜に対して前記第2の配線側に位置する第2のホールと、を形成する工程と、

前記第1のホールと前記第2のホールとに導電性材料膜を埋め込む工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項2】

基板上に、互いに並行する第1と第2の配線を形成する工程と、

前記第1と第2の配線を覆うように、第1の絶縁膜を形成する工程と、

前記第1と第2の配線間の位置で前記第1の絶縁膜に溝を形成する工程と、

前記溝内に第2の絶縁膜を形成する工程と、

前記第1の絶縁膜に、前記第1と第2の配線が延びる方向に沿って互いに位置をずらしつつ、前記溝内に形成された前記第2の絶縁膜に対して前記第1の配線側に位置する第1のホールと、前記溝内に形成された前記第2の絶縁膜に対して前記第2の配線側に位置する第2のホールと、を形成する工程と、

前記第1のホールと前記第2のホールとに導電性材料膜を埋め込む工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項3】

前記第1の配線は、NAND型フラッシュメモリ装置内で隣り合う2つのブロックのうちの一方のセレクトゲート線であり、

前記第2の配線は、前記2つのブロックのうちの他方のセレクトゲート線であることを特徴とする請求項1又は2記載の半導体装置の製造方法。

【請求項4】

基板上に互いに並行するように形成された第1と第2の配線と、

前記第1と第2の配線を覆うように形成された第1の絶縁膜と、

前記第1と第2の配線間の所定位置で前記第1と第2の配線と並行して延びるように形成された、前記第1の絶縁膜と材料の異なる第2の絶縁膜と、

前記第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成された第1のコンタクトと、

前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成された第2のコンタクトと、

を備えたことを特徴とする半導体装置。

【請求項5】

前記第2の絶縁膜は、前記第1と第2の配線間の前記所定位置で前記第1の絶縁膜に形成されたくぼみ部分を埋め込むように配置されたことを特徴とする請求項4記載の半導体装置。

【請求項1】

基板上に、互いに並行する第1と第2の配線を形成する工程と、

前記第1と第2の配線を覆うように、第1の絶縁膜をコンフォーマルに形成する工程と、

前記第1の絶縁膜をコンフォーマルに形成することによって生じた前記第1と第2の配線間のくぼみ部分を埋め込むように、前記第1の絶縁膜上に第2の絶縁膜を形成する工程と、

前記第1の絶縁膜が露出するまで前記第2の絶縁膜の上面を後退させる工程と、

前記第1の絶縁膜に、前記第1と第2の配線が延びる方向に沿って互いに位置をずらしつつ、前記くぼみ部分に残った前記第2の絶縁膜に対して前記第1の配線側に位置する第1のホールと、前記くぼみ部分に残った前記第2の絶縁膜に対して前記第2の配線側に位置する第2のホールと、を形成する工程と、

前記第1のホールと前記第2のホールとに導電性材料膜を埋め込む工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項2】

基板上に、互いに並行する第1と第2の配線を形成する工程と、

前記第1と第2の配線を覆うように、第1の絶縁膜を形成する工程と、

前記第1と第2の配線間の位置で前記第1の絶縁膜に溝を形成する工程と、

前記溝内に第2の絶縁膜を形成する工程と、

前記第1の絶縁膜に、前記第1と第2の配線が延びる方向に沿って互いに位置をずらしつつ、前記溝内に形成された前記第2の絶縁膜に対して前記第1の配線側に位置する第1のホールと、前記溝内に形成された前記第2の絶縁膜に対して前記第2の配線側に位置する第2のホールと、を形成する工程と、

前記第1のホールと前記第2のホールとに導電性材料膜を埋め込む工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項3】

前記第1の配線は、NAND型フラッシュメモリ装置内で隣り合う2つのブロックのうちの一方のセレクトゲート線であり、

前記第2の配線は、前記2つのブロックのうちの他方のセレクトゲート線であることを特徴とする請求項1又は2記載の半導体装置の製造方法。

【請求項4】

基板上に互いに並行するように形成された第1と第2の配線と、

前記第1と第2の配線を覆うように形成された第1の絶縁膜と、

前記第1と第2の配線間の所定位置で前記第1と第2の配線と並行して延びるように形成された、前記第1の絶縁膜と材料の異なる第2の絶縁膜と、

前記第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成された第1のコンタクトと、

前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成された第2のコンタクトと、

を備えたことを特徴とする半導体装置。

【請求項5】

前記第2の絶縁膜は、前記第1と第2の配線間の前記所定位置で前記第1の絶縁膜に形成されたくぼみ部分を埋め込むように配置されたことを特徴とする請求項4記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−105988(P2013−105988A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−250734(P2011−250734)

【出願日】平成23年11月16日(2011.11.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月16日(2011.11.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]