半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法および半導体装置に関する。

【背景技術】

【0002】

耐圧を高めたMOSトランジスタが開発されている(例えば特許文献1参照)。例えばn型MOSトランジスタについて説明する。チャネル領域となるp型領域とn型ドレイン領域との間に、低濃度のn型領域を配置することにより、低濃度n型領域で電圧が緩やかに変化して、耐圧を高めることができる。ゲート電極のドレイン側端部近傍での電界集中を緩和するために、さらに、フィールドプレートを用いる技術が提案されている(例えば特許文献2〜4参照)。

【0003】

ゲート電極からドレイン側の、低濃度n型領域上に絶縁膜が配置され、この絶縁膜上に、フィールドプレートと呼ばれる電極が配置される。フィールドプレートへの電圧印加により、ゲート電極のドレイン側端部近傍における電圧変化を緩やかにすることができ、MOSトランジスタの耐圧を向上させることができる。

【0004】

特許文献2では、フィールドプレートの下地となる絶縁膜として、ゲート絶縁膜を共用している。このような技術では、フィールドプレートの下地絶縁膜の厚さを、ゲート絶縁膜と独立に設定することが難しい。

【0005】

特許文献3では、ゲート絶縁膜とは別に、フィールドプレートの下地絶縁膜を、熱酸化により形成している。このような技術では、フィールドプレートの下地絶縁膜を形成するために、熱酸化工程が必要となる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2005−294584号公報

【特許文献2】特開2006−310580号公報

【特許文献3】特開2001−7327号公報

【特許文献4】特開2009−302548号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の一目的は、耐圧の高められたトランジスタを形成するのに適した、半導体装置の新規な製造方法、および、このような方法で形成される半導体装置を提供することである。

【課題を解決するための手段】

【0008】

本発明の一観点によれば、シリコン基板に、第1導電型の第1領域と、前記第1領域に接する第2導電型の第2領域とを形成する工程と、前記シリコン基板上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に、前記第1領域と前記第2領域とに跨がるゲート電極を形成する工程と、前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆う絶縁膜を形成する工程と、前記ゲート電極をマスクとし、前記シリコン基板に前記第2導電型の不純物を注入して、ソース領域とドレイン領域とを形成する工程と、前記ゲート電極および前記絶縁膜を覆って前記シリコン基板上に金属層を形成し、前記金属層形成後に熱処理を行って、前記ソース領域上、前記ドレイン領域上、および前記ゲート電極上に、シリサイドを形成する工程と、前記ゲート電極および前記絶縁膜を覆って、前記シリコン基板上に、層間絶縁膜を形成する工程と、前記層間絶縁膜に、前記ソース領域に達する第1コンタクトホール、前記ドレイン領域に達する第2コンタクトホール、前記ゲート電極に達する第3コンタクトホール、および、前記絶縁膜に達する少なくとも1つの孔を形成する工程と、前記第1、第2および第3コンタクトホール、および前記孔に導電材料を埋め込み、前記第1、第2および第3コンタクトホールそれぞれの内部に配置された第1、第2および第3導電ビアと、前記孔の内部に配置された導電部材とを形成する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0009】

導電部材は、ゲート電極のドレイン領域側端部近傍における電界集中を緩和するために電圧を印加する電極として用いることができる。シリサイド形成のマスクとして用いられる絶縁膜を、導電部材の下地となる絶縁膜として用いることができる。

【図面の簡単な説明】

【0010】

【図1−1】図1A〜図1Cは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【図1−2】図1D〜図1Fは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【図1−3】図1G〜図1Iは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【図1−4】図1J〜図1Lは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

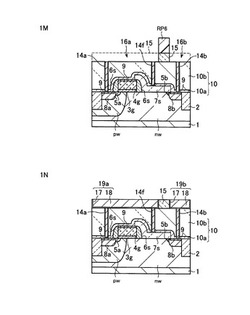

【図1−5】図1Mおよび図1Nは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【図2】図2は、第1実施例の半導体装置の概略平面図である。

【図3】図3A〜図3Cは、それぞれ、第1比較例、第2比較例、および第1実施例について、ゲート電極近傍の電界および等電位線を概略的に示す。

【図4】図4は、第1実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。

【図5】図5は、第1実施例の変形例による半導体装置の概略平面図である。

【図6】図6は、第2実施例の半導体装置の概略的な断面図である。

【図7】図7は、第2実施例の半導体装置の概略的な平面図である。

【図8】図8は、第3実施例の半導体装置の概略的な平面図である。

【図9】図9Aおよび図9Bは、それぞれ、第2実施例および第3実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。

【図10】図10は、第4実施例の半導体装置の概略平面図である。

【図11】図11Aおよび図11Bは、それぞれ、第1実施例および第4実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。

【図12】図12Aおよび図12Bは、変形例の製造工程を示す概略断面図である。

【発明を実施するための形態】

【0011】

まず、本発明の第1実施例による半導体装置について説明する。図1A〜図1Nは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【0012】

図1Aを参照する。半導体基板1に、例えば、シャロートレンチアイソレーション(STI)により酸化シリコンを用いた素子分離絶縁膜2を形成する。半導体基板1は、例えばp型シリコン基板である。

【0013】

基板1にp型不純物を注入して、p型ウェルpwを形成する。p型ウェルpwは、例えば以下のようにして形成される。p型ウェルpwの形成領域を露出するレジストパターンRP1を形成する。レジストパターンRP1をマスクとして、Bを、注入エネルギー400keVでドーズ量1×1013cm−2、注入エネルギー150keVでドーズ量5×1012cm−2、および、注入エネルギー15keVでドーズ量1×1013cm−2の条件で3回注入する。p型ウェルpwの形成後、レジストパターンRP1を除去する。

【0014】

図1Bを参照する。基板1にn型不純物を注入して、n型ウェルnwを形成する。n型ウェルnwは、例えば以下のようにして形成される。基板全面に、Pを、注入エネルギー500keVでドーズ量2×1012cm−2、注入エネルギー15keVでドーズ量1×1012cm−2の条件で2回注入する。

【0015】

図1Cを参照する。シリコン基板1上に、例えば、熱酸化により酸化シリコン膜を厚さ10nm成長させて、ゲート絶縁膜3を形成する。ゲート絶縁膜3上に、例えば、化学気相堆積(CVD)によりポリシリコン膜を厚さ100nm堆積して、導電膜4を形成する。

【0016】

導電膜4上に、ゲート電極形状のレジストパターンRP2を形成する。レジストパターンRP2をマスクとし、例えばHBrおよびO2の混合ガスによるエッチングで、導電膜4をパターニングしてゲート電極4gを形成する。ゲート電極4gは、p型ウェルpwとn型ウェルnwとに跨って配置され、例えばゲート長が1μmで、例えばそのうちp型ウェルpwとの重なり幅Wpが0.6μm、n型ウェルnwとの重なり幅Wnが0.4μmである。このエッチングにより、ゲート絶縁膜3も、ゲート電極4gに整合する形状のゲート絶縁膜3gにパターニングされる。その後、レジストパターンRP2を除去する。

【0017】

図1Dを参照する。ゲート電極4gの外側のn型ウェルnw上に、LDD注入のマスクとなるレジストパターンRP3を形成する。レジストパターンRP3は、n型ウェルnw上から、ゲート電極4のn型ウェルnw側縁部上に延在する。

【0018】

レジストパターンRP3が、ゲート電極4の側面からn型ウェルnw上に重なる幅W1は、接合耐圧の確保に充分な程度に長く設定され、例えば0.9μmである。レジストパターンRP3の、ゲート電極4gのn型ウェルnw側縁部との重なり幅W2は、レジストパターンRP3の縁がずれても、n型ウェルnwにイオン注入されないようにするためのマージンであり、例えば0.1μmである。

【0019】

ゲート電極4gおよびレジストパターンRP3をマスクとして、LDD注入を行なう。LDD注入条件は、例えば、n型不純物としてPを用い、注入エネルギー5keV、ドーズ量1×1014cm−2とする。ゲート電極4gおよびレジストパターンRP3を挟んで、それぞれ、ゲート電極4g側のp型ウェルpwにLDD領域5aが形成され、レジストパターンRP3側のn型ウェルnwにLDD領域5bが形成される。ゲート電極4gの上面上にも、n型不純物が注入される。その後、レジストパターンRP3を除去する。

【0020】

図1Eを参照する。ゲート電極4gを覆って基板1上に、例えば、CVDで酸化シリコン膜を厚さ80nm堆積して、絶縁膜6を形成する。そして、絶縁膜6を異方性エッチングして、ゲート電極4gの側面上に、サイドウォールスペーサ6sを形成する。

【0021】

図1Fを参照する。ゲート電極4gおよびサイドウォールスペーサ6を覆って基板1上に、例えば、CVDで酸化シリコン膜を厚さ40nm〜80nm(例えば60nm)堆積して、絶縁膜7を形成する。絶縁膜7上に、シリサイドブロック層形状のレジストパターンRP4を形成する。レジストパターンRP4をマスクとし、絶縁膜7をエッチングして、シリサイドブロック層7sを形成する。シリサイドブロック層7sは、後のソースドレイン注入工程でのマスクとして用いられるとともに、シリサイド形成工程でシリサイド形成をブロックするマスクとして用いられる。その後、レジストパターンRP4を除去する。

【0022】

シリサイドブロック層7sは、n型ウェルnw上から、n型ウェルnw側のサイドウォールスペーサ6sを覆い、ゲート電極4gのn型ウェルnw側縁部上に延在する形状で形成される。シリサイドブロック層7sが、ゲート電極4gの側面からn型ウェルnw上に重なる幅W3は、接合耐圧の確保に充分な程度に長く設定され、例えば1μmである。シリサイドブロック層7sの、ゲート電極4gのn型ウェルnw側縁部との重なり幅W4は、シリサイドブロック層7sの縁がずれても、n型ウェルnwにイオン注入されないようにするため、あるいは、n型ウェルnwにシリサイド形成されないようにするためのマージンであり、例えば0.1μmである。

【0023】

図1Gを参照する。p型ウェルpw側のサイドウォールスペーサ6s、ゲート電極4g、およびシリサイドブロック層7sをマスクとして、ソースドレイン注入を行なう。ソースドレイン注入条件は、例えば、n型不純物としてPを用い、注入エネルギー8keV、ドーズ量2×1015cm−2とする。p型ウェルpw側のサイドウォールスペーサ6s、ゲート電極4g、およびシリサイドブロック層7sを挟んで、それぞれ、ゲート電極4g側のp型ウェルpwにソースドレイン領域8aが形成され、シリサイドブロック層7s側のn型ウェルnwにソースドレイン領域8bが形成される。ゲート電極4gの上面上にも、n型不純物が注入される。

【0024】

チャネル領域となるp型ウェルpwと、n型LDD領域5bおよびn型ソースドレイン領域8bとの間に、n型ウェルnwが挟まれて、高耐圧のトランジスタ構造が形成される。ソースドレイン領域8aおよび8bの形成後、例えば1000℃で3秒のアニールを行う。

【0025】

図1Hを参照する。基板全面上に金属層として例えばニッケル層を形成し、熱処理を行って、例えばニッケルシリサイドによるシリサイド9を形成する。シリサイド9は、ソースドレイン領域8aおよび8bと、ゲート電極4gの上面に形成される。シリサイドブロック層7sは、シリサイド形成のマスクとして機能する。

【0026】

図1Iを参照する。サイドウォールスペーサ6s、ゲート電極4g、およびシリサイドブロック層7sを覆って基板1上に、例えば、CVDで窒化シリコン膜を厚さ20nm〜40nm(例えば30nm)堆積して、コンタクトストップライナー層となる絶縁膜10aを形成する。絶縁膜10a上に、例えば、CVDで酸化シリコン膜を厚さ300nm〜600nm(例えば400nm)堆積して、層間絶縁膜10bを形成する。化学機械研磨(CMP)により、層間絶縁膜10bの上面を平坦化する。なお、絶縁膜10aおよび10bをまとめて、層間絶縁膜10と呼ぶことができる。

【0027】

図1Jを参照する。絶縁膜10b上に、レジストパターンRP5を形成する。レジストパターンRP5は、コンタクトホール11a、11b、および、フィールドプレート形成用孔11fの形状の開口を有し、さらに、コンタクトホール11gの形状の開口を有する。

【0028】

後の工程で、コンタクトホール11a、11b、11g、および、フィールドプレート形成用孔11f内に、導電ビア14a、14b、14g、および、フィールドプレート14fが形成される。

【0029】

コンタクトホール11aおよび11bは、それぞれ、ソースドレイン領域8aおよび8b上方に配置される。コンタクトホール11gは、断面図1Jには示されていないが、平面図2に示されており、ゲート電極4g上方に配置される。なお、コンタクトホール11g内に形成される導電ビア14gも、平面図2に示される。フィールドプレート形成用孔11fは、シリサイドブロック層7sの、n型ウェルnw上の平坦部上方に配置されている。

【0030】

レジストパターンRP5をマスクとして、絶縁膜10aが露出するまで絶縁膜10bをエッチングする。このエッチングは、絶縁膜10a(例えば窒化シリコン)に対して絶縁膜10b(例えば酸化シリコン)が高い選択比でエッチングされ、絶縁膜10bがエッチングストッパとして機能するような条件で行われる。

【0031】

絶縁膜10bのエッチング条件は、例えば以下のようなものである。エッチングガスとしてC4F6、O2、およびArの混合ガスが用いられ、C4F6、O2、およびArの流量はそれぞれ、10sccm〜30sccm、5sccm〜20sccm、および500sccm〜1000sccmであり、圧力は4Pa〜11Pa (30mTorr〜80mTorr)であり、RFパワーは2000W〜4000Wである。

【0032】

コンタクトホール11a、11b、11gの平面形状、つまり導電ビア14a、14b、14gの平面形状は、例えば、正方形である(図2も参照)。コンタクトホール11aの一辺Wa、コンタクトホール11bの一辺Wb、および、コンタクトホール11gの一辺は、それぞれ、例えば100nm〜160nm程度(例えば130nm)である。

【0033】

フィールドプレート形成用孔11fの平面形状、つまりフィールドプレート14fの平面形状は、導電ビア14a等の平面形状と揃える必要はないが、導電ビア14a等と揃っていれば、フィールドプレート形成用孔11fのエッチング条件が、コンタクトホール11a等のエッチング条件と揃うので、フィールドプレート形成用孔11fの形成が容易となる。第1実施例では、 フィールドプレート14fの平面形状を、導電ビア14a等と一致させており、例えば一辺Wfが130nmの正方形形状としている。

【0034】

ゲート電極4gのnウェルnw側の側面から、フィールドプレート形成用孔11fの(フィールドプレート14fの)ゲート電極側の側面までの距離W5は、例えば200nmである。

【0035】

図1Kを参照する。引き続きレジストパターンRP5をマスクとして、絶縁膜10aをエッチングする。絶縁膜10aのエッチング条件は、例えば以下のようなものである。エッチングガスとしてCH3F、O2、およびArの混合ガスが用いられ、CH3F、O2、およびArの流量はそれぞれ、30sccm〜100sccm、10sccm〜100sccm、および100sccm〜300sccmであり、圧力は6.7Pa〜27Pa (50mTorr〜200mTorr)であり、RFパワーは300W〜1000Wである。絶縁膜10aのエッチング後、レジストパターンRP5を除去する。

【0036】

コンタクトホール11aおよび11bは、それぞれ、ソースドレイン領域8aおよび8bに達する。コンタクトホール11gは、ゲート電極4gに達する。フィールドプレート形成用孔11fは、シリサイドブロック層7sに達する。このようにして、層間絶縁膜10に、コンタクトホール11a、11b、11g、およびフィールドプレート形成用孔11fが形成される。

【0037】

図1Lを参照する。コンタクトホール11a、11b、11g、およびフィールドプレート形成用孔11fの内面を覆って、層間絶縁膜10上に、グルーレイヤー12を形成する。グルーレイヤー12は、例えば、スパッタリングでTi膜を厚さ10nm〜20nm堆積し、このTi膜上にスパッタリングでTiN膜を厚さ10nm〜20nm積層して形成される。

【0038】

さらに、グルーレイヤー12上に、例えばCVDでW膜13を堆積して、コンタクトホール11a、11b、11g、およびフィールドプレート形成用孔11fを埋め込む。そして、層間絶縁膜10上面上の不要なW膜13およびグルーレイヤー12をCMPで除去して、コンタクトホール11a、11b、および11g内に、それぞれ導電ビア14a、14b、および14gを形成するとともに、フィールドプレート形成用孔11f内に、導電部材14fを形成する。

【0039】

導電ビア14aは、ソースドレイン領域8aに電気的に接続し、導電ビア14bは、ソースドレイン領域8bに電気的に接続し、導電ビア14gは、ゲート電極4gに電気的に接続する。フィールドプレート14fは、絶縁膜であるシリサイドブロック層7s上に配置される。シリサイドブロック層7s上に配置された導電部材14fを、フィールドプレート14fと呼ぶこととする。

【0040】

図1Mを参照する。層間絶縁膜10上に、例えば、CVDで酸化シリコン膜を厚さ150nm堆積して、層間絶縁膜15を形成する。層間絶縁膜15上に、配線形状で開口するレジストパターンRP6を形成する。レジストパターンRP6をマスクとし層間絶縁膜15をエッチングして、配線溝16a、16b、および16gを形成する。その後、レジストパターンRP6を除去する。

【0041】

第1実施例において、配線溝16aは、ソースドレイン領域8aに接続する導電ビア14aを露出するとともに、フィールドプレート14fを露出する。配線溝16bは、ソースドレイン領域8bに接続する導電ビア14bを露出する。

【0042】

配線溝16gは、ゲート電極4gに接続する導電ビア14gを露出する。配線溝16gは、断面図1Mには示されていないが、平面図2に示されている。なお、以下の工程で配線溝16g内に形成される配線19gも、平面図2に示される。

【0043】

図1Nを参照する。配線溝16a、16b、および16gの内面を覆って、層間絶縁膜15上に、バリアメタル膜17を形成する。バリアメタル膜17は、例えば、スパッタリングでTaN膜またはTa膜を厚さ5nm〜20nm堆積して形成される。

【0044】

バリアメタル膜17上に、例えば、スパッタリングでCu膜を厚さ20nm堆積して、シード層を形成する。シード層上に、電解めっきによりCu膜18を堆積して、配線溝16a、16b、および16gを埋め込む。そして、層間絶縁膜15上面上の不要なCu膜18、シード層、およびバリアメタル層17をCMPで除去して、配線溝16a、16b、および16g内に、それぞれ配線19a、19b、および19gを形成する。

【0045】

配線19aは、導電ビア14aに電気的に接続するとともに、導電ビア14aとフィールドプレート14fとを電気的に接続する。配線19bおよび19gは、それぞれ、導電ビア14bおよび14gに電気的に接続する。

【0046】

さらに、必要に応じ、公知技術を利用して、上層の配線を形成し、多層配線構造を形成することができる。このようにして、第1実施例の半導体装置が形成される。

【0047】

図2は、第1実施例の半導体装置の概略平面図である。図1A〜図1Nに示した断面図は、図2のAA断面である。活性領域ARを(素子分離絶縁膜2の境界を)、破線で示す。 ゲート電極4gおよびシリサイドブロック層7sを挟んで、それぞれ、ゲート電極4g側に、ソースドレイン領域8aに接続する導電ビア14aが形成され、シリサイドブロック層7s側に、ソースドレイン領域8bに接続する導電ビア14bが形成されている。ゲート電極4gのゲート幅方向一端部分に接続して、導電ビア14gが形成されている。フィールドプレート14fが、シリサイドブロック7s上に形成されている。

【0048】

導電ビア14a、14b、およびフィールドプレート14fは、それぞれ、ゲート幅方向に複数個並んで配置されている。第1実施例では、フィールドプレート14fが、ゲート幅方向に1列に並んで形成されている。

【0049】

ゲート幅方向に隣接する導電ビア14a同士、導電ビア14b同士、およびフィールドプレート14f同士の間隙幅は、それぞれ、必要に応じて適宜設定することができるが、例えば、導電ビア14a、14b、およびフィールドプレート14fの一辺の長さと等しく設定され、例えば130nmである。

【0050】

第1実施例では、導電ビア14aに接続する配線19aが、フィールドプレート14fにも接続するように形成されている。配線19bおよび19gは、それぞれ、導電ビア14bおよび14gに接続している。

【0051】

例えば、配線19aに0V〜5V(例えば0V)が印加され、配線19bに10V〜200V(例えば80V)の高い電圧が印加されて、導電ビア14aに接続されたソースドレイン領域8aがソース、導電ビア14bに接続されたソースドレイン領域8bがドレインとなる。ゲート電極4gに接続する配線19gには、例えば、0V〜5V(例えば0V)が印加される。第1実施例では、導電ビア14aとともにフィールドプレート14fにも、例えば0Vが印加される。

【0052】

次に、第1実施例によるフィールドプレート14fの電界集中抑制効果について説明する。

【0053】

図3A〜図3Cは、それぞれ、ゲート電極GT近傍の電界および等電位線を概略的に示す。各図とも、上側にシリコン基板表面における電界のグラフを示し、下側に厚さ方向断面図に重ねて等電位線をプロットしたグラフを示す。横方向がゲート長方向であり、左方がソース側、右方がドレイン側である。ゲート電極側からドレイン側に向かって、電位が高くなっている。

【0054】

図3Aは、第1比較例として、フィールドプレートFPが形成されていない場合を示す。第1比較例では、ゲート電極GTのドレイン側端部近傍で、ゲート長方向の電界が非常に大きくなり、電界集中が起こっている。

【0055】

図3Bは、第2比較例として、フィールドプレートFPが形成されているが、フィールドプレートFPの下方の絶縁膜がゲート絶縁膜と等しい厚さであり、ゲート電極GTとフィールドプレートFPの下面高さが揃っている場合を示す。第2比較例では、フィールドプレートFPへの印加電位の影響により、ゲート電極GTのドレイン側端部近傍の電界集中が緩和されている。ただし、フィールドプレートFPのドレイン側端部近傍での電界集中が生じている。フィールドプレートFPの下方において(図3B中では明示しない絶縁膜中で)、厚さ方向に関し等電位線の間隔が詰まり電界が大きくなっていることがわかる。これに起因して、絶縁膜厚さ方向で絶縁破壊が生じやすくなっている。

【0056】

図3Cは、第1実施例に対応し、フィールドプレートFPの下方の絶縁膜(シリサイドブロック層)がゲート絶縁膜よりも厚く、ゲート電極GTの下面よりもフィールドプレートFPの下面が高い場合を示す。

【0057】

第1実施例では、ゲート長方向について、ゲート電極GTのドレイン側端部近傍およびフィールドプレートFPのドレイン側端部近傍での電界集中が緩和されている。また、フィールドプレートFPの下方における厚さ方向の電界集中も緩和され、絶縁破壊も抑制されている。

【0058】

図4は、第1実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。0V、2V、4V、および6Vの等電位線を示す。

【0059】

ゲート電極4gのドレイン側端部近傍の、0Vおよび2Vの等電位線のうち、フィールドプレート14fの列のゲート幅方向隙間部分を、囲みISで示している。囲みISで示す、フィールドプレート14fの隙間部分の等電位線は、フィールドプレート14fが配置されていない場合にやや近い形状となる。囲みISの部分では、等電位線間隔が狭く、電界集中が残る傾向が見られる。しかし、フィールドプレート14fが配置された部分では、特に、0Vと2Vの等電位線の間隔が拡がり、電界集中が緩和されていることがわかる。

【0060】

以上説明したように、第1実施例の半導体装置は、フィールドプレート14fにより、ゲート長方向の電界集中を緩和することができる。また、フィールドプレート14fの下方に配置されるシリサイドブロック層7sが(例えばゲート絶縁膜3gより)厚いことにより、厚さ方向の絶縁破壊も抑制される。

【0061】

シリサイドブロック層7sは、例えばゲート絶縁膜3gとは独立に形成されるので、例えばゲート絶縁膜3gに対して独立に厚さを設定することができる。また、シリサイドブロック層7sは、高耐圧トランジスタの形成において、もともとシリサイド形成工程のマスクとして形成されていたものなので、フィールドプレート14fの下地絶縁膜を新たに形成する工程を追加しなくてよい。

【0062】

なお、等電位線の分布を調整するために、例えば、フィールドプレート14fの形状や配置を、必要に応じて変更することができる。

【0063】

図5は、第1実施例の変形例による半導体装置の概略平面図である。第1実施例は、例えば図2に示したように、配線19aにより導電ビア14aとフィールドプレート14fとを接続し、ソース領域8aへの印加電圧を、フィールドプレート14fにも印加する構造とした。

【0064】

図5に示すように、第1実施例の変形例は、配線19gにより、導電ビア14gとフィールドプレート14fとを接続し、ゲート電極4gへの印加電圧を、フィールドプレート14fにも印加する構造としている。第1実施例において、図1M、図1Nを参照して説明した配線19a等の形成工程を変更することにより、本変形例の半導体装置を形成することができる。

【0065】

ドレイン領域8bへの高い印加電圧(例えば80V)に対して、ソース領域8aへの印加電圧(例えば0V)と同様に、ゲート電極4gへの印加電圧(例えば0V)も低い。従って、このような配線構造としても、図3Cおよび図4を参照して説明したような、フィールドプレート14fによる耐圧向上効果を得ることができる。

【0066】

次に、第2実施例による半導体装置について説明する。

【0067】

図6および図7は、それぞれ、第2実施例の半導体装置の概略的な断面図および平面図である。第1実施例との違いについて説明する。第2実施例では、ゲート幅方向に複数個のフィールドプレート14fが並べられた列が、ゲート長方向に2列並べられている。2列のフィールドプレート14fが、配線19aにより、導電ビア14aに電気的に接続されている。

【0068】

導電ビア14a、14b、14gの形状や寸法は、第1実施例と同様である。フィールドプレート14fについても、個々の形状や寸法は、第1実施例と同様である。ゲート側のフィールドプレート14fの列は、第1実施例と同様に、ゲート電極4gからの距離W5を例えば200nmとして配置されている。

【0069】

第2実施例で追加されたドレイン側のフィールドプレート14fの列は、個々のフィールドプレート14fのゲート幅方向の位置を、ゲート側の列の各フィールドプレート14fと揃えて配置されている。ゲート側の列のフィールドプレート14fと、ドレイン側の列のフィールドプレート14fとの間隙幅W6は、例えばフィールドプレート14fの一辺の長さと等しく設定され、例えば130nmである。

【0070】

次に、第3実施例による半導体装置について説明する。

【0071】

図8は、第3実施例の半導体装置の概略的な平面図である。第3実施例でも、第2実施例と同様に、ゲート幅方向に複数個のフィールドプレート14fが並べられた列が、ゲート長方向に2列並べられており、2列のフィールドプレート14fが、配線19aにより導電ビア14aに電気的に接続されている。ただし、第3実施例では、ゲート幅方向について、ゲート側の列と、ドレイン側の列とで、フィールドプレート14fが交互に配置されており、ゲート幅方向に関するフィールプレート14fの隙間が少なくなっている。

【0072】

第2実施例および第3実施例のように、ゲート幅方向に複数個のフィールドプレート14fが並べられた列を、ゲート長方向に複数列並べる構造とすることもできる。なお、必要に応じて、3列以上としてもよい。

【0073】

次に、第2実施例および第3実施例によるフィールドプレート14fの電界集中抑制効果について説明する。

【0074】

図9Aおよび図9Bは、それぞれ、第2実施例および第3実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。0V、2V、4V、および6Vの等電位線を示す。ゲート電極4gのドレイン側端部近傍の、0Vおよび2Vの等電位線のうち、ゲート側の列のフィールドプレート14fのゲート幅方向隙間部分を、囲みISで示している。

【0075】

第2実施例は、第1実施例(図4参照)とほぼ同様な電界集中抑制効果を示すが、第1実施例と同様に、囲みIS部分では等電位線間隔が狭く、電界集中が残る傾向が見られる。

【0076】

第3実施例は、2列のフィールドプレート14fが、ゲート幅方向について交互に配置されているので、フィールドプレート14fの全体配置を見たとき、ゲート幅方向に関しフィールドプレート14fが配置されていない隙間が少なくなる。これにより、囲みIS部分の等電位線間隔が、第2実施例(または第1実施例)よりも拡がり、電界集中の緩和効果が高められている。

【0077】

なお、第2実施例および第3実施例についても、それぞれ、第1実施例の変形例と同様に、配線19gにより、導電ビア14gとフィールドプレート14fとを接続する構造としてもよい。

【0078】

第2実施例および第3実施例、またそれらの変形例の半導体装置も、第1実施例の半導体装置と同様にして形成することができる。フィールドプレート14fの配置変更や、配線19aや19gの形状変更等に応じて、第1実施例の製造工程を適宜変更することができる。

【0079】

次に、第4実施例の半導体装置について説明する。

【0080】

図10は、第4実施例の半導体装置の概略平面図である。第1実施例〜第3実施例のように、複数個のフィールドプレート14fをゲート幅方向に列状に並べる替わりに、第4実施例では、ゲート幅方向に長い1個のフィールドプレート14fを形成している。

【0081】

図11Aおよび図11Bは、それぞれ、第1実施例および第4実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。0V、2V、4V、および6Vの等電位線を示す。第1実施例に係る図11Aは、図4と同一であり、比較のために、第4実施例に係る図11Bと並べて示している。図11Bで、ゲート電極4gのドレイン側端部近傍の、0Vおよび2Vの等電位線を、囲みISで示している。

【0082】

第4実施例では、ゲート幅方向に関するフィールドプレート14fの隙間がなくなる。そのため、第1実施例で見られたような、ゲート幅方向についてのフィールドプレート14fの隙間での電界集中が抑制され、ゲート幅方向に均一に、電界集中緩和効果が得られている。

【0083】

なお、第4実施例についても、第1実施例の変形例と同様に、配線19gにより、導電ビア14gとフィールドプレート14fとを接続する構造としてもよい。

【0084】

第4実施例およびその変形例の半導体装置も、第1実施例の半導体装置と同様にして形成することができる。第4実施例では、導電ビア14a等とフィールドプレート14fの形状が揃っていないが、コンタクトホール11a等とフィールドプレート形成用孔11fとを同時形成するエッチング条件は、例えば実験的に見つけることができよう。

【0085】

なお、上述の第1実施例〜第4実施例では、配線19a、19b、および19gを、銅配線で形成したが、これらの配線は、銅配線に限らず、例えばアルミ配線で形成することもできる。

【0086】

なお、第1実施例で説明した製造工程では、図1Gを参照して説明したように、ソースドレイン注入のマスクとしてシリサイドブロック層7sを用いた。製造工程の変形例として、以下に説明するように、ソースドレイン注入のマスクとしてはシリサイドブロック層7sを用いない方法を採用することもできる。

【0087】

図12Aおよび図12Bは、変形例の製造方法を示す半導体装置の概略断面図である。まず、第1実施例の図1Eの工程までと同様にして、サイドウォールスペーサ6sまでを形成する。

【0088】

図12Aを参照する。n型ウェルnw上に、ソースドレイン注入のマスクとなるレジストパターンRP11を形成する。p型ウェルpw側のサイドウォールスペーサ6s、ゲート電極4g、およびレジストパターンRP11をマスクとし、ソースドレイン注入を行なって、ソースドレイン領域8aおよび8bを形成する。その後、レジストパターンRP11を除去する。

【0089】

レジストパターンRP11は、ソースドレイン注入のマスクとしたシリサイドブロック層7sについて説明したのと同様に、n型ウェルnw上からゲート電極4gのn型ウェルnw側縁部上に延在して形成される。ソースドレイン注入条件は、例えば、シリサイドブロック層7sをマスクとした場合と同様である。

【0090】

図12Bを参照する。ソースドレイン注入後に、図1Fを参照して説明した工程と同様にして、シリサイドブロック層7sを形成する(なお、図12B中のレジストパターンRP12が、図1F中のレジストパターンRP4に対応している)。シリサイドブロック層7sの厚さは、例えば20nm〜80nmである。シリサイドブロック層7sの形成後は、第1実施例の図1Hの工程以後と同様にして、半導体装置が形成される。

【0091】

このような方法では、シリサイドブロック層7sからソースドレイン注入のマスクとしての制限が無くなるので、例えば、シリサイドブロック層7sを薄くしやすくなり、電界緩和に好適なシリサイドブロック層7sの厚さを選択する自由度が高まる。

【0092】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【0093】

以上説明した第1〜第4実施例を含む実施形態に関し、さらに以下の付記を開示する。

(付記1)

シリコン基板に、第1導電型の第1領域と、前記第1領域に接する第2導電型の第2領域とを形成する工程と、

前記シリコン基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、前記第1領域と前記第2領域とに跨がるゲート電極を形成する工程と、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆う絶縁膜を形成する工程と、

前記ゲート電極をマスクとし、前記シリコン基板に前記第2導電型の不純物を注入して、ソース領域とドレイン領域とを形成する工程と、

前記ゲート電極および前記絶縁膜を覆って前記シリコン基板上に金属層を形成し、前記金属層形成後に熱処理を行って、前記ソース領域上、前記ドレイン領域上、および前記ゲート電極上に、シリサイドを形成する工程と、

前記ゲート電極および前記絶縁膜を覆って、前記シリコン基板上に、層間絶縁膜を形成する工程と、

前記層間絶縁膜に、前記ソース領域に達する第1コンタクトホール、前記ドレイン領域に達する第2コンタクトホール、前記ゲート電極に達する第3コンタクトホール、および、前記絶縁膜に達する少なくとも1つの孔を形成する工程と、

前記第1、第2および第3コンタクトホール、および前記孔に導電材料を埋め込み、前記第1、第2および第3コンタクトホールそれぞれの内部に配置された第1、第2および第3導電ビアと、前記孔の内部に配置された導電部材とを形成する工程と

を有する半導体装置の製造方法。

(付記2)

さらに、前記第1導電ビアと前記導電部材とを電気的に接続する配線を形成する工程を有する付記1に記載の半導体装置の製造方法。

(付記3)

さらに、前記第3導電ビアと前記導電部材とを電気的に接続する配線を形成する工程を有する付記1に記載の半導体装置の製造方法。

(付記4)

前記絶縁膜は、前記ゲート絶縁膜よりも厚く形成される付記1〜3のいずれか1つに記載の半導体装置の製造方法。

(付記5)

前記層間絶縁膜を形成する工程は、エッチングストッパとなる第1絶縁膜を形成する工程と、前記第1絶縁膜上に第2絶縁膜を形成する工程を含み、

第1、第2および第3コンタクトホール、および前記絶縁膜に達する前記孔を形成する工程は、前記第1絶縁膜をストッパとして前記第2絶縁膜をエッチングする工程と、前記第2絶縁膜のエッチングの後、前記第1絶縁膜をエッチングする工程とを含む付記1〜4のいずれか1つに記載の半導体装置の製造方法。

(付記6)

前記絶縁膜と前記第2絶縁膜が、酸化シリコンで形成され、前記第1絶縁膜が、窒化シリコンで形成される付記5に記載の半導体装置の製造方法。

(付記7)

前記孔は、ゲート幅方向に分布して複数個配置される付記1〜6のいずれか1つに記載の半導体装置の製造方法。

(付記8)

前記ソース領域と前記ドレイン領域とを形成する工程は、前記ゲート電極とともに前記絶縁膜もマスクとして前記不純物を注入する付記1〜7のいずれか1つに記載の半導体装置の製造方法。

(付記9)

前記孔は、前記第1コンタクトホール、前記第2コンタクトホール、または前記第3コンタクトホールと平面形状が同じである付記1〜8のいずれか1つに記載の半導体装置の製造方法。

(付記10)

さらに、前記ゲート電極形成後、前記絶縁膜の形成前に、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆うレジスト層を形成し、前記ゲート電極および前記レジスト層をマスクとし、前記シリコン基板に前記第2導電型の不純物を注入して、前記ソース領域よりも低濃度の第1不純物領域と、前記ドレイン領域よりも低濃度の第2不純物領域とを形成する工程を有する付記1〜9のいずれか1つに記載の半導体装置の製造方法。

(付記11)

さらに、前記第1不純物領域および前記第2不純物領域の形成後、前記絶縁膜の形成前に、

前記ゲート電極の、前記第1領域側の側面上と前記第2領域側の側面上とに、サイドウォールスペーサ絶縁膜を形成する工程を有する付記10に記載の半導体装置の製造方法。

(付記12)

前記絶縁膜を形成する工程は、前記ゲート電極の、前記第2領域側の側面上の前記サイドウォールスペーサ絶縁膜を覆って、前記絶縁膜を形成し、

前記ソース領域および前記ドレイン領域を形成する工程は、前記ゲート電極および前記絶縁膜とともに、前記ゲート電極の、前記第1領域側の側面上の前記サイドウォールスペーサ絶縁膜もマスクとして、前記第2導電型の不純物を注入する付記11に記載の半導体装置の製造方法。

(付記13)

第1導電型の第1領域、および前記第1領域に接する第2導電型の第2領域が形成されたシリコン基板と、

前記第1領域と前記第2領域とに跨がるゲート電極と、

前記ゲート電極と前記シリコン基板との間に配置されたゲート絶縁膜と、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆う絶縁膜と、

前記シリコン基板に形成されたソース領域およびドレイン領域と、

前記ソース領域上、前記ドレイン領域上、および前記ゲート電極上に形成されたシリサイドと、

前記ゲート電極および前記絶縁膜を覆って前記シリコン基板上に形成された層間絶縁膜と、

前記層間絶縁膜内に形成され、前記ソース領域に電気的に接続する第1導電ビア、前記ドレイン領域に電気的に接続する第2導電ビア、および、前記ゲート電極に電気的に接続する第3導電ビアと、

前記層間絶縁膜内の前記絶縁膜上に、少なくとも1つ形成された導電部材と

を有する半導体装置。

(付記14)

さらに、前記第1導電ビアと前記導電部材とを電気的に接続する配線を有する付記13に記載の半導体装置。

(付記15)

さらに、前記第3導電ビアと前記導電部材とを電気的に接続する配線を有する付記13に記載の半導体装置。

(付記16)

前記ゲート絶縁膜よりも前記絶縁膜の方が厚く、前記ゲート電極の下面よりも前記導電部材の下面の方が高い付記13〜15のいずれか1つに記載の半導体装置。

(付記17)

前記導電部材は、ゲート幅方向に分布して複数個配置されている付記13〜16のいずれか1つに記載の半導体装置。

(付記18)

前記導電部材は、前記第1導電ビア、前記第2導電ビア、または前記第3導電ビアと平面形状が同じである付記13〜17のいずれか1つに記載の半導体装置。

(付記19)

前記導電部材は、複数個の前記導電部材がゲート幅方向に並んで形成された列が、ゲート長方向に複数列配置され、ゲート幅方向に関して、ある列内で隣接する導電部材同士の間隙に、他の列の導電部材が配置されている付記13〜18のいずれか1つに記載の半導体装置。

(付記20)

前記導電部材は、ゲート幅方向に細長い平面形状を有する付記13〜16のいずれか1つに記載の半導体装置。

【符号の説明】

【0094】

1 シリコン基板

2 素子分離絶縁膜

pw p型ウェル

nw n型ウェル

3g ゲート絶縁膜

4g ゲート電極

5a、5b LDD領域

6s サイドウォールスペーサ

7s シリサイドブロック層

8a、8b ソースドレイン領域

8a ソース領域

8b ドレイン領域

9 シリサイド

10a、10b 絶縁膜

10 層間絶縁膜

11a、11b、11g コンタクトホール

11f フィールドプレート形成用孔

12 グルーレイヤー

13 W膜

14a、14b、14g 導電ビア

14f 導電部材(フィールドプレート)

15 層間絶縁膜

16a、16b、16g 配線溝

17 シード層

18 Cu膜

19a、19b、19g 配線

AR 活性領域

RP1〜RP6、RP11、RP12 レジストパターン

【技術分野】

【0001】

本発明は、半導体装置の製造方法および半導体装置に関する。

【背景技術】

【0002】

耐圧を高めたMOSトランジスタが開発されている(例えば特許文献1参照)。例えばn型MOSトランジスタについて説明する。チャネル領域となるp型領域とn型ドレイン領域との間に、低濃度のn型領域を配置することにより、低濃度n型領域で電圧が緩やかに変化して、耐圧を高めることができる。ゲート電極のドレイン側端部近傍での電界集中を緩和するために、さらに、フィールドプレートを用いる技術が提案されている(例えば特許文献2〜4参照)。

【0003】

ゲート電極からドレイン側の、低濃度n型領域上に絶縁膜が配置され、この絶縁膜上に、フィールドプレートと呼ばれる電極が配置される。フィールドプレートへの電圧印加により、ゲート電極のドレイン側端部近傍における電圧変化を緩やかにすることができ、MOSトランジスタの耐圧を向上させることができる。

【0004】

特許文献2では、フィールドプレートの下地となる絶縁膜として、ゲート絶縁膜を共用している。このような技術では、フィールドプレートの下地絶縁膜の厚さを、ゲート絶縁膜と独立に設定することが難しい。

【0005】

特許文献3では、ゲート絶縁膜とは別に、フィールドプレートの下地絶縁膜を、熱酸化により形成している。このような技術では、フィールドプレートの下地絶縁膜を形成するために、熱酸化工程が必要となる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2005−294584号公報

【特許文献2】特開2006−310580号公報

【特許文献3】特開2001−7327号公報

【特許文献4】特開2009−302548号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の一目的は、耐圧の高められたトランジスタを形成するのに適した、半導体装置の新規な製造方法、および、このような方法で形成される半導体装置を提供することである。

【課題を解決するための手段】

【0008】

本発明の一観点によれば、シリコン基板に、第1導電型の第1領域と、前記第1領域に接する第2導電型の第2領域とを形成する工程と、前記シリコン基板上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に、前記第1領域と前記第2領域とに跨がるゲート電極を形成する工程と、前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆う絶縁膜を形成する工程と、前記ゲート電極をマスクとし、前記シリコン基板に前記第2導電型の不純物を注入して、ソース領域とドレイン領域とを形成する工程と、前記ゲート電極および前記絶縁膜を覆って前記シリコン基板上に金属層を形成し、前記金属層形成後に熱処理を行って、前記ソース領域上、前記ドレイン領域上、および前記ゲート電極上に、シリサイドを形成する工程と、前記ゲート電極および前記絶縁膜を覆って、前記シリコン基板上に、層間絶縁膜を形成する工程と、前記層間絶縁膜に、前記ソース領域に達する第1コンタクトホール、前記ドレイン領域に達する第2コンタクトホール、前記ゲート電極に達する第3コンタクトホール、および、前記絶縁膜に達する少なくとも1つの孔を形成する工程と、前記第1、第2および第3コンタクトホール、および前記孔に導電材料を埋め込み、前記第1、第2および第3コンタクトホールそれぞれの内部に配置された第1、第2および第3導電ビアと、前記孔の内部に配置された導電部材とを形成する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0009】

導電部材は、ゲート電極のドレイン領域側端部近傍における電界集中を緩和するために電圧を印加する電極として用いることができる。シリサイド形成のマスクとして用いられる絶縁膜を、導電部材の下地となる絶縁膜として用いることができる。

【図面の簡単な説明】

【0010】

【図1−1】図1A〜図1Cは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【図1−2】図1D〜図1Fは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【図1−3】図1G〜図1Iは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【図1−4】図1J〜図1Lは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【図1−5】図1Mおよび図1Nは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【図2】図2は、第1実施例の半導体装置の概略平面図である。

【図3】図3A〜図3Cは、それぞれ、第1比較例、第2比較例、および第1実施例について、ゲート電極近傍の電界および等電位線を概略的に示す。

【図4】図4は、第1実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。

【図5】図5は、第1実施例の変形例による半導体装置の概略平面図である。

【図6】図6は、第2実施例の半導体装置の概略的な断面図である。

【図7】図7は、第2実施例の半導体装置の概略的な平面図である。

【図8】図8は、第3実施例の半導体装置の概略的な平面図である。

【図9】図9Aおよび図9Bは、それぞれ、第2実施例および第3実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。

【図10】図10は、第4実施例の半導体装置の概略平面図である。

【図11】図11Aおよび図11Bは、それぞれ、第1実施例および第4実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。

【図12】図12Aおよび図12Bは、変形例の製造工程を示す概略断面図である。

【発明を実施するための形態】

【0011】

まず、本発明の第1実施例による半導体装置について説明する。図1A〜図1Nは、第1実施例の半導体装置の主要な製造工程を示す概略断面図である。

【0012】

図1Aを参照する。半導体基板1に、例えば、シャロートレンチアイソレーション(STI)により酸化シリコンを用いた素子分離絶縁膜2を形成する。半導体基板1は、例えばp型シリコン基板である。

【0013】

基板1にp型不純物を注入して、p型ウェルpwを形成する。p型ウェルpwは、例えば以下のようにして形成される。p型ウェルpwの形成領域を露出するレジストパターンRP1を形成する。レジストパターンRP1をマスクとして、Bを、注入エネルギー400keVでドーズ量1×1013cm−2、注入エネルギー150keVでドーズ量5×1012cm−2、および、注入エネルギー15keVでドーズ量1×1013cm−2の条件で3回注入する。p型ウェルpwの形成後、レジストパターンRP1を除去する。

【0014】

図1Bを参照する。基板1にn型不純物を注入して、n型ウェルnwを形成する。n型ウェルnwは、例えば以下のようにして形成される。基板全面に、Pを、注入エネルギー500keVでドーズ量2×1012cm−2、注入エネルギー15keVでドーズ量1×1012cm−2の条件で2回注入する。

【0015】

図1Cを参照する。シリコン基板1上に、例えば、熱酸化により酸化シリコン膜を厚さ10nm成長させて、ゲート絶縁膜3を形成する。ゲート絶縁膜3上に、例えば、化学気相堆積(CVD)によりポリシリコン膜を厚さ100nm堆積して、導電膜4を形成する。

【0016】

導電膜4上に、ゲート電極形状のレジストパターンRP2を形成する。レジストパターンRP2をマスクとし、例えばHBrおよびO2の混合ガスによるエッチングで、導電膜4をパターニングしてゲート電極4gを形成する。ゲート電極4gは、p型ウェルpwとn型ウェルnwとに跨って配置され、例えばゲート長が1μmで、例えばそのうちp型ウェルpwとの重なり幅Wpが0.6μm、n型ウェルnwとの重なり幅Wnが0.4μmである。このエッチングにより、ゲート絶縁膜3も、ゲート電極4gに整合する形状のゲート絶縁膜3gにパターニングされる。その後、レジストパターンRP2を除去する。

【0017】

図1Dを参照する。ゲート電極4gの外側のn型ウェルnw上に、LDD注入のマスクとなるレジストパターンRP3を形成する。レジストパターンRP3は、n型ウェルnw上から、ゲート電極4のn型ウェルnw側縁部上に延在する。

【0018】

レジストパターンRP3が、ゲート電極4の側面からn型ウェルnw上に重なる幅W1は、接合耐圧の確保に充分な程度に長く設定され、例えば0.9μmである。レジストパターンRP3の、ゲート電極4gのn型ウェルnw側縁部との重なり幅W2は、レジストパターンRP3の縁がずれても、n型ウェルnwにイオン注入されないようにするためのマージンであり、例えば0.1μmである。

【0019】

ゲート電極4gおよびレジストパターンRP3をマスクとして、LDD注入を行なう。LDD注入条件は、例えば、n型不純物としてPを用い、注入エネルギー5keV、ドーズ量1×1014cm−2とする。ゲート電極4gおよびレジストパターンRP3を挟んで、それぞれ、ゲート電極4g側のp型ウェルpwにLDD領域5aが形成され、レジストパターンRP3側のn型ウェルnwにLDD領域5bが形成される。ゲート電極4gの上面上にも、n型不純物が注入される。その後、レジストパターンRP3を除去する。

【0020】

図1Eを参照する。ゲート電極4gを覆って基板1上に、例えば、CVDで酸化シリコン膜を厚さ80nm堆積して、絶縁膜6を形成する。そして、絶縁膜6を異方性エッチングして、ゲート電極4gの側面上に、サイドウォールスペーサ6sを形成する。

【0021】

図1Fを参照する。ゲート電極4gおよびサイドウォールスペーサ6を覆って基板1上に、例えば、CVDで酸化シリコン膜を厚さ40nm〜80nm(例えば60nm)堆積して、絶縁膜7を形成する。絶縁膜7上に、シリサイドブロック層形状のレジストパターンRP4を形成する。レジストパターンRP4をマスクとし、絶縁膜7をエッチングして、シリサイドブロック層7sを形成する。シリサイドブロック層7sは、後のソースドレイン注入工程でのマスクとして用いられるとともに、シリサイド形成工程でシリサイド形成をブロックするマスクとして用いられる。その後、レジストパターンRP4を除去する。

【0022】

シリサイドブロック層7sは、n型ウェルnw上から、n型ウェルnw側のサイドウォールスペーサ6sを覆い、ゲート電極4gのn型ウェルnw側縁部上に延在する形状で形成される。シリサイドブロック層7sが、ゲート電極4gの側面からn型ウェルnw上に重なる幅W3は、接合耐圧の確保に充分な程度に長く設定され、例えば1μmである。シリサイドブロック層7sの、ゲート電極4gのn型ウェルnw側縁部との重なり幅W4は、シリサイドブロック層7sの縁がずれても、n型ウェルnwにイオン注入されないようにするため、あるいは、n型ウェルnwにシリサイド形成されないようにするためのマージンであり、例えば0.1μmである。

【0023】

図1Gを参照する。p型ウェルpw側のサイドウォールスペーサ6s、ゲート電極4g、およびシリサイドブロック層7sをマスクとして、ソースドレイン注入を行なう。ソースドレイン注入条件は、例えば、n型不純物としてPを用い、注入エネルギー8keV、ドーズ量2×1015cm−2とする。p型ウェルpw側のサイドウォールスペーサ6s、ゲート電極4g、およびシリサイドブロック層7sを挟んで、それぞれ、ゲート電極4g側のp型ウェルpwにソースドレイン領域8aが形成され、シリサイドブロック層7s側のn型ウェルnwにソースドレイン領域8bが形成される。ゲート電極4gの上面上にも、n型不純物が注入される。

【0024】

チャネル領域となるp型ウェルpwと、n型LDD領域5bおよびn型ソースドレイン領域8bとの間に、n型ウェルnwが挟まれて、高耐圧のトランジスタ構造が形成される。ソースドレイン領域8aおよび8bの形成後、例えば1000℃で3秒のアニールを行う。

【0025】

図1Hを参照する。基板全面上に金属層として例えばニッケル層を形成し、熱処理を行って、例えばニッケルシリサイドによるシリサイド9を形成する。シリサイド9は、ソースドレイン領域8aおよび8bと、ゲート電極4gの上面に形成される。シリサイドブロック層7sは、シリサイド形成のマスクとして機能する。

【0026】

図1Iを参照する。サイドウォールスペーサ6s、ゲート電極4g、およびシリサイドブロック層7sを覆って基板1上に、例えば、CVDで窒化シリコン膜を厚さ20nm〜40nm(例えば30nm)堆積して、コンタクトストップライナー層となる絶縁膜10aを形成する。絶縁膜10a上に、例えば、CVDで酸化シリコン膜を厚さ300nm〜600nm(例えば400nm)堆積して、層間絶縁膜10bを形成する。化学機械研磨(CMP)により、層間絶縁膜10bの上面を平坦化する。なお、絶縁膜10aおよび10bをまとめて、層間絶縁膜10と呼ぶことができる。

【0027】

図1Jを参照する。絶縁膜10b上に、レジストパターンRP5を形成する。レジストパターンRP5は、コンタクトホール11a、11b、および、フィールドプレート形成用孔11fの形状の開口を有し、さらに、コンタクトホール11gの形状の開口を有する。

【0028】

後の工程で、コンタクトホール11a、11b、11g、および、フィールドプレート形成用孔11f内に、導電ビア14a、14b、14g、および、フィールドプレート14fが形成される。

【0029】

コンタクトホール11aおよび11bは、それぞれ、ソースドレイン領域8aおよび8b上方に配置される。コンタクトホール11gは、断面図1Jには示されていないが、平面図2に示されており、ゲート電極4g上方に配置される。なお、コンタクトホール11g内に形成される導電ビア14gも、平面図2に示される。フィールドプレート形成用孔11fは、シリサイドブロック層7sの、n型ウェルnw上の平坦部上方に配置されている。

【0030】

レジストパターンRP5をマスクとして、絶縁膜10aが露出するまで絶縁膜10bをエッチングする。このエッチングは、絶縁膜10a(例えば窒化シリコン)に対して絶縁膜10b(例えば酸化シリコン)が高い選択比でエッチングされ、絶縁膜10bがエッチングストッパとして機能するような条件で行われる。

【0031】

絶縁膜10bのエッチング条件は、例えば以下のようなものである。エッチングガスとしてC4F6、O2、およびArの混合ガスが用いられ、C4F6、O2、およびArの流量はそれぞれ、10sccm〜30sccm、5sccm〜20sccm、および500sccm〜1000sccmであり、圧力は4Pa〜11Pa (30mTorr〜80mTorr)であり、RFパワーは2000W〜4000Wである。

【0032】

コンタクトホール11a、11b、11gの平面形状、つまり導電ビア14a、14b、14gの平面形状は、例えば、正方形である(図2も参照)。コンタクトホール11aの一辺Wa、コンタクトホール11bの一辺Wb、および、コンタクトホール11gの一辺は、それぞれ、例えば100nm〜160nm程度(例えば130nm)である。

【0033】

フィールドプレート形成用孔11fの平面形状、つまりフィールドプレート14fの平面形状は、導電ビア14a等の平面形状と揃える必要はないが、導電ビア14a等と揃っていれば、フィールドプレート形成用孔11fのエッチング条件が、コンタクトホール11a等のエッチング条件と揃うので、フィールドプレート形成用孔11fの形成が容易となる。第1実施例では、 フィールドプレート14fの平面形状を、導電ビア14a等と一致させており、例えば一辺Wfが130nmの正方形形状としている。

【0034】

ゲート電極4gのnウェルnw側の側面から、フィールドプレート形成用孔11fの(フィールドプレート14fの)ゲート電極側の側面までの距離W5は、例えば200nmである。

【0035】

図1Kを参照する。引き続きレジストパターンRP5をマスクとして、絶縁膜10aをエッチングする。絶縁膜10aのエッチング条件は、例えば以下のようなものである。エッチングガスとしてCH3F、O2、およびArの混合ガスが用いられ、CH3F、O2、およびArの流量はそれぞれ、30sccm〜100sccm、10sccm〜100sccm、および100sccm〜300sccmであり、圧力は6.7Pa〜27Pa (50mTorr〜200mTorr)であり、RFパワーは300W〜1000Wである。絶縁膜10aのエッチング後、レジストパターンRP5を除去する。

【0036】

コンタクトホール11aおよび11bは、それぞれ、ソースドレイン領域8aおよび8bに達する。コンタクトホール11gは、ゲート電極4gに達する。フィールドプレート形成用孔11fは、シリサイドブロック層7sに達する。このようにして、層間絶縁膜10に、コンタクトホール11a、11b、11g、およびフィールドプレート形成用孔11fが形成される。

【0037】

図1Lを参照する。コンタクトホール11a、11b、11g、およびフィールドプレート形成用孔11fの内面を覆って、層間絶縁膜10上に、グルーレイヤー12を形成する。グルーレイヤー12は、例えば、スパッタリングでTi膜を厚さ10nm〜20nm堆積し、このTi膜上にスパッタリングでTiN膜を厚さ10nm〜20nm積層して形成される。

【0038】

さらに、グルーレイヤー12上に、例えばCVDでW膜13を堆積して、コンタクトホール11a、11b、11g、およびフィールドプレート形成用孔11fを埋め込む。そして、層間絶縁膜10上面上の不要なW膜13およびグルーレイヤー12をCMPで除去して、コンタクトホール11a、11b、および11g内に、それぞれ導電ビア14a、14b、および14gを形成するとともに、フィールドプレート形成用孔11f内に、導電部材14fを形成する。

【0039】

導電ビア14aは、ソースドレイン領域8aに電気的に接続し、導電ビア14bは、ソースドレイン領域8bに電気的に接続し、導電ビア14gは、ゲート電極4gに電気的に接続する。フィールドプレート14fは、絶縁膜であるシリサイドブロック層7s上に配置される。シリサイドブロック層7s上に配置された導電部材14fを、フィールドプレート14fと呼ぶこととする。

【0040】

図1Mを参照する。層間絶縁膜10上に、例えば、CVDで酸化シリコン膜を厚さ150nm堆積して、層間絶縁膜15を形成する。層間絶縁膜15上に、配線形状で開口するレジストパターンRP6を形成する。レジストパターンRP6をマスクとし層間絶縁膜15をエッチングして、配線溝16a、16b、および16gを形成する。その後、レジストパターンRP6を除去する。

【0041】

第1実施例において、配線溝16aは、ソースドレイン領域8aに接続する導電ビア14aを露出するとともに、フィールドプレート14fを露出する。配線溝16bは、ソースドレイン領域8bに接続する導電ビア14bを露出する。

【0042】

配線溝16gは、ゲート電極4gに接続する導電ビア14gを露出する。配線溝16gは、断面図1Mには示されていないが、平面図2に示されている。なお、以下の工程で配線溝16g内に形成される配線19gも、平面図2に示される。

【0043】

図1Nを参照する。配線溝16a、16b、および16gの内面を覆って、層間絶縁膜15上に、バリアメタル膜17を形成する。バリアメタル膜17は、例えば、スパッタリングでTaN膜またはTa膜を厚さ5nm〜20nm堆積して形成される。

【0044】

バリアメタル膜17上に、例えば、スパッタリングでCu膜を厚さ20nm堆積して、シード層を形成する。シード層上に、電解めっきによりCu膜18を堆積して、配線溝16a、16b、および16gを埋め込む。そして、層間絶縁膜15上面上の不要なCu膜18、シード層、およびバリアメタル層17をCMPで除去して、配線溝16a、16b、および16g内に、それぞれ配線19a、19b、および19gを形成する。

【0045】

配線19aは、導電ビア14aに電気的に接続するとともに、導電ビア14aとフィールドプレート14fとを電気的に接続する。配線19bおよび19gは、それぞれ、導電ビア14bおよび14gに電気的に接続する。

【0046】

さらに、必要に応じ、公知技術を利用して、上層の配線を形成し、多層配線構造を形成することができる。このようにして、第1実施例の半導体装置が形成される。

【0047】

図2は、第1実施例の半導体装置の概略平面図である。図1A〜図1Nに示した断面図は、図2のAA断面である。活性領域ARを(素子分離絶縁膜2の境界を)、破線で示す。 ゲート電極4gおよびシリサイドブロック層7sを挟んで、それぞれ、ゲート電極4g側に、ソースドレイン領域8aに接続する導電ビア14aが形成され、シリサイドブロック層7s側に、ソースドレイン領域8bに接続する導電ビア14bが形成されている。ゲート電極4gのゲート幅方向一端部分に接続して、導電ビア14gが形成されている。フィールドプレート14fが、シリサイドブロック7s上に形成されている。

【0048】

導電ビア14a、14b、およびフィールドプレート14fは、それぞれ、ゲート幅方向に複数個並んで配置されている。第1実施例では、フィールドプレート14fが、ゲート幅方向に1列に並んで形成されている。

【0049】

ゲート幅方向に隣接する導電ビア14a同士、導電ビア14b同士、およびフィールドプレート14f同士の間隙幅は、それぞれ、必要に応じて適宜設定することができるが、例えば、導電ビア14a、14b、およびフィールドプレート14fの一辺の長さと等しく設定され、例えば130nmである。

【0050】

第1実施例では、導電ビア14aに接続する配線19aが、フィールドプレート14fにも接続するように形成されている。配線19bおよび19gは、それぞれ、導電ビア14bおよび14gに接続している。

【0051】

例えば、配線19aに0V〜5V(例えば0V)が印加され、配線19bに10V〜200V(例えば80V)の高い電圧が印加されて、導電ビア14aに接続されたソースドレイン領域8aがソース、導電ビア14bに接続されたソースドレイン領域8bがドレインとなる。ゲート電極4gに接続する配線19gには、例えば、0V〜5V(例えば0V)が印加される。第1実施例では、導電ビア14aとともにフィールドプレート14fにも、例えば0Vが印加される。

【0052】

次に、第1実施例によるフィールドプレート14fの電界集中抑制効果について説明する。

【0053】

図3A〜図3Cは、それぞれ、ゲート電極GT近傍の電界および等電位線を概略的に示す。各図とも、上側にシリコン基板表面における電界のグラフを示し、下側に厚さ方向断面図に重ねて等電位線をプロットしたグラフを示す。横方向がゲート長方向であり、左方がソース側、右方がドレイン側である。ゲート電極側からドレイン側に向かって、電位が高くなっている。

【0054】

図3Aは、第1比較例として、フィールドプレートFPが形成されていない場合を示す。第1比較例では、ゲート電極GTのドレイン側端部近傍で、ゲート長方向の電界が非常に大きくなり、電界集中が起こっている。

【0055】

図3Bは、第2比較例として、フィールドプレートFPが形成されているが、フィールドプレートFPの下方の絶縁膜がゲート絶縁膜と等しい厚さであり、ゲート電極GTとフィールドプレートFPの下面高さが揃っている場合を示す。第2比較例では、フィールドプレートFPへの印加電位の影響により、ゲート電極GTのドレイン側端部近傍の電界集中が緩和されている。ただし、フィールドプレートFPのドレイン側端部近傍での電界集中が生じている。フィールドプレートFPの下方において(図3B中では明示しない絶縁膜中で)、厚さ方向に関し等電位線の間隔が詰まり電界が大きくなっていることがわかる。これに起因して、絶縁膜厚さ方向で絶縁破壊が生じやすくなっている。

【0056】

図3Cは、第1実施例に対応し、フィールドプレートFPの下方の絶縁膜(シリサイドブロック層)がゲート絶縁膜よりも厚く、ゲート電極GTの下面よりもフィールドプレートFPの下面が高い場合を示す。

【0057】

第1実施例では、ゲート長方向について、ゲート電極GTのドレイン側端部近傍およびフィールドプレートFPのドレイン側端部近傍での電界集中が緩和されている。また、フィールドプレートFPの下方における厚さ方向の電界集中も緩和され、絶縁破壊も抑制されている。

【0058】

図4は、第1実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。0V、2V、4V、および6Vの等電位線を示す。

【0059】

ゲート電極4gのドレイン側端部近傍の、0Vおよび2Vの等電位線のうち、フィールドプレート14fの列のゲート幅方向隙間部分を、囲みISで示している。囲みISで示す、フィールドプレート14fの隙間部分の等電位線は、フィールドプレート14fが配置されていない場合にやや近い形状となる。囲みISの部分では、等電位線間隔が狭く、電界集中が残る傾向が見られる。しかし、フィールドプレート14fが配置された部分では、特に、0Vと2Vの等電位線の間隔が拡がり、電界集中が緩和されていることがわかる。

【0060】

以上説明したように、第1実施例の半導体装置は、フィールドプレート14fにより、ゲート長方向の電界集中を緩和することができる。また、フィールドプレート14fの下方に配置されるシリサイドブロック層7sが(例えばゲート絶縁膜3gより)厚いことにより、厚さ方向の絶縁破壊も抑制される。

【0061】

シリサイドブロック層7sは、例えばゲート絶縁膜3gとは独立に形成されるので、例えばゲート絶縁膜3gに対して独立に厚さを設定することができる。また、シリサイドブロック層7sは、高耐圧トランジスタの形成において、もともとシリサイド形成工程のマスクとして形成されていたものなので、フィールドプレート14fの下地絶縁膜を新たに形成する工程を追加しなくてよい。

【0062】

なお、等電位線の分布を調整するために、例えば、フィールドプレート14fの形状や配置を、必要に応じて変更することができる。

【0063】

図5は、第1実施例の変形例による半導体装置の概略平面図である。第1実施例は、例えば図2に示したように、配線19aにより導電ビア14aとフィールドプレート14fとを接続し、ソース領域8aへの印加電圧を、フィールドプレート14fにも印加する構造とした。

【0064】

図5に示すように、第1実施例の変形例は、配線19gにより、導電ビア14gとフィールドプレート14fとを接続し、ゲート電極4gへの印加電圧を、フィールドプレート14fにも印加する構造としている。第1実施例において、図1M、図1Nを参照して説明した配線19a等の形成工程を変更することにより、本変形例の半導体装置を形成することができる。

【0065】

ドレイン領域8bへの高い印加電圧(例えば80V)に対して、ソース領域8aへの印加電圧(例えば0V)と同様に、ゲート電極4gへの印加電圧(例えば0V)も低い。従って、このような配線構造としても、図3Cおよび図4を参照して説明したような、フィールドプレート14fによる耐圧向上効果を得ることができる。

【0066】

次に、第2実施例による半導体装置について説明する。

【0067】

図6および図7は、それぞれ、第2実施例の半導体装置の概略的な断面図および平面図である。第1実施例との違いについて説明する。第2実施例では、ゲート幅方向に複数個のフィールドプレート14fが並べられた列が、ゲート長方向に2列並べられている。2列のフィールドプレート14fが、配線19aにより、導電ビア14aに電気的に接続されている。

【0068】

導電ビア14a、14b、14gの形状や寸法は、第1実施例と同様である。フィールドプレート14fについても、個々の形状や寸法は、第1実施例と同様である。ゲート側のフィールドプレート14fの列は、第1実施例と同様に、ゲート電極4gからの距離W5を例えば200nmとして配置されている。

【0069】

第2実施例で追加されたドレイン側のフィールドプレート14fの列は、個々のフィールドプレート14fのゲート幅方向の位置を、ゲート側の列の各フィールドプレート14fと揃えて配置されている。ゲート側の列のフィールドプレート14fと、ドレイン側の列のフィールドプレート14fとの間隙幅W6は、例えばフィールドプレート14fの一辺の長さと等しく設定され、例えば130nmである。

【0070】

次に、第3実施例による半導体装置について説明する。

【0071】

図8は、第3実施例の半導体装置の概略的な平面図である。第3実施例でも、第2実施例と同様に、ゲート幅方向に複数個のフィールドプレート14fが並べられた列が、ゲート長方向に2列並べられており、2列のフィールドプレート14fが、配線19aにより導電ビア14aに電気的に接続されている。ただし、第3実施例では、ゲート幅方向について、ゲート側の列と、ドレイン側の列とで、フィールドプレート14fが交互に配置されており、ゲート幅方向に関するフィールプレート14fの隙間が少なくなっている。

【0072】

第2実施例および第3実施例のように、ゲート幅方向に複数個のフィールドプレート14fが並べられた列を、ゲート長方向に複数列並べる構造とすることもできる。なお、必要に応じて、3列以上としてもよい。

【0073】

次に、第2実施例および第3実施例によるフィールドプレート14fの電界集中抑制効果について説明する。

【0074】

図9Aおよび図9Bは、それぞれ、第2実施例および第3実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。0V、2V、4V、および6Vの等電位線を示す。ゲート電極4gのドレイン側端部近傍の、0Vおよび2Vの等電位線のうち、ゲート側の列のフィールドプレート14fのゲート幅方向隙間部分を、囲みISで示している。

【0075】

第2実施例は、第1実施例(図4参照)とほぼ同様な電界集中抑制効果を示すが、第1実施例と同様に、囲みIS部分では等電位線間隔が狭く、電界集中が残る傾向が見られる。

【0076】

第3実施例は、2列のフィールドプレート14fが、ゲート幅方向について交互に配置されているので、フィールドプレート14fの全体配置を見たとき、ゲート幅方向に関しフィールドプレート14fが配置されていない隙間が少なくなる。これにより、囲みIS部分の等電位線間隔が、第2実施例(または第1実施例)よりも拡がり、電界集中の緩和効果が高められている。

【0077】

なお、第2実施例および第3実施例についても、それぞれ、第1実施例の変形例と同様に、配線19gにより、導電ビア14gとフィールドプレート14fとを接続する構造としてもよい。

【0078】

第2実施例および第3実施例、またそれらの変形例の半導体装置も、第1実施例の半導体装置と同様にして形成することができる。フィールドプレート14fの配置変更や、配線19aや19gの形状変更等に応じて、第1実施例の製造工程を適宜変更することができる。

【0079】

次に、第4実施例の半導体装置について説明する。

【0080】

図10は、第4実施例の半導体装置の概略平面図である。第1実施例〜第3実施例のように、複数個のフィールドプレート14fをゲート幅方向に列状に並べる替わりに、第4実施例では、ゲート幅方向に長い1個のフィールドプレート14fを形成している。

【0081】

図11Aおよび図11Bは、それぞれ、第1実施例および第4実施例による半導体装置のゲート電極からドレイン側を示す概略平面図に重ねて示した等電位線である。0V、2V、4V、および6Vの等電位線を示す。第1実施例に係る図11Aは、図4と同一であり、比較のために、第4実施例に係る図11Bと並べて示している。図11Bで、ゲート電極4gのドレイン側端部近傍の、0Vおよび2Vの等電位線を、囲みISで示している。

【0082】

第4実施例では、ゲート幅方向に関するフィールドプレート14fの隙間がなくなる。そのため、第1実施例で見られたような、ゲート幅方向についてのフィールドプレート14fの隙間での電界集中が抑制され、ゲート幅方向に均一に、電界集中緩和効果が得られている。

【0083】

なお、第4実施例についても、第1実施例の変形例と同様に、配線19gにより、導電ビア14gとフィールドプレート14fとを接続する構造としてもよい。

【0084】

第4実施例およびその変形例の半導体装置も、第1実施例の半導体装置と同様にして形成することができる。第4実施例では、導電ビア14a等とフィールドプレート14fの形状が揃っていないが、コンタクトホール11a等とフィールドプレート形成用孔11fとを同時形成するエッチング条件は、例えば実験的に見つけることができよう。

【0085】

なお、上述の第1実施例〜第4実施例では、配線19a、19b、および19gを、銅配線で形成したが、これらの配線は、銅配線に限らず、例えばアルミ配線で形成することもできる。

【0086】

なお、第1実施例で説明した製造工程では、図1Gを参照して説明したように、ソースドレイン注入のマスクとしてシリサイドブロック層7sを用いた。製造工程の変形例として、以下に説明するように、ソースドレイン注入のマスクとしてはシリサイドブロック層7sを用いない方法を採用することもできる。

【0087】

図12Aおよび図12Bは、変形例の製造方法を示す半導体装置の概略断面図である。まず、第1実施例の図1Eの工程までと同様にして、サイドウォールスペーサ6sまでを形成する。

【0088】

図12Aを参照する。n型ウェルnw上に、ソースドレイン注入のマスクとなるレジストパターンRP11を形成する。p型ウェルpw側のサイドウォールスペーサ6s、ゲート電極4g、およびレジストパターンRP11をマスクとし、ソースドレイン注入を行なって、ソースドレイン領域8aおよび8bを形成する。その後、レジストパターンRP11を除去する。

【0089】

レジストパターンRP11は、ソースドレイン注入のマスクとしたシリサイドブロック層7sについて説明したのと同様に、n型ウェルnw上からゲート電極4gのn型ウェルnw側縁部上に延在して形成される。ソースドレイン注入条件は、例えば、シリサイドブロック層7sをマスクとした場合と同様である。

【0090】

図12Bを参照する。ソースドレイン注入後に、図1Fを参照して説明した工程と同様にして、シリサイドブロック層7sを形成する(なお、図12B中のレジストパターンRP12が、図1F中のレジストパターンRP4に対応している)。シリサイドブロック層7sの厚さは、例えば20nm〜80nmである。シリサイドブロック層7sの形成後は、第1実施例の図1Hの工程以後と同様にして、半導体装置が形成される。

【0091】

このような方法では、シリサイドブロック層7sからソースドレイン注入のマスクとしての制限が無くなるので、例えば、シリサイドブロック層7sを薄くしやすくなり、電界緩和に好適なシリサイドブロック層7sの厚さを選択する自由度が高まる。

【0092】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【0093】

以上説明した第1〜第4実施例を含む実施形態に関し、さらに以下の付記を開示する。

(付記1)

シリコン基板に、第1導電型の第1領域と、前記第1領域に接する第2導電型の第2領域とを形成する工程と、

前記シリコン基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、前記第1領域と前記第2領域とに跨がるゲート電極を形成する工程と、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆う絶縁膜を形成する工程と、

前記ゲート電極をマスクとし、前記シリコン基板に前記第2導電型の不純物を注入して、ソース領域とドレイン領域とを形成する工程と、

前記ゲート電極および前記絶縁膜を覆って前記シリコン基板上に金属層を形成し、前記金属層形成後に熱処理を行って、前記ソース領域上、前記ドレイン領域上、および前記ゲート電極上に、シリサイドを形成する工程と、

前記ゲート電極および前記絶縁膜を覆って、前記シリコン基板上に、層間絶縁膜を形成する工程と、

前記層間絶縁膜に、前記ソース領域に達する第1コンタクトホール、前記ドレイン領域に達する第2コンタクトホール、前記ゲート電極に達する第3コンタクトホール、および、前記絶縁膜に達する少なくとも1つの孔を形成する工程と、

前記第1、第2および第3コンタクトホール、および前記孔に導電材料を埋め込み、前記第1、第2および第3コンタクトホールそれぞれの内部に配置された第1、第2および第3導電ビアと、前記孔の内部に配置された導電部材とを形成する工程と

を有する半導体装置の製造方法。

(付記2)

さらに、前記第1導電ビアと前記導電部材とを電気的に接続する配線を形成する工程を有する付記1に記載の半導体装置の製造方法。

(付記3)

さらに、前記第3導電ビアと前記導電部材とを電気的に接続する配線を形成する工程を有する付記1に記載の半導体装置の製造方法。

(付記4)

前記絶縁膜は、前記ゲート絶縁膜よりも厚く形成される付記1〜3のいずれか1つに記載の半導体装置の製造方法。

(付記5)

前記層間絶縁膜を形成する工程は、エッチングストッパとなる第1絶縁膜を形成する工程と、前記第1絶縁膜上に第2絶縁膜を形成する工程を含み、

第1、第2および第3コンタクトホール、および前記絶縁膜に達する前記孔を形成する工程は、前記第1絶縁膜をストッパとして前記第2絶縁膜をエッチングする工程と、前記第2絶縁膜のエッチングの後、前記第1絶縁膜をエッチングする工程とを含む付記1〜4のいずれか1つに記載の半導体装置の製造方法。

(付記6)

前記絶縁膜と前記第2絶縁膜が、酸化シリコンで形成され、前記第1絶縁膜が、窒化シリコンで形成される付記5に記載の半導体装置の製造方法。

(付記7)

前記孔は、ゲート幅方向に分布して複数個配置される付記1〜6のいずれか1つに記載の半導体装置の製造方法。

(付記8)

前記ソース領域と前記ドレイン領域とを形成する工程は、前記ゲート電極とともに前記絶縁膜もマスクとして前記不純物を注入する付記1〜7のいずれか1つに記載の半導体装置の製造方法。

(付記9)

前記孔は、前記第1コンタクトホール、前記第2コンタクトホール、または前記第3コンタクトホールと平面形状が同じである付記1〜8のいずれか1つに記載の半導体装置の製造方法。

(付記10)

さらに、前記ゲート電極形成後、前記絶縁膜の形成前に、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆うレジスト層を形成し、前記ゲート電極および前記レジスト層をマスクとし、前記シリコン基板に前記第2導電型の不純物を注入して、前記ソース領域よりも低濃度の第1不純物領域と、前記ドレイン領域よりも低濃度の第2不純物領域とを形成する工程を有する付記1〜9のいずれか1つに記載の半導体装置の製造方法。

(付記11)

さらに、前記第1不純物領域および前記第2不純物領域の形成後、前記絶縁膜の形成前に、

前記ゲート電極の、前記第1領域側の側面上と前記第2領域側の側面上とに、サイドウォールスペーサ絶縁膜を形成する工程を有する付記10に記載の半導体装置の製造方法。

(付記12)

前記絶縁膜を形成する工程は、前記ゲート電極の、前記第2領域側の側面上の前記サイドウォールスペーサ絶縁膜を覆って、前記絶縁膜を形成し、

前記ソース領域および前記ドレイン領域を形成する工程は、前記ゲート電極および前記絶縁膜とともに、前記ゲート電極の、前記第1領域側の側面上の前記サイドウォールスペーサ絶縁膜もマスクとして、前記第2導電型の不純物を注入する付記11に記載の半導体装置の製造方法。

(付記13)

第1導電型の第1領域、および前記第1領域に接する第2導電型の第2領域が形成されたシリコン基板と、

前記第1領域と前記第2領域とに跨がるゲート電極と、

前記ゲート電極と前記シリコン基板との間に配置されたゲート絶縁膜と、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆う絶縁膜と、

前記シリコン基板に形成されたソース領域およびドレイン領域と、

前記ソース領域上、前記ドレイン領域上、および前記ゲート電極上に形成されたシリサイドと、

前記ゲート電極および前記絶縁膜を覆って前記シリコン基板上に形成された層間絶縁膜と、

前記層間絶縁膜内に形成され、前記ソース領域に電気的に接続する第1導電ビア、前記ドレイン領域に電気的に接続する第2導電ビア、および、前記ゲート電極に電気的に接続する第3導電ビアと、

前記層間絶縁膜内の前記絶縁膜上に、少なくとも1つ形成された導電部材と

を有する半導体装置。

(付記14)

さらに、前記第1導電ビアと前記導電部材とを電気的に接続する配線を有する付記13に記載の半導体装置。

(付記15)

さらに、前記第3導電ビアと前記導電部材とを電気的に接続する配線を有する付記13に記載の半導体装置。

(付記16)

前記ゲート絶縁膜よりも前記絶縁膜の方が厚く、前記ゲート電極の下面よりも前記導電部材の下面の方が高い付記13〜15のいずれか1つに記載の半導体装置。

(付記17)

前記導電部材は、ゲート幅方向に分布して複数個配置されている付記13〜16のいずれか1つに記載の半導体装置。

(付記18)

前記導電部材は、前記第1導電ビア、前記第2導電ビア、または前記第3導電ビアと平面形状が同じである付記13〜17のいずれか1つに記載の半導体装置。

(付記19)

前記導電部材は、複数個の前記導電部材がゲート幅方向に並んで形成された列が、ゲート長方向に複数列配置され、ゲート幅方向に関して、ある列内で隣接する導電部材同士の間隙に、他の列の導電部材が配置されている付記13〜18のいずれか1つに記載の半導体装置。

(付記20)

前記導電部材は、ゲート幅方向に細長い平面形状を有する付記13〜16のいずれか1つに記載の半導体装置。

【符号の説明】

【0094】

1 シリコン基板

2 素子分離絶縁膜

pw p型ウェル

nw n型ウェル

3g ゲート絶縁膜

4g ゲート電極

5a、5b LDD領域

6s サイドウォールスペーサ

7s シリサイドブロック層

8a、8b ソースドレイン領域

8a ソース領域

8b ドレイン領域

9 シリサイド

10a、10b 絶縁膜

10 層間絶縁膜

11a、11b、11g コンタクトホール

11f フィールドプレート形成用孔

12 グルーレイヤー

13 W膜

14a、14b、14g 導電ビア

14f 導電部材(フィールドプレート)

15 層間絶縁膜

16a、16b、16g 配線溝

17 シード層

18 Cu膜

19a、19b、19g 配線

AR 活性領域

RP1〜RP6、RP11、RP12 レジストパターン

【特許請求の範囲】

【請求項1】

シリコン基板に、第1導電型の第1領域と、前記第1領域に接する第2導電型の第2領域とを形成する工程と、

前記シリコン基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、前記第1領域と前記第2領域とに跨がるゲート電極を形成する工程と、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆う絶縁膜を形成する工程と、

前記ゲート電極をマスクとし、前記シリコン基板に前記第2導電型の不純物を注入して、ソース領域とドレイン領域とを形成する工程と、

前記ゲート電極および前記絶縁膜を覆って前記シリコン基板上に金属層を形成し、前記金属層形成後に熱処理を行って、前記ソース領域上、前記ドレイン領域上、および前記ゲート電極上に、シリサイドを形成する工程と、

前記ゲート電極および前記絶縁膜を覆って、前記シリコン基板上に、層間絶縁膜を形成する工程と、

前記層間絶縁膜に、前記ソース領域に達する第1コンタクトホール、前記ドレイン領域に達する第2コンタクトホール、前記ゲート電極に達する第3コンタクトホール、および、前記絶縁膜に達する少なくとも1つの孔を形成する工程と、

前記第1、第2および第3コンタクトホール、および前記孔に導電材料を埋め込み、前記第1、第2および第3コンタクトホールそれぞれの内部に配置された第1、第2および第3導電ビアと、前記孔の内部に配置された導電部材とを形成する工程と

を有する半導体装置の製造方法。

【請求項2】

さらに、前記第1導電ビアと前記導電部材とを電気的に接続する配線を形成する工程を有する請求項1に記載の半導体装置の製造方法。

【請求項3】

さらに、前記第3導電ビアと前記導電部材とを電気的に接続する配線を形成する工程を有する請求項1に記載の半導体装置の製造方法。

【請求項4】

前記層間絶縁膜を形成する工程は、エッチングストッパとなる第1絶縁膜を形成する工程と、前記第1絶縁膜上に第2絶縁膜を積層する工程を含み、

第1、第2および第3コンタクトホール、および前記絶縁膜に達する前記孔を形成する工程は、前記第1絶縁膜をストッパとして前記第2絶縁膜をエッチングする工程と、前記第2絶縁膜のエッチングの後、前記第1絶縁膜をエッチングする工程とを含む請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記孔は、ゲート幅方向に分布して複数個配置される請求項1〜4のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記ソース領域と前記ドレイン領域とを形成する工程は、前記ゲート電極とともに前記絶縁膜もマスクとして前記不純物を注入する請求項1〜5のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

さらに、前記ゲート電極形成後、前記絶縁膜の形成前に、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆うレジスト層を形成し、前記ゲート電極および前記レジスト層をマスクとし、前記シリコン基板に前記第2導電型の不純物を注入して、前記ソース領域よりも低濃度の第1不純物領域と、前記ドレイン領域よりも低濃度の第2不純物領域とを形成する工程を有する請求項1〜6のいずれか1項に記載の半導体装置の製造方法。

【請求項8】

第1導電型の第1領域、および前記第1領域に接する第2導電型の第2領域が形成されたシリコン基板と、

前記第1領域と前記第2領域とに跨がるゲート電極と、

前記ゲート電極と前記シリコン基板との間に配置されたゲート絶縁膜と、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆う絶縁膜と、

前記シリコン基板に形成されたソース領域およびドレイン領域と、

前記ソース領域上、前記ドレイン領域上、および前記ゲート電極上に形成されたシリサイドと、

前記ゲート電極および前記絶縁膜を覆って前記シリコン基板上に形成された層間絶縁膜と、

前記層間絶縁膜内に形成され、前記ソース領域に電気的に接続する第1導電ビア、前記ドレイン領域に電気的に接続する第2導電ビア、および、前記ゲート電極に電気的に接続する第3導電ビアと、

前記層間絶縁膜内の前記絶縁膜上に、少なくとも1つ形成された導電部材と

を有する半導体装置。

【請求項9】

さらに、前記第1導電ビアと前記導電部材とを電気的に接続する配線を有する請求項8に記載の半導体装置。

【請求項10】

さらに、前記第3導電ビアと前記導電部材とを電気的に接続する配線を有する請求項8に記載の半導体装置。

【請求項11】

前記ゲート絶縁膜よりも前記絶縁膜の方が厚く、前記ゲート電極の下面よりも前記導電部材の下面の方が高い請求項8〜10のいずれか1項に記載の半導体装置。

【請求項12】

前記導電部材は、ゲート幅方向に分布して複数個配置されている請求項8〜11のいずれか1項に記載の半導体装置。

【請求項13】

前記導電部材は、複数個の前記導電部材がゲート幅方向に並んで形成された列が、ゲート長方向に複数列配置され、ゲート幅方向に関して、ある列内で隣接する導電部材同士の間隙に、他の列の導電部材が配置されている請求項8〜12のいずれか1項に記載の半導体装置。

【請求項14】

前記導電部材は、ゲート幅方向に細長い平面形状を有する請求項8〜11のいずれか1項に記載の半導体装置。

【請求項1】

シリコン基板に、第1導電型の第1領域と、前記第1領域に接する第2導電型の第2領域とを形成する工程と、

前記シリコン基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、前記第1領域と前記第2領域とに跨がるゲート電極を形成する工程と、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆う絶縁膜を形成する工程と、

前記ゲート電極をマスクとし、前記シリコン基板に前記第2導電型の不純物を注入して、ソース領域とドレイン領域とを形成する工程と、

前記ゲート電極および前記絶縁膜を覆って前記シリコン基板上に金属層を形成し、前記金属層形成後に熱処理を行って、前記ソース領域上、前記ドレイン領域上、および前記ゲート電極上に、シリサイドを形成する工程と、

前記ゲート電極および前記絶縁膜を覆って、前記シリコン基板上に、層間絶縁膜を形成する工程と、

前記層間絶縁膜に、前記ソース領域に達する第1コンタクトホール、前記ドレイン領域に達する第2コンタクトホール、前記ゲート電極に達する第3コンタクトホール、および、前記絶縁膜に達する少なくとも1つの孔を形成する工程と、

前記第1、第2および第3コンタクトホール、および前記孔に導電材料を埋め込み、前記第1、第2および第3コンタクトホールそれぞれの内部に配置された第1、第2および第3導電ビアと、前記孔の内部に配置された導電部材とを形成する工程と

を有する半導体装置の製造方法。

【請求項2】

さらに、前記第1導電ビアと前記導電部材とを電気的に接続する配線を形成する工程を有する請求項1に記載の半導体装置の製造方法。

【請求項3】

さらに、前記第3導電ビアと前記導電部材とを電気的に接続する配線を形成する工程を有する請求項1に記載の半導体装置の製造方法。

【請求項4】

前記層間絶縁膜を形成する工程は、エッチングストッパとなる第1絶縁膜を形成する工程と、前記第1絶縁膜上に第2絶縁膜を積層する工程を含み、

第1、第2および第3コンタクトホール、および前記絶縁膜に達する前記孔を形成する工程は、前記第1絶縁膜をストッパとして前記第2絶縁膜をエッチングする工程と、前記第2絶縁膜のエッチングの後、前記第1絶縁膜をエッチングする工程とを含む請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記孔は、ゲート幅方向に分布して複数個配置される請求項1〜4のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記ソース領域と前記ドレイン領域とを形成する工程は、前記ゲート電極とともに前記絶縁膜もマスクとして前記不純物を注入する請求項1〜5のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

さらに、前記ゲート電極形成後、前記絶縁膜の形成前に、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆うレジスト層を形成し、前記ゲート電極および前記レジスト層をマスクとし、前記シリコン基板に前記第2導電型の不純物を注入して、前記ソース領域よりも低濃度の第1不純物領域と、前記ドレイン領域よりも低濃度の第2不純物領域とを形成する工程を有する請求項1〜6のいずれか1項に記載の半導体装置の製造方法。

【請求項8】

第1導電型の第1領域、および前記第1領域に接する第2導電型の第2領域が形成されたシリコン基板と、

前記第1領域と前記第2領域とに跨がるゲート電極と、

前記ゲート電極と前記シリコン基板との間に配置されたゲート絶縁膜と、

前記ゲート電極上から前記第2領域上に延在して、前記ゲート電極の一部および前記第2領域の一部を覆う絶縁膜と、

前記シリコン基板に形成されたソース領域およびドレイン領域と、

前記ソース領域上、前記ドレイン領域上、および前記ゲート電極上に形成されたシリサイドと、

前記ゲート電極および前記絶縁膜を覆って前記シリコン基板上に形成された層間絶縁膜と、

前記層間絶縁膜内に形成され、前記ソース領域に電気的に接続する第1導電ビア、前記ドレイン領域に電気的に接続する第2導電ビア、および、前記ゲート電極に電気的に接続する第3導電ビアと、

前記層間絶縁膜内の前記絶縁膜上に、少なくとも1つ形成された導電部材と

を有する半導体装置。

【請求項9】

さらに、前記第1導電ビアと前記導電部材とを電気的に接続する配線を有する請求項8に記載の半導体装置。

【請求項10】

さらに、前記第3導電ビアと前記導電部材とを電気的に接続する配線を有する請求項8に記載の半導体装置。

【請求項11】

前記ゲート絶縁膜よりも前記絶縁膜の方が厚く、前記ゲート電極の下面よりも前記導電部材の下面の方が高い請求項8〜10のいずれか1項に記載の半導体装置。

【請求項12】

前記導電部材は、ゲート幅方向に分布して複数個配置されている請求項8〜11のいずれか1項に記載の半導体装置。

【請求項13】

前記導電部材は、複数個の前記導電部材がゲート幅方向に並んで形成された列が、ゲート長方向に複数列配置され、ゲート幅方向に関して、ある列内で隣接する導電部材同士の間隙に、他の列の導電部材が配置されている請求項8〜12のいずれか1項に記載の半導体装置。

【請求項14】

前記導電部材は、ゲート幅方向に細長い平面形状を有する請求項8〜11のいずれか1項に記載の半導体装置。

【図1−1】

【図1−2】

【図1−3】

【図1−4】

【図1−5】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図1−2】

【図1−3】

【図1−4】

【図1−5】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−4687(P2013−4687A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2011−133564(P2011−133564)

【出願日】平成23年6月15日(2011.6.15)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成23年6月15日(2011.6.15)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]