半導体装置の製造方法および半導体装置

【課題】互いに異なる特性を備える複数の電界効果トランジスタを同一基板上に有する半導体装置の製造歩留まりを向上させる。

【解決手段】異方性のドライエッチングと等方性のウェットエッチングまたは等方性のドライエッチングとを組み合わせることにより、互いにサイドウォール長の異なる3種類のサイドウォールSWL,SWM,SWHを形成する。異方性のドライエッチングの回数を減らすことにより、配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の削れを防止することができる。

【解決手段】異方性のドライエッチングと等方性のウェットエッチングまたは等方性のドライエッチングとを組み合わせることにより、互いにサイドウォール長の異なる3種類のサイドウォールSWL,SWM,SWHを形成する。異方性のドライエッチングの回数を減らすことにより、配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の削れを防止することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法および半導体装置に関し、特に、互いにゲート長および配置密度の異なる複数の電界効果トランジスタが同一基板に製造された半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

例えば特開平5−326513号公報(特許文献1)には、ドライエッチングによりSiO2スペーサ層を形成したのち、基板表面に残る熱酸化SiO2膜をウェットエッチングにより除去することにより、基板表面のダメージを抑制する技術が開示されている。

【0003】

また、特開2005−5508号公報(特許文献2)には、サイドウォールスペーサ形成層をドライエッチングしてサイドウォールスペーサを形成し、その後、低電圧トランジスタ形成領域のサイドウォールスペーサをウェットエッチングにより除去する技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5−326513号公報

【特許文献2】特開2005−5508号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、細分化された用途に対応するため、要求される各特性(耐圧、リーク電流、動作速度など)に合わせた複数のMISFET(Metal Insulator Semiconductor Field Effect Transistor)を同一基板上に形成している。そのため、要求される各特性を得ようとすると、例えばゲート絶縁膜の厚さ、ゲート長、サイドウォールの厚さ、または配置密度などが互いに異なる複数のMISFETが同一基板上に形成される場合がある。しかし、要求される各特性に合わせた複数のMISFETを同一基板上に形成しようとすると、各製造工程における加工条件の制御が困難となる、または製造プロセスが複雑となる恐れもある。そこで、要求される各特性を満たす複数のMISFETを歩留まり良く製造する技術、あるいは簡易な製造プロセスにより製造する技術が求められている。

【0006】

本発明の目的は、互いに異なる特性を備える複数の電界効果トランジスタを同一基板上に有する半導体装置の製造歩留まりを向上させることのできる技術を提供することにある。

【0007】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0008】

本願において開示される発明のうち、代表的なものの一実施の形態を簡単に説明すれば、次のとおりである。

【0009】

この実施の形態は、高圧系MISFETを第1領域に有し、低リーク用低圧系MISFETを第2領域に有し、高速動作用低圧系MISFETを第3領域に有する半導体装置の製造方法であって、第1領域に第1ゲート絶縁膜を介して第1ゲート電極を形成し、第2領域に第2ゲート絶縁膜を介して第2ゲート電極を形成し、第3領域に第3ゲート絶縁膜を介して第3ゲート電極を形成する工程と、半導体基板の主面上に、第1ゲート電極、第2ゲート電極、および第3ゲート電極を覆うように第1絶縁膜を形成する工程と、第1絶縁膜上に第2絶縁膜を形成する工程と、第2絶縁膜を異方性のドライエッチングにより加工して、第1ゲート電極の側面、第2ゲート電極の側面、および第3ゲート電極の側面にそれぞれ第2絶縁膜を残す工程と、等方性のドライエッチングまたは等方性のウェットエッチングにより、第2ゲート電極の側面および第3ゲート電極の側面に残された第2絶縁膜を加工する工程と、等方性のドライエッチングまたは等方性のウェットエッチングにより、第3ゲート電極の側面に残された第2絶縁膜を除去する工程と、半導体基板の主面上に、第1ゲート電極、第1ゲート電極の側面に残された第2絶縁膜、第2ゲート電極、第2ゲート電極の側面に残された第2絶縁膜、および第3ゲート電極を覆うように第3絶縁膜を形成する工程と、第3絶縁膜を異方性のドライエッチングにより加工して、第1絶縁膜および第2絶縁膜を介した第1ゲート電極の側面、第1絶縁膜および第2絶縁膜を介した第2ゲート電極の側面、第1絶縁膜を介した第3ゲート電極の側面にそれぞれ第3絶縁膜を残す工程と、露出している第1絶縁膜を除去する工程と、を含み、第1ゲート電極の側面に形成された第1絶縁膜、第2絶縁膜、および第3絶縁膜によって第1サイドウォールを構成し、第2ゲート電極の側面に形成された第1絶縁膜、第2絶縁膜、および第3絶縁膜によって第2サイドウォールを構成し、第3ゲート電極の側面に形成された第1絶縁膜および第3絶縁膜によって第3サイドウォールを構成する。

【0010】

また、この実施の形態は、高圧系MISFETを第1領域に有し、低リーク用低圧系MISFETを第2領域に有し、および高速動作用低圧系MISFETを第3領域に有する半導体装置の製造方法であって、第1領域に第1ゲート絶縁膜を介して第1ゲート電極を形成し、第2領域に第2ゲート絶縁膜を介して第2ゲート電極を形成し、第3領域に第3ゲート絶縁膜を介して第3ゲート電極を形成する工程と、半導体基板の主面上に、第1ゲート電極、第2ゲート電極、および第3ゲート電極を覆うように第1絶縁膜を形成する工程と、第1絶縁膜上に第2絶縁膜を形成する工程と、第2絶縁膜を異方性のドライエッチングにより加工して、第1ゲート電極の側面、第2ゲート電極の側面、および第3ゲート電極の側面にそれぞれ第2絶縁膜を残す工程と、等方性のドライエッチングまたは等方性のウェットエッチングにより、第2ゲート電極の側面および第3ゲート電極の側面に残された第2絶縁膜を加工する工程と、等方性のドライエッチングまたは等方性のウェットエッチングにより、第3ゲート電極の側面に残された第3絶縁膜を加工する工程と、露出している第1絶縁膜を除去する工程と、を含み、第1ゲート電極の側面に形成された第1絶縁膜および第2絶縁膜によって第1サイドウォールを構成し、第2ゲート電極の側面に形成された第1絶縁膜および第2絶縁膜によって第2サイドウォールを構成し、第3ゲート電極の側面に形成された第1絶縁膜および第2絶縁膜によって第3サイドウォールを構成する。

【0011】

また、この実施の形態は、高圧系MISFETを第1領域に有し、低リーク用低圧系MISFETを第2領域に有し、および高速動作用低圧系MISFETを第3領域に有し、高圧系MISFETでは、第1ゲート長の第1ゲート電極の側面に第1サイドウォール長の第1サイドウォールが備わり、低リーク用低圧系MISFETでは、第2ゲート長の第2ゲート電極の側面に第2サイドウォール長の第2サイドウォールが備わり、高速動作用低圧系MISFETでは、第3ゲート長の第3ゲート電極の側面に第3サイドウォール長の第3サイドウォールが備わる半導体装置であって、第1サイドウォール長よりも第2サイドウォール長が短く、第2サイドウォール長よりも第3サイドウォール長が短く、さらに、第1サイドウォールの半導体基板の主面からの高さよりも第2サイドウォールの半導体基板の主面からの高さが低く、第2サイドウォールの半導体基板の主面からの高さよりも第3サイドウォールの半導体基板の主面からの高さが低い。

【発明の効果】

【0012】

本願において開示される発明のうち、代表的なものの一実施の形態によって得られる効果を簡単に説明すれば以下のとおりである。

【0013】

互いに異なる特性を備える複数の電界効果トランジスタを同一基板上に有する半導体装置の製造歩留まりを向上させることができる。

【図面の簡単な説明】

【0014】

【図1】本発明の実施の形態1による半導体装置の製造工程を説明する半導体装置の要部断面図である。

【図2】図1に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図3】図2に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図4】図3に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図5】図4に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図6】図5に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図7】図6に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図8】図7に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図9】図8に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図10】図9に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

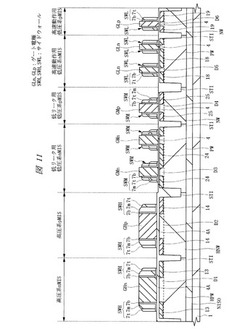

【図11】図10に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図12】図11に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図13】図12に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図14】図13に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図15】図14に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図16】図15に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図17】図16に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図18】本発明の実施の形態1による半導体装置の製造工程の他の例を説明する半導体装置の要部断面図である。

【図19】図18に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図20】図19に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図21】図20に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図22】図21に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図23】図22に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図24】図23に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図25】図24に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図26】図25に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図27】図26に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図28】図27に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図29】図28に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図30】図29に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図31】図30に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図32】図31に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図33】図32に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図34】図33に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図35】図34に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図36】図35に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図37】図36に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図38】本発明の実施の形態2による半導体装置の製造工程を説明する半導体装置の要部断面図である。

【図39】図38に続く半導体装置の製造工程中の図38と同じ箇所の半導体装置の要部断面図である。

【図40】図39に続く半導体装置の製造工程中の図38と同じ箇所の半導体装置の要部断面図である。

【図41】図40に続く半導体装置の製造工程中の図38と同じ箇所の半導体装置の要部断面図である。

【図42】図41に続く半導体装置の製造工程中の図38と同じ箇所の半導体装置の要部断面図である。

【図43】本発明の実施の形態2による半導体装置の製造工程の他の例を説明する半導体装置の要部断面図である。

【図44】本発明の実施の形態3による半導体装置の製造工程を説明する半導体装置の要部断面図である。

【図45】図44に続く半導体装置の製造工程中の図44と同じ箇所の半導体装置の要部断面図である。

【図46】図45に続く半導体装置の製造工程中の図44と同じ箇所の半導体装置の要部断面図である。

【図47】図46に続く半導体装置の製造工程中の図44と同じ箇所の半導体装置の要部断面図である。

【図48】本願発明者らによって検討された半導体装置(高圧系MISFETおよび低圧系MISFET)の製造方法の第1例を説明する半導体装置の要部断面図である。

【図49】本願発明者らによって検討された半導体装置(高圧系MISFETおよび低圧系MISFET)の製造方法の第2例を説明する半導体装置の要部断面図である。

【図50】本願発明者らによって検討された半導体装置(高圧系MISFETおよび低圧系MISFET)の製造方法の第3例を説明する半導体装置の要部断面図である。

【図51】本願発明者らによって見出された半導体装置の製造過程における加工不良を説明する半導体装置の要部断面図である。

【発明を実施するための形態】

【0015】

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0016】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、本実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0017】

また、以下の実施の形態においては、電界効果トランジスタを代表するMISFETをMISと略し、pチャネル型のMISFETをpMIS、nチャネル型のMISFETをnMISと略す。また、以下の実施の形態で記載するMONOS型不揮発性メモリセルについても、上記MISの下位概念に含まれることは勿論である。また、以下の実施の形態において、窒化シリコン、窒化ケイ素またはシリコンナイトライドというときは、Si3N4は勿論であるが、それのみではなく、シリコンの窒化物で類似組成の絶縁膜を含むものとする。また、以下の実施の形態において、ウエハと言うときは、Si(Silicon)単結晶ウエハを主とするが、それのみではなく、SOI(Silicon On Insulator)ウエハ、集積回路をその上に形成するための絶縁膜基板等を指すものとする。その形も円形またはほぼ円形のみでなく、正方形、長方形等も含むものとする。

【0018】

また、以下の実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0019】

まず、本発明の実施の形態による半導体装置の製造方法がより明確となると思われるため、本願発明に先駆けて本願発明者らが検討した高圧系MISFETおよび低圧系MISFETの製造方法について以下に説明する。高圧系MISFETのゲート絶縁膜の厚さは低圧系MISFETのゲート絶縁膜の厚さよりも厚く形成され、また、高圧系MISFETのゲート長は低圧系MISFETのゲート長よりも長く形成されており、これらにより、相対的に高い電圧が印加されても、高圧系MISFETは破壊されずに動作することができる。さらに、耐圧の違いにより、高圧系MISFETの配置密度は、低圧系MISFETの配置密度よりも低くなっている。

【0020】

本願発明者らが検討した高圧系MISFETおよび低圧系MISFETの製造方法の第1例について、図48を用いて以下に説明する。図48には、例えば3.3〜5Vの印加電圧で駆動する高圧系MISFETの要部断面図、例えば1.2Vの印加電圧で駆動する第1低圧系MISFET(低リーク用MISFET)の要部断面図、および例えば1.2Vの印加電圧で駆動する第2低圧系MISFET(高速動作用MISFET)の要部断面図を示す。

【0021】

第1低圧系MISFETは第2低圧系MISFETよりもゲート−ドレイン間の低リークが可能であり、第2低圧系MISFETは第1低圧系MISFETよりも高速動作が可能である。すなわち、第1低圧系MISFETと第2低圧系MISFETとは、ゲート長および配置密度において相違し、第1低圧系MISFETのゲート長が第2低圧系MISFETのゲート長よりも長く、第1低圧系MISFETの配置密度が第2低圧系MISFETの配置密度よりも低い。なお、ここではnチャネル型の高圧系MISFET、第1低圧系MISFET、および第2低圧系MISFETを例示する。

【0022】

まず、高圧系MISFETが形成されるp型の半導体基板101の主面に、例えば厚さ15nm程度のゲート絶縁膜102を形成し、第1および第2低圧系MISFETが形成される半導体基板101の主面に、例えば厚さ3nm程度のゲート絶縁膜103,104を形成する。その後、高圧系MISFETのゲート電極105をゲート絶縁膜102上に形成し、第1低圧系MISFETのゲート電極106をゲート絶縁膜103上に形成し、第2低圧系MISFETのゲート電極107をゲート絶縁膜104上に形成する。高圧系MISFETのゲート長は、例えば800nm程度、第1低圧系MISFETのゲート長は、例えば55nm程度、第2低圧系MISFETのゲート長は、例えば44nm程度である。ゲート電極105,106,107は、例えば多結晶シリコンからなる。

【0023】

次に、高圧系MISFETのゲート電極105をマスクとして、半導体基板101にn型不純物をイオン注入法により導入して、高圧系MISFETの低濃度拡散層108を形成する。同様にして、第1低圧系MISFETの低濃度拡散層109を形成し、第2低圧系MISFETの低濃度拡散層110を形成する。

【0024】

次に、高圧系MISFETのゲート電極105、第1低圧系MISFETのゲート電極106、および第2低圧系MISFETのゲート電極107のそれぞれの側面にサイドウォール111を形成する。その後、高圧系MISFETのゲート電極105、第1低圧系MISFETのゲート電極106、第2低圧系MISFETのゲート電極107、およびサイドウォール111をマスクとして半導体基板101にn型不純物をイオン注入法により導入して、高濃度拡散層112を形成する。

【0025】

次に、自己整合法により、ゲート電極105,106,107の上部および高濃度拡散層112の上面にシリサイド層113を形成する。その後、高圧系MISFET、第1低圧系MISFET、および第2低圧系MISFETを覆う層間絶縁膜、および配線等を形成する。

【0026】

ところで、高圧系MISFETのゲート電極105、第1低圧系MISFETのゲート電極106、および第2低圧系MISFETのゲート電極107のそれぞれの側面に形成されるサイドウォール111のサイドウォール長は、最もゲート長が短くかつ配置密度が高い第2低圧系MISFETに要求される性能から決定される。このため、高圧系MISFETの低濃度拡散層108、第1低圧系MISFETの低濃度拡散層109、および第2低圧系MISFETの低濃度拡散層110を形成する際のイオン注入を、それぞれ異なる工程で行ない、最も適したイオン注入条件(注入エネルギーおよびドーズ量等)を適用することによって、高圧系MISFET、第1低圧系MISFET、および第2低圧系MISFETの性能を満たしている。

【0027】

しかしながら、高圧系MISFETでは、ゲート電極105と高濃度拡散層112の上面に形成されたシリサイド層113との間の電界が強くなり、ゲート電極105と高濃度拡散層112との間および高濃度拡散層112と半導体基板101との間のリーク電流が増加するという問題が生じた。

【0028】

そこで、本願発明者らは、高圧系MISFETのサイドウォールのサイドウォール長を、第1および第2低圧系MISFETのサイドウォールのサイドウォール長よりも長く形成する検討を行った。

【0029】

本願発明者らが検討した高圧系MISFETおよび低圧系MISFETの製造方法の第2例について、図49を用いて以下に説明する。第1および第2低圧系MISFETの構造は、前述の図48に示す構造とほぼ同様である。これに対して、高圧系MISFETでは、ゲート電極105の側面に2層のサイドウォール111,114が形成されている。これにより、高圧系MISFETでは、ゲート電極105と高濃度拡散層112の上面に形成されたシリサイド層113との距離が離れて電界が緩和し、ゲート電極105と高濃度拡散層112との間および高濃度拡散層112と半導体基板101との間のリーク電流を低減することができた。

【0030】

しかしながら、さらに半導体装置の高集積化が進むに伴い、第1低圧系MISFETにおいても、特に、ゲート電極106と高濃度拡散層112との間のリーク電流を低減する要望が強くなってきた。

【0031】

そこで、本願発明者らは、さらに、第1低圧系MISFETのサイドウォールのサイドウォール長を、第2低圧系MISFETのサイドウォールのサイドウォール長よりも長く形成する検討を行った。

【0032】

本願発明者らが検討した高圧系MISFETおよび低圧系MISFETの製造方法の第3例について、図50を用いて以下に説明する。第2低圧系MISFETの構造は、前述の図48に示す構造とほぼ同様である。これに対して、第1低圧系MISFETでは、ゲート電極106の側面に2層のサイドウォール111,114が形成され、高圧系MISFETでは、ゲート電極105の側面に3層のサイドウォール111,114,115が形成されている。これにより、第1低圧系MISFETでは、ゲート電極106と高濃度拡散層112との間の電界が緩和され、高圧系MISFETでは、ゲート電極105と高濃度拡散層112との間の電界がさらに緩和されて、それぞれのリーク電流を低減することができた。

【0033】

ところが、図51に示すように、第2低圧系MISFETにおいて、隣り合うゲート電極107の間の半導体基板101の一部が削れるという問題が生じた。これは、以下の理由によると考えられる。

【0034】

上記2層のサイドウォール111,114および上記3層のサイドウォール111,114,115を形成する際には、高圧系MISFETのゲート電極105、第1低圧系MISFETのゲート電極106、および第2低圧系MISFETのゲート電極107を覆う上層絶縁膜(例えば酸化シリコン膜)を半導体基板101の主面上に堆積する工程と、その上層絶縁膜をエッチバックする工程とを繰り返す必要がある。上層絶縁膜の下には、エッチングストッパとして機能する下層絶縁膜(例えば窒化シリコン膜)116が形成されている。

【0035】

高圧系MISFETまたは第1低圧系MISFETのように、隣り合うゲート電極105の間または隣り合うゲート電極106の間が比較的広い場合は、上層絶縁膜をエッチバックする際のエッチングガスの組成比が変わらないことから、下層絶縁膜116に対する上層絶縁膜のエッチング選択比が変わらない。従って、上層絶縁膜のエッチングは下層絶縁膜116によって止めることができる。これに対して、第2低圧系MISFETのように、隣り合うゲート電極107の間が比較的狭い場合は、エッチングガスを構成する各種ガスが隣り合うゲート電極107の間に均等に入らなくなり、上層絶縁膜をエッチバックする際のエッチングガスの組成比が変わってしまう。このため、下層絶縁膜116に対する上層絶縁膜のエッチング選択比が徐々に変化して、上層絶縁膜のエッチングが下層絶縁膜116によって止まり難くなり、半導体基板101が削れてしまう。

【0036】

(実施の形態1)

本実施の形態1による周辺回路を構成する第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISを有する半導体装置の製造方法を図1〜図17を用いて工程順に説明する。図1〜図17は半導体装置の製造工程中における周辺回路領域に形成された第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISの一例の要部断面図である。各図は、チャネルを各ゲート電極のゲート長方向に沿って切断した要部断面を示している。本実施の形態1においては、第1nMISおよび第1pMISを、例えば高圧系MISFETとして形成し、第2nMISおよび第2pMISを、例えば低リーク用の低圧系MISFETとして形成し、第3nMIS及び第3pMISを、例えば高速動作用の低圧系MISETとして形成している。

【0037】

高圧系MISFETは、例えば入出力(I/O)回路を構成し、低圧系MISFETは、例えばPLL(Phase Locked Loop)、CPU(Central Processing Unit)、またはプロセッサ等の論理回路を構成する。低圧系MISFETには、要求される動作特性に応じて、ゲート材料、ゲート長、ソース・ドレイン領域の不純物濃度、配置密度等の異なる種々の構造が適用されるが、ここでは、低リーク動作が要求される(高速動作よりも低リーク動作を優先する)低リーク用の低圧系MISFETと、高速動作が要求される(低リーク動作よりも高速動作を優先する)高速動作用の低圧系MISFETとを例示する。

【0038】

高圧系MISFETは、例えば3.3〜5Vの印加電圧で駆動し、ゲート電極のゲート長は、例えば800nm程度、ゲート電極の側面に形成されるサイドウォールのサイドウォール長は、例えば80〜90nm程度である。また、低リーク用の低圧系MISFETは、例えば1.2Vの印加電圧で駆動し、ゲート電極のゲート長は、例えば55nm程度、ゲート電極の側面に形成されるサイドウォールのサイドウォール長は、例えば40〜50nm程度である。また、高速動作用の低圧系MISFETは、例えば1.2Vの印加電圧で駆動し、ゲート電極のゲート長は、例えば44nm程度、ゲート電極の側面に形成されるサイドウォールのサイドウォール長は、例えば30nm程度である。

【0039】

すなわち、高圧系MISFETと、低リーク用の低圧系MISFETと、高速動作用の低圧系MISFETとは、構造面において、主にゲート長および配置密度の点で相違する。高圧系MISFETにおけるゲート長が最も長く、以下、低リーク用の低圧系MISFET、高速動作用の低圧系MISFETの順でゲート長は短くなる。また、高圧系MISFETにおける配置密度が最も低く、以下、低リーク用の低圧系MISFET、高速動作用の低圧系MISFETの順で配置密度は高くなる。

【0040】

まず、図1に示すように、半導体基板(この段階では半導体ウエハと称する平面略円形状の半導体の薄板)1の主面に、例えば溝型の素子分離部STIおよびこれに取り囲まれるように配置された活性領域等を形成する。すなわち半導体基板1の所定箇所に分離溝を形成した後、半導体基板1の主面上に、例えば酸化シリコン等からなる絶縁膜を堆積し、さらにその絶縁膜が分離溝内のみに残されるように絶縁膜をCMP(Chemical Mechanical Polishing)法等によって研磨することで、分離溝内に絶縁膜を埋め込む。このようにして素子分離部STIを形成する。

【0041】

次に、半導体基板1にn型不純物を選択的にイオン注入することにより、n型の埋め込みウェルNISOを形成する。続いて第1nMIS領域の半導体基板1にp型不純物を選択的にイオン注入することによりp型のウェルHPWを形成し、第1pMIS領域の半導体基板1にn型不純物を選択的にイオン注入することによりn型のウェルHNWを形成する。同様に、第2nMIS領域および第3nMIS領域の半導体基板1にp型不純物を選択的にイオン注入することによりp型のウェルPWを形成し、第2pMIS領域および第3pMIS領域の半導体基板1にn型不純物を選択的にイオン注入することによりn型のウェルNWを形成する。

【0042】

次に、第1nMIS領域、第1pMIS領域、第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域のそれぞれの半導体基板1に所定の不純物をイオン注入する。これにより、第1nMIS領域、第1pMIS領域、第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域のそれぞれの半導体基板1にチャネル形成用の半導体領域D1,D2,D3,D4,D5,D6を形成する。

【0043】

次に、半導体基板1に対して酸化処理を施すことにより、半導体基板1の主面に、例えば酸化シリコンからなる厚さ10〜20nm程度のゲート絶縁膜4Aを形成する。続いて第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域のゲート絶縁膜4Aを除去した後、半導体基板1に対して酸化処理を施す。これにより、第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域の半導体基板1の主面に、例えば酸化シリコンからなる厚さ1〜5nm程度のゲート絶縁膜4を形成する。ゲート絶縁膜4は、酸化シリコンに限らず、酸化ハフニウム(HfSiON)などの高誘電率膜で形成してもよい。

【0044】

次に、図2に示すように、半導体基板1の主面上に、例えば非晶質シリコンからなる導電膜10をCVD(Chemical Vapor Deposition)法により堆積する。導電膜10の厚さは、例えば100nm程度である。

【0045】

次に、図3に示すように、第1nMIS領域、第2nMIS領域、および第3nMIS領域の導電膜10にn型不純物をイオン注入法等によって導入することにより、n型の導電膜10naを形成する。また、第1pMIS領域、第2pMIS領域、および第3pMIS領域の導電膜10にp型不純物をイオン注入法等によって導入することにより、p型の導電膜10pを形成する。

【0046】

次に、図4に示すように、導電膜10na,10pをフォトリソグラフィおよびドライエッチングを用いてパターニングすることにより、導電膜10naからなる第1nMISのゲート電極GHn、導電膜10pからなる第1pMISのゲート電極GHp、導電膜10naからなる第2nMISのゲート電極GMn、導電膜10pからなる第2pMISのゲート電極GMp、導電膜10naからなる第3nMISのゲート電極GLn、および導電膜10pからなる第3pMISのゲート電極GLpを形成する。

【0047】

活性領域における第1nMISのゲート電極GHnおよび第1pMISのゲート電極GHpのゲート長は、例えば800nm程度である。また、活性領域における第2nMISのゲート電極GMnおよび第2pMISのゲート電極GMpのゲート長は、例えば55nm程度であり、隣り合うゲート電極GMnとゲート電極GMn、隣り合うゲート電極GMnとゲート電極GMp、隣り合うゲート電極GMpとゲート電極GMpとの最小間隔は、例えば110nm程度である。また、活性領域における第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのゲート長は、例えば44nm程度であり、隣り合うゲート電極GLnとゲート電極GLn、隣り合うゲート電極GLnとゲート電極GLp、隣り合うゲート電極GLpとゲート電極GLpとの最小間隔は、例えば88nm程度である。

【0048】

次に、図5に示すように、第1nMIS領域の半導体基板1の主面にn型不純物、例えばヒ素をイオン注入することにより、第1nMIS領域の半導体基板1の主面にn−型の半導体領域13をゲート電極GHnに対して自己整合的に形成する。同様に、第1pMIS領域の半導体基板1の主面にp型不純物、例えばフッ化ボロンをイオン注入することにより、第1pMIS領域の半導体基板1の主面にp−型の半導体領域14をゲート電極GHpに対して自己整合的に形成する。

【0049】

次に、第2nMIS領域の半導体基板1の主面にn型不純物、例えばヒ素をイオン注入することにより、第2nMIS領域の半導体基板1の主面にn−型の半導体領域24をゲート電極GMnに対して自己整合的に形成する。同様に、第2pMIS領域の半導体基板1の主面にp型不純物、例えばフッ化ボロンをイオン注入することにより、第2pMIS領域の半導体基板1の主面にp−型の半導体領域25をゲート電極GMpに対して自己整合的に形成する。

【0050】

次に、第3nMIS領域の半導体基板1の主面にn型不純物、例えばヒ素をイオン注入することにより、第3nMIS領域の半導体基板1の主面にn−型の半導体領域18をゲート電極GLnに対して自己整合的に形成する。同様に、第3pMIS領域の半導体基板1の主面にp型不純物、例えばフッ化ボロンをイオン注入することにより、第3pMIS領域の半導体基板1の主面にp−型の半導体領域19をゲート電極GLpに対して自己整合的に形成する。

【0051】

次に、図6に示すように、半導体基板1の主面上に第1絶縁膜(例えば窒化シリコン膜)7bをCVD法により堆積する。第1絶縁膜7bの厚さは、例えば10nm程度である。続いて、第1絶縁膜7b上に第2絶縁膜(例えば酸化シリコン膜)7mをCVD法により堆積する。第2絶縁膜7mの厚さは、例えば50〜60nm程度である。ここでドライエッチング選択比およびウェットエッチング選択比(第1絶縁膜7bのエッチング速度と第2絶縁膜7mのエッチング速度との比)が高くなるように、第1絶縁膜7bの材料および第2絶縁膜7mの材料は選択される。また、第1絶縁膜7bおよび第2絶縁膜7mのそれぞれの厚さは、第1nMISのゲート電極GHnおよび第1pMISのゲート電極GHpのそれぞれの側面に形成されるサイドウォールのサイドウォール長(例えば80〜90nm程度)を目標に設定される。

【0052】

次に、図7に示すように、第2絶縁膜7mを異方性のドライエッチングでエッチバックする。これにより、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの上面上、ならびにこれらゲート電極GHn,GHp,GMn,GMp,GLn,GLpが形成されていない半導体基板1の主面上の第2絶縁膜7mを完全にまたは一部(例えば1〜3nm程度)が残るように除去する。

【0053】

この際、第1nMIS領域および第1pMIS領域において、ゲート電極GHn,GHpの上面上およびこれらゲート電極GHn,GHpが形成されていない半導体基板1の主面上の第2絶縁膜7mを完全に除去しても、第3nMIS領域および第3pMIS領域では、ゲート電極GLn,GLpが形成されていない半導体基板1の主面上に第2絶縁膜7mが残ることがある。これは、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間に、第2絶縁膜7mが埋め込まれていること、および異方性のドライエッチングに用いられるエッチングガスの組成比が徐々に変化してエッチング速度が遅くなること等に起因すると考えられる。

【0054】

このような場合は、異方性のドライエッチングを行った後、ウェットエッチングを行い、ゲート電極GLn,GLpが形成されていない半導体基板1の主面上に残った第2絶縁膜7mを除去してもよい。隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間が第2絶縁膜7mによって埋め込まれていても、エッチング液が第2絶縁膜7mの表面が接触する界面から毛細管現象により侵入して、ゲート電極GLn,GLpが形成されていない半導体基板1の主面上に残った第2絶縁膜7mを除去することができる。

【0055】

次に、図8に示すように、第1nMIS領域および第1pMIS領域をフォトレジストパターンRP1で覆い、第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングまたは等方性のドライエッチングにより加工する。等方性のエッチングを用いているので、上方向と横方向とから第2絶縁膜7mはエッチングされる。

【0056】

これにより、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの側面に、横方向(ゲート長方向)の幅が20〜30nm程度の第2絶縁膜7mを残存させる。第1絶縁膜7bと第2絶縁膜7mとのエッチング選択比が高いことから、第1絶縁膜7bはエッチングされ難く、半導体基板1の主面が削られることはない。

【0057】

次に、図9に示すように、フォトレジストパターンRP1を除去した後、第1nMIS領域、第1pMIS領域、第2nMIS領域、および第2pMIS領域をフォトレジストパターンRP2で覆い、第3nMIS領域および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングにより除去する。前の工程と同様、第1絶縁膜7bと第2絶縁膜7mとのエッチング選択比が高いことから、第1絶縁膜7bはエッチングされ難く、半導体基板1の主面が削られることはない。

【0058】

次に、図10に示すように、フォトレジストパターンRP2を除去した後、半導体基板1の主面上に第3絶縁膜(例えば酸化シリコン膜)7tをCVD法により堆積する。第3絶縁膜7tの厚さは、例えば20〜30nm程度である。第3絶縁膜7tの厚さは、第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのそれぞれの側面に形成されるサイドウォールのサイドウォール長(例えば30nm程度)を目標にして設定される。

【0059】

次に、図11に示すように、第3絶縁膜7tを異方性のドライエッチングでエッチバックした後、露出している第1絶縁膜7bをドライエッチングまたはウェットエッチングで除去する。これにより、第1nMISおよび第1pMISでは、ゲート電極GHn,GHpの側面に第1絶縁膜7b、第2絶縁膜7m、および第3絶縁膜7tからなるサイドウォールSWHを形成する。また、第2nMISおよび第2pMISでは、ゲート電極GMn,GMpの側面に第1絶縁膜7b、第2絶縁膜7m、および第3絶縁膜7tからなるサイドウォールSWMを形成する。また、第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの側面に第1絶縁膜7bおよび第3絶縁膜7tからなるサイドウォールSWLを形成する。上記サイドウォールSWHのサイドウォール長は、例えば80〜90nm程度であり、上記サイドウォールSWMのサイドウォール長は、例えば40〜50nm程度であり、上記サイドウォールSWLのサイドウォール長は、例えば30nm程度である。

【0060】

このように、互いにサイドウォール長の異なる複数のサイドウォールSWL,SWM,SWHを形成する製造工程において(本実施の形態1では3種類)、異方性のドライエッチングの回数を減らして、異方性のドライエッチングと等方性のウェットエッチングまたは等方性のドライエッチングとの組み合わせにより、上記サイドウォールSWL,SWM,SWHを形成している。従って、特に、配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の削れを防止することができる。

【0061】

また、第2nMISおよび第2pMISのゲート電極GMn,GMpの側面に形成されたサイドウォールSWMの半導体基板1の主面からの高さは、ゲート電極GMn,GMpの半導体基板1の主面からの高さよりも低い。同様に、第3nMISおよび第3pMISのゲート電極GLn,GLpの側面に形成されたサイドウォールSWLの半導体基板1の主面からの高さは、ゲート電極GLn,GLpの半導体基板1の主面からの高さよりも低い。さらに、上記サイドウォールSWMの半導体基板1の主面からの高さと上記サイドウォールSWLの半導体基板1の主面からの高さは、同じである。

【0062】

このように、隣り合うゲート電極の間隔が相対的に小さい領域において、上記サイドウォールSWM,SWLの半導体基板1の主面からの高さを低くすることにより、後述の工程において半導体基板1の主面上に形成される層間絶縁膜の被覆性(埋め込み性)を向上させることができる。層間絶縁膜の被覆性(埋め込み性)が向上すると、第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間に層間絶縁膜が入りやすくなり、ボイド(す)が形成され難くなる。仮にボイドが形成されると、後述の工程において層間絶縁膜にコンタクトホールを形成すると、コンタクトホールの形状不良が生じ、隣り合うコンタクトホールの間で短絡(ショート)が発生する恐れがある。

【0063】

一方、第1nMISおよび第1pMISのゲート電極GHn,GHpの側面に形成されたサイドウォールSWHの半導体基板1の主面からの高さは、ゲート電極GHn,GHpの半導体基板1の主面からの高さとほぼ同じである。さらに、上記サイドウォールSWHの半導体基板1の主面からの高さは、上記サイドウォールSWM,SWLの半導体基板1の主面からの高さよりも高い。このように上記サイドウォールSWHの半導体基板1の主面からの高さを他の上記サイドウォールSWM,SWLと同様に低くしていないのは、以下の理由による。すなわち、第1nMISおよび第1pMISの配置密度が、第2nMIS、第2pMIS、第3nMIS、および第3pMISの配置密度よりも広いことから、後述の工程において半導体基板1の主面上に形成される層間絶縁膜の被覆性(埋め込み性)が良好であるので、上記サイドウォールSWHの半導体基板1の主面からの高さを低くする必要がないからである。

【0064】

また、第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの側面に形成されるサイドウォールSWLのサイドウォール長は、第3絶縁膜7tの厚さと、第3絶縁膜7tの異方性のドライエッチングのエッチング条件とによって決まるので、配置密度が高く、かつ高速動作が要求される第3nMISおよび第3pMISの動作特性の制御が容易となる。

【0065】

次に、図12に示すように、第1nMIS領域、第2nMIS領域、および第3nMIS領域の半導体基板1の主面に、フォトレジストパターン22をマスクとしてn型不純物、例えばヒ素およびリンをイオン注入することにより、第1nMISのゲート電極GHn、第2nMISのゲート電極GMn、および第3nMISのゲート電極GLnに対してn+型の半導体領域23を自己整合的に形成する。

【0066】

これにより、n−型の半導体領域13とn+型の半導体領域23とからなる第1nMISのソース・ドレイン領域SDが形成され、n−型の半導体領域24とn+型の半導体領域23とからなる第2nMISのソース・ドレイン領域SDが形成され、n−型の半導体領域18とn+型の半導体領域23とからなる第3nMISのソース・ドレイン領域SDが形成される。

【0067】

次に、図13に示すように、第1pMIS領域、第2pMIS領域、および第3pMIS領域の半導体基板1の主面に、フォトレジストパターン20をマスクとしてp型不純物、例えばボロンまたはフッ化ボロンをイオン注入することにより、第1pMISのゲート電極GHp、第2pMISのゲート電極GMp、および第3pMISのゲート電極GLpに対してp+型の半導体領域21を自己整合的に形成する。

【0068】

これにより、p−型の半導体領域14とp+型の半導体領域21とからなる第1pMISのソース・ドレイン領域SDが形成され、p−型の半導体領域25とn+型の半導体領域21とからなる第2pMISのソース・ドレイン領域SDが形成され、p−型の半導体領域19とp+型の半導体領域21とからなる第3pMISのソース・ドレイン領域SDが形成される。

【0069】

次に、図14に示すように、第1nMISのゲート電極GHnの上部およびn+型の半導体領域23の上面、第1pMISのゲート電極GHpの上部およびp+型の半導体領域21の上面、第2nMISのゲート電極GMnの上部およびn+型の半導体領域23の上面、第2pMISのゲート電極GMpの上部およびp+型の半導体領域21の上面、第3nMISのゲート電極GLnの上部およびn+型の半導体領域23の上面、第3pMISのゲート電極GLpの上部およびp+型の半導体領域21の上面にシリサイド層3をサリサイド(Salicide:Self-Align silicide)プロセスにより形成する。シリサイド層3としては、例えばニッケルシリサイドまたはコバルトシリサイド等が使用される。

【0070】

シリサイド層3を形成することにより、シリサイド層3と、後述の工程においてその上部に形成されるプラグ等との接続抵抗を低減することができる。また、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLp自身の抵抗、ならびにソース・ドレイン領域SD自身の抵抗を低減することができる。

【0071】

ここで、第1nMISおよび第1pMISでは、ゲート電極GHn,GHpの露出した上面からシリサイド反応が進む。一方、第2nMISおよび第2pMISでは、ゲート電極GMn,GMpの露出した上面と両側面とからシリサイド反応が進み、同様に、第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの露出した上面と両側面とからシリサイド反応が進む。従って、ゲート電極GMn,GMp,GLn,GLpの上部の両側面にもシリサイド層3が形成されるので、ゲート電極GMn,GMp,GLn,GLpの抵抗をより低くすることができる。

【0072】

また、図示はしていないが、第2nMISおよび第2pMISのゲート電極GMn,GMpならびに第3nMISおよび第3pMISのゲート電極GLn,GLpにおいて、上部の両側面から進むシリサイド反応により形成されるシリサイド層3が一体になると、シリサイド層3の全体の膜厚が、上面から形成されるシリサイド層3の膜厚と上部の両側面から形成されるシリサイド層3の膜厚の合計の膜厚となる。これにより、第1nMISおよび第1pMISのゲート電極GHn,GHpに形成されたシリサイド層3の膜厚よりも、第2nMISおよび第2pMISのゲート電極GMn,GMpならびに第3nMISおよび第3pMISのゲート電極GLn,GLpに形成されたシリサイド層3の膜厚の方が厚くなる場合も考えられる。

【0073】

次に、図15に示すように、半導体基板1の主面上に、絶縁膜として窒化シリコン膜9aをCVD法により堆積する。この窒化シリコン膜9aは、後述の工程においてコンタクトホールを形成する際に、エッチングストッパとして機能する。

【0074】

次に、図16に示すように、絶縁膜として酸化シリコン膜9bをCVD法により堆積して、酸化シリコン膜9bの表面をCMP法により研磨することによって、窒化シリコン膜9aおよび酸化シリコン膜9bからなる層間絶縁膜9を形成する。前述したように、第3nMISおよび第3pMISでは、サイドウォールSWLの半導体基板1の主面からの高さが、ゲート電極GLn,GLpの半導体基板1の主面からの高さよりも低く形成されているため、被覆性(埋め込み性)よく層間絶縁膜9を形成することができる。層間絶縁膜9の被覆性(埋め込み性)が向上することにより、後述の工程において層間絶縁膜9に形成されるコンタクトホールの形状不良を防ぐことができる。

【0075】

次に、図17に示すように、第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISにおいて、それぞれのゲート電極GHn,GHp,GMn,GMp,GLn,GLpの上部およびそれぞれのソース・ドレイン領域SDの上面に形成されたシリサイド層3に達するコンタクトホールCAを形成する。図17では、説明簡略化のため、第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISのソース・ドレイン領域SDに達するコンタクトホールCAのみを例示している。

【0076】

次に、コンタクトホールCA内にプラグPAを形成する。プラグPAは、例えばチタンと窒化チタンとを積層した相対的に薄いバリア膜と、そのバリア膜に包まれるように形成されたタングステンまたはアルミニウム等からなる相対的に厚い導電膜とからなる積層膜によって構成される。その後、層間絶縁膜9上に、例えば銅またはアルミニウムを主成分とする第1層目の配線M1を形成する。

【0077】

以上に説明した製造過程により、周辺回路領域に第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISが略完成する。これ以降は、通常の半導体装置の製造工程を経ることにより、さらに上層の配線を形成して、不揮発性メモリを有する半導体装置を製造する。

【0078】

なお、前述した実施の形態1では、第1nMISおよび第1pMISのゲート電極GHn,GHpのゲート長よりも短く、第3nMISおよび第3pMISのゲート電極GLn,GLpのゲート長よりも長いゲート長のゲート電極を備えるMISFETとして、第2nMISおよび第2pMISを例示したが、これに限定されるものではない。例えばメモリ領域に形成される不揮発性メモリセルを構成するMISFETを例示することもできる。

【0079】

近年、電気的に書き換え可能な不揮発性メモリセルとして、窒化膜などのトラップ準位を有する絶縁膜を電荷蓄積層とするMONOS(Metal Oxide Nitride Oxide Silicon)型不揮発性メモリセルが注目されている。この場合、データ記憶に寄与する電荷は、絶縁体である窒化膜の離散トラップに蓄積されるため、蓄積ノードを取り巻く酸化膜のどこか一部に欠陥が生じて異常リークがおきても、電荷蓄積層の電荷が全て抜けてしまうことがないため、データ保持の信頼度を向上させることが可能である。

【0080】

しかしながら、MONOS型不揮発性メモリセルがアレイ状に配置された不揮発性メモリを含む半導体装置については、以下に説明する種々の技術的課題が存在する。

【0081】

信頼性の高い不揮発性メモリを実現するためには、不揮発性メモリの周辺回路にも高い信頼性が要求される。例えば周辺回路には、外部から与えられる電源電圧よりも高い電圧を発生させる昇圧回路および発生させたその高い電圧を不揮発性メモリセルに印加する回路等が必要である。そのため、不揮発性メモリを動作させる際には、不揮発性メモリセルよりも高い耐圧性能を有する半導体素子が周辺回路に必要となる。

【0082】

そこで、本願発明者らは、相対的に低い電圧(例えば電源電圧と同じ電圧)で動作する低圧系MISFETと相対的に高い電圧(例えば電源電圧よりも高い電圧)で動作する高圧系MISFETとを周辺回路に形成することによって、所望する動作性能および耐圧性能を実現している。

【0083】

本実施の形態1による不揮発性メモリセル、ならびに周辺回路を構成する第1nMIS、第1pMIS、第3nMIS、および第3pMISを有する半導体装置の製造方法を図18〜図37を用いて工程順に説明する。図18〜図37は半導体装置の製造工程中におけるメモリ領域に形成された不揮発性メモリセル、ならびに周辺回路領域に形成された第1nMIS、第1pMIS、第3nMIS、および第3pMISの要部断面図である。各図は、チャネルをゲート電極のゲート長方向に沿って切断した要部断面を示している。また、第1nMISおよび第1pMISを、例えば高圧系MISFETとして形成し、第3nMISおよび第3pMISを、例えば高速動作用の低圧系MISFETとして形成している。

【0084】

不揮発性メモリセルは、選択用nMISの選択ゲート電極の片側面にサイドウォール形状のメモリ用nMISのメモリゲート電極を形成したスプリットゲート構造のMONOS型不揮発性メモリセルを例示しており、選択ゲート電極のメモリゲート電極と反対側の側面およびメモリゲート電極の側面に形成されるサイドウォールのサイドウォール長は、40〜50nm程度である。

【0085】

周辺回路を構成する第1nMISおよび第1pMISは、前述したものと同じであり、例えば3.3〜5Vの印加電圧で駆動し、そのゲート電極の側面に形成されるサイドウォールのサイドウォール長は、例えば80〜90nm程度である。また、周辺回路を構成する第3nMISおよび第3pMISは、前述したものと同じであり、例えば1.2Vの印加電圧で駆動し、そのゲート電極の側面に形成されるサイドウォールのサイドウォール長は、例えば30nm程度である。

【0086】

すなわち、周辺回路領域に形成される第1nMISおよび第1pMISと、周辺回路領域に形成される第3nMISおよび第3pMISと、メモリ領域に形成される不揮発性メモリセルとは、ゲート長および配置密度の点で相違する。第1nMISおよび第1pMISにおけるゲート長が最も長く、以下、不揮発性メモリセル、第3nMISおよび第3pMISの順でゲート長は短くなる。また、第1nMISおよび第1pMISにおける配置密度が最も低く、以下、不揮発性メモリセル、第3nMISおよび第3pMISの順で配置密度は高くなる。

【0087】

まず、図18に示すように、前述の図1を用いて説明したと同様にして、半導体基板1の主面に素子分離部STIを形成し、n型の埋め込みウェルNISO、p型のウェルHPW、n型のウェルHNW、p型のウェルPW、n型のウェルNWを形成する。その後、メモリ領域の半導体基板1にp型不純物を選択的にイオン注入する。これによりメモリ領域の半導体基板1に、選択用nMISのチャネル形成用のp型の半導体領域5を形成する。同様に、第1nMIS領域、第1pMIS領域、第3nMIS領域、および第3pMIS領域のそれぞれの半導体基板1に所定の不純物をイオン注入する。これにより、第1nMIS領域、第1pMIS領域、第3nMIS領域、および第3pMIS領域のそれぞれの半導体基板1にチャネル形成用の半導体領域D1,D2,D5,D6を形成する。

【0088】

次に、第1nMIS領域および第1pMIS領域の半導体基板1の主面に、例えば酸化シリコンからなる厚さ10〜20nm程度のゲート絶縁膜4Aを形成し、メモリ領域、第3nMIS領域、および第3pMIS領域の半導体基板1の主面に、例えば酸化シリコンからなる厚さ1〜5nm程度のゲート絶縁膜4を形成する。

【0089】

次に、図19に示すように、半導体基板1の主面上に、例えば非晶質シリコンからなる導電膜10をCVD法により堆積した後、メモリ領域の導電膜10にn型不純物をイオン注入法等によって導入することにより、n型の導電膜10nを形成する。導電膜10,10nの厚さは、例えば100nm程度である。

【0090】

次に、図20に示すように、メモリ領域のn型の導電膜10nをフォトリソグラフィおよびドライエッチングを用いてパターニングする。これにより、メモリ領域に、n型の導電膜10nからなる選択用nMISの選択ゲート電極CGを形成する。メモリ領域の選択ゲート電極CGのゲート長は、例えば100nm程度である。

【0091】

次に、図21に示すように、選択ゲート電極CGおよびフォトレジストパターンをマスクとして、メモリ領域の半導体基板1の主面にn型不純物、例えばヒ素またはリンをイオン注入することにより、メモリ用nMISのチャネル形成用のn型の半導体領域8を形成する。

【0092】

次に、図22に示すように、半導体基板1の主面上に、例えば酸化シリコンからなる絶縁膜6b、トラップ準位を有する絶縁膜として例えば窒化シリコンからなる電荷蓄積層CSL、および例えば酸化シリコンからなる絶縁膜6tを順次形成する。絶縁膜6bは、例えば熱酸化法またはISSG(In-Situ Steam Generation)酸化法等により形成され、電荷蓄積層CSLは、例えばCVD法等により形成され、絶縁膜6tは、例えばCVD法またはISSG酸化法等により形成される。絶縁膜6b、電荷蓄積層CSL、および絶縁膜6tからなる積層膜(以下、絶縁膜6b,6tおよび電荷蓄積層CSLと記す)の厚さは、20nm程度を例示することができる。また、絶縁膜6b,6tは、例えば窒素を含んだ酸化シリコンで形成してもよく、電荷蓄積層CSLは、例えば酸化アルミニウム(アルミナ)、酸化ハフニウム、または酸化タンタルなど、窒化シリコンよりも高い誘電率を有する高誘電率膜により形成してもよい。なお、図中では絶縁膜6b,6tおよび電荷蓄積層CSLの表記を6b/CSL/6tとして表現している。

【0093】

次に、半導体基板1の主面上に低抵抗多結晶シリコンからなる導電膜を堆積する。この導電膜はCVD法により形成され、その厚さは、例えば50nm程度である。続いて、フォトリソグラフィおよび異方性のドライエッチングを用いて、この導電膜を加工する。これにより、メモリ領域に、選択ゲート電極CGの両側面に絶縁膜6b,6tおよび電荷蓄積層CSLを介してサイドウォール11を形成する。

【0094】

次に、図23に示すように、フォトレジストパターンをマスクとして、そこから露出するサイドウォール11をエッチングする。これにより、メモリ領域において、選択ゲート電極CGの片側面のみにメモリ用nMISのメモリゲート電極MGを形成する。メモリゲート電極MGのゲート長は、例えば65nm程度である。

【0095】

次に、メモリ領域において、選択ゲート電極CGとメモリゲート電極MGとの間および半導体基板1とメモリゲート電極MGとの間の絶縁膜6b,6tおよび電荷蓄積層CSLを残して、その他の領域の絶縁膜6b,6tおよび電荷蓄積層CSLを選択的にエッチングする。

【0096】

次に、図24に示すように、第1nMIS領域および第3nMIS領域の導電膜10にn型不純物をイオン注入法等によって導入することにより、n型の導電膜10naを形成する。また、第1pMIS領域および第3pMIS領域の導電膜10にp型不純物をイオン注入法等によって導入することにより、p型の導電膜10pを形成する。

【0097】

次に、図25に示すように、周辺回路領域の導電膜10na,10pをフォトリソグラフィおよびドライエッチングを用いてパターニングすることにより、導電膜10naからなる第1nMISのゲート電極GHn、導電膜10pからなる第1pMISのゲート電極GHp、導電膜10naからなる第3nMISのゲート電極GLn、および導電膜10pからなる第3pMISのゲート電極GLpを形成する。活性領域における第1nMISのゲート電極GHnおよび第1pMISのゲート電極GHpのゲート長は、例えば800nm程度である。また、活性領域における第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのゲート長は、例えば44nm程度であり、隣り合うゲート電極GLnとゲート電極GLnとの最小間隔、隣り合うゲート電極GLnとゲート電極GLpとの最小間隔、または隣り合うゲート電極GLpとゲート電極GLpとの最小間隔は、例えば88nm程度である。

【0098】

次に、第1nMIS領域の半導体基板1の主面にn型不純物、例えばヒ素をイオン注入することにより、第1nMIS領域の半導体基板1の主面にn−型の半導体領域13をゲート電極GHnに対して自己整合的に形成する。同様に、第1pMIS領域の半導体基板1の主面にp型不純物、例えばフッ化ボロンをイオン注入することにより、第1pMIS領域の半導体基板1の主面にp−型の半導体領域14をゲート電極GHpに対して自己整合的に形成する。

【0099】

次に、図26に示すように、半導体基板1の主面上に、例えば酸化シリコンからなる厚さ10nm程度の絶縁膜をCVD法により堆積した後、この絶縁膜を異方性のドライエッチングで加工する。これにより、メモリ領域では、選択ゲート電極CGのメモリゲート電極MGと反対側の側面およびメモリゲート電極MGの側面に、周辺回路領域では、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第3nMISのゲート電極GLn、第3pMISのゲート電極GLpのそれぞれの側面にサイドウォール15を形成する。サイドウォール15のスペーサ長は、例えば3〜6nm程度である。

【0100】

サイドウォール15が形成されることによって、選択ゲート電極CGと半導体基板1との間のゲート絶縁膜4の露出していた側面、ならびにメモリゲート電極MGと半導体基板1との間の絶縁膜6b,6tおよび電荷蓄積層CSLの露出していた側面を保護することができる。また、サイドウォール15が形成されることによって、後述の第3nMIS領域にn−型の半導体領域を形成する工程および後述の第3pMIS領域にp−型の半導体領域を形成する工程において、n−型の半導体領域およびp−型の半導体領域の実効チャネル長が大きくなり、第3nMISおよび第3pMISの短チャネル効果を抑制することができる。

【0101】

次に、その端部がメモリ領域の選択ゲート電極CGの上面に位置してメモリゲート電極MG側の選択ゲート電極CGの一部およびメモリゲート電極MGを覆うフォトレジストパターン16を形成した後、選択ゲート電極CG、メモリゲート電極MG、およびフォトレジストパターン16をマスクとしてn型不純物、例えばヒ素を半導体基板1の主面にイオン注入することにより、半導体基板1の主面にn−型の半導体領域2adを選択ゲート電極CGに対して自己整合的に形成する。

【0102】

次に、図27に示すように、その端部がメモリ領域の選択ゲート電極CGの上面に位置してメモリゲート電極MGと反対側の選択ゲート電極CGの一部を覆うフォトレジストパターン17を形成した後、選択ゲート電極CG、メモリゲート電極MG、およびフォトレジストパターン17をマスクとしてn型不純物、例えばヒ素を半導体基板1の主面にイオン注入することにより、半導体基板1の主面にn−型の半導体領域2asをメモリゲート電極MGに対して自己整合的に形成する。

【0103】

ここでは、先にn−型の半導体領域2adを形成し、その後n−型の半導体領域2asを形成したが、先にn−型の半導体領域2asを形成し、その後n−型の半導体領域2adを形成してもよい。また、n−型の半導体領域2adを形成するn型不純物のイオン注入に続いて、p型不純物、例えばボロンを半導体基板1の主面にイオン注入し、n−型の半導体領域2adの下部を囲むようにp型の半導体領域を形成してもよい。

【0104】

次に、図28に示すように、第3nMIS領域の半導体基板1の主面にn型不純物、例えばヒ素をイオン注入することにより、第3nMIS領域の半導体基板1の主面にn−型の半導体領域18をゲート電極GLnに対して自己整合的に形成する。同様に、第3pMIS領域の半導体基板1の主面にp型不純物、例えばフッ化ボロンをイオン注入することにより、第3pMIS領域の半導体基板1の主面にp−型の半導体領域19をゲート電極GLpに対して自己整合的に形成する。

【0105】

次に、前述の図6〜図11を用いて説明したと同様な製造方法により、メモリ領域では、選択ゲート電極CGのメモリゲート電極MGと反対側の側面およびメモリゲート電極MGの側面にサイドウォールSWを形成し、周辺回路領域の第1nMISおよび第1pMISでは、ゲート電極GHn,GHpの側面にサイドウォールSWHを形成し、周辺回路領域の第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの側面にサイドウォールSWLを形成する。

【0106】

まず、図29に示すように、半導体基板1の主面上に第1絶縁膜(例えば窒化シリコン膜)7bをCVD法により堆積する。第1絶縁膜7bの厚さは、例えば10nm程度である。続いて、第1絶縁膜7b上に第2絶縁膜(例えば酸化シリコン膜)7mをCVD法により堆積する。第2絶縁膜7mの厚さは、例えば50〜60nm程度である。

【0107】

次に、図30に示すように、第2絶縁膜7mを異方性のドライエッチングでエッチバックする。これにより、メモリ領域では、選択ゲート電極CGおよびメモリゲート電極MGの上面上、ならびに選択ゲート電極CGおよびメモリゲート電極MGが形成されていない半導体基板1の主面上の第2絶縁膜7mを完全にまたは一部(例えば1〜3nm程度)が残るように除去する。同様に、周辺回路領域では、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの上面上、ならびにこれらゲート電極GHn,GHp,GLn,GLpが形成されていない半導体基板1の主面上の第2絶縁膜7mを完全にまたは一部(例えば1〜3nm程度)が残るように除去する。

【0108】

次に、図31に示すように、第1nMIS領域および第1pMIS領域をフォトレジストパターンRP1で覆い、メモリ領域、第3nMIS領域、および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングまたは等方性のドライエッチングにより加工する。これにより、メモリ領域では、選択ゲート電極CGのメモリゲート電極MGと反対側の側面およびメモリゲート電極MGの側面に、横方向(ゲート長方向)の幅が20〜30nm程度の第2絶縁膜7mを残存させる。同様に、周辺回路領域では、第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのそれぞれの側面に、横方向(ゲート長方向)の幅が20〜30nm程度の第2絶縁膜7mを残存させる。

【0109】

次に、図32に示すように、フォトレジストパターンRP1を除去した後、メモリ領域、第1nMIS領域、および第1pMIS領域をフォトレジストパターンRP2で覆い、第3nMIS領域および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングにより除去する。

【0110】

次に、図33に示すように、フォトレジストパターンRP2を除去した後、半導体基板1の主面上に第3絶縁膜(例えば酸化シリコン膜)7tをCVD法により堆積する。第3絶縁膜7tの厚さは、例えば20〜30nm程度である。

【0111】

次に、図34に示すように、第3絶縁膜7tを異方性のドライエッチングでエッチバックした後、露出している第1絶縁膜7bをドライエッチングまたはウェットエッチングで除去する。これにより、メモリ領域では、選択ゲート電極CGのメモリゲート電極MGと反対側の側面およびメモリゲート電極MGの側面に第1絶縁膜7b、第2絶縁膜7m、および第3絶縁膜7tからなるサイドウォールSWを形成する。また、周辺回路領域では、第1nMISのゲート電極GHnおよび第1pMISのゲート電極GHpのそれぞれの側面に第1絶縁膜7b、第2絶縁膜7m、および第3絶縁膜7tからなるサイドウォールSWHを形成し、第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのそれぞれの側面に第1絶縁膜7bおよび第3絶縁膜7tからなるサイドウォールSWLを形成する。上記サイドウォールSWのサイドウォール長は、例えば40〜50nm程度であり、上記サイドウォールSWHのサイドウォール長は、例えば80〜90nm程度であり、上記サイドウォールSWLのサイドウォール長は、例えば30nm程度である。

【0112】

次に、図35に示すように、第1pMIS領域および第3pMIS領域の半導体基板1の主面に、フォトレジストパターンRP3をマスクとしてp型不純物、例えばボロンまたはフッ化ボロンをイオン注入することにより、第1pMISのゲート電極GHpおよび第3pMISのゲート電極GLpに対してp+型の半導体領域21を自己整合的に形成する。

【0113】

これにより、p−型の半導体領域14とp+型の半導体領域21とからなる第1pMISのソース・ドレイン領域SDが形成され、p−型の半導体領域19とp+型の半導体領域21とからなる第3pMISのソース・ドレイン領域SDが形成される。

【0114】

次に、図36に示すように、第1nMIS領域、メモリ領域、および第3nMIS領域の半導体基板1の主面に、フォトレジストパターンRP4をマスクとしてn型不純物、例えばヒ素およびリンをイオン注入することにより、メモリ領域では、n+型の半導体領域2bを選択ゲート電極CGおよびメモリゲート電極MGに対して自己整合的に形成し、周辺回路領域では、第1nMISのゲート電極GHnおよび第3nMISのゲート電極GLnに対してn+型の半導体領域23を自己整合的に形成する。

【0115】

これにより、メモリ領域では、n−型の半導体領域2adおよびn+型の半導体領域2bからなるドレイン領域Drm、n−型の半導体領域2asおよびn+型の半導体領域2bからなるソース領域Srmが形成される。また、周辺回路領域では、n−型の半導体領域13とn+型の半導体領域23とからなる第1nMISのソース・ドレイン領域SDが形成され、n−型の半導体領域18とn+型の半導体領域23とからなる第3nMISのソース・ドレイン領域SDが形成される。

【0116】

次に、図37に示すように、メモリ領域では、選択ゲート電極CGの上部、メモリゲート電極MGの上部、およびn+型の半導体領域2bの上面にシリサイド層3を形成する。同様に、周辺回路領域では、第1nMISのゲート電極GHnの上部およびn+型の半導体領域23の上面、第1pMISのゲート電極GHpの上部およびp+型の半導体領域21の上面、第3nMISのゲート電極GLnの上部およびn+型の半導体領域23の上面、第3pMISのゲート電極GLpの上部およびp+型の半導体領域21の上面にそれぞれシリサイド層3を形成する。

【0117】

その後は、前述の製造方法と同様にして、層間絶縁膜を形成し、続いて、メモリ領域では、ドレイン領域Drm上のシリサイド層3に達するコンタクトホール、周辺回路領域では、第1nMIS、第1pMIS、第3nMIS、および第3pMISにおいて、それぞれのゲート電極GHn、GHp、GLn、GLpの上部およびそれぞれのソース・ドレイン領域SDの上面に形成されたシリサイド層3に達するコンタクトホールを形成する。続いて、これらコンタクトホール内にプラグを形成した後、第1層目の配線を形成する。

【0118】

以上に説明した製造方法により、メモリ領域に不揮発性メモリセル、ならびに周辺回路領域に第1nMIS、第1nMIS、第3nMIS、および第3pMISが略完成する。

【0119】

このように、本実施の形態1では、互いにサイドウォール長の異なる複数のサイドウォールSWL,SWM(またはSW),SWHを形成する製造工程において(本実施の形態2では3種類)、異方性のドライエッチングのみでなく、異方性のドライエッチングと等方性のウェットエッチングまたは等方性のドライエッチングとを組み合わせることにより、上記サイドウォールSWL,SWM(またはSW),SWHを形成している。従って、異方性のドライエッチングの回数が減ることにより、特に、周辺回路領域に形成される配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極Gpnとの間の半導体基板1の削れを防止することができる。

【0120】

さらに、配置密度が高い第3nMISおよび第3pMISにおいては、サイドウォールSWLの半導体基板1の主面からの高さを低くできるので、これらを覆うように形成される層間絶縁膜9の被覆性(埋め込み性)が向上して、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間に層間絶縁膜9が入りやすくなり、コンタクトホールCAの形状不良の原因の一つとなるボイドが形成され難くなる。

【0121】

(実施の形態2)

本実施の形態2による周辺回路を構成する第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISを有する半導体装置の製造方法を図38〜図42を用いて工程順に説明する。図38〜図42は半導体装置の製造工程中における周辺回路領域に形成された第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISの一例の要部断面図である。各図は、チャネルをゲート電極のゲート長方向に沿って切断した要部断面を示している。本実施の形態2においては、前述した実施の形態1と同様に、第1nMISおよび第1pMISを、例えば高圧系MISFETとして形成し、第2nMISおよび第2pMISを、例えば低リーク用の低圧系MISFETとして形成し、第3nMIS及び第3pMISを、例えば高速動作用の低圧系MISETとして形成している。

【0122】

半導体基板1の主面上に第1絶縁膜7bおよび第2絶縁膜7mを堆積する工程(前述の図6を用いて説明した製造工程)までの製造過程は、前述した実施の形態1と同様であるためその説明を省略する。

【0123】

前述した実施の形態1において図6を用いて説明した製造工程に続いて、図38に示すように、第2絶縁膜7mを異方性のドライエッチングでエッチバックする。ここでは、第1nMISおよび第1pMISに要求される動作特性を得るために必要となるサイドウォールのサイドウォール長(80〜90nm程度)を有するように、第2絶縁膜7mを残存させる。これにより、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの側面に、横方向(ゲート長方向)の幅が80〜90nm程度の第2絶縁膜7mを残存させる。

【0124】

ここで、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの上面上、ならびに第1nMISのゲート電極GHnおよび第1pMISのゲート電極GHpが形成されていない半導体基板1の主面上の第2絶縁膜7mを完全にまたは一部(例えば1〜3nm程度)が残るように除去する。第1絶縁膜7bと第2絶縁膜7mとのエッチング選択比が高いことから、第1絶縁膜7bはエッチングされ難い。

【0125】

しかし、第2nMIS領域および第2pMIS領域では、隣り合うゲート電極GMnとゲート電極GMnとの間、隣り合うゲート電極GMnとゲート電極GMpとの間、および隣り合うゲート電極GMpとゲート電極GMpとの間の半導体基板1の主面上の第2絶縁膜7mは完全に除去せずに、一部(例えば3〜7nm程度)を残す。同様に、第3nMIS領域および第3pMIS領域では、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の主面上の第2絶縁膜7mは完全に除去せずに、一部(例えば5〜10nm程度)を残す。なお、第2nMIS領域および第2pMIS領域では、隣り合うゲート電極GMnとゲート電極GMn、隣り合うゲート電極GMnとゲート電極GMp、および隣り合うゲート電極GMpとゲート電極GMpとの間隔によっては、半導体基板1の主面上の第2絶縁膜7mを完全に除去してもよい。

【0126】

このように、第2nMIS領域および第2pMIS領域において、隣り合うゲート電極GMnとゲート電極GMnとの間、隣り合うゲート電極GMnとゲート電極GMpとの間、および隣り合うゲート電極GMpとゲート電極GMpとの間の半導体基板1の主面上、ならびに第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の主面上に、第2絶縁膜7mの一部を残すことにより、第1絶縁膜7bが異方性のドライエッチングのエッチングガスに晒されるのを防止することができるので、第1絶縁膜7bはエッチングされることなく残存する。

【0127】

続いて、ウェットエッチングを行い、第2nMIS領域および第2pMIS領域においては、隣り合うゲート電極GMnとゲート電極GMnとの間、隣り合うゲート電極GMnとゲート電極GMpとの間、および隣り合うゲート電極GMpとゲート電極GMpとの間の半導体基板1の主面上、ならびに第3nMIS領域および第3pMIS領域においては、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の主面上に残存している第2絶縁膜7mを除去する。第1絶縁膜7bはウェットエッチングのエッチング液には晒されるが、ウェットエッチングによるダメージは異方性のドライエッチングのダメージよりも遥かに小さい。なお、このような半導体基板1の主面上に残存している第2絶縁膜7mは、後述の工程における等方性のエッチングにおいても除去することは可能であるため、必要に応じて上記ウェットエッチングは行われる。

【0128】

次に、図39に示すように、第1nMIS領域および第1pMIS領域をフォトレジストパターンRP5で覆い、第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングまたは等方性のドライエッチングにより加工する。等方性のエッチングを用いているので、上方向と横方向とから第2絶縁膜7mはエッチングされる。

【0129】

ここでは、第2nMISおよび第2pMISに要求される動作特性を得るために必要となるサイドウォールのサイドウォール長(40〜50nm)を有するように、第2絶縁膜7mを残存させる。これにより、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの側面に、横方向(ゲート長方向)の幅が40〜50nm程度の第2絶縁膜7mを残存させる。第1絶縁膜7bと第2絶縁膜7mとのエッチング選択比が高いことから、第1絶縁膜7bはエッチングされ難く、半導体基板1の主面が削られることはない。

【0130】

次に、図40に示すように、フォトレジストパターンRP5を除去した後、第1nMIS領域、第1pMIS領域、第2nMIS領域、および第2pMIS領域をフォトレジストパターンRP6で覆い、第3nMIS領域および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングまたは等方性のドライエッチングにより加工する。等方性のエッチングを用いているので、上方向と横方向とから第2絶縁膜7mはエッチングされる。

【0131】

ここでは、第3nMISおよび第3pMISに要求される動作特性を得るために必要となるサイドウォールのサイドウォール長(30nm程度)を有するように、第2絶縁膜7mを残存させる。これにより、第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのそれぞれの側面に、横方向(ゲート長方向)の幅が30nm程度の第2絶縁膜7mを残存させる。第1絶縁膜7bと第2絶縁膜7mとのエッチング選択比が高いことから、第1絶縁膜7bはエッチングされ難く、半導体基板1の主面が削られることはない。

【0132】

次に、図41に示すように、フォトレジストパターンRP6を除去した後、露出している第1絶縁膜7bをドライエッチングまたはウェットエッチングで除去する。

【0133】

これにより、第1nMISおよび第1pMISでは、ゲート電極GHn,GHpの側面に第1絶縁膜7bおよび第2絶縁膜7mからなるサイドウォールSWHを形成する。また、第2nMISおよび第2pMISでは、ゲート電極GMn,GMpの側面に第1絶縁膜7bおよび第2絶縁膜7mからなるサイドウォールSWMを形成する。また、第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの側面に第1絶縁膜7bおよび第2絶縁膜7mからなるサイドウォールSWLを形成する。

【0134】

第1nMISおよび第1pMISに設けられたサイドウォールSWHのサイドウォール長が最も長く、以下、第2nMISおよび第2pMISに設けられたサイドウォールSWMのサイドウォール長、第3nMISおよび第3pMISに設けられたサイドウォールSWLのサイドウォール長の順に短くなる。上記サイドウォールSWHのサイドウォール長は、例えば80〜90nm程度であり、上記サイドウォールSWMのサイドウォール長は、例えば40〜50nm程度であり、上記サイドウォールSWLのサイドウォール長は、例えば30nm程度である。

【0135】

このように、第3nMISおよび第3pMISでは、サイドウォールSWLのサイドウォール長が、第1nMISおよび第1pMISのサイドウォールSWHのサイドウォール長、ならびに第2nMISおよび第2pMISのサイドウォールSWMのサイドウォール長よりも短く、かつ隣り合うサイドウォールSWLの間の半導体基板1の面積が極力広くとれることから、第1絶縁膜7bをエッチングする際のエッチング速度の変動を抑えることができる。

【0136】

また、第1nMISおよび第1pMISに設けられたサイドウォールSWHの半導体基板1の主面からの高さが最も高く、以下、第2nMISおよび第2pMISに設けられたサイドウォールSWMの半導体基板1の主面からの高さ、第3nMISおよび第3pMISに設けられたサイドウォールSWLの半導体基板1の主面からの高さの順に低くなる。

【0137】

次に、図42に示すように、n−型の半導体領域13とn+型の半導体領域23とからなる第1nMISのソース・ドレイン領域SDが形成され、n−型の半導体領域24とn+型の半導体領域23とからなる第2nMISのソース・ドレイン領域SDが形成され、n−型の半導体領域18とn+型の半導体領域23とからなる第3nMISのソース・ドレイン領域SDが形成される。

【0138】

さらに、p−型の半導体領域14とp+型の半導体領域21とからなる第1pMISのソース・ドレイン領域SDが形成され、p−型の半導体領域25とp+型の半導体領域21とからなる第2pMISのソース・ドレイン領域SDが形成され、p−型の半導体領域19とp+型の半導体領域21とからなる第3pMISのソース・ドレイン領域SDが形成される。

【0139】

次に、第1nMISのゲート電極GHnの上部およびn+型の半導体領域23の上面、第1pMISのゲート電極GHpの上部およびp+型の半導体領域21の上面、第2nMISのゲート電極GMnの上部およびn+型の半導体領域23の上面、第2pMISのゲート電極GMpの上部およびp+型の半導体領域21の上面、第3nMISのゲート電極GLnの上部およびn+型の半導体領域23の上面、第3pMISのゲート電極GLpの上部およびp+型の半導体領域21の上面にシリサイド層3をサリサイドプロセスにより形成する。

【0140】

ここで、第1nMISおよび第1pMISでは、ゲート電極GHn,GHpの露出した上面からシリサイド反応が進む。一方、第2nMISおよび第2pMISでは、ゲート電極GMn,GMpの露出した上面と両側面とからシリサイド反応が進み、同様に、第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの露出した上面と両側面とからシリサイド反応が進む。従って、ゲート電極GMn,GMp,GLn,GLpの上部の両側面にもシリサイド層3が形成されるので、ゲート電極GMn,GMp,GLn,GLpの抵抗をより低くすることができる。

【0141】

また、第3nMISおよび第3pMISでは、相対的にゲート長が短いことから、ゲート電極GLn,GLpの上部の両側面から進むシリサイド反応により形成されるシリサイド層3が一体となり易い。この場合、シリサイド層3の全体の膜厚が、上面から形成されるシリサイド層3の膜厚と上部の両側面から形成されるシリサイド層3の膜厚の合計の厚さとなる。これにより、第3nMISおよび第3pMISのゲート電極GLn,GLpに形成されたシリサイド層3の膜厚は、第1nMISおよび第1pMISのゲート電極GHn,GHpに形成されたシリサイド層3の膜厚よりも厚くなり、ゲート電極GLn,GLpの抵抗をより低くし、高速動作が可能となる。

【0142】

また、図示はしていないが、第2nMISおよび第2pMISのゲート電極GMn,GMpにおいても、同様に、ゲート電極GMn,GMpの上部の両側面から進むシリサイド反応により形成されるシリサイド層3が一体になると、シリサイド層3の全体の膜厚が、上面から形成されるシリサイド層3の膜厚と上部の両側面から形成されるシリサイド層3の膜厚の合計の膜厚となる。これにより、第2nMISおよび第2pMISのゲート電極GMn,GMpに形成されたシリサイド層3の膜厚の方が、第1nMISおよび第1pMISのゲート電極GHn,GHpに形成されたシリサイド層3の膜厚よりも厚くなる場合も考えられる。

【0143】

このような場合は、第1nMISおよび第1pMISのゲート電極GHn,GHpに形成されたシリサイド層3よりも、第2nMISおよび第2pMISのゲート電極GMn,GMpに形成されたシリサイド層3の膜厚の方が厚く、第2nMISおよび第2pMISのゲート電極GMn,GMpに形成されたシリサイド層3の膜厚よりも、第3nMISおよび第3pMISのゲート電極GLn,GLpに形成されたシリサイド層3の膜厚の方が厚くなると考えられる。

【0144】

その後は、前述した実施の形態1の製造方法と同様にして、層間絶縁膜、コンタクトホール、プラグ、および配線等を順次形成する。

【0145】

配置密度が高い第3nMISおよび第3pMISでは、サイドウォールSWLの半導体基板1の主面からの高さを低くできるので、これらを覆うように形成される層間絶縁膜の被覆性(埋め込み性)が向上して、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間に層間絶縁膜が入りやすくなり、コンタクトホールの形状不良の原因の一つとなるボイドが形成され難くなる。

【0146】

なお、前述した実施の形態1と同様に、第1nMISおよび第1pMISのゲート電極GHn,GHpのゲート長よりも短く、第3nMISおよび第3pMISのゲート電極GLn,GLpのゲート長よりも長いゲート長のゲート電極を備えるMISFETとして、第2nMISおよび第2pMISを例示したが、これに限定されるものではない。例えばメモリ領域に形成される不揮発性メモリセルを例示することもできる。

【0147】

図43に、本実施の形態2による不揮発性メモリセル、ならびに周辺回路を構成する第1nMIS、第1pMIS、第3nMIS、および第3pMISを有する半導体装置の一例である要部断面図を示す。

【0148】

図43に示すように、第1nMIS、第1pMIS、第3nMIS、および第3pMISの構造および製造方法は、前述したものと同じである。また、不揮発性メモリセルのゲート電極(選択ゲート電極CGおよびメモリゲート電極MG)の構造および製造方法は、第2nMISおよび第2pMISの構造および製造方法において異なるが、サイドウォールSWの構造および製造方法は、前述の図38〜図41を用いて説明したものとほぼ同じである。

【0149】

従って、第1nMISおよび第1pMISに設けられたサイドウォールSWHのサイドウォール長(例えば80〜90nm)が最も長く、以下、不揮発性メモリセルに設けられたサイドウォールSWのサイドウォール長(例えば40〜50nm)、第3nMISおよび第3pMISに設けられたサイドウォールSWLのサイドウォール長(例えば30nm)の順に短くなる。また、第1nMISおよび第1pMISに設けられたサイドウォールSWHの半導体基板1の主面からの高さが最も高く、以下、不揮発性メモリセルに設けられたサイドウォールSWの半導体基板1の主面からの高さ、第3nMISおよび第3pMISに設けられたサイドウォールSWLの半導体基板1の主面からの高さの順に低くなる。

【0150】

このように、本実施の形態2では、互いにサイドウォール長の異なる複数のサイドウォールSWL,SWM(またはSW),SWHを形成する製造工程において(本実施の形態2では3種類)、異方性のドライエッチングを1回行った後は、等方性のウェットエッチングまたは等方性のドライエッチングを複数回(本実施の形態2では2回)行うことにより、上記サイドウォールSWL,SWM(またはSW),SWHを形成している。従って、特に、周辺回路領域に形成される配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の削れを防止することができる。

【0151】

(実施の形態3)

本実施の形態3による周辺回路を構成する第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISを有する半導体装置の製造方法を図44〜図47を用いて工程順に説明する。図44〜図47は半導体装置の製造工程中における周辺回路領域に形成される第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISの一例の要部断面図である。各図は、チャネルをゲート電極のゲート長方向に沿って切断した要部断面を示している。本実施の形態3においては、前述した実施の形態1と同様に、第1nMISおよび第1pMISを、例えば高圧系MISFETとして形成し、第2nMISおよび第2pMISを、例えば低リーク用の低圧系MISFETとして形成し、第3nMIS及び第3pMISを、例えば高速動作用の低圧系MISETとして形成している。

【0152】

半導体基板1の主面上に第1絶縁膜7bおよび第2絶縁膜7mを堆積する工程(前述の図6を用いて説明した製造工程)までの製造過程は、前述した実施の形態1と同様であるためその説明を省略する。

【0153】

前述した実施の形態1において図6を用いて説明した製造工程に続いて、図44に示すように、第2絶縁膜7mを異方性のドライエッチングでエッチバックする。ここでは、第1nMISおよび第1pMISに要求される動作特性を得るために必要となるサイドウォールのサイドウォール長(80〜90nm程度)を有するように、第2絶縁膜7mを残存させる。これにより、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの側面に、横方向(ゲート長方向)の幅が80〜90nm程度の第2絶縁膜7mを残存させる。第1絶縁膜7bと第2絶縁膜7mとのエッチング選択比が高いことから、第1絶縁膜7bはエッチングされ難くい。

【0154】

また、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの上面上、ならびにこれらゲート電極GHn,GHp,GMn,GMp,GLn,GLpが形成されていない半導体基板1の主面上の第2絶縁膜7mを完全に除去する。

【0155】

次に、図45に示すように、第1nMIS領域および第1pMIS領域をフォトレジストパターンRP5で覆い、第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングまたは等方性のドライエッチングにより加工する。等方性のエッチングを用いているので、上方向と横方向とから第2絶縁膜7mはエッチングされる。

【0156】

ここでは、第2nMISおよび第2pMISに要求される動作特性を得るために必要となるサイドウォールのサイドウォール長(40〜50nm)を有するように、第2絶縁膜7mを残存させる。これにより、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの側面に、横方向(ゲート長方向)の幅が40〜50nm程度の第2絶縁膜7mを残存させる。第1絶縁膜7bと第2絶縁膜7mとのエッチング選択比が高いことから、第1絶縁膜7bはエッチングされ難く、半導体基板1の主面が削られることはない。

【0157】

次に、図46に示すように、フォトレジストパターンRP5を除去した後、第1nMIS領域、第1pMIS領域、第2nMIS領域、および第2pMIS領域をフォトレジストパターンRP6で覆い、第3nMIS領域および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングまたは等方性のドライエッチングにより加工する。等方性のエッチングを用いているので、上方向と横方向とから第2絶縁膜7mはエッチングされる。

【0158】

ここでは、第3nMISおよび第3pMISに要求される動作特性を得るために必要となるサイドウォールのサイドウォール長(30nm程度)を有するように、第2絶縁膜7mを残存させる。これにより、第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのそれぞれの側面に、横方向(ゲート長方向)の幅が30nm程度の第2絶縁膜7mを残存させる。第1絶縁膜7bと第2絶縁膜7mとのエッチング選択比が高いことから、第1絶縁膜7bはエッチングされ難く、半導体基板1の主面が削られることはない。

【0159】

次に、図47に示すように、フォトレジストパターンRP6を除去した後、露出している第1絶縁膜7bをドライエッチングまたはウェットエッチングで除去する。

【0160】

これにより、第1nMISおよび第1pMISでは、ゲート電極GHn,GHpの側面に第1絶縁膜7bおよび第2絶縁膜7mからなるサイドウォールSWHを形成する。また、第2nMISおよび第2pMISでは、ゲート電極GMn,GMpの側面に第1絶縁膜7bおよび第2絶縁膜7mからなるサイドウォールSWMを形成する。また、第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの側面に第1絶縁膜7bおよび第2絶縁膜7mからなるサイドウォールSWLを形成する。

【0161】

第1nMISおよび第1pMISに設けられたサイドウォールSWHのサイドウォール長が最も長く、以下、第2nMISおよび第2pMISに設けられたサイドウォールSWMのサイドウォール長、第3nMISおよび第3pMISに設けられたサイドウォールSWLのサイドウォール長の順に短くなる。上記サイドウォールSWHのサイドウォール長は、例えば80〜90nm程度であり、上記サイドウォールSWMのサイドウォール長は、例えば40〜50nm程度であり、上記サイドウォールSWLのサイドウォール長は、例えば30nm程度である。

【0162】

また、第1nMISおよび第1pMISに設けられたサイドウォールSWHの半導体基板1の主面からの高さが最も高く、以下、第2nMISおよび第2pMISに設けられたサイドウォールSWMの半導体基板1の主面からの高さ、第3nMISおよび第3pMISに設けられたサイドウォールSWLの半導体基板1の主面からの高さの順に低くなる。

【0163】

その後、前述した実施の形態2と同様にして、前述の図43に示したように、n−型の半導体領域13とn+型の半導体領域23とからなる第1nMISのソース・ドレイン領域SD、n−型の半導体領域24とn+型の半導体領域23とからなる第2nMISのソース・ドレイン領域SD、およびn−型の半導体領域18とn+型の半導体領域23とからなる第3nMISのソース・ドレイン領域SDを形成する。さらに、p−型の半導体領域14とp+型の半導体領域21とからなる第1pMISのソース・ドレイン領域SD、p−型の半導体領域25とp+型の半導体領域21とからなる第2pMISのソース・ドレイン領域SD、p−型の半導体領域19とp+型の半導体領域21とからなる第3pMISのソース・ドレイン領域SDを形成する。

【0164】

さらに、第1nMISのゲート電極GHnの上部およびn+型の半導体領域23の上面、第1pMISのゲート電極GHpの上部およびp+型の半導体領域21の上面、第2nMISのゲート電極GMnの上部およびn+型の半導体領域23の上面、第2pMISのゲート電極GMpの上部およびp+型の半導体領域21の上面、第3nMISのゲート電極GLnの上部およびn+型の半導体領域23の上面、第3pMISのゲート電極GLpの上部およびp+型の半導体領域21の上面にシリサイド層3を形成する。

【0165】

その後は、前述した実施の形態1の製造方法と同様にして、層間絶縁膜、コンタクトホール、プラグ、および配線等を順次形成する。

【0166】

このように、本実施の形態3によれば、前述した実施の形態2と同様の効果を得ることができる。

【0167】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0168】

例えば、前記実施の形態では、互いにサイドウォール長の異なる3種類のMISFETに本願発明を適用したが、これに限定されるものではなく、互いにサイドウォール長の異なる2種類または4種類以上のMISFETにも適用することができる。

【産業上の利用可能性】

【0169】

本発明は、互いにサイドウォール長の異なるサイドウォールを有する複数の半導体素子を備える半導体装置に適用することができる。

【符号の説明】

【0170】

1 半導体基板

2ad n−型の半導体領域

2as n−型の半導体領域

2b n+型の半導体領域

3 シリサイド層

4,4A ゲート絶縁膜

5 p型の半導体領域

6b,6t 絶縁膜

7b 第1絶縁膜

7m 第2絶縁膜

7t 第3絶縁膜

8 n型の半導体領域

9 層間絶縁膜

9a 窒化シリコン膜

9b 酸化シリコン膜

10 導電膜

10n,10na n型の導電膜

10p p型の導電膜

11 サイドウォール

13 n−型の半導体領域

14 p−型の半導体領域

15 サイドウォール

16,17 フォトレジストパターン

18 n−型の半導体領域

19 p−型の半導体領域

20 フォトレジストパターン

21 p+型の半導体領域

22 フォトレジストパターン

23 n+型の半導体領域

24 n−型の半導体領域

25 p−型の半導体領域

101 半導体基板

102,103,104 ゲート絶縁膜

105,106,107 ゲート電極

108,109,110 低濃度拡散層

111 サイドウォール

112 高濃度拡散層

113 シリサイド層

114,115 サイドウォール

116 下層絶縁膜

CA コンタクトホール

CG 選択ゲート電極

CSL 電荷蓄積層

D1,D2,D3,D4,D5,D6 半導体領域

Drm ドレイン領域

GHn 第1nMISのゲート電極

GHp 第1pMISのゲート電極

GMn 第2nMISのゲート電極

GMp 第2pMISのゲート電極

GLn 第3nMISのゲート電極

GLp 第3pMISのゲート電極

HNW n型のウェル

HPW p型のウェル

M1 配線

MG メモリゲート電極

NISO n型の埋め込みウェル

NW n型のウェル

PA プラグ

PW p型のウェル

RP1,RP2,RP3,RP4,RP5,RP6 フォトレジストパターン

SD ソース・ドレイン領域

Srm ソース領域

STI 素子分離部

SW,SWH,SWL,SWM サイドウォール

【技術分野】

【0001】

本発明は、半導体装置の製造方法および半導体装置に関し、特に、互いにゲート長および配置密度の異なる複数の電界効果トランジスタが同一基板に製造された半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

例えば特開平5−326513号公報(特許文献1)には、ドライエッチングによりSiO2スペーサ層を形成したのち、基板表面に残る熱酸化SiO2膜をウェットエッチングにより除去することにより、基板表面のダメージを抑制する技術が開示されている。

【0003】

また、特開2005−5508号公報(特許文献2)には、サイドウォールスペーサ形成層をドライエッチングしてサイドウォールスペーサを形成し、その後、低電圧トランジスタ形成領域のサイドウォールスペーサをウェットエッチングにより除去する技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5−326513号公報

【特許文献2】特開2005−5508号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、細分化された用途に対応するため、要求される各特性(耐圧、リーク電流、動作速度など)に合わせた複数のMISFET(Metal Insulator Semiconductor Field Effect Transistor)を同一基板上に形成している。そのため、要求される各特性を得ようとすると、例えばゲート絶縁膜の厚さ、ゲート長、サイドウォールの厚さ、または配置密度などが互いに異なる複数のMISFETが同一基板上に形成される場合がある。しかし、要求される各特性に合わせた複数のMISFETを同一基板上に形成しようとすると、各製造工程における加工条件の制御が困難となる、または製造プロセスが複雑となる恐れもある。そこで、要求される各特性を満たす複数のMISFETを歩留まり良く製造する技術、あるいは簡易な製造プロセスにより製造する技術が求められている。

【0006】

本発明の目的は、互いに異なる特性を備える複数の電界効果トランジスタを同一基板上に有する半導体装置の製造歩留まりを向上させることのできる技術を提供することにある。

【0007】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0008】

本願において開示される発明のうち、代表的なものの一実施の形態を簡単に説明すれば、次のとおりである。

【0009】

この実施の形態は、高圧系MISFETを第1領域に有し、低リーク用低圧系MISFETを第2領域に有し、高速動作用低圧系MISFETを第3領域に有する半導体装置の製造方法であって、第1領域に第1ゲート絶縁膜を介して第1ゲート電極を形成し、第2領域に第2ゲート絶縁膜を介して第2ゲート電極を形成し、第3領域に第3ゲート絶縁膜を介して第3ゲート電極を形成する工程と、半導体基板の主面上に、第1ゲート電極、第2ゲート電極、および第3ゲート電極を覆うように第1絶縁膜を形成する工程と、第1絶縁膜上に第2絶縁膜を形成する工程と、第2絶縁膜を異方性のドライエッチングにより加工して、第1ゲート電極の側面、第2ゲート電極の側面、および第3ゲート電極の側面にそれぞれ第2絶縁膜を残す工程と、等方性のドライエッチングまたは等方性のウェットエッチングにより、第2ゲート電極の側面および第3ゲート電極の側面に残された第2絶縁膜を加工する工程と、等方性のドライエッチングまたは等方性のウェットエッチングにより、第3ゲート電極の側面に残された第2絶縁膜を除去する工程と、半導体基板の主面上に、第1ゲート電極、第1ゲート電極の側面に残された第2絶縁膜、第2ゲート電極、第2ゲート電極の側面に残された第2絶縁膜、および第3ゲート電極を覆うように第3絶縁膜を形成する工程と、第3絶縁膜を異方性のドライエッチングにより加工して、第1絶縁膜および第2絶縁膜を介した第1ゲート電極の側面、第1絶縁膜および第2絶縁膜を介した第2ゲート電極の側面、第1絶縁膜を介した第3ゲート電極の側面にそれぞれ第3絶縁膜を残す工程と、露出している第1絶縁膜を除去する工程と、を含み、第1ゲート電極の側面に形成された第1絶縁膜、第2絶縁膜、および第3絶縁膜によって第1サイドウォールを構成し、第2ゲート電極の側面に形成された第1絶縁膜、第2絶縁膜、および第3絶縁膜によって第2サイドウォールを構成し、第3ゲート電極の側面に形成された第1絶縁膜および第3絶縁膜によって第3サイドウォールを構成する。

【0010】

また、この実施の形態は、高圧系MISFETを第1領域に有し、低リーク用低圧系MISFETを第2領域に有し、および高速動作用低圧系MISFETを第3領域に有する半導体装置の製造方法であって、第1領域に第1ゲート絶縁膜を介して第1ゲート電極を形成し、第2領域に第2ゲート絶縁膜を介して第2ゲート電極を形成し、第3領域に第3ゲート絶縁膜を介して第3ゲート電極を形成する工程と、半導体基板の主面上に、第1ゲート電極、第2ゲート電極、および第3ゲート電極を覆うように第1絶縁膜を形成する工程と、第1絶縁膜上に第2絶縁膜を形成する工程と、第2絶縁膜を異方性のドライエッチングにより加工して、第1ゲート電極の側面、第2ゲート電極の側面、および第3ゲート電極の側面にそれぞれ第2絶縁膜を残す工程と、等方性のドライエッチングまたは等方性のウェットエッチングにより、第2ゲート電極の側面および第3ゲート電極の側面に残された第2絶縁膜を加工する工程と、等方性のドライエッチングまたは等方性のウェットエッチングにより、第3ゲート電極の側面に残された第3絶縁膜を加工する工程と、露出している第1絶縁膜を除去する工程と、を含み、第1ゲート電極の側面に形成された第1絶縁膜および第2絶縁膜によって第1サイドウォールを構成し、第2ゲート電極の側面に形成された第1絶縁膜および第2絶縁膜によって第2サイドウォールを構成し、第3ゲート電極の側面に形成された第1絶縁膜および第2絶縁膜によって第3サイドウォールを構成する。

【0011】

また、この実施の形態は、高圧系MISFETを第1領域に有し、低リーク用低圧系MISFETを第2領域に有し、および高速動作用低圧系MISFETを第3領域に有し、高圧系MISFETでは、第1ゲート長の第1ゲート電極の側面に第1サイドウォール長の第1サイドウォールが備わり、低リーク用低圧系MISFETでは、第2ゲート長の第2ゲート電極の側面に第2サイドウォール長の第2サイドウォールが備わり、高速動作用低圧系MISFETでは、第3ゲート長の第3ゲート電極の側面に第3サイドウォール長の第3サイドウォールが備わる半導体装置であって、第1サイドウォール長よりも第2サイドウォール長が短く、第2サイドウォール長よりも第3サイドウォール長が短く、さらに、第1サイドウォールの半導体基板の主面からの高さよりも第2サイドウォールの半導体基板の主面からの高さが低く、第2サイドウォールの半導体基板の主面からの高さよりも第3サイドウォールの半導体基板の主面からの高さが低い。

【発明の効果】

【0012】

本願において開示される発明のうち、代表的なものの一実施の形態によって得られる効果を簡単に説明すれば以下のとおりである。

【0013】

互いに異なる特性を備える複数の電界効果トランジスタを同一基板上に有する半導体装置の製造歩留まりを向上させることができる。

【図面の簡単な説明】

【0014】

【図1】本発明の実施の形態1による半導体装置の製造工程を説明する半導体装置の要部断面図である。

【図2】図1に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図3】図2に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図4】図3に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図5】図4に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図6】図5に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図7】図6に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図8】図7に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図9】図8に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図10】図9に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図11】図10に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図12】図11に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図13】図12に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図14】図13に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図15】図14に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図16】図15に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図17】図16に続く半導体装置の製造工程中の図1と同じ箇所の半導体装置の要部断面図である。

【図18】本発明の実施の形態1による半導体装置の製造工程の他の例を説明する半導体装置の要部断面図である。

【図19】図18に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図20】図19に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図21】図20に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図22】図21に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図23】図22に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図24】図23に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図25】図24に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図26】図25に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図27】図26に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図28】図27に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図29】図28に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図30】図29に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図31】図30に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図32】図31に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図33】図32に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図34】図33に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図35】図34に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図36】図35に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図37】図36に続く半導体装置の製造工程中の図18と同じ箇所の半導体装置の要部断面図である。

【図38】本発明の実施の形態2による半導体装置の製造工程を説明する半導体装置の要部断面図である。

【図39】図38に続く半導体装置の製造工程中の図38と同じ箇所の半導体装置の要部断面図である。

【図40】図39に続く半導体装置の製造工程中の図38と同じ箇所の半導体装置の要部断面図である。

【図41】図40に続く半導体装置の製造工程中の図38と同じ箇所の半導体装置の要部断面図である。

【図42】図41に続く半導体装置の製造工程中の図38と同じ箇所の半導体装置の要部断面図である。

【図43】本発明の実施の形態2による半導体装置の製造工程の他の例を説明する半導体装置の要部断面図である。

【図44】本発明の実施の形態3による半導体装置の製造工程を説明する半導体装置の要部断面図である。

【図45】図44に続く半導体装置の製造工程中の図44と同じ箇所の半導体装置の要部断面図である。

【図46】図45に続く半導体装置の製造工程中の図44と同じ箇所の半導体装置の要部断面図である。

【図47】図46に続く半導体装置の製造工程中の図44と同じ箇所の半導体装置の要部断面図である。

【図48】本願発明者らによって検討された半導体装置(高圧系MISFETおよび低圧系MISFET)の製造方法の第1例を説明する半導体装置の要部断面図である。

【図49】本願発明者らによって検討された半導体装置(高圧系MISFETおよび低圧系MISFET)の製造方法の第2例を説明する半導体装置の要部断面図である。

【図50】本願発明者らによって検討された半導体装置(高圧系MISFETおよび低圧系MISFET)の製造方法の第3例を説明する半導体装置の要部断面図である。

【図51】本願発明者らによって見出された半導体装置の製造過程における加工不良を説明する半導体装置の要部断面図である。

【発明を実施するための形態】

【0015】

以下の実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0016】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、本実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0017】

また、以下の実施の形態においては、電界効果トランジスタを代表するMISFETをMISと略し、pチャネル型のMISFETをpMIS、nチャネル型のMISFETをnMISと略す。また、以下の実施の形態で記載するMONOS型不揮発性メモリセルについても、上記MISの下位概念に含まれることは勿論である。また、以下の実施の形態において、窒化シリコン、窒化ケイ素またはシリコンナイトライドというときは、Si3N4は勿論であるが、それのみではなく、シリコンの窒化物で類似組成の絶縁膜を含むものとする。また、以下の実施の形態において、ウエハと言うときは、Si(Silicon)単結晶ウエハを主とするが、それのみではなく、SOI(Silicon On Insulator)ウエハ、集積回路をその上に形成するための絶縁膜基板等を指すものとする。その形も円形またはほぼ円形のみでなく、正方形、長方形等も含むものとする。

【0018】

また、以下の実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0019】

まず、本発明の実施の形態による半導体装置の製造方法がより明確となると思われるため、本願発明に先駆けて本願発明者らが検討した高圧系MISFETおよび低圧系MISFETの製造方法について以下に説明する。高圧系MISFETのゲート絶縁膜の厚さは低圧系MISFETのゲート絶縁膜の厚さよりも厚く形成され、また、高圧系MISFETのゲート長は低圧系MISFETのゲート長よりも長く形成されており、これらにより、相対的に高い電圧が印加されても、高圧系MISFETは破壊されずに動作することができる。さらに、耐圧の違いにより、高圧系MISFETの配置密度は、低圧系MISFETの配置密度よりも低くなっている。

【0020】

本願発明者らが検討した高圧系MISFETおよび低圧系MISFETの製造方法の第1例について、図48を用いて以下に説明する。図48には、例えば3.3〜5Vの印加電圧で駆動する高圧系MISFETの要部断面図、例えば1.2Vの印加電圧で駆動する第1低圧系MISFET(低リーク用MISFET)の要部断面図、および例えば1.2Vの印加電圧で駆動する第2低圧系MISFET(高速動作用MISFET)の要部断面図を示す。

【0021】

第1低圧系MISFETは第2低圧系MISFETよりもゲート−ドレイン間の低リークが可能であり、第2低圧系MISFETは第1低圧系MISFETよりも高速動作が可能である。すなわち、第1低圧系MISFETと第2低圧系MISFETとは、ゲート長および配置密度において相違し、第1低圧系MISFETのゲート長が第2低圧系MISFETのゲート長よりも長く、第1低圧系MISFETの配置密度が第2低圧系MISFETの配置密度よりも低い。なお、ここではnチャネル型の高圧系MISFET、第1低圧系MISFET、および第2低圧系MISFETを例示する。

【0022】

まず、高圧系MISFETが形成されるp型の半導体基板101の主面に、例えば厚さ15nm程度のゲート絶縁膜102を形成し、第1および第2低圧系MISFETが形成される半導体基板101の主面に、例えば厚さ3nm程度のゲート絶縁膜103,104を形成する。その後、高圧系MISFETのゲート電極105をゲート絶縁膜102上に形成し、第1低圧系MISFETのゲート電極106をゲート絶縁膜103上に形成し、第2低圧系MISFETのゲート電極107をゲート絶縁膜104上に形成する。高圧系MISFETのゲート長は、例えば800nm程度、第1低圧系MISFETのゲート長は、例えば55nm程度、第2低圧系MISFETのゲート長は、例えば44nm程度である。ゲート電極105,106,107は、例えば多結晶シリコンからなる。

【0023】

次に、高圧系MISFETのゲート電極105をマスクとして、半導体基板101にn型不純物をイオン注入法により導入して、高圧系MISFETの低濃度拡散層108を形成する。同様にして、第1低圧系MISFETの低濃度拡散層109を形成し、第2低圧系MISFETの低濃度拡散層110を形成する。

【0024】

次に、高圧系MISFETのゲート電極105、第1低圧系MISFETのゲート電極106、および第2低圧系MISFETのゲート電極107のそれぞれの側面にサイドウォール111を形成する。その後、高圧系MISFETのゲート電極105、第1低圧系MISFETのゲート電極106、第2低圧系MISFETのゲート電極107、およびサイドウォール111をマスクとして半導体基板101にn型不純物をイオン注入法により導入して、高濃度拡散層112を形成する。

【0025】

次に、自己整合法により、ゲート電極105,106,107の上部および高濃度拡散層112の上面にシリサイド層113を形成する。その後、高圧系MISFET、第1低圧系MISFET、および第2低圧系MISFETを覆う層間絶縁膜、および配線等を形成する。

【0026】

ところで、高圧系MISFETのゲート電極105、第1低圧系MISFETのゲート電極106、および第2低圧系MISFETのゲート電極107のそれぞれの側面に形成されるサイドウォール111のサイドウォール長は、最もゲート長が短くかつ配置密度が高い第2低圧系MISFETに要求される性能から決定される。このため、高圧系MISFETの低濃度拡散層108、第1低圧系MISFETの低濃度拡散層109、および第2低圧系MISFETの低濃度拡散層110を形成する際のイオン注入を、それぞれ異なる工程で行ない、最も適したイオン注入条件(注入エネルギーおよびドーズ量等)を適用することによって、高圧系MISFET、第1低圧系MISFET、および第2低圧系MISFETの性能を満たしている。

【0027】

しかしながら、高圧系MISFETでは、ゲート電極105と高濃度拡散層112の上面に形成されたシリサイド層113との間の電界が強くなり、ゲート電極105と高濃度拡散層112との間および高濃度拡散層112と半導体基板101との間のリーク電流が増加するという問題が生じた。

【0028】

そこで、本願発明者らは、高圧系MISFETのサイドウォールのサイドウォール長を、第1および第2低圧系MISFETのサイドウォールのサイドウォール長よりも長く形成する検討を行った。

【0029】

本願発明者らが検討した高圧系MISFETおよび低圧系MISFETの製造方法の第2例について、図49を用いて以下に説明する。第1および第2低圧系MISFETの構造は、前述の図48に示す構造とほぼ同様である。これに対して、高圧系MISFETでは、ゲート電極105の側面に2層のサイドウォール111,114が形成されている。これにより、高圧系MISFETでは、ゲート電極105と高濃度拡散層112の上面に形成されたシリサイド層113との距離が離れて電界が緩和し、ゲート電極105と高濃度拡散層112との間および高濃度拡散層112と半導体基板101との間のリーク電流を低減することができた。

【0030】

しかしながら、さらに半導体装置の高集積化が進むに伴い、第1低圧系MISFETにおいても、特に、ゲート電極106と高濃度拡散層112との間のリーク電流を低減する要望が強くなってきた。

【0031】

そこで、本願発明者らは、さらに、第1低圧系MISFETのサイドウォールのサイドウォール長を、第2低圧系MISFETのサイドウォールのサイドウォール長よりも長く形成する検討を行った。

【0032】

本願発明者らが検討した高圧系MISFETおよび低圧系MISFETの製造方法の第3例について、図50を用いて以下に説明する。第2低圧系MISFETの構造は、前述の図48に示す構造とほぼ同様である。これに対して、第1低圧系MISFETでは、ゲート電極106の側面に2層のサイドウォール111,114が形成され、高圧系MISFETでは、ゲート電極105の側面に3層のサイドウォール111,114,115が形成されている。これにより、第1低圧系MISFETでは、ゲート電極106と高濃度拡散層112との間の電界が緩和され、高圧系MISFETでは、ゲート電極105と高濃度拡散層112との間の電界がさらに緩和されて、それぞれのリーク電流を低減することができた。

【0033】

ところが、図51に示すように、第2低圧系MISFETにおいて、隣り合うゲート電極107の間の半導体基板101の一部が削れるという問題が生じた。これは、以下の理由によると考えられる。

【0034】

上記2層のサイドウォール111,114および上記3層のサイドウォール111,114,115を形成する際には、高圧系MISFETのゲート電極105、第1低圧系MISFETのゲート電極106、および第2低圧系MISFETのゲート電極107を覆う上層絶縁膜(例えば酸化シリコン膜)を半導体基板101の主面上に堆積する工程と、その上層絶縁膜をエッチバックする工程とを繰り返す必要がある。上層絶縁膜の下には、エッチングストッパとして機能する下層絶縁膜(例えば窒化シリコン膜)116が形成されている。

【0035】

高圧系MISFETまたは第1低圧系MISFETのように、隣り合うゲート電極105の間または隣り合うゲート電極106の間が比較的広い場合は、上層絶縁膜をエッチバックする際のエッチングガスの組成比が変わらないことから、下層絶縁膜116に対する上層絶縁膜のエッチング選択比が変わらない。従って、上層絶縁膜のエッチングは下層絶縁膜116によって止めることができる。これに対して、第2低圧系MISFETのように、隣り合うゲート電極107の間が比較的狭い場合は、エッチングガスを構成する各種ガスが隣り合うゲート電極107の間に均等に入らなくなり、上層絶縁膜をエッチバックする際のエッチングガスの組成比が変わってしまう。このため、下層絶縁膜116に対する上層絶縁膜のエッチング選択比が徐々に変化して、上層絶縁膜のエッチングが下層絶縁膜116によって止まり難くなり、半導体基板101が削れてしまう。

【0036】

(実施の形態1)

本実施の形態1による周辺回路を構成する第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISを有する半導体装置の製造方法を図1〜図17を用いて工程順に説明する。図1〜図17は半導体装置の製造工程中における周辺回路領域に形成された第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISの一例の要部断面図である。各図は、チャネルを各ゲート電極のゲート長方向に沿って切断した要部断面を示している。本実施の形態1においては、第1nMISおよび第1pMISを、例えば高圧系MISFETとして形成し、第2nMISおよび第2pMISを、例えば低リーク用の低圧系MISFETとして形成し、第3nMIS及び第3pMISを、例えば高速動作用の低圧系MISETとして形成している。

【0037】

高圧系MISFETは、例えば入出力(I/O)回路を構成し、低圧系MISFETは、例えばPLL(Phase Locked Loop)、CPU(Central Processing Unit)、またはプロセッサ等の論理回路を構成する。低圧系MISFETには、要求される動作特性に応じて、ゲート材料、ゲート長、ソース・ドレイン領域の不純物濃度、配置密度等の異なる種々の構造が適用されるが、ここでは、低リーク動作が要求される(高速動作よりも低リーク動作を優先する)低リーク用の低圧系MISFETと、高速動作が要求される(低リーク動作よりも高速動作を優先する)高速動作用の低圧系MISFETとを例示する。

【0038】

高圧系MISFETは、例えば3.3〜5Vの印加電圧で駆動し、ゲート電極のゲート長は、例えば800nm程度、ゲート電極の側面に形成されるサイドウォールのサイドウォール長は、例えば80〜90nm程度である。また、低リーク用の低圧系MISFETは、例えば1.2Vの印加電圧で駆動し、ゲート電極のゲート長は、例えば55nm程度、ゲート電極の側面に形成されるサイドウォールのサイドウォール長は、例えば40〜50nm程度である。また、高速動作用の低圧系MISFETは、例えば1.2Vの印加電圧で駆動し、ゲート電極のゲート長は、例えば44nm程度、ゲート電極の側面に形成されるサイドウォールのサイドウォール長は、例えば30nm程度である。

【0039】

すなわち、高圧系MISFETと、低リーク用の低圧系MISFETと、高速動作用の低圧系MISFETとは、構造面において、主にゲート長および配置密度の点で相違する。高圧系MISFETにおけるゲート長が最も長く、以下、低リーク用の低圧系MISFET、高速動作用の低圧系MISFETの順でゲート長は短くなる。また、高圧系MISFETにおける配置密度が最も低く、以下、低リーク用の低圧系MISFET、高速動作用の低圧系MISFETの順で配置密度は高くなる。

【0040】

まず、図1に示すように、半導体基板(この段階では半導体ウエハと称する平面略円形状の半導体の薄板)1の主面に、例えば溝型の素子分離部STIおよびこれに取り囲まれるように配置された活性領域等を形成する。すなわち半導体基板1の所定箇所に分離溝を形成した後、半導体基板1の主面上に、例えば酸化シリコン等からなる絶縁膜を堆積し、さらにその絶縁膜が分離溝内のみに残されるように絶縁膜をCMP(Chemical Mechanical Polishing)法等によって研磨することで、分離溝内に絶縁膜を埋め込む。このようにして素子分離部STIを形成する。

【0041】

次に、半導体基板1にn型不純物を選択的にイオン注入することにより、n型の埋め込みウェルNISOを形成する。続いて第1nMIS領域の半導体基板1にp型不純物を選択的にイオン注入することによりp型のウェルHPWを形成し、第1pMIS領域の半導体基板1にn型不純物を選択的にイオン注入することによりn型のウェルHNWを形成する。同様に、第2nMIS領域および第3nMIS領域の半導体基板1にp型不純物を選択的にイオン注入することによりp型のウェルPWを形成し、第2pMIS領域および第3pMIS領域の半導体基板1にn型不純物を選択的にイオン注入することによりn型のウェルNWを形成する。

【0042】

次に、第1nMIS領域、第1pMIS領域、第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域のそれぞれの半導体基板1に所定の不純物をイオン注入する。これにより、第1nMIS領域、第1pMIS領域、第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域のそれぞれの半導体基板1にチャネル形成用の半導体領域D1,D2,D3,D4,D5,D6を形成する。

【0043】

次に、半導体基板1に対して酸化処理を施すことにより、半導体基板1の主面に、例えば酸化シリコンからなる厚さ10〜20nm程度のゲート絶縁膜4Aを形成する。続いて第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域のゲート絶縁膜4Aを除去した後、半導体基板1に対して酸化処理を施す。これにより、第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域の半導体基板1の主面に、例えば酸化シリコンからなる厚さ1〜5nm程度のゲート絶縁膜4を形成する。ゲート絶縁膜4は、酸化シリコンに限らず、酸化ハフニウム(HfSiON)などの高誘電率膜で形成してもよい。

【0044】

次に、図2に示すように、半導体基板1の主面上に、例えば非晶質シリコンからなる導電膜10をCVD(Chemical Vapor Deposition)法により堆積する。導電膜10の厚さは、例えば100nm程度である。

【0045】

次に、図3に示すように、第1nMIS領域、第2nMIS領域、および第3nMIS領域の導電膜10にn型不純物をイオン注入法等によって導入することにより、n型の導電膜10naを形成する。また、第1pMIS領域、第2pMIS領域、および第3pMIS領域の導電膜10にp型不純物をイオン注入法等によって導入することにより、p型の導電膜10pを形成する。

【0046】

次に、図4に示すように、導電膜10na,10pをフォトリソグラフィおよびドライエッチングを用いてパターニングすることにより、導電膜10naからなる第1nMISのゲート電極GHn、導電膜10pからなる第1pMISのゲート電極GHp、導電膜10naからなる第2nMISのゲート電極GMn、導電膜10pからなる第2pMISのゲート電極GMp、導電膜10naからなる第3nMISのゲート電極GLn、および導電膜10pからなる第3pMISのゲート電極GLpを形成する。

【0047】

活性領域における第1nMISのゲート電極GHnおよび第1pMISのゲート電極GHpのゲート長は、例えば800nm程度である。また、活性領域における第2nMISのゲート電極GMnおよび第2pMISのゲート電極GMpのゲート長は、例えば55nm程度であり、隣り合うゲート電極GMnとゲート電極GMn、隣り合うゲート電極GMnとゲート電極GMp、隣り合うゲート電極GMpとゲート電極GMpとの最小間隔は、例えば110nm程度である。また、活性領域における第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのゲート長は、例えば44nm程度であり、隣り合うゲート電極GLnとゲート電極GLn、隣り合うゲート電極GLnとゲート電極GLp、隣り合うゲート電極GLpとゲート電極GLpとの最小間隔は、例えば88nm程度である。

【0048】

次に、図5に示すように、第1nMIS領域の半導体基板1の主面にn型不純物、例えばヒ素をイオン注入することにより、第1nMIS領域の半導体基板1の主面にn−型の半導体領域13をゲート電極GHnに対して自己整合的に形成する。同様に、第1pMIS領域の半導体基板1の主面にp型不純物、例えばフッ化ボロンをイオン注入することにより、第1pMIS領域の半導体基板1の主面にp−型の半導体領域14をゲート電極GHpに対して自己整合的に形成する。

【0049】

次に、第2nMIS領域の半導体基板1の主面にn型不純物、例えばヒ素をイオン注入することにより、第2nMIS領域の半導体基板1の主面にn−型の半導体領域24をゲート電極GMnに対して自己整合的に形成する。同様に、第2pMIS領域の半導体基板1の主面にp型不純物、例えばフッ化ボロンをイオン注入することにより、第2pMIS領域の半導体基板1の主面にp−型の半導体領域25をゲート電極GMpに対して自己整合的に形成する。

【0050】

次に、第3nMIS領域の半導体基板1の主面にn型不純物、例えばヒ素をイオン注入することにより、第3nMIS領域の半導体基板1の主面にn−型の半導体領域18をゲート電極GLnに対して自己整合的に形成する。同様に、第3pMIS領域の半導体基板1の主面にp型不純物、例えばフッ化ボロンをイオン注入することにより、第3pMIS領域の半導体基板1の主面にp−型の半導体領域19をゲート電極GLpに対して自己整合的に形成する。

【0051】

次に、図6に示すように、半導体基板1の主面上に第1絶縁膜(例えば窒化シリコン膜)7bをCVD法により堆積する。第1絶縁膜7bの厚さは、例えば10nm程度である。続いて、第1絶縁膜7b上に第2絶縁膜(例えば酸化シリコン膜)7mをCVD法により堆積する。第2絶縁膜7mの厚さは、例えば50〜60nm程度である。ここでドライエッチング選択比およびウェットエッチング選択比(第1絶縁膜7bのエッチング速度と第2絶縁膜7mのエッチング速度との比)が高くなるように、第1絶縁膜7bの材料および第2絶縁膜7mの材料は選択される。また、第1絶縁膜7bおよび第2絶縁膜7mのそれぞれの厚さは、第1nMISのゲート電極GHnおよび第1pMISのゲート電極GHpのそれぞれの側面に形成されるサイドウォールのサイドウォール長(例えば80〜90nm程度)を目標に設定される。

【0052】

次に、図7に示すように、第2絶縁膜7mを異方性のドライエッチングでエッチバックする。これにより、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの上面上、ならびにこれらゲート電極GHn,GHp,GMn,GMp,GLn,GLpが形成されていない半導体基板1の主面上の第2絶縁膜7mを完全にまたは一部(例えば1〜3nm程度)が残るように除去する。

【0053】

この際、第1nMIS領域および第1pMIS領域において、ゲート電極GHn,GHpの上面上およびこれらゲート電極GHn,GHpが形成されていない半導体基板1の主面上の第2絶縁膜7mを完全に除去しても、第3nMIS領域および第3pMIS領域では、ゲート電極GLn,GLpが形成されていない半導体基板1の主面上に第2絶縁膜7mが残ることがある。これは、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間に、第2絶縁膜7mが埋め込まれていること、および異方性のドライエッチングに用いられるエッチングガスの組成比が徐々に変化してエッチング速度が遅くなること等に起因すると考えられる。

【0054】

このような場合は、異方性のドライエッチングを行った後、ウェットエッチングを行い、ゲート電極GLn,GLpが形成されていない半導体基板1の主面上に残った第2絶縁膜7mを除去してもよい。隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間が第2絶縁膜7mによって埋め込まれていても、エッチング液が第2絶縁膜7mの表面が接触する界面から毛細管現象により侵入して、ゲート電極GLn,GLpが形成されていない半導体基板1の主面上に残った第2絶縁膜7mを除去することができる。

【0055】

次に、図8に示すように、第1nMIS領域および第1pMIS領域をフォトレジストパターンRP1で覆い、第2nMIS領域、第2pMIS領域、第3nMIS領域、および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングまたは等方性のドライエッチングにより加工する。等方性のエッチングを用いているので、上方向と横方向とから第2絶縁膜7mはエッチングされる。

【0056】

これにより、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの側面に、横方向(ゲート長方向)の幅が20〜30nm程度の第2絶縁膜7mを残存させる。第1絶縁膜7bと第2絶縁膜7mとのエッチング選択比が高いことから、第1絶縁膜7bはエッチングされ難く、半導体基板1の主面が削られることはない。

【0057】

次に、図9に示すように、フォトレジストパターンRP1を除去した後、第1nMIS領域、第1pMIS領域、第2nMIS領域、および第2pMIS領域をフォトレジストパターンRP2で覆い、第3nMIS領域および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングにより除去する。前の工程と同様、第1絶縁膜7bと第2絶縁膜7mとのエッチング選択比が高いことから、第1絶縁膜7bはエッチングされ難く、半導体基板1の主面が削られることはない。

【0058】

次に、図10に示すように、フォトレジストパターンRP2を除去した後、半導体基板1の主面上に第3絶縁膜(例えば酸化シリコン膜)7tをCVD法により堆積する。第3絶縁膜7tの厚さは、例えば20〜30nm程度である。第3絶縁膜7tの厚さは、第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのそれぞれの側面に形成されるサイドウォールのサイドウォール長(例えば30nm程度)を目標にして設定される。

【0059】

次に、図11に示すように、第3絶縁膜7tを異方性のドライエッチングでエッチバックした後、露出している第1絶縁膜7bをドライエッチングまたはウェットエッチングで除去する。これにより、第1nMISおよび第1pMISでは、ゲート電極GHn,GHpの側面に第1絶縁膜7b、第2絶縁膜7m、および第3絶縁膜7tからなるサイドウォールSWHを形成する。また、第2nMISおよび第2pMISでは、ゲート電極GMn,GMpの側面に第1絶縁膜7b、第2絶縁膜7m、および第3絶縁膜7tからなるサイドウォールSWMを形成する。また、第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの側面に第1絶縁膜7bおよび第3絶縁膜7tからなるサイドウォールSWLを形成する。上記サイドウォールSWHのサイドウォール長は、例えば80〜90nm程度であり、上記サイドウォールSWMのサイドウォール長は、例えば40〜50nm程度であり、上記サイドウォールSWLのサイドウォール長は、例えば30nm程度である。

【0060】

このように、互いにサイドウォール長の異なる複数のサイドウォールSWL,SWM,SWHを形成する製造工程において(本実施の形態1では3種類)、異方性のドライエッチングの回数を減らして、異方性のドライエッチングと等方性のウェットエッチングまたは等方性のドライエッチングとの組み合わせにより、上記サイドウォールSWL,SWM,SWHを形成している。従って、特に、配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の削れを防止することができる。

【0061】

また、第2nMISおよび第2pMISのゲート電極GMn,GMpの側面に形成されたサイドウォールSWMの半導体基板1の主面からの高さは、ゲート電極GMn,GMpの半導体基板1の主面からの高さよりも低い。同様に、第3nMISおよび第3pMISのゲート電極GLn,GLpの側面に形成されたサイドウォールSWLの半導体基板1の主面からの高さは、ゲート電極GLn,GLpの半導体基板1の主面からの高さよりも低い。さらに、上記サイドウォールSWMの半導体基板1の主面からの高さと上記サイドウォールSWLの半導体基板1の主面からの高さは、同じである。

【0062】

このように、隣り合うゲート電極の間隔が相対的に小さい領域において、上記サイドウォールSWM,SWLの半導体基板1の主面からの高さを低くすることにより、後述の工程において半導体基板1の主面上に形成される層間絶縁膜の被覆性(埋め込み性)を向上させることができる。層間絶縁膜の被覆性(埋め込み性)が向上すると、第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間に層間絶縁膜が入りやすくなり、ボイド(す)が形成され難くなる。仮にボイドが形成されると、後述の工程において層間絶縁膜にコンタクトホールを形成すると、コンタクトホールの形状不良が生じ、隣り合うコンタクトホールの間で短絡(ショート)が発生する恐れがある。

【0063】

一方、第1nMISおよび第1pMISのゲート電極GHn,GHpの側面に形成されたサイドウォールSWHの半導体基板1の主面からの高さは、ゲート電極GHn,GHpの半導体基板1の主面からの高さとほぼ同じである。さらに、上記サイドウォールSWHの半導体基板1の主面からの高さは、上記サイドウォールSWM,SWLの半導体基板1の主面からの高さよりも高い。このように上記サイドウォールSWHの半導体基板1の主面からの高さを他の上記サイドウォールSWM,SWLと同様に低くしていないのは、以下の理由による。すなわち、第1nMISおよび第1pMISの配置密度が、第2nMIS、第2pMIS、第3nMIS、および第3pMISの配置密度よりも広いことから、後述の工程において半導体基板1の主面上に形成される層間絶縁膜の被覆性(埋め込み性)が良好であるので、上記サイドウォールSWHの半導体基板1の主面からの高さを低くする必要がないからである。

【0064】

また、第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの側面に形成されるサイドウォールSWLのサイドウォール長は、第3絶縁膜7tの厚さと、第3絶縁膜7tの異方性のドライエッチングのエッチング条件とによって決まるので、配置密度が高く、かつ高速動作が要求される第3nMISおよび第3pMISの動作特性の制御が容易となる。

【0065】

次に、図12に示すように、第1nMIS領域、第2nMIS領域、および第3nMIS領域の半導体基板1の主面に、フォトレジストパターン22をマスクとしてn型不純物、例えばヒ素およびリンをイオン注入することにより、第1nMISのゲート電極GHn、第2nMISのゲート電極GMn、および第3nMISのゲート電極GLnに対してn+型の半導体領域23を自己整合的に形成する。

【0066】

これにより、n−型の半導体領域13とn+型の半導体領域23とからなる第1nMISのソース・ドレイン領域SDが形成され、n−型の半導体領域24とn+型の半導体領域23とからなる第2nMISのソース・ドレイン領域SDが形成され、n−型の半導体領域18とn+型の半導体領域23とからなる第3nMISのソース・ドレイン領域SDが形成される。

【0067】

次に、図13に示すように、第1pMIS領域、第2pMIS領域、および第3pMIS領域の半導体基板1の主面に、フォトレジストパターン20をマスクとしてp型不純物、例えばボロンまたはフッ化ボロンをイオン注入することにより、第1pMISのゲート電極GHp、第2pMISのゲート電極GMp、および第3pMISのゲート電極GLpに対してp+型の半導体領域21を自己整合的に形成する。

【0068】

これにより、p−型の半導体領域14とp+型の半導体領域21とからなる第1pMISのソース・ドレイン領域SDが形成され、p−型の半導体領域25とn+型の半導体領域21とからなる第2pMISのソース・ドレイン領域SDが形成され、p−型の半導体領域19とp+型の半導体領域21とからなる第3pMISのソース・ドレイン領域SDが形成される。

【0069】

次に、図14に示すように、第1nMISのゲート電極GHnの上部およびn+型の半導体領域23の上面、第1pMISのゲート電極GHpの上部およびp+型の半導体領域21の上面、第2nMISのゲート電極GMnの上部およびn+型の半導体領域23の上面、第2pMISのゲート電極GMpの上部およびp+型の半導体領域21の上面、第3nMISのゲート電極GLnの上部およびn+型の半導体領域23の上面、第3pMISのゲート電極GLpの上部およびp+型の半導体領域21の上面にシリサイド層3をサリサイド(Salicide:Self-Align silicide)プロセスにより形成する。シリサイド層3としては、例えばニッケルシリサイドまたはコバルトシリサイド等が使用される。

【0070】

シリサイド層3を形成することにより、シリサイド層3と、後述の工程においてその上部に形成されるプラグ等との接続抵抗を低減することができる。また、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第2nMISのゲート電極GMn、第2pMISのゲート電極GMp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLp自身の抵抗、ならびにソース・ドレイン領域SD自身の抵抗を低減することができる。

【0071】

ここで、第1nMISおよび第1pMISでは、ゲート電極GHn,GHpの露出した上面からシリサイド反応が進む。一方、第2nMISおよび第2pMISでは、ゲート電極GMn,GMpの露出した上面と両側面とからシリサイド反応が進み、同様に、第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの露出した上面と両側面とからシリサイド反応が進む。従って、ゲート電極GMn,GMp,GLn,GLpの上部の両側面にもシリサイド層3が形成されるので、ゲート電極GMn,GMp,GLn,GLpの抵抗をより低くすることができる。

【0072】

また、図示はしていないが、第2nMISおよび第2pMISのゲート電極GMn,GMpならびに第3nMISおよび第3pMISのゲート電極GLn,GLpにおいて、上部の両側面から進むシリサイド反応により形成されるシリサイド層3が一体になると、シリサイド層3の全体の膜厚が、上面から形成されるシリサイド層3の膜厚と上部の両側面から形成されるシリサイド層3の膜厚の合計の膜厚となる。これにより、第1nMISおよび第1pMISのゲート電極GHn,GHpに形成されたシリサイド層3の膜厚よりも、第2nMISおよび第2pMISのゲート電極GMn,GMpならびに第3nMISおよび第3pMISのゲート電極GLn,GLpに形成されたシリサイド層3の膜厚の方が厚くなる場合も考えられる。

【0073】

次に、図15に示すように、半導体基板1の主面上に、絶縁膜として窒化シリコン膜9aをCVD法により堆積する。この窒化シリコン膜9aは、後述の工程においてコンタクトホールを形成する際に、エッチングストッパとして機能する。

【0074】

次に、図16に示すように、絶縁膜として酸化シリコン膜9bをCVD法により堆積して、酸化シリコン膜9bの表面をCMP法により研磨することによって、窒化シリコン膜9aおよび酸化シリコン膜9bからなる層間絶縁膜9を形成する。前述したように、第3nMISおよび第3pMISでは、サイドウォールSWLの半導体基板1の主面からの高さが、ゲート電極GLn,GLpの半導体基板1の主面からの高さよりも低く形成されているため、被覆性(埋め込み性)よく層間絶縁膜9を形成することができる。層間絶縁膜9の被覆性(埋め込み性)が向上することにより、後述の工程において層間絶縁膜9に形成されるコンタクトホールの形状不良を防ぐことができる。

【0075】

次に、図17に示すように、第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISにおいて、それぞれのゲート電極GHn,GHp,GMn,GMp,GLn,GLpの上部およびそれぞれのソース・ドレイン領域SDの上面に形成されたシリサイド層3に達するコンタクトホールCAを形成する。図17では、説明簡略化のため、第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISのソース・ドレイン領域SDに達するコンタクトホールCAのみを例示している。

【0076】

次に、コンタクトホールCA内にプラグPAを形成する。プラグPAは、例えばチタンと窒化チタンとを積層した相対的に薄いバリア膜と、そのバリア膜に包まれるように形成されたタングステンまたはアルミニウム等からなる相対的に厚い導電膜とからなる積層膜によって構成される。その後、層間絶縁膜9上に、例えば銅またはアルミニウムを主成分とする第1層目の配線M1を形成する。

【0077】

以上に説明した製造過程により、周辺回路領域に第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISが略完成する。これ以降は、通常の半導体装置の製造工程を経ることにより、さらに上層の配線を形成して、不揮発性メモリを有する半導体装置を製造する。

【0078】

なお、前述した実施の形態1では、第1nMISおよび第1pMISのゲート電極GHn,GHpのゲート長よりも短く、第3nMISおよび第3pMISのゲート電極GLn,GLpのゲート長よりも長いゲート長のゲート電極を備えるMISFETとして、第2nMISおよび第2pMISを例示したが、これに限定されるものではない。例えばメモリ領域に形成される不揮発性メモリセルを構成するMISFETを例示することもできる。

【0079】

近年、電気的に書き換え可能な不揮発性メモリセルとして、窒化膜などのトラップ準位を有する絶縁膜を電荷蓄積層とするMONOS(Metal Oxide Nitride Oxide Silicon)型不揮発性メモリセルが注目されている。この場合、データ記憶に寄与する電荷は、絶縁体である窒化膜の離散トラップに蓄積されるため、蓄積ノードを取り巻く酸化膜のどこか一部に欠陥が生じて異常リークがおきても、電荷蓄積層の電荷が全て抜けてしまうことがないため、データ保持の信頼度を向上させることが可能である。

【0080】

しかしながら、MONOS型不揮発性メモリセルがアレイ状に配置された不揮発性メモリを含む半導体装置については、以下に説明する種々の技術的課題が存在する。

【0081】

信頼性の高い不揮発性メモリを実現するためには、不揮発性メモリの周辺回路にも高い信頼性が要求される。例えば周辺回路には、外部から与えられる電源電圧よりも高い電圧を発生させる昇圧回路および発生させたその高い電圧を不揮発性メモリセルに印加する回路等が必要である。そのため、不揮発性メモリを動作させる際には、不揮発性メモリセルよりも高い耐圧性能を有する半導体素子が周辺回路に必要となる。

【0082】

そこで、本願発明者らは、相対的に低い電圧(例えば電源電圧と同じ電圧)で動作する低圧系MISFETと相対的に高い電圧(例えば電源電圧よりも高い電圧)で動作する高圧系MISFETとを周辺回路に形成することによって、所望する動作性能および耐圧性能を実現している。

【0083】

本実施の形態1による不揮発性メモリセル、ならびに周辺回路を構成する第1nMIS、第1pMIS、第3nMIS、および第3pMISを有する半導体装置の製造方法を図18〜図37を用いて工程順に説明する。図18〜図37は半導体装置の製造工程中におけるメモリ領域に形成された不揮発性メモリセル、ならびに周辺回路領域に形成された第1nMIS、第1pMIS、第3nMIS、および第3pMISの要部断面図である。各図は、チャネルをゲート電極のゲート長方向に沿って切断した要部断面を示している。また、第1nMISおよび第1pMISを、例えば高圧系MISFETとして形成し、第3nMISおよび第3pMISを、例えば高速動作用の低圧系MISFETとして形成している。

【0084】

不揮発性メモリセルは、選択用nMISの選択ゲート電極の片側面にサイドウォール形状のメモリ用nMISのメモリゲート電極を形成したスプリットゲート構造のMONOS型不揮発性メモリセルを例示しており、選択ゲート電極のメモリゲート電極と反対側の側面およびメモリゲート電極の側面に形成されるサイドウォールのサイドウォール長は、40〜50nm程度である。

【0085】

周辺回路を構成する第1nMISおよび第1pMISは、前述したものと同じであり、例えば3.3〜5Vの印加電圧で駆動し、そのゲート電極の側面に形成されるサイドウォールのサイドウォール長は、例えば80〜90nm程度である。また、周辺回路を構成する第3nMISおよび第3pMISは、前述したものと同じであり、例えば1.2Vの印加電圧で駆動し、そのゲート電極の側面に形成されるサイドウォールのサイドウォール長は、例えば30nm程度である。

【0086】

すなわち、周辺回路領域に形成される第1nMISおよび第1pMISと、周辺回路領域に形成される第3nMISおよび第3pMISと、メモリ領域に形成される不揮発性メモリセルとは、ゲート長および配置密度の点で相違する。第1nMISおよび第1pMISにおけるゲート長が最も長く、以下、不揮発性メモリセル、第3nMISおよび第3pMISの順でゲート長は短くなる。また、第1nMISおよび第1pMISにおける配置密度が最も低く、以下、不揮発性メモリセル、第3nMISおよび第3pMISの順で配置密度は高くなる。

【0087】

まず、図18に示すように、前述の図1を用いて説明したと同様にして、半導体基板1の主面に素子分離部STIを形成し、n型の埋め込みウェルNISO、p型のウェルHPW、n型のウェルHNW、p型のウェルPW、n型のウェルNWを形成する。その後、メモリ領域の半導体基板1にp型不純物を選択的にイオン注入する。これによりメモリ領域の半導体基板1に、選択用nMISのチャネル形成用のp型の半導体領域5を形成する。同様に、第1nMIS領域、第1pMIS領域、第3nMIS領域、および第3pMIS領域のそれぞれの半導体基板1に所定の不純物をイオン注入する。これにより、第1nMIS領域、第1pMIS領域、第3nMIS領域、および第3pMIS領域のそれぞれの半導体基板1にチャネル形成用の半導体領域D1,D2,D5,D6を形成する。

【0088】

次に、第1nMIS領域および第1pMIS領域の半導体基板1の主面に、例えば酸化シリコンからなる厚さ10〜20nm程度のゲート絶縁膜4Aを形成し、メモリ領域、第3nMIS領域、および第3pMIS領域の半導体基板1の主面に、例えば酸化シリコンからなる厚さ1〜5nm程度のゲート絶縁膜4を形成する。

【0089】

次に、図19に示すように、半導体基板1の主面上に、例えば非晶質シリコンからなる導電膜10をCVD法により堆積した後、メモリ領域の導電膜10にn型不純物をイオン注入法等によって導入することにより、n型の導電膜10nを形成する。導電膜10,10nの厚さは、例えば100nm程度である。

【0090】

次に、図20に示すように、メモリ領域のn型の導電膜10nをフォトリソグラフィおよびドライエッチングを用いてパターニングする。これにより、メモリ領域に、n型の導電膜10nからなる選択用nMISの選択ゲート電極CGを形成する。メモリ領域の選択ゲート電極CGのゲート長は、例えば100nm程度である。

【0091】

次に、図21に示すように、選択ゲート電極CGおよびフォトレジストパターンをマスクとして、メモリ領域の半導体基板1の主面にn型不純物、例えばヒ素またはリンをイオン注入することにより、メモリ用nMISのチャネル形成用のn型の半導体領域8を形成する。

【0092】

次に、図22に示すように、半導体基板1の主面上に、例えば酸化シリコンからなる絶縁膜6b、トラップ準位を有する絶縁膜として例えば窒化シリコンからなる電荷蓄積層CSL、および例えば酸化シリコンからなる絶縁膜6tを順次形成する。絶縁膜6bは、例えば熱酸化法またはISSG(In-Situ Steam Generation)酸化法等により形成され、電荷蓄積層CSLは、例えばCVD法等により形成され、絶縁膜6tは、例えばCVD法またはISSG酸化法等により形成される。絶縁膜6b、電荷蓄積層CSL、および絶縁膜6tからなる積層膜(以下、絶縁膜6b,6tおよび電荷蓄積層CSLと記す)の厚さは、20nm程度を例示することができる。また、絶縁膜6b,6tは、例えば窒素を含んだ酸化シリコンで形成してもよく、電荷蓄積層CSLは、例えば酸化アルミニウム(アルミナ)、酸化ハフニウム、または酸化タンタルなど、窒化シリコンよりも高い誘電率を有する高誘電率膜により形成してもよい。なお、図中では絶縁膜6b,6tおよび電荷蓄積層CSLの表記を6b/CSL/6tとして表現している。

【0093】

次に、半導体基板1の主面上に低抵抗多結晶シリコンからなる導電膜を堆積する。この導電膜はCVD法により形成され、その厚さは、例えば50nm程度である。続いて、フォトリソグラフィおよび異方性のドライエッチングを用いて、この導電膜を加工する。これにより、メモリ領域に、選択ゲート電極CGの両側面に絶縁膜6b,6tおよび電荷蓄積層CSLを介してサイドウォール11を形成する。

【0094】

次に、図23に示すように、フォトレジストパターンをマスクとして、そこから露出するサイドウォール11をエッチングする。これにより、メモリ領域において、選択ゲート電極CGの片側面のみにメモリ用nMISのメモリゲート電極MGを形成する。メモリゲート電極MGのゲート長は、例えば65nm程度である。

【0095】

次に、メモリ領域において、選択ゲート電極CGとメモリゲート電極MGとの間および半導体基板1とメモリゲート電極MGとの間の絶縁膜6b,6tおよび電荷蓄積層CSLを残して、その他の領域の絶縁膜6b,6tおよび電荷蓄積層CSLを選択的にエッチングする。

【0096】

次に、図24に示すように、第1nMIS領域および第3nMIS領域の導電膜10にn型不純物をイオン注入法等によって導入することにより、n型の導電膜10naを形成する。また、第1pMIS領域および第3pMIS領域の導電膜10にp型不純物をイオン注入法等によって導入することにより、p型の導電膜10pを形成する。

【0097】

次に、図25に示すように、周辺回路領域の導電膜10na,10pをフォトリソグラフィおよびドライエッチングを用いてパターニングすることにより、導電膜10naからなる第1nMISのゲート電極GHn、導電膜10pからなる第1pMISのゲート電極GHp、導電膜10naからなる第3nMISのゲート電極GLn、および導電膜10pからなる第3pMISのゲート電極GLpを形成する。活性領域における第1nMISのゲート電極GHnおよび第1pMISのゲート電極GHpのゲート長は、例えば800nm程度である。また、活性領域における第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのゲート長は、例えば44nm程度であり、隣り合うゲート電極GLnとゲート電極GLnとの最小間隔、隣り合うゲート電極GLnとゲート電極GLpとの最小間隔、または隣り合うゲート電極GLpとゲート電極GLpとの最小間隔は、例えば88nm程度である。

【0098】

次に、第1nMIS領域の半導体基板1の主面にn型不純物、例えばヒ素をイオン注入することにより、第1nMIS領域の半導体基板1の主面にn−型の半導体領域13をゲート電極GHnに対して自己整合的に形成する。同様に、第1pMIS領域の半導体基板1の主面にp型不純物、例えばフッ化ボロンをイオン注入することにより、第1pMIS領域の半導体基板1の主面にp−型の半導体領域14をゲート電極GHpに対して自己整合的に形成する。

【0099】

次に、図26に示すように、半導体基板1の主面上に、例えば酸化シリコンからなる厚さ10nm程度の絶縁膜をCVD法により堆積した後、この絶縁膜を異方性のドライエッチングで加工する。これにより、メモリ領域では、選択ゲート電極CGのメモリゲート電極MGと反対側の側面およびメモリゲート電極MGの側面に、周辺回路領域では、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第3nMISのゲート電極GLn、第3pMISのゲート電極GLpのそれぞれの側面にサイドウォール15を形成する。サイドウォール15のスペーサ長は、例えば3〜6nm程度である。

【0100】

サイドウォール15が形成されることによって、選択ゲート電極CGと半導体基板1との間のゲート絶縁膜4の露出していた側面、ならびにメモリゲート電極MGと半導体基板1との間の絶縁膜6b,6tおよび電荷蓄積層CSLの露出していた側面を保護することができる。また、サイドウォール15が形成されることによって、後述の第3nMIS領域にn−型の半導体領域を形成する工程および後述の第3pMIS領域にp−型の半導体領域を形成する工程において、n−型の半導体領域およびp−型の半導体領域の実効チャネル長が大きくなり、第3nMISおよび第3pMISの短チャネル効果を抑制することができる。

【0101】

次に、その端部がメモリ領域の選択ゲート電極CGの上面に位置してメモリゲート電極MG側の選択ゲート電極CGの一部およびメモリゲート電極MGを覆うフォトレジストパターン16を形成した後、選択ゲート電極CG、メモリゲート電極MG、およびフォトレジストパターン16をマスクとしてn型不純物、例えばヒ素を半導体基板1の主面にイオン注入することにより、半導体基板1の主面にn−型の半導体領域2adを選択ゲート電極CGに対して自己整合的に形成する。

【0102】

次に、図27に示すように、その端部がメモリ領域の選択ゲート電極CGの上面に位置してメモリゲート電極MGと反対側の選択ゲート電極CGの一部を覆うフォトレジストパターン17を形成した後、選択ゲート電極CG、メモリゲート電極MG、およびフォトレジストパターン17をマスクとしてn型不純物、例えばヒ素を半導体基板1の主面にイオン注入することにより、半導体基板1の主面にn−型の半導体領域2asをメモリゲート電極MGに対して自己整合的に形成する。

【0103】

ここでは、先にn−型の半導体領域2adを形成し、その後n−型の半導体領域2asを形成したが、先にn−型の半導体領域2asを形成し、その後n−型の半導体領域2adを形成してもよい。また、n−型の半導体領域2adを形成するn型不純物のイオン注入に続いて、p型不純物、例えばボロンを半導体基板1の主面にイオン注入し、n−型の半導体領域2adの下部を囲むようにp型の半導体領域を形成してもよい。

【0104】

次に、図28に示すように、第3nMIS領域の半導体基板1の主面にn型不純物、例えばヒ素をイオン注入することにより、第3nMIS領域の半導体基板1の主面にn−型の半導体領域18をゲート電極GLnに対して自己整合的に形成する。同様に、第3pMIS領域の半導体基板1の主面にp型不純物、例えばフッ化ボロンをイオン注入することにより、第3pMIS領域の半導体基板1の主面にp−型の半導体領域19をゲート電極GLpに対して自己整合的に形成する。

【0105】

次に、前述の図6〜図11を用いて説明したと同様な製造方法により、メモリ領域では、選択ゲート電極CGのメモリゲート電極MGと反対側の側面およびメモリゲート電極MGの側面にサイドウォールSWを形成し、周辺回路領域の第1nMISおよび第1pMISでは、ゲート電極GHn,GHpの側面にサイドウォールSWHを形成し、周辺回路領域の第3nMISおよび第3pMISでは、ゲート電極GLn,GLpの側面にサイドウォールSWLを形成する。

【0106】

まず、図29に示すように、半導体基板1の主面上に第1絶縁膜(例えば窒化シリコン膜)7bをCVD法により堆積する。第1絶縁膜7bの厚さは、例えば10nm程度である。続いて、第1絶縁膜7b上に第2絶縁膜(例えば酸化シリコン膜)7mをCVD法により堆積する。第2絶縁膜7mの厚さは、例えば50〜60nm程度である。

【0107】

次に、図30に示すように、第2絶縁膜7mを異方性のドライエッチングでエッチバックする。これにより、メモリ領域では、選択ゲート電極CGおよびメモリゲート電極MGの上面上、ならびに選択ゲート電極CGおよびメモリゲート電極MGが形成されていない半導体基板1の主面上の第2絶縁膜7mを完全にまたは一部(例えば1〜3nm程度)が残るように除去する。同様に、周辺回路領域では、第1nMISのゲート電極GHn、第1pMISのゲート電極GHp、第3nMISのゲート電極GLn、および第3pMISのゲート電極GLpのそれぞれの上面上、ならびにこれらゲート電極GHn,GHp,GLn,GLpが形成されていない半導体基板1の主面上の第2絶縁膜7mを完全にまたは一部(例えば1〜3nm程度)が残るように除去する。

【0108】

次に、図31に示すように、第1nMIS領域および第1pMIS領域をフォトレジストパターンRP1で覆い、メモリ領域、第3nMIS領域、および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングまたは等方性のドライエッチングにより加工する。これにより、メモリ領域では、選択ゲート電極CGのメモリゲート電極MGと反対側の側面およびメモリゲート電極MGの側面に、横方向(ゲート長方向)の幅が20〜30nm程度の第2絶縁膜7mを残存させる。同様に、周辺回路領域では、第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのそれぞれの側面に、横方向(ゲート長方向)の幅が20〜30nm程度の第2絶縁膜7mを残存させる。

【0109】

次に、図32に示すように、フォトレジストパターンRP1を除去した後、メモリ領域、第1nMIS領域、および第1pMIS領域をフォトレジストパターンRP2で覆い、第3nMIS領域および第3pMIS領域の第2絶縁膜7mを等方性のウェットエッチングにより除去する。

【0110】

次に、図33に示すように、フォトレジストパターンRP2を除去した後、半導体基板1の主面上に第3絶縁膜(例えば酸化シリコン膜)7tをCVD法により堆積する。第3絶縁膜7tの厚さは、例えば20〜30nm程度である。

【0111】

次に、図34に示すように、第3絶縁膜7tを異方性のドライエッチングでエッチバックした後、露出している第1絶縁膜7bをドライエッチングまたはウェットエッチングで除去する。これにより、メモリ領域では、選択ゲート電極CGのメモリゲート電極MGと反対側の側面およびメモリゲート電極MGの側面に第1絶縁膜7b、第2絶縁膜7m、および第3絶縁膜7tからなるサイドウォールSWを形成する。また、周辺回路領域では、第1nMISのゲート電極GHnおよび第1pMISのゲート電極GHpのそれぞれの側面に第1絶縁膜7b、第2絶縁膜7m、および第3絶縁膜7tからなるサイドウォールSWHを形成し、第3nMISのゲート電極GLnおよび第3pMISのゲート電極GLpのそれぞれの側面に第1絶縁膜7bおよび第3絶縁膜7tからなるサイドウォールSWLを形成する。上記サイドウォールSWのサイドウォール長は、例えば40〜50nm程度であり、上記サイドウォールSWHのサイドウォール長は、例えば80〜90nm程度であり、上記サイドウォールSWLのサイドウォール長は、例えば30nm程度である。

【0112】

次に、図35に示すように、第1pMIS領域および第3pMIS領域の半導体基板1の主面に、フォトレジストパターンRP3をマスクとしてp型不純物、例えばボロンまたはフッ化ボロンをイオン注入することにより、第1pMISのゲート電極GHpおよび第3pMISのゲート電極GLpに対してp+型の半導体領域21を自己整合的に形成する。

【0113】

これにより、p−型の半導体領域14とp+型の半導体領域21とからなる第1pMISのソース・ドレイン領域SDが形成され、p−型の半導体領域19とp+型の半導体領域21とからなる第3pMISのソース・ドレイン領域SDが形成される。

【0114】

次に、図36に示すように、第1nMIS領域、メモリ領域、および第3nMIS領域の半導体基板1の主面に、フォトレジストパターンRP4をマスクとしてn型不純物、例えばヒ素およびリンをイオン注入することにより、メモリ領域では、n+型の半導体領域2bを選択ゲート電極CGおよびメモリゲート電極MGに対して自己整合的に形成し、周辺回路領域では、第1nMISのゲート電極GHnおよび第3nMISのゲート電極GLnに対してn+型の半導体領域23を自己整合的に形成する。

【0115】

これにより、メモリ領域では、n−型の半導体領域2adおよびn+型の半導体領域2bからなるドレイン領域Drm、n−型の半導体領域2asおよびn+型の半導体領域2bからなるソース領域Srmが形成される。また、周辺回路領域では、n−型の半導体領域13とn+型の半導体領域23とからなる第1nMISのソース・ドレイン領域SDが形成され、n−型の半導体領域18とn+型の半導体領域23とからなる第3nMISのソース・ドレイン領域SDが形成される。

【0116】

次に、図37に示すように、メモリ領域では、選択ゲート電極CGの上部、メモリゲート電極MGの上部、およびn+型の半導体領域2bの上面にシリサイド層3を形成する。同様に、周辺回路領域では、第1nMISのゲート電極GHnの上部およびn+型の半導体領域23の上面、第1pMISのゲート電極GHpの上部およびp+型の半導体領域21の上面、第3nMISのゲート電極GLnの上部およびn+型の半導体領域23の上面、第3pMISのゲート電極GLpの上部およびp+型の半導体領域21の上面にそれぞれシリサイド層3を形成する。

【0117】

その後は、前述の製造方法と同様にして、層間絶縁膜を形成し、続いて、メモリ領域では、ドレイン領域Drm上のシリサイド層3に達するコンタクトホール、周辺回路領域では、第1nMIS、第1pMIS、第3nMIS、および第3pMISにおいて、それぞれのゲート電極GHn、GHp、GLn、GLpの上部およびそれぞれのソース・ドレイン領域SDの上面に形成されたシリサイド層3に達するコンタクトホールを形成する。続いて、これらコンタクトホール内にプラグを形成した後、第1層目の配線を形成する。

【0118】

以上に説明した製造方法により、メモリ領域に不揮発性メモリセル、ならびに周辺回路領域に第1nMIS、第1nMIS、第3nMIS、および第3pMISが略完成する。

【0119】

このように、本実施の形態1では、互いにサイドウォール長の異なる複数のサイドウォールSWL,SWM(またはSW),SWHを形成する製造工程において(本実施の形態2では3種類)、異方性のドライエッチングのみでなく、異方性のドライエッチングと等方性のウェットエッチングまたは等方性のドライエッチングとを組み合わせることにより、上記サイドウォールSWL,SWM(またはSW),SWHを形成している。従って、異方性のドライエッチングの回数が減ることにより、特に、周辺回路領域に形成される配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極Gpnとの間の半導体基板1の削れを防止することができる。

【0120】

さらに、配置密度が高い第3nMISおよび第3pMISにおいては、サイドウォールSWLの半導体基板1の主面からの高さを低くできるので、これらを覆うように形成される層間絶縁膜9の被覆性(埋め込み性)が向上して、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間に層間絶縁膜9が入りやすくなり、コンタクトホールCAの形状不良の原因の一つとなるボイドが形成され難くなる。

【0121】

(実施の形態2)

本実施の形態2による周辺回路を構成する第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISを有する半導体装置の製造方法を図38〜図42を用いて工程順に説明する。図38〜図42は半導体装置の製造工程中における周辺回路領域に形成された第1nMIS、第1pMIS、第2nMIS、第2pMIS、第3nMIS、および第3pMISの一例の要部断面図である。各図は、チャネルをゲート電極のゲート長方向に沿って切断した要部断面を示している。本実施の形態2においては、前述した実施の形態1と同様に、第1nMISおよび第1pMISを、例えば高圧系MISFETとして形成し、第2nMISおよび第2pMISを、例えば低リーク用の低圧系MISFETとして形成し、第3nMIS及び第3pMISを、例えば高速動作用の低圧系MISETとして形成している。

【0122】