半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電解めっき法により金属膜を形成する工程を有する半導体装置の製造方法及びめっき装置に関する。

【背景技術】

【0002】

LSIのCu多層配線の形成方法として、ダマシン法がある。ダマシン法においては、トランジスタを具備したSiウェハ上に、単層または多層の絶縁膜を形成し、絶縁膜を選択的に除去することにより、配線形状の溝、及び多層配線の層間を電気的に結ぶビアを形成する。次に、バリアメタルとなる高融点金属を含む材料を化学気相成長法や物理気相成長法により堆積する。つづいて、シード膜となるCu薄膜を化学気相成長法や物理気相成長法にて堆積する。さらに、シード膜をカソードとした電解めっき法によりCu膜をシード膜上に成膜して、溝やビアをCuにより埋設する。その後、溝やビアの外に位置するバリアメタル、シード膜、及びCu膜を化学機械研磨法により除去する。これらの工程を繰り返すことにより、Cu多層配線が形成される。電解めっきによってCu膜を埋設する場合、Cu膜の埋設不良が生じないようにする必要がある。

【0003】

電解めっき法によるCu膜の埋設に関する技術としては、例えば特許文献1乃至3の技術がある。特許文献1には、カソード−アノード間の電圧を一定として、そのときの電流をモニタしてめっきの終点を検知する手法、およびカソード−アノード間の電流を一定として、そのときの電圧をモニタしてめっきの終点を検知する手法が開示されている。このときの電圧値、或いは、電流値はパターン埋設中には変化するが、埋設が終了すると一定となるので、それを以ってめっきの終点を検知する、としている。

【0004】

特許文献2においては、カソードまたはアノードを含む回路に流れる電流または電圧をモニタすることにより、めっき成膜の終点を検知する方法が開示されている。詳細には、電流一定の場合、めっき初期にはめっき電圧は下がっていき、次いでほぼ一定となるので、それを以ってめっきの終点を検知する、としている。

【0005】

特許文献3には、めっき液中のウェハの近傍に参照電極を設置し、この参照電極から得られるウェハの表面電位に基づいて、印加電圧を制御して成膜する方法が開示されている。参照電極はアノードよりもカソード側にある。このため、従来と比較してウェハの表面電位を正確に測定することができる。従って、カソード-アノード間の電圧を基に印加電圧を制御するよりも、ウェハの表面電位の制御性が良くなり、めっき膜の成膜不良を防止することができる、としている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2005−213596号公報

【特許文献2】特開2003−013297号公報

【特許文献3】特開2002−322592号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、上記した特許文献1及び2に記載のようにアノード−カソード間の電流を一定にした場合、めっき液が新しいうちはめっき膜の埋設不良を発生することを防止できたが、めっき液の使用期間が長くなるにつれて、めっき膜の埋設不良が発生しやすくなっていた。また、特許文献3に記載の技術でも、めっき膜の埋設不良が発生することがあった。

【課題を解決するための手段】

【0008】

本発明によれば、半導体基板上に形成されたシード膜にカソード電極を接続し、前記シード膜とめっき液中のアノード電極との間で電流を流すことにより、前記シード膜上にめっき膜を形成する工程において、前記めっき液中に挿入された参照電極と前記カソード電極との間の電位差、または前記カソード電極と前記アノード電極の電位差を、時間の経過と共に徐々に下げる工程を有する半導体装置の製造方法が提供される。

【0009】

また本発明によれば、めっき液を収容するめっき槽と、

めっき膜が形成される半導体基板に接続されるカソード電極と、

前記めっき液に浸漬されるアノード電極と、

前記アノード電極と前記カソード電極の間に電流を流す電源と、

前記めっき液に浸漬される参照電極と、

前記電源を制御する制御部と、

を備え、

前記制御部は、前記めっき膜の少なくとも一部を形成している間に、前記参照電極の電位と、前記カソード電極の電位との電位差が時間の経過と共に徐々に下がるように前記電源を制御するめっき装置が提供される。

【発明の効果】

【0010】

本発明によれば、めっき膜の埋設不良が発生することを抑制できる。

【図面の簡単な説明】

【0011】

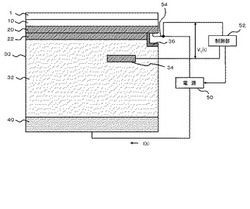

【図1】第1実施形態にかかるめっき装置の構成を示す概略図である。

【図2】参照電極を用いてウェハ上にめっき成膜を行う場合の電圧、電流、及び抵抗を説明する概略図である。

【図3】参照電極を用いてウェハ上にめっき成膜を行う場合の電圧、電流、及び抵抗を説明する概略図である。

【図4】VR(t)を一定値に制御した場合の被めっき面の表面電位VI(t)の変動を示す図である。

【図5】カソード電極と参照電極との間に成り立つ等価回路を示す図である。

【図6】制御部による電源の制御を説明するためのグラフである。

【図7】めっき膜が形成された後のウェハの断面図を示す図である。

【図8】配線溝にめっき膜が埋め込まれる様子を説明する断面図である。

【図9】第2の実施形態にかかるめっき装置における、制御部による電源の制御を説明するためのグラフである。

【図10】制御部による電源の制御の変形例を説明するためのグラフである。

【図11】制御部による電源の制御の変形例を説明するためのグラフである。

【図12】電解めっき法により、絶縁膜に形成された凹部にCu膜を埋設する際において、VI>VI(ideal)となった場合を示す図である。

【図13】電解めっき法により、絶縁膜に形成された凹部にCu膜を埋設する際において、VI<VI(ideal)となった場合を示す図である。

【図14】めっき電流I(t)が時間tによらず一定値Iをとる場合の、カソード−アノード間の電圧V0(t)の変動を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

(第1実施形態)

【0013】

図1は、第1実施形態にかかるめっき装置の構成を示す概略図である。このめっき装置は、 ウェハ1(半導体基板)に形成されたシード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程を行う装置である。めっき膜22を形成する工程は、めっき液32中に挿入された参照電極34とカソード電極54との間の電位差を、時間の経過と共に徐々に下げる工程を有する。このため、被めっき面であるめっき膜22の表面電位と所望する表面電位との誤差が小さくなる。ここで電位差には、ハンチングが生じてもよい。以下、詳細に説明する。

【0014】

図1に示すめっき装置は、めっき槽30、参照電極34、アノード電極40、カソード電極54、電源50、及び制御部52を有する。めっき槽30はめっき液32を収容する。アノード電極40はめっき液32に浸漬される。カソード電極54は、ウェハ1のシード膜20に接続される。本図においてカソード電極54は、ウェハ1の右端側のみに接続しているが、ウェハ1の外周部の略全周に接続されていてもよい。電源50は、アノード電極40とカソード電極54の間に電流を流す。このとき電源50は、電流を制御する場合もあるし、電圧を制御する場合もある。参照電極34は、めっき液32に浸漬される。参照電極34は、めっき液32のうち、アノード電極40とシード膜20の間に位置するが、好ましくはシード膜20の近傍に位置する。制御部52は、カソード電極54と参照電極34の間の電位差VR(t)に基づいて、電源50を制御する。例えば制御部52は、めっき膜22の少なくとも一部を形成している間に、電位差VR(t)が時間の経過と共に徐々に下がるように電源50を制御する。この制御は、例えばアノード電極40とカソード電極54の電位差V0(t)が徐々に下がるように電源50を制御することにより、行える。

【0015】

また、ウェハ1には絶縁膜10が形成されている。絶縁膜10は、例えば配線層間を絶縁するための膜であり、表面に微細な溝パターンが形成されている。めっき膜22は、この微細パターンに埋設される。ウェハ1は、例えば直径が300mmのウェハである。

【0016】

次に、本実施の形態に至った経緯について説明する。埋設不良を抑制するために、めっき液には硫酸銅水溶液の他に塩酸と添加剤と呼ばれる複数種類の有機物が加わっている。この有機物によって、溝およびビアにおいては、側壁や間口よりも底部のめっき速度が高い、所謂ボトムアップ成膜を行うことができる。ボトムアップ成膜を行うためには、添加剤の濃度と基板に吸着した添加剤の活性度が重要である。

【0017】

添加剤の活性度はめっき液に対する被めっき面の表面電位によって決まるため、被めっき面の電位の制御がCu埋め込みを良好にするためには重要である。添加剤のうち成膜を加速する成分は、表面電位が高いほど活性化する。

【0018】

一方、パターンの間口での電界集中による成膜速度の増加も、被めっき面の表面電位が高いほど加速する。添加剤によって加速されたパターン底部での成膜速度が、パターン間口での成膜速度よりも十分速い場合にボトムアップにより埋設が成立する。このため、被めっき面の表面電位VIには、理想的な埋設をするための値VI(ideal)が存在する。

【0019】

図12は、電解めっき法により、絶縁膜110に形成された凹部112にCu膜を埋設する際において、VI>VI(ideal)となった場合を示している。まず図12(a)に示すように、絶縁膜110上及び凹部112内にシード膜120を形成する。ついで、図12(b)及び図12(c)に示すように、シード膜120をカソードとして、シード膜120とめっき液中に設けられたアノードとの間にバイアス電圧を印加することにより、凹部112内にCu膜122を形成する。VI>VI(ideal)であるため、凹部112の間口における成膜速度が速くなりすぎる。このため、図12(c)に示すように、Cu膜122には埋設不足が生じ、ボイド112aが生成する。

【0020】

図13は、電解めっき法により、絶縁膜110に形成された凹部112にCu膜を埋設する際において、VI<VI(ideal)となった場合を示している。図13(a)乃至図13(c)に示す各工程は、図12(a)乃至図12(c)に示す各工程とほぼ同様である。VI<VI(ideal)であるため、凹部112の底部における成膜速度が遅くなりすぎる。このため、図13(c)に示すように、Cu膜122には埋設不足が生じ、ボイド112aが生成する。

【0021】

このため、電解めっき法により、凹部内へめっき膜を埋設する場合は、めっき開始からの時間tによらず、被めっき面の表面電位VIをVI(ideal)に制御することが望ましい。

【0022】

図14は、めっき電流I(t)が時間tによらず一定値Iをとる場合の、カソード−アノード間の電圧V0(t)の変動を示している。カソード-アノード間の電流を一定としてめっき膜を成膜した場合、めっき液抵抗及びアノード抵抗の成膜中の変化は無視できるから、表面電位VIは時間tによって変化はない。なお、シード膜抵抗の抵抗は下がるため、印加電圧V0(t)は時間tとともに減少する。

【0023】

しかしながら、めっき液抵抗及びアノード抵抗は長期的には変化する。従って、めっき電流I(t)を時間tによらず一定値Iに制御するのみでは、長期的にはVIが変化する。なお、めっき液抵抗が変化する理由は、めっき液の長時間の使用により添加剤の分解生成物が蓄積することなどである。また、アノード抵抗が変化する理由は、ブラックフィルムの変化、及び長時間の使用によりアノード厚さが元の厚みに対して大きく変化するため、などである。

【0024】

また、参照電極の電位をVIと見なした場合、めっき膜が成膜されるにつれて、参照電極の電位と実際のVIの誤差が大きくなってしまうことがわかった。その理由を図2及び図3を用いて説明する。

【0025】

図2、及び図3は、参照電極34を用いてウェハ1上にめっき成膜を行う場合の電圧、電流、及び抵抗を説明する概略図である。図4は、カソード電極54と参照電極34の間の電位差VR(t)を一定に制御した場合におけるめっき膜22の表面電位VI(t)の変化を示すグラフである。図2は、めっき開始直後のめっき槽30の断面を示しており、図3は、めっき膜22がある程度成長した後のめっき槽30の断面を示している。また本図においては、ケーブル抵抗や接触抵抗は無視しており、めっき液抵抗REにはアノード、カソードでの分極抵抗等を含めており、アノード抵抗RAにはブラックフィルム(図示せず)等の抵抗も含めている。また、被めっき面と参照電極34の間の電位差を、被めっき面の表面電位VI(t)とする。

【0026】

ウェハ1へ電解めっきを行う場合、ウェハ1の外周に位置するシード膜20にカソード電極54を接続し、カソード電極54とアノード電極40の間に電圧V0(t)を印加する。するとめっき電流I(t)は、アノード電極40、めっき液32、及びカソードであるシード膜20を流れ、シード膜20の中心から外周に向かって流れる。このため、参照電極34とカソード電極54の電位差VR(t)は、シード膜抵抗Rc(t)によって変動する。一方、図3に示すようにシード膜20上にめっき膜22が成長すると、シード膜20を流れていた電流はシード膜20及びめっき膜22それぞれに分かれて流れるため、シード膜抵抗Rc(t)は低下する。

【0027】

このため、図4に示すように、VR(t)を一定値に制御しても、被めっき面の表面電位VI(t)はΔVI(t)ほど大きくなる。

【0028】

以上のことから、VR(t)を初期値に対してΔVI(t)ほど小さくすると、被めっき面の表面電位VI(t)の変動量(誤差)を小さくすることができる。ΔVI(t)は、時間tが経過するにつれて大きくなる。従って、本実施形態のように、制御部52が、めっき膜22の少なくとも一部を形成している間に、電位差VR(t)が徐々に下がるように電源50を制御すると、成膜中に生じるめっき膜22の表面電位と所望する表面電位との誤差を小さくすることができる。電位差VR(t)の降下量ΔVR(t)は、好ましくはΔVI(t)に等しい。また、本実施形態では電流ではなく電圧を制御しているため、長期的な使用によりめっき液の質が変化した場合でも、めっき膜22の表面電位と所望する表面電位との誤差が大きくなることを抑制できる。

【0029】

次に、ΔVI(t)の求め方について説明する。カソード-アノード間の電流を一定としてテスト用のウェハにめっき膜22の成膜を行い、この成膜における初期電圧、及び成膜中における電圧を測定し、電圧降下量を所定時間ごとに算出する。この電圧降下量がΔVI(t)に相当する。

【0030】

また、以下に説明するように、ΔVI(t)は、一次関数で近似することもできる。

【0031】

図5は、カソード電極54と参照電極34との間に成り立つ等価回路を示す図である。参照電極34とめっき膜22の表面の間の抵抗値をR1、シード膜20単体の抵抗をR0(=Rc(0))、めっき膜22単体の抵抗をR(t)とする。ΔVI(t)の初期値VI(0)に対するΔVI(t)の理論比は、以下の(1)式で求めることができる。

【数1】

【0032】

一方、成膜初期にはR(t)≫R0であるため、(R(t)+R0)をR(t)に近似できる。また、1/R(t)はめっき膜22の膜厚に比例し、さらにこの膜厚は成膜時間にほぼ比例する。このため、(1)式は成膜時間の一次関数に近似される。従って、ΔVI(t)及びVI(t)は、成膜時間の一次関数に近似される。VI(t)を近似する一次関数は、テスト用のウェハを用いて測定されたVI(0)、及びΔVI(t)を用いて求めることができる。

【0033】

図6は、制御部52による電源50の制御を説明するためのグラフである。このグラフの縦軸はVR(t)及びVI(t)であり、横軸は時間(t)である。上記したように、電位差VR(t)の降下量ΔVR(t)は、好ましくはΔVI(t)に等しい。またΔVI(t)は時間の一次関数で近似できる。このため、制御部52は、例えば実線で示すように、VR(t)=−At+Bという時間の一次関数に従うように電源50を制御してもよい。ただし、A,Bはともに正数である。また制御部52は、点線で示すように、VR(t)の降下量がΔVI(t)の実測値に従うように電源50を制御してもよい。

【0034】

図7は、めっき膜22が形成された後のウェハ1の断面図を示す。ウェハ1には複数の半導体装置が形成されている。この半導体装置は、ウェハ1に形勢されたトランジスタ等と、ウェハ1上に形成された第1の層間絶縁膜4と、その上に形成された絶縁膜10とを含む。本図に示す例において、絶縁膜10は第2の層間絶縁膜である。第1の層間絶縁膜4および絶縁膜10中には、配線やビアが形成されている。また絶縁膜10には、複数の凹部が形成されており、これら凹部にはめっき膜22が埋設される。めっき膜22は、例えばCu膜である。ここで凹部は例えば配線溝であるが、これに限らず、コンタクトホール、ビアホール等であってもよい。配線溝には、微細パターンである配線溝(例えば配線溝14)と、微細パターンである上記配線溝より幅広である配線溝(例えば配線溝12)と、の少なくとも2種類がある。微細パターンである配線溝の幅は、例えば0.3μm以下であり、アスペクト比は1以上である。これら配線溝にはめっき膜22が埋設されている。

【0035】

図8は、配線溝にめっき膜22が埋め込まれる様子を説明する断面図である。本図は、配線溝を代表して配線溝12,14を示す。配線溝は、絶縁膜10を選択的にエッチングすることにより形成されている。

【0036】

まず、図8(a)に示すように、絶縁膜10上ならびに配線溝12,14の側壁及び底面に、バリアメタル膜(図示せず)及びシード膜20を形成する。バリアメタル膜は、例えばTaN膜上へTa膜が形成された積層膜である。めっき膜22がCu膜である場合、シード膜20は、例えばCu膜である。シード膜20には、Cu以外にも、W、Ru、Pt、Pd、Rh、Ir、Ag、Te、およびTcからなる群より選択される少なくとも1種を主成分として含む材料を用いてもよい。またバリアメタル膜をシード膜20として使用できる場合もある。バリアメタル膜及びシード膜20は、例えばスパッタリング法等により形成される。

【0037】

ついで、図1に示しためっき装置を用いて電解めっきを行い、図8(b)に示すように、シード膜20上にめっき膜22を形成する。図1に示した制御部52は、めっき膜22の表面電位が、理想的な埋設を行うための表面電位になるように、電位差VR(t)を制御する。例えば制御部52は、通電開始直後から少なくともめっき膜22が微細パターンの配線溝12に埋設されるまで、電位差VR(t)が徐々に下がるように電源50を制御する。このため、めっき膜22が成長しても、めっき膜22の表面電位と、理想的な埋設を行うための表面電位との誤差は小さくなる。従って、配線溝に埋設されためっき膜22に埋設不良が生じることを抑制できる。

【0038】

なお、通電開始直後の電位差VR(t)は、例えば3V以上5V以下である。この場合、電位差VR(t)を徐々に下げる工程における電位差VR(t)の降下量の総量は、例えば0.1V以上1V以下である。

【0039】

その後、図8(c)に示すように、制御部52は、めっき膜22が幅広の配線溝(例えば配線溝14)に埋設され、その後一定の厚さになるまで、めっき電流I(t)が一定値となるように電源50を制御する。ここでの電流値は、例えば20A以上50A以下である。

【0040】

電解めっき工程の終了後、ウェハ1はアニール処理される。そしてCMPにより、配線溝外部に露出しためっき膜、シード膜、及びバリアメタル膜は除去される。本実施の形態の半導体装置は平坦化後における欠陥数が低減されている。この後、さらに層間絶縁膜形成、凹部形成、および金属膜形成を繰り返すことにより、多層配線構造が得られる。

(第2実施形態)

【0041】

次に、第2実施形態にかかるめっき装置について説明する。このめっき装置は、制御部52による電源50の制御を除いて、第1実施形態にかかるめっき装置と同様である。以下、制御部52による電源50の制御を除いて説明を省略する。

【0042】

図9は、本実施形態において制御部52は、通電開始直後から電位差VR(t)が徐々に下がるように電源50を制御するが、微細パターンの配線溝12に対するめっき膜22の埋設が完了する前に、電位差VR(t)の降下を終了する。この間、制御部52は、例えば一次関数VR(t)=−At+Bに従って電位差VR(t)を徐々に下げる。なお、A,Bはともに正数である。

【0043】

その後、制御部52は、配線溝12に対するめっき膜22の埋設が完了するまで、電位差VR(t)が一定値Cとなるように電源50を制御する。その後、制御部52は、めっき膜22が幅広の配線溝14に埋設され、その後一定の厚さになるまで、電流値が一定値となるように電源50を制御する。

【0044】

例えばシード膜抵抗の初期値R0が大きい場合、通電開始直後における被めっき面の表面電位の降下量ΔVI(t)は大きいが、その後の降下量ΔVI(t)は小さくなる。このような場合、電位差VR(t)を一種類の一次関数のみで近似すると誤差が大きくなる。これに対して制御部52が本実施形態のような制御を行うと、電位差VR(t)を近似しても誤差の発生を抑制できる。ウェハ1の表面積に対する、絶縁膜10に形成された凹部の総面積の比が大きい場合も、同様である。

【0045】

以上、図面を参照して実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【0046】

例えば、第1及び第2の実施形態において制御部52は、ΔVI(t)を2次以上の高次関数で近似し、この関数に従って電位差VR(t)を制御してもよい。また、通電開始から所定時間までは電位差VR(t)を一定にして、その後電位差VR(t)を徐々に下げ始めてもよい。

【0047】

また、第1の実施形態において制御部52は、図10に示すように、階段状に電位差VR(t)を徐々に下げてもよい。また第1及び第2の実施形態において制御部52は、電位差VR(t)が徐々に下がるように電源50を制御する場合に、図11に示すように、通電開始直後の期間である第1の期間には第1の一次関数VR(t)=−A1t+B1に従って電位差VR(t)を徐々に下げ、第2の期間には第2の一次関数VR(t)=−A2t+B2に従って電位差VR(t)を徐々に下げてもよい。ただしA1、A2、B1、及びB2はすべて正数であり、A1>A2、かつB1>B2である。

【0048】

このように、必要に応じて微細パターンである配線溝12の埋設終了までの区間を更に細かく分割し、それぞれの区間ごとに近似して精度を上げることは当該技術者であれば容易にできる。

【0049】

また第1及び第2の実施形態にかかるめっき装置において、制御部52は、V0(t)が徐々に下がるように電源50を制御してもよい。これは、V0(t)が徐々に下がると電位差VR(t)も徐々に下がるためである。V0(t)の具体的な制御方法は、第1及び第2の実施形態に示した電位差VR(t)の制御方法と同様である。なおこの場合、めっき装置に参照電極34を設けなくてもよい。

【符号の説明】

【0050】

1...ウェハ、10...絶縁膜、12,14...配線溝、20...シード膜、22...めっき膜、30...めっき槽、32...めっき液、34...参照電極、40...アノード電極、50...電源、52...制御部、54...カソード電極

【技術分野】

【0001】

本発明は、電解めっき法により金属膜を形成する工程を有する半導体装置の製造方法及びめっき装置に関する。

【背景技術】

【0002】

LSIのCu多層配線の形成方法として、ダマシン法がある。ダマシン法においては、トランジスタを具備したSiウェハ上に、単層または多層の絶縁膜を形成し、絶縁膜を選択的に除去することにより、配線形状の溝、及び多層配線の層間を電気的に結ぶビアを形成する。次に、バリアメタルとなる高融点金属を含む材料を化学気相成長法や物理気相成長法により堆積する。つづいて、シード膜となるCu薄膜を化学気相成長法や物理気相成長法にて堆積する。さらに、シード膜をカソードとした電解めっき法によりCu膜をシード膜上に成膜して、溝やビアをCuにより埋設する。その後、溝やビアの外に位置するバリアメタル、シード膜、及びCu膜を化学機械研磨法により除去する。これらの工程を繰り返すことにより、Cu多層配線が形成される。電解めっきによってCu膜を埋設する場合、Cu膜の埋設不良が生じないようにする必要がある。

【0003】

電解めっき法によるCu膜の埋設に関する技術としては、例えば特許文献1乃至3の技術がある。特許文献1には、カソード−アノード間の電圧を一定として、そのときの電流をモニタしてめっきの終点を検知する手法、およびカソード−アノード間の電流を一定として、そのときの電圧をモニタしてめっきの終点を検知する手法が開示されている。このときの電圧値、或いは、電流値はパターン埋設中には変化するが、埋設が終了すると一定となるので、それを以ってめっきの終点を検知する、としている。

【0004】

特許文献2においては、カソードまたはアノードを含む回路に流れる電流または電圧をモニタすることにより、めっき成膜の終点を検知する方法が開示されている。詳細には、電流一定の場合、めっき初期にはめっき電圧は下がっていき、次いでほぼ一定となるので、それを以ってめっきの終点を検知する、としている。

【0005】

特許文献3には、めっき液中のウェハの近傍に参照電極を設置し、この参照電極から得られるウェハの表面電位に基づいて、印加電圧を制御して成膜する方法が開示されている。参照電極はアノードよりもカソード側にある。このため、従来と比較してウェハの表面電位を正確に測定することができる。従って、カソード-アノード間の電圧を基に印加電圧を制御するよりも、ウェハの表面電位の制御性が良くなり、めっき膜の成膜不良を防止することができる、としている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2005−213596号公報

【特許文献2】特開2003−013297号公報

【特許文献3】特開2002−322592号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、上記した特許文献1及び2に記載のようにアノード−カソード間の電流を一定にした場合、めっき液が新しいうちはめっき膜の埋設不良を発生することを防止できたが、めっき液の使用期間が長くなるにつれて、めっき膜の埋設不良が発生しやすくなっていた。また、特許文献3に記載の技術でも、めっき膜の埋設不良が発生することがあった。

【課題を解決するための手段】

【0008】

本発明によれば、半導体基板上に形成されたシード膜にカソード電極を接続し、前記シード膜とめっき液中のアノード電極との間で電流を流すことにより、前記シード膜上にめっき膜を形成する工程において、前記めっき液中に挿入された参照電極と前記カソード電極との間の電位差、または前記カソード電極と前記アノード電極の電位差を、時間の経過と共に徐々に下げる工程を有する半導体装置の製造方法が提供される。

【0009】

また本発明によれば、めっき液を収容するめっき槽と、

めっき膜が形成される半導体基板に接続されるカソード電極と、

前記めっき液に浸漬されるアノード電極と、

前記アノード電極と前記カソード電極の間に電流を流す電源と、

前記めっき液に浸漬される参照電極と、

前記電源を制御する制御部と、

を備え、

前記制御部は、前記めっき膜の少なくとも一部を形成している間に、前記参照電極の電位と、前記カソード電極の電位との電位差が時間の経過と共に徐々に下がるように前記電源を制御するめっき装置が提供される。

【発明の効果】

【0010】

本発明によれば、めっき膜の埋設不良が発生することを抑制できる。

【図面の簡単な説明】

【0011】

【図1】第1実施形態にかかるめっき装置の構成を示す概略図である。

【図2】参照電極を用いてウェハ上にめっき成膜を行う場合の電圧、電流、及び抵抗を説明する概略図である。

【図3】参照電極を用いてウェハ上にめっき成膜を行う場合の電圧、電流、及び抵抗を説明する概略図である。

【図4】VR(t)を一定値に制御した場合の被めっき面の表面電位VI(t)の変動を示す図である。

【図5】カソード電極と参照電極との間に成り立つ等価回路を示す図である。

【図6】制御部による電源の制御を説明するためのグラフである。

【図7】めっき膜が形成された後のウェハの断面図を示す図である。

【図8】配線溝にめっき膜が埋め込まれる様子を説明する断面図である。

【図9】第2の実施形態にかかるめっき装置における、制御部による電源の制御を説明するためのグラフである。

【図10】制御部による電源の制御の変形例を説明するためのグラフである。

【図11】制御部による電源の制御の変形例を説明するためのグラフである。

【図12】電解めっき法により、絶縁膜に形成された凹部にCu膜を埋設する際において、VI>VI(ideal)となった場合を示す図である。

【図13】電解めっき法により、絶縁膜に形成された凹部にCu膜を埋設する際において、VI<VI(ideal)となった場合を示す図である。

【図14】めっき電流I(t)が時間tによらず一定値Iをとる場合の、カソード−アノード間の電圧V0(t)の変動を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

(第1実施形態)

【0013】

図1は、第1実施形態にかかるめっき装置の構成を示す概略図である。このめっき装置は、 ウェハ1(半導体基板)に形成されたシード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程を行う装置である。めっき膜22を形成する工程は、めっき液32中に挿入された参照電極34とカソード電極54との間の電位差を、時間の経過と共に徐々に下げる工程を有する。このため、被めっき面であるめっき膜22の表面電位と所望する表面電位との誤差が小さくなる。ここで電位差には、ハンチングが生じてもよい。以下、詳細に説明する。

【0014】

図1に示すめっき装置は、めっき槽30、参照電極34、アノード電極40、カソード電極54、電源50、及び制御部52を有する。めっき槽30はめっき液32を収容する。アノード電極40はめっき液32に浸漬される。カソード電極54は、ウェハ1のシード膜20に接続される。本図においてカソード電極54は、ウェハ1の右端側のみに接続しているが、ウェハ1の外周部の略全周に接続されていてもよい。電源50は、アノード電極40とカソード電極54の間に電流を流す。このとき電源50は、電流を制御する場合もあるし、電圧を制御する場合もある。参照電極34は、めっき液32に浸漬される。参照電極34は、めっき液32のうち、アノード電極40とシード膜20の間に位置するが、好ましくはシード膜20の近傍に位置する。制御部52は、カソード電極54と参照電極34の間の電位差VR(t)に基づいて、電源50を制御する。例えば制御部52は、めっき膜22の少なくとも一部を形成している間に、電位差VR(t)が時間の経過と共に徐々に下がるように電源50を制御する。この制御は、例えばアノード電極40とカソード電極54の電位差V0(t)が徐々に下がるように電源50を制御することにより、行える。

【0015】

また、ウェハ1には絶縁膜10が形成されている。絶縁膜10は、例えば配線層間を絶縁するための膜であり、表面に微細な溝パターンが形成されている。めっき膜22は、この微細パターンに埋設される。ウェハ1は、例えば直径が300mmのウェハである。

【0016】

次に、本実施の形態に至った経緯について説明する。埋設不良を抑制するために、めっき液には硫酸銅水溶液の他に塩酸と添加剤と呼ばれる複数種類の有機物が加わっている。この有機物によって、溝およびビアにおいては、側壁や間口よりも底部のめっき速度が高い、所謂ボトムアップ成膜を行うことができる。ボトムアップ成膜を行うためには、添加剤の濃度と基板に吸着した添加剤の活性度が重要である。

【0017】

添加剤の活性度はめっき液に対する被めっき面の表面電位によって決まるため、被めっき面の電位の制御がCu埋め込みを良好にするためには重要である。添加剤のうち成膜を加速する成分は、表面電位が高いほど活性化する。

【0018】

一方、パターンの間口での電界集中による成膜速度の増加も、被めっき面の表面電位が高いほど加速する。添加剤によって加速されたパターン底部での成膜速度が、パターン間口での成膜速度よりも十分速い場合にボトムアップにより埋設が成立する。このため、被めっき面の表面電位VIには、理想的な埋設をするための値VI(ideal)が存在する。

【0019】

図12は、電解めっき法により、絶縁膜110に形成された凹部112にCu膜を埋設する際において、VI>VI(ideal)となった場合を示している。まず図12(a)に示すように、絶縁膜110上及び凹部112内にシード膜120を形成する。ついで、図12(b)及び図12(c)に示すように、シード膜120をカソードとして、シード膜120とめっき液中に設けられたアノードとの間にバイアス電圧を印加することにより、凹部112内にCu膜122を形成する。VI>VI(ideal)であるため、凹部112の間口における成膜速度が速くなりすぎる。このため、図12(c)に示すように、Cu膜122には埋設不足が生じ、ボイド112aが生成する。

【0020】

図13は、電解めっき法により、絶縁膜110に形成された凹部112にCu膜を埋設する際において、VI<VI(ideal)となった場合を示している。図13(a)乃至図13(c)に示す各工程は、図12(a)乃至図12(c)に示す各工程とほぼ同様である。VI<VI(ideal)であるため、凹部112の底部における成膜速度が遅くなりすぎる。このため、図13(c)に示すように、Cu膜122には埋設不足が生じ、ボイド112aが生成する。

【0021】

このため、電解めっき法により、凹部内へめっき膜を埋設する場合は、めっき開始からの時間tによらず、被めっき面の表面電位VIをVI(ideal)に制御することが望ましい。

【0022】

図14は、めっき電流I(t)が時間tによらず一定値Iをとる場合の、カソード−アノード間の電圧V0(t)の変動を示している。カソード-アノード間の電流を一定としてめっき膜を成膜した場合、めっき液抵抗及びアノード抵抗の成膜中の変化は無視できるから、表面電位VIは時間tによって変化はない。なお、シード膜抵抗の抵抗は下がるため、印加電圧V0(t)は時間tとともに減少する。

【0023】

しかしながら、めっき液抵抗及びアノード抵抗は長期的には変化する。従って、めっき電流I(t)を時間tによらず一定値Iに制御するのみでは、長期的にはVIが変化する。なお、めっき液抵抗が変化する理由は、めっき液の長時間の使用により添加剤の分解生成物が蓄積することなどである。また、アノード抵抗が変化する理由は、ブラックフィルムの変化、及び長時間の使用によりアノード厚さが元の厚みに対して大きく変化するため、などである。

【0024】

また、参照電極の電位をVIと見なした場合、めっき膜が成膜されるにつれて、参照電極の電位と実際のVIの誤差が大きくなってしまうことがわかった。その理由を図2及び図3を用いて説明する。

【0025】

図2、及び図3は、参照電極34を用いてウェハ1上にめっき成膜を行う場合の電圧、電流、及び抵抗を説明する概略図である。図4は、カソード電極54と参照電極34の間の電位差VR(t)を一定に制御した場合におけるめっき膜22の表面電位VI(t)の変化を示すグラフである。図2は、めっき開始直後のめっき槽30の断面を示しており、図3は、めっき膜22がある程度成長した後のめっき槽30の断面を示している。また本図においては、ケーブル抵抗や接触抵抗は無視しており、めっき液抵抗REにはアノード、カソードでの分極抵抗等を含めており、アノード抵抗RAにはブラックフィルム(図示せず)等の抵抗も含めている。また、被めっき面と参照電極34の間の電位差を、被めっき面の表面電位VI(t)とする。

【0026】

ウェハ1へ電解めっきを行う場合、ウェハ1の外周に位置するシード膜20にカソード電極54を接続し、カソード電極54とアノード電極40の間に電圧V0(t)を印加する。するとめっき電流I(t)は、アノード電極40、めっき液32、及びカソードであるシード膜20を流れ、シード膜20の中心から外周に向かって流れる。このため、参照電極34とカソード電極54の電位差VR(t)は、シード膜抵抗Rc(t)によって変動する。一方、図3に示すようにシード膜20上にめっき膜22が成長すると、シード膜20を流れていた電流はシード膜20及びめっき膜22それぞれに分かれて流れるため、シード膜抵抗Rc(t)は低下する。

【0027】

このため、図4に示すように、VR(t)を一定値に制御しても、被めっき面の表面電位VI(t)はΔVI(t)ほど大きくなる。

【0028】

以上のことから、VR(t)を初期値に対してΔVI(t)ほど小さくすると、被めっき面の表面電位VI(t)の変動量(誤差)を小さくすることができる。ΔVI(t)は、時間tが経過するにつれて大きくなる。従って、本実施形態のように、制御部52が、めっき膜22の少なくとも一部を形成している間に、電位差VR(t)が徐々に下がるように電源50を制御すると、成膜中に生じるめっき膜22の表面電位と所望する表面電位との誤差を小さくすることができる。電位差VR(t)の降下量ΔVR(t)は、好ましくはΔVI(t)に等しい。また、本実施形態では電流ではなく電圧を制御しているため、長期的な使用によりめっき液の質が変化した場合でも、めっき膜22の表面電位と所望する表面電位との誤差が大きくなることを抑制できる。

【0029】

次に、ΔVI(t)の求め方について説明する。カソード-アノード間の電流を一定としてテスト用のウェハにめっき膜22の成膜を行い、この成膜における初期電圧、及び成膜中における電圧を測定し、電圧降下量を所定時間ごとに算出する。この電圧降下量がΔVI(t)に相当する。

【0030】

また、以下に説明するように、ΔVI(t)は、一次関数で近似することもできる。

【0031】

図5は、カソード電極54と参照電極34との間に成り立つ等価回路を示す図である。参照電極34とめっき膜22の表面の間の抵抗値をR1、シード膜20単体の抵抗をR0(=Rc(0))、めっき膜22単体の抵抗をR(t)とする。ΔVI(t)の初期値VI(0)に対するΔVI(t)の理論比は、以下の(1)式で求めることができる。

【数1】

【0032】

一方、成膜初期にはR(t)≫R0であるため、(R(t)+R0)をR(t)に近似できる。また、1/R(t)はめっき膜22の膜厚に比例し、さらにこの膜厚は成膜時間にほぼ比例する。このため、(1)式は成膜時間の一次関数に近似される。従って、ΔVI(t)及びVI(t)は、成膜時間の一次関数に近似される。VI(t)を近似する一次関数は、テスト用のウェハを用いて測定されたVI(0)、及びΔVI(t)を用いて求めることができる。

【0033】

図6は、制御部52による電源50の制御を説明するためのグラフである。このグラフの縦軸はVR(t)及びVI(t)であり、横軸は時間(t)である。上記したように、電位差VR(t)の降下量ΔVR(t)は、好ましくはΔVI(t)に等しい。またΔVI(t)は時間の一次関数で近似できる。このため、制御部52は、例えば実線で示すように、VR(t)=−At+Bという時間の一次関数に従うように電源50を制御してもよい。ただし、A,Bはともに正数である。また制御部52は、点線で示すように、VR(t)の降下量がΔVI(t)の実測値に従うように電源50を制御してもよい。

【0034】

図7は、めっき膜22が形成された後のウェハ1の断面図を示す。ウェハ1には複数の半導体装置が形成されている。この半導体装置は、ウェハ1に形勢されたトランジスタ等と、ウェハ1上に形成された第1の層間絶縁膜4と、その上に形成された絶縁膜10とを含む。本図に示す例において、絶縁膜10は第2の層間絶縁膜である。第1の層間絶縁膜4および絶縁膜10中には、配線やビアが形成されている。また絶縁膜10には、複数の凹部が形成されており、これら凹部にはめっき膜22が埋設される。めっき膜22は、例えばCu膜である。ここで凹部は例えば配線溝であるが、これに限らず、コンタクトホール、ビアホール等であってもよい。配線溝には、微細パターンである配線溝(例えば配線溝14)と、微細パターンである上記配線溝より幅広である配線溝(例えば配線溝12)と、の少なくとも2種類がある。微細パターンである配線溝の幅は、例えば0.3μm以下であり、アスペクト比は1以上である。これら配線溝にはめっき膜22が埋設されている。

【0035】

図8は、配線溝にめっき膜22が埋め込まれる様子を説明する断面図である。本図は、配線溝を代表して配線溝12,14を示す。配線溝は、絶縁膜10を選択的にエッチングすることにより形成されている。

【0036】

まず、図8(a)に示すように、絶縁膜10上ならびに配線溝12,14の側壁及び底面に、バリアメタル膜(図示せず)及びシード膜20を形成する。バリアメタル膜は、例えばTaN膜上へTa膜が形成された積層膜である。めっき膜22がCu膜である場合、シード膜20は、例えばCu膜である。シード膜20には、Cu以外にも、W、Ru、Pt、Pd、Rh、Ir、Ag、Te、およびTcからなる群より選択される少なくとも1種を主成分として含む材料を用いてもよい。またバリアメタル膜をシード膜20として使用できる場合もある。バリアメタル膜及びシード膜20は、例えばスパッタリング法等により形成される。

【0037】

ついで、図1に示しためっき装置を用いて電解めっきを行い、図8(b)に示すように、シード膜20上にめっき膜22を形成する。図1に示した制御部52は、めっき膜22の表面電位が、理想的な埋設を行うための表面電位になるように、電位差VR(t)を制御する。例えば制御部52は、通電開始直後から少なくともめっき膜22が微細パターンの配線溝12に埋設されるまで、電位差VR(t)が徐々に下がるように電源50を制御する。このため、めっき膜22が成長しても、めっき膜22の表面電位と、理想的な埋設を行うための表面電位との誤差は小さくなる。従って、配線溝に埋設されためっき膜22に埋設不良が生じることを抑制できる。

【0038】

なお、通電開始直後の電位差VR(t)は、例えば3V以上5V以下である。この場合、電位差VR(t)を徐々に下げる工程における電位差VR(t)の降下量の総量は、例えば0.1V以上1V以下である。

【0039】

その後、図8(c)に示すように、制御部52は、めっき膜22が幅広の配線溝(例えば配線溝14)に埋設され、その後一定の厚さになるまで、めっき電流I(t)が一定値となるように電源50を制御する。ここでの電流値は、例えば20A以上50A以下である。

【0040】

電解めっき工程の終了後、ウェハ1はアニール処理される。そしてCMPにより、配線溝外部に露出しためっき膜、シード膜、及びバリアメタル膜は除去される。本実施の形態の半導体装置は平坦化後における欠陥数が低減されている。この後、さらに層間絶縁膜形成、凹部形成、および金属膜形成を繰り返すことにより、多層配線構造が得られる。

(第2実施形態)

【0041】

次に、第2実施形態にかかるめっき装置について説明する。このめっき装置は、制御部52による電源50の制御を除いて、第1実施形態にかかるめっき装置と同様である。以下、制御部52による電源50の制御を除いて説明を省略する。

【0042】

図9は、本実施形態において制御部52は、通電開始直後から電位差VR(t)が徐々に下がるように電源50を制御するが、微細パターンの配線溝12に対するめっき膜22の埋設が完了する前に、電位差VR(t)の降下を終了する。この間、制御部52は、例えば一次関数VR(t)=−At+Bに従って電位差VR(t)を徐々に下げる。なお、A,Bはともに正数である。

【0043】

その後、制御部52は、配線溝12に対するめっき膜22の埋設が完了するまで、電位差VR(t)が一定値Cとなるように電源50を制御する。その後、制御部52は、めっき膜22が幅広の配線溝14に埋設され、その後一定の厚さになるまで、電流値が一定値となるように電源50を制御する。

【0044】

例えばシード膜抵抗の初期値R0が大きい場合、通電開始直後における被めっき面の表面電位の降下量ΔVI(t)は大きいが、その後の降下量ΔVI(t)は小さくなる。このような場合、電位差VR(t)を一種類の一次関数のみで近似すると誤差が大きくなる。これに対して制御部52が本実施形態のような制御を行うと、電位差VR(t)を近似しても誤差の発生を抑制できる。ウェハ1の表面積に対する、絶縁膜10に形成された凹部の総面積の比が大きい場合も、同様である。

【0045】

以上、図面を参照して実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【0046】

例えば、第1及び第2の実施形態において制御部52は、ΔVI(t)を2次以上の高次関数で近似し、この関数に従って電位差VR(t)を制御してもよい。また、通電開始から所定時間までは電位差VR(t)を一定にして、その後電位差VR(t)を徐々に下げ始めてもよい。

【0047】

また、第1の実施形態において制御部52は、図10に示すように、階段状に電位差VR(t)を徐々に下げてもよい。また第1及び第2の実施形態において制御部52は、電位差VR(t)が徐々に下がるように電源50を制御する場合に、図11に示すように、通電開始直後の期間である第1の期間には第1の一次関数VR(t)=−A1t+B1に従って電位差VR(t)を徐々に下げ、第2の期間には第2の一次関数VR(t)=−A2t+B2に従って電位差VR(t)を徐々に下げてもよい。ただしA1、A2、B1、及びB2はすべて正数であり、A1>A2、かつB1>B2である。

【0048】

このように、必要に応じて微細パターンである配線溝12の埋設終了までの区間を更に細かく分割し、それぞれの区間ごとに近似して精度を上げることは当該技術者であれば容易にできる。

【0049】

また第1及び第2の実施形態にかかるめっき装置において、制御部52は、V0(t)が徐々に下がるように電源50を制御してもよい。これは、V0(t)が徐々に下がると電位差VR(t)も徐々に下がるためである。V0(t)の具体的な制御方法は、第1及び第2の実施形態に示した電位差VR(t)の制御方法と同様である。なおこの場合、めっき装置に参照電極34を設けなくてもよい。

【符号の説明】

【0050】

1...ウェハ、10...絶縁膜、12,14...配線溝、20...シード膜、22...めっき膜、30...めっき槽、32...めっき液、34...参照電極、40...アノード電極、50...電源、52...制御部、54...カソード電極

【特許請求の範囲】

【請求項1】

半導体基板上に形成されたシード膜にカソード電極を接続し、前記シード膜とめっき液中のアノード電極との間で電流を流すことにより、前記シード膜上にめっき膜を形成する工程を備え、

前記めっき膜を形成する工程において、前記めっき液中に挿入された参照電極と前記カソード電極との間の電位差、または前記カソード電極と前記アノード電極の電位差を、時間の経過と共に徐々に下げる工程を有する半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法において、

前記電位差を徐々に下げる工程において、前記電位差を時間の一次関数に従って下げる半導体装置の製造方法。

【請求項3】

請求項1又は2に記載の半導体装置の製造方法において、

前記半導体基板は絶縁膜と、前記絶縁膜に形成された開口パターンと、を備え、

前記シード膜は、前記絶縁膜上並びに前記開口パターンの側壁及び底面に形成されている半導体装置の製造方法。

【請求項4】

請求項3に記載の半導体装置の製造方法において、

前記電位差を徐々に下げる工程は、通電開始直後に開始し、前記めっき膜が前記開口パターン内を埋める以降に終了する半導体装置の製造方法。

【請求項5】

請求項3に記載の半導体装置の製造方法において、

前記めっき膜を形成する工程において、

前記電位差を徐々に下げる工程は、通電開始直後から開始し、前記めっき膜が前記開口パターン内を埋める前に終了し、

その後、前記めっき膜が前記開口パターン内を埋めるまで前記電位差を一定値に制御する記載の半導体装置の製造方法。

【請求項6】

請求項3乃至5に記載の半導体装置の製造方法において、

前記開口パターンは幅0.3μm以下であり、

前記電位差を徐々に下げる工程における前記電位差の降下量の総量は0.1V以上1V以下である半導体装置の製造方法。

【請求項7】

めっき液を収容するめっき槽と、

めっき膜が形成される半導体基板に接続されるカソード電極と、

前記めっき液に浸漬されるアノード電極と、

前記アノード電極と前記カソード電極の間に電圧を印加する電源と、

前記めっき液に浸漬される参照電極と、

前記電源を制御する制御部と、

を備え、

前記制御部は、前記めっき膜の少なくとも一部を形成している間に、前記参照電極の電位と、前記カソード電極の電位との電位差が時間の経過と共に徐々に下がるように前記電源を制御するめっき装置。

【請求項1】

半導体基板上に形成されたシード膜にカソード電極を接続し、前記シード膜とめっき液中のアノード電極との間で電流を流すことにより、前記シード膜上にめっき膜を形成する工程を備え、

前記めっき膜を形成する工程において、前記めっき液中に挿入された参照電極と前記カソード電極との間の電位差、または前記カソード電極と前記アノード電極の電位差を、時間の経過と共に徐々に下げる工程を有する半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法において、

前記電位差を徐々に下げる工程において、前記電位差を時間の一次関数に従って下げる半導体装置の製造方法。

【請求項3】

請求項1又は2に記載の半導体装置の製造方法において、

前記半導体基板は絶縁膜と、前記絶縁膜に形成された開口パターンと、を備え、

前記シード膜は、前記絶縁膜上並びに前記開口パターンの側壁及び底面に形成されている半導体装置の製造方法。

【請求項4】

請求項3に記載の半導体装置の製造方法において、

前記電位差を徐々に下げる工程は、通電開始直後に開始し、前記めっき膜が前記開口パターン内を埋める以降に終了する半導体装置の製造方法。

【請求項5】

請求項3に記載の半導体装置の製造方法において、

前記めっき膜を形成する工程において、

前記電位差を徐々に下げる工程は、通電開始直後から開始し、前記めっき膜が前記開口パターン内を埋める前に終了し、

その後、前記めっき膜が前記開口パターン内を埋めるまで前記電位差を一定値に制御する記載の半導体装置の製造方法。

【請求項6】

請求項3乃至5に記載の半導体装置の製造方法において、

前記開口パターンは幅0.3μm以下であり、

前記電位差を徐々に下げる工程における前記電位差の降下量の総量は0.1V以上1V以下である半導体装置の製造方法。

【請求項7】

めっき液を収容するめっき槽と、

めっき膜が形成される半導体基板に接続されるカソード電極と、

前記めっき液に浸漬されるアノード電極と、

前記アノード電極と前記カソード電極の間に電圧を印加する電源と、

前記めっき液に浸漬される参照電極と、

前記電源を制御する制御部と、

を備え、

前記制御部は、前記めっき膜の少なくとも一部を形成している間に、前記参照電極の電位と、前記カソード電極の電位との電位差が時間の経過と共に徐々に下がるように前記電源を制御するめっき装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−211394(P2012−211394A)

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願番号】特願2012−131579(P2012−131579)

【出願日】平成24年6月11日(2012.6.11)

【分割の表示】特願2008−30875(P2008−30875)の分割

【原出願日】平成20年2月12日(2008.2.12)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願日】平成24年6月11日(2012.6.11)

【分割の表示】特願2008−30875(P2008−30875)の分割

【原出願日】平成20年2月12日(2008.2.12)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]