半導体装置の製造方法及び半導体装置、電子機器

【課題】空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供する。

【解決手段】第1の基板は、第1の面と第2の面とを有する第1の基材と、第1の基材の第1の面側に設けられた犠牲層と、第1の基材の第1の面と第2の面との間を貫通する貫通電極と、貫通電極と第1の基材との間に設けられた絶縁膜と、を有する。第2の基板は、第3の面を有する第2の基材と、第2の基材の第3の面側に設けられたバンプと、第2の基材の第3の面側に設けられ、バンプを囲む環状導電部と、を有する。第2の面と第3の面とを対向させた状態で、貫通電極とバンプとを接続すると共に、第1の基板の周縁部を環状導電部に埋入させる実装工程と、実装工程の後で、犠牲層をエッチングして第1の基材の第1の面側に空洞部を形成するエッチング工程と、を含む。

【解決手段】第1の基板は、第1の面と第2の面とを有する第1の基材と、第1の基材の第1の面側に設けられた犠牲層と、第1の基材の第1の面と第2の面との間を貫通する貫通電極と、貫通電極と第1の基材との間に設けられた絶縁膜と、を有する。第2の基板は、第3の面を有する第2の基材と、第2の基材の第3の面側に設けられたバンプと、第2の基材の第3の面側に設けられ、バンプを囲む環状導電部と、を有する。第2の面と第3の面とを対向させた状態で、貫通電極とバンプとを接続すると共に、第1の基板の周縁部を環状導電部に埋入させる実装工程と、実装工程の後で、犠牲層をエッチングして第1の基材の第1の面側に空洞部を形成するエッチング工程と、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法及び半導体装置、電子機器に関する。

【背景技術】

【0002】

従来技術として、例えば、特許文献1〜3に開示されたものがある。即ち、特許文献1には、犠牲層を除去することにより形成された空洞部の上方で支持部により支えられた構造の焦電型検出素子が開示されている。また、特許文献2には、シリコンの第1の面(集積回路形成面)と第2の面(裏面)との間を貫く貫通電極が開示されている。そして、特許文献3には、電子回路素子を基板に実装する際に、電子回路素子が有する外周封止用電極を、基板が有する封止用電極に接合することによって、外周封止用電極の内側に配置されているチップ電極を封止する技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011−153851号公報

【特許文献2】特開2010−177237号公報

【特許文献3】特開2004−214469号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、特許文献1に開示されたような、空洞部の上方で支えられた構造の焦電型検出素子を他の基板に実装する場合、この焦電型素子に実装時の荷重が加えられると、その荷重によって空洞部が破壊されてしまう可能性がある。このような空洞部の破壊を防ぐ方法として、空洞部が形成される前に焦電型素子を基板に実装しておき、実装後に空洞部を形成する方法が考えられる。また、上記の実装に際しては、特許文献3に開示されているように、外周封止用電極と封止用電極とを接続することにより、それらの内側に位置するチップ電極を気密封止する方法が考えられる。

【0005】

ここで、上記の焦電型検出素子が、特許文献2に開示されたような貫通電極を有する場合は、特許文献2の図3に記載されている下地層141(例えばシリコン酸化物(SiO2)やシリコン窒化物(Si3N4)等の絶縁性材料からなる)は外周封止用電極の外側に露出した構造となる。このため、犠牲層をエッチングして空洞部を形成する際に、この下地層もエッチングされてしまう可能性があった。下地層がエッチングされると、外周封止用電極と半導体基板との間に隙間が生じてエッチャント等が侵入する。その結果、上記の気密封止が破られて、焦電型素子と基板との接続の信頼性が低下してしまう可能性があった。

そこで、この発明はこのような事情に鑑みてなされたものであって、空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供することを目的の一つとする。

【課題を解決するための手段】

【0006】

上記課題を解決するために、本発明の一態様に係る半導体装置の製造方法は、少なくとも一方が半導体素子を含む第1の基板及び第2の基板を互いに接続して半導体装置を製造する方法であって、前記第1の基板は、第1の面及び該第1の面の反対側の第2の面を有する第1の基材と、前記第1の基材の第1の面側に設けられた犠牲層と、前記第1の基材の前記第1の面と前記第2の面との間を貫通する貫通電極と、前記貫通電極と前記第1の基材との間に設けられた絶縁膜と、を有し、前記第2の基板は、第3の面を有する第2の基材と、前記第2の基材の前記第3の面側に設けられたバンプと、前記第2の基材の前記第3の面側に設けられ、前記バンプを囲む環状導電部と、を有し、前記第2の面と前記第3の面とを対向させた状態で、前記貫通電極と前記バンプとを接続すると共に、前記第1の基板の周縁部を前記環状導電部に埋入させる実装工程と、前記実装工程の後で、前記犠牲層をエッチングして前記第1の基材の前記第1の面側に空洞部を形成するエッチング工程と、を含むことを特徴とする。

このような製造方法であれば、エッチング工程の前に実装工程を行う。実装工程では空洞部は未形成であり、第1の基板に付加される荷重で空洞部が壊れることはない。このため、上記の空洞部を壊すことなく、第1の基板を第2の基板に実装することができる。

【0007】

また、この実装工程では、第1の基板の周縁部を環状導電部に埋入することにより、絶縁膜を環状導電部で囲まれた領域内に封止する。絶縁膜が環状導電部の外側に露出しないようにすることができるので、エッチング工程で絶縁膜がエッチングされることを防ぐことができ、第1の基板と第2の基板との間に隙間が生じることを防ぐことができる。従って、この隙間を通って半導体装置内に水分等が侵入することを防ぐことができ、貫通電極等の腐食を防ぐことができる。これにより、第1の基板と第2の基板との接続の信頼性を高めることができる。

【0008】

なお、本発明の「第1の基板」としては、例えば、後述する半導体チップ10、又は、半導体チップ110が該当する。「第2の基板」としては、例えば、後述するベース基板50が該当する。「第1の基材」としては例えば後述する基材1が該当し、「第1の面」としては例えば後述する表面1aが該当し、「第2の面」としては例えば後述する裏面1bが該当する。また、「第2の基材」としては例えば後述する基材51が該当し、「第3の面」としては例えば後述する表面51aが該当する。さらに、「絶縁膜」としては、例えば、後述するTSV絶縁膜27が該当する。「環状導電部」としては、例えば、後述する環状バンプ70が該当する。

【0009】

また、上記の半導体装置の製造方法において、前記実装工程の前に、前記貫通電極の前記バンプと接続される側の面に凹部を形成する凹部形成工程、をさらに含み、前記実装工程では、前記凹部の内側に前記バンプの先端部を入れた状態で前記貫通電極と前記バンプとを接続することを特徴としてもよい。このような製造方法であれば、実装工程でのバンプの潰れを抑制することができる。これにより、バンプが潰れて水平方向に広がり、隣り合うバンプ同士が意図せず接触する(即ち、ショートする)可能性を低減することができる。

【0010】

本発明の別の態様に係る半導体装置は、少なくとも一方が半導体素子を含む第1の基板及び第2の基板が互いに接続された半導体装置であって、前記第1の基板は、第1の面及び該第1の面の反対側の第2の面を有し、前記第1の面側に空洞部が設けられた第1の基材と、前記第1の基材の前記第1の面と前記第2の面との間を貫通する貫通電極と、前記貫通電極と前記第1の基材との間に設けられた絶縁膜と、を有し、前記第2の基板は、前記第2の面と対向する第3の面を有する第2の基材と、前記第2の基材の前記第3の面側に設けられ、前記貫通電極に接続されたバンプと、前記第2の基材の前記第3の面側に設けられ、前記バンプを囲む環状導電部と、を有し、前記第1の基板の周縁部が前記環状導電部に埋入していることを特徴とする。このような構成であれば、上記の製造方法により半導体装置を製造することができる。従って、空洞部が破壊されておらず、且つ、第1の基板と第2の基板とが信頼性高く接続された半導体装置を提供することができる。

【0011】

また、上記の半導体装置において、前記第1の基板は、前記第1の基材の前記第1の面と前記第2の面との間であって、前記貫通電極よりも前記周縁部に近い位置を貫通する第2の貫通電極、をさらに有し、前記第2の貫通電極と前記第1の基材との間に絶縁膜が設けられており、前記第2の貫通電極と前記環状導電部とが接続されていることを特徴としてもよい。このような構成であれば、第2の基板の環状導電部を第1の基板と接続する端子として用いることができる。例えば、環状導電部が接地電位(グランド)に接続される場合は、この環状導電部を半導体素子と第2の基板とに共通のグランド端子として用いることができる。

【0012】

また、上記の半導体装置において、前記第1の基板の前記第2の面と前記第2の基板の前記第3の面との間であって、前記環状導電部で囲まれる領域に設けられた樹脂、をさらに有することを特徴としてもよい。このような構成であれば、第1の基板と第2の基板とに樹脂を密着させることができる。樹脂と第1の基板との間に働く接着力と、樹脂と第2の基板との間に働く接着力とにより、第1の基板と第2の基板との接続強度をさらに高めることができる。これにより、第1の基板と第2の基板との接続の信頼性をさらに高めることができる。なお、本発明の「樹脂」としては、例えば、後述する封止樹脂81が該当する。

本発明のさらに別の態様に係る電子機器は、上記の半導体装置を備えることを特徴とする。このような構成であれば、空洞部が破壊されておらず、且つ、第1の基板と第2の基板とが信頼性高く接続された半導体装置を備えた電子機器を提供することができる。

【図面の簡単な説明】

【0013】

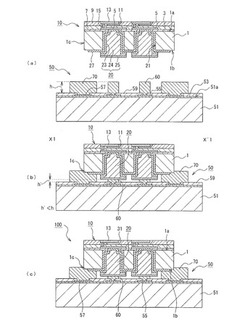

【図1】第1実施形態に係る半導体装置100の製造方法を示す図。

【図2】バンプ60及び環状バンプ70の形状等の一例を示す図。

【図3】半導体チップ10と環状バンプ70との位置関係の一例を示す図。

【図4】半導体装置100の第1変形例を示す図。

【図5】半導体装置100の第2変形例を示す図。

【図6】半導体装置100の第3変形例を示す図。

【図7】第2実施形態に係る半導体装置200の製造方法を示す図。

【図8】第2の貫通電極20bと環状バンプ70との位置関係の一例を示す図。

【図9】半導体装置200の第1変形例を示す図。

【図10】半導体装置200の第2変形例を示す図。

【図11】半導体装置200の第3変形例を示す図。

【発明を実施するための形態】

【0014】

以下、本発明の実施の形態について図面を参照しながら説明する。なお、以下に説明する各図において、同一の構成を有する部分には同一の符号を付し、その重複する説明は省略する。

(1)第1実施形態

(1.1)製造方法及び構成

図1(a)〜(c)は、本発明の第1実施形態に係る半導体装置100の製造方法を示す断面図である。図1(a)に示すように、まず始めに、半導体チップ10と、ベース基板50とを用意する。

【0015】

半導体チップ10は、例えばシリコン等からなる基材1と、この基材1の表面1aの側に形成された第1の絶縁層3と、第1の絶縁層3上に形成された電極5と、電極5を覆うように形成された第2の絶縁層7と、第2の絶縁層7上に形成された第3の絶縁層9と、第3の絶縁層9に埋め込まれた犠牲層11と、この犠牲層11の一部を覆うように第3の絶縁層9上に設けられた素子13と、素子13と電極5とを接続するプラグ電極15と、を備える。第1の絶縁層3、第2の絶縁層7、第3の絶縁層9は、例えばシリコン酸化膜(SiO2)又はシリコン窒化膜(Si3N4)からなる。電極5は、例えば、窒化チタン(TiN)からなる。犠牲層11は、例えばシリコン酸化膜からなる。素子13は、例えば赤外線を検出可能な焦電センサーである。プラグ電極15は、例えばタングステン(W)からなる。

【0016】

なお、図示しないが、第3の絶縁層9の表面と、第2の絶縁層7と犠牲層11との間、及び、第3の絶縁層9と犠牲層11との間には、エッチング防止膜が設けられていてもよい。また、第1の絶縁層3と、第2の絶縁層7及び、第3の絶縁層9の側面にもエッチング防止膜が設けられていてもよい。このエッチング防止膜は、後述の空洞部を形成するために犠牲層11をエッチングする工程において、第2の絶縁層7と第3の絶縁層9がエッチングされることを防止するための膜である。エッチング防止膜としては、例えば、シリコン酸化膜からなる犠牲層11をエッチングするときに用いられるフッ化水素(HF)に対して、耐食性のある材質(例えば、シリコン窒化膜、アルミニウム、タングステン等)の膜である。

【0017】

また、この半導体チップ10は、貫通電極(TSV:Through Si Via)20と、この貫通電極20と基材1との間に設けられたTSV絶縁膜27と、を備える。図1(a)に示すように、基材1には、その表面1aと裏面1bとの間を貫通する貫通孔21が設けられている。貫通電極20は、この貫通孔21内にTSV絶縁膜27を介して設けられている。即ち、TSV絶縁膜27は、貫通孔21の内側面から基材1の裏面1bにかけて設けられている。TSV絶縁膜27は、例えばシリコン酸化膜である。

【0018】

貫通電極20は、例えば、スパッタリングで形成されたシード層23と、電解めっき法で形成された電極本体24と、電極本体24のベース基板50と接続される側の面(例えば、下面)に設けられたろう材25と、を有する。シード層23及び電極本体24は例えば銅(Cu)であり、ろう材25は例えばスズと銀との合金(Sn−Ag)である。このような構成の貫通電極20は、第1の絶縁層3を貫いて電極5に接続されている。

【0019】

一方、ベース基板50は、例えばシリコン等からなる基材51と、この基材51の表面51aの側に形成された絶縁層53と、この絶縁層53上に形成された第1の電極55及び第2の電極57と、これら第1の電極55及び第2の電極57を覆うように絶縁層53上に形成されたパシベーション膜59と、このパシベーション膜59上に形成されたバンプ60及び環状バンプ70と、を備える。図1(a)に示すように、パシベーション膜59には、第1の電極55又は第2の電極57を底面とする開口部が設けられている。この開口部を介して、バンプ60は電極55に接続され、環状バンプ70は電極57に接続されている。

【0020】

図2は、バンプ60及び環状バンプ70の各形状と、これらの位置関係の一例を示す平面図である。図2に示すように、バンプ60の平面視による形状(以下、平面形状)は例えば円形である。また、環状バンプ70の平面形状は例えば矩形枠である。環状バンプ70はバンプ60を平面視で囲むように配置されている(即ち、バンプ60は環状バンプ70で囲まれた領域に配置されている。)。

【0021】

図1(a)に戻って、絶縁層53は、例えばシリコン酸化膜からなる。第1の電極55と第2の電極57は、例えばアルミニウム(Al)からなる。バンプ60及び環状バンプ70は、例えば金(Au)からなる。パシベーション膜59は、例えばポリイミドからなる。また、図1(a)において、バンプ60及び環状バンプ70のパシベーション膜59からの高さをhとしたとき、hは例えば10〜25μmである。なお、図示しないが、第1の電極55とバンプ60との間、及び第2の電極57と環状バンプ70との間には、それぞれ、チタン(Ti)、タングステン(W)、プラチナ(Pt)、銅(Cu)又はクロム(Cr)等の中間層が設けられていてもよい。

【0022】

次に、用意した半導体チップ10とベース基板50とを重ね合わせて接合する。即ち、半導体チップ10をベース基板50に実装する(実装工程)。ここでは、図1(a)の矢印で示すように、半導体チップ10の裏面1bの側とベース基板50の表面51aの側とを対向させる。そして、この状態で半導体チップ10をベース基板50に相対的に押圧して、半導体チップ10をベース基板50に接合する。

【0023】

これにより、図1(b)に示すように、貫通電極20とバンプ60とを接続すると共に、半導体チップ10の周縁部(側面を含む)1cを環状バンプ70に埋入させる。なお、この実装工程では、バンプ60は貫通電極20と接合することにより押し潰される。押し潰された後のバンプ60のパシベーション膜59からの高さをh´としたとき、h>h´である。h´は例えば5〜15μmである。

図3は、半導体チップ10をベース基板50に実装した後の、半導体チップ10と環状バンプ70との位置関係の一例を示す平面図である。図3に示すように、犠牲層11のエッチング工程では、半導体チップ10の周縁部1cは全周に亘って環状バンプ70に埋設されている。

【0024】

次に、実装工程の後で、犠牲層11をエッチングして除去する(エッチング工程)。このエッチング工程では、図1(b)及び図3に示したように、犠牲層11の一部が素子13の下から露出している。このため、半導体チップ10をベース基板50と共に、HF溶液に浸漬する(又は、HFべ―パー雰囲気に晒す)ことによって、シリコン酸化膜からなる犠牲層11をエッチングして除去することができる。これにより、図1(c)に示すように、半導体チップ10に空洞部31が形成される。以上の工程を経て、半導体チップ10とベース基板50とが接続され、空洞部31の上方に素子13を有する構造の半導体装置100が完成する。

【0025】

完成後の半導体装置100は、下記の構成を有する。即ち、図1(c)に示すように、半導体装置100は、半導体チップ10とベース基板50とを備える。半導体チップ10は、表面1a側に空洞部31が設けられた基材1と、この基材1の表面1aと裏面1bとの間を貫通する貫通電極20と、貫通電極20と基材1との間に設けられたTSV絶縁膜27と、を有する。ベース基板50は、基材51と、この基材51の表面51a側に設けられたバンプ60と、表面51側に設けられ、バンプ60を囲む環状バンプ70と、を有する。そして、半導体チップ10の裏面1bとベース基板50の表面51aとが対向した状態で、貫通電極20とバンプ60とが接続されると共に、半導体チップ10の周縁部1cが環状バンプ70に埋入している。ここで、「半導体チップ10の周縁部1cが環状バンプ70に埋入している」とは、半導体チップ10の表面1a及び裏面1bを接続する側面と裏面1bとで形成される角部とが、環状バンプ70に覆われている状態のことである。

【0026】

なお、図示しないが、ベース基板50には、第1の電極55又は第2の電極57等の配線の他に、例えば、半導体チップ10を制御する制御回路等が形成されていてもよい。この図示しない制御回路は、実装工程の前に、CMOSプロセスでベース基板50に形成することが可能である。このように、制御回路がベース基板50に形成されている場合は、例えば、この制御回路と素子13との間で貫通電極20(第2実施形態では、第1の貫通電極20a)を経由して、信号の送受が行われる。

【0027】

(1.2)第1実施形態の効果

本発明の第1実施形態によれば、エッチング工程の前に実装工程を行う。実装工程では空洞部31は未形成であり、半導体チップ10に付加される荷重で空洞部31が壊れることはない。このため、素子13の下方に形成される空洞部31を壊すことなく、半導体チップ10をベース基板50に実装することができる。

【0028】

また、この実装工程では、半導体チップ10の周縁部1cを環状バンプ70に埋入させる。これにより、TSV絶縁膜27を環状バンプ70で囲まれた領域内に封止する。TSV絶縁膜27が環状バンプ70の外側に露出しないようにすることができるので、エッチング工程でTSV絶縁膜27がエッチングされることを防ぐことができ、半導体チップ10とベース基板50との間に隙間が生じることを防ぐことができる。この隙間を通って半導体装置内に水分等が侵入することを防ぐことができるため、貫通電極20等の腐食を防ぐことができる。従って、半導体チップ10とベース基板50との接続の信頼性を高めることができる。次に、第1実施形態の変形例を示す。

【0029】

(1.3)第1変形例

図4は、半導体装置100の第1変形例を示す断面図である。図4に示すように、半導体装置100は、半導体チップ10とベース基板50との間であって、環状バンプ70で囲まれた領域内に封止樹脂81を有していてもよい。封止樹脂81としては、例えば、熱硬化性のエポキシ系樹脂、ポリイミド系樹脂、アクリル系樹脂などが挙げられる。このような構成であれば、半導体チップ10とベース基板50とに封止樹脂81を密着させることができる。封止樹脂81と半導体チップ10との間に働く接着力と、封止樹脂81とベース基板50との間に働く接着力とにより、半導体チップ10とベース基板50との接続強度をさらに高めることができる。これにより、半導体チップ10とベース基板50との接続の信頼性をさらに高めることができる。

【0030】

なお、上記の封止樹脂81は、例えば実装工程の前に、ベース基板50の環状バンプ70で囲まれた領域に塗布する。そして、封止樹脂81を塗布した後で半導体チップ10をベース基板50に実装する。これにより、半導体チップ10とベース基板50との間であって、環状バンプ70で囲まれた領域に封止樹脂81を封入することができる。この封止樹脂81が熱硬化性の場合は、例えば、実装時の熱で封止樹脂81を硬化させることができる。

【0031】

(1.4)第2の変形例

図5は、半導体装置100の第2変形例を示す断面図である。図5に示すように、半導体装置100は、環状バンプ70の半導体チップ10から露出している領域71上に、半導体チップ10の側面を覆う絶縁性の樹脂83を有していてもよい。この樹脂83は、例えば、図1(b)の段階で上記の領域71上に塗布しておく。即ち、半導体チップ10の周縁部1cを環状バンプ70に埋設した後で樹脂83を塗布しておく。そして、樹脂83を塗布した後で、犠牲層11をエッチングする。樹脂83としては、例えば、熱硬化性又は紫外線硬化性のエポキシ系樹脂、ポリイミド系樹脂、アクリル系樹脂などが挙げられる。

【0032】

このような構成であれば、犠牲層11をエッチングする際に、半導体チップ10と環状バンプ70との接触界面にエッチャントが直接触れることを防ぐことができる。エッチャントが接触界面に沿ってTSV絶縁膜27まで到達する可能性をさらに低減することができるので、半導体チップ10とベース基板50との接続の信頼性をさらに高めることができる。

【0033】

(1.5)第3の変形例

図6は、半導体装置100の第3の変形例を示す断面図である。図6に示すように、半導体装置100の製造工程では、貫通電極20のバンプ60と接続される側の面に凹部29を形成してもよい(凹部形成工程)。この凹部29は、貫通電極20を形成する際のめっき処理時間を、凹部29を有さない場合(例えば、図1(a)の場合)よりも短めに調整することで、形成することができる。また、ろう材25は、貫通電極20に凹部29を形成した後で、その凹部29の底面及び内側面を覆うように形成する。そして、実装工程では、バンプ60の先端部61を凹部29の内側まで入れて、貫通電極20とバンプ60とを接続する。このような製造方法であれば、バンプ60の潰れを抑制することができる。これにより、バンプ60が潰れて水平方向に広がり、隣り合うバンプ60同士が意図せず接触する(即ち、ショートする)可能性を低減することができる。

【0034】

(2)第2実施形態

上記の第1実施形態では、半導体チップ10の周縁部1cを環状バンプ70に埋め込んで、この環状バンプ70で囲まれた領域を封止する場合について説明した。つまり、環状バンプ70を封止材として用いる場合について説明した。しかしながら、本発明では、環状バンプ70に電極としての機能を追加してもよい。第2実施形態では、このような形態について説明する。

【0035】

(2.1)製造方法及び構成

図7(a)〜(c)は、本発明の第2実施形態に係る半導体装置200の製造方法を示す断面図である。図2(a)に示すように、まず始めに、半導体チップ110と、ベース基板50とを用意する。

半導体チップ110は、例えば、基材1と、第1の絶縁層3と、第1の絶縁層3上に形成された第1の電極5a及び第2の電極5bと、第1の電極5a及び第2の電極5bを覆うように形成された第2の絶縁層7と、第3の絶縁層9と、犠牲層11と、素子13と、を備える。第1の電極5a及び第2の電極5bの材質は、例えば、第1実施形態で説明した電極5と同じである。

【0036】

また、この半導体チップ110は、第1の貫通電極20aと、第2の貫通電極20bと、TSV絶縁膜27と、プラグ電極15と、を備える。ここで、基材1の表面1aと裏面1bとの間には、当該間を貫通する第1の貫通孔21aと第2の貫通孔21bとが設けられている。第2の貫通孔21bは、第1の貫通孔21aよりも周縁部1cに近い位置に設けられている。第1の貫通電極20aはTSV絶縁膜27を介して第1の貫通孔21a内に設けられており、第2の貫通電極20bはTSV絶縁膜27を介して第2の貫通孔21b内に設けられている。第1の貫通電極20aと第2の貫通電極20bの各構造及び各材質は、第1実施形態で説明した貫通電極20と同じである。

なお、第2の貫通電極20bに接続する第2の電極5bは、素子13に接続するための電極ではなく、例えば、グランド電極(即ち、接地電位の電極)として用いられる。

【0037】

次に、用意した半導体チップ110をベース基板50に実装する(実装工程)。ここでは、図7(a)の矢印で示すように、半導体チップ110の裏面1bの側とベース基板50の表面51aの側とを対向させる。そして、この状態で半導体チップ110をベース基板50に相対的に押圧して、半導体チップ110をベース基板50に接合する。これにより、図1(b)に示すように、貫通電極20aとバンプ60とを接続すると共に、半導体チップ110の周縁部(側面を含む)1cを環状バンプ70に埋入させる。また同時に、貫通電極20bを環状バンプ70に接続する。

【0038】

図8は、半導体チップ110をベース基板50に実装した後の、第2の貫通電極20bと環状バンプ70との位置関係の一例を示す平面図である。図8に示すように、第2の貫通電極20bの少なくとも一部は環状バンプ70と平面視で重なるように配置されている。これにより、第2の貫通電極20bと環状バンプ70とが接続される。このため、環状バンプ70を、例えば、半導体チップ110とベース基板50とに共通のグランド電極とすることができる。

【0039】

次に、ベース基板50に実装された半導体チップ110の犠牲層11をエッチングして除去する(エッチング工程)。エッチングの方法は第1実施形態と同じである。これにより、図7(c)に示すように、半導体チップ110の表面1a側に空洞部31が形成される。以上の工程を経て、半導体チップ110とベース基板50とが接続され、空洞部31の上方に素子13を有する構造の半導体装置200が完成する。

【0040】

完成後の半導体装置200は、下記の構成を有する。即ち、図7(c)に示すように、半導体装置200は、半導体チップ110とベース基板50とを備える。半導体チップ1110は、基材1の表面1aと裏面1bとの間を貫通する第1の貫通電極20aと、第1の貫通電極20aよりも周縁部1cに近い位置を貫通する第2の貫通電極20bと、を有する。また、TSV絶縁膜27は、第1の貫通電極20aと基材1との間、及び、第2の貫通電極20bと基材1との間にそれぞれ設けられている。そして、第1の貫通電極20aはバンプ60に接続され、第2の貫通電極20bは環状バンプ70に接続されている。

【0041】

(2.2)第2実施形態の効果

本発明の第2実施形態によれば、第1実施形態と同様の効果を奏する。

また、本発明の第2実施形態によれば、環状バンプ70を半導体チップ110と接続する端子として用いることができる。例えば、環状バンプ70が接地電位(グランド)に接続される場合は、この環状バンプ70を半導体チップ110とベース基板50とに共通のグランド端子として用いることができる。

【0042】

(2.3)変形例

なお、この第2実施形態においても、第1実施形態で説明した第1〜第3の変形例と同様の態様を採ることができる。即ち、図9に示すように、半導体装置200は、半導体チップ110とベース基板50との間であって、環状バンプ70で囲まれた領域内に封止樹脂81を有していてもよい。これにより、半導体チップ10とベース基板50との接続の信頼性をさらに高めることができる。

【0043】

また、図10に示すように、半導体装置200は、環状バンプ70の半導体チップ110から露出している領域71上から半導体チップ110の側面を覆う絶縁性の樹脂83を有していてもよい。これにより、犠牲層11をエッチングする際に、半導体チップ110と環状バンプ70との接触界面にエッチャントが直接触れることを防ぐことができる。エッチャントが接触界面に沿ってTSV絶縁膜27まで到達する可能性を低減することができるので、半導体チップ110とベース基板50との接続の信頼性をさらに高めることができる。

【0044】

さらに、図11に示すように、半導体装置200を製造する過程では、第1の貫通電極20aのバンプ60と接続される側の面、及び、第2の貫通電極20bの環状バンプ70と接続される側の面にそれぞれ凹部29を形成してもよい(凹部形成工程)。これらの凹部29は、第1の貫通電極20a及び第2の貫通電極20bを同時に形成する際のめっき処理時間を、凹部を有さない場合(例えば、図7(a)の場合)よりも短めに調整することで、形成することができる。このような製造方法であれば、バンプ60の潰れを抑制することができる。これにより、バンプ60が潰れて水平方向に広がり、隣り合うバンプ60同士が意図せず接触する可能性を低減することができる。

【0045】

(3)電子機器、その他

本発明の実施形態に係る電子機器は、上記の半導体装置100(又は、半導体装置200)を含んだものである。この電子機器が備える半導体装置は、素子の下方に位置する空洞部が破壊されておらず、且つ、半導体チップとベース基板とが信頼性高く接続されている。従って、信頼性の高い電子機器を提供することができる。

【0046】

なお、上記の各実施形態に係る半導体装置の製造方法及び半導体装置、並びに、電子機器は、例えば、赤外線を受光することにより人体の存在を検出する人感センサーや、人体の温度分布などを検出する温度センサー等を一例とする各種機器と、その製造方法に適用することができる。また、本発明は、いわゆるMEMS(Micro Electro Mechanical Systems)プロセスを利用した半導体装置の製造方法と、この製造方法により形成される半導体装置にも適用することができる。

【符号の説明】

【0047】

1 (半導体チップの)基材、1a、51a 表面、1b 裏面、1c 周縁部(側面を含む)、3 第1の絶縁層、5 電極、5a 第1の電極、5b 第2の電極、7 第2の絶縁層、9 第3の絶縁層、10、110 半導体チップ、11 犠牲層、13 素子、15 プラグ電極、20、20a、20b 貫通電極、21 貫通孔、23 シード層、24 電極本体、25 ろう材、27 TSV絶縁膜、29 凹部、31 空洞部、50 ベース基板、51 (ベース基板の)基材、51a 表面、53 絶縁層、55 第1の電極、57 第2の電極、59 パシベーション膜、60 バンプ、61 先端部、70 環状バンプ、71 (環状バンプの半導体チップ11から露出している)領域、81 封止樹脂、83 樹脂、100、200 半導体装置

【技術分野】

【0001】

本発明は、半導体装置の製造方法及び半導体装置、電子機器に関する。

【背景技術】

【0002】

従来技術として、例えば、特許文献1〜3に開示されたものがある。即ち、特許文献1には、犠牲層を除去することにより形成された空洞部の上方で支持部により支えられた構造の焦電型検出素子が開示されている。また、特許文献2には、シリコンの第1の面(集積回路形成面)と第2の面(裏面)との間を貫く貫通電極が開示されている。そして、特許文献3には、電子回路素子を基板に実装する際に、電子回路素子が有する外周封止用電極を、基板が有する封止用電極に接合することによって、外周封止用電極の内側に配置されているチップ電極を封止する技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011−153851号公報

【特許文献2】特開2010−177237号公報

【特許文献3】特開2004−214469号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、特許文献1に開示されたような、空洞部の上方で支えられた構造の焦電型検出素子を他の基板に実装する場合、この焦電型素子に実装時の荷重が加えられると、その荷重によって空洞部が破壊されてしまう可能性がある。このような空洞部の破壊を防ぐ方法として、空洞部が形成される前に焦電型素子を基板に実装しておき、実装後に空洞部を形成する方法が考えられる。また、上記の実装に際しては、特許文献3に開示されているように、外周封止用電極と封止用電極とを接続することにより、それらの内側に位置するチップ電極を気密封止する方法が考えられる。

【0005】

ここで、上記の焦電型検出素子が、特許文献2に開示されたような貫通電極を有する場合は、特許文献2の図3に記載されている下地層141(例えばシリコン酸化物(SiO2)やシリコン窒化物(Si3N4)等の絶縁性材料からなる)は外周封止用電極の外側に露出した構造となる。このため、犠牲層をエッチングして空洞部を形成する際に、この下地層もエッチングされてしまう可能性があった。下地層がエッチングされると、外周封止用電極と半導体基板との間に隙間が生じてエッチャント等が侵入する。その結果、上記の気密封止が破られて、焦電型素子と基板との接続の信頼性が低下してしまう可能性があった。

そこで、この発明はこのような事情に鑑みてなされたものであって、空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供することを目的の一つとする。

【課題を解決するための手段】

【0006】

上記課題を解決するために、本発明の一態様に係る半導体装置の製造方法は、少なくとも一方が半導体素子を含む第1の基板及び第2の基板を互いに接続して半導体装置を製造する方法であって、前記第1の基板は、第1の面及び該第1の面の反対側の第2の面を有する第1の基材と、前記第1の基材の第1の面側に設けられた犠牲層と、前記第1の基材の前記第1の面と前記第2の面との間を貫通する貫通電極と、前記貫通電極と前記第1の基材との間に設けられた絶縁膜と、を有し、前記第2の基板は、第3の面を有する第2の基材と、前記第2の基材の前記第3の面側に設けられたバンプと、前記第2の基材の前記第3の面側に設けられ、前記バンプを囲む環状導電部と、を有し、前記第2の面と前記第3の面とを対向させた状態で、前記貫通電極と前記バンプとを接続すると共に、前記第1の基板の周縁部を前記環状導電部に埋入させる実装工程と、前記実装工程の後で、前記犠牲層をエッチングして前記第1の基材の前記第1の面側に空洞部を形成するエッチング工程と、を含むことを特徴とする。

このような製造方法であれば、エッチング工程の前に実装工程を行う。実装工程では空洞部は未形成であり、第1の基板に付加される荷重で空洞部が壊れることはない。このため、上記の空洞部を壊すことなく、第1の基板を第2の基板に実装することができる。

【0007】

また、この実装工程では、第1の基板の周縁部を環状導電部に埋入することにより、絶縁膜を環状導電部で囲まれた領域内に封止する。絶縁膜が環状導電部の外側に露出しないようにすることができるので、エッチング工程で絶縁膜がエッチングされることを防ぐことができ、第1の基板と第2の基板との間に隙間が生じることを防ぐことができる。従って、この隙間を通って半導体装置内に水分等が侵入することを防ぐことができ、貫通電極等の腐食を防ぐことができる。これにより、第1の基板と第2の基板との接続の信頼性を高めることができる。

【0008】

なお、本発明の「第1の基板」としては、例えば、後述する半導体チップ10、又は、半導体チップ110が該当する。「第2の基板」としては、例えば、後述するベース基板50が該当する。「第1の基材」としては例えば後述する基材1が該当し、「第1の面」としては例えば後述する表面1aが該当し、「第2の面」としては例えば後述する裏面1bが該当する。また、「第2の基材」としては例えば後述する基材51が該当し、「第3の面」としては例えば後述する表面51aが該当する。さらに、「絶縁膜」としては、例えば、後述するTSV絶縁膜27が該当する。「環状導電部」としては、例えば、後述する環状バンプ70が該当する。

【0009】

また、上記の半導体装置の製造方法において、前記実装工程の前に、前記貫通電極の前記バンプと接続される側の面に凹部を形成する凹部形成工程、をさらに含み、前記実装工程では、前記凹部の内側に前記バンプの先端部を入れた状態で前記貫通電極と前記バンプとを接続することを特徴としてもよい。このような製造方法であれば、実装工程でのバンプの潰れを抑制することができる。これにより、バンプが潰れて水平方向に広がり、隣り合うバンプ同士が意図せず接触する(即ち、ショートする)可能性を低減することができる。

【0010】

本発明の別の態様に係る半導体装置は、少なくとも一方が半導体素子を含む第1の基板及び第2の基板が互いに接続された半導体装置であって、前記第1の基板は、第1の面及び該第1の面の反対側の第2の面を有し、前記第1の面側に空洞部が設けられた第1の基材と、前記第1の基材の前記第1の面と前記第2の面との間を貫通する貫通電極と、前記貫通電極と前記第1の基材との間に設けられた絶縁膜と、を有し、前記第2の基板は、前記第2の面と対向する第3の面を有する第2の基材と、前記第2の基材の前記第3の面側に設けられ、前記貫通電極に接続されたバンプと、前記第2の基材の前記第3の面側に設けられ、前記バンプを囲む環状導電部と、を有し、前記第1の基板の周縁部が前記環状導電部に埋入していることを特徴とする。このような構成であれば、上記の製造方法により半導体装置を製造することができる。従って、空洞部が破壊されておらず、且つ、第1の基板と第2の基板とが信頼性高く接続された半導体装置を提供することができる。

【0011】

また、上記の半導体装置において、前記第1の基板は、前記第1の基材の前記第1の面と前記第2の面との間であって、前記貫通電極よりも前記周縁部に近い位置を貫通する第2の貫通電極、をさらに有し、前記第2の貫通電極と前記第1の基材との間に絶縁膜が設けられており、前記第2の貫通電極と前記環状導電部とが接続されていることを特徴としてもよい。このような構成であれば、第2の基板の環状導電部を第1の基板と接続する端子として用いることができる。例えば、環状導電部が接地電位(グランド)に接続される場合は、この環状導電部を半導体素子と第2の基板とに共通のグランド端子として用いることができる。

【0012】

また、上記の半導体装置において、前記第1の基板の前記第2の面と前記第2の基板の前記第3の面との間であって、前記環状導電部で囲まれる領域に設けられた樹脂、をさらに有することを特徴としてもよい。このような構成であれば、第1の基板と第2の基板とに樹脂を密着させることができる。樹脂と第1の基板との間に働く接着力と、樹脂と第2の基板との間に働く接着力とにより、第1の基板と第2の基板との接続強度をさらに高めることができる。これにより、第1の基板と第2の基板との接続の信頼性をさらに高めることができる。なお、本発明の「樹脂」としては、例えば、後述する封止樹脂81が該当する。

本発明のさらに別の態様に係る電子機器は、上記の半導体装置を備えることを特徴とする。このような構成であれば、空洞部が破壊されておらず、且つ、第1の基板と第2の基板とが信頼性高く接続された半導体装置を備えた電子機器を提供することができる。

【図面の簡単な説明】

【0013】

【図1】第1実施形態に係る半導体装置100の製造方法を示す図。

【図2】バンプ60及び環状バンプ70の形状等の一例を示す図。

【図3】半導体チップ10と環状バンプ70との位置関係の一例を示す図。

【図4】半導体装置100の第1変形例を示す図。

【図5】半導体装置100の第2変形例を示す図。

【図6】半導体装置100の第3変形例を示す図。

【図7】第2実施形態に係る半導体装置200の製造方法を示す図。

【図8】第2の貫通電極20bと環状バンプ70との位置関係の一例を示す図。

【図9】半導体装置200の第1変形例を示す図。

【図10】半導体装置200の第2変形例を示す図。

【図11】半導体装置200の第3変形例を示す図。

【発明を実施するための形態】

【0014】

以下、本発明の実施の形態について図面を参照しながら説明する。なお、以下に説明する各図において、同一の構成を有する部分には同一の符号を付し、その重複する説明は省略する。

(1)第1実施形態

(1.1)製造方法及び構成

図1(a)〜(c)は、本発明の第1実施形態に係る半導体装置100の製造方法を示す断面図である。図1(a)に示すように、まず始めに、半導体チップ10と、ベース基板50とを用意する。

【0015】

半導体チップ10は、例えばシリコン等からなる基材1と、この基材1の表面1aの側に形成された第1の絶縁層3と、第1の絶縁層3上に形成された電極5と、電極5を覆うように形成された第2の絶縁層7と、第2の絶縁層7上に形成された第3の絶縁層9と、第3の絶縁層9に埋め込まれた犠牲層11と、この犠牲層11の一部を覆うように第3の絶縁層9上に設けられた素子13と、素子13と電極5とを接続するプラグ電極15と、を備える。第1の絶縁層3、第2の絶縁層7、第3の絶縁層9は、例えばシリコン酸化膜(SiO2)又はシリコン窒化膜(Si3N4)からなる。電極5は、例えば、窒化チタン(TiN)からなる。犠牲層11は、例えばシリコン酸化膜からなる。素子13は、例えば赤外線を検出可能な焦電センサーである。プラグ電極15は、例えばタングステン(W)からなる。

【0016】

なお、図示しないが、第3の絶縁層9の表面と、第2の絶縁層7と犠牲層11との間、及び、第3の絶縁層9と犠牲層11との間には、エッチング防止膜が設けられていてもよい。また、第1の絶縁層3と、第2の絶縁層7及び、第3の絶縁層9の側面にもエッチング防止膜が設けられていてもよい。このエッチング防止膜は、後述の空洞部を形成するために犠牲層11をエッチングする工程において、第2の絶縁層7と第3の絶縁層9がエッチングされることを防止するための膜である。エッチング防止膜としては、例えば、シリコン酸化膜からなる犠牲層11をエッチングするときに用いられるフッ化水素(HF)に対して、耐食性のある材質(例えば、シリコン窒化膜、アルミニウム、タングステン等)の膜である。

【0017】

また、この半導体チップ10は、貫通電極(TSV:Through Si Via)20と、この貫通電極20と基材1との間に設けられたTSV絶縁膜27と、を備える。図1(a)に示すように、基材1には、その表面1aと裏面1bとの間を貫通する貫通孔21が設けられている。貫通電極20は、この貫通孔21内にTSV絶縁膜27を介して設けられている。即ち、TSV絶縁膜27は、貫通孔21の内側面から基材1の裏面1bにかけて設けられている。TSV絶縁膜27は、例えばシリコン酸化膜である。

【0018】

貫通電極20は、例えば、スパッタリングで形成されたシード層23と、電解めっき法で形成された電極本体24と、電極本体24のベース基板50と接続される側の面(例えば、下面)に設けられたろう材25と、を有する。シード層23及び電極本体24は例えば銅(Cu)であり、ろう材25は例えばスズと銀との合金(Sn−Ag)である。このような構成の貫通電極20は、第1の絶縁層3を貫いて電極5に接続されている。

【0019】

一方、ベース基板50は、例えばシリコン等からなる基材51と、この基材51の表面51aの側に形成された絶縁層53と、この絶縁層53上に形成された第1の電極55及び第2の電極57と、これら第1の電極55及び第2の電極57を覆うように絶縁層53上に形成されたパシベーション膜59と、このパシベーション膜59上に形成されたバンプ60及び環状バンプ70と、を備える。図1(a)に示すように、パシベーション膜59には、第1の電極55又は第2の電極57を底面とする開口部が設けられている。この開口部を介して、バンプ60は電極55に接続され、環状バンプ70は電極57に接続されている。

【0020】

図2は、バンプ60及び環状バンプ70の各形状と、これらの位置関係の一例を示す平面図である。図2に示すように、バンプ60の平面視による形状(以下、平面形状)は例えば円形である。また、環状バンプ70の平面形状は例えば矩形枠である。環状バンプ70はバンプ60を平面視で囲むように配置されている(即ち、バンプ60は環状バンプ70で囲まれた領域に配置されている。)。

【0021】

図1(a)に戻って、絶縁層53は、例えばシリコン酸化膜からなる。第1の電極55と第2の電極57は、例えばアルミニウム(Al)からなる。バンプ60及び環状バンプ70は、例えば金(Au)からなる。パシベーション膜59は、例えばポリイミドからなる。また、図1(a)において、バンプ60及び環状バンプ70のパシベーション膜59からの高さをhとしたとき、hは例えば10〜25μmである。なお、図示しないが、第1の電極55とバンプ60との間、及び第2の電極57と環状バンプ70との間には、それぞれ、チタン(Ti)、タングステン(W)、プラチナ(Pt)、銅(Cu)又はクロム(Cr)等の中間層が設けられていてもよい。

【0022】

次に、用意した半導体チップ10とベース基板50とを重ね合わせて接合する。即ち、半導体チップ10をベース基板50に実装する(実装工程)。ここでは、図1(a)の矢印で示すように、半導体チップ10の裏面1bの側とベース基板50の表面51aの側とを対向させる。そして、この状態で半導体チップ10をベース基板50に相対的に押圧して、半導体チップ10をベース基板50に接合する。

【0023】

これにより、図1(b)に示すように、貫通電極20とバンプ60とを接続すると共に、半導体チップ10の周縁部(側面を含む)1cを環状バンプ70に埋入させる。なお、この実装工程では、バンプ60は貫通電極20と接合することにより押し潰される。押し潰された後のバンプ60のパシベーション膜59からの高さをh´としたとき、h>h´である。h´は例えば5〜15μmである。

図3は、半導体チップ10をベース基板50に実装した後の、半導体チップ10と環状バンプ70との位置関係の一例を示す平面図である。図3に示すように、犠牲層11のエッチング工程では、半導体チップ10の周縁部1cは全周に亘って環状バンプ70に埋設されている。

【0024】

次に、実装工程の後で、犠牲層11をエッチングして除去する(エッチング工程)。このエッチング工程では、図1(b)及び図3に示したように、犠牲層11の一部が素子13の下から露出している。このため、半導体チップ10をベース基板50と共に、HF溶液に浸漬する(又は、HFべ―パー雰囲気に晒す)ことによって、シリコン酸化膜からなる犠牲層11をエッチングして除去することができる。これにより、図1(c)に示すように、半導体チップ10に空洞部31が形成される。以上の工程を経て、半導体チップ10とベース基板50とが接続され、空洞部31の上方に素子13を有する構造の半導体装置100が完成する。

【0025】

完成後の半導体装置100は、下記の構成を有する。即ち、図1(c)に示すように、半導体装置100は、半導体チップ10とベース基板50とを備える。半導体チップ10は、表面1a側に空洞部31が設けられた基材1と、この基材1の表面1aと裏面1bとの間を貫通する貫通電極20と、貫通電極20と基材1との間に設けられたTSV絶縁膜27と、を有する。ベース基板50は、基材51と、この基材51の表面51a側に設けられたバンプ60と、表面51側に設けられ、バンプ60を囲む環状バンプ70と、を有する。そして、半導体チップ10の裏面1bとベース基板50の表面51aとが対向した状態で、貫通電極20とバンプ60とが接続されると共に、半導体チップ10の周縁部1cが環状バンプ70に埋入している。ここで、「半導体チップ10の周縁部1cが環状バンプ70に埋入している」とは、半導体チップ10の表面1a及び裏面1bを接続する側面と裏面1bとで形成される角部とが、環状バンプ70に覆われている状態のことである。

【0026】

なお、図示しないが、ベース基板50には、第1の電極55又は第2の電極57等の配線の他に、例えば、半導体チップ10を制御する制御回路等が形成されていてもよい。この図示しない制御回路は、実装工程の前に、CMOSプロセスでベース基板50に形成することが可能である。このように、制御回路がベース基板50に形成されている場合は、例えば、この制御回路と素子13との間で貫通電極20(第2実施形態では、第1の貫通電極20a)を経由して、信号の送受が行われる。

【0027】

(1.2)第1実施形態の効果

本発明の第1実施形態によれば、エッチング工程の前に実装工程を行う。実装工程では空洞部31は未形成であり、半導体チップ10に付加される荷重で空洞部31が壊れることはない。このため、素子13の下方に形成される空洞部31を壊すことなく、半導体チップ10をベース基板50に実装することができる。

【0028】

また、この実装工程では、半導体チップ10の周縁部1cを環状バンプ70に埋入させる。これにより、TSV絶縁膜27を環状バンプ70で囲まれた領域内に封止する。TSV絶縁膜27が環状バンプ70の外側に露出しないようにすることができるので、エッチング工程でTSV絶縁膜27がエッチングされることを防ぐことができ、半導体チップ10とベース基板50との間に隙間が生じることを防ぐことができる。この隙間を通って半導体装置内に水分等が侵入することを防ぐことができるため、貫通電極20等の腐食を防ぐことができる。従って、半導体チップ10とベース基板50との接続の信頼性を高めることができる。次に、第1実施形態の変形例を示す。

【0029】

(1.3)第1変形例

図4は、半導体装置100の第1変形例を示す断面図である。図4に示すように、半導体装置100は、半導体チップ10とベース基板50との間であって、環状バンプ70で囲まれた領域内に封止樹脂81を有していてもよい。封止樹脂81としては、例えば、熱硬化性のエポキシ系樹脂、ポリイミド系樹脂、アクリル系樹脂などが挙げられる。このような構成であれば、半導体チップ10とベース基板50とに封止樹脂81を密着させることができる。封止樹脂81と半導体チップ10との間に働く接着力と、封止樹脂81とベース基板50との間に働く接着力とにより、半導体チップ10とベース基板50との接続強度をさらに高めることができる。これにより、半導体チップ10とベース基板50との接続の信頼性をさらに高めることができる。

【0030】

なお、上記の封止樹脂81は、例えば実装工程の前に、ベース基板50の環状バンプ70で囲まれた領域に塗布する。そして、封止樹脂81を塗布した後で半導体チップ10をベース基板50に実装する。これにより、半導体チップ10とベース基板50との間であって、環状バンプ70で囲まれた領域に封止樹脂81を封入することができる。この封止樹脂81が熱硬化性の場合は、例えば、実装時の熱で封止樹脂81を硬化させることができる。

【0031】

(1.4)第2の変形例

図5は、半導体装置100の第2変形例を示す断面図である。図5に示すように、半導体装置100は、環状バンプ70の半導体チップ10から露出している領域71上に、半導体チップ10の側面を覆う絶縁性の樹脂83を有していてもよい。この樹脂83は、例えば、図1(b)の段階で上記の領域71上に塗布しておく。即ち、半導体チップ10の周縁部1cを環状バンプ70に埋設した後で樹脂83を塗布しておく。そして、樹脂83を塗布した後で、犠牲層11をエッチングする。樹脂83としては、例えば、熱硬化性又は紫外線硬化性のエポキシ系樹脂、ポリイミド系樹脂、アクリル系樹脂などが挙げられる。

【0032】

このような構成であれば、犠牲層11をエッチングする際に、半導体チップ10と環状バンプ70との接触界面にエッチャントが直接触れることを防ぐことができる。エッチャントが接触界面に沿ってTSV絶縁膜27まで到達する可能性をさらに低減することができるので、半導体チップ10とベース基板50との接続の信頼性をさらに高めることができる。

【0033】

(1.5)第3の変形例

図6は、半導体装置100の第3の変形例を示す断面図である。図6に示すように、半導体装置100の製造工程では、貫通電極20のバンプ60と接続される側の面に凹部29を形成してもよい(凹部形成工程)。この凹部29は、貫通電極20を形成する際のめっき処理時間を、凹部29を有さない場合(例えば、図1(a)の場合)よりも短めに調整することで、形成することができる。また、ろう材25は、貫通電極20に凹部29を形成した後で、その凹部29の底面及び内側面を覆うように形成する。そして、実装工程では、バンプ60の先端部61を凹部29の内側まで入れて、貫通電極20とバンプ60とを接続する。このような製造方法であれば、バンプ60の潰れを抑制することができる。これにより、バンプ60が潰れて水平方向に広がり、隣り合うバンプ60同士が意図せず接触する(即ち、ショートする)可能性を低減することができる。

【0034】

(2)第2実施形態

上記の第1実施形態では、半導体チップ10の周縁部1cを環状バンプ70に埋め込んで、この環状バンプ70で囲まれた領域を封止する場合について説明した。つまり、環状バンプ70を封止材として用いる場合について説明した。しかしながら、本発明では、環状バンプ70に電極としての機能を追加してもよい。第2実施形態では、このような形態について説明する。

【0035】

(2.1)製造方法及び構成

図7(a)〜(c)は、本発明の第2実施形態に係る半導体装置200の製造方法を示す断面図である。図2(a)に示すように、まず始めに、半導体チップ110と、ベース基板50とを用意する。

半導体チップ110は、例えば、基材1と、第1の絶縁層3と、第1の絶縁層3上に形成された第1の電極5a及び第2の電極5bと、第1の電極5a及び第2の電極5bを覆うように形成された第2の絶縁層7と、第3の絶縁層9と、犠牲層11と、素子13と、を備える。第1の電極5a及び第2の電極5bの材質は、例えば、第1実施形態で説明した電極5と同じである。

【0036】

また、この半導体チップ110は、第1の貫通電極20aと、第2の貫通電極20bと、TSV絶縁膜27と、プラグ電極15と、を備える。ここで、基材1の表面1aと裏面1bとの間には、当該間を貫通する第1の貫通孔21aと第2の貫通孔21bとが設けられている。第2の貫通孔21bは、第1の貫通孔21aよりも周縁部1cに近い位置に設けられている。第1の貫通電極20aはTSV絶縁膜27を介して第1の貫通孔21a内に設けられており、第2の貫通電極20bはTSV絶縁膜27を介して第2の貫通孔21b内に設けられている。第1の貫通電極20aと第2の貫通電極20bの各構造及び各材質は、第1実施形態で説明した貫通電極20と同じである。

なお、第2の貫通電極20bに接続する第2の電極5bは、素子13に接続するための電極ではなく、例えば、グランド電極(即ち、接地電位の電極)として用いられる。

【0037】

次に、用意した半導体チップ110をベース基板50に実装する(実装工程)。ここでは、図7(a)の矢印で示すように、半導体チップ110の裏面1bの側とベース基板50の表面51aの側とを対向させる。そして、この状態で半導体チップ110をベース基板50に相対的に押圧して、半導体チップ110をベース基板50に接合する。これにより、図1(b)に示すように、貫通電極20aとバンプ60とを接続すると共に、半導体チップ110の周縁部(側面を含む)1cを環状バンプ70に埋入させる。また同時に、貫通電極20bを環状バンプ70に接続する。

【0038】

図8は、半導体チップ110をベース基板50に実装した後の、第2の貫通電極20bと環状バンプ70との位置関係の一例を示す平面図である。図8に示すように、第2の貫通電極20bの少なくとも一部は環状バンプ70と平面視で重なるように配置されている。これにより、第2の貫通電極20bと環状バンプ70とが接続される。このため、環状バンプ70を、例えば、半導体チップ110とベース基板50とに共通のグランド電極とすることができる。

【0039】

次に、ベース基板50に実装された半導体チップ110の犠牲層11をエッチングして除去する(エッチング工程)。エッチングの方法は第1実施形態と同じである。これにより、図7(c)に示すように、半導体チップ110の表面1a側に空洞部31が形成される。以上の工程を経て、半導体チップ110とベース基板50とが接続され、空洞部31の上方に素子13を有する構造の半導体装置200が完成する。

【0040】

完成後の半導体装置200は、下記の構成を有する。即ち、図7(c)に示すように、半導体装置200は、半導体チップ110とベース基板50とを備える。半導体チップ1110は、基材1の表面1aと裏面1bとの間を貫通する第1の貫通電極20aと、第1の貫通電極20aよりも周縁部1cに近い位置を貫通する第2の貫通電極20bと、を有する。また、TSV絶縁膜27は、第1の貫通電極20aと基材1との間、及び、第2の貫通電極20bと基材1との間にそれぞれ設けられている。そして、第1の貫通電極20aはバンプ60に接続され、第2の貫通電極20bは環状バンプ70に接続されている。

【0041】

(2.2)第2実施形態の効果

本発明の第2実施形態によれば、第1実施形態と同様の効果を奏する。

また、本発明の第2実施形態によれば、環状バンプ70を半導体チップ110と接続する端子として用いることができる。例えば、環状バンプ70が接地電位(グランド)に接続される場合は、この環状バンプ70を半導体チップ110とベース基板50とに共通のグランド端子として用いることができる。

【0042】

(2.3)変形例

なお、この第2実施形態においても、第1実施形態で説明した第1〜第3の変形例と同様の態様を採ることができる。即ち、図9に示すように、半導体装置200は、半導体チップ110とベース基板50との間であって、環状バンプ70で囲まれた領域内に封止樹脂81を有していてもよい。これにより、半導体チップ10とベース基板50との接続の信頼性をさらに高めることができる。

【0043】

また、図10に示すように、半導体装置200は、環状バンプ70の半導体チップ110から露出している領域71上から半導体チップ110の側面を覆う絶縁性の樹脂83を有していてもよい。これにより、犠牲層11をエッチングする際に、半導体チップ110と環状バンプ70との接触界面にエッチャントが直接触れることを防ぐことができる。エッチャントが接触界面に沿ってTSV絶縁膜27まで到達する可能性を低減することができるので、半導体チップ110とベース基板50との接続の信頼性をさらに高めることができる。

【0044】

さらに、図11に示すように、半導体装置200を製造する過程では、第1の貫通電極20aのバンプ60と接続される側の面、及び、第2の貫通電極20bの環状バンプ70と接続される側の面にそれぞれ凹部29を形成してもよい(凹部形成工程)。これらの凹部29は、第1の貫通電極20a及び第2の貫通電極20bを同時に形成する際のめっき処理時間を、凹部を有さない場合(例えば、図7(a)の場合)よりも短めに調整することで、形成することができる。このような製造方法であれば、バンプ60の潰れを抑制することができる。これにより、バンプ60が潰れて水平方向に広がり、隣り合うバンプ60同士が意図せず接触する可能性を低減することができる。

【0045】

(3)電子機器、その他

本発明の実施形態に係る電子機器は、上記の半導体装置100(又は、半導体装置200)を含んだものである。この電子機器が備える半導体装置は、素子の下方に位置する空洞部が破壊されておらず、且つ、半導体チップとベース基板とが信頼性高く接続されている。従って、信頼性の高い電子機器を提供することができる。

【0046】

なお、上記の各実施形態に係る半導体装置の製造方法及び半導体装置、並びに、電子機器は、例えば、赤外線を受光することにより人体の存在を検出する人感センサーや、人体の温度分布などを検出する温度センサー等を一例とする各種機器と、その製造方法に適用することができる。また、本発明は、いわゆるMEMS(Micro Electro Mechanical Systems)プロセスを利用した半導体装置の製造方法と、この製造方法により形成される半導体装置にも適用することができる。

【符号の説明】

【0047】

1 (半導体チップの)基材、1a、51a 表面、1b 裏面、1c 周縁部(側面を含む)、3 第1の絶縁層、5 電極、5a 第1の電極、5b 第2の電極、7 第2の絶縁層、9 第3の絶縁層、10、110 半導体チップ、11 犠牲層、13 素子、15 プラグ電極、20、20a、20b 貫通電極、21 貫通孔、23 シード層、24 電極本体、25 ろう材、27 TSV絶縁膜、29 凹部、31 空洞部、50 ベース基板、51 (ベース基板の)基材、51a 表面、53 絶縁層、55 第1の電極、57 第2の電極、59 パシベーション膜、60 バンプ、61 先端部、70 環状バンプ、71 (環状バンプの半導体チップ11から露出している)領域、81 封止樹脂、83 樹脂、100、200 半導体装置

【特許請求の範囲】

【請求項1】

少なくとも一方が半導体素子を含む第1の基板及び第2の基板を互いに接続して半導体装置を製造する方法であって、

前記第1の基板は、

第1の面及び該第1の面の反対側の第2の面を有する第1の基材と、

前記第1の基材の第1の面側に設けられた犠牲層と、

前記第1の基材の前記第1の面と前記第2の面との間を貫通する貫通電極と、

前記貫通電極と前記第1の基材との間に設けられた絶縁膜と、を有し、

前記第2の基板は、

第3の面を有する第2の基材と、

前記第2の基材の前記第3の面側に設けられたバンプと、

前記第2の基材の前記第3の面側に設けられ、前記バンプを囲む環状導電部と、を有し、

前記第2の面と前記第3の面とを対向させた状態で、前記貫通電極と前記バンプとを接続すると共に、前記第1の基板の周縁部を前記環状導電部に埋入させる実装工程と、

前記実装工程の後で、前記犠牲層をエッチングして前記第1の基材の前記第1の面側に空洞部を形成するエッチング工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記実装工程の前に、前記貫通電極の前記バンプと接続される側の面に凹部を形成する凹部形成工程、をさらに含み、

前記実装工程では、前記凹部の内側に前記バンプの先端部を入れた状態で前記貫通電極と前記バンプとを接続することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

少なくとも一方が半導体素子を含む第1の基板及び第2の基板が互いに接続された半導体装置であって、

前記第1の基板は、

第1の面及び該第1の面の反対側の第2の面を有し、前記第1の面側に空洞部が設けられた第1の基材と、

前記第1の基材の前記第1の面と前記第2の面との間を貫通する貫通電極と、

前記貫通電極と前記第1の基材との間に設けられた絶縁膜と、を有し、

前記第2の基板は、

前記第2の面と対向する第3の面を有する第2の基材と、

前記第2の基材の前記第3の面側に設けられ、前記貫通電極に接続されたバンプと、

前記第2の基材の前記第3の面側に設けられ、前記バンプを囲む環状導電部と、を有し、

前記第1の基板の周縁部が前記環状導電部に埋入していることを特徴とする半導体装置。

【請求項4】

前記第1の基板は、

前記第1の基材の前記第1の面と前記第2の面との間であって、前記貫通電極よりも前記周縁部に近い位置を貫通する第2の貫通電極、をさらに有し、

前記第2の貫通電極と前記第1の基材との間に絶縁膜が設けられており、

前記第2の貫通電極と前記環状導電部とが接続されていることを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記第1の基板の前記第2の面と前記第2の基板の前記第3の面との間であって、前記環状導電部で囲まれる領域に設けられた樹脂、をさらに有することを特徴とする請求項3又は請求項4に記載の半導体装置。

【請求項6】

請求項3から請求項5の何れか一項に記載の半導体装置を備えることを特徴とする電子機器。

【請求項1】

少なくとも一方が半導体素子を含む第1の基板及び第2の基板を互いに接続して半導体装置を製造する方法であって、

前記第1の基板は、

第1の面及び該第1の面の反対側の第2の面を有する第1の基材と、

前記第1の基材の第1の面側に設けられた犠牲層と、

前記第1の基材の前記第1の面と前記第2の面との間を貫通する貫通電極と、

前記貫通電極と前記第1の基材との間に設けられた絶縁膜と、を有し、

前記第2の基板は、

第3の面を有する第2の基材と、

前記第2の基材の前記第3の面側に設けられたバンプと、

前記第2の基材の前記第3の面側に設けられ、前記バンプを囲む環状導電部と、を有し、

前記第2の面と前記第3の面とを対向させた状態で、前記貫通電極と前記バンプとを接続すると共に、前記第1の基板の周縁部を前記環状導電部に埋入させる実装工程と、

前記実装工程の後で、前記犠牲層をエッチングして前記第1の基材の前記第1の面側に空洞部を形成するエッチング工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記実装工程の前に、前記貫通電極の前記バンプと接続される側の面に凹部を形成する凹部形成工程、をさらに含み、

前記実装工程では、前記凹部の内側に前記バンプの先端部を入れた状態で前記貫通電極と前記バンプとを接続することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

少なくとも一方が半導体素子を含む第1の基板及び第2の基板が互いに接続された半導体装置であって、

前記第1の基板は、

第1の面及び該第1の面の反対側の第2の面を有し、前記第1の面側に空洞部が設けられた第1の基材と、

前記第1の基材の前記第1の面と前記第2の面との間を貫通する貫通電極と、

前記貫通電極と前記第1の基材との間に設けられた絶縁膜と、を有し、

前記第2の基板は、

前記第2の面と対向する第3の面を有する第2の基材と、

前記第2の基材の前記第3の面側に設けられ、前記貫通電極に接続されたバンプと、

前記第2の基材の前記第3の面側に設けられ、前記バンプを囲む環状導電部と、を有し、

前記第1の基板の周縁部が前記環状導電部に埋入していることを特徴とする半導体装置。

【請求項4】

前記第1の基板は、

前記第1の基材の前記第1の面と前記第2の面との間であって、前記貫通電極よりも前記周縁部に近い位置を貫通する第2の貫通電極、をさらに有し、

前記第2の貫通電極と前記第1の基材との間に絶縁膜が設けられており、

前記第2の貫通電極と前記環状導電部とが接続されていることを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記第1の基板の前記第2の面と前記第2の基板の前記第3の面との間であって、前記環状導電部で囲まれる領域に設けられた樹脂、をさらに有することを特徴とする請求項3又は請求項4に記載の半導体装置。

【請求項6】

請求項3から請求項5の何れか一項に記載の半導体装置を備えることを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−98514(P2013−98514A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−243132(P2011−243132)

【出願日】平成23年11月7日(2011.11.7)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年11月7日(2011.11.7)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]