半導体装置の製造方法及び半導体装置

【課題】 ミスフィット転位の発生を抑制しつつ、量子ドットからの発光波長を長波長化することができる半導体装置の製造技術が望まれている。

【解決手段】 チャンバ内に単結晶基板を装填し、単結晶基板上に、分子線エピタキシにより、In及びAsを含む量子ドットを形成する。チャンバ内で、量子ドットに、少なくともAs2分子線を照射しながら第1アニールを行う。

【解決手段】 チャンバ内に単結晶基板を装填し、単結晶基板上に、分子線エピタキシにより、In及びAsを含む量子ドットを形成する。チャンバ内で、量子ドットに、少なくともAs2分子線を照射しながら第1アニールを行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、量子ドットを含む半導体装置の製造方法及び半導体装置に関する。

【背景技術】

【0002】

化合物半導体基板上に、格子整合しない化合物半導体をヘテロエピタキシャル成長させると、成長初期にS−K(ストランスキ・クラスタノフ)モード成長が出現する。S−Kモード成長を利用することにより、下地表面に離散的に分布する微細な結晶(量子ドット)を形成することができる。例えば、GaAs基板上に、InAs組成が50%程度のInGaAsを数分子層、分子線エピタキシ(MBE)により成長させると、直径30〜40nm程度のInGaAsの量子ドットが形成される。

【0003】

S−Kモード成長を利用することにより、リソグラフィ等による加工プロセスを用いた場合に比べて、簡便に量子ドットを形成することができる。さらに、S−Kモード成長を利用する場合には、加工プロセスを実行する必要がないため、加工時に導入され得る欠陥等のない高品質な量子ドットを得ることができる。

【0004】

GaAs基板上に、通常のMBEによりInAs量子ドットを形成した光素子の発光波長は、1.1〜1.2μm程度である。波長1.3μm帯の通信用の光素子に、量子ドット素子を適用する場合には、発光波長を長波長化しなければならない。InAs量子ドットを、InAs組成が20%程度で厚さが数nmのInGaAs層(歪緩和層)で覆うことにより、発光波長を長波長化できることが知られている。

【0005】

InAs量子ドットを形成した後、アンチモン照射等を行うことにより、巨大ドット構造等の結晶欠陥の発生を抑制し、量子ドットの結晶性を向上させる技術が知られている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−176821号公報

【非特許文献】

【0007】

【非特許文献1】D. Leonard et al.: Appl. Phys. Lett., Vol. 63, No. 23, pp. 3203-3205 (1993)

【非特許文献2】K. Nishi et al.: Appl. Phys. Lett., Vol. 74 (1999), p. 1111

【発明の概要】

【発明が解決しようとする課題】

【0008】

歪緩和層は、基板と格子整合しないため、歪緩和層を配置しない場合に比べて、エピタキシャル層内に蓄積される歪が大きくなる。特に、量子ドットと歪緩和層とを積層する繰り返し回数を増やすと、ミスフィット転位が発生しやすくなる。ミスフィット転位の発生を抑制するために、量子ドットと歪緩和層とを積層する繰り返し回数の上限は、例えば10回程度に制限される。

【0009】

ミスフィット転位の発生を抑制しつつ、量子ドットからの発光波長を長波長化することができる半導体装置の製造技術が望まれている。

【課題を解決するための手段】

【0010】

本発明の一観点によると、

チャンバ内に単結晶基板を装填し、前記単結晶基板上に、分子線エピタキシにより、In及びAsを含む量子ドットを形成する工程と、

前記チャンバ内で、前記量子ドットに、少なくともAs2分子線を照射しながら第1アニールを行う工程と

を有する半導体装置の製造方法が提供される。

【0011】

本発明の他の観点によると、

単結晶基板の上に、面内分布密度が5×1010cm−2以上になるように分布し、各々の高さが6nm〜8nmの範囲内である複数の量子ドットと、

前記量子ドットを覆うように、前記単結晶基板の上に形成され、前記量子ドットよりもバンドギャップが大きく、前記単結晶基板の格子定数と前記量子ドットの格子定数との中間の格子定数を有する半導体材料からなる歪緩和層と

を有する半導体装置が提供される。

【発明の効果】

【0012】

第1アニールを行うことにより、量子ドットの寸法の減少を抑制することができる。これにより、発光波長の短波長化が抑制される。

【図面の簡単な説明】

【0013】

【図1】実施例による方法で用いられるMBE装置の概略図である。

【図2】クラッカーセルの概略図である。

【図3】実施例による製造方法で適用される基板温度、及び原料供給装置のシャッタの開閉を示すタイミングチャートである。

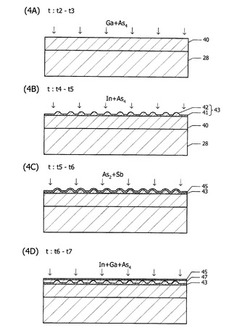

【図4−1】(4A)〜(4D)は、実施例による製造方法で製造される半導体装置の、製造途中段階における断面図である。

【図4−2】(4E)〜(4F)は、実施例による製造方法で製造される半導体装置の、製造途中段階における断面図であり、(4G)は、製造された半導体装置の断面図である。

【図5】(5A)は、実施李及び比較例による方法で製造した試料のPLスペクトルを示すグラフであり、(5B)は、歪緩和層のInAsの組成比を異ならせ、量子ドット形成後のアニール条件を異ならせて製造した試料のPL波長を示すグラフである。

【図6】(6A)は、量子ドット形成後のAFM写真であり、(6B)は、量子ドットをGaAs層で覆った後の断面TEM写真であり、(6C)は、量子ドット形成後に、As2とSbの分子線照射アニールを行った後のAM写真である。

【図7】(7A)は、実施例による方法で作製した量子ドットの近傍のSb及びInの原子濃度の測定結果を示すグラフであり、(7B)は、測定箇所を示す概略断面図である。

【図8】(8A)及び(8B)は、実施例による半導体製造方法を用いて製造したレーザダイオードの断面図である。

【発明を実施するための形態】

【0014】

図1に、実施例による製造方法で用いられるMBE装置の概略図を示す。チャンバ10内にステージ11が収容されている。チャンバ10内が、排気管14を介して真空排気される。ステージ11に、基板28が保持される。ステージ11内にヒータ16が配置されており、基板28を加熱することができる。温度測定器13が、基板28の温度を測定し、測定結果が制御装置25に入力される。温度測定器13には、例えば放射温度計(パイロメータ)が用いられる。また、ヒータ16は、制御装置25により制御される。

【0015】

ステージ11に対向する位置に原料供給装置20が取り付けられている。原料供給装置20は、As2、As4、Sb、Ga、Inごとに準備される。As4、Sb、Ga、Inの原料供給装置20には、例えばクヌードセンセル(Kセル)が用いられる。As2の原料供給装置20には、クラッカーセルが用いられる。供給量制御部21が、制御装置25からの指令を受けて各Kセル及びクラッカーセルの温度を制御することにより、原料ごとに供給量を変化させることができる。

【0016】

原料供給装置20から見てステージ11の後方にビーム強度計12が配置されている。ビーム強度計12には、例えば電離真空計が用いられる。ビーム強度計12は、ステージ11をビーム経路から退避させた状態で、分子線のビーム強度を測定することができる。ビーム強度計12による測定結果が制御装置25に入力される。分子線のビーム強度は、等価圧力に換算することができる。

【0017】

チャンバ10に、反射高速電子回折(RHEED)測定器15が取り付けられている。RHEED測定器15は、電子銃15A及び回折ビーム検出器15Bを含む。RHEED用電子銃15Aは、基板28に電子ビームを入射させる。基板28で回折された電子ビームが、検出器15Bにより検出される。検出結果が制御装置25に入力される。

【0018】

図2に、As2用クラッカーセルの概略図を示す。原料貯蔵部30内に、金属砒素31が貯蔵されている。ヒータ32で加熱されて金属砒素31が昇華し、As4分子が生成される。As4分子は、輸送チューブ33を通ってクラッキング部35まで輸送される。輸送チューブ33内にもヒータ34が配置されている。

【0019】

クラッキング部35に配置されたヒータ36が、As4分子を加熱する。As4分子が加熱されることにより、クラッキングされ、As2分子となって、チャンバ10(図1)内に放出される。

【0020】

図3、図4A〜図4Gを参照して、実施例による半導体装置の製造方法について説明する。

【0021】

図3に、基板温度、及び原料供給装置20の各々のシャッタの開閉のタイミングチャートを示す。図3の横軸は、経過時間tを表す。なお、図3において、横軸方向の長さは、実際の時間の長さに対応していない。図3は、以下の製造方法の説明中で、適宜参照される。

【0022】

図4Aに示した単結晶基板28を、チャンバ10内のステージ11(図1)によって保持する。単結晶基板28には、例えば(100)面のGaAs基板が用いられる。As4の原料供給装置20のシャッタ(以下、単に「As4のシャッタ」という。他の原料供給装置20のシャッタについても同様とする。)を開け、基板温度をT1まで上昇させる。As4分子線の強度は、基板表面からのAsの脱離を抑止するために、例えば2.67×10−3Pa(2×10−5Torr)とする。温度T1は、例えば580℃である。この状態を維持することにより、基板28の表面に形成されていた酸化膜が消滅し、GaAsの清浄な表面が現れる。

【0023】

基板28の表面の酸化膜が除去されたことは、RHEEDの回折像を観測することにより検知することができる。基板28の表面に酸化膜が残存している状態では、ブロードな回折像が現れる。清浄なGaAs表面が現れると、(100)結晶面に対応したシャープなスポット像またはストリーク像が現れる。

【0024】

清浄なGaAs表面が現れた後、基板温度を約20℃昇温させ、数分間維持した後、再度、温度T1まで降下させる。

【0025】

基板温度がT1まで降下した時刻t2において、Gaのシャッタを開ける。As4分子線の強度は、2.67×10−3Paに維持されており、Ga分子線の強度は、1.33×10−5Pa(1×10−7Torr)とする。この条件で、GaAsの成長速度は約0.8μm/hである。Gaのシャッタを開けてから30分後の時刻t3に、Gaのシャッタを閉じる。これにより、厚さ40nmのGaAsバッファ層40が形成される。

【0026】

時刻t3からt4の間に、基板温度をT1からT2まで低下させる。温度T2は、例えば500℃である。このとき、As4のシャッタは開けたままとする。

【0027】

図4Bに示すように、時刻t4からt5までの間に、InAs量子ドット42を形成する。以下、時刻t4からt5までの工程について説明する。

【0028】

時刻t4において、As4分子線の強度を1.07×10−3Pa(8×10−6Torr)まで下げ、Inのシャッタを開ける。Inの分子線の強度は、5.33×10−6Pa(4×10−8Torr)とする。この条件で、InAsの成長速度は、約0.05分子層/sである。時刻t4から約30秒が経過するまでの間は、ストリーク状のRHEED回折像が観測される。これは、基板表面が平坦であり、InAsの濡れ層41が均一に形成されていることを意味する。

【0029】

さらに成長を続けると、RHEED回折像がスポット状に変化する。これは、離散的に分布する量子ドット42が形成され始めたことを意味する。RHEED回折像がスポット状に変化してからさらに20秒程度、成長を継続した後、時刻t5においてInのシャッタを閉じる。これにより、InAs量子ドット42が形成される。量子ドット42と濡れ層41とを合わせて、量子ドット層43ということとする。

【0030】

なお、量子ドット42を、In及びAsを含む他の化合物半導体で形成してもよい。例えば、InGaAsで量子ドット42を形成してもよい。

【0031】

図4Cに示すように、時刻t5からt6までの間、As2分子線及びSb分子線を、基板表面(量子ドット層43の表面)に照射しながら、基板温度T2でアニールを行う。アニール時間は、例えば約60秒間とする。以下、時刻t5からt6までの工程について説明する。

【0032】

時刻t5において、As4のシャッタ及びInのシャッタを閉じ、As2のシャッタ及びSbのシャッタを開ける。これにより、基板に、As2分子線及びSb分子線が照射される。As2分子線の強度は、1.33×10−4Pa〜1.07×10−2Pa(1×10−6Torr〜8×10−5Torr)の範囲内とする。クラッキング部35(図2)の温度は、900℃とした。Sb分子線の強度は、6.67×10−6Pa〜6.67×10−5Pa(5×10−8Torr〜5×10−7Torr)の範囲内とする。

【0033】

基板にAs2分子線を照射する場合には、As4分子線を照射する場合に比べて、基板表面にAs原子が付着しやすい。従って、量子ドット層43の表面に、過剰なAs原子が付着する。さらに、SbはAsよりも、InAs表面に、付着しやすいため、量子ドット層43の表面にSbが残留する。これにより、量子ドット層43の表面に、As及びSbが過剰に付着した過剰付着層45が形成されると考えられる。

【0034】

図4Dに示すように、時刻t6からt7の間に、量子ドット層43の上に、InGaAsからなる歪緩和層47を形成する。以下、時刻t6からt7までの工程について説明する。

【0035】

時刻t6において、As2のシャッタ及びSbのシャッタを閉じ、As4、Ga、及びInのシャッタを開ける。InAsの成長速度が0.05μm/h、GaAsの成長速度が0.28μm/hになるように、As4、Ga、及びInの分子線の強度を調整する。これにより、InAs組成が0.15のInGaAsが成長する。時刻t6から約55秒後の時刻t7において、Inのシャッタを閉じる。ここまでの工程で、InGaAsからなる厚さ5nmの歪緩和層47が形成される。歪緩和層47は、単結晶基板28の格子定数と、量子ドット42の格子定数との中間の格子定数を持つ。また、歪緩和層47のバンドギャップは、量子ドット42のバンドギャップより大きい。

【0036】

量子ドット層43の表面に過剰に付着していたAs及びSbは、歪緩和層47の表面に偏析すると考えられる。これにより、歪緩和層47の上に、As及びSbの過剰付着層45が残留する。

【0037】

図4Eに示すように、時刻t7からt8の間に、歪緩和層47の上に、GaAsからなる第1障壁層50を形成する。第1障壁層50は、単結晶基板28に格子整合し、量子ドット42のバンドギャップより大きなバンドギャップを有する。以下、時刻t7からt8までの工程について説明する。

【0038】

時刻t7において、Inのシャッタを閉じることにより、GaAsが成長し始める。時刻t7から約1分後の時刻t8において、Gaのシャッタを閉じる。ここまでの工程で、GaAsからなる厚さ約5nmの第1障壁層50が形成される。

【0039】

歪緩和層47の上に過剰に付着していたAs及びSbが、第1障壁層50の表面に偏析する。これにより、第1障壁層50の上に、As及びSbの過剰付着層45が残留する。

【0040】

図4Fに示すように、時刻t8からt10の間に、過剰付着層45のAs及びSbを除去するためのアニールを行う。以下、時刻t8からt10までの工程について説明する。

【0041】

時刻t8において、Gaのシャッタを閉じた後、基板温度をT2からT3まで昇温させる。As4分子線は基板に照射されたままである。温度T3は、例えば560℃である。時刻t9で基板温度がT3に達した後、時刻t10までの約1分間、温度T3でアニールを行う。これにより、第1障壁層50の表面に過剰に付着していたAs及びSbが除去され、過剰付着層45(図4E)が消失する。過剰なAs及びSbを除去するためには、このアニール工程の基板温度T3を、量子ドット層43を形成するときの基板温度T2よりも高くすることが好ましい。

【0042】

図4Gに示すように、時刻t10からt11までの間に、第1障壁層50の上に、第1障壁層50と同一の材料、すなわちGaAsからなる第2障壁層51を形成する。以下、時刻t10からt11までの工程について説明する。

【0043】

時刻t10において、Gaのシャッタを開ける。これにより、GaAsの成長が始まる。時刻t10から約21分が経過した時刻t11に、Gaのシャッタを閉じる。ここまでの工程で、GaAsからなる厚さ約98nmの第2障壁層51が形成される。

【0044】

必要に応じて、量子ドット層43、歪緩和層47、第1障壁層50、及び第2障壁層51からなる単位積層構造55を複数回積み重ねてもよい。

【0045】

次に、図5A、図5Bを参照して、上記実施例の効果について説明する。

【0046】

図5Aに、上記実施例による方法で作製した試料からのフォトルミネッセンス(PL)スペクトルの測定結果を、比較例による方法で作製した試料と比較して示す。比較例による方法では、図4Cに示したアニール工程、図4Eに示した第1障壁層50の形成工程、及び図4Fに示した過剰付着層45除去のためのアニール工程が実施されない。なお、比較例による試料においては、図4Gに示した第2障壁層51の膜厚を100nmとした。

【0047】

図5Aの実線が、実施例による方法で作製した試料のPLスペクトルを示し、破線が、比較例による方法で作製した試料のPLスペクトルを示す。比較例による試料のPLピーク波長が約1.25μmであるのに対し、実施例による試料のPLピーク波長は約1.33μmであった。実施例による方法を適用することにより、PL波長が長波長化し、1.3μm帯の発光が得られていることがわかる。

【0048】

比較例による方法で、1.33μm程度のPL波長を実現するためには、歪緩和層47のInAsの組成比を0.2程度にしなければならない。これに対し、実施例による方法では、歪緩和層47のInAsの組成比が0.15程度であっても、1.33μm程度のPL波長を実現することができた。歪緩和層47のInAsの組成比が小さいということは、その格子定数が、GaAs基板の格子定数に近いということである。このため、歪緩和層47内の歪量が小さくなる。

【0049】

歪緩和層47内の歪量が大きくなると、単位積層構造55を積み重ねることができる積層数の上限が少なくなる。実施例においては、歪緩和層47内の歪量を小さくすることができるため、単位積層構造55の積み重ね数を多くすることが可能である。さらに、単位積層構造55を積み重ねたときのミスフィット転位の発生を抑制することができる。

【0050】

図5Bに、歪緩和層47の組成が異なる複数の試料のPL波長の測定結果を示す。横軸は、InGaAs歪緩和層47のInAsの組成比を表し、縦軸はPL波長を単位「μm」で表す。図5B中の中空の丸記号、中空の三角記号、中実の四角記号、及び中実の三角記号は、それぞれ図4Cに示したアニール工程で照射する分子線を、As2+Sb、As2、As4+Sb、及びAs4として作製した試料を示す。

【0051】

歪緩和層47の組成を同一にした試料同士を比較すると、アニール工程で、As2+Sb分子線を照射した試料のPL波長が最も長いことがわかる。アニール工程で、As2分子線を照射した試料のPL波長が2番目に長く、As4+Sb分子線を照射した試料のPL波長が3番目に長く、As4分子線を照射した試料のPL波長が最も短い。

【0052】

この評価結果から分かるように、図4Cに示したアニール工程で照射する分子線を、成膜時等に用いたAs4分子線からAs2分子線に切り替えることにより、PL波長を長くすることができる。さらに、アニール工程で照射する分子線に、Sb分子線を含めることにより、PL波長を、より長くすることができる。

【0053】

次に、図6A〜図6Cを参照して、上述の長波長化の効果が得られる理由について説明する。

【0054】

図6Aに、図4Bに示した量子ドット層43を形成した状態の原子間力顕微鏡(AFM)写真を示す。基板表面に点在する複数の量子ドットが観察される。量子ドットの高さは、6nm〜8nmであった。

【0055】

図6Bに、InAs量子ドット層の上にGaAs障壁層を形成した状態の1つの量子ドットの透過型電子顕微鏡(TEM)写真を示す。黒く表示された量子ドットの直下のGaAsバッファ層、及び直上のGaAs障壁層も、歪が内在することによってやや黒く表示されている。上方の黒色の領域と、下方の黒色領域との間の白い湾曲した領域が、量子ドットの表面に対応する。このTEM写真から、量子ドットの高さは3nm〜5nmであると見積もられる。

【0056】

GaAs障壁層を形成することによって、量子ドットの高さが、6nm〜8nmから3nm〜5nmまで低くなることがわかった。これは、GaAs障壁層の成膜中に、量子ドット中のInが障壁層内に偏析または拡散したためと考えられる。量子ドットの底面の直径は約20nmであり、その高さに比べて十分大きい。このため、PL波長は、量子ドットの高さに大きく依存する。量子ドットが低くなると、PL波長が短くなってしまう。

【0057】

図6Cに、図4Cに示したアニール後の表面のAFM写真を示す。アニール後においても、量子ドットの高さが6nm〜8nmに保たれていることが確認された。実施例による方法では、図4Dに示した歪緩和層47を形成する際に、過剰付着層45を構成するAs及びSbが、歪緩和層47の表面に偏析する。As及びSbの偏析係数は、Inの偏析係数より大きいため、As及びSbがInよりも優先的に偏析し、量子ドット中のInの偏析または拡散が抑制されると考えられる。これにより、量子ドットの高さの減少が防止される。

【0058】

量子ドット42が、InGaAs歪緩和層47(図4D)で被われてしまうと、量子ドット42は安定になる。このため、第1障壁層50(図4E)及び第2障壁層51(図4G)の成膜時には、Inの偏析は生じにくい。

【0059】

実施例による方法では、量子ドットの高さを、6nm〜8nmに維持することができるため、図5Aに示した比較例に比べて、PL波長が長くなっていると考えられる。

【0060】

Sbが結晶内に残留すると、InSbやGaSbが生成される。InSb及びGaSbは、基板のGaAsに比べて格子定数が大きいため、歪源となる。また、Sbは、アンチサイト欠陥を生じさせやすい元素である。アンチサイト欠陥は、非発光センターとして作用する。従って、Sbを結晶内に残留させることは好ましくない。

【0061】

実施例においては、図4Fに示したように、Sb除去のためのアニールを行っている。このため、Sbに起因する素子特性の低下を抑制することができる。

【0062】

図7Aに、残留Sbの濃度を測定した結果を示す。残留Sbの濃度測定は、図7Bに示すように、量子ドット42の中心を高さ方向に貫通する直線上で行った。図7Aの横軸は、高さ方向の位置を単位「nm」で表し、縦軸は、原子濃度を単位「原子%」で表す。図7A中の中空の丸記号がSb濃度を示す。比較のために、In濃度を中実の丸記号で示す。Sbは、量子ドット42の近傍に残留していないことがわかる。

【0063】

残留Sbが観測されないのは、図4Cの工程で、量子ドット42の表面に過剰に付着したSbが、図4D及び図4Eの工程で、それぞれ歪緩和層47及び第1障壁層50の表面に偏析し、図4Fの工程で除去されたためであると考えられる。

【0064】

Sbを除去するためのアニールは、相対的に厚い第2障壁層51(図4G)を形成する前に、相対的に薄い第1障壁層50を形成した時点で行われる。このため、Sbを効率的に除去することができる。Sbを効率的に除去するために、第1障壁層50の厚さを10 nm以下にすることが好ましい。

【0065】

第1障壁層50を形成する前に、すなわち歪緩和層47(図4D)を形成した直後に、Sb除去のためのアニールを行うと、歪緩和層47内のInの再蒸発起こる。これに伴って、量子ドット42内のInが歪緩和層47内に拡散しやすくなり、量子ドット42の高さが低くなってしまう。量子ドット42の高さが低下する現象を防止するために、歪緩和層47と第1障壁層50との合計の厚さを、量子ドット42の高さ以上にすることが好ましい。

【0066】

上記実施例では、図4Cに示したアニール工程で、As2及びSbの分子線を照射したが、As2分子線のみを照射してもよい。As2分子線のみを照射する場合にも、図5Bに示したように、PL波長の長波長化の効果が得られる。

【0067】

図3の時刻t1〜t5、及びt6〜t11の間に、As2分子線を基板に照射すると、チャンバ10(図1)の内壁や、チャンバ10内の種々の測定器に、Asが付着しやすくなる。従って、クリーニング等のメンテナンス周期を短くしなければならない。このため、時刻t1〜t5、及びt6〜t11の間には、As2分子線ではなく、As4分子線を基板に照射することが好ましい。

【0068】

上記実施例では、図4Cの工程でアニールを行い、過剰なAs及びSbを量子ドット層43の表面に付着させることにより、量子ドット42の高さの減少を抑制した。量子ドットの成長速度を遅くすることによっても、量子ドットの寸法を大きくすることが可能である。ただし、成長速度を遅くすると、量子ドットの面内分布密度が低下してしまう。

【0069】

上記実施例による方法を適用することにより、量子ドットの高さの低下を抑制し、かつ量子ドットの面内分布密度の低下も抑制することができる。実施例による方法では、例えば、 面内分布密度が5×1010cm−2以上になり、かつ各々の量子ドットの高さが6nm〜8nmの範囲内である半導体装置を製造することが可能である。従来の方法を用いて量子ドットの高さを6nm〜8nmにすると、面内分布密度が5×1010cm−2よりも低くなってしまう。

【0070】

図8A及び図8Bに、上記実施例による方法を用いて製造されるレーザダイオードの断面図を示す。図8Aは、レーザ光の伝搬方向に平行な断面図を示し、図8Bは、レーザ光の伝搬方向に垂直な断面図を示す。

【0071】

以下、レーザダイオードの製造方法について説明する。(100)面が露出したn+型GaAs基板60の上に、n+型GaAsからなる厚さ400nm〜500nmのバッファ層61を形成する。バッファ層61の上に、n+型AlGaAsからなる厚さ約1300nmの下側クラッド層62を形成する。下側クラッド層62の上に、n型GaAsからなる厚さ約10nmの下側導波層63を形成する。下側導波層63の上に、厚さ約20nmのアンドープGaAs層64を形成する。これらの層は、例えば基板温度580℃の条件で、MBEにより形成される。

【0072】

アンドープGaAs層64の上に、活性層65を形成する。活性層65の形成は、図4Bに示した量子ドット層43の形成から図4Gに示した第2障壁層51の形成までの工程と同一である。なお、第2障壁層51の厚さは、例えば20nmに設定される。この工程を、合計で10回繰り返すことにより、活性層65が形成される。すなわち、活性層65は、図4Gに示した単位積層構造55を10層積み重ねることにより形成される。

【0073】

活性層65の上に、厚さ約20nmのアンドープGaAs層66を形成する。アンドープGaAs層66の上に、p型GaAsからなる厚さ約20nmの上側導波層67を形成する。上側導波層67の上に、p+型AlGaAsからなる厚さ約1300nmの上側クラッド層68を形成する。上側クラッド層68の上に、p+型GaAsからなる厚さ約50nmのキャップ層69を形成する。これらの層は、基板温度580℃の条件で、MBEにより形成される。

【0074】

図8Bに示すように、キャップ層69から下側クラッド層62までを、バッファ層61が露出するまでメサエッチングすることにより、メサ72を形成する。メサエッチング後、バッファ層61の表面、及びメサ72の表面を、SiNからなる保護膜70で覆う。この保護膜70に、電極を形成するための複数の開口を形成する。開口内に、バッファ層61の一部、及びキャップ層69の一部が露出する。開口内に露出したキャップ層69及びバッファ層61の上に、それぞれ電極71を形成する。電極形成後、基板60をレーザダイオードごとに個片化する。

【0075】

図8Aに示すように、一方の端面に高反射膜73を形成し、他方の端面に低反射膜74を形成する。これにより、1.3μm帯のレーザダイオードが完成する。活性層65の形成に、上記実施例による方法を適用するため、活性層65内のミスフィット転位の発生が抑制される。このため、高品質なレーザダイオードが得られる。

【0076】

なお、下側クラッド層62と下側導波層63との間に、回折格子を配置することにより、分布帰還型レーザダイオードを作製することもできる。また、図8Aに示した一対の端面の両方に、低反射膜を形成することにより、光増幅器とすることもできる。

【0077】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0078】

10 チャンバ

11 ステージ

12 ビーム強度計

13 温度測定器

14 排気管

15 RHEED測定器

15A 電子銃

15B 検出器

16 ヒータ

20 原料供給装置

21 供給量制御部

25 制御装置

28 基板

30 原料貯蔵部

31 金属砒素

32 ヒータ

33 輸送チューブ

34 ヒータ

35 クラッキング部

36 ヒータ

40 バッファ層

41 濡れ層

42 量子ドット

43 量子ドット層

45 過剰付着層

47 歪緩和層

50 第1障壁層

51 第2障壁層

55 単位積層構造

60 GaAs基板

61 バッファ層

62 下側クラッド層

63 下側導波層

64 アンドープGaAs層

65 活性層

66 アンドープGaAs層

67 上側導波層

68 上側クラッド層

69 キャップ層

70 保護膜

71 電極

72 メサ

【技術分野】

【0001】

本発明は、量子ドットを含む半導体装置の製造方法及び半導体装置に関する。

【背景技術】

【0002】

化合物半導体基板上に、格子整合しない化合物半導体をヘテロエピタキシャル成長させると、成長初期にS−K(ストランスキ・クラスタノフ)モード成長が出現する。S−Kモード成長を利用することにより、下地表面に離散的に分布する微細な結晶(量子ドット)を形成することができる。例えば、GaAs基板上に、InAs組成が50%程度のInGaAsを数分子層、分子線エピタキシ(MBE)により成長させると、直径30〜40nm程度のInGaAsの量子ドットが形成される。

【0003】

S−Kモード成長を利用することにより、リソグラフィ等による加工プロセスを用いた場合に比べて、簡便に量子ドットを形成することができる。さらに、S−Kモード成長を利用する場合には、加工プロセスを実行する必要がないため、加工時に導入され得る欠陥等のない高品質な量子ドットを得ることができる。

【0004】

GaAs基板上に、通常のMBEによりInAs量子ドットを形成した光素子の発光波長は、1.1〜1.2μm程度である。波長1.3μm帯の通信用の光素子に、量子ドット素子を適用する場合には、発光波長を長波長化しなければならない。InAs量子ドットを、InAs組成が20%程度で厚さが数nmのInGaAs層(歪緩和層)で覆うことにより、発光波長を長波長化できることが知られている。

【0005】

InAs量子ドットを形成した後、アンチモン照射等を行うことにより、巨大ドット構造等の結晶欠陥の発生を抑制し、量子ドットの結晶性を向上させる技術が知られている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−176821号公報

【非特許文献】

【0007】

【非特許文献1】D. Leonard et al.: Appl. Phys. Lett., Vol. 63, No. 23, pp. 3203-3205 (1993)

【非特許文献2】K. Nishi et al.: Appl. Phys. Lett., Vol. 74 (1999), p. 1111

【発明の概要】

【発明が解決しようとする課題】

【0008】

歪緩和層は、基板と格子整合しないため、歪緩和層を配置しない場合に比べて、エピタキシャル層内に蓄積される歪が大きくなる。特に、量子ドットと歪緩和層とを積層する繰り返し回数を増やすと、ミスフィット転位が発生しやすくなる。ミスフィット転位の発生を抑制するために、量子ドットと歪緩和層とを積層する繰り返し回数の上限は、例えば10回程度に制限される。

【0009】

ミスフィット転位の発生を抑制しつつ、量子ドットからの発光波長を長波長化することができる半導体装置の製造技術が望まれている。

【課題を解決するための手段】

【0010】

本発明の一観点によると、

チャンバ内に単結晶基板を装填し、前記単結晶基板上に、分子線エピタキシにより、In及びAsを含む量子ドットを形成する工程と、

前記チャンバ内で、前記量子ドットに、少なくともAs2分子線を照射しながら第1アニールを行う工程と

を有する半導体装置の製造方法が提供される。

【0011】

本発明の他の観点によると、

単結晶基板の上に、面内分布密度が5×1010cm−2以上になるように分布し、各々の高さが6nm〜8nmの範囲内である複数の量子ドットと、

前記量子ドットを覆うように、前記単結晶基板の上に形成され、前記量子ドットよりもバンドギャップが大きく、前記単結晶基板の格子定数と前記量子ドットの格子定数との中間の格子定数を有する半導体材料からなる歪緩和層と

を有する半導体装置が提供される。

【発明の効果】

【0012】

第1アニールを行うことにより、量子ドットの寸法の減少を抑制することができる。これにより、発光波長の短波長化が抑制される。

【図面の簡単な説明】

【0013】

【図1】実施例による方法で用いられるMBE装置の概略図である。

【図2】クラッカーセルの概略図である。

【図3】実施例による製造方法で適用される基板温度、及び原料供給装置のシャッタの開閉を示すタイミングチャートである。

【図4−1】(4A)〜(4D)は、実施例による製造方法で製造される半導体装置の、製造途中段階における断面図である。

【図4−2】(4E)〜(4F)は、実施例による製造方法で製造される半導体装置の、製造途中段階における断面図であり、(4G)は、製造された半導体装置の断面図である。

【図5】(5A)は、実施李及び比較例による方法で製造した試料のPLスペクトルを示すグラフであり、(5B)は、歪緩和層のInAsの組成比を異ならせ、量子ドット形成後のアニール条件を異ならせて製造した試料のPL波長を示すグラフである。

【図6】(6A)は、量子ドット形成後のAFM写真であり、(6B)は、量子ドットをGaAs層で覆った後の断面TEM写真であり、(6C)は、量子ドット形成後に、As2とSbの分子線照射アニールを行った後のAM写真である。

【図7】(7A)は、実施例による方法で作製した量子ドットの近傍のSb及びInの原子濃度の測定結果を示すグラフであり、(7B)は、測定箇所を示す概略断面図である。

【図8】(8A)及び(8B)は、実施例による半導体製造方法を用いて製造したレーザダイオードの断面図である。

【発明を実施するための形態】

【0014】

図1に、実施例による製造方法で用いられるMBE装置の概略図を示す。チャンバ10内にステージ11が収容されている。チャンバ10内が、排気管14を介して真空排気される。ステージ11に、基板28が保持される。ステージ11内にヒータ16が配置されており、基板28を加熱することができる。温度測定器13が、基板28の温度を測定し、測定結果が制御装置25に入力される。温度測定器13には、例えば放射温度計(パイロメータ)が用いられる。また、ヒータ16は、制御装置25により制御される。

【0015】

ステージ11に対向する位置に原料供給装置20が取り付けられている。原料供給装置20は、As2、As4、Sb、Ga、Inごとに準備される。As4、Sb、Ga、Inの原料供給装置20には、例えばクヌードセンセル(Kセル)が用いられる。As2の原料供給装置20には、クラッカーセルが用いられる。供給量制御部21が、制御装置25からの指令を受けて各Kセル及びクラッカーセルの温度を制御することにより、原料ごとに供給量を変化させることができる。

【0016】

原料供給装置20から見てステージ11の後方にビーム強度計12が配置されている。ビーム強度計12には、例えば電離真空計が用いられる。ビーム強度計12は、ステージ11をビーム経路から退避させた状態で、分子線のビーム強度を測定することができる。ビーム強度計12による測定結果が制御装置25に入力される。分子線のビーム強度は、等価圧力に換算することができる。

【0017】

チャンバ10に、反射高速電子回折(RHEED)測定器15が取り付けられている。RHEED測定器15は、電子銃15A及び回折ビーム検出器15Bを含む。RHEED用電子銃15Aは、基板28に電子ビームを入射させる。基板28で回折された電子ビームが、検出器15Bにより検出される。検出結果が制御装置25に入力される。

【0018】

図2に、As2用クラッカーセルの概略図を示す。原料貯蔵部30内に、金属砒素31が貯蔵されている。ヒータ32で加熱されて金属砒素31が昇華し、As4分子が生成される。As4分子は、輸送チューブ33を通ってクラッキング部35まで輸送される。輸送チューブ33内にもヒータ34が配置されている。

【0019】

クラッキング部35に配置されたヒータ36が、As4分子を加熱する。As4分子が加熱されることにより、クラッキングされ、As2分子となって、チャンバ10(図1)内に放出される。

【0020】

図3、図4A〜図4Gを参照して、実施例による半導体装置の製造方法について説明する。

【0021】

図3に、基板温度、及び原料供給装置20の各々のシャッタの開閉のタイミングチャートを示す。図3の横軸は、経過時間tを表す。なお、図3において、横軸方向の長さは、実際の時間の長さに対応していない。図3は、以下の製造方法の説明中で、適宜参照される。

【0022】

図4Aに示した単結晶基板28を、チャンバ10内のステージ11(図1)によって保持する。単結晶基板28には、例えば(100)面のGaAs基板が用いられる。As4の原料供給装置20のシャッタ(以下、単に「As4のシャッタ」という。他の原料供給装置20のシャッタについても同様とする。)を開け、基板温度をT1まで上昇させる。As4分子線の強度は、基板表面からのAsの脱離を抑止するために、例えば2.67×10−3Pa(2×10−5Torr)とする。温度T1は、例えば580℃である。この状態を維持することにより、基板28の表面に形成されていた酸化膜が消滅し、GaAsの清浄な表面が現れる。

【0023】

基板28の表面の酸化膜が除去されたことは、RHEEDの回折像を観測することにより検知することができる。基板28の表面に酸化膜が残存している状態では、ブロードな回折像が現れる。清浄なGaAs表面が現れると、(100)結晶面に対応したシャープなスポット像またはストリーク像が現れる。

【0024】

清浄なGaAs表面が現れた後、基板温度を約20℃昇温させ、数分間維持した後、再度、温度T1まで降下させる。

【0025】

基板温度がT1まで降下した時刻t2において、Gaのシャッタを開ける。As4分子線の強度は、2.67×10−3Paに維持されており、Ga分子線の強度は、1.33×10−5Pa(1×10−7Torr)とする。この条件で、GaAsの成長速度は約0.8μm/hである。Gaのシャッタを開けてから30分後の時刻t3に、Gaのシャッタを閉じる。これにより、厚さ40nmのGaAsバッファ層40が形成される。

【0026】

時刻t3からt4の間に、基板温度をT1からT2まで低下させる。温度T2は、例えば500℃である。このとき、As4のシャッタは開けたままとする。

【0027】

図4Bに示すように、時刻t4からt5までの間に、InAs量子ドット42を形成する。以下、時刻t4からt5までの工程について説明する。

【0028】

時刻t4において、As4分子線の強度を1.07×10−3Pa(8×10−6Torr)まで下げ、Inのシャッタを開ける。Inの分子線の強度は、5.33×10−6Pa(4×10−8Torr)とする。この条件で、InAsの成長速度は、約0.05分子層/sである。時刻t4から約30秒が経過するまでの間は、ストリーク状のRHEED回折像が観測される。これは、基板表面が平坦であり、InAsの濡れ層41が均一に形成されていることを意味する。

【0029】

さらに成長を続けると、RHEED回折像がスポット状に変化する。これは、離散的に分布する量子ドット42が形成され始めたことを意味する。RHEED回折像がスポット状に変化してからさらに20秒程度、成長を継続した後、時刻t5においてInのシャッタを閉じる。これにより、InAs量子ドット42が形成される。量子ドット42と濡れ層41とを合わせて、量子ドット層43ということとする。

【0030】

なお、量子ドット42を、In及びAsを含む他の化合物半導体で形成してもよい。例えば、InGaAsで量子ドット42を形成してもよい。

【0031】

図4Cに示すように、時刻t5からt6までの間、As2分子線及びSb分子線を、基板表面(量子ドット層43の表面)に照射しながら、基板温度T2でアニールを行う。アニール時間は、例えば約60秒間とする。以下、時刻t5からt6までの工程について説明する。

【0032】

時刻t5において、As4のシャッタ及びInのシャッタを閉じ、As2のシャッタ及びSbのシャッタを開ける。これにより、基板に、As2分子線及びSb分子線が照射される。As2分子線の強度は、1.33×10−4Pa〜1.07×10−2Pa(1×10−6Torr〜8×10−5Torr)の範囲内とする。クラッキング部35(図2)の温度は、900℃とした。Sb分子線の強度は、6.67×10−6Pa〜6.67×10−5Pa(5×10−8Torr〜5×10−7Torr)の範囲内とする。

【0033】

基板にAs2分子線を照射する場合には、As4分子線を照射する場合に比べて、基板表面にAs原子が付着しやすい。従って、量子ドット層43の表面に、過剰なAs原子が付着する。さらに、SbはAsよりも、InAs表面に、付着しやすいため、量子ドット層43の表面にSbが残留する。これにより、量子ドット層43の表面に、As及びSbが過剰に付着した過剰付着層45が形成されると考えられる。

【0034】

図4Dに示すように、時刻t6からt7の間に、量子ドット層43の上に、InGaAsからなる歪緩和層47を形成する。以下、時刻t6からt7までの工程について説明する。

【0035】

時刻t6において、As2のシャッタ及びSbのシャッタを閉じ、As4、Ga、及びInのシャッタを開ける。InAsの成長速度が0.05μm/h、GaAsの成長速度が0.28μm/hになるように、As4、Ga、及びInの分子線の強度を調整する。これにより、InAs組成が0.15のInGaAsが成長する。時刻t6から約55秒後の時刻t7において、Inのシャッタを閉じる。ここまでの工程で、InGaAsからなる厚さ5nmの歪緩和層47が形成される。歪緩和層47は、単結晶基板28の格子定数と、量子ドット42の格子定数との中間の格子定数を持つ。また、歪緩和層47のバンドギャップは、量子ドット42のバンドギャップより大きい。

【0036】

量子ドット層43の表面に過剰に付着していたAs及びSbは、歪緩和層47の表面に偏析すると考えられる。これにより、歪緩和層47の上に、As及びSbの過剰付着層45が残留する。

【0037】

図4Eに示すように、時刻t7からt8の間に、歪緩和層47の上に、GaAsからなる第1障壁層50を形成する。第1障壁層50は、単結晶基板28に格子整合し、量子ドット42のバンドギャップより大きなバンドギャップを有する。以下、時刻t7からt8までの工程について説明する。

【0038】

時刻t7において、Inのシャッタを閉じることにより、GaAsが成長し始める。時刻t7から約1分後の時刻t8において、Gaのシャッタを閉じる。ここまでの工程で、GaAsからなる厚さ約5nmの第1障壁層50が形成される。

【0039】

歪緩和層47の上に過剰に付着していたAs及びSbが、第1障壁層50の表面に偏析する。これにより、第1障壁層50の上に、As及びSbの過剰付着層45が残留する。

【0040】

図4Fに示すように、時刻t8からt10の間に、過剰付着層45のAs及びSbを除去するためのアニールを行う。以下、時刻t8からt10までの工程について説明する。

【0041】

時刻t8において、Gaのシャッタを閉じた後、基板温度をT2からT3まで昇温させる。As4分子線は基板に照射されたままである。温度T3は、例えば560℃である。時刻t9で基板温度がT3に達した後、時刻t10までの約1分間、温度T3でアニールを行う。これにより、第1障壁層50の表面に過剰に付着していたAs及びSbが除去され、過剰付着層45(図4E)が消失する。過剰なAs及びSbを除去するためには、このアニール工程の基板温度T3を、量子ドット層43を形成するときの基板温度T2よりも高くすることが好ましい。

【0042】

図4Gに示すように、時刻t10からt11までの間に、第1障壁層50の上に、第1障壁層50と同一の材料、すなわちGaAsからなる第2障壁層51を形成する。以下、時刻t10からt11までの工程について説明する。

【0043】

時刻t10において、Gaのシャッタを開ける。これにより、GaAsの成長が始まる。時刻t10から約21分が経過した時刻t11に、Gaのシャッタを閉じる。ここまでの工程で、GaAsからなる厚さ約98nmの第2障壁層51が形成される。

【0044】

必要に応じて、量子ドット層43、歪緩和層47、第1障壁層50、及び第2障壁層51からなる単位積層構造55を複数回積み重ねてもよい。

【0045】

次に、図5A、図5Bを参照して、上記実施例の効果について説明する。

【0046】

図5Aに、上記実施例による方法で作製した試料からのフォトルミネッセンス(PL)スペクトルの測定結果を、比較例による方法で作製した試料と比較して示す。比較例による方法では、図4Cに示したアニール工程、図4Eに示した第1障壁層50の形成工程、及び図4Fに示した過剰付着層45除去のためのアニール工程が実施されない。なお、比較例による試料においては、図4Gに示した第2障壁層51の膜厚を100nmとした。

【0047】

図5Aの実線が、実施例による方法で作製した試料のPLスペクトルを示し、破線が、比較例による方法で作製した試料のPLスペクトルを示す。比較例による試料のPLピーク波長が約1.25μmであるのに対し、実施例による試料のPLピーク波長は約1.33μmであった。実施例による方法を適用することにより、PL波長が長波長化し、1.3μm帯の発光が得られていることがわかる。

【0048】

比較例による方法で、1.33μm程度のPL波長を実現するためには、歪緩和層47のInAsの組成比を0.2程度にしなければならない。これに対し、実施例による方法では、歪緩和層47のInAsの組成比が0.15程度であっても、1.33μm程度のPL波長を実現することができた。歪緩和層47のInAsの組成比が小さいということは、その格子定数が、GaAs基板の格子定数に近いということである。このため、歪緩和層47内の歪量が小さくなる。

【0049】

歪緩和層47内の歪量が大きくなると、単位積層構造55を積み重ねることができる積層数の上限が少なくなる。実施例においては、歪緩和層47内の歪量を小さくすることができるため、単位積層構造55の積み重ね数を多くすることが可能である。さらに、単位積層構造55を積み重ねたときのミスフィット転位の発生を抑制することができる。

【0050】

図5Bに、歪緩和層47の組成が異なる複数の試料のPL波長の測定結果を示す。横軸は、InGaAs歪緩和層47のInAsの組成比を表し、縦軸はPL波長を単位「μm」で表す。図5B中の中空の丸記号、中空の三角記号、中実の四角記号、及び中実の三角記号は、それぞれ図4Cに示したアニール工程で照射する分子線を、As2+Sb、As2、As4+Sb、及びAs4として作製した試料を示す。

【0051】

歪緩和層47の組成を同一にした試料同士を比較すると、アニール工程で、As2+Sb分子線を照射した試料のPL波長が最も長いことがわかる。アニール工程で、As2分子線を照射した試料のPL波長が2番目に長く、As4+Sb分子線を照射した試料のPL波長が3番目に長く、As4分子線を照射した試料のPL波長が最も短い。

【0052】

この評価結果から分かるように、図4Cに示したアニール工程で照射する分子線を、成膜時等に用いたAs4分子線からAs2分子線に切り替えることにより、PL波長を長くすることができる。さらに、アニール工程で照射する分子線に、Sb分子線を含めることにより、PL波長を、より長くすることができる。

【0053】

次に、図6A〜図6Cを参照して、上述の長波長化の効果が得られる理由について説明する。

【0054】

図6Aに、図4Bに示した量子ドット層43を形成した状態の原子間力顕微鏡(AFM)写真を示す。基板表面に点在する複数の量子ドットが観察される。量子ドットの高さは、6nm〜8nmであった。

【0055】

図6Bに、InAs量子ドット層の上にGaAs障壁層を形成した状態の1つの量子ドットの透過型電子顕微鏡(TEM)写真を示す。黒く表示された量子ドットの直下のGaAsバッファ層、及び直上のGaAs障壁層も、歪が内在することによってやや黒く表示されている。上方の黒色の領域と、下方の黒色領域との間の白い湾曲した領域が、量子ドットの表面に対応する。このTEM写真から、量子ドットの高さは3nm〜5nmであると見積もられる。

【0056】

GaAs障壁層を形成することによって、量子ドットの高さが、6nm〜8nmから3nm〜5nmまで低くなることがわかった。これは、GaAs障壁層の成膜中に、量子ドット中のInが障壁層内に偏析または拡散したためと考えられる。量子ドットの底面の直径は約20nmであり、その高さに比べて十分大きい。このため、PL波長は、量子ドットの高さに大きく依存する。量子ドットが低くなると、PL波長が短くなってしまう。

【0057】

図6Cに、図4Cに示したアニール後の表面のAFM写真を示す。アニール後においても、量子ドットの高さが6nm〜8nmに保たれていることが確認された。実施例による方法では、図4Dに示した歪緩和層47を形成する際に、過剰付着層45を構成するAs及びSbが、歪緩和層47の表面に偏析する。As及びSbの偏析係数は、Inの偏析係数より大きいため、As及びSbがInよりも優先的に偏析し、量子ドット中のInの偏析または拡散が抑制されると考えられる。これにより、量子ドットの高さの減少が防止される。

【0058】

量子ドット42が、InGaAs歪緩和層47(図4D)で被われてしまうと、量子ドット42は安定になる。このため、第1障壁層50(図4E)及び第2障壁層51(図4G)の成膜時には、Inの偏析は生じにくい。

【0059】

実施例による方法では、量子ドットの高さを、6nm〜8nmに維持することができるため、図5Aに示した比較例に比べて、PL波長が長くなっていると考えられる。

【0060】

Sbが結晶内に残留すると、InSbやGaSbが生成される。InSb及びGaSbは、基板のGaAsに比べて格子定数が大きいため、歪源となる。また、Sbは、アンチサイト欠陥を生じさせやすい元素である。アンチサイト欠陥は、非発光センターとして作用する。従って、Sbを結晶内に残留させることは好ましくない。

【0061】

実施例においては、図4Fに示したように、Sb除去のためのアニールを行っている。このため、Sbに起因する素子特性の低下を抑制することができる。

【0062】

図7Aに、残留Sbの濃度を測定した結果を示す。残留Sbの濃度測定は、図7Bに示すように、量子ドット42の中心を高さ方向に貫通する直線上で行った。図7Aの横軸は、高さ方向の位置を単位「nm」で表し、縦軸は、原子濃度を単位「原子%」で表す。図7A中の中空の丸記号がSb濃度を示す。比較のために、In濃度を中実の丸記号で示す。Sbは、量子ドット42の近傍に残留していないことがわかる。

【0063】

残留Sbが観測されないのは、図4Cの工程で、量子ドット42の表面に過剰に付着したSbが、図4D及び図4Eの工程で、それぞれ歪緩和層47及び第1障壁層50の表面に偏析し、図4Fの工程で除去されたためであると考えられる。

【0064】

Sbを除去するためのアニールは、相対的に厚い第2障壁層51(図4G)を形成する前に、相対的に薄い第1障壁層50を形成した時点で行われる。このため、Sbを効率的に除去することができる。Sbを効率的に除去するために、第1障壁層50の厚さを10 nm以下にすることが好ましい。

【0065】

第1障壁層50を形成する前に、すなわち歪緩和層47(図4D)を形成した直後に、Sb除去のためのアニールを行うと、歪緩和層47内のInの再蒸発起こる。これに伴って、量子ドット42内のInが歪緩和層47内に拡散しやすくなり、量子ドット42の高さが低くなってしまう。量子ドット42の高さが低下する現象を防止するために、歪緩和層47と第1障壁層50との合計の厚さを、量子ドット42の高さ以上にすることが好ましい。

【0066】

上記実施例では、図4Cに示したアニール工程で、As2及びSbの分子線を照射したが、As2分子線のみを照射してもよい。As2分子線のみを照射する場合にも、図5Bに示したように、PL波長の長波長化の効果が得られる。

【0067】

図3の時刻t1〜t5、及びt6〜t11の間に、As2分子線を基板に照射すると、チャンバ10(図1)の内壁や、チャンバ10内の種々の測定器に、Asが付着しやすくなる。従って、クリーニング等のメンテナンス周期を短くしなければならない。このため、時刻t1〜t5、及びt6〜t11の間には、As2分子線ではなく、As4分子線を基板に照射することが好ましい。

【0068】

上記実施例では、図4Cの工程でアニールを行い、過剰なAs及びSbを量子ドット層43の表面に付着させることにより、量子ドット42の高さの減少を抑制した。量子ドットの成長速度を遅くすることによっても、量子ドットの寸法を大きくすることが可能である。ただし、成長速度を遅くすると、量子ドットの面内分布密度が低下してしまう。

【0069】

上記実施例による方法を適用することにより、量子ドットの高さの低下を抑制し、かつ量子ドットの面内分布密度の低下も抑制することができる。実施例による方法では、例えば、 面内分布密度が5×1010cm−2以上になり、かつ各々の量子ドットの高さが6nm〜8nmの範囲内である半導体装置を製造することが可能である。従来の方法を用いて量子ドットの高さを6nm〜8nmにすると、面内分布密度が5×1010cm−2よりも低くなってしまう。

【0070】

図8A及び図8Bに、上記実施例による方法を用いて製造されるレーザダイオードの断面図を示す。図8Aは、レーザ光の伝搬方向に平行な断面図を示し、図8Bは、レーザ光の伝搬方向に垂直な断面図を示す。

【0071】

以下、レーザダイオードの製造方法について説明する。(100)面が露出したn+型GaAs基板60の上に、n+型GaAsからなる厚さ400nm〜500nmのバッファ層61を形成する。バッファ層61の上に、n+型AlGaAsからなる厚さ約1300nmの下側クラッド層62を形成する。下側クラッド層62の上に、n型GaAsからなる厚さ約10nmの下側導波層63を形成する。下側導波層63の上に、厚さ約20nmのアンドープGaAs層64を形成する。これらの層は、例えば基板温度580℃の条件で、MBEにより形成される。

【0072】

アンドープGaAs層64の上に、活性層65を形成する。活性層65の形成は、図4Bに示した量子ドット層43の形成から図4Gに示した第2障壁層51の形成までの工程と同一である。なお、第2障壁層51の厚さは、例えば20nmに設定される。この工程を、合計で10回繰り返すことにより、活性層65が形成される。すなわち、活性層65は、図4Gに示した単位積層構造55を10層積み重ねることにより形成される。

【0073】

活性層65の上に、厚さ約20nmのアンドープGaAs層66を形成する。アンドープGaAs層66の上に、p型GaAsからなる厚さ約20nmの上側導波層67を形成する。上側導波層67の上に、p+型AlGaAsからなる厚さ約1300nmの上側クラッド層68を形成する。上側クラッド層68の上に、p+型GaAsからなる厚さ約50nmのキャップ層69を形成する。これらの層は、基板温度580℃の条件で、MBEにより形成される。

【0074】

図8Bに示すように、キャップ層69から下側クラッド層62までを、バッファ層61が露出するまでメサエッチングすることにより、メサ72を形成する。メサエッチング後、バッファ層61の表面、及びメサ72の表面を、SiNからなる保護膜70で覆う。この保護膜70に、電極を形成するための複数の開口を形成する。開口内に、バッファ層61の一部、及びキャップ層69の一部が露出する。開口内に露出したキャップ層69及びバッファ層61の上に、それぞれ電極71を形成する。電極形成後、基板60をレーザダイオードごとに個片化する。

【0075】

図8Aに示すように、一方の端面に高反射膜73を形成し、他方の端面に低反射膜74を形成する。これにより、1.3μm帯のレーザダイオードが完成する。活性層65の形成に、上記実施例による方法を適用するため、活性層65内のミスフィット転位の発生が抑制される。このため、高品質なレーザダイオードが得られる。

【0076】

なお、下側クラッド層62と下側導波層63との間に、回折格子を配置することにより、分布帰還型レーザダイオードを作製することもできる。また、図8Aに示した一対の端面の両方に、低反射膜を形成することにより、光増幅器とすることもできる。

【0077】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0078】

10 チャンバ

11 ステージ

12 ビーム強度計

13 温度測定器

14 排気管

15 RHEED測定器

15A 電子銃

15B 検出器

16 ヒータ

20 原料供給装置

21 供給量制御部

25 制御装置

28 基板

30 原料貯蔵部

31 金属砒素

32 ヒータ

33 輸送チューブ

34 ヒータ

35 クラッキング部

36 ヒータ

40 バッファ層

41 濡れ層

42 量子ドット

43 量子ドット層

45 過剰付着層

47 歪緩和層

50 第1障壁層

51 第2障壁層

55 単位積層構造

60 GaAs基板

61 バッファ層

62 下側クラッド層

63 下側導波層

64 アンドープGaAs層

65 活性層

66 アンドープGaAs層

67 上側導波層

68 上側クラッド層

69 キャップ層

70 保護膜

71 電極

72 メサ

【特許請求の範囲】

【請求項1】

チャンバ内に単結晶基板を装填し、前記単結晶基板上に、分子線エピタキシにより、In及びAsを含む量子ドットを形成する工程と、

前記チャンバ内で、前記量子ドットに、少なくともAs2分子線を照射しながら第1アニールを行う工程と

を有する半導体装置の製造方法。

【請求項2】

前記第1アニールを行う工程において、さらに、Sb分子線を照射しながらアニールを行う請求項1に記載の半導体装置の製造方法。

【請求項3】

前記量子ドットを形成する工程では、Asの原料としてAs4分子線を、前記単結晶基板に照射する請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記第1のアニールの後、前記チャンバ内において、分子線エピタキシにより、前記量子ドットを覆うように、前記単結晶基板の上に、前記単結晶基板の格子定数と前記量子ドットの格子定数との中間の格子定数を持つ半導体からなる歪緩和層を形成する工程と、

前記歪緩和層の上に、前記単結晶基板に格子整合する半導体からなる第1障壁層を、分子線エピタキシにより形成する工程と、

前記第1障壁層を形成した後、前記第1障壁層にAs4分子線を照射しながら、前記単結晶基板を昇温させて、第2アニールを行う工程と、

前記第2アニールの後、前記第1障壁層の上に、前記第1障壁層と同一の半導体材料からなる第2障壁層を、分子線エピタキシにより形成する工程と

を、さらに有する請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

単結晶基板の上に、面内分布密度が5×1010cm−2以上になるように分布し、各々の高さが6nm〜8nmの範囲内である複数の量子ドットと、

前記量子ドットを覆うように、前記単結晶基板の上に形成され、前記量子ドットよりもバンドギャップが大きく、前記単結晶基板の格子定数と前記量子ドットの格子定数との中間の格子定数を有する半導体材料からなる歪緩和層と

を有する半導体装置。

【請求項1】

チャンバ内に単結晶基板を装填し、前記単結晶基板上に、分子線エピタキシにより、In及びAsを含む量子ドットを形成する工程と、

前記チャンバ内で、前記量子ドットに、少なくともAs2分子線を照射しながら第1アニールを行う工程と

を有する半導体装置の製造方法。

【請求項2】

前記第1アニールを行う工程において、さらに、Sb分子線を照射しながらアニールを行う請求項1に記載の半導体装置の製造方法。

【請求項3】

前記量子ドットを形成する工程では、Asの原料としてAs4分子線を、前記単結晶基板に照射する請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記第1のアニールの後、前記チャンバ内において、分子線エピタキシにより、前記量子ドットを覆うように、前記単結晶基板の上に、前記単結晶基板の格子定数と前記量子ドットの格子定数との中間の格子定数を持つ半導体からなる歪緩和層を形成する工程と、

前記歪緩和層の上に、前記単結晶基板に格子整合する半導体からなる第1障壁層を、分子線エピタキシにより形成する工程と、

前記第1障壁層を形成した後、前記第1障壁層にAs4分子線を照射しながら、前記単結晶基板を昇温させて、第2アニールを行う工程と、

前記第2アニールの後、前記第1障壁層の上に、前記第1障壁層と同一の半導体材料からなる第2障壁層を、分子線エピタキシにより形成する工程と

を、さらに有する請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

単結晶基板の上に、面内分布密度が5×1010cm−2以上になるように分布し、各々の高さが6nm〜8nmの範囲内である複数の量子ドットと、

前記量子ドットを覆うように、前記単結晶基板の上に形成され、前記量子ドットよりもバンドギャップが大きく、前記単結晶基板の格子定数と前記量子ドットの格子定数との中間の格子定数を有する半導体材料からなる歪緩和層と

を有する半導体装置。

【図1】

【図2】

【図3】

【図4−1】

【図4−2】

【図5】

【図7】

【図8】

【図6】

【図2】

【図3】

【図4−1】

【図4−2】

【図5】

【図7】

【図8】

【図6】

【公開番号】特開2013−8925(P2013−8925A)

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願番号】特願2011−142057(P2011−142057)

【出願日】平成23年6月27日(2011.6.27)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願日】平成23年6月27日(2011.6.27)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]