半導体装置の製造方法

【課題】凹部内の配線におけるボイドを減少させることが可能であり、かつ配線の信頼性を確保することが可能な半導体装置の製造方法を提供する。

【解決手段】めっき膜4上に、めっき膜4を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質からなる圧縮応力印加膜5を形成し、圧縮応力印加膜5によりめっき膜4に圧縮応力を印加しながら熱処理を施す。

【解決手段】めっき膜4上に、めっき膜4を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質からなる圧縮応力印加膜5を形成し、圧縮応力印加膜5によりめっき膜4に圧縮応力を印加しながら熱処理を施す。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の配線としては、配線抵抗の低減、配線不良の原因となるエレクトロマイグレーション(EM)及びストレスマイグレーション(SM)等のマイグレーションの耐性向上のために、Alの代わりにCuが用いられている。

【0003】

Cuは、AlのようなRIE(反応性イオンエッチング)による加工が困難であるため、Cuで配線を形成するには、絶縁膜の表面に予め溝やホールからなる凹部を形成しておき、その溝やホールにCuを埋め込み、その後CMP(化学的機械的研磨)により不要なCuを除去して配線を形成するダマシン法が用いられている。

【0004】

ダマシン法におけるCuの埋め込み方法としては、主にめっき法が用いられている。現在、めっき法を使用したCuの埋め込みにおいては、微細構造をボイド(空隙)無く埋め込むために様々な努力がなされている。例えば、微細部分にめっきが優先的に施されるような添加剤をめっき液中に含ませることにより、溝やホールの底面から成長させている(いわゆるボトムアップ成長)。

【0005】

しかしながら、Cuの断面観察等により完全にCuが埋め込まれた場合であってもCu中に微小な空孔が形成されており、めっき工程後の熱処理工程においてCu粒径が大きくなるとともに空孔が集結してボイドが形成されることがある。ここで、熱処理温度を下げることや熱処理時間を短くすることにより、この現象を回避することが可能であるが、粒成長が十分に行われないため、信頼性試験において配線に不良が発生してしまう。

【0006】

なお、めっき銅膜上にTi,Zr,及びW等の異種元素を含んだバイアススパッタ銅含有金属膜を形成する技術が開示されている(例えば特許文献1参照)。ここで、バイアススパッタ銅含有金属膜に対する異種元素の含有率は極めて低く、また異種元素はめっき銅膜中に拡散させるために使用されるものである。

【特許文献1】特開2004−40022号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、上記課題を解決するためになされたものである。即ち、凹部内の配線におけるボイドを減少させることが可能であり、かつ配線の信頼性を確保することが可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一の態様によれば、表面に凹部を有する基板上に、前記凹部に埋め込まれるようにめっき法によりめっき膜を形成する工程と、前記めっき膜上に、前記めっき膜を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質からなる圧縮応力印加膜を形成する工程と、前記圧縮応力印加膜により前記めっき膜に圧縮応力を印加しながら熱処理を施す工程と、前記圧縮応力印加膜及び前記凹部に埋め込まれた部分以外の前記めっき膜を除去する工程とを具備することを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0009】

本発明の一の態様によれば、めっき膜上に圧縮応力印加膜を形成した状態で熱処理を施すことにより、凹部内の配線におけるボイドを減少させることができ、かつ配線の信頼性を確保することができる。

【発明を実施するための最良の形態】

【0010】

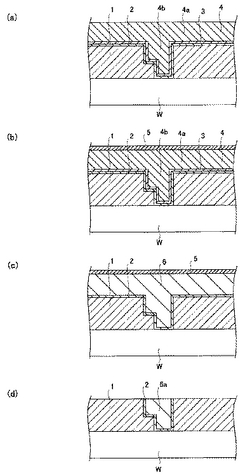

以下、図面を参照して、本発明の実施の形態を説明する。以下の図面において、同一の部材には同一の符号を付している。図1は本実施の形態に係る半導体装置の製造プロセスの流れを示したフローチャートであり、図2(a)〜図3(c)は本実施の形態に係る半導体装置の模式的な製造プロセス図である。

【0011】

図1及び図2(a)に示されるように、図示しない半導体素子等が形成された半導体ウェハW(以下、単に「ウェハ」という。)上に、例えば化学気相成長法(Chemical Vapor Deposition:CVD)或いは塗布法により層間絶縁膜1を形成する(ステップ1)。層間絶縁膜1の構成材料としては、例えば、有機Si酸化膜、有機樹脂膜及びポーラスSi酸化膜等の低誘電率絶縁膜、SiO2膜等が挙げられる。

【0012】

層間絶縁膜1を形成した後、図2(b)に示されるようにフォトリソグラフィ技術及び反応性イオンエッチング(RIE)により層間絶縁膜1に、ビアホール1a及び配線溝1bからなる凹部を形成する(ステップ2)。

【0013】

ビアホール1a及び配線溝1bを形成するには、まず、層間絶縁膜1上にレジストパターンを形成し、その後レジストパターンをマスクとして、RIEにより層間絶縁膜1をエッチングし、層間絶縁膜1にビアホール1aを形成する。層間絶縁膜1にビアホール1aを形成した後、アッシング等によりレジストパターンを除去する。その後、同様の手順により配線溝1bを形成する。なお、このような手順により、配線溝1bを形成した後にビアホール1aを形成することも可能である。

【0014】

層間絶縁膜1にビアホール1a及び配線溝1bを形成した後、図2(c)に示されるように層間絶縁膜1上に、例えばスパッタ法或いはCVD法により層間絶縁膜1への金属拡散を抑制するためのバリアメタル膜2を形成する(ステップ3)。バリアメタル膜2の構成材料としては、例えばTa、Ti、TaN、TiN、NbN、WN、或いはVN等の導電性材料が挙げられる。なお、これらの材料を積層したものからバリアメタル膜2を形成してもよい。

【0015】

層間絶縁膜1上にバリアメタル膜2を形成した後、図2(d)に示されるようにバリアメタル膜2上に、例えばスパッタ法により電解めっき時に電流を流すためのシード膜3を形成する(ステップ4)。シード膜3の構成材料としては、例えばCu等の金属が挙げられる。

【0016】

バリアメタル膜2上にシード膜3を形成した後、図3(a)に示されるようにシード膜3上に、例えば電解めっき法によりめっき膜4を形成する(ステップ5)。めっき膜4の構成材料としては、例えばCu等の金属が挙げられる。めっき膜4はビアホール1a及び配線溝1bの全体に埋め込まれるように形成される。

【0017】

めっき膜4の厚さは、ビアホール1a及び配線溝1bからなる凹部の外部で層間絶縁膜1上に形成されるめっき膜4の部分4a(以下、この部分を「積み増し部」と称する。)において、200nm以上であることが好ましい。これは、めっき膜4の厚さが200nm未満であると、ビアホール1a内及び配線溝1b内のめっき膜4の部分4b(以下、この部分を「配線構成部」と称する。)上における積み増し部4aの体積が小さく、めっき膜4に圧縮応力を印加しても積み増し部4aから配線構成部4bへの原子移動を促進する効果が小さくなるからである。

【0018】

めっき膜4を形成した後、図3(b)に示されるようにめっき膜4上に、例えばスパッタ法、めっき法、或いは蒸着法等の室温付近の温度或いは無加熱で行われる成膜方法によりめっき膜4に圧縮応力を印加する圧縮応力印加膜5を形成する(ステップ6)。圧縮応力印加膜5は、めっき膜4を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質から構成されている。

【0019】

圧縮応力印加膜5は、このような熱膨張率を有するTi、Zr、Nb、Mo、Ta、W、及びそれらの炭化物、それらの窒化物、Siの炭化物、Siの窒化物、並びにC(炭素)等から構成することが可能である。具体的には、めっき膜4を構成する金属にもよるが、例えばめっき膜4をCuから構成した場合には、圧縮応力印加膜5を例えば、Ti、Zr、Nb、Mo、Ta、W、SiC、及びSiNの少なくともいずれかから構成することが可能である。ここで、圧縮応力印加膜5をTaから構成した場合には、めっき膜4に対して拡散し難いという利点を有する。また、圧縮応力印加膜5をSiC及びSiNのいずれかから構成した場合には、めっき膜4に対する密着性が高くかつ拡散し難いという利点を有する。なお、本実施の形態での「熱膨張率」とは室温〜400℃における熱膨張率を意味する。圧縮応力印加膜5の厚さは、めっき膜4に圧縮応力を印加することができる厚さであれば十分であるが、膜厚が大き過ぎると後述する熱処理中に剥離するおそれが生じるため、20nm以上100nm以下程度が好ましい。

【0020】

圧縮応力印加膜5を形成した後、めっき膜4及び圧縮応力印加膜5等に熱処理(アニール)を施し、シード膜3及びめっき膜4の結晶を成長させて、図3(c)に示されるように配線膜6を形成する(ステップ7)。

【0021】

ウェハWに熱処理を施した後、例えば化学的機械的研磨(Chemical Mechanical Polishing:CMP)により研磨して、ビアホール1a及び配線溝1b内に存在するバリアメタル膜2、配線膜6がそれぞれ残るように、圧縮応力印加膜5並びに層間絶縁膜1上の不要なバリアメタル膜2及び配線膜6をそれぞれ除去する(ステップ8)。具体的には、ウェハWを研磨パッド(図示せず)に接触させた状態で、ウェハW及び研磨パッドを回転させるとともにウェハW上にスラリ(図示せず)を供給して、配線膜6等を研磨する。なお、CMPで研磨する場合に限らず、その他の手法で研磨してもよい。その他の手法としては、例えば電解研磨が挙げられる。これにより、図3(d)に示されるようにビアホール1a及び配線溝1b内に配線6aが形成される。

【0022】

本実施の形態では、めっき膜4を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質から構成された圧縮応力印加膜5をめっき膜4上に形成した状態で、めっき膜4及び圧縮応力印加膜5に熱処理を施すので、配線6aにおけるボイドを減少させることができるとともに配線6aの信頼性を確保することができる。即ち、めっき膜4上に圧縮応力印加膜5を形成した状態で、めっき膜4及び圧縮応力印加膜5に熱処理を施すと、めっき膜4を構成している金属と圧縮応力印加膜5を構成している物質の熱膨張率の差から積み増し部4aに圧縮応力が印加され、積み増し部4aを構成している原子が配線構成部4bに拡散しようとする。これにより、配線構成部4bに存在する空孔が押し出され、積み増し部4aに向かって排出される。それ故、配線6aにおけるボイドを減少させることができる。

【0023】

ここで、この効果は、めっき膜4を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質から圧縮応力印加膜5を構成した場合に顕著に得られる。さらに、熱処理を高い温度で行った場合は、この効果を格別顕著に得ることができるので、本実施の形態では熱処理を、めっき膜4を構成している金属の結晶成長を進行させるうえで最適な温度、例えば200℃以上で好ましくは400℃以下の温度で行うことができる。これにより、配線6aの信頼性を確保することができる。なお、特許文献1に記載されているように異種元素を含むバイアススパッタ銅含有金属膜をめっき膜4上に形成した場合には、バイアススパッタ銅含有金属膜に対する異種元素の含有率が極めて低いために、めっき膜4に有効な圧縮応力を印加することができないものと考えられる。

【0024】

本実施の形態では、めっき膜4はビアホール1a及び配線溝1b全体に埋め込まれるように形成されるので、熱処理時にめっき膜4に圧縮応力印加膜5を構成している物質が拡散した場合であっても、配線構成部4b中に到達し難い。これにより、配線抵抗の上昇を抑制することができる。

【0025】

本実施の形態では、圧縮応力印加膜5が室温付近の温度或いは無加熱で形成されるので、より大きな圧縮応力をめっき膜4に印加することができる。即ち、熱処理温度におけるめっき膜4と圧縮応力印加膜5の熱膨張差が大きいほど、めっき膜4に印加される圧縮応力は大きくなる。一方、温度を上昇させると、圧縮応力印加膜5は圧縮応力印加膜5を構成している物質の熱膨張率に基づいて膨張していくので、圧縮応力印加膜5の成膜温度が低いほど熱処理温度におけるめっき膜4との熱膨張差は大きくなる。従って、圧縮応力印加膜5の成膜温度が低いほど、熱処理時にめっき膜4に印加される圧縮応力は大きくなる。本実施の形態では、圧縮応力印加膜5を室温付近の温度或いは無加熱で形成するので、圧縮応力印加膜5を高い温度で形成するよりも、より大きな圧縮応力をめっき膜4に印加することができる。

【0026】

(実施例1)

以下、実施例1について説明する。本実施例においては、上記実施の形態の手法により形成され、かつ異なる熱処理温度で熱処理された配線を有するウェハを熱処理温度毎にそれぞれ3枚ずつ用意し、それぞれについて配線中の欠陥密度を欠陥検査装置により測定するとともに配線の信頼性試験を行った。本実施例においては、めっき膜をCuから構成し、圧縮応力印加膜をTaから構成した。圧縮応力印加膜はスパッタ法により50nmの厚さに形成された。Cuの室温における熱膨張率は16.7×10−6/℃であり、Taの室温における熱膨張率は7.1×10−6/℃であるので、Cuの熱膨張率に対しTaの熱膨張率は42.5%となっている。熱処理は、150℃、200℃、250℃、及び300℃でそれぞれ1時間行われた。なお、実施例と比較するために比較例として、圧縮応力印加膜を形成せずに配線を形成した例についても実施例と同様に欠陥密度を測定するとともに信頼性試験を行った。

【0027】

以下、結果を述べる。表1は実施例及び比較例に係る熱処理温度と配線中の欠陥密度を表したものである。なお、表1中における数値は、ウェハ1枚あたりの欠陥密度の平均値である。

【表1】

【0028】

表1に示されるように比較例においては熱処理温度が上昇するほど、欠陥密度が増大していたが、実施例においては熱処理温度が上昇しても、欠陥密度はほぼ変化しなかった。一方、信頼性試験は配線が不良となるまで行われたが、実施例及び比較例とともに熱処理温度が上昇するほど、不良となるまでの時間が長かった。これらの結果から、めっき膜上にTaから構成された圧縮応力印加膜を形成した場合には、欠陥数の減少と信頼性の確保との両立が可能であることが確認された。

【0029】

(実施例2)

以下、実施例2について説明する。本実施例においても、実施例1と同様の手法により配線中の欠陥密度を測定するとともに配線の信頼性試験を行った。本実施例においては、めっき膜をCuから構成し、圧縮応力印加膜をSiCから構成し、スパッタ法により形成した。SiCの室温における熱膨張率は4.9×10−6/℃であるので、Cuの熱膨張率に対してSiCの熱膨張率は29.3%となっている。

【0030】

以下、結果について述べる。本実施例においても、実施例1と同様に熱処理温度が上昇しても、欠陥密度はほぼ変化しなかった。また、実施例1と同様に熱処理温度が上昇するほど、不良となるまでの時間が長かった。これらの結果から、めっき膜上にSiCから構成された圧縮応力印加膜を形成した場合には、欠陥数の減少と信頼性の確保との両立が可能であることが確認された。

【0031】

(実施例3)

以下、実施例3について説明する。本実施例においても、実施例1と同様の手法により配線中の欠陥密度を測定するとともに配線の信頼性試験を行った。本実施例においては、めっき膜をCuから構成し、圧縮応力印加膜をTiから構成した。Tiの室温における熱膨張率は8.6×10−6/℃であるので、Cuの熱膨張率に対してTiの熱膨張率は51.5%となっている。

【0032】

以下、結果について述べる。本実施例においても、実施例1と同様に熱処理温度が上昇しても、欠陥密度はほぼ変化しなかった。また、実施例1と同様に熱処理温度が上昇するほど、不良となるまでの時間が長かった。これらの結果から、めっき膜上にTiから構成された圧縮応力印加膜を形成した場合には、欠陥数の減少と信頼性の確保との両立が可能であることが確認された。

【0033】

なお、本発明は上記実施の形態の記載内容に限定されるものではなく、構造や材質、各部材の配置等は、本発明の要旨を逸脱しない範囲で適宜変更可能である。

【図面の簡単な説明】

【0034】

【図1】実施の形態に係る半導体装置の製造プロセスの流れを示したフローチャートである。

【図2】(a)〜(c)は実施の形態に係る半導体装置の模式的な製造プロセス図である。

【図3】(a)〜(c)は実施の形態に係る半導体装置の模式的な製造プロセス図である。

【符号の説明】

【0035】

W…ウェハ、1a…ビアホール、1b…配線溝、4…めっき膜、5…圧縮応力印加膜、6a…配線。

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の配線としては、配線抵抗の低減、配線不良の原因となるエレクトロマイグレーション(EM)及びストレスマイグレーション(SM)等のマイグレーションの耐性向上のために、Alの代わりにCuが用いられている。

【0003】

Cuは、AlのようなRIE(反応性イオンエッチング)による加工が困難であるため、Cuで配線を形成するには、絶縁膜の表面に予め溝やホールからなる凹部を形成しておき、その溝やホールにCuを埋め込み、その後CMP(化学的機械的研磨)により不要なCuを除去して配線を形成するダマシン法が用いられている。

【0004】

ダマシン法におけるCuの埋め込み方法としては、主にめっき法が用いられている。現在、めっき法を使用したCuの埋め込みにおいては、微細構造をボイド(空隙)無く埋め込むために様々な努力がなされている。例えば、微細部分にめっきが優先的に施されるような添加剤をめっき液中に含ませることにより、溝やホールの底面から成長させている(いわゆるボトムアップ成長)。

【0005】

しかしながら、Cuの断面観察等により完全にCuが埋め込まれた場合であってもCu中に微小な空孔が形成されており、めっき工程後の熱処理工程においてCu粒径が大きくなるとともに空孔が集結してボイドが形成されることがある。ここで、熱処理温度を下げることや熱処理時間を短くすることにより、この現象を回避することが可能であるが、粒成長が十分に行われないため、信頼性試験において配線に不良が発生してしまう。

【0006】

なお、めっき銅膜上にTi,Zr,及びW等の異種元素を含んだバイアススパッタ銅含有金属膜を形成する技術が開示されている(例えば特許文献1参照)。ここで、バイアススパッタ銅含有金属膜に対する異種元素の含有率は極めて低く、また異種元素はめっき銅膜中に拡散させるために使用されるものである。

【特許文献1】特開2004−40022号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、上記課題を解決するためになされたものである。即ち、凹部内の配線におけるボイドを減少させることが可能であり、かつ配線の信頼性を確保することが可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一の態様によれば、表面に凹部を有する基板上に、前記凹部に埋め込まれるようにめっき法によりめっき膜を形成する工程と、前記めっき膜上に、前記めっき膜を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質からなる圧縮応力印加膜を形成する工程と、前記圧縮応力印加膜により前記めっき膜に圧縮応力を印加しながら熱処理を施す工程と、前記圧縮応力印加膜及び前記凹部に埋め込まれた部分以外の前記めっき膜を除去する工程とを具備することを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0009】

本発明の一の態様によれば、めっき膜上に圧縮応力印加膜を形成した状態で熱処理を施すことにより、凹部内の配線におけるボイドを減少させることができ、かつ配線の信頼性を確保することができる。

【発明を実施するための最良の形態】

【0010】

以下、図面を参照して、本発明の実施の形態を説明する。以下の図面において、同一の部材には同一の符号を付している。図1は本実施の形態に係る半導体装置の製造プロセスの流れを示したフローチャートであり、図2(a)〜図3(c)は本実施の形態に係る半導体装置の模式的な製造プロセス図である。

【0011】

図1及び図2(a)に示されるように、図示しない半導体素子等が形成された半導体ウェハW(以下、単に「ウェハ」という。)上に、例えば化学気相成長法(Chemical Vapor Deposition:CVD)或いは塗布法により層間絶縁膜1を形成する(ステップ1)。層間絶縁膜1の構成材料としては、例えば、有機Si酸化膜、有機樹脂膜及びポーラスSi酸化膜等の低誘電率絶縁膜、SiO2膜等が挙げられる。

【0012】

層間絶縁膜1を形成した後、図2(b)に示されるようにフォトリソグラフィ技術及び反応性イオンエッチング(RIE)により層間絶縁膜1に、ビアホール1a及び配線溝1bからなる凹部を形成する(ステップ2)。

【0013】

ビアホール1a及び配線溝1bを形成するには、まず、層間絶縁膜1上にレジストパターンを形成し、その後レジストパターンをマスクとして、RIEにより層間絶縁膜1をエッチングし、層間絶縁膜1にビアホール1aを形成する。層間絶縁膜1にビアホール1aを形成した後、アッシング等によりレジストパターンを除去する。その後、同様の手順により配線溝1bを形成する。なお、このような手順により、配線溝1bを形成した後にビアホール1aを形成することも可能である。

【0014】

層間絶縁膜1にビアホール1a及び配線溝1bを形成した後、図2(c)に示されるように層間絶縁膜1上に、例えばスパッタ法或いはCVD法により層間絶縁膜1への金属拡散を抑制するためのバリアメタル膜2を形成する(ステップ3)。バリアメタル膜2の構成材料としては、例えばTa、Ti、TaN、TiN、NbN、WN、或いはVN等の導電性材料が挙げられる。なお、これらの材料を積層したものからバリアメタル膜2を形成してもよい。

【0015】

層間絶縁膜1上にバリアメタル膜2を形成した後、図2(d)に示されるようにバリアメタル膜2上に、例えばスパッタ法により電解めっき時に電流を流すためのシード膜3を形成する(ステップ4)。シード膜3の構成材料としては、例えばCu等の金属が挙げられる。

【0016】

バリアメタル膜2上にシード膜3を形成した後、図3(a)に示されるようにシード膜3上に、例えば電解めっき法によりめっき膜4を形成する(ステップ5)。めっき膜4の構成材料としては、例えばCu等の金属が挙げられる。めっき膜4はビアホール1a及び配線溝1bの全体に埋め込まれるように形成される。

【0017】

めっき膜4の厚さは、ビアホール1a及び配線溝1bからなる凹部の外部で層間絶縁膜1上に形成されるめっき膜4の部分4a(以下、この部分を「積み増し部」と称する。)において、200nm以上であることが好ましい。これは、めっき膜4の厚さが200nm未満であると、ビアホール1a内及び配線溝1b内のめっき膜4の部分4b(以下、この部分を「配線構成部」と称する。)上における積み増し部4aの体積が小さく、めっき膜4に圧縮応力を印加しても積み増し部4aから配線構成部4bへの原子移動を促進する効果が小さくなるからである。

【0018】

めっき膜4を形成した後、図3(b)に示されるようにめっき膜4上に、例えばスパッタ法、めっき法、或いは蒸着法等の室温付近の温度或いは無加熱で行われる成膜方法によりめっき膜4に圧縮応力を印加する圧縮応力印加膜5を形成する(ステップ6)。圧縮応力印加膜5は、めっき膜4を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質から構成されている。

【0019】

圧縮応力印加膜5は、このような熱膨張率を有するTi、Zr、Nb、Mo、Ta、W、及びそれらの炭化物、それらの窒化物、Siの炭化物、Siの窒化物、並びにC(炭素)等から構成することが可能である。具体的には、めっき膜4を構成する金属にもよるが、例えばめっき膜4をCuから構成した場合には、圧縮応力印加膜5を例えば、Ti、Zr、Nb、Mo、Ta、W、SiC、及びSiNの少なくともいずれかから構成することが可能である。ここで、圧縮応力印加膜5をTaから構成した場合には、めっき膜4に対して拡散し難いという利点を有する。また、圧縮応力印加膜5をSiC及びSiNのいずれかから構成した場合には、めっき膜4に対する密着性が高くかつ拡散し難いという利点を有する。なお、本実施の形態での「熱膨張率」とは室温〜400℃における熱膨張率を意味する。圧縮応力印加膜5の厚さは、めっき膜4に圧縮応力を印加することができる厚さであれば十分であるが、膜厚が大き過ぎると後述する熱処理中に剥離するおそれが生じるため、20nm以上100nm以下程度が好ましい。

【0020】

圧縮応力印加膜5を形成した後、めっき膜4及び圧縮応力印加膜5等に熱処理(アニール)を施し、シード膜3及びめっき膜4の結晶を成長させて、図3(c)に示されるように配線膜6を形成する(ステップ7)。

【0021】

ウェハWに熱処理を施した後、例えば化学的機械的研磨(Chemical Mechanical Polishing:CMP)により研磨して、ビアホール1a及び配線溝1b内に存在するバリアメタル膜2、配線膜6がそれぞれ残るように、圧縮応力印加膜5並びに層間絶縁膜1上の不要なバリアメタル膜2及び配線膜6をそれぞれ除去する(ステップ8)。具体的には、ウェハWを研磨パッド(図示せず)に接触させた状態で、ウェハW及び研磨パッドを回転させるとともにウェハW上にスラリ(図示せず)を供給して、配線膜6等を研磨する。なお、CMPで研磨する場合に限らず、その他の手法で研磨してもよい。その他の手法としては、例えば電解研磨が挙げられる。これにより、図3(d)に示されるようにビアホール1a及び配線溝1b内に配線6aが形成される。

【0022】

本実施の形態では、めっき膜4を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質から構成された圧縮応力印加膜5をめっき膜4上に形成した状態で、めっき膜4及び圧縮応力印加膜5に熱処理を施すので、配線6aにおけるボイドを減少させることができるとともに配線6aの信頼性を確保することができる。即ち、めっき膜4上に圧縮応力印加膜5を形成した状態で、めっき膜4及び圧縮応力印加膜5に熱処理を施すと、めっき膜4を構成している金属と圧縮応力印加膜5を構成している物質の熱膨張率の差から積み増し部4aに圧縮応力が印加され、積み増し部4aを構成している原子が配線構成部4bに拡散しようとする。これにより、配線構成部4bに存在する空孔が押し出され、積み増し部4aに向かって排出される。それ故、配線6aにおけるボイドを減少させることができる。

【0023】

ここで、この効果は、めっき膜4を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質から圧縮応力印加膜5を構成した場合に顕著に得られる。さらに、熱処理を高い温度で行った場合は、この効果を格別顕著に得ることができるので、本実施の形態では熱処理を、めっき膜4を構成している金属の結晶成長を進行させるうえで最適な温度、例えば200℃以上で好ましくは400℃以下の温度で行うことができる。これにより、配線6aの信頼性を確保することができる。なお、特許文献1に記載されているように異種元素を含むバイアススパッタ銅含有金属膜をめっき膜4上に形成した場合には、バイアススパッタ銅含有金属膜に対する異種元素の含有率が極めて低いために、めっき膜4に有効な圧縮応力を印加することができないものと考えられる。

【0024】

本実施の形態では、めっき膜4はビアホール1a及び配線溝1b全体に埋め込まれるように形成されるので、熱処理時にめっき膜4に圧縮応力印加膜5を構成している物質が拡散した場合であっても、配線構成部4b中に到達し難い。これにより、配線抵抗の上昇を抑制することができる。

【0025】

本実施の形態では、圧縮応力印加膜5が室温付近の温度或いは無加熱で形成されるので、より大きな圧縮応力をめっき膜4に印加することができる。即ち、熱処理温度におけるめっき膜4と圧縮応力印加膜5の熱膨張差が大きいほど、めっき膜4に印加される圧縮応力は大きくなる。一方、温度を上昇させると、圧縮応力印加膜5は圧縮応力印加膜5を構成している物質の熱膨張率に基づいて膨張していくので、圧縮応力印加膜5の成膜温度が低いほど熱処理温度におけるめっき膜4との熱膨張差は大きくなる。従って、圧縮応力印加膜5の成膜温度が低いほど、熱処理時にめっき膜4に印加される圧縮応力は大きくなる。本実施の形態では、圧縮応力印加膜5を室温付近の温度或いは無加熱で形成するので、圧縮応力印加膜5を高い温度で形成するよりも、より大きな圧縮応力をめっき膜4に印加することができる。

【0026】

(実施例1)

以下、実施例1について説明する。本実施例においては、上記実施の形態の手法により形成され、かつ異なる熱処理温度で熱処理された配線を有するウェハを熱処理温度毎にそれぞれ3枚ずつ用意し、それぞれについて配線中の欠陥密度を欠陥検査装置により測定するとともに配線の信頼性試験を行った。本実施例においては、めっき膜をCuから構成し、圧縮応力印加膜をTaから構成した。圧縮応力印加膜はスパッタ法により50nmの厚さに形成された。Cuの室温における熱膨張率は16.7×10−6/℃であり、Taの室温における熱膨張率は7.1×10−6/℃であるので、Cuの熱膨張率に対しTaの熱膨張率は42.5%となっている。熱処理は、150℃、200℃、250℃、及び300℃でそれぞれ1時間行われた。なお、実施例と比較するために比較例として、圧縮応力印加膜を形成せずに配線を形成した例についても実施例と同様に欠陥密度を測定するとともに信頼性試験を行った。

【0027】

以下、結果を述べる。表1は実施例及び比較例に係る熱処理温度と配線中の欠陥密度を表したものである。なお、表1中における数値は、ウェハ1枚あたりの欠陥密度の平均値である。

【表1】

【0028】

表1に示されるように比較例においては熱処理温度が上昇するほど、欠陥密度が増大していたが、実施例においては熱処理温度が上昇しても、欠陥密度はほぼ変化しなかった。一方、信頼性試験は配線が不良となるまで行われたが、実施例及び比較例とともに熱処理温度が上昇するほど、不良となるまでの時間が長かった。これらの結果から、めっき膜上にTaから構成された圧縮応力印加膜を形成した場合には、欠陥数の減少と信頼性の確保との両立が可能であることが確認された。

【0029】

(実施例2)

以下、実施例2について説明する。本実施例においても、実施例1と同様の手法により配線中の欠陥密度を測定するとともに配線の信頼性試験を行った。本実施例においては、めっき膜をCuから構成し、圧縮応力印加膜をSiCから構成し、スパッタ法により形成した。SiCの室温における熱膨張率は4.9×10−6/℃であるので、Cuの熱膨張率に対してSiCの熱膨張率は29.3%となっている。

【0030】

以下、結果について述べる。本実施例においても、実施例1と同様に熱処理温度が上昇しても、欠陥密度はほぼ変化しなかった。また、実施例1と同様に熱処理温度が上昇するほど、不良となるまでの時間が長かった。これらの結果から、めっき膜上にSiCから構成された圧縮応力印加膜を形成した場合には、欠陥数の減少と信頼性の確保との両立が可能であることが確認された。

【0031】

(実施例3)

以下、実施例3について説明する。本実施例においても、実施例1と同様の手法により配線中の欠陥密度を測定するとともに配線の信頼性試験を行った。本実施例においては、めっき膜をCuから構成し、圧縮応力印加膜をTiから構成した。Tiの室温における熱膨張率は8.6×10−6/℃であるので、Cuの熱膨張率に対してTiの熱膨張率は51.5%となっている。

【0032】

以下、結果について述べる。本実施例においても、実施例1と同様に熱処理温度が上昇しても、欠陥密度はほぼ変化しなかった。また、実施例1と同様に熱処理温度が上昇するほど、不良となるまでの時間が長かった。これらの結果から、めっき膜上にTiから構成された圧縮応力印加膜を形成した場合には、欠陥数の減少と信頼性の確保との両立が可能であることが確認された。

【0033】

なお、本発明は上記実施の形態の記載内容に限定されるものではなく、構造や材質、各部材の配置等は、本発明の要旨を逸脱しない範囲で適宜変更可能である。

【図面の簡単な説明】

【0034】

【図1】実施の形態に係る半導体装置の製造プロセスの流れを示したフローチャートである。

【図2】(a)〜(c)は実施の形態に係る半導体装置の模式的な製造プロセス図である。

【図3】(a)〜(c)は実施の形態に係る半導体装置の模式的な製造プロセス図である。

【符号の説明】

【0035】

W…ウェハ、1a…ビアホール、1b…配線溝、4…めっき膜、5…圧縮応力印加膜、6a…配線。

【特許請求の範囲】

【請求項1】

表面に凹部を有する基板上に、前記凹部に埋め込まれるようにめっき法によりめっき膜を形成する工程と、

前記めっき膜上に、前記めっき膜を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質からなる圧縮応力印加膜を形成する工程と、

前記圧縮応力印加膜により前記めっき膜に圧縮応力を印加しながら熱処理を施す工程と、

前記圧縮応力印加膜及び前記凹部に埋め込まれた部分以外の前記めっき膜を除去する工程と

を具備することを特徴とする半導体装置の製造方法。

【請求項2】

前記めっき膜は、前記凹部の全体に埋め込まれるように形成されることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記めっき膜は、前記凹部の外部で前記基板上に形成される厚さが200nm以上であることを特徴とする請求項1又は2記載の半導体装置の製造方法。

【請求項4】

前記圧縮応力印加膜の膜厚は、20nm以上100nm以下であることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記圧縮応力印加膜は、Ti、Zr、Nb、Mo、Ta、W、及びそれらの炭化物、それらの窒化物、Siの炭化物、Siの窒化物、並びにCの少なくともいずれかを含んでいることを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

【請求項1】

表面に凹部を有する基板上に、前記凹部に埋め込まれるようにめっき法によりめっき膜を形成する工程と、

前記めっき膜上に、前記めっき膜を構成している金属の熱膨張率に対して60%以下の熱膨張率を有する物質からなる圧縮応力印加膜を形成する工程と、

前記圧縮応力印加膜により前記めっき膜に圧縮応力を印加しながら熱処理を施す工程と、

前記圧縮応力印加膜及び前記凹部に埋め込まれた部分以外の前記めっき膜を除去する工程と

を具備することを特徴とする半導体装置の製造方法。

【請求項2】

前記めっき膜は、前記凹部の全体に埋め込まれるように形成されることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記めっき膜は、前記凹部の外部で前記基板上に形成される厚さが200nm以上であることを特徴とする請求項1又は2記載の半導体装置の製造方法。

【請求項4】

前記圧縮応力印加膜の膜厚は、20nm以上100nm以下であることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記圧縮応力印加膜は、Ti、Zr、Nb、Mo、Ta、W、及びそれらの炭化物、それらの窒化物、Siの炭化物、Siの窒化物、並びにCの少なくともいずれかを含んでいることを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2006−100698(P2006−100698A)

【公開日】平成18年4月13日(2006.4.13)

【国際特許分類】

【出願番号】特願2004−287089(P2004−287089)

【出願日】平成16年9月30日(2004.9.30)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成18年4月13日(2006.4.13)

【国際特許分類】

【出願日】平成16年9月30日(2004.9.30)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]