半導体装置の製造方法

【課題】 ファセット形状のない金属シリサイド層を形成し、ソース・ドレインとシリコン基板との間の接合リークを減少させる。

【解決手段】 シリコン基板1の上にソース・ドレイン5を形成し、その上にシリサイド化用金属膜(Ni膜)6、ストレス膜7を形成する。ストレス膜7としてTiN膜およびCo膜からなる積層膜を形成する。この状態でシリサイド化アニールを行うと、ストレス膜7は引っ張り応力10aを有する。この応力に対応するように、シリサイド化用金属膜6は圧縮応力10bを有する。

このようにしてシリサイド化用金属膜6をシリコン基板1とシリサイド化反応させることにより、反応速度が抑制される。このため、ファセット形状を有しないNiモノシリサイド層(NiSi)を形成することができる。これにより、ソース・ドレイン5とシリコン基板1との間の接合リーク電流を減少させることができる。

【解決手段】 シリコン基板1の上にソース・ドレイン5を形成し、その上にシリサイド化用金属膜(Ni膜)6、ストレス膜7を形成する。ストレス膜7としてTiN膜およびCo膜からなる積層膜を形成する。この状態でシリサイド化アニールを行うと、ストレス膜7は引っ張り応力10aを有する。この応力に対応するように、シリサイド化用金属膜6は圧縮応力10bを有する。

このようにしてシリサイド化用金属膜6をシリコン基板1とシリサイド化反応させることにより、反応速度が抑制される。このため、ファセット形状を有しないNiモノシリサイド層(NiSi)を形成することができる。これにより、ソース・ドレイン5とシリコン基板1との間の接合リーク電流を減少させることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置の製造方法に関し、特にトランジスタのソース・ドレインを低抵抗化するための金属シリサイド層の形成方法に関する。

【背景技術】

【0002】

SoC(システム・オン・チップ)デバイスの微細化に伴い、トランジスタのソース・ドレインを浅く形成することが要求されている。また、デバイスの高速化のために、ソース・ドレインを低抵抗化することが要求されている。これらの要求を満たすため、ソース・ドレインを浅く形成し、その表面に金属シリサイド層を設けた構造が用いられてきた。

例えば、特許文献1には、ソース・ドレインの表面にCo(コバルト)シリサイド層、Ni(ニッケル)シリサイド層などの金属シリサイド層を設けた構造が開示されている。

【0003】

ここで、従来の半導体装置の製造方法により、ソース・ドレインの表面に金属シリサイド層を形成する例について説明する。

まず、図25(a)に示すように、シリコン基板1の主面上に、ゲート絶縁膜2、ゲート電極3を形成する。次に、ゲート絶縁膜2、ゲート電極3の側面に、シリコン酸化膜からなるサイドウォール4を形成する。次に、シリコン基板1の表面に不純物を注入し、さらにシリコン基板1の熱処理を行う。この結果、図25(b)に示すように、ソース・ドレイン5が形成される。

【0004】

次に、図25(c)に示すように、全面にNi膜などのシリサイド化用金属膜6を成膜する。さらに、シリサイド化用金属膜6をシリコン基板1とシリサイド化反応させる。これと同時に、シリサイド化用金属膜6をゲート電極3とシリサイド化反応させる。このとき、シリコン基板1、ゲート電極3の上に未反応のシリサイド用金属膜が残留している。次に、未反応のシリサイド化用金属膜を除去する。この結果、図25(d)に示すように、ソース・ドレイン5の表面にNiモノシリサイド(NiSi)層8aが露出し、ゲート電極3の表面にNiモノシリサイド(NiSi)層8bが露出する。

【0005】

【特許文献1】特開2003−37083号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

上記従来の半導体装置の製造方法において、シリサイド化用金属膜6をシリコン基板1とシリサイド化反応させる際に、シリサイド化反応が局所的に速く進むことがある。この場合、図26に示すように、ソース・ドレイン5の表面にファセット形状25を有する金属シリサイド層8aが形成される。このファセット形状は、ソース・ドレイン5とシリコン基板1との間の接合リーク電流を増加させる。

【0007】

本発明は上記課題を解決するためになされたもので、ソース・ドレインの表面にファセット形状のない金属シリサイド層を形成することにより、ソース・ドレインとシリコン基板との間の接合リークを減少させることを目的とする。

【課題を解決するための手段】

【0008】

本発明に係る半導体装置の製造方法は、シリコン基板上に、前記シリコン基板とシリサイド化反応を生じさせる第1の金属膜を形成する工程と、前記第1の金属膜に引っ張り応力のストレスを印加しながら、前記第1の金属膜を前記シリコン基板とシリサイド化反応させる第1工程とを含むことを特徴とする。

本発明のその他の特徴については、以下において詳細に説明する。

【発明の効果】

【0009】

本発明によれば、ファセット形状のない金属シリサイド層をソース・ドレインの表面に形成することができる。これにより、ソース・ドレインとシリコン基板との間の接合リークを減少させることができる。

【発明を実施するための最良の形態】

【0010】

以下、図面を参照しながら本発明の実施の形態について説明する。なお、各図において同一または相当する部分には同一符号を付して、その説明を簡略化ないし省略する。

【0011】

実施の形態1.

図1〜図8は、本実施の形態に係る半導体装置の製造方法を示す工程断面図である。

本実施の形態で形成する半導体装置は、図1に示すシリコン基板1の主面上に形成される。まず、図示しないが、シリコン基板1の表面に素子分離を形成する。次に、シリコン基板1の主面上にゲート絶縁膜2、ゲート電極3を形成する。ゲート絶縁膜2としては、例えば、2〜3nm程度の膜厚のシリコン酸化膜を形成する。ゲート電極3としては、例えば、100〜150nm程度の膜厚の多結晶シリコン膜を形成する。

次に、シリコン基板1の上に、化学気相成長法(Chemical Vapor Deposition;CVD法)などにより全面にシリコン酸化膜を形成する。さらに、このシリコン酸化膜を全面エッチバックする。この結果、図1に示すように、ゲート絶縁膜2、ゲート電極3の側面に、サイドウォール4が形成される。

【0012】

次に、図1に示したゲート電極3、サイドウォール4をマスクとして、シリコン基板1の表面に不純物をイオン注入する。さらに、シリコン基板1を熱処理する。この結果、図2に示すように、シリコン基板1の表面にソース・ドレイン5が形成される。

【0013】

次に、図3に示すように、シリコン基板1の上に、全面にシリサイド化用金属膜6を形成する。この膜は、シリコン基板1とシリサイド化反応を生じさせる膜とする。例えば、Ni(ニッケル)膜を5〜10nm程度の膜厚で形成する。さらに、図4に示すように、シリサイド化用金属膜6の上にストレス膜7を形成する。例えば、TiN(窒化チタン)膜を5〜10nm程度の膜厚で成膜し、その上にCo(コバルト)膜を5〜10nm程度の膜厚で成膜した積層膜を形成する。この膜は、後の工程でシリサイド化用金属膜6をシリコン基板1とシリサイド化反応させる際に、その膜自身の内部に引っ張り応力を発生する膜(以下、その膜を「引っ張り応力を有する膜」という)である。(同様に、膜がその膜自身の内部に圧縮応力を発生する場合、その膜を「圧縮応力を有する膜」と言う。)

【0014】

次に、図4に示したシリコン基板1を熱処理して、シリサイド化用金属膜6をシリコン基板1とシリサイド化反応させる。これと同時に、シリサイド化用金属膜6をゲート電極3とシリサイド化反応させる。

上記シリサイド化反応させる熱処理(以下、「シリサイド化アニール」という)は、例えば100〜450℃程度の温度のランプアニールとする。上記の温度で熱処理することにより、シリサイド化用金属膜(ニッケル膜)6をシリコン基板1およびゲート電極3とシリサイド化反応させることができる。

【0015】

上記シリサイド化反応の結果、図5に示すように、ソース・ドレイン5の表面にNiモノシリサイド(NiSi)層8aが形成される。また、ゲート電極3の表面にNiモノシリサイド(NiSi)層8bが形成される。このとき、これらのシリサイド化反応により消費されなかったシリサイド化用金属膜6a(以下、「未反応のシリサイド化用金属膜6a」という)が、シリコン基板1、ゲート電極3、およびサイドウォール4の上に残留している。

【0016】

上記シリサイド化反応において、図5に示したNiモノシリサイド(NiSi)層8aは、ファセット形状25(図26参照)を有していない。この理由について説明する。一般に固相反応では、ストレスの存在により反応が異常に速く進んだり、逆に遅くなったりすることが知られている。従って、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制することが可能である。

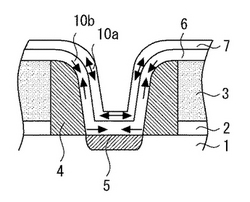

ここで、上記シリサイド化アニールを行う際の、図4に示した点線部分Aの拡大図を図6に示す。シリサイド化アニールを行う際には、ストレス膜7は、引っ張り応力10a(0.2GPa程度)を有している。これに対応するように、シリサイド化用金属膜6は、圧縮応力10b(0.2GPa程度)を有している。つまり、シリサイド化用金属膜6に引っ張り応力のストレスが与えられた状態で、シリサイド化アニールが行われている。

このようにシリサイド化アニールを行うことにより、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制することができる。これにより、ソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド(NiSi)層8aを形成することができる。

【0017】

次に、図5に示した未反応のシリサイド化用金属膜6a、およびその上のストレス膜7を薬液などにより除去する。この結果、図7に示すように、ソース・ドレイン5の表面にNiモノシリサイド層8aが露出し、ゲート電極3の表面にNiモノシリサイド層8bが露出する。

以上説明した製造方法により、シリコン基板1の主面上にトランジスタが形成される。さらに、図8に示すように、シリコン基板1の上に、シリコン酸化膜などの層間絶縁膜9を全面に成膜する。

【0018】

本実施の形態では、シリサイド化用金属膜6としてNi膜を用いるようにした。シリサイド化用金属膜6は、Ti(チタン)膜、Co(コバルト)膜、W(タングステン)膜などの膜であっても良い。または、NiN(窒化ニッケル)膜、TiN(窒化チタン)膜、CoN(窒化コバルト)膜、WN(窒化タングステン)膜であっても良い。またあるいは、Ni膜とNiN膜との積層膜、Ti膜とTiNとの積層膜、Co膜とCoN膜との積層膜、W膜とWN膜との積層膜のうち、いずれかの積層膜であっても良い。

これらの膜は、いずれもシリコンとシリサイド化反応を生じさせる膜である。このため、これらの膜は、シリサイド化アニールによりシリコン基板1とシリサイド化反応し、ソース・ドレイン5に金属シリサイド層を形成させることができる。

【0019】

また、本実施の形態ではシリコン基板1の上にシリサイド化用金属膜6を形成し(図3参照)、その上にストレス膜7を形成する(図4参照)ようにした。しかし、シリサイド化用金属膜6の上にTiN膜などのキャップ膜を形成し、その上にストレス膜7を形成するようにしても良い。このキャップ膜は、シリサイド化アニールの際に、金属シリサイド層の異常酸化を防止するための膜である。

【0020】

次に、本実施の形態の製造方法により形成されたトランジスタのソース・ドレイン5と、シリコン基板1との間の接合リーク電流を評価した結果について説明する。

図9は、図8に示したソース・ドレイン5とシリコン基板1との間の接合リーク電流をプロットしたグラフである。このグラフでは、プロットされた曲線が左側にシフトするほど、リーク電流が小さいことを示している。

本実施の形態により形成されたソース・ドレイン5とシリコン基板1との間の接合リーク電流が、曲線11aにプロットされている。また、従来技術により形成されたソース・ドレインとシリコン基板との間の接合リーク電流が、曲線11bにプロットされている。両者を比較すると、曲線11aは、曲線11bよりも全体的に左側にシフトしている。従って、本実施の形態により形成されたソース・ドレイン5とシリコン基板1との間の接合リーク電流は、従来技術と比較して減少していることが確認された。

これは、本実施の形態により形成したトランジスタのソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド層8aが形成されたためと考えられる。従って、本実施の形態の製造方法により、ソース・ドレイン5と、シリコン基板1との間の接合リーク電流を減少させることができる。

【0021】

次に、本実施の形態の変形例について説明する。

図4に示したストレス膜7としては、引っ張り応力を有する膜(TiN膜およびCo膜の積層膜)を形成した。しかし、上記ストレス膜7は、上記シリサイド化アニールを行う際に、圧縮応力を有する膜であっても良い。例えば、TiN膜、W(タングステン)膜を順次積層した膜を形成するようにしても良い。またはTiN膜、WN(窒化タングステン)膜、およびW(タングステン)膜を順次積層した膜を形成するようにしても良い。

この場合の、シリサイド化アニールにおける、ストレス膜7、シリサイド化用金属膜6の有する応力を図10に示す。ストレス膜7は、3.1GPa程度の圧縮応力12aを有している。この応力に対応するように、シリサイド化用金属膜6は引っ張り応力12bを有している。つまり、シリサイド化用金属膜6に圧縮応力のストレスが与えられた状態で、シリサイド化アニールが行われている。

【0022】

この方法により形成されたトランジスタのソース・ドレインと、シリコン基板との間の接合リーク電流については、現在データを取得中である。(シリサイド化用金属膜の材料により、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制できる可能性があると考えられる。)

ここで、従来技術においては、シリサイド化用金属の上にTiNキャップ膜を積層した状態で、その上にストレス膜が形成されることなく、シリサイド化アニールが行われていた。この場合、TiNキャップ膜は1.8GPa程度の圧縮応力を有しているが、金属シリサイド層の異常酸化を十分に防止できなかった。従って本変形例のようにストレス膜として圧縮応力を有する膜を用いる場合は、1.8GPaより大きい圧縮応力を有する膜を用いることが好適であると予想されている。

【0023】

実施の形態2.

本実施の形態に係る半導体装置の製造方法について説明する。ここでは、実施の形態1と異なる構成を中心に説明する。

まず、実施の形態1と同様にして、シリコン基板1の上に素子分離を形成する工程から、シリサイド化用金属膜(Ni膜)6を形成するまでの工程(図1〜図3参照)を行う。

次に、図11に示すように、シリサイド化用金属膜6の上に合金化用金属膜13を形成する。この膜は、後のシリサイド化アニールにおいて、シリサイド化用金属膜6と合金化反応を生じ得る膜とする。また、その際に、引っ張り応力を有する膜とする。

次に、合金化用金属膜13の上に、ストレス膜7を実施の形態1と同様にして形成する。

【0024】

上述したシリサイド化用金属膜6と合金化用金属膜13は、同一装置で連続的に形成するようにしても良い。例えば、シリサイド化用金属膜6を成膜するチャンバと、合金化用金属膜13を成膜するチャンバとを備えたクラスタツールを用いて形成する。

図12に、上記クラスタツールの構成例を示す。このクラスタツールは搬送系ユニット14、15を備えている。搬送系ユニット14の周囲には、シリサイド化用金属膜(Ni膜等)成膜用チャンバ14a、キャップ膜(TiN膜等)成膜用チャンバ14b、合金化用金属膜(Co膜、W膜等)成膜用チャンバ14c、14dが備えられている。搬送系ユニット15の周囲には、スパッタエッチチャンバ15a、デガス(degassig extrusion;順次式ガス抜き押し出し)チャンバ15b、ロードロックチャンバ15c、冷却用チャンバ15dが備えられている。

上記構成のクラスタツールを用いることにより、シリサイド化用金属膜6、合金化用金属膜13を同一の装置で連続的に形成することができる。このように形成することにより、これらの膜の界面の酸化、汚染を防止することができる。これにより、シリサイド化用金属膜6がシリコン基板1とシリサイド化反応する際に、金属シリサイド層が異常成長することを抑制できる。

【0025】

次に、図11に示したシリコン基板1を熱処理し、シリサイド化アニールを行う。その結果、図13に示すように、ソース・ドレイン5の表面にNiモノシリサイド(NiSi)層8aが形成される。また、ゲート電極3の表面にNiモノシリサイド(NiSi)層8bが形成される。

このとき、合金化用金属膜13は、シリサイド化用金属膜6(またはストレス膜7)と合金化反応を起こす。これに伴い、これらの膜は、体積変化を起こす。前述したように、合金化用金属膜13は、合金化反応の際に、引っ張り応力を有する膜である。よってこのとき、シリサイド化用金属膜6には、引っ張り応力のストレスが与えられる。

【0026】

上記シリサイド化アニールの際の、図11の点線部分Aの拡大図を図14に示す。シリサイド化アニールを行う際に、合金化用金属膜13は引っ張り応力16aを有している。この応力に対応するように、シリサイド化用金属膜6は圧縮応力16bを有している。つまり、シリサイド化用金属膜6に引っ張り応力のストレスが与えられた状態で、シリサイド化アニールが行われている。

このため、実施の形態1と同様に、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制することができる。従って、ソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド(NiSi)層8aを形成することができる。

本実施の形態のその他の構成については、実施の形態1と同様であるので、説明を省略する。

【0027】

以上説明したように、本実施の形態の製造方法によれば、トランジスタのソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド層8aを形成することができる。従って、実施の形態1と同様に、ソース・ドレイン5と、シリコン基板1との間の接合リーク電流を減少させることができる。

【0028】

実施の形態3.

本実施の形態に係る半導体装置の製造方法について説明する。ここでは、実施の形態1と異なる構成を中心に説明する。

まず、実施の形態1と同様にして、シリコン基板1の上に素子分離を形成する工程から、シリサイド化用金属膜(Ni膜)6を形成するまでの工程(図1〜図3参照)を行う。

次に、図15に示すように、シリサイド化用金属膜6の上にキャップ膜17を形成する。例えば、TiN膜などの金属窒化膜を5〜10nm程度の膜厚で形成する。さらに、その上に、金属膜18を形成する。例えば、Co膜、Ti膜、W膜、Ni膜などの純金属膜を50nm以上の膜厚、例えば50〜100nm程度の膜厚で形成する。

【0029】

次に、図15に示したシリコン基板1を熱処理し、シリサイド化アニールを行う。この熱処理は、赤外線ランプ加熱式アニール装置を用いて行う。この装置を用いて熱処理する場合、被熱処理膜の最表面の反射率を大きくすると、被熱処理膜の深さ方向に温度勾配をもたせることができる。ここで、金属膜18は50〜100nm程度の膜厚で形成されているので、表面の反射率が上昇し、赤外線が透過しにくくなっている。このため、上記アニールでは金属膜18の温度は高くなるが、シリサイド化用金属膜6の温度は、あまり上昇しない。すると、金属膜18とシリサイド化用金属膜6の熱膨張が異なるため、それぞれの膜に応力が発生する。

上記シリサイド化アニールの際の、図15の点線部分Aの拡大図を図16に示す。このとき、金属膜18、キャップ膜17は、引っ張り応力19aを有している。この応力に対応するように、シリサイド化用金属膜6は圧縮応力19bを有している。つまり、シリサイド化用金属膜6に引っ張り応力のストレスが与えられた状態で、シリサイド化アニールが行われている。

【0030】

上述したシリサイド化アニールの結果、図17に示すように、ソース・ドレイン5の表面にNiモノシリサイド(NiSi)層8aが形成される。また、ゲート電極3の表面にNiモノシリサイド(NiSi)層8bが形成される。

このとき、実施の形態1と同様に、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制することができる。従って、ソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド(NiSi)層8aを形成することができる。

本実施の形態のその他の構成については、実施の形態1と同様であるので、説明を省略する。

【0031】

以上説明したように、本実施の形態の製造方法によれば、トランジスタのソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド層8aを形成することができる。従って、実施の形態1と同様に、ソース・ドレイン5と、シリコン基板1との間の接合リーク電流を減少させることができる。

【0032】

実施の形態4.

本実施の形態に係る半導体装置の製造方法について説明する。ここでは、実施の形態1と異なる構成を中心に説明する。

まず、実施の形態1と同様にして、シリコン基板1の上に素子分離を形成する工程から、シリコン基板1の表面にソース・ドレイン5を形成するまでの工程(図1〜図2参照)を行う。

【0033】

次に、図18(a)に示すように、シリコン基板1の裏面に、裏面ストレス膜20を形成する。ここでは、裏面ストレス膜20を形成した段階で、シリコン基板1の裏面側が凹形状となるように、引っ張り応力を有する膜を形成する。ここで、図18(a)の点線部分Aの拡大図を図18(b)に示す。裏面ストレス膜20は、引っ張り応力を有する膜であるため、シリコン基板1の裏面側が凹形状となるように、反り21が発生する。

【0034】

次に、図19(a)に示すように、シリコン基板1の上にシリサイド化用金属膜6を形成する。図19(a)の点線部分Aの拡大図を図19(b)に示す。シリコン基板1には反り21が残留した状態のままである。

次に、図20(a)に示すように、裏面ストレス膜20を除去する。図20(a)の点線部分Aの拡大図を図20(b)に示す。シリコン基板1には反りがなくなり、平坦になっている。シリサイド化用金属膜6は、シリコン基板1に反り21が発生した状態で形成されたものである。このため、シリサイド化用金属膜6は圧縮応力22を有している。

【0035】

次に、図20(a)に示したシリコン基板1を熱処理し、シリサイド化アニールを行う。その結果、図21に示すように、ソース・ドレイン5の表面にNiモノシリサイド(NiSi)層8aが形成される。また、ゲート電極3の表面にNiモノシリサイド(NiSi)層8bが形成される。

このとき、シリサイド化用金属膜6が圧縮応力22を有した状態で、シリサイド化アニールが行われる。

このため、実施の形態1と同様に、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制することができる。従って、ソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド(NiSi)層8aを形成することができる。

【0036】

以上説明したように、本実施の形態の製造方法によれば、トランジスタのソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド層8aを形成することができる。従って、実施の形態1と同様に、ソース・ドレイン5と、シリコン基板1との間の接合リーク電流を減少させることができる。

その他の構成については、実施の形態1と同様であるので、説明を省略する。

【0037】

次に、本実施の形態の変形例について説明する。

図18(a)(b)に示した裏面ストレス膜20としては、その膜を形成した段階で、引っ張り応力を有する膜を形成した。しかし、上記裏面ストレス膜20は、その膜を形成した段階で、圧縮応力を有する膜であっても良い。

【0038】

この場合の、図18(b)、図19(b)、図20(b)に対応する部分の断面図を、それぞれ図22、図23、図24に示す。まず、図22に示すように、裏面ストレス膜20として、圧縮応力を有する膜を形成する。すると、シリコン基板1の主面側が凹形状となるように、反り23が発生する。次に、図23に示すようにシリコン基板1の上にシリサイド化用金属膜6を形成する。ここではシリコン基板1には反り23が残留した状態のままである。次に、図24に示すように、裏面ストレス膜20を除去する。すると、シリコン基板1には反りがなくなり、平坦になっている。ここでシリサイド化用金属6は、シリコン基板1に反り23が発生した状態で形成されたものである。このため、シリサイド化用金属膜6は、引っ張り応力24を有している。

この場合、シリサイド化用金属膜6が引っ張り応力24を有した状態で、シリサイド化アニールが行われる。

本変形例によれば、実施の形態1の変形例で述べたように、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制できる可能性があると考えられる。

【0039】

本実施の形態(図18〜図21)に示した製造方法では、引っ張り応力を有する裏面ストレス膜20を形成後、シリサイド化用金属膜6を形成し、その後に裏面ストレス膜20を除去することによって、シリサイド化アニールの際に、シリサイド化用金属膜6が圧縮応力22を有するようにした。

上記アニールの際にシリサイド化用金属膜6が圧縮応力を有するためには、シリサイド化用金属膜6を形成後に、シリコン基板1の主面側が凹形状となるように裏面ストレス膜を形成して、シリサイド化アニールを行うようにしても良い。この場合には、裏面ストレス膜としては、圧縮応力を有する膜を形成する。このようにしても、シリサイド化用金属膜6が圧縮応力を有した状態で、シリサイド化アニールを行うことが可能である。上記のようにしてシリサイド化アニールを行い、その後に裏面ストレス膜20を除去すれば、本実施の形態(図18〜図21)と同様の効果を得ることができる。

【図面の簡単な説明】

【0040】

【図1】実施の形態1に係る半導体装置の製造方法を示す図。

【図2】実施の形態1に係る半導体装置の製造方法を示す図。

【図3】実施の形態1に係る半導体装置の製造方法を示す図。

【図4】実施の形態1に係る半導体装置の製造方法を示す図。

【図5】実施の形態1に係る半導体装置の製造方法を示す図。

【図6】シリサイド化アニールの際に発生する応力を示す図。

【図7】実施の形態1に係る半導体装置の製造方法を示す図。

【図8】実施の形態1に係る半導体装置の製造方法を示す図。

【図9】ソース・ドレインと基板との界面の接合リーク電流を示す図。

【図10】シリサイド化アニールの際に発生する応力を示す図。

【図11】実施の形態2に係る半導体装置の製造方法を示す図。

【図12】実施の形態2に係る半導体製造装置の構成を示す図。

【図13】実施の形態2に係る半導体装置の製造方法を示す図。

【図14】シリサイド化アニールの際に発生する応力を示す図。

【図15】実施の形態3に係る半導体装置の製造方法を示す図。

【図16】シリサイド化アニールの際に発生する応力を示す図。

【図17】実施の形態3に係る半導体装置の製造方法を示す図。

【図18】実施の形態4に係る半導体装置の製造方法を示す図。

【図19】実施の形態4に係る半導体装置の製造方法を示す図。

【図20】実施の形態4に係る半導体装置の製造方法を示す図。

【図21】実施の形態4に係る半導体装置の製造方法を示す図。

【図22】実施の形態4の変形例を示す図。

【図23】実施の形態4の変形例を示す図。

【図24】実施の形態4の変形例を示す図。

【図25】従来の半導体の製造方法を示す図。

【図26】金属シリサイド層のファセット形状を示す図。

【符号の説明】

【0041】

1 シリコン基板、2 ゲート絶縁膜、3 ゲート電極、4 サイドウォール、5 ソース・ドレイン、6シリサイド化用金属膜、7 ストレス膜、8a、8b Niモノシリサイド層、13 合金化用金属膜、17 キャップ膜、18 金属膜、20 裏面ストレス膜、25 ファセット形状。

【技術分野】

【0001】

本発明は半導体装置の製造方法に関し、特にトランジスタのソース・ドレインを低抵抗化するための金属シリサイド層の形成方法に関する。

【背景技術】

【0002】

SoC(システム・オン・チップ)デバイスの微細化に伴い、トランジスタのソース・ドレインを浅く形成することが要求されている。また、デバイスの高速化のために、ソース・ドレインを低抵抗化することが要求されている。これらの要求を満たすため、ソース・ドレインを浅く形成し、その表面に金属シリサイド層を設けた構造が用いられてきた。

例えば、特許文献1には、ソース・ドレインの表面にCo(コバルト)シリサイド層、Ni(ニッケル)シリサイド層などの金属シリサイド層を設けた構造が開示されている。

【0003】

ここで、従来の半導体装置の製造方法により、ソース・ドレインの表面に金属シリサイド層を形成する例について説明する。

まず、図25(a)に示すように、シリコン基板1の主面上に、ゲート絶縁膜2、ゲート電極3を形成する。次に、ゲート絶縁膜2、ゲート電極3の側面に、シリコン酸化膜からなるサイドウォール4を形成する。次に、シリコン基板1の表面に不純物を注入し、さらにシリコン基板1の熱処理を行う。この結果、図25(b)に示すように、ソース・ドレイン5が形成される。

【0004】

次に、図25(c)に示すように、全面にNi膜などのシリサイド化用金属膜6を成膜する。さらに、シリサイド化用金属膜6をシリコン基板1とシリサイド化反応させる。これと同時に、シリサイド化用金属膜6をゲート電極3とシリサイド化反応させる。このとき、シリコン基板1、ゲート電極3の上に未反応のシリサイド用金属膜が残留している。次に、未反応のシリサイド化用金属膜を除去する。この結果、図25(d)に示すように、ソース・ドレイン5の表面にNiモノシリサイド(NiSi)層8aが露出し、ゲート電極3の表面にNiモノシリサイド(NiSi)層8bが露出する。

【0005】

【特許文献1】特開2003−37083号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

上記従来の半導体装置の製造方法において、シリサイド化用金属膜6をシリコン基板1とシリサイド化反応させる際に、シリサイド化反応が局所的に速く進むことがある。この場合、図26に示すように、ソース・ドレイン5の表面にファセット形状25を有する金属シリサイド層8aが形成される。このファセット形状は、ソース・ドレイン5とシリコン基板1との間の接合リーク電流を増加させる。

【0007】

本発明は上記課題を解決するためになされたもので、ソース・ドレインの表面にファセット形状のない金属シリサイド層を形成することにより、ソース・ドレインとシリコン基板との間の接合リークを減少させることを目的とする。

【課題を解決するための手段】

【0008】

本発明に係る半導体装置の製造方法は、シリコン基板上に、前記シリコン基板とシリサイド化反応を生じさせる第1の金属膜を形成する工程と、前記第1の金属膜に引っ張り応力のストレスを印加しながら、前記第1の金属膜を前記シリコン基板とシリサイド化反応させる第1工程とを含むことを特徴とする。

本発明のその他の特徴については、以下において詳細に説明する。

【発明の効果】

【0009】

本発明によれば、ファセット形状のない金属シリサイド層をソース・ドレインの表面に形成することができる。これにより、ソース・ドレインとシリコン基板との間の接合リークを減少させることができる。

【発明を実施するための最良の形態】

【0010】

以下、図面を参照しながら本発明の実施の形態について説明する。なお、各図において同一または相当する部分には同一符号を付して、その説明を簡略化ないし省略する。

【0011】

実施の形態1.

図1〜図8は、本実施の形態に係る半導体装置の製造方法を示す工程断面図である。

本実施の形態で形成する半導体装置は、図1に示すシリコン基板1の主面上に形成される。まず、図示しないが、シリコン基板1の表面に素子分離を形成する。次に、シリコン基板1の主面上にゲート絶縁膜2、ゲート電極3を形成する。ゲート絶縁膜2としては、例えば、2〜3nm程度の膜厚のシリコン酸化膜を形成する。ゲート電極3としては、例えば、100〜150nm程度の膜厚の多結晶シリコン膜を形成する。

次に、シリコン基板1の上に、化学気相成長法(Chemical Vapor Deposition;CVD法)などにより全面にシリコン酸化膜を形成する。さらに、このシリコン酸化膜を全面エッチバックする。この結果、図1に示すように、ゲート絶縁膜2、ゲート電極3の側面に、サイドウォール4が形成される。

【0012】

次に、図1に示したゲート電極3、サイドウォール4をマスクとして、シリコン基板1の表面に不純物をイオン注入する。さらに、シリコン基板1を熱処理する。この結果、図2に示すように、シリコン基板1の表面にソース・ドレイン5が形成される。

【0013】

次に、図3に示すように、シリコン基板1の上に、全面にシリサイド化用金属膜6を形成する。この膜は、シリコン基板1とシリサイド化反応を生じさせる膜とする。例えば、Ni(ニッケル)膜を5〜10nm程度の膜厚で形成する。さらに、図4に示すように、シリサイド化用金属膜6の上にストレス膜7を形成する。例えば、TiN(窒化チタン)膜を5〜10nm程度の膜厚で成膜し、その上にCo(コバルト)膜を5〜10nm程度の膜厚で成膜した積層膜を形成する。この膜は、後の工程でシリサイド化用金属膜6をシリコン基板1とシリサイド化反応させる際に、その膜自身の内部に引っ張り応力を発生する膜(以下、その膜を「引っ張り応力を有する膜」という)である。(同様に、膜がその膜自身の内部に圧縮応力を発生する場合、その膜を「圧縮応力を有する膜」と言う。)

【0014】

次に、図4に示したシリコン基板1を熱処理して、シリサイド化用金属膜6をシリコン基板1とシリサイド化反応させる。これと同時に、シリサイド化用金属膜6をゲート電極3とシリサイド化反応させる。

上記シリサイド化反応させる熱処理(以下、「シリサイド化アニール」という)は、例えば100〜450℃程度の温度のランプアニールとする。上記の温度で熱処理することにより、シリサイド化用金属膜(ニッケル膜)6をシリコン基板1およびゲート電極3とシリサイド化反応させることができる。

【0015】

上記シリサイド化反応の結果、図5に示すように、ソース・ドレイン5の表面にNiモノシリサイド(NiSi)層8aが形成される。また、ゲート電極3の表面にNiモノシリサイド(NiSi)層8bが形成される。このとき、これらのシリサイド化反応により消費されなかったシリサイド化用金属膜6a(以下、「未反応のシリサイド化用金属膜6a」という)が、シリコン基板1、ゲート電極3、およびサイドウォール4の上に残留している。

【0016】

上記シリサイド化反応において、図5に示したNiモノシリサイド(NiSi)層8aは、ファセット形状25(図26参照)を有していない。この理由について説明する。一般に固相反応では、ストレスの存在により反応が異常に速く進んだり、逆に遅くなったりすることが知られている。従って、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制することが可能である。

ここで、上記シリサイド化アニールを行う際の、図4に示した点線部分Aの拡大図を図6に示す。シリサイド化アニールを行う際には、ストレス膜7は、引っ張り応力10a(0.2GPa程度)を有している。これに対応するように、シリサイド化用金属膜6は、圧縮応力10b(0.2GPa程度)を有している。つまり、シリサイド化用金属膜6に引っ張り応力のストレスが与えられた状態で、シリサイド化アニールが行われている。

このようにシリサイド化アニールを行うことにより、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制することができる。これにより、ソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド(NiSi)層8aを形成することができる。

【0017】

次に、図5に示した未反応のシリサイド化用金属膜6a、およびその上のストレス膜7を薬液などにより除去する。この結果、図7に示すように、ソース・ドレイン5の表面にNiモノシリサイド層8aが露出し、ゲート電極3の表面にNiモノシリサイド層8bが露出する。

以上説明した製造方法により、シリコン基板1の主面上にトランジスタが形成される。さらに、図8に示すように、シリコン基板1の上に、シリコン酸化膜などの層間絶縁膜9を全面に成膜する。

【0018】

本実施の形態では、シリサイド化用金属膜6としてNi膜を用いるようにした。シリサイド化用金属膜6は、Ti(チタン)膜、Co(コバルト)膜、W(タングステン)膜などの膜であっても良い。または、NiN(窒化ニッケル)膜、TiN(窒化チタン)膜、CoN(窒化コバルト)膜、WN(窒化タングステン)膜であっても良い。またあるいは、Ni膜とNiN膜との積層膜、Ti膜とTiNとの積層膜、Co膜とCoN膜との積層膜、W膜とWN膜との積層膜のうち、いずれかの積層膜であっても良い。

これらの膜は、いずれもシリコンとシリサイド化反応を生じさせる膜である。このため、これらの膜は、シリサイド化アニールによりシリコン基板1とシリサイド化反応し、ソース・ドレイン5に金属シリサイド層を形成させることができる。

【0019】

また、本実施の形態ではシリコン基板1の上にシリサイド化用金属膜6を形成し(図3参照)、その上にストレス膜7を形成する(図4参照)ようにした。しかし、シリサイド化用金属膜6の上にTiN膜などのキャップ膜を形成し、その上にストレス膜7を形成するようにしても良い。このキャップ膜は、シリサイド化アニールの際に、金属シリサイド層の異常酸化を防止するための膜である。

【0020】

次に、本実施の形態の製造方法により形成されたトランジスタのソース・ドレイン5と、シリコン基板1との間の接合リーク電流を評価した結果について説明する。

図9は、図8に示したソース・ドレイン5とシリコン基板1との間の接合リーク電流をプロットしたグラフである。このグラフでは、プロットされた曲線が左側にシフトするほど、リーク電流が小さいことを示している。

本実施の形態により形成されたソース・ドレイン5とシリコン基板1との間の接合リーク電流が、曲線11aにプロットされている。また、従来技術により形成されたソース・ドレインとシリコン基板との間の接合リーク電流が、曲線11bにプロットされている。両者を比較すると、曲線11aは、曲線11bよりも全体的に左側にシフトしている。従って、本実施の形態により形成されたソース・ドレイン5とシリコン基板1との間の接合リーク電流は、従来技術と比較して減少していることが確認された。

これは、本実施の形態により形成したトランジスタのソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド層8aが形成されたためと考えられる。従って、本実施の形態の製造方法により、ソース・ドレイン5と、シリコン基板1との間の接合リーク電流を減少させることができる。

【0021】

次に、本実施の形態の変形例について説明する。

図4に示したストレス膜7としては、引っ張り応力を有する膜(TiN膜およびCo膜の積層膜)を形成した。しかし、上記ストレス膜7は、上記シリサイド化アニールを行う際に、圧縮応力を有する膜であっても良い。例えば、TiN膜、W(タングステン)膜を順次積層した膜を形成するようにしても良い。またはTiN膜、WN(窒化タングステン)膜、およびW(タングステン)膜を順次積層した膜を形成するようにしても良い。

この場合の、シリサイド化アニールにおける、ストレス膜7、シリサイド化用金属膜6の有する応力を図10に示す。ストレス膜7は、3.1GPa程度の圧縮応力12aを有している。この応力に対応するように、シリサイド化用金属膜6は引っ張り応力12bを有している。つまり、シリサイド化用金属膜6に圧縮応力のストレスが与えられた状態で、シリサイド化アニールが行われている。

【0022】

この方法により形成されたトランジスタのソース・ドレインと、シリコン基板との間の接合リーク電流については、現在データを取得中である。(シリサイド化用金属膜の材料により、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制できる可能性があると考えられる。)

ここで、従来技術においては、シリサイド化用金属の上にTiNキャップ膜を積層した状態で、その上にストレス膜が形成されることなく、シリサイド化アニールが行われていた。この場合、TiNキャップ膜は1.8GPa程度の圧縮応力を有しているが、金属シリサイド層の異常酸化を十分に防止できなかった。従って本変形例のようにストレス膜として圧縮応力を有する膜を用いる場合は、1.8GPaより大きい圧縮応力を有する膜を用いることが好適であると予想されている。

【0023】

実施の形態2.

本実施の形態に係る半導体装置の製造方法について説明する。ここでは、実施の形態1と異なる構成を中心に説明する。

まず、実施の形態1と同様にして、シリコン基板1の上に素子分離を形成する工程から、シリサイド化用金属膜(Ni膜)6を形成するまでの工程(図1〜図3参照)を行う。

次に、図11に示すように、シリサイド化用金属膜6の上に合金化用金属膜13を形成する。この膜は、後のシリサイド化アニールにおいて、シリサイド化用金属膜6と合金化反応を生じ得る膜とする。また、その際に、引っ張り応力を有する膜とする。

次に、合金化用金属膜13の上に、ストレス膜7を実施の形態1と同様にして形成する。

【0024】

上述したシリサイド化用金属膜6と合金化用金属膜13は、同一装置で連続的に形成するようにしても良い。例えば、シリサイド化用金属膜6を成膜するチャンバと、合金化用金属膜13を成膜するチャンバとを備えたクラスタツールを用いて形成する。

図12に、上記クラスタツールの構成例を示す。このクラスタツールは搬送系ユニット14、15を備えている。搬送系ユニット14の周囲には、シリサイド化用金属膜(Ni膜等)成膜用チャンバ14a、キャップ膜(TiN膜等)成膜用チャンバ14b、合金化用金属膜(Co膜、W膜等)成膜用チャンバ14c、14dが備えられている。搬送系ユニット15の周囲には、スパッタエッチチャンバ15a、デガス(degassig extrusion;順次式ガス抜き押し出し)チャンバ15b、ロードロックチャンバ15c、冷却用チャンバ15dが備えられている。

上記構成のクラスタツールを用いることにより、シリサイド化用金属膜6、合金化用金属膜13を同一の装置で連続的に形成することができる。このように形成することにより、これらの膜の界面の酸化、汚染を防止することができる。これにより、シリサイド化用金属膜6がシリコン基板1とシリサイド化反応する際に、金属シリサイド層が異常成長することを抑制できる。

【0025】

次に、図11に示したシリコン基板1を熱処理し、シリサイド化アニールを行う。その結果、図13に示すように、ソース・ドレイン5の表面にNiモノシリサイド(NiSi)層8aが形成される。また、ゲート電極3の表面にNiモノシリサイド(NiSi)層8bが形成される。

このとき、合金化用金属膜13は、シリサイド化用金属膜6(またはストレス膜7)と合金化反応を起こす。これに伴い、これらの膜は、体積変化を起こす。前述したように、合金化用金属膜13は、合金化反応の際に、引っ張り応力を有する膜である。よってこのとき、シリサイド化用金属膜6には、引っ張り応力のストレスが与えられる。

【0026】

上記シリサイド化アニールの際の、図11の点線部分Aの拡大図を図14に示す。シリサイド化アニールを行う際に、合金化用金属膜13は引っ張り応力16aを有している。この応力に対応するように、シリサイド化用金属膜6は圧縮応力16bを有している。つまり、シリサイド化用金属膜6に引っ張り応力のストレスが与えられた状態で、シリサイド化アニールが行われている。

このため、実施の形態1と同様に、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制することができる。従って、ソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド(NiSi)層8aを形成することができる。

本実施の形態のその他の構成については、実施の形態1と同様であるので、説明を省略する。

【0027】

以上説明したように、本実施の形態の製造方法によれば、トランジスタのソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド層8aを形成することができる。従って、実施の形態1と同様に、ソース・ドレイン5と、シリコン基板1との間の接合リーク電流を減少させることができる。

【0028】

実施の形態3.

本実施の形態に係る半導体装置の製造方法について説明する。ここでは、実施の形態1と異なる構成を中心に説明する。

まず、実施の形態1と同様にして、シリコン基板1の上に素子分離を形成する工程から、シリサイド化用金属膜(Ni膜)6を形成するまでの工程(図1〜図3参照)を行う。

次に、図15に示すように、シリサイド化用金属膜6の上にキャップ膜17を形成する。例えば、TiN膜などの金属窒化膜を5〜10nm程度の膜厚で形成する。さらに、その上に、金属膜18を形成する。例えば、Co膜、Ti膜、W膜、Ni膜などの純金属膜を50nm以上の膜厚、例えば50〜100nm程度の膜厚で形成する。

【0029】

次に、図15に示したシリコン基板1を熱処理し、シリサイド化アニールを行う。この熱処理は、赤外線ランプ加熱式アニール装置を用いて行う。この装置を用いて熱処理する場合、被熱処理膜の最表面の反射率を大きくすると、被熱処理膜の深さ方向に温度勾配をもたせることができる。ここで、金属膜18は50〜100nm程度の膜厚で形成されているので、表面の反射率が上昇し、赤外線が透過しにくくなっている。このため、上記アニールでは金属膜18の温度は高くなるが、シリサイド化用金属膜6の温度は、あまり上昇しない。すると、金属膜18とシリサイド化用金属膜6の熱膨張が異なるため、それぞれの膜に応力が発生する。

上記シリサイド化アニールの際の、図15の点線部分Aの拡大図を図16に示す。このとき、金属膜18、キャップ膜17は、引っ張り応力19aを有している。この応力に対応するように、シリサイド化用金属膜6は圧縮応力19bを有している。つまり、シリサイド化用金属膜6に引っ張り応力のストレスが与えられた状態で、シリサイド化アニールが行われている。

【0030】

上述したシリサイド化アニールの結果、図17に示すように、ソース・ドレイン5の表面にNiモノシリサイド(NiSi)層8aが形成される。また、ゲート電極3の表面にNiモノシリサイド(NiSi)層8bが形成される。

このとき、実施の形態1と同様に、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制することができる。従って、ソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド(NiSi)層8aを形成することができる。

本実施の形態のその他の構成については、実施の形態1と同様であるので、説明を省略する。

【0031】

以上説明したように、本実施の形態の製造方法によれば、トランジスタのソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド層8aを形成することができる。従って、実施の形態1と同様に、ソース・ドレイン5と、シリコン基板1との間の接合リーク電流を減少させることができる。

【0032】

実施の形態4.

本実施の形態に係る半導体装置の製造方法について説明する。ここでは、実施の形態1と異なる構成を中心に説明する。

まず、実施の形態1と同様にして、シリコン基板1の上に素子分離を形成する工程から、シリコン基板1の表面にソース・ドレイン5を形成するまでの工程(図1〜図2参照)を行う。

【0033】

次に、図18(a)に示すように、シリコン基板1の裏面に、裏面ストレス膜20を形成する。ここでは、裏面ストレス膜20を形成した段階で、シリコン基板1の裏面側が凹形状となるように、引っ張り応力を有する膜を形成する。ここで、図18(a)の点線部分Aの拡大図を図18(b)に示す。裏面ストレス膜20は、引っ張り応力を有する膜であるため、シリコン基板1の裏面側が凹形状となるように、反り21が発生する。

【0034】

次に、図19(a)に示すように、シリコン基板1の上にシリサイド化用金属膜6を形成する。図19(a)の点線部分Aの拡大図を図19(b)に示す。シリコン基板1には反り21が残留した状態のままである。

次に、図20(a)に示すように、裏面ストレス膜20を除去する。図20(a)の点線部分Aの拡大図を図20(b)に示す。シリコン基板1には反りがなくなり、平坦になっている。シリサイド化用金属膜6は、シリコン基板1に反り21が発生した状態で形成されたものである。このため、シリサイド化用金属膜6は圧縮応力22を有している。

【0035】

次に、図20(a)に示したシリコン基板1を熱処理し、シリサイド化アニールを行う。その結果、図21に示すように、ソース・ドレイン5の表面にNiモノシリサイド(NiSi)層8aが形成される。また、ゲート電極3の表面にNiモノシリサイド(NiSi)層8bが形成される。

このとき、シリサイド化用金属膜6が圧縮応力22を有した状態で、シリサイド化アニールが行われる。

このため、実施の形態1と同様に、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制することができる。従って、ソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド(NiSi)層8aを形成することができる。

【0036】

以上説明したように、本実施の形態の製造方法によれば、トランジスタのソース・ドレイン5に、ファセット形状を有しないNiモノシリサイド層8aを形成することができる。従って、実施の形態1と同様に、ソース・ドレイン5と、シリコン基板1との間の接合リーク電流を減少させることができる。

その他の構成については、実施の形態1と同様であるので、説明を省略する。

【0037】

次に、本実施の形態の変形例について説明する。

図18(a)(b)に示した裏面ストレス膜20としては、その膜を形成した段階で、引っ張り応力を有する膜を形成した。しかし、上記裏面ストレス膜20は、その膜を形成した段階で、圧縮応力を有する膜であっても良い。

【0038】

この場合の、図18(b)、図19(b)、図20(b)に対応する部分の断面図を、それぞれ図22、図23、図24に示す。まず、図22に示すように、裏面ストレス膜20として、圧縮応力を有する膜を形成する。すると、シリコン基板1の主面側が凹形状となるように、反り23が発生する。次に、図23に示すようにシリコン基板1の上にシリサイド化用金属膜6を形成する。ここではシリコン基板1には反り23が残留した状態のままである。次に、図24に示すように、裏面ストレス膜20を除去する。すると、シリコン基板1には反りがなくなり、平坦になっている。ここでシリサイド化用金属6は、シリコン基板1に反り23が発生した状態で形成されたものである。このため、シリサイド化用金属膜6は、引っ張り応力24を有している。

この場合、シリサイド化用金属膜6が引っ張り応力24を有した状態で、シリサイド化アニールが行われる。

本変形例によれば、実施の形態1の変形例で述べたように、シリサイド化用金属膜6とシリコン基板1とのシリサイド化反応の反応速度を抑制できる可能性があると考えられる。

【0039】

本実施の形態(図18〜図21)に示した製造方法では、引っ張り応力を有する裏面ストレス膜20を形成後、シリサイド化用金属膜6を形成し、その後に裏面ストレス膜20を除去することによって、シリサイド化アニールの際に、シリサイド化用金属膜6が圧縮応力22を有するようにした。

上記アニールの際にシリサイド化用金属膜6が圧縮応力を有するためには、シリサイド化用金属膜6を形成後に、シリコン基板1の主面側が凹形状となるように裏面ストレス膜を形成して、シリサイド化アニールを行うようにしても良い。この場合には、裏面ストレス膜としては、圧縮応力を有する膜を形成する。このようにしても、シリサイド化用金属膜6が圧縮応力を有した状態で、シリサイド化アニールを行うことが可能である。上記のようにしてシリサイド化アニールを行い、その後に裏面ストレス膜20を除去すれば、本実施の形態(図18〜図21)と同様の効果を得ることができる。

【図面の簡単な説明】

【0040】

【図1】実施の形態1に係る半導体装置の製造方法を示す図。

【図2】実施の形態1に係る半導体装置の製造方法を示す図。

【図3】実施の形態1に係る半導体装置の製造方法を示す図。

【図4】実施の形態1に係る半導体装置の製造方法を示す図。

【図5】実施の形態1に係る半導体装置の製造方法を示す図。

【図6】シリサイド化アニールの際に発生する応力を示す図。

【図7】実施の形態1に係る半導体装置の製造方法を示す図。

【図8】実施の形態1に係る半導体装置の製造方法を示す図。

【図9】ソース・ドレインと基板との界面の接合リーク電流を示す図。

【図10】シリサイド化アニールの際に発生する応力を示す図。

【図11】実施の形態2に係る半導体装置の製造方法を示す図。

【図12】実施の形態2に係る半導体製造装置の構成を示す図。

【図13】実施の形態2に係る半導体装置の製造方法を示す図。

【図14】シリサイド化アニールの際に発生する応力を示す図。

【図15】実施の形態3に係る半導体装置の製造方法を示す図。

【図16】シリサイド化アニールの際に発生する応力を示す図。

【図17】実施の形態3に係る半導体装置の製造方法を示す図。

【図18】実施の形態4に係る半導体装置の製造方法を示す図。

【図19】実施の形態4に係る半導体装置の製造方法を示す図。

【図20】実施の形態4に係る半導体装置の製造方法を示す図。

【図21】実施の形態4に係る半導体装置の製造方法を示す図。

【図22】実施の形態4の変形例を示す図。

【図23】実施の形態4の変形例を示す図。

【図24】実施の形態4の変形例を示す図。

【図25】従来の半導体の製造方法を示す図。

【図26】金属シリサイド層のファセット形状を示す図。

【符号の説明】

【0041】

1 シリコン基板、2 ゲート絶縁膜、3 ゲート電極、4 サイドウォール、5 ソース・ドレイン、6シリサイド化用金属膜、7 ストレス膜、8a、8b Niモノシリサイド層、13 合金化用金属膜、17 キャップ膜、18 金属膜、20 裏面ストレス膜、25 ファセット形状。

【特許請求の範囲】

【請求項1】

シリコン基板上に、前記シリコン基板とシリサイド化反応を生じさせる第1の金属膜を形成する工程と、

前記第1の金属膜に引っ張り応力のストレスを印加しながら、前記第1の金属膜を前記シリコン基板とシリサイド化反応させる第1工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記第1工程は、前記第1の金属膜の上に、前記第1の金属膜と合金化反応を生じさせる第2の金属膜を形成する工程と、これらの金属膜の合金化反応により前記引っ張り応力のストレスを発生させる工程と、を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1の金属膜および前記第2の金属膜は、同一の装置により連続して形成されることを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1工程は、前記第1の金属膜の上に50nm以上の第3の金属膜を形成する工程と、前記第3の金属膜の表面を赤外線ランプアニールで熱処理することにより前記引っ張り応力のストレスを発生させる工程と、を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項5】

シリコン基板の裏面に、前記シリコン基板の裏面側が凹形状となるように第1の膜を形成する工程と、

前記シリコン基板上に、前記シリコン基板とシリサイド化反応を生じさせる第1の金属膜を形成する工程と、

前記第1の膜を除去する工程と、

前記前記第1の金属膜を前記シリコン基板とシリサイド化反応させる工程と、

を順に施すことを特徴とする半導体装置の製造方法。

【請求項6】

シリコン基板上に、前記シリコン基板とシリサイド化反応を生じさせる第1の金属膜を形成する工程と、

前記シリコン基板の裏面に、前記シリコン基板の主面側が凹形状となるように第1の膜を形成する工程と、

前記前記第1の金属膜を前記シリコン基板とシリサイド化反応させる工程と、

を順に施すことを特徴とする半導体装置の製造方法。

【請求項7】

前記シリサイド化反応させる工程は、100〜450℃の温度の熱処理により行われることを特徴とする請求項1〜6に記載の半導体装置の製造方法。

【請求項1】

シリコン基板上に、前記シリコン基板とシリサイド化反応を生じさせる第1の金属膜を形成する工程と、

前記第1の金属膜に引っ張り応力のストレスを印加しながら、前記第1の金属膜を前記シリコン基板とシリサイド化反応させる第1工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記第1工程は、前記第1の金属膜の上に、前記第1の金属膜と合金化反応を生じさせる第2の金属膜を形成する工程と、これらの金属膜の合金化反応により前記引っ張り応力のストレスを発生させる工程と、を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1の金属膜および前記第2の金属膜は、同一の装置により連続して形成されることを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1工程は、前記第1の金属膜の上に50nm以上の第3の金属膜を形成する工程と、前記第3の金属膜の表面を赤外線ランプアニールで熱処理することにより前記引っ張り応力のストレスを発生させる工程と、を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項5】

シリコン基板の裏面に、前記シリコン基板の裏面側が凹形状となるように第1の膜を形成する工程と、

前記シリコン基板上に、前記シリコン基板とシリサイド化反応を生じさせる第1の金属膜を形成する工程と、

前記第1の膜を除去する工程と、

前記前記第1の金属膜を前記シリコン基板とシリサイド化反応させる工程と、

を順に施すことを特徴とする半導体装置の製造方法。

【請求項6】

シリコン基板上に、前記シリコン基板とシリサイド化反応を生じさせる第1の金属膜を形成する工程と、

前記シリコン基板の裏面に、前記シリコン基板の主面側が凹形状となるように第1の膜を形成する工程と、

前記前記第1の金属膜を前記シリコン基板とシリサイド化反応させる工程と、

を順に施すことを特徴とする半導体装置の製造方法。

【請求項7】

前記シリサイド化反応させる工程は、100〜450℃の温度の熱処理により行われることを特徴とする請求項1〜6に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【公開番号】特開2006−332511(P2006−332511A)

【公開日】平成18年12月7日(2006.12.7)

【国際特許分類】

【出願番号】特願2005−157099(P2005−157099)

【出願日】平成17年5月30日(2005.5.30)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成18年12月7日(2006.12.7)

【国際特許分類】

【出願日】平成17年5月30日(2005.5.30)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]