半導体装置の製造方法

【課題】コリメータを備えるスパッタリング装置の生産効率を向上させることのできる技術を提供する。

【解決手段】上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を相対的に短く、上部シールド13の下縁部の内径を相対的に広くして、ターゲット3と上部シールド13との間の隙間量を相対的に広くし、さらに台座リング15の内径を相対的に広く、台座リング15の高さを相対的に低くして、パッキングプレート11(ターゲット3)と台座リング15との間の隙間量を相対的に広くすることにより、ターゲット3と上部シールド13との接触またはパッキングプレート11(ターゲット3)と台座リング15との接触を回避する。

【解決手段】上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を相対的に短く、上部シールド13の下縁部の内径を相対的に広くして、ターゲット3と上部シールド13との間の隙間量を相対的に広くし、さらに台座リング15の内径を相対的に広く、台座リング15の高さを相対的に低くして、パッキングプレート11(ターゲット3)と台座リング15との間の隙間量を相対的に広くすることにより、ターゲット3と上部シールド13との接触またはパッキングプレート11(ターゲット3)と台座リング15との接触を回避する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造技術に関し、特に、物理的成膜手段、例えばスパッタリング法によって半導体ウエハ上に薄膜を成膜する工程に適用して有効な技術に関するものである。

【背景技術】

【0002】

LSI(Large Scale Integration)の微細化により必要となった半導体ウエハ上のパターンの深い孔への薄膜配線形成に対して、従来のスパッタリング法では半導体ウエハの主面(回路形成面)に対して斜めに入射するスパッタ粒子が含まれるため、孔の底まで十分に膜が堆積する前に、孔の入口付近を成膜物質が塞いでしまう問題点があった。これを解決するために、いくつかの技術が開発されており、その1つとしてコリメートスパッタリング法がある。コリメートスパッタリング法は、ターゲットと半導体ウエハとの間に格子状に孔のあいたコリメータ(整合板)を設置し、斜め入射成分を除去するものである。

【0003】

例えばコリメータを用いて半導体ウエハに成膜するスパッタリング方法において、コリメータと半導体ウエハとの間に電圧を印加させながら成膜することで、コリメータから半導体ウエハ方向に発生した電界により、コリメータを斜めに通過したスパッタ粒子を半導体ウエハの法線方向に偏向させて堆積させる技術が特開平8−203828号公報(特許文献1)に開示されている。

【0004】

また、スパッタリング装置に、筒状の上部シールドおよび中間シールドをターゲットとコリメータとの間およびコリメータとペディスタルとの間にそれぞれ設けることにより、ターゲットに対して影となる部分の形成を制御して、コリメータの通過後に指向性を失ったスパッタ粒子による発塵しやすい低密度で脆弱な膜の形成の可能性を低くする技術が特開平10−176267号公報(特許文献2)に開示されている。

【0005】

また、マグネトロン上にターゲットを配し、ターゲットに対向して被加工物の基板を配置し、ターゲットと基板との間に、基板の法線方向に進行するスパッタ粒子を選択的に通過させるコリメータを配置してスパッタ蒸着を行うスパッタリング法において、処理ガスにArより比重の大きなガスを用いて、ターゲット面の垂直方向に強い指向性をもたせる技術が特許第2707951号明細書(特許文献3)に開示されている。

【特許文献1】特開平8−203828号公報

【特許文献2】特開平10−176267号公報

【特許文献3】特許第2707951号明細書

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、コリメータを用いたスパッタリング法については、以下に説明する種々の技術的課題が存在する。

【0007】

コリメータを備えるスパッタリング装置(以下、単にコリメートスパッタ装置と記す)においては、指向性のあるスパッタ粒子が高いエネルギーを持って到達しない部分が真空チャンバ内に存在する。この部分は、例えばチャンバ内壁であり、スパッタ粒子がガスの拡散により低いエネルギーを持ってチャンバ内壁に到達し、付着したスパッタ粒子により密度の低い膜が形成される。このような膜は付着力が小さいために剥離しやすく、真空チャンバ内において発塵源となる。

【0008】

そこで、真空チャンバ内のチャンバ内壁にスパッタ粒子が付着するのを防ぐために、例えばターゲットとコリメータとの間には、チャンバ内壁を保護するための筒状の上部シールドが設けられている(例えば上記特許文献3参照)。上部シールドの上縁部は台座リングによってアダプタリングにねじ止めされ、また上部シールドの下縁部はコリメータから一定の隙間をもって離間された状態で、コリメータの上面近傍まで延びており、上部シールドがターゲットを囲むようにしている。

【0009】

ところが、上記コリメートスパッタ装置では、ターゲットと上部シールドとの間またはターゲットと台座リングとの間の隙間量が少なく、さらに付着した膜を取り除くための洗浄または加熱により上部シールドが変形するため、例えばコリメートスパッタ装置のメンテナンス作業を行う度に上記隙間量が変わり、ターゲットと上部シールドまたはターゲットと台座リングとが接触するという問題が生じている。この接触は、メンテナンス作業を終えた後、真空チャンバ内を真空排気して所定の真空度まで減圧し、さらに真空チャンバ内を放電させることによって、初めて異常放電として確認されるものである。このため、ターゲットと上部シールドまたはターゲットと台座リングとの接触を確認するまでに多大な時間を要してしまう。また、ターゲットと上部シールドとの間またはターゲットと台座リングとの間の隙間量を修正するためには、再度真空チャンバ内を大気圧に戻し、上記隙間量を調整した後、真空チャンバ内を真空排気して所定の真空度まで減圧し、さらに真空チャンバ内を放電させることによって確認しなければならず、コリメートスパッタ装置の稼動停止時間が長くなり、生産効率が低下してしまう。

【0010】

本発明の目的は、コリメータを備えるスパッタリング装置の生産効率を向上させることのできる技術を提供することにある。

【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0013】

本発明は、上部シールドの上部折曲部と下部折曲部との上下垂直位置の距離を相対的に短く、上部シールドの下縁部の内径を相対的に広くして、ターゲットの周縁と上部シールドの下部折曲部との隙間を広くし、さらに台座リングの内径を相対的に広く、台座リングの高さを相対的に低くして、ターゲットと台座リングの内側端部との隙間および台座リングの上面とその上部に位置するターゲットとの隙間を相対的に広くすることにより、ターゲットと上部シールドとの間またはターゲットと台座リングとの間の隙間量を相対的に広くする。

【発明の効果】

【0014】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0015】

ターゲットと上部シールドまたはターゲットと台座リングとの接触が回避されて、真空チャンバ内を放電させた時の異常放電を防ぐことができる。これにより、メンテナンス作業後の真空チャンバ内の立ち上げ作業における無駄な時間を排除することができるので、スパッタリング装置の稼動停止時間が短くなり、生産効率が向上する。

【発明を実施するための最良の形態】

【0016】

以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

【0017】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0018】

さらに、以下の実施の形態において、ウエハとは、集積回路の製造に用いるシリコン単結晶基板(一般にほぼ平面円形状)、サファイア基板、ガラス基板、その他の絶縁、反絶縁または半導体基板等並びにそれらの複合的基板を言う。また、以下の実施の形態において半導体集積回路装置というときは、シリコンウエハやサファイア基板等の半導体または絶縁体基板上に作られるものだけでなく、特に、そうでない旨明示された場合を除き、TFT(Thin-Film-Transistor)およびSTN(Super-Twisted-Nematic)液晶等のようなガラス等の他の絶縁基板上に作られるもの等も含むものとする。

【0019】

さらに、以下の実施の形態において、電界効果トランジスタを代表するMIS・FET(Metal Insulator Semiconductor Field Effect Transistor)をMISと略し、nチャネル型のMIS・FETをnMISと略し、pチャネル型のMIS・FETをpMISと略す。

【0020】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0021】

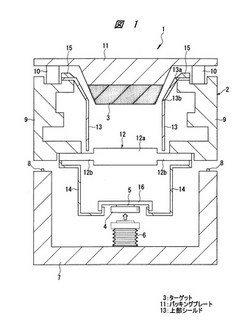

本実施の形態である半導体装置の製造方法で使用するコリメートスパッタ装置の構成の一例を図1〜図5を用いて説明する。図1はコリメートスパッタ装置の構成を示す概略図、図2はコリメータ部分の拡大図、図3は上部シールド部分の拡大図、図4は台座リング部分の拡大図、図5はターゲット部分の拡大図である。

【0022】

図1に示すように、コリメートスパッタ装置1は、チタン(Ti)膜の成膜用の装置であり、真空チャンバ2と、その上部開口部に配置されたチタン製のターゲット3とを備えている。真空チャンバ2の内部には、ターゲット3と同軸にウエハステージ4が配置されており、その上面でウエハ5を支持するように構成されている。ウエハ5は、例えば直径が6インチの平面略円形状の半導体の薄板である。ウエハステージ4の下面には昇降機構を有する駆動軸がベロー6によって保護された状態で接続され、ウエハステージ4が上下運動可能となっている。

【0023】

さらに、真空チャンバ2は、導電性材料のチャンバ本体7と、チャンバ本体7のノッチ8に着脱可能に取り付けられる環状のアダプタリング9とを備えている。このアダプタリング9は導電性材料からなり、例えばステンレス鋼(SUS304)、アルミニウム(Al)またはチタン等から作られている。アダプタリング9の上面にはセラミックリング10を介して、ターゲット3を備えるパッキングプレート11が載置され、着脱可能に固定されている。このパッキングプレート11は導電性材料からなり、例えばアルミニウム等から作られており、ターゲット3とパッキングプレート11とは電気的に接続されている。また、本実施の形態では、ターゲット3が凸形状のパッキングプレート11の先端部に備わっているが、パッキングプレート11のほぼ全面にターゲット材料を備えてもよく、またはパッキングプレート11のほぼ全部をターゲット材料で構成してもよい。

【0024】

また、真空チャンバ2には、プロセスガスの供給手段としてアルゴン(Ar)ガス供給源および窒素(N2)ガス供給源が接続されており、さらに真空チャンバ2内を真空とするための真空ポンプが接続されている。なお、部材間にはO(オー)リングが設けられて真空チャンバ2の気密性を保つようにしてもよい。また、セラミックリング10によりチャンバ本体7等から絶縁されているターゲット3には、直流電源の負端子が電気配線により接続されており、直流電源の正端子は真空チャンバ2に接続されると共に接地されている。

【0025】

また、真空チャンバ2は、コリメータ12を備えている。コリメータ12は、例えば蜂の巣状に配列された断面六角形の孔を備えたチタン製の円板状プレート12aと、その外周部に取り付けられた支持枠12bとからなり、ターゲット3とウエハステージ4との間において、それらと平行かつ同軸に配列されるようになっている。

【0026】

また、真空チャンバ2には、チャンバ内壁面がスパッタ粒子により被覆されるのを防止するために、筒状の上部シールド13および筒状の下部シールド14が設けられている。これら上部シールド13および下部シールド14は導電性材料、例えばステンレス鋼から作られている。

【0027】

まず、上部シールド13について説明する。上部シールド13はアダプタリング9とコリメータ12との間のチャンバ内壁面を保護するためのものである。上部シールド13は、少なくとも2箇所の折曲部(上部折曲部13aおよび下部折曲部13b)で曲げられて、ターゲット3に平行な上縁部とターゲット3に垂直な下縁部とを有している。上部シールド13の上縁部はアダプタリング9の上面に台座リング15を用いて固定されており、また、上部シールド13の下縁部はコリメータ12から一定の隙間をもって離隔された状態でコリメータ12の上面近傍まで延びており、上部シールド13がターゲット3を囲むようにしている。

【0028】

図2に、コリメータ部分の拡大図を示す。(a)は本実施の形態であるコリメータ部分、(b)は本発明者が検討したコリメータ部分である。

【0029】

本発明者によってこれまで検討されたコリメータ部分は、上部シールド13wの内径をΦ290.1mmとし、コリメータ12wの円板状プレート12awの端部と上部シールド13wとの距離を0.95mmとしていたが、本実施の形態であるコリメータ部分では、コリメータ12の円板状プレート12aの端部とアダプタリング9の内側端部との間のほぼ中心に上部シールド13が位置するように、上部シールド13の内径を、例えばΦ292〜295mm程度と広くし、コリメータ12の円板状プレート12aの端部と上部シールド13との距離を、例えば1.9mm程度と広くする。これにより、本実施の形態では、上部シールド部分の各部寸法を、例えば図3に示すように設定することができる。

【0030】

図3に、上部シールド部分の拡大図を示す。(a)は本実施の形態である上部シールド部分、(b)は本発明者が検討した上部シールド部分である。

【0031】

本発明者によってこれまで検討された上部シールド部分は、上部シールド13wの上部折曲部13awと下部折曲部13bwとの上下垂直位置の距離を29.47mmとし、上部シールド13wの下縁部の内径をΦ290.1mmとしていた。これに対し、本実施の形態である上部シールド部分では、上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を、例えば27.6〜22.4mm程度と短くし、上部シールド13の下縁部の内径を、例えばΦ292〜Φ295mm程度と広くする。

【0032】

さらに、本実施の形態では、台座リング部分の各部寸法を、例えば以下のように設定する。

【0033】

図4に、台座リング部分の拡大図を示す。(a)は本実施の形態である台座リング部分、(b)は本発明者が検討した台座リング部分である。

【0034】

本発明者によってこれまで検討された台座リング部分は、台座リング15wの内側端部を上部シールド13wの上縁部の内側端部よりも内側に設けて、台座リング15wの内径をΦ306.83mmとしていた。これに対し、本実施の形態である台座リング部分では、台座リング15の内側端部を上部シールド13の上縁部の内側端部と同じ位置または外側に設け、台座リング15の内径を、例えばΦ309〜Φ312.2mm程度と広くする。さらに、本発明者によってこれまで検討された台座リング部分では、台座リング15wの高さを5.1mmとしていたが、本実施の形態である台座リング部分では、台座リング15の高さを、例えば4.0mm程度と低くする。台座リング15の高さを4.0mmよりも低くすると、スパッタ粒子の回り込みが生じ、また取り付けねじ部の締め付け力が低下するため、4〜4.3mm程度の範囲が好ましい。

【0035】

以上のように、上部シールド部分および台座リング部分の各部寸法を設定することにより、本実施の形態では、例えば図5に示すようにターゲット3と上部シールド13との間の隙間量およびパッキングプレート11と台座リング15との間の隙間量を相対的に広くすることができる。なお、パッキングプレート11およびそれに固定されるターゲット3の形状として、例えば台座リング15に隣接する部分がパッキングプレート11のみの場合(例えば本実施の形態の図1)、パッキングプレート11およびターゲット3の場合、またはターゲット3のみの場合が考えられるが、以下の説明ではこれら全ての場合を含むものとし、例えばパッキングプレート(またはターゲット)と記載する。また、台座リング15に隣接する部分がパッキングプレート11のみであっても、パッキングプレート11は導電性材料であることから、パッキングプレート11と台座リング15との接触により、異常放電が容易に生じてしまう。

【0036】

図5に、ターゲット部分の拡大図を示す。(a)に、本実施の形態であるターゲットと上部シールドおよびパッキングプレート(またはターゲット)と台座リングとの隙間関係をまとめ、(b)に、本発明者が検討したターゲットと上部シールドおよびパッキングプレート(またはターゲット)と台座リングとの隙間関係をまとめる。

【0037】

前記図3を用いて説明したように、本実施の形態では、本発明者が検討したこれまでの上部シールド部分よりも上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を短くして、上部シールド13の下縁部の内径を広げることにより、ターゲット3の周縁と上部シールド13の下部折曲部との隙間S1を、本発明者が検討したこれまでの1.2mm(S1w)から、例えば1.8〜3.6mm程度へ広げることができる。さらに、前記図4を用いて説明したように、本実施の形態では、本発明者が検討したこれまでの台座リング部分よりも台座リング15の内径を広げることにより、パッキングプレート11(またはターゲット3)と台座リング15の内側端部との隙間S2を本発明者が検討したこれまでの1.6mm(S2w)から、例えば2.7〜4.3mm程度へ広げることができる。さらに、前記図4を用いて説明したように、本実施の形態では、本発明者が検討したこれまでの台座リング部分よりも台座リング15の高さを低くすることにより、台座リング15の上面と、その上部に位置するパッキングプレート11(またはターゲット3)との隙間S3を本発明者が検討したこれまでの1.65mm(S3w)から、例えば2.45〜2.75mm程度へ広げることができる。

【0038】

なお、本実施の形態では、ターゲット3の周辺部に位置する上部シールド13および台座リング15の各部寸法を変更することにより、ターゲット3の周縁と上部シールド13の下部折曲部との隙間S1、パッキングプレート11(またはターゲット3)と台座リング15の内側端部との隙間S2または台座リング15の上面と、その上部に位置するパッキングプレート11(またはターゲット3)との隙間S3を広げたが、ターゲット3またはパッキングプレート11の各部寸法を変更して上記隙間を広げることは可能である。しかし、パッキングプレート11は上部シールド13または台座リング15よりも高価であり、通常は、パッキングプレート11の形状を規格化(標準化)することで、その価格を下げている。このため、本願においては、ターゲット3およびパッキングプレート11の寸法を変更することなく、ターゲット3と上部シールド13との接触またはパッキングプレート11(またはターゲット3)と台座リング15との接触を防止し、コリメートスパッタ装置1の処理能力の向上をさせることのできる技術を提案した。

【0039】

次に、下部シールド14について説明する。前記図1に示すように、下部シールド14は、上昇して成膜処理が可能な位置にあるウエハステージ4とコリメータ12との間のチャンバ内壁面を保護するためのものである。下部シールド14の上部はねじ止めされ、コリメータ12を囲むようにしてウエハステージ4の周囲まで延びている。下部シールド14の自由縁部は上方に折り返されており、この部分は、ウエハステージ4が下降された際、クランプリング16を支持するようになっている。クランプリング16は、ウエハ5を処理する際、ウエハステージ4が上昇されたときにウエハ5をウエハステージ4に押さえ付け、ガス加熱のため、ウエハ5の裏面に圧力が均等に加わるようにするためのものである。また、この下部シールド14の上部に開口部が設けられており、そこから真空ポンプにより下部シールド14が取り囲んでいる空間が真空排気される。

【0040】

また、チャンバ本体7、アダプタリング9、コリメータ12、上部シールド13および下部シールド14は互いに電気的に接続されている。これに対して、ウエハステージ4はチャンバ本体7と電気的に絶縁されている。

【0041】

このように、本実施の形態によれば、上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を相対的に短くし(例えば27.6〜22.4mm程度)、上部シールド13の下縁部の内径を相対的に広くする(例えばΦ292〜Φ295mm程度)ことにより、ターゲット3と上部シールド13との間の隙間量を相対的に広くすることができ、さらに、台座リング15の内径を相対的に広くし(例えばΦ309〜Φ312.2mm程度)、台座リング15の高さを相対的に低くする(例えば4.0〜4.3mm程度)ことにより、パッキングプレート11(またはターゲット3)と台座リング15との間の隙間量を相対的に広くすることができる。これにより、ターゲット3と上部シールド13との接触またはパッキングプレート11(またはターゲット3)と台座リング15との接触が回避され、真空チャンバ2内を放電させた時の異常放電を防ぐことができる。

【0042】

例えば、コリメートスパッタ装置1のメンテナンス作業を終えた後、真空チャンバ2の立ち上げ作業は以下のように行われる。まず、メンテナンス作業を行う(例えば100分程度)。続いて真空チャンバ2内を真空排気して所定の真空度まで減圧し(例えば70分程度)、さらに真空チャンバ2内を加熱した後(例えば120分程度)、真空チャンバ2内を放電させる(例えば90分程度)。この放電では、製品用のウエハ5上に堆積されるチタン膜と同じレシピを用いてウエハステージ4の上面に載置されたダミーウエハ上にチタン膜を形成する。メンテナンス作業後のコリメータ12、上部シールド13、下部シールド14およびクランプリング16などのシールド類には残留分子が付着しており、この残留分子は加熱だけで除去することが難しい。このため、製品用のウエハ5上に堆積されるチタン膜と同じレシピを用いてスパッタリングを行い、ダミーウエハ上にチタン膜を形成すると同時に、シールド類にチタン膜を付着させ、残留分子をチタン膜で閉じこめることにより清浄な真空度を生成する。

【0043】

その後、コリメートスパッタ装置1のQC(Quality Control)が行われる(例えば130分程度)。QCでは、ダミーウエハ上に成膜されたチタン膜の膜厚、抵抗値および反射率などが規格値に入っているか、ダミーウエハ上の異物の数が規格値に入っているかなどが確認される。これら全てが規格値内であれば製品用のウエハが着工される。なお、このQCは、メンテナンス作業後だけでなく1回/2日程度の頻度で行ってもよい。

【0044】

ターゲット3と上部シールド13あるいはパッキングプレート11(またはターゲット3)と台座リング15とが接触した場合は、QC前の放電において異常放電が発生する。すなわち、上記接触は、メンテナンス作業、真空チャンバ2内の減圧および真空チャンバ2内の加熱を終えた後に発見されるものであり、異常放電が発見されると、再びメンテナンス作業、真空チャンバ2内の減圧および真空チャンバ2内の加熱の一連の作業が行われることになり、重なる作業による約290分(100分程度+70分程度+120分程度)の無駄な時間を要してしまう。

【0045】

しかしながら、前述したように、本実施の形態では、ターゲット3と上部シールド13あるいはパッキングプレート11(またはターゲット3)と台座リング15との接触を回避して、真空チャンバ2内を放電させた時の異常放電を防ぐことができるので、真空チャンバ2内の立ち上げ作業における上記無駄な時間を排除することができる。

【0046】

本発明者によってこれまで検討されたコリメートスパッタ装置1では、メンテナンス作業を、例えば1ヶ月に6〜7回程度行っており、そのうち、例えば4回の異常放電が発生していた。本発明により異常放電が無くなると、

290分/回×4回/月=1160分/月(19.3時間/月)

の無駄な時間を排除することができる。さらにこの無駄な時間の排除により、コリメートスパッタ装置1の稼動停止時間が短くなり、生産効率が向上する。例えば本発明者により、1台のコリメートスパッタ装置1の処理能力が、342.7枚/日から344.5枚/日へ向上することが確かめられている。

【0047】

本発明は、コリメートスパッタ装置1に限定されるものではなく、コリメータを備えないスパッタ装置にも適用することができる。次に、本実施の形態である半導体装置の製造方法で使用するスパッタリング装置(以下、単にスパッタ装置と記す)の他の例を説明する。図6は、例えばアルミニウム膜を成膜するスパッタ装置の構成を示す概略図である。

【0048】

スパッタ装置17は、アルミニウム膜の成膜用の装置であり、コリメータ12および下部シールド13が設置されていないことを除けば、前記図1に示したコリメートスパッタ装置1とほぼ同様の構成である。スパッタ装置17は、真空チャンバ2の上部開口部に配置されたアルミニウム製のターゲット18を備え、さらに、筒状の上部シールド19は、少なくとも2箇所の折曲部(上部折曲部19aおよび下部折曲部19b)で曲げられて、ターゲット18に平行な上縁部とターゲット18に垂直な下縁部とを有しており、その上縁部を台座リング20で押さえることによりアダプタリング9の上面に固定されている。上部シールド19は、ターゲット18を囲むようにしてウエハステージ4の周囲まで延びている。また、上部シールド19の自由縁部は上方に折り返されており、この部分は、ウエハステージ4が下降された際、クランプリング16を支持するようになっている。

【0049】

前記コリメートスパッタ装置1と同様に、上部シールド19の上部折曲部19aと下部折曲部19bとの上下垂直位置の距離を相対的に短くし、上部シールド19の下縁部の内径を相対的に広することにより、ターゲット18と上部シールド19との間の隙間量を相対的に広くし、さらに、台座リング20の内径を相対的に広くし、台座リング20の高さを相対的に低くするとすることにより、パッキングプレート11(またはターゲット18)と台座リング20との間の隙間量を相対的に広くしている。これにより、ターゲット18と上部シールド19あるいはパッキングプレート11(またはターゲット18)と台座リング20との接触を回避することができる。さらに、このスパッタ装置17にはコリメータが備わっていないので、コリメータによる上部シールド19の寸法の制約が無く、前記コリメートスパッタ装置1よりも、上記隙間量を大きくすることが可能である。

【0050】

次に、本実施の形態におけるコリメートスパッタ装置を使用して半導体集積回路装置を製造する工程を図7〜図12を用いて工程順に説明する。ここでは、デュアルゲート構成のCMOS(Complementary Metal Oxide Semiconductor)型集積回路を例示する。

【0051】

まず、図7に示すように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンからなる半導体基板(以下、単に基板と記す)21の主面に素子分離溝22を形成する。素子分離溝22は、素子分離領域の基板21をエッチングして形成され、その後、素子分離溝22の内部を含む基板1上にCVD(Chemical Vapor Deposition)法により酸化シリコン膜23を堆積し、続いて素子分離溝22の外部の不要な酸化シリコン膜23をCMP(Chemical Mechanical Polishing)法によって除去する。

【0052】

次に、基板21の一部にボロン(B)をイオン注入し、他の一部にリン(P)をイオン注入することによって、p型ウェル24およびn型ウェル25を形成した後、基板21をスチーム酸化することによって、p型ウェル24およびn型ウェル25のそれぞれの表面にゲート酸化膜26を形成する。

【0053】

次に、図8に示すように、p型ウェル24およびn型ウェル25のそれぞれの上部にゲート電極27を形成する。ゲート電極27を形成するには、例えばゲート酸化膜26の上部にCVD法により多結晶シリコン膜を堆積した後、p型ウェル24の上部の多結晶シリコン膜にリンをイオン注入し、n型ウェル25の上部の多結晶シリコン膜にボロンをイオン注入した後、レジストパターンをマスクにしたドライエッチングにより多結晶シリコン膜をパターニングする。

【0054】

次に、ゲート電極27をマスクとしてp型ウェル24にリンまたはヒ素(As)をイオン注入することによって低不純物濃度のn-型半導体領域28を形成し、ゲート電極27をマスクとしてn型ウェル25にボロンをイオン注入することによって低不純物濃度のp-型半導体領域29を形成する。

【0055】

次に、図9に示すように、基板21上にCVD法により堆積した窒化シリコン膜を異方的にエッチングすることによって、ゲート電極27の側壁にサイドウォール30を形成すると共に、基板21(n-型半導体領域28、p-型半導体領域29)の表面を露出させる。続いて、ゲート電極27およびサイドウォール30をマスクとしてp型ウェル24にリンまたはヒ素をイオン注入することによって、nMISQnのソース、ドレインを構成する高不純物濃度のn+型半導体領域31を形成し、ゲート電極27およびサイドウォール30をマスクとしてn型ウェル25にボロンをイオン注入することによって、pMISQpのソース、ドレインを構成する高不純物濃度のp+型半導体領域32を形成する。

【0056】

次に、基板21の表面をバッファードフッ酸によりバッチ洗浄した後、例えばサリサイド方式によってゲート電極27およびソース、ドレイン(n+型半導体領域31、p+型半導体領域32)のそれぞれの表面に、例えばコバルトダイシリサイド(CoSi2)またはニッケルダイシリサイド(NiSi2)を主成分とするシリサイド層33を形成する。ここまでの工程により、nMISQnおよびpMISQpが完成する。

【0057】

その後、図10に示すように、基板21上にCVD法により窒化シリコン膜34および酸化シリコン膜35を堆積し、続いてソース、ドレイン(n+型半導体領域31、p+型半導体領域32)のそれぞれの上部の酸化シリコン膜35および窒化シリコン膜34を順次ドライエッチングしてコンタクトホール36を形成した後、コンタクトホール36の内部を含む酸化シリコン膜35上に、バリア層として機能するチタン膜37を堆積する。

【0058】

上記チタン膜37は、例えば前述したコリメータスパッタ装置1を用いて堆積することができる。以下に、前記図1に記載したコリメータスパッタ装置1を用いてチタン膜37を成膜する一連の動作を説明する。まず、真空ポンプを作動させて真空チャンバ2内を所定の真空度まで減圧した後、アルゴンガス供給源から所定流量でアルゴンガスを真空チャンバ2内に導入する。次いで、ウエハステージ4の上面にウエハ5(基板21)を載置し、ウエハステージ4を上昇させて処理位置に配置する。続いて、直流電源を投入してターゲット3に負のバイアスをかけると、ターゲット3とウエハステージ4との間(より詳細にはターゲット3とコリメータ12との間)にプラズマが発生し、プラズマ中の正のアルゴンイオンが、負に耐電しているターゲット3を衝撃する。アルゴンイオンがターゲット3に衝突すると、ターゲット3からターゲット原子、すなわちチタンからなる粒子がはじき出される。このチタンはウエハ5(基板21)上に堆積されてチタン膜37を形成する。

【0059】

この成膜工程において、ターゲット3とウエハステージ4との間には、接地されたコリメータ12が配置されているため、ターゲット3からウエハステージ4へ向かうチタン粒子のうち実質的に垂直方向に進む粒子のみがコリメータ12の円板状プレート12aの孔を通過する。従って、ウエハ5(基板21)上にチタン粒子が付着して成膜するときには、ウエハ5(基板21)のコンタクトホール36の内部のカバレッジ率が高くなる。

【0060】

一方、垂直方向成分以外のチタン粒子は指向性を失い、例えばチャンバ内壁等に付着して真空チャンバ2における発塵源となるが、コリメートスパッタ装置1では、上部シールド13の下縁部がコリメータ12の支持枠12bの上面周縁部まで延びている。また円板状プレート12aを通過してもアルゴンとの衝突などにより指向性を失い、拡散する恐れがあるが、下部シールド14がコリメータ12を囲むようにしてウエハステージ4の周囲まで延びているので、真空チャンバ2内のチャンバ内壁にチタン粒子が付着するのを防ぐことができる。

【0061】

次に、図11に示すように、コンタクトホール36の内部を含む酸化シリコン膜35上に、例えばCVD法によりタングステン(W)膜を堆積した後、例えばCMP法またはドライエッチング法によりコンタクトホール36の内部以外のタングステン膜を除去し、コンタクトホール36の内部にプラグ38を形成する。

【0062】

次に、図12に示すように、スパッタリング法により、例えばチタン膜、アルミニウム膜およびチタン膜を順次成膜する。アルミニウム膜の形成には、前記図6に示したコリメートスパッタ装置17を用いることができる。その後、レジストパターンをマスクとしたドライエッチングにより半導体素子間の配線金属膜としてアルミ合金膜を形成し、第1層配線39を形成する。

【0063】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0064】

例えば、前記実施の形態では、6インチのウエハに適用した例を説明したが、12インチなど様々な大きさのウエハに適用することができる。

【0065】

また、前記実施の形態では、CMOS型集積回路の製造工程におけるチタン膜37の形成に適用した場合について説明したが、例えばサリサイド方式における金属膜(例えばコバルト膜、ニッケル膜またはコバルトニッケル膜)の形成等にも適用することができる。さらに、プリント配線基板に成膜する場合、液晶表示装置の製造方法において液晶パネルに成膜する場合または磁気ディスクまたはコンパクトディスクに成膜する場合等の成膜技術全般に適用することができる。

【産業上の利用可能性】

【0066】

本発明の半導体装置の製造方法は、物理的成膜手段を使用した枚葉式の成膜装置、特にコリメータを使用し、ターゲットとコリメータとの間にチャンバ内壁を保護するための筒状の上部シールドが設けられたスパッタリング装置に適用することができる。

【図面の簡単な説明】

【0067】

【図1】本発明の一実施の形態であるチタン膜の形成に用いるコリメートスパッタ装置の概略断面図である。

【図2】本発明の一実施の形態であるコリメートスパッタ装置に備わるコリメータ部の拡大図を示す。

【図3】本発明の一実施の形態であるコリメートスパッタ装置に備わる上部シールド部分の拡大図を示す。

【図4】本発明の一実施の形態であるコリメートスパッタ装置に備わる台座リング部分の拡大図を示す。

【図5】本発明の一実施の形態であるコリメートスパッタ装置に備わるターゲット部分の拡大図を示す。

【図6】本発明の一実施の形態であるアルミニウム膜の形成に用いるスパッタ装置の概略断面図である。

【図7】本発明の一実施の形態である半導体装置の製造工程の一例を示す半導体基板の要部断面図である。

【図8】図7に続く半導体装置の製造工程中の半導体基板の要部断面図である。

【図9】図8に続く半導体装置の製造工程中の半導体基板の要部断面図である。

【図10】図9に続く半導体装置の製造工程中の半導体基板の要部断面図である。

【図11】図10に続く半導体装置の製造工程中の半導体基板の要部断面図である。

【図12】図11に続く半導体装置の製造工程中の半導体基板の要部断面図である。

【符号の説明】

【0068】

1 コリメートスパッタ装置

2 真空チャンバ

3 ターゲット

3w ターゲット

4 ウエハステージ

5 ウエハ

6 ベロー

7 チャンバ本体

8 ノッチ

9 アダプタリング

10 セラミックリング

11 パッキングプレート

12 コリメータ

12a 円板状プレート

12b 支持枠

12w コリメータ

12aw 円板状プレート

13 上部シールド

13a 上部折曲部

13b 下部折曲部

13w 上部シールド

13aw 上部折曲部

13bw 下部折曲部

14 下部シールド

15 台座リング

15w 台座リング

16 クランプリング

17 スパッタ装置

18 ターゲット

19 上部シールド

19a 上部折曲部

19b 下部折曲部

20 台座リング

21 半導体基板

22 素子分離溝

23 酸化シリコン膜

24 p型ウェル

25 n型ウェル

26 ゲート酸化膜

27 ゲート電極

28 n-型半導体領域

29 p-型半導体領域

30 サイドウォール

31 n+型半導体領域

32 p+型半導体領域

33 シリサイド層

34 窒化シリコン膜

35 酸化シリコン膜

36 コンタクトホール

37 チタン膜

38 プラグ

39 第1層配線

Qn nチャネル型MIS・FET

Qp pチャネル型MIS・FET

S1 隙間

S2 隙間

S3 隙間

【技術分野】

【0001】

本発明は、半導体装置の製造技術に関し、特に、物理的成膜手段、例えばスパッタリング法によって半導体ウエハ上に薄膜を成膜する工程に適用して有効な技術に関するものである。

【背景技術】

【0002】

LSI(Large Scale Integration)の微細化により必要となった半導体ウエハ上のパターンの深い孔への薄膜配線形成に対して、従来のスパッタリング法では半導体ウエハの主面(回路形成面)に対して斜めに入射するスパッタ粒子が含まれるため、孔の底まで十分に膜が堆積する前に、孔の入口付近を成膜物質が塞いでしまう問題点があった。これを解決するために、いくつかの技術が開発されており、その1つとしてコリメートスパッタリング法がある。コリメートスパッタリング法は、ターゲットと半導体ウエハとの間に格子状に孔のあいたコリメータ(整合板)を設置し、斜め入射成分を除去するものである。

【0003】

例えばコリメータを用いて半導体ウエハに成膜するスパッタリング方法において、コリメータと半導体ウエハとの間に電圧を印加させながら成膜することで、コリメータから半導体ウエハ方向に発生した電界により、コリメータを斜めに通過したスパッタ粒子を半導体ウエハの法線方向に偏向させて堆積させる技術が特開平8−203828号公報(特許文献1)に開示されている。

【0004】

また、スパッタリング装置に、筒状の上部シールドおよび中間シールドをターゲットとコリメータとの間およびコリメータとペディスタルとの間にそれぞれ設けることにより、ターゲットに対して影となる部分の形成を制御して、コリメータの通過後に指向性を失ったスパッタ粒子による発塵しやすい低密度で脆弱な膜の形成の可能性を低くする技術が特開平10−176267号公報(特許文献2)に開示されている。

【0005】

また、マグネトロン上にターゲットを配し、ターゲットに対向して被加工物の基板を配置し、ターゲットと基板との間に、基板の法線方向に進行するスパッタ粒子を選択的に通過させるコリメータを配置してスパッタ蒸着を行うスパッタリング法において、処理ガスにArより比重の大きなガスを用いて、ターゲット面の垂直方向に強い指向性をもたせる技術が特許第2707951号明細書(特許文献3)に開示されている。

【特許文献1】特開平8−203828号公報

【特許文献2】特開平10−176267号公報

【特許文献3】特許第2707951号明細書

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、コリメータを用いたスパッタリング法については、以下に説明する種々の技術的課題が存在する。

【0007】

コリメータを備えるスパッタリング装置(以下、単にコリメートスパッタ装置と記す)においては、指向性のあるスパッタ粒子が高いエネルギーを持って到達しない部分が真空チャンバ内に存在する。この部分は、例えばチャンバ内壁であり、スパッタ粒子がガスの拡散により低いエネルギーを持ってチャンバ内壁に到達し、付着したスパッタ粒子により密度の低い膜が形成される。このような膜は付着力が小さいために剥離しやすく、真空チャンバ内において発塵源となる。

【0008】

そこで、真空チャンバ内のチャンバ内壁にスパッタ粒子が付着するのを防ぐために、例えばターゲットとコリメータとの間には、チャンバ内壁を保護するための筒状の上部シールドが設けられている(例えば上記特許文献3参照)。上部シールドの上縁部は台座リングによってアダプタリングにねじ止めされ、また上部シールドの下縁部はコリメータから一定の隙間をもって離間された状態で、コリメータの上面近傍まで延びており、上部シールドがターゲットを囲むようにしている。

【0009】

ところが、上記コリメートスパッタ装置では、ターゲットと上部シールドとの間またはターゲットと台座リングとの間の隙間量が少なく、さらに付着した膜を取り除くための洗浄または加熱により上部シールドが変形するため、例えばコリメートスパッタ装置のメンテナンス作業を行う度に上記隙間量が変わり、ターゲットと上部シールドまたはターゲットと台座リングとが接触するという問題が生じている。この接触は、メンテナンス作業を終えた後、真空チャンバ内を真空排気して所定の真空度まで減圧し、さらに真空チャンバ内を放電させることによって、初めて異常放電として確認されるものである。このため、ターゲットと上部シールドまたはターゲットと台座リングとの接触を確認するまでに多大な時間を要してしまう。また、ターゲットと上部シールドとの間またはターゲットと台座リングとの間の隙間量を修正するためには、再度真空チャンバ内を大気圧に戻し、上記隙間量を調整した後、真空チャンバ内を真空排気して所定の真空度まで減圧し、さらに真空チャンバ内を放電させることによって確認しなければならず、コリメートスパッタ装置の稼動停止時間が長くなり、生産効率が低下してしまう。

【0010】

本発明の目的は、コリメータを備えるスパッタリング装置の生産効率を向上させることのできる技術を提供することにある。

【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0013】

本発明は、上部シールドの上部折曲部と下部折曲部との上下垂直位置の距離を相対的に短く、上部シールドの下縁部の内径を相対的に広くして、ターゲットの周縁と上部シールドの下部折曲部との隙間を広くし、さらに台座リングの内径を相対的に広く、台座リングの高さを相対的に低くして、ターゲットと台座リングの内側端部との隙間および台座リングの上面とその上部に位置するターゲットとの隙間を相対的に広くすることにより、ターゲットと上部シールドとの間またはターゲットと台座リングとの間の隙間量を相対的に広くする。

【発明の効果】

【0014】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0015】

ターゲットと上部シールドまたはターゲットと台座リングとの接触が回避されて、真空チャンバ内を放電させた時の異常放電を防ぐことができる。これにより、メンテナンス作業後の真空チャンバ内の立ち上げ作業における無駄な時間を排除することができるので、スパッタリング装置の稼動停止時間が短くなり、生産効率が向上する。

【発明を実施するための最良の形態】

【0016】

以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

【0017】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0018】

さらに、以下の実施の形態において、ウエハとは、集積回路の製造に用いるシリコン単結晶基板(一般にほぼ平面円形状)、サファイア基板、ガラス基板、その他の絶縁、反絶縁または半導体基板等並びにそれらの複合的基板を言う。また、以下の実施の形態において半導体集積回路装置というときは、シリコンウエハやサファイア基板等の半導体または絶縁体基板上に作られるものだけでなく、特に、そうでない旨明示された場合を除き、TFT(Thin-Film-Transistor)およびSTN(Super-Twisted-Nematic)液晶等のようなガラス等の他の絶縁基板上に作られるもの等も含むものとする。

【0019】

さらに、以下の実施の形態において、電界効果トランジスタを代表するMIS・FET(Metal Insulator Semiconductor Field Effect Transistor)をMISと略し、nチャネル型のMIS・FETをnMISと略し、pチャネル型のMIS・FETをpMISと略す。

【0020】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0021】

本実施の形態である半導体装置の製造方法で使用するコリメートスパッタ装置の構成の一例を図1〜図5を用いて説明する。図1はコリメートスパッタ装置の構成を示す概略図、図2はコリメータ部分の拡大図、図3は上部シールド部分の拡大図、図4は台座リング部分の拡大図、図5はターゲット部分の拡大図である。

【0022】

図1に示すように、コリメートスパッタ装置1は、チタン(Ti)膜の成膜用の装置であり、真空チャンバ2と、その上部開口部に配置されたチタン製のターゲット3とを備えている。真空チャンバ2の内部には、ターゲット3と同軸にウエハステージ4が配置されており、その上面でウエハ5を支持するように構成されている。ウエハ5は、例えば直径が6インチの平面略円形状の半導体の薄板である。ウエハステージ4の下面には昇降機構を有する駆動軸がベロー6によって保護された状態で接続され、ウエハステージ4が上下運動可能となっている。

【0023】

さらに、真空チャンバ2は、導電性材料のチャンバ本体7と、チャンバ本体7のノッチ8に着脱可能に取り付けられる環状のアダプタリング9とを備えている。このアダプタリング9は導電性材料からなり、例えばステンレス鋼(SUS304)、アルミニウム(Al)またはチタン等から作られている。アダプタリング9の上面にはセラミックリング10を介して、ターゲット3を備えるパッキングプレート11が載置され、着脱可能に固定されている。このパッキングプレート11は導電性材料からなり、例えばアルミニウム等から作られており、ターゲット3とパッキングプレート11とは電気的に接続されている。また、本実施の形態では、ターゲット3が凸形状のパッキングプレート11の先端部に備わっているが、パッキングプレート11のほぼ全面にターゲット材料を備えてもよく、またはパッキングプレート11のほぼ全部をターゲット材料で構成してもよい。

【0024】

また、真空チャンバ2には、プロセスガスの供給手段としてアルゴン(Ar)ガス供給源および窒素(N2)ガス供給源が接続されており、さらに真空チャンバ2内を真空とするための真空ポンプが接続されている。なお、部材間にはO(オー)リングが設けられて真空チャンバ2の気密性を保つようにしてもよい。また、セラミックリング10によりチャンバ本体7等から絶縁されているターゲット3には、直流電源の負端子が電気配線により接続されており、直流電源の正端子は真空チャンバ2に接続されると共に接地されている。

【0025】

また、真空チャンバ2は、コリメータ12を備えている。コリメータ12は、例えば蜂の巣状に配列された断面六角形の孔を備えたチタン製の円板状プレート12aと、その外周部に取り付けられた支持枠12bとからなり、ターゲット3とウエハステージ4との間において、それらと平行かつ同軸に配列されるようになっている。

【0026】

また、真空チャンバ2には、チャンバ内壁面がスパッタ粒子により被覆されるのを防止するために、筒状の上部シールド13および筒状の下部シールド14が設けられている。これら上部シールド13および下部シールド14は導電性材料、例えばステンレス鋼から作られている。

【0027】

まず、上部シールド13について説明する。上部シールド13はアダプタリング9とコリメータ12との間のチャンバ内壁面を保護するためのものである。上部シールド13は、少なくとも2箇所の折曲部(上部折曲部13aおよび下部折曲部13b)で曲げられて、ターゲット3に平行な上縁部とターゲット3に垂直な下縁部とを有している。上部シールド13の上縁部はアダプタリング9の上面に台座リング15を用いて固定されており、また、上部シールド13の下縁部はコリメータ12から一定の隙間をもって離隔された状態でコリメータ12の上面近傍まで延びており、上部シールド13がターゲット3を囲むようにしている。

【0028】

図2に、コリメータ部分の拡大図を示す。(a)は本実施の形態であるコリメータ部分、(b)は本発明者が検討したコリメータ部分である。

【0029】

本発明者によってこれまで検討されたコリメータ部分は、上部シールド13wの内径をΦ290.1mmとし、コリメータ12wの円板状プレート12awの端部と上部シールド13wとの距離を0.95mmとしていたが、本実施の形態であるコリメータ部分では、コリメータ12の円板状プレート12aの端部とアダプタリング9の内側端部との間のほぼ中心に上部シールド13が位置するように、上部シールド13の内径を、例えばΦ292〜295mm程度と広くし、コリメータ12の円板状プレート12aの端部と上部シールド13との距離を、例えば1.9mm程度と広くする。これにより、本実施の形態では、上部シールド部分の各部寸法を、例えば図3に示すように設定することができる。

【0030】

図3に、上部シールド部分の拡大図を示す。(a)は本実施の形態である上部シールド部分、(b)は本発明者が検討した上部シールド部分である。

【0031】

本発明者によってこれまで検討された上部シールド部分は、上部シールド13wの上部折曲部13awと下部折曲部13bwとの上下垂直位置の距離を29.47mmとし、上部シールド13wの下縁部の内径をΦ290.1mmとしていた。これに対し、本実施の形態である上部シールド部分では、上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を、例えば27.6〜22.4mm程度と短くし、上部シールド13の下縁部の内径を、例えばΦ292〜Φ295mm程度と広くする。

【0032】

さらに、本実施の形態では、台座リング部分の各部寸法を、例えば以下のように設定する。

【0033】

図4に、台座リング部分の拡大図を示す。(a)は本実施の形態である台座リング部分、(b)は本発明者が検討した台座リング部分である。

【0034】

本発明者によってこれまで検討された台座リング部分は、台座リング15wの内側端部を上部シールド13wの上縁部の内側端部よりも内側に設けて、台座リング15wの内径をΦ306.83mmとしていた。これに対し、本実施の形態である台座リング部分では、台座リング15の内側端部を上部シールド13の上縁部の内側端部と同じ位置または外側に設け、台座リング15の内径を、例えばΦ309〜Φ312.2mm程度と広くする。さらに、本発明者によってこれまで検討された台座リング部分では、台座リング15wの高さを5.1mmとしていたが、本実施の形態である台座リング部分では、台座リング15の高さを、例えば4.0mm程度と低くする。台座リング15の高さを4.0mmよりも低くすると、スパッタ粒子の回り込みが生じ、また取り付けねじ部の締め付け力が低下するため、4〜4.3mm程度の範囲が好ましい。

【0035】

以上のように、上部シールド部分および台座リング部分の各部寸法を設定することにより、本実施の形態では、例えば図5に示すようにターゲット3と上部シールド13との間の隙間量およびパッキングプレート11と台座リング15との間の隙間量を相対的に広くすることができる。なお、パッキングプレート11およびそれに固定されるターゲット3の形状として、例えば台座リング15に隣接する部分がパッキングプレート11のみの場合(例えば本実施の形態の図1)、パッキングプレート11およびターゲット3の場合、またはターゲット3のみの場合が考えられるが、以下の説明ではこれら全ての場合を含むものとし、例えばパッキングプレート(またはターゲット)と記載する。また、台座リング15に隣接する部分がパッキングプレート11のみであっても、パッキングプレート11は導電性材料であることから、パッキングプレート11と台座リング15との接触により、異常放電が容易に生じてしまう。

【0036】

図5に、ターゲット部分の拡大図を示す。(a)に、本実施の形態であるターゲットと上部シールドおよびパッキングプレート(またはターゲット)と台座リングとの隙間関係をまとめ、(b)に、本発明者が検討したターゲットと上部シールドおよびパッキングプレート(またはターゲット)と台座リングとの隙間関係をまとめる。

【0037】

前記図3を用いて説明したように、本実施の形態では、本発明者が検討したこれまでの上部シールド部分よりも上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を短くして、上部シールド13の下縁部の内径を広げることにより、ターゲット3の周縁と上部シールド13の下部折曲部との隙間S1を、本発明者が検討したこれまでの1.2mm(S1w)から、例えば1.8〜3.6mm程度へ広げることができる。さらに、前記図4を用いて説明したように、本実施の形態では、本発明者が検討したこれまでの台座リング部分よりも台座リング15の内径を広げることにより、パッキングプレート11(またはターゲット3)と台座リング15の内側端部との隙間S2を本発明者が検討したこれまでの1.6mm(S2w)から、例えば2.7〜4.3mm程度へ広げることができる。さらに、前記図4を用いて説明したように、本実施の形態では、本発明者が検討したこれまでの台座リング部分よりも台座リング15の高さを低くすることにより、台座リング15の上面と、その上部に位置するパッキングプレート11(またはターゲット3)との隙間S3を本発明者が検討したこれまでの1.65mm(S3w)から、例えば2.45〜2.75mm程度へ広げることができる。

【0038】

なお、本実施の形態では、ターゲット3の周辺部に位置する上部シールド13および台座リング15の各部寸法を変更することにより、ターゲット3の周縁と上部シールド13の下部折曲部との隙間S1、パッキングプレート11(またはターゲット3)と台座リング15の内側端部との隙間S2または台座リング15の上面と、その上部に位置するパッキングプレート11(またはターゲット3)との隙間S3を広げたが、ターゲット3またはパッキングプレート11の各部寸法を変更して上記隙間を広げることは可能である。しかし、パッキングプレート11は上部シールド13または台座リング15よりも高価であり、通常は、パッキングプレート11の形状を規格化(標準化)することで、その価格を下げている。このため、本願においては、ターゲット3およびパッキングプレート11の寸法を変更することなく、ターゲット3と上部シールド13との接触またはパッキングプレート11(またはターゲット3)と台座リング15との接触を防止し、コリメートスパッタ装置1の処理能力の向上をさせることのできる技術を提案した。

【0039】

次に、下部シールド14について説明する。前記図1に示すように、下部シールド14は、上昇して成膜処理が可能な位置にあるウエハステージ4とコリメータ12との間のチャンバ内壁面を保護するためのものである。下部シールド14の上部はねじ止めされ、コリメータ12を囲むようにしてウエハステージ4の周囲まで延びている。下部シールド14の自由縁部は上方に折り返されており、この部分は、ウエハステージ4が下降された際、クランプリング16を支持するようになっている。クランプリング16は、ウエハ5を処理する際、ウエハステージ4が上昇されたときにウエハ5をウエハステージ4に押さえ付け、ガス加熱のため、ウエハ5の裏面に圧力が均等に加わるようにするためのものである。また、この下部シールド14の上部に開口部が設けられており、そこから真空ポンプにより下部シールド14が取り囲んでいる空間が真空排気される。

【0040】

また、チャンバ本体7、アダプタリング9、コリメータ12、上部シールド13および下部シールド14は互いに電気的に接続されている。これに対して、ウエハステージ4はチャンバ本体7と電気的に絶縁されている。

【0041】

このように、本実施の形態によれば、上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を相対的に短くし(例えば27.6〜22.4mm程度)、上部シールド13の下縁部の内径を相対的に広くする(例えばΦ292〜Φ295mm程度)ことにより、ターゲット3と上部シールド13との間の隙間量を相対的に広くすることができ、さらに、台座リング15の内径を相対的に広くし(例えばΦ309〜Φ312.2mm程度)、台座リング15の高さを相対的に低くする(例えば4.0〜4.3mm程度)ことにより、パッキングプレート11(またはターゲット3)と台座リング15との間の隙間量を相対的に広くすることができる。これにより、ターゲット3と上部シールド13との接触またはパッキングプレート11(またはターゲット3)と台座リング15との接触が回避され、真空チャンバ2内を放電させた時の異常放電を防ぐことができる。

【0042】

例えば、コリメートスパッタ装置1のメンテナンス作業を終えた後、真空チャンバ2の立ち上げ作業は以下のように行われる。まず、メンテナンス作業を行う(例えば100分程度)。続いて真空チャンバ2内を真空排気して所定の真空度まで減圧し(例えば70分程度)、さらに真空チャンバ2内を加熱した後(例えば120分程度)、真空チャンバ2内を放電させる(例えば90分程度)。この放電では、製品用のウエハ5上に堆積されるチタン膜と同じレシピを用いてウエハステージ4の上面に載置されたダミーウエハ上にチタン膜を形成する。メンテナンス作業後のコリメータ12、上部シールド13、下部シールド14およびクランプリング16などのシールド類には残留分子が付着しており、この残留分子は加熱だけで除去することが難しい。このため、製品用のウエハ5上に堆積されるチタン膜と同じレシピを用いてスパッタリングを行い、ダミーウエハ上にチタン膜を形成すると同時に、シールド類にチタン膜を付着させ、残留分子をチタン膜で閉じこめることにより清浄な真空度を生成する。

【0043】

その後、コリメートスパッタ装置1のQC(Quality Control)が行われる(例えば130分程度)。QCでは、ダミーウエハ上に成膜されたチタン膜の膜厚、抵抗値および反射率などが規格値に入っているか、ダミーウエハ上の異物の数が規格値に入っているかなどが確認される。これら全てが規格値内であれば製品用のウエハが着工される。なお、このQCは、メンテナンス作業後だけでなく1回/2日程度の頻度で行ってもよい。

【0044】

ターゲット3と上部シールド13あるいはパッキングプレート11(またはターゲット3)と台座リング15とが接触した場合は、QC前の放電において異常放電が発生する。すなわち、上記接触は、メンテナンス作業、真空チャンバ2内の減圧および真空チャンバ2内の加熱を終えた後に発見されるものであり、異常放電が発見されると、再びメンテナンス作業、真空チャンバ2内の減圧および真空チャンバ2内の加熱の一連の作業が行われることになり、重なる作業による約290分(100分程度+70分程度+120分程度)の無駄な時間を要してしまう。

【0045】

しかしながら、前述したように、本実施の形態では、ターゲット3と上部シールド13あるいはパッキングプレート11(またはターゲット3)と台座リング15との接触を回避して、真空チャンバ2内を放電させた時の異常放電を防ぐことができるので、真空チャンバ2内の立ち上げ作業における上記無駄な時間を排除することができる。

【0046】

本発明者によってこれまで検討されたコリメートスパッタ装置1では、メンテナンス作業を、例えば1ヶ月に6〜7回程度行っており、そのうち、例えば4回の異常放電が発生していた。本発明により異常放電が無くなると、

290分/回×4回/月=1160分/月(19.3時間/月)

の無駄な時間を排除することができる。さらにこの無駄な時間の排除により、コリメートスパッタ装置1の稼動停止時間が短くなり、生産効率が向上する。例えば本発明者により、1台のコリメートスパッタ装置1の処理能力が、342.7枚/日から344.5枚/日へ向上することが確かめられている。

【0047】

本発明は、コリメートスパッタ装置1に限定されるものではなく、コリメータを備えないスパッタ装置にも適用することができる。次に、本実施の形態である半導体装置の製造方法で使用するスパッタリング装置(以下、単にスパッタ装置と記す)の他の例を説明する。図6は、例えばアルミニウム膜を成膜するスパッタ装置の構成を示す概略図である。

【0048】

スパッタ装置17は、アルミニウム膜の成膜用の装置であり、コリメータ12および下部シールド13が設置されていないことを除けば、前記図1に示したコリメートスパッタ装置1とほぼ同様の構成である。スパッタ装置17は、真空チャンバ2の上部開口部に配置されたアルミニウム製のターゲット18を備え、さらに、筒状の上部シールド19は、少なくとも2箇所の折曲部(上部折曲部19aおよび下部折曲部19b)で曲げられて、ターゲット18に平行な上縁部とターゲット18に垂直な下縁部とを有しており、その上縁部を台座リング20で押さえることによりアダプタリング9の上面に固定されている。上部シールド19は、ターゲット18を囲むようにしてウエハステージ4の周囲まで延びている。また、上部シールド19の自由縁部は上方に折り返されており、この部分は、ウエハステージ4が下降された際、クランプリング16を支持するようになっている。

【0049】

前記コリメートスパッタ装置1と同様に、上部シールド19の上部折曲部19aと下部折曲部19bとの上下垂直位置の距離を相対的に短くし、上部シールド19の下縁部の内径を相対的に広することにより、ターゲット18と上部シールド19との間の隙間量を相対的に広くし、さらに、台座リング20の内径を相対的に広くし、台座リング20の高さを相対的に低くするとすることにより、パッキングプレート11(またはターゲット18)と台座リング20との間の隙間量を相対的に広くしている。これにより、ターゲット18と上部シールド19あるいはパッキングプレート11(またはターゲット18)と台座リング20との接触を回避することができる。さらに、このスパッタ装置17にはコリメータが備わっていないので、コリメータによる上部シールド19の寸法の制約が無く、前記コリメートスパッタ装置1よりも、上記隙間量を大きくすることが可能である。

【0050】

次に、本実施の形態におけるコリメートスパッタ装置を使用して半導体集積回路装置を製造する工程を図7〜図12を用いて工程順に説明する。ここでは、デュアルゲート構成のCMOS(Complementary Metal Oxide Semiconductor)型集積回路を例示する。

【0051】

まず、図7に示すように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンからなる半導体基板(以下、単に基板と記す)21の主面に素子分離溝22を形成する。素子分離溝22は、素子分離領域の基板21をエッチングして形成され、その後、素子分離溝22の内部を含む基板1上にCVD(Chemical Vapor Deposition)法により酸化シリコン膜23を堆積し、続いて素子分離溝22の外部の不要な酸化シリコン膜23をCMP(Chemical Mechanical Polishing)法によって除去する。

【0052】

次に、基板21の一部にボロン(B)をイオン注入し、他の一部にリン(P)をイオン注入することによって、p型ウェル24およびn型ウェル25を形成した後、基板21をスチーム酸化することによって、p型ウェル24およびn型ウェル25のそれぞれの表面にゲート酸化膜26を形成する。

【0053】

次に、図8に示すように、p型ウェル24およびn型ウェル25のそれぞれの上部にゲート電極27を形成する。ゲート電極27を形成するには、例えばゲート酸化膜26の上部にCVD法により多結晶シリコン膜を堆積した後、p型ウェル24の上部の多結晶シリコン膜にリンをイオン注入し、n型ウェル25の上部の多結晶シリコン膜にボロンをイオン注入した後、レジストパターンをマスクにしたドライエッチングにより多結晶シリコン膜をパターニングする。

【0054】

次に、ゲート電極27をマスクとしてp型ウェル24にリンまたはヒ素(As)をイオン注入することによって低不純物濃度のn-型半導体領域28を形成し、ゲート電極27をマスクとしてn型ウェル25にボロンをイオン注入することによって低不純物濃度のp-型半導体領域29を形成する。

【0055】

次に、図9に示すように、基板21上にCVD法により堆積した窒化シリコン膜を異方的にエッチングすることによって、ゲート電極27の側壁にサイドウォール30を形成すると共に、基板21(n-型半導体領域28、p-型半導体領域29)の表面を露出させる。続いて、ゲート電極27およびサイドウォール30をマスクとしてp型ウェル24にリンまたはヒ素をイオン注入することによって、nMISQnのソース、ドレインを構成する高不純物濃度のn+型半導体領域31を形成し、ゲート電極27およびサイドウォール30をマスクとしてn型ウェル25にボロンをイオン注入することによって、pMISQpのソース、ドレインを構成する高不純物濃度のp+型半導体領域32を形成する。

【0056】

次に、基板21の表面をバッファードフッ酸によりバッチ洗浄した後、例えばサリサイド方式によってゲート電極27およびソース、ドレイン(n+型半導体領域31、p+型半導体領域32)のそれぞれの表面に、例えばコバルトダイシリサイド(CoSi2)またはニッケルダイシリサイド(NiSi2)を主成分とするシリサイド層33を形成する。ここまでの工程により、nMISQnおよびpMISQpが完成する。

【0057】

その後、図10に示すように、基板21上にCVD法により窒化シリコン膜34および酸化シリコン膜35を堆積し、続いてソース、ドレイン(n+型半導体領域31、p+型半導体領域32)のそれぞれの上部の酸化シリコン膜35および窒化シリコン膜34を順次ドライエッチングしてコンタクトホール36を形成した後、コンタクトホール36の内部を含む酸化シリコン膜35上に、バリア層として機能するチタン膜37を堆積する。

【0058】

上記チタン膜37は、例えば前述したコリメータスパッタ装置1を用いて堆積することができる。以下に、前記図1に記載したコリメータスパッタ装置1を用いてチタン膜37を成膜する一連の動作を説明する。まず、真空ポンプを作動させて真空チャンバ2内を所定の真空度まで減圧した後、アルゴンガス供給源から所定流量でアルゴンガスを真空チャンバ2内に導入する。次いで、ウエハステージ4の上面にウエハ5(基板21)を載置し、ウエハステージ4を上昇させて処理位置に配置する。続いて、直流電源を投入してターゲット3に負のバイアスをかけると、ターゲット3とウエハステージ4との間(より詳細にはターゲット3とコリメータ12との間)にプラズマが発生し、プラズマ中の正のアルゴンイオンが、負に耐電しているターゲット3を衝撃する。アルゴンイオンがターゲット3に衝突すると、ターゲット3からターゲット原子、すなわちチタンからなる粒子がはじき出される。このチタンはウエハ5(基板21)上に堆積されてチタン膜37を形成する。

【0059】

この成膜工程において、ターゲット3とウエハステージ4との間には、接地されたコリメータ12が配置されているため、ターゲット3からウエハステージ4へ向かうチタン粒子のうち実質的に垂直方向に進む粒子のみがコリメータ12の円板状プレート12aの孔を通過する。従って、ウエハ5(基板21)上にチタン粒子が付着して成膜するときには、ウエハ5(基板21)のコンタクトホール36の内部のカバレッジ率が高くなる。

【0060】

一方、垂直方向成分以外のチタン粒子は指向性を失い、例えばチャンバ内壁等に付着して真空チャンバ2における発塵源となるが、コリメートスパッタ装置1では、上部シールド13の下縁部がコリメータ12の支持枠12bの上面周縁部まで延びている。また円板状プレート12aを通過してもアルゴンとの衝突などにより指向性を失い、拡散する恐れがあるが、下部シールド14がコリメータ12を囲むようにしてウエハステージ4の周囲まで延びているので、真空チャンバ2内のチャンバ内壁にチタン粒子が付着するのを防ぐことができる。

【0061】

次に、図11に示すように、コンタクトホール36の内部を含む酸化シリコン膜35上に、例えばCVD法によりタングステン(W)膜を堆積した後、例えばCMP法またはドライエッチング法によりコンタクトホール36の内部以外のタングステン膜を除去し、コンタクトホール36の内部にプラグ38を形成する。

【0062】

次に、図12に示すように、スパッタリング法により、例えばチタン膜、アルミニウム膜およびチタン膜を順次成膜する。アルミニウム膜の形成には、前記図6に示したコリメートスパッタ装置17を用いることができる。その後、レジストパターンをマスクとしたドライエッチングにより半導体素子間の配線金属膜としてアルミ合金膜を形成し、第1層配線39を形成する。

【0063】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0064】

例えば、前記実施の形態では、6インチのウエハに適用した例を説明したが、12インチなど様々な大きさのウエハに適用することができる。

【0065】

また、前記実施の形態では、CMOS型集積回路の製造工程におけるチタン膜37の形成に適用した場合について説明したが、例えばサリサイド方式における金属膜(例えばコバルト膜、ニッケル膜またはコバルトニッケル膜)の形成等にも適用することができる。さらに、プリント配線基板に成膜する場合、液晶表示装置の製造方法において液晶パネルに成膜する場合または磁気ディスクまたはコンパクトディスクに成膜する場合等の成膜技術全般に適用することができる。

【産業上の利用可能性】

【0066】

本発明の半導体装置の製造方法は、物理的成膜手段を使用した枚葉式の成膜装置、特にコリメータを使用し、ターゲットとコリメータとの間にチャンバ内壁を保護するための筒状の上部シールドが設けられたスパッタリング装置に適用することができる。

【図面の簡単な説明】

【0067】

【図1】本発明の一実施の形態であるチタン膜の形成に用いるコリメートスパッタ装置の概略断面図である。

【図2】本発明の一実施の形態であるコリメートスパッタ装置に備わるコリメータ部の拡大図を示す。

【図3】本発明の一実施の形態であるコリメートスパッタ装置に備わる上部シールド部分の拡大図を示す。

【図4】本発明の一実施の形態であるコリメートスパッタ装置に備わる台座リング部分の拡大図を示す。

【図5】本発明の一実施の形態であるコリメートスパッタ装置に備わるターゲット部分の拡大図を示す。

【図6】本発明の一実施の形態であるアルミニウム膜の形成に用いるスパッタ装置の概略断面図である。

【図7】本発明の一実施の形態である半導体装置の製造工程の一例を示す半導体基板の要部断面図である。

【図8】図7に続く半導体装置の製造工程中の半導体基板の要部断面図である。

【図9】図8に続く半導体装置の製造工程中の半導体基板の要部断面図である。

【図10】図9に続く半導体装置の製造工程中の半導体基板の要部断面図である。

【図11】図10に続く半導体装置の製造工程中の半導体基板の要部断面図である。

【図12】図11に続く半導体装置の製造工程中の半導体基板の要部断面図である。

【符号の説明】

【0068】

1 コリメートスパッタ装置

2 真空チャンバ

3 ターゲット

3w ターゲット

4 ウエハステージ

5 ウエハ

6 ベロー

7 チャンバ本体

8 ノッチ

9 アダプタリング

10 セラミックリング

11 パッキングプレート

12 コリメータ

12a 円板状プレート

12b 支持枠

12w コリメータ

12aw 円板状プレート

13 上部シールド

13a 上部折曲部

13b 下部折曲部

13w 上部シールド

13aw 上部折曲部

13bw 下部折曲部

14 下部シールド

15 台座リング

15w 台座リング

16 クランプリング

17 スパッタ装置

18 ターゲット

19 上部シールド

19a 上部折曲部

19b 下部折曲部

20 台座リング

21 半導体基板

22 素子分離溝

23 酸化シリコン膜

24 p型ウェル

25 n型ウェル

26 ゲート酸化膜

27 ゲート電極

28 n-型半導体領域

29 p-型半導体領域

30 サイドウォール

31 n+型半導体領域

32 p+型半導体領域

33 シリサイド層

34 窒化シリコン膜

35 酸化シリコン膜

36 コンタクトホール

37 チタン膜

38 プラグ

39 第1層配線

Qn nチャネル型MIS・FET

Qp pチャネル型MIS・FET

S1 隙間

S2 隙間

S3 隙間

【特許請求の範囲】

【請求項1】

チャンバ本体と、前記チャンバ本体の上部に着脱可能に設けられたアダプタリングと、前記アダプタリングに着脱可能に設けられ、パッキングプレートに支持されてウエハの主面に対向するように設けられたターゲットと、少なくとも上部および下部の2箇所の折曲部で曲げられて前記ターゲットに平行な上縁部と前記ターゲットに垂直な下縁部とを有し、前記ターゲットを囲む筒状の上部シールドと、前記上部シールドの上縁部を前記アダプタリングに固定する台座リングとを備えるスパッタリング装置によって前記ウエハの主面に膜を形成する工程を含む半導体装置の製造方法であって、

前記ターゲットの周縁と前記上部シールドの下部折曲部との隙間が1.8〜3.6mm程度であることを特徴とする半導体装置の製造方法。

【請求項2】

チャンバ本体と、前記チャンバ本体の上部に着脱可能に設けられたアダプタリングと、前記アダプタリングに着脱可能に設けられ、パッキングプレートに支持されてウエハの主面に対向するように設けられたターゲットと、少なくとも2箇所の折曲部で曲げられて前記ターゲットに平行な上縁部と前記ターゲットに垂直な下縁部とを有し、前記ターゲットを囲む筒状の上部シールドと、前記上部シールドの上縁部を前記アダプタリングに固定する台座リングとを備えるスパッタリング装置によって前記ウエハの主面に膜を形成する工程を含む半導体装置の製造方法であって、

前記台座リングの内側端部が前記上部シールドの上縁部の内側端部と同じ位置または外側に設けられ、前記ターゲットまたは前記パッキングプレートと前記台座リングの内側端部との隙間が2.7〜4.3mm程度であることを特徴とする半導体装置の製造方法。

【請求項3】

チャンバ本体と、前記チャンバ本体の上部に着脱可能に設けられたアダプタリングと、前記アダプタリングに着脱可能に設けられ、パッキングプレートに支持されてウエハの主面に対向するように設けられたターゲットと、少なくとも2箇所の折曲部で曲げられて前記ターゲットに平行な上縁部と前記ターゲットに垂直な下縁部とを有し、前記ターゲットを囲む筒状の上部シールドと、前記上部シールドの上縁部を前記アダプタリングに固定する台座リングとを備えるスパッタリング装置によって前記ウエハの主面に膜を形成する工程を含む半導体装置の製造方法であって、

前記台座リングの上面と前記台座リングの上部に位置する前記ダーゲットまたは前記パッキングプレートとの隙間が2.45〜2.75mm程度であることを特徴とする半導体装置の製造方法。

【請求項4】

チャンバ本体と、前記チャンバ本体の上部に着脱可能に設けられたアダプタリングと、前記アダプタリングに着脱可能に設けられ、パッキングプレートに支持されてウエハの主面に対向するように設けられたターゲットと、孔が形成された円板状プレートを中央部に有し、その外周部に前記アダプタリングに支持される支持枠が取り付けられて、前記ウエハと前記ターゲットとの間に配置されたコリメータと、少なくとも2箇所の折曲部で曲げられて前記ターゲットに平行な上縁部と前記ターゲットに垂直な下縁部とを有し、前記ターゲットを囲む筒状の上部シールドと、前記上部シールドの上縁部を前記アダプタリングに固定する台座リングとを備えるスパッタリング装置によって前記ウエハの主面に膜を形成する工程を含む半導体装置の製造方法であって、

前記上部シールドの下端が前記コリメータの前記円板状プレートの端部とアダプタリングの内側端部との間のほぼ中心に位置することを特徴とする半導体装置の製造方法。

【請求項1】

チャンバ本体と、前記チャンバ本体の上部に着脱可能に設けられたアダプタリングと、前記アダプタリングに着脱可能に設けられ、パッキングプレートに支持されてウエハの主面に対向するように設けられたターゲットと、少なくとも上部および下部の2箇所の折曲部で曲げられて前記ターゲットに平行な上縁部と前記ターゲットに垂直な下縁部とを有し、前記ターゲットを囲む筒状の上部シールドと、前記上部シールドの上縁部を前記アダプタリングに固定する台座リングとを備えるスパッタリング装置によって前記ウエハの主面に膜を形成する工程を含む半導体装置の製造方法であって、

前記ターゲットの周縁と前記上部シールドの下部折曲部との隙間が1.8〜3.6mm程度であることを特徴とする半導体装置の製造方法。

【請求項2】

チャンバ本体と、前記チャンバ本体の上部に着脱可能に設けられたアダプタリングと、前記アダプタリングに着脱可能に設けられ、パッキングプレートに支持されてウエハの主面に対向するように設けられたターゲットと、少なくとも2箇所の折曲部で曲げられて前記ターゲットに平行な上縁部と前記ターゲットに垂直な下縁部とを有し、前記ターゲットを囲む筒状の上部シールドと、前記上部シールドの上縁部を前記アダプタリングに固定する台座リングとを備えるスパッタリング装置によって前記ウエハの主面に膜を形成する工程を含む半導体装置の製造方法であって、

前記台座リングの内側端部が前記上部シールドの上縁部の内側端部と同じ位置または外側に設けられ、前記ターゲットまたは前記パッキングプレートと前記台座リングの内側端部との隙間が2.7〜4.3mm程度であることを特徴とする半導体装置の製造方法。

【請求項3】

チャンバ本体と、前記チャンバ本体の上部に着脱可能に設けられたアダプタリングと、前記アダプタリングに着脱可能に設けられ、パッキングプレートに支持されてウエハの主面に対向するように設けられたターゲットと、少なくとも2箇所の折曲部で曲げられて前記ターゲットに平行な上縁部と前記ターゲットに垂直な下縁部とを有し、前記ターゲットを囲む筒状の上部シールドと、前記上部シールドの上縁部を前記アダプタリングに固定する台座リングとを備えるスパッタリング装置によって前記ウエハの主面に膜を形成する工程を含む半導体装置の製造方法であって、

前記台座リングの上面と前記台座リングの上部に位置する前記ダーゲットまたは前記パッキングプレートとの隙間が2.45〜2.75mm程度であることを特徴とする半導体装置の製造方法。

【請求項4】

チャンバ本体と、前記チャンバ本体の上部に着脱可能に設けられたアダプタリングと、前記アダプタリングに着脱可能に設けられ、パッキングプレートに支持されてウエハの主面に対向するように設けられたターゲットと、孔が形成された円板状プレートを中央部に有し、その外周部に前記アダプタリングに支持される支持枠が取り付けられて、前記ウエハと前記ターゲットとの間に配置されたコリメータと、少なくとも2箇所の折曲部で曲げられて前記ターゲットに平行な上縁部と前記ターゲットに垂直な下縁部とを有し、前記ターゲットを囲む筒状の上部シールドと、前記上部シールドの上縁部を前記アダプタリングに固定する台座リングとを備えるスパッタリング装置によって前記ウエハの主面に膜を形成する工程を含む半導体装置の製造方法であって、

前記上部シールドの下端が前記コリメータの前記円板状プレートの端部とアダプタリングの内側端部との間のほぼ中心に位置することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2006−37120(P2006−37120A)

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願番号】特願2004−214117(P2004−214117)

【出願日】平成16年7月22日(2004.7.22)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願日】平成16年7月22日(2004.7.22)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]