半導体装置の製造方法

【課題】 抵抗率のばらつきによる抵抗値のばらつきをもなくすため、抵抗素子の抵抗値を正確に知ることが可能であって、かつ、抵抗値を知るために回路領域が制限されることがない半導体装置の製造方法を提供する。

【解決手段】 抵抗素子を構成するポリシリコン膜と共にスクライブライン9上にもポリシリコン膜を成膜し、スクライブライン9上に成膜されたポリシリコン膜をパターニングし、モニタパターン7を形成する。また、モニタパターン7を使ったポリシリコン膜の抵抗率の測定結果に基づいて、抵抗素子を構成するポリシリコン膜を、このポリシリコン膜よりも上方に設けられる膜と同時にエッチングする。

【解決手段】 抵抗素子を構成するポリシリコン膜と共にスクライブライン9上にもポリシリコン膜を成膜し、スクライブライン9上に成膜されたポリシリコン膜をパターニングし、モニタパターン7を形成する。また、モニタパターン7を使ったポリシリコン膜の抵抗率の測定結果に基づいて、抵抗素子を構成するポリシリコン膜を、このポリシリコン膜よりも上方に設けられる膜と同時にエッチングする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、成膜工程を含む半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置は、半導体の電気特性を利用して動作する回路であって、トランジスタ等の能動素子や抵抗等の受動素子とを組み合わせて形成されている。

ところで、素子は、多くが各部材を材料にした膜の生成(成膜)と、成膜された膜のパターニングとによって形成される。各要素の電気的特性は、材料の特性のばらつきや成膜条件、パターニング後の寸法や形状のばらつきによって変化する。特に、抵抗素子のばらつきは、素子全体の電気特性に大きく影響する。このため、抵抗素子の抵抗値を一定に保つことを目的とした発明が、従来から提案されている。

【0003】

このような従来技術として、例えば、特許文献1に記載された発明がある。特許文献1に記載された発明は、抵抗素子のパターニング工程で形成されるマスクパターンのばらつきを防ぐことを目的にしてなされている。具体的には、フォトマスク上に、抵抗素子をパターニングするためのマスクパターンと、このマスクパターンの光の干渉による寸法変動を抑えるためのマスクパターンとを形成する。

【0004】

このような特許文献1に記載された発明によれば、抵抗素子をパターニングするためのレジストパターンの寸法、形状を一定にし、ひいては抵抗素子の寸法、形状を一定にすることができる。したがって、特許文献1に記載された発明は、抵抗素子の寸法、形状のばらつきによる抵抗値のばらつきをなくすことに効果を奏するものといえる。

また、特許文献2に記載された技術のように、複数のヒューズを予め設けておくことによって抵抗値を設計値にあわせこむ技術もある。特許文献2に記載された技術によれば、素子特性を測定し、測定結果に応じて複数のヒューズのうちの選択された箇所だけを切断(トリミング)することによって望ましい抵抗値を得ることができる。

【特許文献1】特開平11−163263号公報

【特許文献2】特開平10−334787号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、抵抗素子の抵抗値のばらつきは、寸法形状のばらつきによってのみ起こるものではない。ばらつきの他の原因としては、膜の成膜条件や材料そのものの特性があげられる。

例えば、ノンドープのポリシリコンは、高抵抗(GΩ/unit)の抵抗素子材料に使用されるものの、特に抵抗率自体のばらつきが大きい材料である。ノンドープポリシリコン膜の抵抗率は、材料自身の特性の他、成膜雰囲気中にあるB等の不純物量や成膜工程時の温度の影響によって設計値の半分から倍程度にまで変化する。以下に、高抵抗の抵抗素子として使用されるノンドープポリシリコン膜の抵抗率の規格値を例示する。

【0006】

10G−5G+10GΩ/unit

特許文献1に記載されたように寸法、形状を一定にする技術は、ノンドープポリシリコン膜のように抵抗率のばらつきが大きい膜に適用した場合、ウェハ内での抵抗値のばらつきを抑えることは可能である。ただし、膜生成の工程において成膜の状態に変化が生じた場合、異なるウェハ間の抵抗値のばらつきを抑えることが難しいという欠点がある。

【0007】

また、特許文献2に記載されたヒューズ回路を形成する構成は、半導体装置が複数形成される回路領域にヒューズ回路を形成するため、回路領域が制限されるという不具合がある。また、ヒューズ回路によって抵抗値を調整する構成では、ヒューズ回路の所望の箇所だけを選択的に切断することが難しい。このため、所望の箇所だけを切断する、あるいは切断されたことを確認するための特有の工程が必要となる。

【0008】

本発明は、上記した点に鑑みてなされたものであり、成膜された素子膜に対し、該素子膜の状態に係る電気的特性を取得する。そして、取得した電気的特性に基づいて電気的特性を調整し、電気的特性のばらつきをなくし、特性を高精度に合わせこむことができる半導体装置の製造方法を提供することを目的とする。また、この調整を、より簡易に実行できる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

以上の課題を解決するため、本発明の半導体装置の製造方法は、半導体集積回路内の半導体素子を構成する素子膜を成膜する成膜工程と、前記成膜工程で成膜された素子膜をパターニングするパターニング工程と、前記成膜工程で成膜された素子膜の電気的特性を取得し、取得された電気的特性に基づいて前記パターニング工程後に得られた素子膜の形状を変更することによってパターニングされた素子膜の電気的特性を調整する調整工程と、を含むことを特徴とする半導体装置の製造方法。

【0010】

このような発明によれば、半導体素子を構成する素子膜を成膜する。そして、成膜された素子膜の電気的特性を取得し、取得した電気的特性に基づいて、パターニングされた素子膜の形状を変更することができる。このため、成膜された素子膜に対し、素子膜個々の電気的特性を取得し、取得した電気的特性に基づいて素子膜の電気的特性を調整することができる。このため、電気的特性のばらつきなくし、特性を高精度に合わせこむことができる。

【0011】

また、このような発明によれば、素子膜の形状を変更することによりパターニング後の素子膜の電気的特性を調整するため、回路の一点だけを切断する等の方法よりも簡易に調整の実行ができる。

また、本発明の半導体装置の製造方法は、前記調整工程が、前記素子膜または素子膜と同時に成膜された膜を実測することによって得られた電気的特性に基づいて素子膜の形状を変更することを特徴とする。

【0012】

このような発明によれば、素子膜または素子膜と同時に成膜された膜を実測して膜の電気的特性を得ることができる。このため、より正確に膜ごとの電気的特性を取得し、電気的特性のばらつきをなくし、特性を高精度に合わせこむことができる。

また、本発明の半導体装置の製造方法は、前記調整工程が、前記素子膜の電気的特性を実測するための測定用パターンを、前記半導体集積回路が形成される領域の外部領域に形成する測定用パターン形成工程を含み、該測定用パターンを実測することによって得られた電気的特性に基づいて素子膜の形状を変更することを特徴とする。

【0013】

このような発明によれば、測定用パターンを回路領域の外部に形成するため、測定用パターンの形成によって素子を形成できる領域が制限されることをなくし、素子の設計の自由度を維持することができる。また、回路領域が大きくなることも防ぎ、チップサイズの大型化を防ぐことができる。

また、本発明の半導体装置の製造方法は、前記測定用パターンは、前記外部領域に成膜された素子膜を、測定用の電極または探針とコンタクトするためのコンタクト用パターンを含むことを特徴とする。

【0014】

このような発明によれば、測定用パターンを探針等と適切にコンタクトしやすい形状とし、電気的特性の測定の信頼性を高めることができる。

また、本発明の半導体装置の製造方法は、前記調整工程が、前記成膜工程が行われた成膜装置の状態にかかる情報を含む情報を用いて統計的に得られる電気的特性に基づいて素子膜の形状を変更することを特徴とする。

【0015】

このような発明によれば、成膜された膜を実測する処理をなくし、より簡易に膜の電気的特性を取得することができる。

また、本発明の半導体装置の製造方法は、前記調整工程が、パターニングされた素子膜の厚さを増減することによって素子膜の形状を変更することを特徴とする。

このような発明によれば、比較的簡単に素子膜の形状を変更でき、ひいては電気的特性を調整することができる。

【0016】

また、本発明の半導体装置の製造方法は、前記調整工程が、パターニングされた素子膜をエッチングして素子膜の厚さを減じることにより素子膜の形状を変更することを特徴とする。

このような発明によれば、比較的簡単に素子膜の形状を変更でき、ひいては電気的特性を調整することができる。

【0017】

また、本発明の半導体装置の製造方法は、前記調整工程が、前記パターニング工程でパターニングされた素子膜上に第1の膜を成膜した後、パターニングして第1パターンを形成する第1パターン形成工程と、前記第1パターン上に第2の膜を成膜した後、パターニングして第2パターンを形成する第2パターン形成工程と、を含み、前記第1パターンは、パターニングされた素子膜上であって、かつ前記第2パターン下にない開口面を有することを特徴とする。

【0018】

このような発明によれば、第2パターンのエッチング後、素子膜上の開口面から素子膜がエッチングされる。このため、第2パターンの形成にあたって第2の膜をオーバーエッチングすることによって素子膜をエッチングすることができる。このため、新たなエッチング工程を追加することなく素子膜を追加エッチングすることができる。したがって、追加エッチングすることによって半導体装置の製造効率が低下することを防ぐことができる。

【0019】

また、本発明の半導体装置の製造方法は、前記素子膜がポリシリコン膜であって、前記第1パターン形成工程は絶縁膜を成膜した後、パターニングしてポリシリコン膜と配線とを絶縁する層間絶縁パターンを形成する工程であり、かつ、前記第2パターン形成工程はアルミニウム膜を成膜した後、パターニングして配線パターンを形成する工程であることを特徴とする。

【0020】

このような発明によれば、アルミニウム膜とポリシリコン膜とを同じ条件でエッチングできるので、アルミニウムをそのままの条件でオーバーエッチングすることによってポリシリコン膜をエッチングすることができる。また、アルミニウム、ポリシリコンが、絶縁物に対して比較的高い選択比を得ることから、オーバーエッチングの間に層間絶縁パターンが損なわれることを防ぐことができる。

【0021】

また、本発明の半導体装置の製造方法は、半導体集積回路内に抵抗素子を形成する工程を含む半導体装置の製造方法であって、前記抵抗素子を構成する素子膜と共に、前記半導体集積回路が形成される領域の外部領域にも前記素子膜を成膜する成膜工程と、前記前記成膜工程において、前記半導体集積回路が形成された領域及び前記外部領域に成膜された素子膜をパターニングし、前記抵抗素子と共にモニタ用パターンを形成するパターニング工程と、前記モニタ用パターンを使った前記素子膜の抵抗値の測定結果に基づいて、前記抵抗素子を構成する素子膜を、該素子膜よりも上方に設けられる膜と同時にエッチングする追加エッチング工程と、を含むことを特徴とする。

【0022】

このような発明によれば、素子膜と共に成膜された膜をパターニングしたモニタ用パターンを使って素子膜の抵抗率を取得することができる。そして、測定結果に基づいて、前記半導体素子を構成する素子膜を、該素子膜よりも上方に設けられる膜と同時にエッチングすることによって追加エッチングすることができる。このため、成膜された素子膜に対し、素子膜個々の正確な抵抗値を取得し、取得した抵抗値に基づいて素子膜の抵抗値を調整することができる。このため、抵抗値のばらつきをなくし、特性を高精度に合わせこむことができる半導体装置の製造方法を提供することができる。

【発明を実施するための最良の形態】

【0023】

以下、図を参照して本発明に係る半導体装置の製造方法の実施の形態を説明する。なお、本実施形態の説明において、半導体装置、素子等の用語を以下のように定義して用いるものとする。

本実施形態でいう半導体装置とは、半導体素子(能動素子、受動素子を含む。)を電気伝導体で接続して電流路を作り、目的とする動作を行う回路である。能動素子とは、外部から供給された電力を変換、整流、スイッチング等する素子をいい、例えば、ダイオードやトランジスタ等がある。受動素子とは、供給された電圧や電流に対してその物理的な特性の通りの特性を示す素子をいい、例えば、抵抗素子やコンデンサをいう。

【0024】

また、複数の半導体装置をまとめて特定の機能を果たすものを半導体集積回路と記す。半導体集積回路は、多くの場合、1つのチップにまとめられてパッケージ化される。

本実施形態の半導体装置の製造方法は、半導体集積回路内の半導体素子を構成する素子膜を成膜する成膜工程と、前記成膜工程で成膜された素子膜をパターニングするパターニング工程と、前記成膜工程で成膜された素子膜の電気的特性を取得し、取得された電気的特性に基づいて前記パターニング工程後に得られた素子膜の形状を変更することによってパターニングされた素子膜の電気的特性を調整する調整工程とを含む。

【0025】

以上の構成において、本実施形態では、半導体素子を抵抗素子、素子膜をノンドープポリシリコン膜とする。また、取得される電気的特性を、ノンドープポリシリコン膜の抵抗率とする。

また、本実施形態では、ノンドープポリシリコン膜、またはこのノンドープポリシリコン膜と同時に成膜された膜を実測する。そして、得られた抵抗率に基づいてノンドープポリシリコン膜の形状を変更する。さらに、ノンドープポリシリコン膜の抵抗率を実測するため、測定用パターンであるモニタパターンを、半導体集積回路が形成される領域(回路領域)の外部領域に形成するものとする。

【0026】

以下、本実施形態の半導体装置の製造方法を、工程をおって説明する。

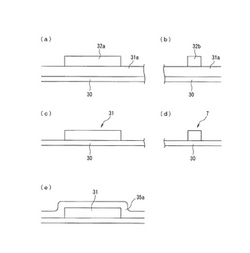

図1(a)〜(e)、図2(f)〜(h)は、本実施形態の半導体装置の製造方法を説明するための工程図である。このうち、図2(a)は、回路領域で行われる抵抗素子製造の工程を示す。(b)は、(a)に示した工程と同時にスクライブライン上で行われるモニタパターンの製造工程を示す。また、同様に、(c)は、回路領域で行われる抵抗素子製造の工程を示す。(d)は、(c)に示した工程と同時にスクライブライン上で行われるモニタパターンの製造工程を示す。

【0027】

ここで、図3を用い、上記した回路領域、スクラブライン及びモニタパターンの位置関係を説明する。図3は、ウェハ1上に形成された4つのチップa、b、c、dを示している。各チップには半導体集積回路5が回路領域3の内部に形成されている。回路領域3の外周にはスクライブライン9がある。本実施形態では、スクライブライン9を、回路領域3の周辺を内周とし、破線で示すチップの境界線11を外周とする領域とする。

【0028】

図1(a)及び(b)に示すように、ウェハ1の回路領域の一部およびスクライブライン9上の一部にはLOCOS(local oxidization of silicon)30が形成されている。抵抗素子となるノンドープのポリシリコン膜31aは、回路領域3とスクライブライン9とを含むウェハ1の全面に成膜される。 抵抗素子の形成時、ポリシリコン膜31aの全面にレジストが塗布される。そして、レジスト上からフォトマスク(図示せず。)を通して光が照射され、レジストを露光する。この結果、ポリシリコンエッチングのためのレジストマスクが形成される。図中、レジストマスク32aは、抵抗素子をパターニングするためのレジストマスクである(図1(a))。また、レジストマスク32bは、モニタパターン7をパターニングするためのレジストマスクである(図1(b))。

【0029】

なお、本実施形態では、レジストマスク32bを形成するためのパターンを、レジストマスク32aを形成するためのフォトマスクに追加しておく。このため、本実施形態は、1回のマスク工程でレジストマスク32aとレジストマスク32bとを形成でき、モニタパターン7を形成するためにマスク工程を追加する必要がない。

次に、本実施形態では、ポリシリコン膜31aをドライエッチングして抵抗素子31を形成する(図1(c))。このとき、スクライブライン9ではレジストマスク32b下以外のポリシリコン膜31aが同時にエッチングされ、モニタパターン7が形成される(図1(d))。

【0030】

形成されたモニタパターンの斜視図を図4に示す。モニタパターン7は、本体パターン7aと、コンタクトパターン7bとを備えている。モニタパターン7の抵抗率は、測定用の治具によって測定される。コンタクトパターン7bは、治具に設けられた抵抗値測定用の電極または探針とコンタクトするためのパターンである。コンタクトパターンbを設けたことにより、モニタパターン7と治具の探針等とが適切にコンタクトでき、モニタパターン7の抵抗率を適正に測定することができる。

【0031】

次に、本実施形態では、オペレータが、形成されたモニタパターン7の抵抗値を実測する。そして、実測した抵抗値とモニタパターン7の寸法形状とからポリシリコン膜31aの抵抗率を求める。さらに、抵抗素子31の寸法形状と抵抗率とから抵抗素子31の抵抗値を求める。

以上の方法によれば、膜の材料や成膜状態に起因するばらつきによらず、ポリシリコン膜31aの抵抗率を正確に測定することができる。このため、抵抗素子31の抵抗値を、膜起因のばらつきによらず正確に求めることができる。

【0032】

なお、形成された抵抗素子31のうち、後述するコンタクト孔下にはコンタクト抵抗を引き下げるための不純物が不純物層形成のタイミングで注入される。この際、抵抗素子31の寸法形状のうち不純物が注入された領域の抵抗値はノンドープポリシリコン部の抵抗値と比較して小さいため、その領域の抵抗値は無視できる。

また、本実施形態は、さらに、モニタパターン7を使ったポリシリコン膜31aの抵抗値の測定結果に基づいて、抵抗素子31としていったんパターニングされたポリシリコン膜の形状を変更する工程を含む。本実施形態では、形状の変更を、ポリシリコン膜をエッチングし、抵抗素子31のパターンの厚さを減じることによって行い、これによって抵抗値を増加させ抵抗設計値に合わせ込む方法を取る。このため、本実施形態では、予め設計値よりも小さい抵抗値を有する抵抗素子を作成しておく必要がある。そのためには、設計値が得られる厚さよりも厚くポリシリコンを堆積してポリシリコン膜31aを成膜する方法か、または、ポリシリコンのパターンサイズを設計値が得られるサイズよりも小さくパターニングする方法を取る。

【0033】

ところで、いったんパターニングされたポリシリコン膜の形状を変更する場合、ポリシリコン膜を再度エッチングするための工程を追加することが必要になる。工程の追加は、半導体装置製造の効率を低下させるために望ましくない。そこで、本実施形態では、素子膜であるポリシリコン膜をパターニングした抵抗素子31上に第1の膜を成膜し、パターニングして第1パターンを形成する。また、第1パターン上に第2の膜を成膜した後、パターニングして第2パターンを形成する。

【0034】

そして、第1パターンに、抵抗素子31上にあって、かつ第2パターン下にない開口面を設けた。このような構成によれば、第2パターンのパターニング時に開口面下にある抵抗素子31がエッチング雰囲気にさらされる。したがって、第2パターンのエッチング時間を延長することにより、素子膜を第2膜と同一のエッチング工程でエッチングする。このようにすると、素子膜の形状を変更するためのエッチング工程を追加する必要がなく、半導体装置の製造効率低下を防ぐことができる。

【0035】

このような構成は、一般的な半導体のプロセス工程において、抵抗素子31上に抵抗素子31とコンタクトするアルミニウム配線が形成されること。アルミニウムをエッチングする際のドライエッチングは、ポリシリコン膜をもエッチング可能である点に注目してなされたものである。

すなわち、本実施形態では、図1(e)のように、抵抗素子31上に絶縁膜35aを堆積する。そして、図2(f)に示すように、絶縁膜35aをパターニングしてコンタクトホール40と、追加エッチング用の開口面であるホール45とを備えた絶縁層パターン50を形成する。

【0036】

さらに、本実施形態では、配線となるアルミニウム膜42aをスパッタリング等によって成膜し、アルミニウム膜42a上に配線をパターニングするためのレジストマスク41を形成する(図2(g))。

次に、レジストマスク41をマスクにしてアルミニウム膜42aをエッチングする。エッチングによってアルミニウム膜42aがパターニングされて配線パターン42が形成される。

【0037】

ホール45は、抵抗素子31の上にあって、かつ、配線パターン42下にない。このため、配線パターン42が形成される過程でアルミニウム膜42a下のホール45から抵抗素子31表面が露出する。アルミニウム膜42aのエッチングにおいて、さらにオーバーエッチングすることによって抵抗素子31のうちホール45から露出している面がエッチングされる(図2(h))。

【0038】

なお、本実施形態では、ポリシリコン膜31a及びアルミニウム膜42aとの選択比が充分に高い材料を絶縁膜35aに用いている。このため、アルミニウム膜42aをオーバーエッチングする際に絶縁層パターン50がエッチングされることはほとんどない。なお、オーバーエッチングの量は、モニタパターン7の実測で得られた抵抗率を使って求められた抵抗素子31の抵抗値と設計値との差分に応じて決定する。

【0039】

以上の工程により、抵抗素子31は、追加エッチングされて設計通りの抵抗値を有するものとなる。以下に、図2(g)から(h)に示したエッチングの条件について例示する。

エッチング装置タイプ: マイクロ波プラズマエッチング装置

エッチングガス: トータル圧力1 5 mtorr

トータル流量150sccm

ガス種 Cl2、BCl3 (流量比2:3 )

エッチングレート: 平均8000Å/分

エッチング時間(トータル): 60秒

マイクロ波パワー: 1000W

ステージバイアス: 100W

以上述べた本実施形態によれば、素子膜と同時に成膜された膜をパターニングしモニタパターン7を形成できる。このため、モニタパターン7と抵抗用膜とが同じ抵抗率を有し、モニタパターン7の抵抗を測定することによって抵抗素子の抵抗率を知ることを可能にする。このような本実施形態は、特に抵抗率のばらつきが大きいノンドープポリシリコン等の膜を抵抗素子に用いる場合、寸法、形状による抵抗のばらつきを抑えるよりも有効に抵抗値のばらつきを抑えることができる。

【0040】

また、実施形態によれば、モニタパターン7を回路領域3の外部に設けたため、回路領域3がモニタパターン7形成のために制限されることがない。このため、モニタパターンを設けたことによって素子5の設計の自由度が低下することを防ぐことができる。また、スクライブライン9は半導体装置のダイシング後に不要になるので、モニタパターンを設けたことによって半導体チップのサイズが大きくなることを回避することができる。

【0041】

また、本実施形態は、以上述べた構成に限定されるものではない。すなわち、上記した実施形態では、スクライブライン9上にモニタパターン7を設け、モニタパターン7の抵抗率を実測して抵抗素子31の抵抗値を得ている。しかし、本発明は、ポリシリコン膜の抵抗率の実測にモニタパターンを用いるものに限定されるものではない。

すなわち、ポリシリコン膜の抵抗率は、ウェハ1の全面にポリシリコン膜が成膜され、エッチングされる以前に測定することもできる。また、エッチング後、スクライブライン9上に残ったポリシリコン膜を使って抵抗率を測定することができる。さらに、本実施形態は、形成された抵抗素子を実測して抵抗率を取得するものであってもよい。

【0042】

また、測定に使用されるポリシリコン膜は同一ウェハ上に成膜されたものに限定されるものではない。すなわち、ポリシリコン膜が複数のウェハに対して一度に成膜されるとき、各ウェハのポリシリコン膜の抵抗率は、他のウェハ上に同時に成膜されたポリシリコン膜から求められる。このとき、他のウェハは、ロット内にあって任意に抜き取られたウェハであってもよく、また、ダミーウェハであってもよい。

【0043】

また、本実施形態は、ポリシリコン膜の電気的特性を実測して得るものに限定されるものでなく、成膜工程が行われた成膜装置の状態にかかる情報を含む情報を用いて統計的に電気的特性を得るものであってもよい。

なお、成膜装置の状態にかかる情報とは、例えば、成膜装置の直前のメンテナンスから経過した時間や稼働の累積時間を指す。そして、成膜装置の状態にかかる情報を含む情報とは、メンテナンス後に経過した時間等と、成膜された膜質との関係とを対応付けて記録したデータ等をいう。

【0044】

このような実施形態によれば、オペレータは、ポリシリコン膜を成膜したときの成膜装置の状態に対応する抵抗率をエッチングすべきポリシリコン膜の抵抗率として取得する。そして、取得したポリシリコン膜の抵抗率から抵抗素子の抵抗値を算出し、算出された抵抗値と設計値との差分が打ち消されるよう抵抗素子の形状を変更する。

さらに、上記した本実施形態では、ホール45の平面視における開口面の形状については言及していない。しかし、開口面の形状は、エッチングによって抵抗素子が受ける影響等に応じて任意の形状にすることができる(例えば開口面をストライプ形状にし、半導体素子に溝を設けるようエッチングする)。また、開口面を複数設けることも可能である。

【0045】

また、上記した実施形態では、抵抗素子を構成するポリシリコン膜をエッチングして減じることによって抵抗値をより高い方向に調整している。しかし、本実施形態は、必要に応じて抵抗素子上に膜を堆積し、抵抗値をより低く調整することも可能である。

さらに、上記した実施形態では、抵抗素子を形成する膜にポリシリコン、配線にアルミニウムを用いている。しかし、本実施形態は、このような構成に限定されるものでなく、抵抗素子、配線としてそれぞれ適当であり、かつ、同じエッチング条件でエッチング可能な他の材料を使って実現することができる。

また、回路内抵抗素子パターンおよびモニターパターンはLOCOS上に形成しなくても構わない。

【図面の簡単な説明】

【0046】

【図1】本発明の一実施形態の半導体装置の製造方法を説明するための工程図である。

【図2】本発明の一実施形態の半導体装置の製造方法を説明するための他の工程図である。

【図3】本発明の一実施形態の半導体装置が形成されたウェハの一部を示した図である。

【図4】図3に示したモニタパターンの斜視図である。

【符号の説明】

【0047】

1 ウェハ、3 回路領域、5 素子、7 モニタパターン、7a 本体パターン

7b コンタクトパターン、9 スクライブライン、31 抵抗素子、

31a ポリシリコン膜、32a、32b、41 レジストマスク、

35a 絶縁膜、40 コンタクトホール、42 配線パターン、45 ホール、50 絶縁層パターン

【技術分野】

【0001】

本発明は、成膜工程を含む半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置は、半導体の電気特性を利用して動作する回路であって、トランジスタ等の能動素子や抵抗等の受動素子とを組み合わせて形成されている。

ところで、素子は、多くが各部材を材料にした膜の生成(成膜)と、成膜された膜のパターニングとによって形成される。各要素の電気的特性は、材料の特性のばらつきや成膜条件、パターニング後の寸法や形状のばらつきによって変化する。特に、抵抗素子のばらつきは、素子全体の電気特性に大きく影響する。このため、抵抗素子の抵抗値を一定に保つことを目的とした発明が、従来から提案されている。

【0003】

このような従来技術として、例えば、特許文献1に記載された発明がある。特許文献1に記載された発明は、抵抗素子のパターニング工程で形成されるマスクパターンのばらつきを防ぐことを目的にしてなされている。具体的には、フォトマスク上に、抵抗素子をパターニングするためのマスクパターンと、このマスクパターンの光の干渉による寸法変動を抑えるためのマスクパターンとを形成する。

【0004】

このような特許文献1に記載された発明によれば、抵抗素子をパターニングするためのレジストパターンの寸法、形状を一定にし、ひいては抵抗素子の寸法、形状を一定にすることができる。したがって、特許文献1に記載された発明は、抵抗素子の寸法、形状のばらつきによる抵抗値のばらつきをなくすことに効果を奏するものといえる。

また、特許文献2に記載された技術のように、複数のヒューズを予め設けておくことによって抵抗値を設計値にあわせこむ技術もある。特許文献2に記載された技術によれば、素子特性を測定し、測定結果に応じて複数のヒューズのうちの選択された箇所だけを切断(トリミング)することによって望ましい抵抗値を得ることができる。

【特許文献1】特開平11−163263号公報

【特許文献2】特開平10−334787号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、抵抗素子の抵抗値のばらつきは、寸法形状のばらつきによってのみ起こるものではない。ばらつきの他の原因としては、膜の成膜条件や材料そのものの特性があげられる。

例えば、ノンドープのポリシリコンは、高抵抗(GΩ/unit)の抵抗素子材料に使用されるものの、特に抵抗率自体のばらつきが大きい材料である。ノンドープポリシリコン膜の抵抗率は、材料自身の特性の他、成膜雰囲気中にあるB等の不純物量や成膜工程時の温度の影響によって設計値の半分から倍程度にまで変化する。以下に、高抵抗の抵抗素子として使用されるノンドープポリシリコン膜の抵抗率の規格値を例示する。

【0006】

10G−5G+10GΩ/unit

特許文献1に記載されたように寸法、形状を一定にする技術は、ノンドープポリシリコン膜のように抵抗率のばらつきが大きい膜に適用した場合、ウェハ内での抵抗値のばらつきを抑えることは可能である。ただし、膜生成の工程において成膜の状態に変化が生じた場合、異なるウェハ間の抵抗値のばらつきを抑えることが難しいという欠点がある。

【0007】

また、特許文献2に記載されたヒューズ回路を形成する構成は、半導体装置が複数形成される回路領域にヒューズ回路を形成するため、回路領域が制限されるという不具合がある。また、ヒューズ回路によって抵抗値を調整する構成では、ヒューズ回路の所望の箇所だけを選択的に切断することが難しい。このため、所望の箇所だけを切断する、あるいは切断されたことを確認するための特有の工程が必要となる。

【0008】

本発明は、上記した点に鑑みてなされたものであり、成膜された素子膜に対し、該素子膜の状態に係る電気的特性を取得する。そして、取得した電気的特性に基づいて電気的特性を調整し、電気的特性のばらつきをなくし、特性を高精度に合わせこむことができる半導体装置の製造方法を提供することを目的とする。また、この調整を、より簡易に実行できる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

以上の課題を解決するため、本発明の半導体装置の製造方法は、半導体集積回路内の半導体素子を構成する素子膜を成膜する成膜工程と、前記成膜工程で成膜された素子膜をパターニングするパターニング工程と、前記成膜工程で成膜された素子膜の電気的特性を取得し、取得された電気的特性に基づいて前記パターニング工程後に得られた素子膜の形状を変更することによってパターニングされた素子膜の電気的特性を調整する調整工程と、を含むことを特徴とする半導体装置の製造方法。

【0010】

このような発明によれば、半導体素子を構成する素子膜を成膜する。そして、成膜された素子膜の電気的特性を取得し、取得した電気的特性に基づいて、パターニングされた素子膜の形状を変更することができる。このため、成膜された素子膜に対し、素子膜個々の電気的特性を取得し、取得した電気的特性に基づいて素子膜の電気的特性を調整することができる。このため、電気的特性のばらつきなくし、特性を高精度に合わせこむことができる。

【0011】

また、このような発明によれば、素子膜の形状を変更することによりパターニング後の素子膜の電気的特性を調整するため、回路の一点だけを切断する等の方法よりも簡易に調整の実行ができる。

また、本発明の半導体装置の製造方法は、前記調整工程が、前記素子膜または素子膜と同時に成膜された膜を実測することによって得られた電気的特性に基づいて素子膜の形状を変更することを特徴とする。

【0012】

このような発明によれば、素子膜または素子膜と同時に成膜された膜を実測して膜の電気的特性を得ることができる。このため、より正確に膜ごとの電気的特性を取得し、電気的特性のばらつきをなくし、特性を高精度に合わせこむことができる。

また、本発明の半導体装置の製造方法は、前記調整工程が、前記素子膜の電気的特性を実測するための測定用パターンを、前記半導体集積回路が形成される領域の外部領域に形成する測定用パターン形成工程を含み、該測定用パターンを実測することによって得られた電気的特性に基づいて素子膜の形状を変更することを特徴とする。

【0013】

このような発明によれば、測定用パターンを回路領域の外部に形成するため、測定用パターンの形成によって素子を形成できる領域が制限されることをなくし、素子の設計の自由度を維持することができる。また、回路領域が大きくなることも防ぎ、チップサイズの大型化を防ぐことができる。

また、本発明の半導体装置の製造方法は、前記測定用パターンは、前記外部領域に成膜された素子膜を、測定用の電極または探針とコンタクトするためのコンタクト用パターンを含むことを特徴とする。

【0014】

このような発明によれば、測定用パターンを探針等と適切にコンタクトしやすい形状とし、電気的特性の測定の信頼性を高めることができる。

また、本発明の半導体装置の製造方法は、前記調整工程が、前記成膜工程が行われた成膜装置の状態にかかる情報を含む情報を用いて統計的に得られる電気的特性に基づいて素子膜の形状を変更することを特徴とする。

【0015】

このような発明によれば、成膜された膜を実測する処理をなくし、より簡易に膜の電気的特性を取得することができる。

また、本発明の半導体装置の製造方法は、前記調整工程が、パターニングされた素子膜の厚さを増減することによって素子膜の形状を変更することを特徴とする。

このような発明によれば、比較的簡単に素子膜の形状を変更でき、ひいては電気的特性を調整することができる。

【0016】

また、本発明の半導体装置の製造方法は、前記調整工程が、パターニングされた素子膜をエッチングして素子膜の厚さを減じることにより素子膜の形状を変更することを特徴とする。

このような発明によれば、比較的簡単に素子膜の形状を変更でき、ひいては電気的特性を調整することができる。

【0017】

また、本発明の半導体装置の製造方法は、前記調整工程が、前記パターニング工程でパターニングされた素子膜上に第1の膜を成膜した後、パターニングして第1パターンを形成する第1パターン形成工程と、前記第1パターン上に第2の膜を成膜した後、パターニングして第2パターンを形成する第2パターン形成工程と、を含み、前記第1パターンは、パターニングされた素子膜上であって、かつ前記第2パターン下にない開口面を有することを特徴とする。

【0018】

このような発明によれば、第2パターンのエッチング後、素子膜上の開口面から素子膜がエッチングされる。このため、第2パターンの形成にあたって第2の膜をオーバーエッチングすることによって素子膜をエッチングすることができる。このため、新たなエッチング工程を追加することなく素子膜を追加エッチングすることができる。したがって、追加エッチングすることによって半導体装置の製造効率が低下することを防ぐことができる。

【0019】

また、本発明の半導体装置の製造方法は、前記素子膜がポリシリコン膜であって、前記第1パターン形成工程は絶縁膜を成膜した後、パターニングしてポリシリコン膜と配線とを絶縁する層間絶縁パターンを形成する工程であり、かつ、前記第2パターン形成工程はアルミニウム膜を成膜した後、パターニングして配線パターンを形成する工程であることを特徴とする。

【0020】

このような発明によれば、アルミニウム膜とポリシリコン膜とを同じ条件でエッチングできるので、アルミニウムをそのままの条件でオーバーエッチングすることによってポリシリコン膜をエッチングすることができる。また、アルミニウム、ポリシリコンが、絶縁物に対して比較的高い選択比を得ることから、オーバーエッチングの間に層間絶縁パターンが損なわれることを防ぐことができる。

【0021】

また、本発明の半導体装置の製造方法は、半導体集積回路内に抵抗素子を形成する工程を含む半導体装置の製造方法であって、前記抵抗素子を構成する素子膜と共に、前記半導体集積回路が形成される領域の外部領域にも前記素子膜を成膜する成膜工程と、前記前記成膜工程において、前記半導体集積回路が形成された領域及び前記外部領域に成膜された素子膜をパターニングし、前記抵抗素子と共にモニタ用パターンを形成するパターニング工程と、前記モニタ用パターンを使った前記素子膜の抵抗値の測定結果に基づいて、前記抵抗素子を構成する素子膜を、該素子膜よりも上方に設けられる膜と同時にエッチングする追加エッチング工程と、を含むことを特徴とする。

【0022】

このような発明によれば、素子膜と共に成膜された膜をパターニングしたモニタ用パターンを使って素子膜の抵抗率を取得することができる。そして、測定結果に基づいて、前記半導体素子を構成する素子膜を、該素子膜よりも上方に設けられる膜と同時にエッチングすることによって追加エッチングすることができる。このため、成膜された素子膜に対し、素子膜個々の正確な抵抗値を取得し、取得した抵抗値に基づいて素子膜の抵抗値を調整することができる。このため、抵抗値のばらつきをなくし、特性を高精度に合わせこむことができる半導体装置の製造方法を提供することができる。

【発明を実施するための最良の形態】

【0023】

以下、図を参照して本発明に係る半導体装置の製造方法の実施の形態を説明する。なお、本実施形態の説明において、半導体装置、素子等の用語を以下のように定義して用いるものとする。

本実施形態でいう半導体装置とは、半導体素子(能動素子、受動素子を含む。)を電気伝導体で接続して電流路を作り、目的とする動作を行う回路である。能動素子とは、外部から供給された電力を変換、整流、スイッチング等する素子をいい、例えば、ダイオードやトランジスタ等がある。受動素子とは、供給された電圧や電流に対してその物理的な特性の通りの特性を示す素子をいい、例えば、抵抗素子やコンデンサをいう。

【0024】

また、複数の半導体装置をまとめて特定の機能を果たすものを半導体集積回路と記す。半導体集積回路は、多くの場合、1つのチップにまとめられてパッケージ化される。

本実施形態の半導体装置の製造方法は、半導体集積回路内の半導体素子を構成する素子膜を成膜する成膜工程と、前記成膜工程で成膜された素子膜をパターニングするパターニング工程と、前記成膜工程で成膜された素子膜の電気的特性を取得し、取得された電気的特性に基づいて前記パターニング工程後に得られた素子膜の形状を変更することによってパターニングされた素子膜の電気的特性を調整する調整工程とを含む。

【0025】

以上の構成において、本実施形態では、半導体素子を抵抗素子、素子膜をノンドープポリシリコン膜とする。また、取得される電気的特性を、ノンドープポリシリコン膜の抵抗率とする。

また、本実施形態では、ノンドープポリシリコン膜、またはこのノンドープポリシリコン膜と同時に成膜された膜を実測する。そして、得られた抵抗率に基づいてノンドープポリシリコン膜の形状を変更する。さらに、ノンドープポリシリコン膜の抵抗率を実測するため、測定用パターンであるモニタパターンを、半導体集積回路が形成される領域(回路領域)の外部領域に形成するものとする。

【0026】

以下、本実施形態の半導体装置の製造方法を、工程をおって説明する。

図1(a)〜(e)、図2(f)〜(h)は、本実施形態の半導体装置の製造方法を説明するための工程図である。このうち、図2(a)は、回路領域で行われる抵抗素子製造の工程を示す。(b)は、(a)に示した工程と同時にスクライブライン上で行われるモニタパターンの製造工程を示す。また、同様に、(c)は、回路領域で行われる抵抗素子製造の工程を示す。(d)は、(c)に示した工程と同時にスクライブライン上で行われるモニタパターンの製造工程を示す。

【0027】

ここで、図3を用い、上記した回路領域、スクラブライン及びモニタパターンの位置関係を説明する。図3は、ウェハ1上に形成された4つのチップa、b、c、dを示している。各チップには半導体集積回路5が回路領域3の内部に形成されている。回路領域3の外周にはスクライブライン9がある。本実施形態では、スクライブライン9を、回路領域3の周辺を内周とし、破線で示すチップの境界線11を外周とする領域とする。

【0028】

図1(a)及び(b)に示すように、ウェハ1の回路領域の一部およびスクライブライン9上の一部にはLOCOS(local oxidization of silicon)30が形成されている。抵抗素子となるノンドープのポリシリコン膜31aは、回路領域3とスクライブライン9とを含むウェハ1の全面に成膜される。 抵抗素子の形成時、ポリシリコン膜31aの全面にレジストが塗布される。そして、レジスト上からフォトマスク(図示せず。)を通して光が照射され、レジストを露光する。この結果、ポリシリコンエッチングのためのレジストマスクが形成される。図中、レジストマスク32aは、抵抗素子をパターニングするためのレジストマスクである(図1(a))。また、レジストマスク32bは、モニタパターン7をパターニングするためのレジストマスクである(図1(b))。

【0029】

なお、本実施形態では、レジストマスク32bを形成するためのパターンを、レジストマスク32aを形成するためのフォトマスクに追加しておく。このため、本実施形態は、1回のマスク工程でレジストマスク32aとレジストマスク32bとを形成でき、モニタパターン7を形成するためにマスク工程を追加する必要がない。

次に、本実施形態では、ポリシリコン膜31aをドライエッチングして抵抗素子31を形成する(図1(c))。このとき、スクライブライン9ではレジストマスク32b下以外のポリシリコン膜31aが同時にエッチングされ、モニタパターン7が形成される(図1(d))。

【0030】

形成されたモニタパターンの斜視図を図4に示す。モニタパターン7は、本体パターン7aと、コンタクトパターン7bとを備えている。モニタパターン7の抵抗率は、測定用の治具によって測定される。コンタクトパターン7bは、治具に設けられた抵抗値測定用の電極または探針とコンタクトするためのパターンである。コンタクトパターンbを設けたことにより、モニタパターン7と治具の探針等とが適切にコンタクトでき、モニタパターン7の抵抗率を適正に測定することができる。

【0031】

次に、本実施形態では、オペレータが、形成されたモニタパターン7の抵抗値を実測する。そして、実測した抵抗値とモニタパターン7の寸法形状とからポリシリコン膜31aの抵抗率を求める。さらに、抵抗素子31の寸法形状と抵抗率とから抵抗素子31の抵抗値を求める。

以上の方法によれば、膜の材料や成膜状態に起因するばらつきによらず、ポリシリコン膜31aの抵抗率を正確に測定することができる。このため、抵抗素子31の抵抗値を、膜起因のばらつきによらず正確に求めることができる。

【0032】

なお、形成された抵抗素子31のうち、後述するコンタクト孔下にはコンタクト抵抗を引き下げるための不純物が不純物層形成のタイミングで注入される。この際、抵抗素子31の寸法形状のうち不純物が注入された領域の抵抗値はノンドープポリシリコン部の抵抗値と比較して小さいため、その領域の抵抗値は無視できる。

また、本実施形態は、さらに、モニタパターン7を使ったポリシリコン膜31aの抵抗値の測定結果に基づいて、抵抗素子31としていったんパターニングされたポリシリコン膜の形状を変更する工程を含む。本実施形態では、形状の変更を、ポリシリコン膜をエッチングし、抵抗素子31のパターンの厚さを減じることによって行い、これによって抵抗値を増加させ抵抗設計値に合わせ込む方法を取る。このため、本実施形態では、予め設計値よりも小さい抵抗値を有する抵抗素子を作成しておく必要がある。そのためには、設計値が得られる厚さよりも厚くポリシリコンを堆積してポリシリコン膜31aを成膜する方法か、または、ポリシリコンのパターンサイズを設計値が得られるサイズよりも小さくパターニングする方法を取る。

【0033】

ところで、いったんパターニングされたポリシリコン膜の形状を変更する場合、ポリシリコン膜を再度エッチングするための工程を追加することが必要になる。工程の追加は、半導体装置製造の効率を低下させるために望ましくない。そこで、本実施形態では、素子膜であるポリシリコン膜をパターニングした抵抗素子31上に第1の膜を成膜し、パターニングして第1パターンを形成する。また、第1パターン上に第2の膜を成膜した後、パターニングして第2パターンを形成する。

【0034】

そして、第1パターンに、抵抗素子31上にあって、かつ第2パターン下にない開口面を設けた。このような構成によれば、第2パターンのパターニング時に開口面下にある抵抗素子31がエッチング雰囲気にさらされる。したがって、第2パターンのエッチング時間を延長することにより、素子膜を第2膜と同一のエッチング工程でエッチングする。このようにすると、素子膜の形状を変更するためのエッチング工程を追加する必要がなく、半導体装置の製造効率低下を防ぐことができる。

【0035】

このような構成は、一般的な半導体のプロセス工程において、抵抗素子31上に抵抗素子31とコンタクトするアルミニウム配線が形成されること。アルミニウムをエッチングする際のドライエッチングは、ポリシリコン膜をもエッチング可能である点に注目してなされたものである。

すなわち、本実施形態では、図1(e)のように、抵抗素子31上に絶縁膜35aを堆積する。そして、図2(f)に示すように、絶縁膜35aをパターニングしてコンタクトホール40と、追加エッチング用の開口面であるホール45とを備えた絶縁層パターン50を形成する。

【0036】

さらに、本実施形態では、配線となるアルミニウム膜42aをスパッタリング等によって成膜し、アルミニウム膜42a上に配線をパターニングするためのレジストマスク41を形成する(図2(g))。

次に、レジストマスク41をマスクにしてアルミニウム膜42aをエッチングする。エッチングによってアルミニウム膜42aがパターニングされて配線パターン42が形成される。

【0037】

ホール45は、抵抗素子31の上にあって、かつ、配線パターン42下にない。このため、配線パターン42が形成される過程でアルミニウム膜42a下のホール45から抵抗素子31表面が露出する。アルミニウム膜42aのエッチングにおいて、さらにオーバーエッチングすることによって抵抗素子31のうちホール45から露出している面がエッチングされる(図2(h))。

【0038】

なお、本実施形態では、ポリシリコン膜31a及びアルミニウム膜42aとの選択比が充分に高い材料を絶縁膜35aに用いている。このため、アルミニウム膜42aをオーバーエッチングする際に絶縁層パターン50がエッチングされることはほとんどない。なお、オーバーエッチングの量は、モニタパターン7の実測で得られた抵抗率を使って求められた抵抗素子31の抵抗値と設計値との差分に応じて決定する。

【0039】

以上の工程により、抵抗素子31は、追加エッチングされて設計通りの抵抗値を有するものとなる。以下に、図2(g)から(h)に示したエッチングの条件について例示する。

エッチング装置タイプ: マイクロ波プラズマエッチング装置

エッチングガス: トータル圧力1 5 mtorr

トータル流量150sccm

ガス種 Cl2、BCl3 (流量比2:3 )

エッチングレート: 平均8000Å/分

エッチング時間(トータル): 60秒

マイクロ波パワー: 1000W

ステージバイアス: 100W

以上述べた本実施形態によれば、素子膜と同時に成膜された膜をパターニングしモニタパターン7を形成できる。このため、モニタパターン7と抵抗用膜とが同じ抵抗率を有し、モニタパターン7の抵抗を測定することによって抵抗素子の抵抗率を知ることを可能にする。このような本実施形態は、特に抵抗率のばらつきが大きいノンドープポリシリコン等の膜を抵抗素子に用いる場合、寸法、形状による抵抗のばらつきを抑えるよりも有効に抵抗値のばらつきを抑えることができる。

【0040】

また、実施形態によれば、モニタパターン7を回路領域3の外部に設けたため、回路領域3がモニタパターン7形成のために制限されることがない。このため、モニタパターンを設けたことによって素子5の設計の自由度が低下することを防ぐことができる。また、スクライブライン9は半導体装置のダイシング後に不要になるので、モニタパターンを設けたことによって半導体チップのサイズが大きくなることを回避することができる。

【0041】

また、本実施形態は、以上述べた構成に限定されるものではない。すなわち、上記した実施形態では、スクライブライン9上にモニタパターン7を設け、モニタパターン7の抵抗率を実測して抵抗素子31の抵抗値を得ている。しかし、本発明は、ポリシリコン膜の抵抗率の実測にモニタパターンを用いるものに限定されるものではない。

すなわち、ポリシリコン膜の抵抗率は、ウェハ1の全面にポリシリコン膜が成膜され、エッチングされる以前に測定することもできる。また、エッチング後、スクライブライン9上に残ったポリシリコン膜を使って抵抗率を測定することができる。さらに、本実施形態は、形成された抵抗素子を実測して抵抗率を取得するものであってもよい。

【0042】

また、測定に使用されるポリシリコン膜は同一ウェハ上に成膜されたものに限定されるものではない。すなわち、ポリシリコン膜が複数のウェハに対して一度に成膜されるとき、各ウェハのポリシリコン膜の抵抗率は、他のウェハ上に同時に成膜されたポリシリコン膜から求められる。このとき、他のウェハは、ロット内にあって任意に抜き取られたウェハであってもよく、また、ダミーウェハであってもよい。

【0043】

また、本実施形態は、ポリシリコン膜の電気的特性を実測して得るものに限定されるものでなく、成膜工程が行われた成膜装置の状態にかかる情報を含む情報を用いて統計的に電気的特性を得るものであってもよい。

なお、成膜装置の状態にかかる情報とは、例えば、成膜装置の直前のメンテナンスから経過した時間や稼働の累積時間を指す。そして、成膜装置の状態にかかる情報を含む情報とは、メンテナンス後に経過した時間等と、成膜された膜質との関係とを対応付けて記録したデータ等をいう。

【0044】

このような実施形態によれば、オペレータは、ポリシリコン膜を成膜したときの成膜装置の状態に対応する抵抗率をエッチングすべきポリシリコン膜の抵抗率として取得する。そして、取得したポリシリコン膜の抵抗率から抵抗素子の抵抗値を算出し、算出された抵抗値と設計値との差分が打ち消されるよう抵抗素子の形状を変更する。

さらに、上記した本実施形態では、ホール45の平面視における開口面の形状については言及していない。しかし、開口面の形状は、エッチングによって抵抗素子が受ける影響等に応じて任意の形状にすることができる(例えば開口面をストライプ形状にし、半導体素子に溝を設けるようエッチングする)。また、開口面を複数設けることも可能である。

【0045】

また、上記した実施形態では、抵抗素子を構成するポリシリコン膜をエッチングして減じることによって抵抗値をより高い方向に調整している。しかし、本実施形態は、必要に応じて抵抗素子上に膜を堆積し、抵抗値をより低く調整することも可能である。

さらに、上記した実施形態では、抵抗素子を形成する膜にポリシリコン、配線にアルミニウムを用いている。しかし、本実施形態は、このような構成に限定されるものでなく、抵抗素子、配線としてそれぞれ適当であり、かつ、同じエッチング条件でエッチング可能な他の材料を使って実現することができる。

また、回路内抵抗素子パターンおよびモニターパターンはLOCOS上に形成しなくても構わない。

【図面の簡単な説明】

【0046】

【図1】本発明の一実施形態の半導体装置の製造方法を説明するための工程図である。

【図2】本発明の一実施形態の半導体装置の製造方法を説明するための他の工程図である。

【図3】本発明の一実施形態の半導体装置が形成されたウェハの一部を示した図である。

【図4】図3に示したモニタパターンの斜視図である。

【符号の説明】

【0047】

1 ウェハ、3 回路領域、5 素子、7 モニタパターン、7a 本体パターン

7b コンタクトパターン、9 スクライブライン、31 抵抗素子、

31a ポリシリコン膜、32a、32b、41 レジストマスク、

35a 絶縁膜、40 コンタクトホール、42 配線パターン、45 ホール、50 絶縁層パターン

【特許請求の範囲】

【請求項1】

半導体集積回路内の半導体素子を構成する素子膜を成膜する成膜工程と、

前記成膜工程で成膜された素子膜をパターニングするパターニング工程と、

前記成膜工程で成膜された素子膜の電気的特性を取得し、取得された電気的特性に基づいて前記パターニング工程後に得られた素子膜の形状を変更することによってパターニングされた素子膜の電気的特性を調整する調整工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記調整工程は、前記素子膜または素子膜と同時に成膜された膜を実測することによって得られた電気的特性に基づいて素子膜の形状を変更することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記調整工程は、前記素子膜の電気的特性を実測するための測定用パターンを、前記半導体集積回路が形成される領域の外部領域に形成する測定用パターン形成工程を含み、該測定用パターンを実測することによって得られた電気的特性に基づいて素子膜の形状を変更することを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項4】

前記測定用パターンは、前記外部領域に成膜された素子膜を、測定用の電極または探針とコンタクトするためのコンタクト用パターンを含むことを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記調整工程は、前記成膜工程が行われた成膜装置の状態にかかる情報を含む情報を用いて統計的に得られる電気的特性に基づいて素子膜の形状を変更することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項6】

前記調整工程は、パターニングされた素子膜の厚さを増減することによって素子膜の形状を変更することを特徴とする請求項1から4のいずれか一つに記載の半導体装置の製造方法。

【請求項7】

前記調整工程は、パターニングされた素子膜をエッチングして素子膜の厚さを減じることにより素子膜の形状を変更することを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記調整工程は、

前記パターニング工程でパターニングされた素子膜上に第1の膜を成膜した後、パターニングして第1パターンを形成する第1パターン形成工程と、

前記第1パターン上に第2の膜を成膜した後、パターニングして第2パターンを形成する第2パターン形成工程と、を含み、

前記第1パターンは、パターニングされた素子膜上であって、かつ前記第2パターン下にない開口面を有することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記素子膜がポリシリコン膜であって、前記第1パターン形成工程は絶縁膜を成膜した後、パターニングしてポリシリコン膜と配線とを絶縁する層間絶縁パターンを形成する工程であり、かつ、前記第2パターン形成工程はアルミニウム膜を成膜した後、パターニングして配線パターンを形成する工程であることを特徴とする請求項8に記載の半導体装置の製造方法。

【請求項10】

半導体集積回路内に抵抗素子を形成する工程を含む半導体装置の製造方法であって、

前記抵抗素子を構成する素子膜と共に、前記半導体集積回路が形成される領域の外部領域にも前記素子膜を成膜する成膜工程と、

前記成膜工程において、前記半導体集積回路が形成された領域及び前記外部領域に成膜された素子膜をパターニングし、前記抵抗素子と共にモニタ用パターンを形成するパターニング工程と、

前記モニタ用パターンを使った前記素子膜の抵抗値の測定結果に基づいて、前記抵抗素子を構成する素子膜を、該素子膜よりも上方に設けられる膜と同時にエッチングする追加エッチング工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項1】

半導体集積回路内の半導体素子を構成する素子膜を成膜する成膜工程と、

前記成膜工程で成膜された素子膜をパターニングするパターニング工程と、

前記成膜工程で成膜された素子膜の電気的特性を取得し、取得された電気的特性に基づいて前記パターニング工程後に得られた素子膜の形状を変更することによってパターニングされた素子膜の電気的特性を調整する調整工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記調整工程は、前記素子膜または素子膜と同時に成膜された膜を実測することによって得られた電気的特性に基づいて素子膜の形状を変更することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記調整工程は、前記素子膜の電気的特性を実測するための測定用パターンを、前記半導体集積回路が形成される領域の外部領域に形成する測定用パターン形成工程を含み、該測定用パターンを実測することによって得られた電気的特性に基づいて素子膜の形状を変更することを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項4】

前記測定用パターンは、前記外部領域に成膜された素子膜を、測定用の電極または探針とコンタクトするためのコンタクト用パターンを含むことを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記調整工程は、前記成膜工程が行われた成膜装置の状態にかかる情報を含む情報を用いて統計的に得られる電気的特性に基づいて素子膜の形状を変更することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項6】

前記調整工程は、パターニングされた素子膜の厚さを増減することによって素子膜の形状を変更することを特徴とする請求項1から4のいずれか一つに記載の半導体装置の製造方法。

【請求項7】

前記調整工程は、パターニングされた素子膜をエッチングして素子膜の厚さを減じることにより素子膜の形状を変更することを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記調整工程は、

前記パターニング工程でパターニングされた素子膜上に第1の膜を成膜した後、パターニングして第1パターンを形成する第1パターン形成工程と、

前記第1パターン上に第2の膜を成膜した後、パターニングして第2パターンを形成する第2パターン形成工程と、を含み、

前記第1パターンは、パターニングされた素子膜上であって、かつ前記第2パターン下にない開口面を有することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記素子膜がポリシリコン膜であって、前記第1パターン形成工程は絶縁膜を成膜した後、パターニングしてポリシリコン膜と配線とを絶縁する層間絶縁パターンを形成する工程であり、かつ、前記第2パターン形成工程はアルミニウム膜を成膜した後、パターニングして配線パターンを形成する工程であることを特徴とする請求項8に記載の半導体装置の製造方法。

【請求項10】

半導体集積回路内に抵抗素子を形成する工程を含む半導体装置の製造方法であって、

前記抵抗素子を構成する素子膜と共に、前記半導体集積回路が形成される領域の外部領域にも前記素子膜を成膜する成膜工程と、

前記成膜工程において、前記半導体集積回路が形成された領域及び前記外部領域に成膜された素子膜をパターニングし、前記抵抗素子と共にモニタ用パターンを形成するパターニング工程と、

前記モニタ用パターンを使った前記素子膜の抵抗値の測定結果に基づいて、前記抵抗素子を構成する素子膜を、該素子膜よりも上方に設けられる膜と同時にエッチングする追加エッチング工程と、

を含むことを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2006−40917(P2006−40917A)

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願番号】特願2004−213934(P2004−213934)

【出願日】平成16年7月22日(2004.7.22)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願日】平成16年7月22日(2004.7.22)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]