半導体装置の製造方法

【課題】p−MOSトランジスタとn−MOSトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板11の第1領域13、第2領域、14にn型、p型ゲート電極膜34、37を形成する工程と、ゲート電極膜34、37上に第1保護膜38および第2保護膜39を形成する工程と、第2保護膜39に、ゲート電極サイズL1、L2より大きいサイズL3のゲート電極パターンを形成する工程と、第2保護膜39bに選択的に燐イオンを注入し、熱酸化速度が第2保護膜39aより大きくなるようにする工程と、第2保護膜39a、39bを熱酸化し、生成した第1および第2酸化膜42、43を選択的にエッチングして、ゲート電極パターンをスリム化する工程と、スリム化された第2保護膜39a、39bを用いてサイズL1、L2のゲート電極18、23を形成する工程と、を具備する。

【解決手段】半導体基板11の第1領域13、第2領域、14にn型、p型ゲート電極膜34、37を形成する工程と、ゲート電極膜34、37上に第1保護膜38および第2保護膜39を形成する工程と、第2保護膜39に、ゲート電極サイズL1、L2より大きいサイズL3のゲート電極パターンを形成する工程と、第2保護膜39bに選択的に燐イオンを注入し、熱酸化速度が第2保護膜39aより大きくなるようにする工程と、第2保護膜39a、39bを熱酸化し、生成した第1および第2酸化膜42、43を選択的にエッチングして、ゲート電極パターンをスリム化する工程と、スリム化された第2保護膜39a、39bを用いてサイズL1、L2のゲート電極18、23を形成する工程と、を具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に係り、特に絶縁ゲート電界効果トランジスタを有する半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の高集積化に伴って、チップサイズの増大を抑制するために絶縁ゲート電界効果トランジスタ(MOSトランジスタ)の微細化が求められている。

微細化による短チャンネル効果を抑制し従来の閾値電圧を維持するために、CMOS半導体装置では、p+ポリシリコンゲート電極を有するp−MOSトランジスタとn+ポリシリコンゲート電極を有するn−MOSトランジスタとを同一半導体基板に形成した所謂デュアルゲート構造が用いられている。

【0003】

然しながら、高濃度のp+ポリシリコンゲート電極およびn+ポリシリコンゲート電極を得るために、予めポリシリコン膜にp型およびn型不純物を高濃度にドープする場合に、高濃度にドープされたポリシリコン膜は導電型によりRIE(Reactive Ion Etching)のエッチング速度が異なるため、p−MOSトランジスタとn−MOSトランジスタとで、得られるゲート電極の寸法や形状にばらつきが生じるという問題がある。

【0004】

その結果、p−MOSトランジスタとn−MOSトランジスタとに特性のばらつきが生じ、特性が安定したCMOS半導体装置が得られないという問題がある。従って、微細化が妨げられるという問題がある。

【0005】

これに対して、p型およびn型不純物が高濃度にドープされたポリシリコン膜の不純物濃度が高い領域と低い領域とで、エッチング条件を変更する方法が知られている(例えば、特許文献1参照。)。

【0006】

特許文献1に開示された半導体装置の製造方法は、不純物濃度が高い上部領域を第2のエッチング条件よりサイドエッチングの入りにくい第1のエッチング条件(CF系を含むガス)でエッチング加工し、不純物濃度が低い下部領域を第2のエッチング条件(ハロゲン/O2系を含むガス)でエッチング加工している。

【0007】

これにより、p−MOSトランジスタとn−MOSトランジスタとで、形状差が小さく、寸法差の少ないゲート電極形状を得ている。

【0008】

然しながら、特許文献1に開示された半導体装置の製造方法は、プロセスの途中でエッチング条件を切り替えているので、切り替えるタイミングのばらつきにより、所望のゲート電極形状が得られない恐れがある。

【特許文献1】特開2004−266249号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明は、p−MOSトランジスタとn−MOSトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記目的を達成するために、本発明の一態様の半導体装置の製造方法では、半導体基板の主面の第1領域にゲート絶縁膜を介してn型ゲート電極膜を形成し、第2領域にゲート絶縁膜を介してp型ゲート電極膜を形成する工程と、前記第1および第2領域における前記ゲート電極膜上に第1保護膜を形成し、前記第1保護膜上に前記第1保護膜と異なる第2保護膜を形成する工程と、前記第1および第2領域における前記第2保護膜にゲート電極サイズより大きいサイズを有するゲート電極パターンを形成する工程と、前記ゲート電極パターンを形成した後、前記第2領域における前記第2保護膜に選択的にイオンを注入し、前記第2領域における前記第2保護膜の熱酸化速度が前記第1領域における前記第2保護膜の熱酸化速度より大きくなるようにする工程と、前記イオンを注入した後、前記第1および第2領域における前記第2保護膜を熱酸化し、生成した酸化膜を選択的にエッチングして、前記ゲート電極パターンをスリム化する工程と、前記第1および第2領域におけるスリム化された前記ゲート電極パターンを有する前記第2保護膜をマスクとして、前記第1および第2領域における前記第1保護膜をエッチングする工程と、前記第1および第2領域における前記第1保護膜をマスクとして、前記第1および第2領域における前記ゲート電極膜をエッチングしてゲート電極を形成する工程と、を具備することを特徴としている。

【0011】

本発明の別態様の半導体装置の製造方法では、半導体基板の主面の第1領域にゲート絶縁膜を介してn型ゲート電極膜を形成し、第2領域にゲート絶縁膜を介してp型ゲート電極膜を形成する工程と、前記第1および第2領域における前記ゲート電極膜上に第1保護膜を形成し、前記第1保護膜上に前記第1保護膜と異なる第2保護膜を形成する工程と、前記第1および第2領域における前記第2保護膜にゲート電極サイズより大きいサイズを有するゲート電極パターンを形成する工程と、前記ゲート電極パターンを形成した後、前記第1領域における前記第2保護膜にイオンを選択的に注入し、前記第1領域における前記第2保護膜のエッチング速度が前記第2領域における前記第2保護膜のエッチング速度より小さくなるようにする工程と、前記イオンを注入した後、前記第1および第2領域における前記第2保護膜を所定時間エッチングして、前記ゲート電極パターンをスリム化する工程と、前記第1および第2領域におけるスリム化された前記ゲート電極パターンを有する前記第2保護膜をマスクとして、前記第1および第2領域における前記第1保護膜をエッチングする工程と、前記第1および第2領域における前記第1保護膜をマスクとして、前記第1および第2領域における前記ゲート電極膜をエッチングしてゲート電極を形成する工程と、を具備することを特徴としている。

【発明の効果】

【0012】

本発明によれば、p−MOSトランジスタとn−MOSトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法が得られる。

【発明を実施するための最良の形態】

【0013】

以下、本発明の実施例について図面を参照しながら説明する。

【実施例1】

【0014】

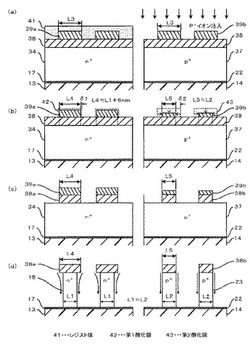

本発明の実施例1に係る半導体装置の製造方法について図1乃至図4を用いて説明する。図1は半導体装置を示す断面図、図2乃至図4は半導体装置の製造工程を順に示す断面図である。

【0015】

図1に示すように、本実施例の半導体装置10は、半導体基板、例えばn型シリコン基板11にSTI(Shallow Trench Isolation)12により絶縁分離されたp型ウェル領域(第1領域)13およびn型ウェル領域(第2領域)14と、p型ウェル領域13に形成されたn−MOSトランジスタ15と、n型ウェル領域14に形成されたp−MOSトランジスタ16とを具備している。

【0016】

n−MOSトランジスタ15は、ゲート絶縁膜17と、n+ポリシリコン第1ゲート電極18と、n+ポリシリコン第1ゲート電極18の両側に形成されたソース領域20およびドレイン領域21とを有している。

【0017】

同様に、p−MOSトランジスタ16は、ゲート絶縁膜22と、p+ポリシリコン第2ゲート電極23と、p+ポリシリコン第2ゲート電極23の両側に形成されたソース領域25およびドレイン領域26とを有している。

【0018】

n+ポリシリコン第1ゲート電極18とp+ポリシリコン第2ゲート電極23は、ゲート電極サイズ、例えばゲート長L1、L2がそれぞれ30nm、ゲート高さがそれぞれ130nm程度であり、その形状は略等しく形成されている。

【0019】

以後、n+ポリシリコン第1ゲート電極18を単に第1ゲート電極18、p+ポリシリコン第2ゲート電極23を単に第2ゲート電極23とも称する。

【0020】

次に、半導体装置10の製造方法について図2乃至図4を用いて詳しく説明する。

始めに、n型シリコン基板11にトレンチを形成し、トレンチ内部に絶縁物を埋め込んで形成したSTI12により電気的に分離されたp型ウェル領域13およびn型ウェル領域14を形成する。

【0021】

次に、図2(a)に示すように、n型シリコン基板11上に、ゲート絶縁膜17、22として、例えば熱酸化法により厚さ1.5nm程度のシリコン酸化膜を形成し、ゲート電極膜として、例えばCVD(Chemical Vapor Deposition)法により厚さ130nm程度のアンドープポリシリコン膜31を形成する。

【0022】

次に、図2(b)に示すように、アンドープポリシリコン膜31上にフォトリソグラフィ法によりp型ウェル領域13に対向する位置に開口32を有するレジスト膜33を形成し、レジスト膜33をマスクとしてアンドープポリシリコン膜31に燐イオン(P+)を、例えば加速電圧1keV、ドーズ量1E15cm−2程度注入する。

【0023】

これにより、p型ウェル領域13におけるアンドープポリシリコン膜31には、Pイオンの注入プロファイルに応じた不純物濃度プロファイルを有するn+ゲート電極膜34が形成される。

【0024】

次に、図2(c)に示すように、n+ゲート電極膜34上にフォトリソグラフィ法によりn型ウェル領域14に対向する位置に開口35を有するフォトレジスト膜36を形成し、フォトレジスト膜36をマスクとしてアンドープポリシリコン膜31にホウ素イオン(B+)を、例えば加速電圧3keV、ドーズ量4E15cm−2程度注入する。

【0025】

これによりn型ウェル領域14におけるアンドープポリシリコン膜31にはBイオンの注入プロファイルに応じた不純物濃度プロファイルを有するp+ゲート電極膜37が形成される。

【0026】

次に、図3(a)に示すように、第1および第2領域13、14におけるゲート電極膜34、37上に第1保護膜として、例えば厚さ60nm程度のシリコン窒化膜38を形成する。

次に、シリコン窒化膜38上に、第2保護膜として、例えば厚さ40nm程度のアモルファスシリコン膜39を形成する。

【0027】

次に、図3(b)に示すように、アモルファスシリコン膜39上に、反射防止膜(図示せず)を介してレジスト膜40を形成し、ArFエキシマレーザ光を用いた投影露光法を用いて、レジスト膜40にゲート電極サイズより大きいサイズを有するゲート電極パターンを形成する。ゲート電極パターンサイズL3は、例えばゲート長L1、L2=30nmより大きい42nm、厚さは280nm程度である。

【0028】

具体的には、例えばフォトリソグラフィ法により、レジスト膜40にサイズが60〜80nmのゲート電極パターンを形成し、O2系プラズマエッチングにより、反射防止膜を除去する過程でレジスト膜40をスリミングして、サイズが42nmのゲート電極パターンを形成する。

【0029】

次に、図3(c)に示すように、フォトレジスト膜40が有するゲート電極パターンを、アモルファスシリコン膜39に転写するために、ICP(Inductively Coupled Plasma)型RIE(Reactive Ion Etching)装置を用い、以下のエッチング条件に従い、反射防止膜およびアモルファスシリコン膜39をエッチングする。

【0030】

反射防止膜のエッチングは、例えば圧力10mT、CF4/O2=50/50sccm、上部電極に印加するソースパワーを350W、下部電極に印加するバイアスパワーを30Wで行う。

アモルファスシリコン膜39のエッチングは、例えば圧力6mT、HBr/CF4/Cl2=50/120/10sccm、上部電極に印加するソースパワーを600W、下部電極に印加するバイアスパワーを150Wで行う。

【0031】

次に、例えば圧力90mT、HBr/O2=150/4sccm、上部電極に印加するソースパワーを800W、下部電極に印加するバイアスパワーを100Wとして、アモルファスシリコン膜39の残渣を除去する。

【0032】

次に、アッシャーを用いて、レジスト膜40を灰化し、硫酸と過酸化水素の混合液(SH液)により、エッチング後の付着物を除去する。

【0033】

これにより、ゲート電極サイズより大きいサイズを有するゲート電極パターンを備えたアモルファスシリコン膜39a、39bが形成される。

【0034】

次に、図4(a)に示すように、p型ウェル領域13をレジスト膜41で被覆し、n型ウェル領域14に燐イオン(P+)を、例えば加速電圧1keV、ドーズ量1E15cm−2程度注入する。

次に、アッシャーを用いて、レジスト膜41を灰化し、硫酸と過酸化水素の混合液(SH液)により、付着物を除去する。

これにより、n型ウェル領域14におけるアモルファスシリコン膜39bにのみ燐(P)がドープされる。

【0035】

次に、図4(b)に示すように、まずp型ウェル領域13およびn型ウェル領域14におけるアモルファスシリコン膜39a、39bを、例えば650℃、70sec程度で、熱酸化する。燐(P)がドープされたアモルファスシリコン膜39bは、アンドープのアモルファスシリコン膜39aより熱酸化速度が大きくなる。

【0036】

その結果、p型ウェル領域13における熱酸化速度の小さいアモルファスシリコン膜39aには、膜厚が0.75nm程度の薄い第1酸化膜42が形成される。

一方、n型ウェル領域14における熱酸化速度の大きいアモルファスシリコン膜39bには、膜厚が1.5nm程度の厚い第2酸化膜43が形成される。

【0037】

次に、フッ酸を含むエッチング液を用いて、第1酸化膜42および第2酸化膜43をエッチングすることにより、p型ウェル領域13におけるアモルファスシリコン膜39aは1.5nmスリム化され、n型ウェル領域14におけるアモルファスシリコン膜39bは3nmスリム化される。

【0038】

次に、上述した熱酸化工程とエッチング工程をトータル4回繰り返すことにより、p型ウェル領域13におけるアモルファスシリコン膜39aのゲート電極パターンサイズL4は、第1ゲート電極18のゲート電極サイズL1=30nmより6nm大きい、36nmとなる。

【0039】

一方、n型ウェル領域14におけるアモルファスシリコン膜39bのゲート電極パターンサイズL5は、第2ゲート電極23のゲート電極サイズL2=30nmに略等しくなる。本明細書では、アモルファスシリコン膜39bのゲート電極パターンサイズL5が、第2ゲート電極23のゲート電極サイズL2に略等しいとは、後述するp+ゲート電極膜37を異方性エッチングしたときに、ゲート電極サイズL2の第2ゲート電極23が得られることを意味している。

【0040】

また、図中において、δ1は第1酸化膜42のトータルの膜厚を示し、δ2は第2酸化膜43のトータルの膜厚を示している。

【0041】

次に、図4(c)に示すように、p型ウェル領域13におけるゲート電極パターンサイズL4が36nmのアモルファスシリコン膜39a、およびn型ウェル領域14におけるゲート電極パターンサイズL5が30nmのアモルファスシリコン膜39bをマスクとして、ICP型RIE装置によりシリコン窒化膜38をエッチングする。

【0042】

シリコン窒化膜38のエッチングは、例えば圧力20mT、CH3F/O2/He=80/30/100sccm、上部電極に印加するソースパワーを400W、下部電極に印加するバイアスパワーを200Wで行う。

【0043】

次に、図4(d)に示すように、p型ウェル領域13およびn型ウェル領域14におけるシリコン窒化膜38a、38bをマスクとして、ICP型RIE装置によりn+ゲート電極膜34およびp+ゲート電極膜37をエッチングする。

【0044】

n+ゲート電極膜34およびp+ゲート電極膜37の上部のエッチングは、例えば圧力6mT、HBr/CF4/Cl2=150/20/10sccm、上部電極に印加するソースパワーを600W、下部電極に印加するバイアスパワーを150Wで行う。

【0045】

次に、n+ゲート電極膜34およびp+ゲート電極膜37の下部のエッチングは例えば、圧力15mT、HBr/O2=150/4sccm、上部電極に印加するソースパワーを500W、下部電極に印加するバイアスパワーを45Wで行う。

【0046】

次に、例えば圧力90mT、HBr/O2=150/4sccm、上部電極に印加するソースパワーを800W、下部電極に印加するバイアスパワーを100Wとして、n+ゲート電極膜34およびp+ゲート電極膜37の残渣を除去する。

【0047】

これにより、エッチング速度の小さいp+ゲート電極膜37は、サイドエッチングされることなく、ほぼ垂直にエッチングされる。その結果、所定のゲート長L2を有するp+ゲート電極23が得られる。

【0048】

一方、エッチング速度の大きいn+ゲート電極膜34は、サイドエッチングされながら、ほぼ垂直にエッチングされる。その結果、所定のゲート長L1を有するn+ゲート電極18が得られる。

【0049】

これにより、n+ゲート電極膜34とp+ゲート電極膜37とのエッチング速度の差によるゲート電極形状のばらつきが防止され、形状の揃ったn+ゲート電極18、p+ゲート電極23を得ることが可能である。

【0050】

図5は、燐およびホウ素が高濃度に注入されたポリシリコン膜のICP型RIE装置によるエッチング速度を示す図で、図中のaは燐が高濃度に注入されたポリシリコン膜、bはホウ素が高濃度に注入されたポリシリコン膜、cは比較としてアンドープポリシリコン膜の場合である。

【0051】

図5に示すように、実験によれば、燐が高濃度に注入されたポリシリコン膜aのエッチング速度はホウ素が高濃度に注入されたポリシリコン膜bより1.2倍程度大きな値が得られた。

【0052】

また、燐が高濃度に注入されたポリシリコン膜aのエッチング速度はアンドープポリシリコン膜cより大きく、ホウ素が高濃度に注入されたポリシリコン膜bのエッチング速度はアンドープポリシリコン膜cより小さくなる結果が得られた。

【0053】

更に、実験によれば、ポリシリコン膜中の燐の濃度が1E18cm−3を越えるあたりから、ポリシリコン膜のエッチング速度が大きくなる結果が得られた。

これから、n+ゲート電極膜34の表面から不純物濃度が略1E18cm−3になるまでの領域を上部とし、それより深い領域を下部と規定する。

【0054】

例えば、アンドープポリシリコン膜31に燐を加速電圧5keV、ドーズ量5E15cm−2程度イオン注入した場合に、ピーク不純物濃度が〜E21cm−3台、不純物濃度が1E18cm−3になる深さが30nm程度の注入プロファイルが得られるので、ここでは、表面から深さ30nmまでの領域を上部とし、深さ30nm以上の領域を下部としている。

【0055】

次に、周知のプロセスにより、p型ウェル領域13にソース領域20およびドレイン領域21を形成し、n型ウェル領域14にソース領域25およびドレイン領域26を形成する。

【0056】

次に、第1および第2ゲート電極18、23の下を除いたゲート絶縁膜17、22をそれぞれ除去し、第1および第2ゲート電極18、23、ソース領域20、25およびドレイン領域21、26上にニッケル(Ni)膜を、例えばスパッタリング法により形成し、熱処理することによりNiシリサイド層(図示せず)を形成する。

【0057】

これにより、n+ポリシリコン第1ゲート電極18とp+ポリシリコン第2ゲート電極23とのゲート電極形状のばらつきが防止され、特性の揃ったp−MOSトランジスタ15とn−MOSトランジスタ16を有するCMOS半導体装置10が得られる。

【0058】

以上説明したように、本実施例によれば、エッチング速度の大きいn+ゲート電極膜34上にゲート長L1より大きいゲート電極パターンサイズL4のシリコン窒化膜38aを形成し、エッチング速度の小さいp+ゲート電極膜37上にゲート長L2に略等しいゲート電極パターンサイズL5のシリコン窒化膜38bを形成している。

【0059】

その結果、n+ゲート電極膜34がサイドエッチングされ、ゲート電極パターンサイズL4より小さいゲート長L1を有する第1ゲート電極18が得られる。

p+ゲート電極膜37はサイドエッチングされることなく、ゲート電極パターンサイズL5に略等しいゲート長L2を有する第2ゲート電極23が得られる。

【0060】

従って、ゲート電極形状のばらつきが少なく、特性の揃ったp−MOSトランジスタ15とn−MOSトランジスタ16を有するCMOS半導体装置10を安定して製造することができる。

また、微細化によりチップサイズが小さく、集積度の高い半導体装置を提供することができる。

【0061】

ここでは、n+ゲート電極膜34またはp+ゲート電極膜37を、アンドープポリシリコン膜31にn型不純物またはp型不純物をイオン注入して形成した場合について説明したが、予めn型不純物またはp型不純物がドープされたドープドポリシリコン膜を各領域でパターン形成することで得たものであっても構わない。

【0062】

n+ゲート電極膜34およびp+ゲート電極膜37がポリシリコン膜である場合について説明したが、シリコン・ゲルマニウム化合物(SiGe)膜とすることもできる。

この場合、例えばゲート絶縁膜17、22上にSiH4ガスとGeH4ガスを用いたCVD法により、例えばGeの組成が20atm%程度の多結晶シリコン・ゲルマニウム(SiGe)化合物膜を形成する。

【0063】

シリコン・ゲルマニウム化合物は、キャリアの移動度がポリシリコンより大きいためゲート抵抗をより低減させることができるので、ゲート電極の空乏化の抑制が容易になり、p−MOSトランジスタおよびn−MOSトランジスタの特性が向上する利点がある。

【0064】

シリコン・ゲルマニウム化合物膜のゲルマニウムの組成は20atm%に限らず、所望の特性が得られる範囲で自由に設定することができる。

また、ゲート電極膜がシリコン・ゲルマニウム化合物膜に炭素(C)を添加したSiGeC膜であっても構わない。

【実施例2】

【0065】

図6は本発明の実施例2に係る半導体装置の製造工程の要部を、順に示す断面図である。本実施例において、上記実施例1と同一の構成部分には同一符号を付してその説明は省略し、異なる部分についてのみ説明する。

本実施例が実施例1と異なる点は、第1領域における第2保護膜にホウ素イオンを選択的に注入したことにある。

【0066】

即ち、図6(a)に示すように、n型ウェル領域14をレジスト膜44で被覆し、p型ウェル領域13にホウ素イオン(B+)を、例えば加速電圧1keV、ドーズ量5E15cm−2程度注入する。

これにより、p型ウェル領域13におけるアモルファスシリコン膜39aにのみホウ素(B)がドープされる。

次にアッシャーを用いて、レジスト膜44を灰化し、硫酸と過酸化水素の混合液(SH液)により、付着物を除去する。

【0067】

ここで、p型ウェル領域13およびn型ウェル領域14におけるアモルファスシリコン膜39a、39bのゲート電極パターンサイズL6を36nmに設定しておく。

【0068】

次に、図6(b)に示すように、n型ウェル領域14におけるホウ素(B)がドープされていないアモルファスシリコン膜39bを選択的にエッチングするエッチング液、例えば水酸化2−ヒドロキシエチルトリメチルアンモニウムを含む水溶液を用いて、p型ウェル領域13およびn型ウェル領域14におけるアモルファスシリコン膜39a、39bをウェットエッチングする。

【0069】

実験によれば、水酸化2−ヒドロキシエチルトリメチルアンモニウムを0.05wt%含む水溶液に対して、アンドープアモルファスシリコン膜39bのエッチング速度が6nm/min程度であるのに対して、Bがドープされたアモルファスシリコン膜39aのエッチング速度が0.03nm/min程度と、エッチング速度が約200倍異なることが判明している。

【0070】

従って、p型ウェル領域13およびn型ウェル領域14におけるアモルファスシリコン膜39a、39bを30sec程度エッチングすることにより、p型ウェル領域13におけるBがドープされたアモルファスシリコン膜39aはほとんどエッチングされない(エッチング量δ3〜0.015nm)ので、ゲート電極パターンサイズL4はエッチング前のゲート電極パターンサイズL6をほぼ維持することができる。

一方、n型ウェル領域14におけるアンドープアモルファスシリコン膜39bはエッチングされる(エッチング量δ4〜3nm)ので、ゲート電極パターンサイズL5はゲート電極パターンサイズL6より6nm程度細くなり、第2ゲート電極23のゲート長L2に略等しくすることができる。

【0071】

次に、p型ウェル領域13およびn型ウェル領域14におけるアモルファスシリコン膜39a、39bをマスクとして、ICP型RIE装置によりシリコン窒化膜38をエッチングする。

【0072】

次に、図4(d)と同様にしてp型ウェル領域13およびn型ウェル領域14におけるシリコン窒化膜38a、38bをマスクとして、ICP型RIE装置によりn+ゲート電極膜34およびp+ゲート電極膜37をエッチングする。

【0073】

これにより、エッチング速度の小さいp+ゲート電極膜37は、サイドエッチングされることなく、ほぼ垂直にエッチングされる。その結果、所定のゲート長L2を有するp+ゲート電極23が得られる。

【0074】

一方、エッチング速度の大きいn+ゲート電極膜34は、サイドエッチングされながら、ほぼ垂直にエッチングされる。その結果、所定のゲート長L1を有するn+ゲート電極18が得られる。

【0075】

これにより、n+ゲート電極膜34とp+ゲート電極膜37とのエッチング速度の差によるゲート電極形状のばらつきが防止され、形状の揃ったn+ゲート電極18、p+ゲート電極23を得ることが可能である。

【0076】

以上説明したように、本実施例の半導体装置の製造方法によれば、p型ウェル領域13におけるアモルファスシリコン膜39aにのみホウ素(B)をドープして、アモルファスシリコン膜39aのエッチング速度がアモルファスシリコン膜39bのエッチング速度より小さくなるようにしているので、熱酸化工程が不要になる利点がある。

【0077】

ここでは、Bがドープされていないアモルファスシリコン膜39bを選択的にエッチングするエッチング液として、水酸化2−ヒドロキシエチルトリメチルアンモニウムを含むエッチング液を用いる場合について説明したが、基本的にアルカリ性の薬液であれば、Bがドープされていないアモルファスシリコン膜39bとBがドープされているアモルファスシリコン膜39aとでエッチング速度が異なるので、目的のエッチング選択比が得られる範囲において使用することができる。

【図面の簡単な説明】

【0078】

【図1】本発明の実施例1に係る半導体装置を示す断面図。

【図2】本発明の実施例1に係る半導体装置の製造工程を示す断面図。

【図3】本発明の実施例1に係る半導体装置の製造工程を示す断面図。

【図4】本発明の実施例1に係る半導体装置の製造工程を示す断面図。

【図5】本発明の実施例1に係るポリシリコン膜のエッチング速度を示す図。

【図6】本発明の実施例2に係る半導体装置の製造工程の要部を示す断面図。

【符号の説明】

【0079】

10 半導体装置

11 n型シリコン基板

12 STI

13 p型ウェル領域(第1領域)

14 n型ウェル領域(第2領域)

15 n―MOSトランジスタ

16 p―MOSトランジスタ

17、22 ゲート絶縁膜

18 第1ゲート電極

20、25 ソース領域

21、26 ドレイン領域

23 第2ゲート電極

31 アンドープポリシリコン膜

32、35 開口

33、36、40、41、44 レジスト膜

34 n+ゲート電極膜

37 p+ゲート電極膜

38 シリコン窒化膜(第1保護膜)

39 アモルファスシリコン膜(第2保護膜)

42 第1酸化膜

43 第2酸化膜

【技術分野】

【0001】

本発明は、半導体装置の製造方法に係り、特に絶縁ゲート電界効果トランジスタを有する半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の高集積化に伴って、チップサイズの増大を抑制するために絶縁ゲート電界効果トランジスタ(MOSトランジスタ)の微細化が求められている。

微細化による短チャンネル効果を抑制し従来の閾値電圧を維持するために、CMOS半導体装置では、p+ポリシリコンゲート電極を有するp−MOSトランジスタとn+ポリシリコンゲート電極を有するn−MOSトランジスタとを同一半導体基板に形成した所謂デュアルゲート構造が用いられている。

【0003】

然しながら、高濃度のp+ポリシリコンゲート電極およびn+ポリシリコンゲート電極を得るために、予めポリシリコン膜にp型およびn型不純物を高濃度にドープする場合に、高濃度にドープされたポリシリコン膜は導電型によりRIE(Reactive Ion Etching)のエッチング速度が異なるため、p−MOSトランジスタとn−MOSトランジスタとで、得られるゲート電極の寸法や形状にばらつきが生じるという問題がある。

【0004】

その結果、p−MOSトランジスタとn−MOSトランジスタとに特性のばらつきが生じ、特性が安定したCMOS半導体装置が得られないという問題がある。従って、微細化が妨げられるという問題がある。

【0005】

これに対して、p型およびn型不純物が高濃度にドープされたポリシリコン膜の不純物濃度が高い領域と低い領域とで、エッチング条件を変更する方法が知られている(例えば、特許文献1参照。)。

【0006】

特許文献1に開示された半導体装置の製造方法は、不純物濃度が高い上部領域を第2のエッチング条件よりサイドエッチングの入りにくい第1のエッチング条件(CF系を含むガス)でエッチング加工し、不純物濃度が低い下部領域を第2のエッチング条件(ハロゲン/O2系を含むガス)でエッチング加工している。

【0007】

これにより、p−MOSトランジスタとn−MOSトランジスタとで、形状差が小さく、寸法差の少ないゲート電極形状を得ている。

【0008】

然しながら、特許文献1に開示された半導体装置の製造方法は、プロセスの途中でエッチング条件を切り替えているので、切り替えるタイミングのばらつきにより、所望のゲート電極形状が得られない恐れがある。

【特許文献1】特開2004−266249号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明は、p−MOSトランジスタとn−MOSトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記目的を達成するために、本発明の一態様の半導体装置の製造方法では、半導体基板の主面の第1領域にゲート絶縁膜を介してn型ゲート電極膜を形成し、第2領域にゲート絶縁膜を介してp型ゲート電極膜を形成する工程と、前記第1および第2領域における前記ゲート電極膜上に第1保護膜を形成し、前記第1保護膜上に前記第1保護膜と異なる第2保護膜を形成する工程と、前記第1および第2領域における前記第2保護膜にゲート電極サイズより大きいサイズを有するゲート電極パターンを形成する工程と、前記ゲート電極パターンを形成した後、前記第2領域における前記第2保護膜に選択的にイオンを注入し、前記第2領域における前記第2保護膜の熱酸化速度が前記第1領域における前記第2保護膜の熱酸化速度より大きくなるようにする工程と、前記イオンを注入した後、前記第1および第2領域における前記第2保護膜を熱酸化し、生成した酸化膜を選択的にエッチングして、前記ゲート電極パターンをスリム化する工程と、前記第1および第2領域におけるスリム化された前記ゲート電極パターンを有する前記第2保護膜をマスクとして、前記第1および第2領域における前記第1保護膜をエッチングする工程と、前記第1および第2領域における前記第1保護膜をマスクとして、前記第1および第2領域における前記ゲート電極膜をエッチングしてゲート電極を形成する工程と、を具備することを特徴としている。

【0011】

本発明の別態様の半導体装置の製造方法では、半導体基板の主面の第1領域にゲート絶縁膜を介してn型ゲート電極膜を形成し、第2領域にゲート絶縁膜を介してp型ゲート電極膜を形成する工程と、前記第1および第2領域における前記ゲート電極膜上に第1保護膜を形成し、前記第1保護膜上に前記第1保護膜と異なる第2保護膜を形成する工程と、前記第1および第2領域における前記第2保護膜にゲート電極サイズより大きいサイズを有するゲート電極パターンを形成する工程と、前記ゲート電極パターンを形成した後、前記第1領域における前記第2保護膜にイオンを選択的に注入し、前記第1領域における前記第2保護膜のエッチング速度が前記第2領域における前記第2保護膜のエッチング速度より小さくなるようにする工程と、前記イオンを注入した後、前記第1および第2領域における前記第2保護膜を所定時間エッチングして、前記ゲート電極パターンをスリム化する工程と、前記第1および第2領域におけるスリム化された前記ゲート電極パターンを有する前記第2保護膜をマスクとして、前記第1および第2領域における前記第1保護膜をエッチングする工程と、前記第1および第2領域における前記第1保護膜をマスクとして、前記第1および第2領域における前記ゲート電極膜をエッチングしてゲート電極を形成する工程と、を具備することを特徴としている。

【発明の効果】

【0012】

本発明によれば、p−MOSトランジスタとn−MOSトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法が得られる。

【発明を実施するための最良の形態】

【0013】

以下、本発明の実施例について図面を参照しながら説明する。

【実施例1】

【0014】

本発明の実施例1に係る半導体装置の製造方法について図1乃至図4を用いて説明する。図1は半導体装置を示す断面図、図2乃至図4は半導体装置の製造工程を順に示す断面図である。

【0015】

図1に示すように、本実施例の半導体装置10は、半導体基板、例えばn型シリコン基板11にSTI(Shallow Trench Isolation)12により絶縁分離されたp型ウェル領域(第1領域)13およびn型ウェル領域(第2領域)14と、p型ウェル領域13に形成されたn−MOSトランジスタ15と、n型ウェル領域14に形成されたp−MOSトランジスタ16とを具備している。

【0016】

n−MOSトランジスタ15は、ゲート絶縁膜17と、n+ポリシリコン第1ゲート電極18と、n+ポリシリコン第1ゲート電極18の両側に形成されたソース領域20およびドレイン領域21とを有している。

【0017】

同様に、p−MOSトランジスタ16は、ゲート絶縁膜22と、p+ポリシリコン第2ゲート電極23と、p+ポリシリコン第2ゲート電極23の両側に形成されたソース領域25およびドレイン領域26とを有している。

【0018】

n+ポリシリコン第1ゲート電極18とp+ポリシリコン第2ゲート電極23は、ゲート電極サイズ、例えばゲート長L1、L2がそれぞれ30nm、ゲート高さがそれぞれ130nm程度であり、その形状は略等しく形成されている。

【0019】

以後、n+ポリシリコン第1ゲート電極18を単に第1ゲート電極18、p+ポリシリコン第2ゲート電極23を単に第2ゲート電極23とも称する。

【0020】

次に、半導体装置10の製造方法について図2乃至図4を用いて詳しく説明する。

始めに、n型シリコン基板11にトレンチを形成し、トレンチ内部に絶縁物を埋め込んで形成したSTI12により電気的に分離されたp型ウェル領域13およびn型ウェル領域14を形成する。

【0021】

次に、図2(a)に示すように、n型シリコン基板11上に、ゲート絶縁膜17、22として、例えば熱酸化法により厚さ1.5nm程度のシリコン酸化膜を形成し、ゲート電極膜として、例えばCVD(Chemical Vapor Deposition)法により厚さ130nm程度のアンドープポリシリコン膜31を形成する。

【0022】

次に、図2(b)に示すように、アンドープポリシリコン膜31上にフォトリソグラフィ法によりp型ウェル領域13に対向する位置に開口32を有するレジスト膜33を形成し、レジスト膜33をマスクとしてアンドープポリシリコン膜31に燐イオン(P+)を、例えば加速電圧1keV、ドーズ量1E15cm−2程度注入する。

【0023】

これにより、p型ウェル領域13におけるアンドープポリシリコン膜31には、Pイオンの注入プロファイルに応じた不純物濃度プロファイルを有するn+ゲート電極膜34が形成される。

【0024】

次に、図2(c)に示すように、n+ゲート電極膜34上にフォトリソグラフィ法によりn型ウェル領域14に対向する位置に開口35を有するフォトレジスト膜36を形成し、フォトレジスト膜36をマスクとしてアンドープポリシリコン膜31にホウ素イオン(B+)を、例えば加速電圧3keV、ドーズ量4E15cm−2程度注入する。

【0025】

これによりn型ウェル領域14におけるアンドープポリシリコン膜31にはBイオンの注入プロファイルに応じた不純物濃度プロファイルを有するp+ゲート電極膜37が形成される。

【0026】

次に、図3(a)に示すように、第1および第2領域13、14におけるゲート電極膜34、37上に第1保護膜として、例えば厚さ60nm程度のシリコン窒化膜38を形成する。

次に、シリコン窒化膜38上に、第2保護膜として、例えば厚さ40nm程度のアモルファスシリコン膜39を形成する。

【0027】

次に、図3(b)に示すように、アモルファスシリコン膜39上に、反射防止膜(図示せず)を介してレジスト膜40を形成し、ArFエキシマレーザ光を用いた投影露光法を用いて、レジスト膜40にゲート電極サイズより大きいサイズを有するゲート電極パターンを形成する。ゲート電極パターンサイズL3は、例えばゲート長L1、L2=30nmより大きい42nm、厚さは280nm程度である。

【0028】

具体的には、例えばフォトリソグラフィ法により、レジスト膜40にサイズが60〜80nmのゲート電極パターンを形成し、O2系プラズマエッチングにより、反射防止膜を除去する過程でレジスト膜40をスリミングして、サイズが42nmのゲート電極パターンを形成する。

【0029】

次に、図3(c)に示すように、フォトレジスト膜40が有するゲート電極パターンを、アモルファスシリコン膜39に転写するために、ICP(Inductively Coupled Plasma)型RIE(Reactive Ion Etching)装置を用い、以下のエッチング条件に従い、反射防止膜およびアモルファスシリコン膜39をエッチングする。

【0030】

反射防止膜のエッチングは、例えば圧力10mT、CF4/O2=50/50sccm、上部電極に印加するソースパワーを350W、下部電極に印加するバイアスパワーを30Wで行う。

アモルファスシリコン膜39のエッチングは、例えば圧力6mT、HBr/CF4/Cl2=50/120/10sccm、上部電極に印加するソースパワーを600W、下部電極に印加するバイアスパワーを150Wで行う。

【0031】

次に、例えば圧力90mT、HBr/O2=150/4sccm、上部電極に印加するソースパワーを800W、下部電極に印加するバイアスパワーを100Wとして、アモルファスシリコン膜39の残渣を除去する。

【0032】

次に、アッシャーを用いて、レジスト膜40を灰化し、硫酸と過酸化水素の混合液(SH液)により、エッチング後の付着物を除去する。

【0033】

これにより、ゲート電極サイズより大きいサイズを有するゲート電極パターンを備えたアモルファスシリコン膜39a、39bが形成される。

【0034】

次に、図4(a)に示すように、p型ウェル領域13をレジスト膜41で被覆し、n型ウェル領域14に燐イオン(P+)を、例えば加速電圧1keV、ドーズ量1E15cm−2程度注入する。

次に、アッシャーを用いて、レジスト膜41を灰化し、硫酸と過酸化水素の混合液(SH液)により、付着物を除去する。

これにより、n型ウェル領域14におけるアモルファスシリコン膜39bにのみ燐(P)がドープされる。

【0035】

次に、図4(b)に示すように、まずp型ウェル領域13およびn型ウェル領域14におけるアモルファスシリコン膜39a、39bを、例えば650℃、70sec程度で、熱酸化する。燐(P)がドープされたアモルファスシリコン膜39bは、アンドープのアモルファスシリコン膜39aより熱酸化速度が大きくなる。

【0036】

その結果、p型ウェル領域13における熱酸化速度の小さいアモルファスシリコン膜39aには、膜厚が0.75nm程度の薄い第1酸化膜42が形成される。

一方、n型ウェル領域14における熱酸化速度の大きいアモルファスシリコン膜39bには、膜厚が1.5nm程度の厚い第2酸化膜43が形成される。

【0037】

次に、フッ酸を含むエッチング液を用いて、第1酸化膜42および第2酸化膜43をエッチングすることにより、p型ウェル領域13におけるアモルファスシリコン膜39aは1.5nmスリム化され、n型ウェル領域14におけるアモルファスシリコン膜39bは3nmスリム化される。

【0038】

次に、上述した熱酸化工程とエッチング工程をトータル4回繰り返すことにより、p型ウェル領域13におけるアモルファスシリコン膜39aのゲート電極パターンサイズL4は、第1ゲート電極18のゲート電極サイズL1=30nmより6nm大きい、36nmとなる。

【0039】

一方、n型ウェル領域14におけるアモルファスシリコン膜39bのゲート電極パターンサイズL5は、第2ゲート電極23のゲート電極サイズL2=30nmに略等しくなる。本明細書では、アモルファスシリコン膜39bのゲート電極パターンサイズL5が、第2ゲート電極23のゲート電極サイズL2に略等しいとは、後述するp+ゲート電極膜37を異方性エッチングしたときに、ゲート電極サイズL2の第2ゲート電極23が得られることを意味している。

【0040】

また、図中において、δ1は第1酸化膜42のトータルの膜厚を示し、δ2は第2酸化膜43のトータルの膜厚を示している。

【0041】

次に、図4(c)に示すように、p型ウェル領域13におけるゲート電極パターンサイズL4が36nmのアモルファスシリコン膜39a、およびn型ウェル領域14におけるゲート電極パターンサイズL5が30nmのアモルファスシリコン膜39bをマスクとして、ICP型RIE装置によりシリコン窒化膜38をエッチングする。

【0042】

シリコン窒化膜38のエッチングは、例えば圧力20mT、CH3F/O2/He=80/30/100sccm、上部電極に印加するソースパワーを400W、下部電極に印加するバイアスパワーを200Wで行う。

【0043】

次に、図4(d)に示すように、p型ウェル領域13およびn型ウェル領域14におけるシリコン窒化膜38a、38bをマスクとして、ICP型RIE装置によりn+ゲート電極膜34およびp+ゲート電極膜37をエッチングする。

【0044】

n+ゲート電極膜34およびp+ゲート電極膜37の上部のエッチングは、例えば圧力6mT、HBr/CF4/Cl2=150/20/10sccm、上部電極に印加するソースパワーを600W、下部電極に印加するバイアスパワーを150Wで行う。

【0045】

次に、n+ゲート電極膜34およびp+ゲート電極膜37の下部のエッチングは例えば、圧力15mT、HBr/O2=150/4sccm、上部電極に印加するソースパワーを500W、下部電極に印加するバイアスパワーを45Wで行う。

【0046】

次に、例えば圧力90mT、HBr/O2=150/4sccm、上部電極に印加するソースパワーを800W、下部電極に印加するバイアスパワーを100Wとして、n+ゲート電極膜34およびp+ゲート電極膜37の残渣を除去する。

【0047】

これにより、エッチング速度の小さいp+ゲート電極膜37は、サイドエッチングされることなく、ほぼ垂直にエッチングされる。その結果、所定のゲート長L2を有するp+ゲート電極23が得られる。

【0048】

一方、エッチング速度の大きいn+ゲート電極膜34は、サイドエッチングされながら、ほぼ垂直にエッチングされる。その結果、所定のゲート長L1を有するn+ゲート電極18が得られる。

【0049】

これにより、n+ゲート電極膜34とp+ゲート電極膜37とのエッチング速度の差によるゲート電極形状のばらつきが防止され、形状の揃ったn+ゲート電極18、p+ゲート電極23を得ることが可能である。

【0050】

図5は、燐およびホウ素が高濃度に注入されたポリシリコン膜のICP型RIE装置によるエッチング速度を示す図で、図中のaは燐が高濃度に注入されたポリシリコン膜、bはホウ素が高濃度に注入されたポリシリコン膜、cは比較としてアンドープポリシリコン膜の場合である。

【0051】

図5に示すように、実験によれば、燐が高濃度に注入されたポリシリコン膜aのエッチング速度はホウ素が高濃度に注入されたポリシリコン膜bより1.2倍程度大きな値が得られた。

【0052】

また、燐が高濃度に注入されたポリシリコン膜aのエッチング速度はアンドープポリシリコン膜cより大きく、ホウ素が高濃度に注入されたポリシリコン膜bのエッチング速度はアンドープポリシリコン膜cより小さくなる結果が得られた。

【0053】

更に、実験によれば、ポリシリコン膜中の燐の濃度が1E18cm−3を越えるあたりから、ポリシリコン膜のエッチング速度が大きくなる結果が得られた。

これから、n+ゲート電極膜34の表面から不純物濃度が略1E18cm−3になるまでの領域を上部とし、それより深い領域を下部と規定する。

【0054】

例えば、アンドープポリシリコン膜31に燐を加速電圧5keV、ドーズ量5E15cm−2程度イオン注入した場合に、ピーク不純物濃度が〜E21cm−3台、不純物濃度が1E18cm−3になる深さが30nm程度の注入プロファイルが得られるので、ここでは、表面から深さ30nmまでの領域を上部とし、深さ30nm以上の領域を下部としている。

【0055】

次に、周知のプロセスにより、p型ウェル領域13にソース領域20およびドレイン領域21を形成し、n型ウェル領域14にソース領域25およびドレイン領域26を形成する。

【0056】

次に、第1および第2ゲート電極18、23の下を除いたゲート絶縁膜17、22をそれぞれ除去し、第1および第2ゲート電極18、23、ソース領域20、25およびドレイン領域21、26上にニッケル(Ni)膜を、例えばスパッタリング法により形成し、熱処理することによりNiシリサイド層(図示せず)を形成する。

【0057】

これにより、n+ポリシリコン第1ゲート電極18とp+ポリシリコン第2ゲート電極23とのゲート電極形状のばらつきが防止され、特性の揃ったp−MOSトランジスタ15とn−MOSトランジスタ16を有するCMOS半導体装置10が得られる。

【0058】

以上説明したように、本実施例によれば、エッチング速度の大きいn+ゲート電極膜34上にゲート長L1より大きいゲート電極パターンサイズL4のシリコン窒化膜38aを形成し、エッチング速度の小さいp+ゲート電極膜37上にゲート長L2に略等しいゲート電極パターンサイズL5のシリコン窒化膜38bを形成している。

【0059】

その結果、n+ゲート電極膜34がサイドエッチングされ、ゲート電極パターンサイズL4より小さいゲート長L1を有する第1ゲート電極18が得られる。

p+ゲート電極膜37はサイドエッチングされることなく、ゲート電極パターンサイズL5に略等しいゲート長L2を有する第2ゲート電極23が得られる。

【0060】

従って、ゲート電極形状のばらつきが少なく、特性の揃ったp−MOSトランジスタ15とn−MOSトランジスタ16を有するCMOS半導体装置10を安定して製造することができる。

また、微細化によりチップサイズが小さく、集積度の高い半導体装置を提供することができる。

【0061】

ここでは、n+ゲート電極膜34またはp+ゲート電極膜37を、アンドープポリシリコン膜31にn型不純物またはp型不純物をイオン注入して形成した場合について説明したが、予めn型不純物またはp型不純物がドープされたドープドポリシリコン膜を各領域でパターン形成することで得たものであっても構わない。

【0062】

n+ゲート電極膜34およびp+ゲート電極膜37がポリシリコン膜である場合について説明したが、シリコン・ゲルマニウム化合物(SiGe)膜とすることもできる。

この場合、例えばゲート絶縁膜17、22上にSiH4ガスとGeH4ガスを用いたCVD法により、例えばGeの組成が20atm%程度の多結晶シリコン・ゲルマニウム(SiGe)化合物膜を形成する。

【0063】

シリコン・ゲルマニウム化合物は、キャリアの移動度がポリシリコンより大きいためゲート抵抗をより低減させることができるので、ゲート電極の空乏化の抑制が容易になり、p−MOSトランジスタおよびn−MOSトランジスタの特性が向上する利点がある。

【0064】

シリコン・ゲルマニウム化合物膜のゲルマニウムの組成は20atm%に限らず、所望の特性が得られる範囲で自由に設定することができる。

また、ゲート電極膜がシリコン・ゲルマニウム化合物膜に炭素(C)を添加したSiGeC膜であっても構わない。

【実施例2】

【0065】

図6は本発明の実施例2に係る半導体装置の製造工程の要部を、順に示す断面図である。本実施例において、上記実施例1と同一の構成部分には同一符号を付してその説明は省略し、異なる部分についてのみ説明する。

本実施例が実施例1と異なる点は、第1領域における第2保護膜にホウ素イオンを選択的に注入したことにある。

【0066】

即ち、図6(a)に示すように、n型ウェル領域14をレジスト膜44で被覆し、p型ウェル領域13にホウ素イオン(B+)を、例えば加速電圧1keV、ドーズ量5E15cm−2程度注入する。

これにより、p型ウェル領域13におけるアモルファスシリコン膜39aにのみホウ素(B)がドープされる。

次にアッシャーを用いて、レジスト膜44を灰化し、硫酸と過酸化水素の混合液(SH液)により、付着物を除去する。

【0067】

ここで、p型ウェル領域13およびn型ウェル領域14におけるアモルファスシリコン膜39a、39bのゲート電極パターンサイズL6を36nmに設定しておく。

【0068】

次に、図6(b)に示すように、n型ウェル領域14におけるホウ素(B)がドープされていないアモルファスシリコン膜39bを選択的にエッチングするエッチング液、例えば水酸化2−ヒドロキシエチルトリメチルアンモニウムを含む水溶液を用いて、p型ウェル領域13およびn型ウェル領域14におけるアモルファスシリコン膜39a、39bをウェットエッチングする。

【0069】

実験によれば、水酸化2−ヒドロキシエチルトリメチルアンモニウムを0.05wt%含む水溶液に対して、アンドープアモルファスシリコン膜39bのエッチング速度が6nm/min程度であるのに対して、Bがドープされたアモルファスシリコン膜39aのエッチング速度が0.03nm/min程度と、エッチング速度が約200倍異なることが判明している。

【0070】

従って、p型ウェル領域13およびn型ウェル領域14におけるアモルファスシリコン膜39a、39bを30sec程度エッチングすることにより、p型ウェル領域13におけるBがドープされたアモルファスシリコン膜39aはほとんどエッチングされない(エッチング量δ3〜0.015nm)ので、ゲート電極パターンサイズL4はエッチング前のゲート電極パターンサイズL6をほぼ維持することができる。

一方、n型ウェル領域14におけるアンドープアモルファスシリコン膜39bはエッチングされる(エッチング量δ4〜3nm)ので、ゲート電極パターンサイズL5はゲート電極パターンサイズL6より6nm程度細くなり、第2ゲート電極23のゲート長L2に略等しくすることができる。

【0071】

次に、p型ウェル領域13およびn型ウェル領域14におけるアモルファスシリコン膜39a、39bをマスクとして、ICP型RIE装置によりシリコン窒化膜38をエッチングする。

【0072】

次に、図4(d)と同様にしてp型ウェル領域13およびn型ウェル領域14におけるシリコン窒化膜38a、38bをマスクとして、ICP型RIE装置によりn+ゲート電極膜34およびp+ゲート電極膜37をエッチングする。

【0073】

これにより、エッチング速度の小さいp+ゲート電極膜37は、サイドエッチングされることなく、ほぼ垂直にエッチングされる。その結果、所定のゲート長L2を有するp+ゲート電極23が得られる。

【0074】

一方、エッチング速度の大きいn+ゲート電極膜34は、サイドエッチングされながら、ほぼ垂直にエッチングされる。その結果、所定のゲート長L1を有するn+ゲート電極18が得られる。

【0075】

これにより、n+ゲート電極膜34とp+ゲート電極膜37とのエッチング速度の差によるゲート電極形状のばらつきが防止され、形状の揃ったn+ゲート電極18、p+ゲート電極23を得ることが可能である。

【0076】

以上説明したように、本実施例の半導体装置の製造方法によれば、p型ウェル領域13におけるアモルファスシリコン膜39aにのみホウ素(B)をドープして、アモルファスシリコン膜39aのエッチング速度がアモルファスシリコン膜39bのエッチング速度より小さくなるようにしているので、熱酸化工程が不要になる利点がある。

【0077】

ここでは、Bがドープされていないアモルファスシリコン膜39bを選択的にエッチングするエッチング液として、水酸化2−ヒドロキシエチルトリメチルアンモニウムを含むエッチング液を用いる場合について説明したが、基本的にアルカリ性の薬液であれば、Bがドープされていないアモルファスシリコン膜39bとBがドープされているアモルファスシリコン膜39aとでエッチング速度が異なるので、目的のエッチング選択比が得られる範囲において使用することができる。

【図面の簡単な説明】

【0078】

【図1】本発明の実施例1に係る半導体装置を示す断面図。

【図2】本発明の実施例1に係る半導体装置の製造工程を示す断面図。

【図3】本発明の実施例1に係る半導体装置の製造工程を示す断面図。

【図4】本発明の実施例1に係る半導体装置の製造工程を示す断面図。

【図5】本発明の実施例1に係るポリシリコン膜のエッチング速度を示す図。

【図6】本発明の実施例2に係る半導体装置の製造工程の要部を示す断面図。

【符号の説明】

【0079】

10 半導体装置

11 n型シリコン基板

12 STI

13 p型ウェル領域(第1領域)

14 n型ウェル領域(第2領域)

15 n―MOSトランジスタ

16 p―MOSトランジスタ

17、22 ゲート絶縁膜

18 第1ゲート電極

20、25 ソース領域

21、26 ドレイン領域

23 第2ゲート電極

31 アンドープポリシリコン膜

32、35 開口

33、36、40、41、44 レジスト膜

34 n+ゲート電極膜

37 p+ゲート電極膜

38 シリコン窒化膜(第1保護膜)

39 アモルファスシリコン膜(第2保護膜)

42 第1酸化膜

43 第2酸化膜

【特許請求の範囲】

【請求項1】

半導体基板の主面の第1領域にゲート絶縁膜を介してn型ゲート電極膜を形成し、第2領域にゲート絶縁膜を介してp型ゲート電極膜を形成する工程と、

前記第1および第2領域における前記ゲート電極膜上に第1保護膜を形成し、前記第1保護膜上に前記第1保護膜と異なる第2保護膜を形成する工程と、

前記第1および第2領域における前記第2保護膜にゲート電極サイズより大きいサイズを有するゲート電極パターンを形成する工程と、

前記ゲート電極パターンを形成した後、前記第2領域における前記第2保護膜に選択的にイオンを注入し、前記第2領域における前記第2保護膜の熱酸化速度が前記第1領域における前記第2保護膜の熱酸化速度より大きくなるようにする工程と、

前記イオンを注入した後、前記第1および第2領域における前記第2保護膜を熱酸化し、生成した酸化膜を選択的にエッチングして、前記ゲート電極パターンをスリム化する工程と、

前記第1および第2領域におけるスリム化された前記ゲート電極パターンを有する前記第2保護膜をマスクとして、前記第1および第2領域における前記第1保護膜をエッチングする工程と、

前記第1および第2領域における前記第1保護膜をマスクとして、前記第1および第2領域における前記ゲート電極膜をエッチングしてゲート電極を形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項2】

半導体基板の主面の第1領域にゲート絶縁膜を介してn型ゲート電極膜を形成し、第2領域にゲート絶縁膜を介してp型ゲート電極膜を形成する工程と、

前記第1および第2領域における前記ゲート電極膜上に第1保護膜を形成し、前記第1保護膜上に前記第1保護膜と異なる第2保護膜を形成する工程と、

前記第1および第2領域における前記第2保護膜にゲート電極サイズより大きいサイズを有するゲート電極パターンを形成する工程と、

前記ゲート電極パターンを形成した後、前記第1領域における前記第2保護膜にイオンを選択的に注入し、前記第1領域における前記第2保護膜のエッチング速度が前記第2領域における前記第2保護膜のエッチング速度より小さくなるようにする工程と、

前記イオンを注入した後、前記第1および第2領域における前記第2保護膜を所定時間エッチングして、前記ゲート電極パターンをスリム化する工程と、

前記第1および第2領域におけるスリム化された前記ゲート電極パターンを有する前記第2保護膜をマスクとして、前記第1および第2領域における前記第1保護膜をエッチングする工程と、

前記第1および第2領域における前記第1保護膜をマスクとして、前記第1および第2領域における前記ゲート電極膜をエッチングしてゲート電極を形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項3】

前期第1保護膜がシリコン窒化膜であり、前記第2保護膜がシリコン膜であることを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1領域における前記スリム化されたゲート電極パターンサイズが前記ゲート電極サイズより大きく、且つ前記第2領域における前記スリム化されたゲート電極パターンサイズが前記ゲート電極サイズに略等しいことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項5】

前記第2保護膜のエッチングが、アルカリ性の薬液を用いたウェットエッチングであることを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項1】

半導体基板の主面の第1領域にゲート絶縁膜を介してn型ゲート電極膜を形成し、第2領域にゲート絶縁膜を介してp型ゲート電極膜を形成する工程と、

前記第1および第2領域における前記ゲート電極膜上に第1保護膜を形成し、前記第1保護膜上に前記第1保護膜と異なる第2保護膜を形成する工程と、

前記第1および第2領域における前記第2保護膜にゲート電極サイズより大きいサイズを有するゲート電極パターンを形成する工程と、

前記ゲート電極パターンを形成した後、前記第2領域における前記第2保護膜に選択的にイオンを注入し、前記第2領域における前記第2保護膜の熱酸化速度が前記第1領域における前記第2保護膜の熱酸化速度より大きくなるようにする工程と、

前記イオンを注入した後、前記第1および第2領域における前記第2保護膜を熱酸化し、生成した酸化膜を選択的にエッチングして、前記ゲート電極パターンをスリム化する工程と、

前記第1および第2領域におけるスリム化された前記ゲート電極パターンを有する前記第2保護膜をマスクとして、前記第1および第2領域における前記第1保護膜をエッチングする工程と、

前記第1および第2領域における前記第1保護膜をマスクとして、前記第1および第2領域における前記ゲート電極膜をエッチングしてゲート電極を形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項2】

半導体基板の主面の第1領域にゲート絶縁膜を介してn型ゲート電極膜を形成し、第2領域にゲート絶縁膜を介してp型ゲート電極膜を形成する工程と、

前記第1および第2領域における前記ゲート電極膜上に第1保護膜を形成し、前記第1保護膜上に前記第1保護膜と異なる第2保護膜を形成する工程と、

前記第1および第2領域における前記第2保護膜にゲート電極サイズより大きいサイズを有するゲート電極パターンを形成する工程と、

前記ゲート電極パターンを形成した後、前記第1領域における前記第2保護膜にイオンを選択的に注入し、前記第1領域における前記第2保護膜のエッチング速度が前記第2領域における前記第2保護膜のエッチング速度より小さくなるようにする工程と、

前記イオンを注入した後、前記第1および第2領域における前記第2保護膜を所定時間エッチングして、前記ゲート電極パターンをスリム化する工程と、

前記第1および第2領域におけるスリム化された前記ゲート電極パターンを有する前記第2保護膜をマスクとして、前記第1および第2領域における前記第1保護膜をエッチングする工程と、

前記第1および第2領域における前記第1保護膜をマスクとして、前記第1および第2領域における前記ゲート電極膜をエッチングしてゲート電極を形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項3】

前期第1保護膜がシリコン窒化膜であり、前記第2保護膜がシリコン膜であることを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1領域における前記スリム化されたゲート電極パターンサイズが前記ゲート電極サイズより大きく、且つ前記第2領域における前記スリム化されたゲート電極パターンサイズが前記ゲート電極サイズに略等しいことを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項5】

前記第2保護膜のエッチングが、アルカリ性の薬液を用いたウェットエッチングであることを特徴とする請求項2に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2008−181957(P2008−181957A)

【公開日】平成20年8月7日(2008.8.7)

【国際特許分類】

【出願番号】特願2007−12699(P2007−12699)

【出願日】平成19年1月23日(2007.1.23)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成20年8月7日(2008.8.7)

【国際特許分類】

【出願日】平成19年1月23日(2007.1.23)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]