半導体装置の製造方法

【課題】ゲート長に依存する仕事関数の変動を抑えることができる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜14上の多結晶シリコン膜を露出した後、半導体基板11を400℃まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜21を全面に形成する。ニッケル膜21の厚さは、シリコン酸化膜20上で60nmとする。この結果、シリコン酸化膜20上にはニッケル膜21が形成されるが、多結晶シリコン膜の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜と反応し、多結晶シリコン膜の全体がニッケルシリサイド膜22に変化する。従って、pMOS領域1には、p型不純物を含有するニッケルシリサイド膜22からなるゲート電極が形成され、nMOS領域2には、n型不純物を含有するニッケルシリサイド膜22からなるゲート電極が形成される。

【解決手段】ゲート絶縁膜14上の多結晶シリコン膜を露出した後、半導体基板11を400℃まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜21を全面に形成する。ニッケル膜21の厚さは、シリコン酸化膜20上で60nmとする。この結果、シリコン酸化膜20上にはニッケル膜21が形成されるが、多結晶シリコン膜の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜と反応し、多結晶シリコン膜の全体がニッケルシリサイド膜22に変化する。従って、pMOS領域1には、p型不純物を含有するニッケルシリサイド膜22からなるゲート電極が形成され、nMOS領域2には、n型不純物を含有するニッケルシリサイド膜22からなるゲート電極が形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ゲート電極の低抵抗化を図った半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、MOSトランジスタを備えた半導体装置においては、微細化が進むにつれて、多結晶シリコン膜からなるゲート電極の高抵抗化及び空乏層の発生に伴う駆動電流の低下が懸念されている。これらの課題を解決するために、ゲート電極を金属膜から形成する試みがなされている。しかしながら、金属膜からゲート電極を形成するためには、金属膜をドライエッチングする必要があり、この際に、金属が絶縁膜上等に飛散して残留することがある。この結果、多結晶シリコンでは問題とならないような飛散及び残留であっても、金属の場合には重大な欠陥に繋がることがある。従って、単にゲート電極の材料を変更するだけでは、所望の特性の半導体装置を得ることは困難である。

【0003】

また、ゲート電極を構成する多結晶シリコン膜の表面をシリサイド化する技術も開発されている。この技術によれば、多結晶シリコン膜のみからなるゲート電極と比較すると、低抵抗のゲート電極が得られる。また、金属膜をドライエッチングする必要もないため、上述のような問題は生じにくい。

【0004】

しかしながら、このようなシリサイド化の技術によっても、近時のゲート長の短縮化に伴うゲート電極の高抵抗化の抑制には対応しきれなくなってきている。つまり、十分に低い抵抗のゲート電極を得ることが困難になってきている。そこで、ゲート電極の全体をシリサイド化する技術が提案されている(特許文献1及び非特許文献1)。この技術は、フルシリサイデーション化技術ともよばれる。この技術によれば、ゲート電極の抵抗をより低下させることができる。また、多結晶シリコン膜内に生成する可能性のある空乏層の発生を防止することができ、トランジスタ特性が向上する。

【0005】

ニッケルシリサイドからなるゲート電極を形成する際には、ゲート電極の形状の多結晶シリコン膜、サイドウォール絶縁膜及び不純物拡散層等を形成した後に、多結晶シリコン膜上にニッケル膜を室温で形成する。そして、400℃に加熱することにより、シリコンとニッケルとを反応させて、多結晶シリコン膜をニッケルシリサイド膜に変化させる。従来、このような方法により、全体がシリサイド化したゲート電極が得られている。

【0006】

しかしながら、非特許文献2に記載されているように、ゲート長に応じて多結晶シリコン膜に入り込んでくる単位体積当たりのニッケルの量が異なるため、ニッケルシリサイド中のニッケルとシリコンとの比率がゲート長に応じて変化してしまう。つまり、図6A及び図6Bに示すように、シリコン基板101の上方の多結晶シリコン膜102上には、その上に形成されたニッケル膜103からニッケルが供給されるが、この際に、ニッケルは多結晶シリコン膜102の直上だけでなく、その側方からも供給される。但し、側方からのニッケルの供給量は、ゲート長に拘わらず一定である。このため、ゲート長が短いMOSトランジスタ(図6A)と長いMOSトランジスタ(図6B)との間で、多結晶シリコン膜102の上面の単位面積当たりの側方からの供給量を比較すると、ゲート長が短いMOSトランジスタへの供給量が多くなる。この結果、ゲート長に応じてゲート電極の仕事関数が変動してしまい、MOSトランジスタの動作電圧も変動してしまう。

【0007】

【特許文献1】特開2005−129551号公報

【特許文献2】特開平8−255769号公報

【特許文献3】特開平9−69497号公報

【特許文献4】特開2005−243664号公報

【特許文献5】特開2005−252192号公報

【非特許文献1】J Kedzierski et.al IEDM2002 p.247

【非特許文献2】Kittl et al., EDL pp. 966 vol.27 (2006)

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明の目的は、ゲート長に依存する仕事関数の変動を抑えることができる半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0009】

本願発明者は、上記課題を解決すべく、鋭意検討を重ねた結果、以下に示す発明の諸態様に想到した。

【0010】

半導体装置の製造方法の一態様では、半導体基板上にゲート絶縁膜を形成し、その後、前記ゲート絶縁膜上に半導体膜を形成する。次いで、前記半導体膜を所定の温度に加熱する。そして、前記半導体膜が前記所定の温度に達している状態で、前記所定の温度下で前記半導体膜を構成する半導体と反応して金属半導体化合物を生成する金属を前記半導体膜上に供給することにより、前記半導体膜を金属半導体化合物膜に変化させる。

【発明の効果】

【0011】

上記の半導体装置の製造方法によれば、金属半導体化合物膜を適切に形成しているため、そのサイズに拘わらずその組成を安定したものとすることができる。従って、これをゲート電極に用いれば、仕事関数の変動を抑制することができる。

【発明を実施するための最良の形態】

【0012】

(基本的原理)

本方法では、半導体膜としてシリコン(Si)膜を用いる場合、シリコン膜のシリサイド化に際して、従来のようにニッケル膜等の原料膜を形成した後に加熱するのではなく、シリサイド反応が生じる温度にシリコン膜を加熱しておき、この状態でニッケル等の金属原料の供給を行うこととする。

【0013】

ここで、このような相違点に関して、本願発明者らが行った実験について説明する。

【0014】

先ず、従来の方法を反映した方法により試料を作製した。この方法では、基板上にゲート絶縁膜に相当するSiO2膜(厚さ:10nm)を形成し、その上に多結晶シリコン膜(厚さ:100nm)を形成した。次いで、原料膜となるニッケル(Ni)膜(厚さ:60nm)を多結晶シリコン膜上に室温で形成した。その後、基板を400℃まで加熱し、120秒間の熱処理を行うことにより、多結晶シリコン膜からニッケルシリサイド膜を得た。そして、ニッケルシリサイド膜のX線分析を行った。この結果を図7Aに示す。

【0015】

その一方で、本発明を反映させた方法により試料を作製した。この方法では、基板上にゲート絶縁膜に相当するSiO2膜(厚さ:10nm)を形成し、その上に多結晶シリコン膜(厚さ:100nm)を形成した。次いで、基板を400℃まで加熱し、その温度が安定してからニッケル膜(厚さ:60nm)を多結晶シリコン膜上に形成した。この際に、多結晶シリコン膜からニッケルシリサイド膜が得られた。そして、ニッケルシリサイド膜のX線分析を行った。この結果を図7Bに示す。

【0016】

400℃という温度はNiSiの生成に適した温度といわれているが、図7Aに示すように、従来の方法を反映した方法では、NiSiだけでなく、Ni2Siも検出された。つまり、NiSi(112)、NiSi(211)及びNi2Si(002)のピークが現れた。これは、この方法ではニッケル膜からニッケルが過剰に供給されたことを示している。一方、図7Bに示すように、本発明を反映させた方法によれば、NiSiのみが検出され、Ni2Siは検出されなかった。つまり、NiSi(112)及びNiSi(211)のピークが現れ、Ni2Si(002)のピークは現れなかった。これは、この方法によれば所望の組成のニッケルシリサイドが得られたことを示している。

【0017】

そこで、本発明では、全体がシリサイド化したゲート電極の形成に当たり、シリコン膜を形成した後に、これを所望のシリサイド相反応が生じる温度まで加熱しておき、この状態で金属原料の供給を行うこととしているのである。

【0018】

(第1の実施形態)

次に、第1の実施形態について説明する。図1A乃至図1Kは、第1の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【0019】

先ず、図1Aに示すように、pMOS領域1及びnMOS領域2を画定する素子分離絶縁膜2をSTI(Shallow Trench Isolation)法等によりシリコン基板等の半導体基板11の表面に形成する。pMOS領域1は、pチャネルMOSトランジスタを形成する予定の領域であり、nMOS領域2は、nチャネルMOSトランジスタを形成する予定の領域である。次いで、pMOS領域1にn型不純物をイオン注入し、nMOS領域2にp型不純物をイオン注入し、熱処理を行うことにより、これらの不純物を活性化させる。この結果、pMOS領域1にnウェル13nが形成され、nMOS領域2にpウェル13pが形成される。

【0020】

次いで、図1Bに示すように、半導体基板11上に、ゲート絶縁膜14、多結晶シリコン膜15及びシリコン窒化膜16を順次形成する。ゲート絶縁膜14としては、厚さが2nm程度のシリコン酸化膜を形成する。多結晶シリコン膜15は、例えば原料ガスとしてSiH4ガスを用いたCVD(Chemical Vapor Deposition)法により580℃で形成する。多結晶シリコン膜15の厚さは、100nm程度とする。シリコン窒化膜16は、例えば原料ガスとしてNH3及びSiH4の混合ガスを用いたCVD法により形成する。シリコン窒化膜16の厚さは、10nm程度とする。

【0021】

その後、図1Cに示すように、ドライエッチングにより、シリコン窒化膜16、多結晶シリコン膜15及びゲート絶縁膜14をゲート電極の平面形状に加工する。

【0022】

続いて、nMOS領域2を覆うフォトレジスト膜(図示せず)を形成し、このフォトレジスト膜及びpMOS領域1内の多結晶シリコン膜15をマスクとして、nウェル13nに不純物イオンを注入する。このイオン注入では、例えば、加速エネルギを10keV程度、ドーズ量を2×1013cm-2程度として、ホウ素(B)を注入し、更に、加速エネルギを4keV程度、ドーズ量を1×1015cm-2程度として、砒素(As)を注入する。この結果、図1Dに示すように、p型不純物拡散層17pが形成され、その近傍にn型不純物拡散層が形成される。なお、図1Dでは、このn型不純物拡散層を省略している。

【0023】

次いで、nMOS領域2を覆うフォトレジスト膜を灰化処理等により除去し、pMOS領域1を覆うフォトレジスト膜(図示せず)を形成し、このフォトレジスト膜及びnMOS領域2内の多結晶シリコン膜15をマスクとして、pウェル13pに不純物イオンを注入する。このイオン注入では、例えば、加速エネルギを80keV程度、ドーズ量を2×1013cm-2程度として、砒素(As)を注入し、更に、加速エネルギを1keV程度、ドーズ量を1×1015cm-2程度として、ホウ素(B)を注入する。この結果、図1Dに示すように、n型不純物拡散層17nが形成され、その近傍にp型不純物拡散層が形成される。なお、図1Dでは、このp型不純物拡散層を省略している。

【0024】

その後、pMOS領域1を覆うフォトレジスト膜を灰化処理等により除去する。続いて、シリコン酸化膜等の絶縁膜を全面に形成し、これを全面異方性エッチングすることにより、多結晶シリコン膜15の側方にサイドウォール絶縁膜18を形成する。

【0025】

次いで、上記のようなフォトレジスト膜の形成及び除去を行いながら、図1Eに示すように、p型不純物拡散層17pよりも深いp型不純物拡散層19pをnウェル13nに形成し、n型不純物拡散層17nよりも深いn型不純物拡散層19nをpウェル13pに形成する。そして、1000℃程度での熱処理を行うことにより、各不純物拡散層中の不純物を活性化させる。なお、p型不純物拡散層19pの形成に当たっては、加速エネルギを5keV程度とし、ドーズ量を5×1015cm-2程度としてホウ素(B)を注入する。また、n型不純物拡散層19nの形成に当たっては、加速エネルギを20keV程度とし、ドーズ量を7×1015cm-2程度としてリン(P)を注入する。更に、このイオン注入では、イオンが多結晶シリコン膜15にも導入される。

【0026】

その後、図1Fに示すように、多結晶シリコン膜15間の隙間を埋め込むシリコン酸化膜20を全面に形成する。

【0027】

続いて、図1Gに示すように、CMP(Chemical Mechanical Polishing)等により、シリコン窒化膜16が露出するまでシリコン酸化膜20を研磨する。つまり、平坦化処理を行う。

【0028】

次いで、図1Hに示すように、シリコン窒化膜16を除去することにより、多結晶シリコン膜15を露出する。シリコン窒化膜16の除去に当たっては、150℃程度の熱リン酸を用いたウェット処理を行う。この場合のシリコン窒化膜16のシリコン酸化膜20に対する選択比は3〜4倍程度である。

【0029】

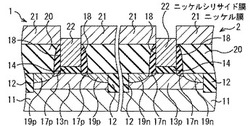

その後、半導体基板11を400℃まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜21を全面に形成する。ニッケル膜21の厚さは、シリコン酸化膜20上で60nmとする。この結果、シリコン酸化膜20上にはニッケル膜21が形成されるが、多結晶シリコン膜15の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜15と反応し、多結晶シリコン膜15の全体がニッケルシリサイド膜22に変化する。従って、pMOS領域1には、ホウ素(B)を含有するニッケルシリサイド膜22からなるゲート電極が形成され、nMOS領域2には、リン(P)を含有するニッケルシリサイド膜22からなるゲート電極が形成される。なお、多結晶シリコン膜15からニッケルシリサイド膜22への変化に伴って、その厚さは30nm程度増加する。

【0030】

続いて、図1Jに示すように、ニッケル膜21を除去する。そして、図1Kに示すように、全面に層間絶縁膜23を形成する。層間絶縁膜23としては、例えばシリコン酸化膜を形成する。次いで、層間絶縁膜23及びシリコン酸化膜20に不純物拡散層19n及び19pまで到達するコンタクトホールを形成し、その中にコンタクトプラグ24を形成する。その後、コンタクトプラグ24に接続される配線25を形成する。図示しないが、層間絶縁膜23にはニッケルシリサイド膜22まで到達するコンタクトホールも形成し、その中にもコンタクトプラグを形成する。更に、このコンタクトプラグに接する配線も形成する。

【0031】

その後、更に上層の層間絶縁膜及び配線等を形成して、CMOSトランジスタを備えた半導体装置を完成させる。

【0032】

このような第1の実施形態によれば、ニッケルシリサイド膜22の形成に際して、多結晶シリコン膜15を加熱した状態でニッケルの供給を行っているので、ニッケルシリサイド膜22の組成を確実にNiSiとすることができる。従って、ゲート長が相違する複数のMOSトランジスタが形成される場合であっても、ゲート長の相違に起因する動作電圧の変動を抑えることができる。

【0033】

また、pチャネルMOSトランジスタとnチャネルMOSトランジスタとの間では、ゲート電極に含有される不純物を相違させているので、夫々に適した仕事関数を得ることができる。

【0034】

(第2の実施形態)

次に、第2の実施形態について説明する。図2A乃至図2Fは、第2の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【0035】

先ず、第1の実施形態と同様にして、シリコン酸化膜20の研磨(図1G)までの処理を行う。次いで、図2Aに示すように、nMOS領域2を覆うフォトレジスト膜31をシリコン酸化膜20等の上に形成する。

【0036】

その後、図2Bに示すように、pMOS領域1内において、シリコン窒化膜16を除去することにより、多結晶シリコン膜15を露出する。

【0037】

続いて、図2Cに示すように、フォトレジスト膜31を灰化処理等により除去する。次いで、半導体基板11を420℃〜600℃程度まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜32を全面に形成する。ニッケル膜32の厚さは、シリコン酸化膜20上で120nmとする。この結果、シリコン酸化膜20上にはニッケル膜32が形成されるが、pMOS領域1内の多結晶シリコン膜15の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜15と反応し、多結晶シリコン膜15の全体がニッケルシリサイド膜33に変化する。従って、pMOS領域1に、ホウ素(B)を含有するニッケルシリサイド膜33からなるゲート電極が形成される。なお、このような条件で形成されたニッケルシリサイド膜33の組成はNi2Siとなる。

【0038】

次いで、図2Dに示すように、ニッケル膜32を除去する。

【0039】

その後、図2Eに示すように、pMOS領域1を覆うフォトレジスト膜34をシリコン酸化膜20等の上に形成する。

【0040】

続いて、図2Fに示すように、nMOS領域2内において、シリコン窒化膜16を除去することにより、多結晶シリコン膜15を露出する。

【0041】

次いで、図2Gに示すように、フォトレジスト膜34を灰化処理等により除去する。その後、半導体基板11をニッケル膜32の形成時よりも低い温度、例えば400℃程度まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜35を全面に形成する。ニッケル膜35の厚さは、シリコン酸化膜20上で60nmとする。この結果、シリコン酸化膜20上にはニッケル膜35が形成されるが、nMOS領域2内の多結晶シリコン膜15の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜15と反応し、多結晶シリコン膜15の全体がニッケルシリサイド膜36に変化する。従って、nMOS領域2に、リン(P)を含有するニッケルシリサイド膜36からなるゲート電極が形成される。なお、このような条件で形成されたニッケルシリサイド膜36の組成はNiSiとなる。

【0042】

次いで、図2Hに示すように、ニッケル膜35を除去する。

【0043】

その後、第1の実施形態と同様にして、層間絶縁膜23の形成(図1K)以降の処理を行う。

【0044】

このような第2の実施形態によっても第1の実施形態と同様の効果が得られる。また、pチャネルMOSトランジスタとnチャネルMOSトランジスタとの間で、ゲート電極の組成を意図的に相違させているので、仕事関数を所望のものとすることがより一層容易になる。

【0045】

なお、pMOS領域1にNiSiからなるゲート電極を形成し、nMOS領域2にNi2Siからなるゲート電極を形成することも可能であるが、この場合にも、より高温への加熱が必要とされる処理を先に行うことが好ましい。つまり、Ni2Siからなるゲート電極を形成した後に、NiSiからなるゲート電極を形成することが好ましい。この順序を逆にすると、Ni2Siからなるゲート電極を形成する際に、NiSiがNi2Siに変化する虞があるからである。

【0046】

また、ニッケルシリサイドのNi量を増やすことも可能である。この場合には、ニッケル膜の形成時の温度を高くしたり、時間を長くしたりすればよい。

【0047】

(第3の実施形態)

次に、第3の実施形態について説明する。図3A乃至図3Gは、第3の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【0048】

先ず、第1の実施形態と同様にして、ゲート絶縁膜14の形成(図1B)までの処理を行う。次いで、図3Aに示すように、nMOS領域2を覆うフォトレジスト膜41をゲート絶縁膜14の上に形成する。

【0049】

その後、図3Bに示すように、pMOS領域1内において、ゲート絶縁膜14上に、閾値制御膜として、厚さが10nm程度の窒化ハフニウム膜42を形成する。

【0050】

続いて、図3Cに示すように、フォトレジスト膜41を灰化処理等により除去する。次いで、pMOS領域1を覆うフォトレジスト膜43を窒化ハフニウム膜42の上に形成する。

【0051】

その後、図3Dに示すように、nMOS領域2内において、ゲート絶縁膜14上に、閾値制御膜として、厚さが10nm程度の炭化ハフニウム膜44を形成する。

【0052】

続いて、図3Eに示すように、フォトレジスト膜43を灰化処理等により除去する。次いで、図1Bに示すように、窒化ハフニウム膜42及び炭化ハフニウム膜44上に、多結晶シリコン膜15及びシリコン窒化膜16を順次形成する。このとき、多結晶シリコン膜15の厚さは、90nm程度とする。つまり、第1の実施形態と比較すると、窒化ハフニウム膜42及び炭化ハフニウム膜44の分だけ薄くする。

【0053】

その後、図3Fに示すように、ドライエッチングにより、シリコン窒化膜16、多結晶シリコン膜15、窒化ハフニウム膜42、炭化ハフニウム膜44及びゲート絶縁膜14をゲート電極の平面形状に加工する。

【0054】

続いて、図3Gに示すように、第1の実施形態と同様にして、不純物拡散層17p及び17nの形成(図1D)から配線25の形成までの処理を行い、更に上層の層間絶縁膜及び配線等を形成して、CMOSトランジスタを備えた半導体装置を完成させる。

【0055】

このような第3の実施形態によっても第1の実施形態と同様の効果が得られる。また、pチャネルMOSトランジスタ及びnチャネルMOSトランジスタに、互いに異なる材料からなる閾値制御膜(窒化ハフニウム膜42及び炭化ハフニウム膜44)を設けているので、仕事関数を所望のものとすることがより一層容易になる。

【0056】

なお、第3の実施形態を第2の実施形態に組み合わせてもよい。

【0057】

(第4の実施形態)

次に、第4の実施形態について説明する。図4A乃至図4Cは、第4の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【0058】

先ず、第3の実施形態と同様にして、窒化ハフニウム膜42及び炭化ハフニウム膜44の形成並びにフォトレジスト膜43の除去(図3E)までの処理を行う。次いで、図4Aに示すように、第3の実施形態よりも薄い多結晶シリコン膜15、及び第3の実施形態よりも厚いシリコン窒化膜16を窒化ハフニウム膜42及び炭化ハフニウム膜44上に順次形成する。

【0059】

その後、図4Bに示すように、ドライエッチングにより、シリコン窒化膜16、多結晶シリコン膜15、窒化ハフニウム膜42、炭化ハフニウム膜44及びゲート絶縁膜14をゲート電極の平面形状に加工する。

【0060】

続いて、図4Cに示すように、第1の実施形態と同様にして、不純物拡散層17p及び17nの形成(図1D)から配線25の形成までの処理を行い、更に上層の層間絶縁膜及び配線等を形成して、CMOSトランジスタを備えた半導体装置を完成させる。

【0061】

このような第4の実施形態によっても第3の実施形態と同様の効果が得られる。第3の実施形態では、ニッケルシリサイド膜22に不純物が含有されているため、この不純物が窒化ハフニウム膜42及び炭化ハフニウム膜44との界面近傍に偏析する虞がある。これに対し、第4の実施形態では、シリコン窒化膜16を厚くしているので、不純物拡散層19p及び19nの形成時にニッケルシリサイド膜22へ不純物が導入されにくく、このような偏析を回避することができる。

【0062】

なお、第4の実施形態を閾値制御膜(窒化ハフニウム膜42及び炭化ハフニウム膜44)が存在しない第1の実施形態及び第2の実施形態に組み合わせてもよい。このような組み合わせにより得られる方法は、ニッケルシリサイド膜22への不純物の導入を回避した方がよい場合に有効である。

【0063】

(第5の実施形態)

次に、第5の実施形態について説明する。図5A乃至図5Cは、第5の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【0064】

先ず、第1の実施形態と同様にして、シリコン窒化膜16の除去(図1H)までの処理を行う。次いで、図5Aに示すように、多結晶シリコン膜15を除去する。

【0065】

その後、図5Bに示すように、pMOS領域1内のゲート絶縁膜14上に窒化ハフニウム膜42を形成し、nMOS領域2内のゲート絶縁膜14上に炭化ハフニウム膜44を形成する。なお、多結晶シリコン膜15の除去の際にゲート絶縁膜14も除去されてしまった場合には、窒化ハフニウム膜42及び炭化ハフニウム膜44の形成の前にゲート絶縁膜14を形成し直せばよい。

【0066】

続いて、図5Cに示すように、窒化ハフニウム膜42上及び炭化ハフニウム膜44上に多結晶シリコン膜51を形成する。多結晶シリコン膜51の厚さは、第3の実施形態と同様に、90nm程度とする。

【0067】

そして、第1の実施形態と同様にして、ニッケル膜21の形成(図1I)以降の処理を行う。

【0068】

このような第5の実施形態によっても第3の実施形態と同様の効果が得られる。また、閾値制御膜(窒化ハフニウム膜42上及び炭化ハフニウム膜44)の形成を不純物拡散層中の不純物の活性化のための熱処理の後に行っているので、閾値制御膜として、比較的融点が低い金属からなる膜を用いることも可能である。

【0069】

なお、第5の実施形態を第4の実施形態に組み合わせてもよい。

【0070】

このように、これらの実施形態によれば、ニッケルシリサイド膜の形成に際して、多結晶シリコン膜を加熱した状態でニッケルの供給を行っているので、所望のニッケルシリサイド膜の組成を確実にNiSiとすることができる。従って、ゲート長が相違する複数のMOSトランジスタが形成される場合であっても、ゲート長の相違に起因する動作電圧の変動を抑えることができる。

【0071】

また、必要に応じて、ニッケルシリサイド膜の組成を調整したり、閾値制御膜を形成したり、不純物の導入を調整したりすることにより、ゲート電極の仕事関数を広い範囲内から選択することができる。

【0072】

なお、シリサイドの原料はニッケルに限定されず、例えば、コバルト(Co)、チタン(Ti)、タングステン(W)、モリブデン(Mo)、白金(Pt)又はハフニウム(Hf)を用いてもよい。

【0073】

また、シリコン窒化膜16の代わりにシリコン酸化膜を用いてもよく、シリコン酸化膜20の代わりにシリコン窒化膜を用いてもよい。他の絶縁膜等についてもその材料は特に限定されない。

【0074】

また、ゲート電極に含まれる不純物はホウ素及びリンに限定されず、n型の置換型不純物として砒素(As)及び/又はアンチモン(Sb)を用いてもよく、p型の置換型不純物としてガリウム(Ga)及び/又はインジウム(In)を用いてもよい。このような置換型不純物は、上述の実施形態のように、不純物拡散層の形成の際に導入されてもよく、多結晶シリコン膜の形成時に導入されてもよい。

【0075】

また、閾値制御膜の材料としては、ハフニウム(Hf)、白金、タングステン又はルテニウム(Ru)も挙げられる。また、これらの窒化物又は炭化物を用いてもよい。

【0076】

また、半導体として、シリコン以外に、ゲルマニウム(Ge)、SiGe又はSiC等を用いてもよい。これらの半導体を用いた場合、金属半導体化合物として、ゲリサイド又はシリサイドが得られる。

【0077】

なお、特許文献1には、ゲート電極の仕事関数を制御し易くするための技術が記載されているが、この技術によっても、上記の実施形態と比較すると、得られる仕事関数の範囲は限られており、ゲート電極の閾電圧の範囲も限定されている。

【図面の簡単な説明】

【0078】

【図1A】第1の実施形態に係る半導体装置の製造方法を示す断面図である。

【図1B】図1Aに引き続き、半導体装置の製造方法を示す断面図である。

【図1C】図1Bに引き続き、半導体装置の製造方法を示す断面図である。

【図1D】図1Cに引き続き、半導体装置の製造方法を示す断面図である。

【図1E】図1Dに引き続き、半導体装置の製造方法を示す断面図である。

【図1F】図1Eに引き続き、半導体装置の製造方法を示す断面図である。

【図1G】図1Fに引き続き、半導体装置の製造方法を示す断面図である。

【図1H】図1Gに引き続き、半導体装置の製造方法を示す断面図である。

【図1I】図1Hに引き続き、半導体装置の製造方法を示す断面図である。

【図1J】図1Iに引き続き、半導体装置の製造方法を示す断面図である。

【図1K】図1Jに引き続き、半導体装置の製造方法を示す断面図である。

【図2A】第2の実施形態に係る半導体装置の製造方法を示す断面図である。

【図2B】図2Aに引き続き、半導体装置の製造方法を示す断面図である。

【図2C】図2Bに引き続き、半導体装置の製造方法を示す断面図である。

【図2D】図2Cに引き続き、半導体装置の製造方法を示す断面図である。

【図2E】図2Dに引き続き、半導体装置の製造方法を示す断面図である。

【図2F】図2Eに引き続き、半導体装置の製造方法を示す断面図である。

【図2G】図2Fに引き続き、半導体装置の製造方法を示す断面図である。

【図2H】図2に引き続き、半導体装置の製造方法を示す断面図である。

【図3A】第3の実施形態に係る半導体装置の製造方法を示す断面図である。

【図3B】図3Aに引き続き、半導体装置の製造方法を示す断面図である。

【図3C】図3Bに引き続き、半導体装置の製造方法を示す断面図である。

【図3D】図3Cに引き続き、半導体装置の製造方法を示す断面図である。

【図3E】図3Dに引き続き、半導体装置の製造方法を示す断面図である。

【図3F】図3Eに引き続き、半導体装置の製造方法を示す断面図である。

【図3G】図3Fに引き続き、半導体装置の製造方法を示す断面図である。

【図4A】第4の実施形態に係る半導体装置の製造方法を示す断面図である。

【図4B】図4Aに引き続き、半導体装置の製造方法を示す断面図である。

【図4C】図4Bに引き続き、半導体装置の製造方法を示す断面図である。

【図5A】第5の実施形態に係る半導体装置の製造方法を示す断面図である。

【図5B】図5Aに引き続き、半導体装置の製造方法を示す断面図である。

【図5C】図5Bに引き続き、半導体装置の製造方法を示す断面図である。

【図6A】ゲート長が短いMOSトランジスタにおけるNiの拡散を示す模式図である。

【図6B】ゲート長が長いMOSトランジスタにおけるNiの拡散を示す模式図である。

【図7A】従来の方法を反映した方法により作製した試料のX線分析の結果を示す図である。

【図7B】本発明を反映した方法により作製した試料のX線分析の結果を示す図である。

【符号の説明】

【0079】

1:pMOS領域

2:nMOS領域

11:半導体基板

14:ゲート絶縁膜

15、51:多結晶シリコン膜

21、32、35:ニッケル膜

22、33、36:ニッケルシリサイド膜

42:窒化ハフニウム膜

44:炭化ハフニウム膜

【技術分野】

【0001】

本発明は、ゲート電極の低抵抗化を図った半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、MOSトランジスタを備えた半導体装置においては、微細化が進むにつれて、多結晶シリコン膜からなるゲート電極の高抵抗化及び空乏層の発生に伴う駆動電流の低下が懸念されている。これらの課題を解決するために、ゲート電極を金属膜から形成する試みがなされている。しかしながら、金属膜からゲート電極を形成するためには、金属膜をドライエッチングする必要があり、この際に、金属が絶縁膜上等に飛散して残留することがある。この結果、多結晶シリコンでは問題とならないような飛散及び残留であっても、金属の場合には重大な欠陥に繋がることがある。従って、単にゲート電極の材料を変更するだけでは、所望の特性の半導体装置を得ることは困難である。

【0003】

また、ゲート電極を構成する多結晶シリコン膜の表面をシリサイド化する技術も開発されている。この技術によれば、多結晶シリコン膜のみからなるゲート電極と比較すると、低抵抗のゲート電極が得られる。また、金属膜をドライエッチングする必要もないため、上述のような問題は生じにくい。

【0004】

しかしながら、このようなシリサイド化の技術によっても、近時のゲート長の短縮化に伴うゲート電極の高抵抗化の抑制には対応しきれなくなってきている。つまり、十分に低い抵抗のゲート電極を得ることが困難になってきている。そこで、ゲート電極の全体をシリサイド化する技術が提案されている(特許文献1及び非特許文献1)。この技術は、フルシリサイデーション化技術ともよばれる。この技術によれば、ゲート電極の抵抗をより低下させることができる。また、多結晶シリコン膜内に生成する可能性のある空乏層の発生を防止することができ、トランジスタ特性が向上する。

【0005】

ニッケルシリサイドからなるゲート電極を形成する際には、ゲート電極の形状の多結晶シリコン膜、サイドウォール絶縁膜及び不純物拡散層等を形成した後に、多結晶シリコン膜上にニッケル膜を室温で形成する。そして、400℃に加熱することにより、シリコンとニッケルとを反応させて、多結晶シリコン膜をニッケルシリサイド膜に変化させる。従来、このような方法により、全体がシリサイド化したゲート電極が得られている。

【0006】

しかしながら、非特許文献2に記載されているように、ゲート長に応じて多結晶シリコン膜に入り込んでくる単位体積当たりのニッケルの量が異なるため、ニッケルシリサイド中のニッケルとシリコンとの比率がゲート長に応じて変化してしまう。つまり、図6A及び図6Bに示すように、シリコン基板101の上方の多結晶シリコン膜102上には、その上に形成されたニッケル膜103からニッケルが供給されるが、この際に、ニッケルは多結晶シリコン膜102の直上だけでなく、その側方からも供給される。但し、側方からのニッケルの供給量は、ゲート長に拘わらず一定である。このため、ゲート長が短いMOSトランジスタ(図6A)と長いMOSトランジスタ(図6B)との間で、多結晶シリコン膜102の上面の単位面積当たりの側方からの供給量を比較すると、ゲート長が短いMOSトランジスタへの供給量が多くなる。この結果、ゲート長に応じてゲート電極の仕事関数が変動してしまい、MOSトランジスタの動作電圧も変動してしまう。

【0007】

【特許文献1】特開2005−129551号公報

【特許文献2】特開平8−255769号公報

【特許文献3】特開平9−69497号公報

【特許文献4】特開2005−243664号公報

【特許文献5】特開2005−252192号公報

【非特許文献1】J Kedzierski et.al IEDM2002 p.247

【非特許文献2】Kittl et al., EDL pp. 966 vol.27 (2006)

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明の目的は、ゲート長に依存する仕事関数の変動を抑えることができる半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0009】

本願発明者は、上記課題を解決すべく、鋭意検討を重ねた結果、以下に示す発明の諸態様に想到した。

【0010】

半導体装置の製造方法の一態様では、半導体基板上にゲート絶縁膜を形成し、その後、前記ゲート絶縁膜上に半導体膜を形成する。次いで、前記半導体膜を所定の温度に加熱する。そして、前記半導体膜が前記所定の温度に達している状態で、前記所定の温度下で前記半導体膜を構成する半導体と反応して金属半導体化合物を生成する金属を前記半導体膜上に供給することにより、前記半導体膜を金属半導体化合物膜に変化させる。

【発明の効果】

【0011】

上記の半導体装置の製造方法によれば、金属半導体化合物膜を適切に形成しているため、そのサイズに拘わらずその組成を安定したものとすることができる。従って、これをゲート電極に用いれば、仕事関数の変動を抑制することができる。

【発明を実施するための最良の形態】

【0012】

(基本的原理)

本方法では、半導体膜としてシリコン(Si)膜を用いる場合、シリコン膜のシリサイド化に際して、従来のようにニッケル膜等の原料膜を形成した後に加熱するのではなく、シリサイド反応が生じる温度にシリコン膜を加熱しておき、この状態でニッケル等の金属原料の供給を行うこととする。

【0013】

ここで、このような相違点に関して、本願発明者らが行った実験について説明する。

【0014】

先ず、従来の方法を反映した方法により試料を作製した。この方法では、基板上にゲート絶縁膜に相当するSiO2膜(厚さ:10nm)を形成し、その上に多結晶シリコン膜(厚さ:100nm)を形成した。次いで、原料膜となるニッケル(Ni)膜(厚さ:60nm)を多結晶シリコン膜上に室温で形成した。その後、基板を400℃まで加熱し、120秒間の熱処理を行うことにより、多結晶シリコン膜からニッケルシリサイド膜を得た。そして、ニッケルシリサイド膜のX線分析を行った。この結果を図7Aに示す。

【0015】

その一方で、本発明を反映させた方法により試料を作製した。この方法では、基板上にゲート絶縁膜に相当するSiO2膜(厚さ:10nm)を形成し、その上に多結晶シリコン膜(厚さ:100nm)を形成した。次いで、基板を400℃まで加熱し、その温度が安定してからニッケル膜(厚さ:60nm)を多結晶シリコン膜上に形成した。この際に、多結晶シリコン膜からニッケルシリサイド膜が得られた。そして、ニッケルシリサイド膜のX線分析を行った。この結果を図7Bに示す。

【0016】

400℃という温度はNiSiの生成に適した温度といわれているが、図7Aに示すように、従来の方法を反映した方法では、NiSiだけでなく、Ni2Siも検出された。つまり、NiSi(112)、NiSi(211)及びNi2Si(002)のピークが現れた。これは、この方法ではニッケル膜からニッケルが過剰に供給されたことを示している。一方、図7Bに示すように、本発明を反映させた方法によれば、NiSiのみが検出され、Ni2Siは検出されなかった。つまり、NiSi(112)及びNiSi(211)のピークが現れ、Ni2Si(002)のピークは現れなかった。これは、この方法によれば所望の組成のニッケルシリサイドが得られたことを示している。

【0017】

そこで、本発明では、全体がシリサイド化したゲート電極の形成に当たり、シリコン膜を形成した後に、これを所望のシリサイド相反応が生じる温度まで加熱しておき、この状態で金属原料の供給を行うこととしているのである。

【0018】

(第1の実施形態)

次に、第1の実施形態について説明する。図1A乃至図1Kは、第1の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【0019】

先ず、図1Aに示すように、pMOS領域1及びnMOS領域2を画定する素子分離絶縁膜2をSTI(Shallow Trench Isolation)法等によりシリコン基板等の半導体基板11の表面に形成する。pMOS領域1は、pチャネルMOSトランジスタを形成する予定の領域であり、nMOS領域2は、nチャネルMOSトランジスタを形成する予定の領域である。次いで、pMOS領域1にn型不純物をイオン注入し、nMOS領域2にp型不純物をイオン注入し、熱処理を行うことにより、これらの不純物を活性化させる。この結果、pMOS領域1にnウェル13nが形成され、nMOS領域2にpウェル13pが形成される。

【0020】

次いで、図1Bに示すように、半導体基板11上に、ゲート絶縁膜14、多結晶シリコン膜15及びシリコン窒化膜16を順次形成する。ゲート絶縁膜14としては、厚さが2nm程度のシリコン酸化膜を形成する。多結晶シリコン膜15は、例えば原料ガスとしてSiH4ガスを用いたCVD(Chemical Vapor Deposition)法により580℃で形成する。多結晶シリコン膜15の厚さは、100nm程度とする。シリコン窒化膜16は、例えば原料ガスとしてNH3及びSiH4の混合ガスを用いたCVD法により形成する。シリコン窒化膜16の厚さは、10nm程度とする。

【0021】

その後、図1Cに示すように、ドライエッチングにより、シリコン窒化膜16、多結晶シリコン膜15及びゲート絶縁膜14をゲート電極の平面形状に加工する。

【0022】

続いて、nMOS領域2を覆うフォトレジスト膜(図示せず)を形成し、このフォトレジスト膜及びpMOS領域1内の多結晶シリコン膜15をマスクとして、nウェル13nに不純物イオンを注入する。このイオン注入では、例えば、加速エネルギを10keV程度、ドーズ量を2×1013cm-2程度として、ホウ素(B)を注入し、更に、加速エネルギを4keV程度、ドーズ量を1×1015cm-2程度として、砒素(As)を注入する。この結果、図1Dに示すように、p型不純物拡散層17pが形成され、その近傍にn型不純物拡散層が形成される。なお、図1Dでは、このn型不純物拡散層を省略している。

【0023】

次いで、nMOS領域2を覆うフォトレジスト膜を灰化処理等により除去し、pMOS領域1を覆うフォトレジスト膜(図示せず)を形成し、このフォトレジスト膜及びnMOS領域2内の多結晶シリコン膜15をマスクとして、pウェル13pに不純物イオンを注入する。このイオン注入では、例えば、加速エネルギを80keV程度、ドーズ量を2×1013cm-2程度として、砒素(As)を注入し、更に、加速エネルギを1keV程度、ドーズ量を1×1015cm-2程度として、ホウ素(B)を注入する。この結果、図1Dに示すように、n型不純物拡散層17nが形成され、その近傍にp型不純物拡散層が形成される。なお、図1Dでは、このp型不純物拡散層を省略している。

【0024】

その後、pMOS領域1を覆うフォトレジスト膜を灰化処理等により除去する。続いて、シリコン酸化膜等の絶縁膜を全面に形成し、これを全面異方性エッチングすることにより、多結晶シリコン膜15の側方にサイドウォール絶縁膜18を形成する。

【0025】

次いで、上記のようなフォトレジスト膜の形成及び除去を行いながら、図1Eに示すように、p型不純物拡散層17pよりも深いp型不純物拡散層19pをnウェル13nに形成し、n型不純物拡散層17nよりも深いn型不純物拡散層19nをpウェル13pに形成する。そして、1000℃程度での熱処理を行うことにより、各不純物拡散層中の不純物を活性化させる。なお、p型不純物拡散層19pの形成に当たっては、加速エネルギを5keV程度とし、ドーズ量を5×1015cm-2程度としてホウ素(B)を注入する。また、n型不純物拡散層19nの形成に当たっては、加速エネルギを20keV程度とし、ドーズ量を7×1015cm-2程度としてリン(P)を注入する。更に、このイオン注入では、イオンが多結晶シリコン膜15にも導入される。

【0026】

その後、図1Fに示すように、多結晶シリコン膜15間の隙間を埋め込むシリコン酸化膜20を全面に形成する。

【0027】

続いて、図1Gに示すように、CMP(Chemical Mechanical Polishing)等により、シリコン窒化膜16が露出するまでシリコン酸化膜20を研磨する。つまり、平坦化処理を行う。

【0028】

次いで、図1Hに示すように、シリコン窒化膜16を除去することにより、多結晶シリコン膜15を露出する。シリコン窒化膜16の除去に当たっては、150℃程度の熱リン酸を用いたウェット処理を行う。この場合のシリコン窒化膜16のシリコン酸化膜20に対する選択比は3〜4倍程度である。

【0029】

その後、半導体基板11を400℃まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜21を全面に形成する。ニッケル膜21の厚さは、シリコン酸化膜20上で60nmとする。この結果、シリコン酸化膜20上にはニッケル膜21が形成されるが、多結晶シリコン膜15の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜15と反応し、多結晶シリコン膜15の全体がニッケルシリサイド膜22に変化する。従って、pMOS領域1には、ホウ素(B)を含有するニッケルシリサイド膜22からなるゲート電極が形成され、nMOS領域2には、リン(P)を含有するニッケルシリサイド膜22からなるゲート電極が形成される。なお、多結晶シリコン膜15からニッケルシリサイド膜22への変化に伴って、その厚さは30nm程度増加する。

【0030】

続いて、図1Jに示すように、ニッケル膜21を除去する。そして、図1Kに示すように、全面に層間絶縁膜23を形成する。層間絶縁膜23としては、例えばシリコン酸化膜を形成する。次いで、層間絶縁膜23及びシリコン酸化膜20に不純物拡散層19n及び19pまで到達するコンタクトホールを形成し、その中にコンタクトプラグ24を形成する。その後、コンタクトプラグ24に接続される配線25を形成する。図示しないが、層間絶縁膜23にはニッケルシリサイド膜22まで到達するコンタクトホールも形成し、その中にもコンタクトプラグを形成する。更に、このコンタクトプラグに接する配線も形成する。

【0031】

その後、更に上層の層間絶縁膜及び配線等を形成して、CMOSトランジスタを備えた半導体装置を完成させる。

【0032】

このような第1の実施形態によれば、ニッケルシリサイド膜22の形成に際して、多結晶シリコン膜15を加熱した状態でニッケルの供給を行っているので、ニッケルシリサイド膜22の組成を確実にNiSiとすることができる。従って、ゲート長が相違する複数のMOSトランジスタが形成される場合であっても、ゲート長の相違に起因する動作電圧の変動を抑えることができる。

【0033】

また、pチャネルMOSトランジスタとnチャネルMOSトランジスタとの間では、ゲート電極に含有される不純物を相違させているので、夫々に適した仕事関数を得ることができる。

【0034】

(第2の実施形態)

次に、第2の実施形態について説明する。図2A乃至図2Fは、第2の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【0035】

先ず、第1の実施形態と同様にして、シリコン酸化膜20の研磨(図1G)までの処理を行う。次いで、図2Aに示すように、nMOS領域2を覆うフォトレジスト膜31をシリコン酸化膜20等の上に形成する。

【0036】

その後、図2Bに示すように、pMOS領域1内において、シリコン窒化膜16を除去することにより、多結晶シリコン膜15を露出する。

【0037】

続いて、図2Cに示すように、フォトレジスト膜31を灰化処理等により除去する。次いで、半導体基板11を420℃〜600℃程度まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜32を全面に形成する。ニッケル膜32の厚さは、シリコン酸化膜20上で120nmとする。この結果、シリコン酸化膜20上にはニッケル膜32が形成されるが、pMOS領域1内の多結晶シリコン膜15の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜15と反応し、多結晶シリコン膜15の全体がニッケルシリサイド膜33に変化する。従って、pMOS領域1に、ホウ素(B)を含有するニッケルシリサイド膜33からなるゲート電極が形成される。なお、このような条件で形成されたニッケルシリサイド膜33の組成はNi2Siとなる。

【0038】

次いで、図2Dに示すように、ニッケル膜32を除去する。

【0039】

その後、図2Eに示すように、pMOS領域1を覆うフォトレジスト膜34をシリコン酸化膜20等の上に形成する。

【0040】

続いて、図2Fに示すように、nMOS領域2内において、シリコン窒化膜16を除去することにより、多結晶シリコン膜15を露出する。

【0041】

次いで、図2Gに示すように、フォトレジスト膜34を灰化処理等により除去する。その後、半導体基板11をニッケル膜32の形成時よりも低い温度、例えば400℃程度まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜35を全面に形成する。ニッケル膜35の厚さは、シリコン酸化膜20上で60nmとする。この結果、シリコン酸化膜20上にはニッケル膜35が形成されるが、nMOS領域2内の多結晶シリコン膜15の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜15と反応し、多結晶シリコン膜15の全体がニッケルシリサイド膜36に変化する。従って、nMOS領域2に、リン(P)を含有するニッケルシリサイド膜36からなるゲート電極が形成される。なお、このような条件で形成されたニッケルシリサイド膜36の組成はNiSiとなる。

【0042】

次いで、図2Hに示すように、ニッケル膜35を除去する。

【0043】

その後、第1の実施形態と同様にして、層間絶縁膜23の形成(図1K)以降の処理を行う。

【0044】

このような第2の実施形態によっても第1の実施形態と同様の効果が得られる。また、pチャネルMOSトランジスタとnチャネルMOSトランジスタとの間で、ゲート電極の組成を意図的に相違させているので、仕事関数を所望のものとすることがより一層容易になる。

【0045】

なお、pMOS領域1にNiSiからなるゲート電極を形成し、nMOS領域2にNi2Siからなるゲート電極を形成することも可能であるが、この場合にも、より高温への加熱が必要とされる処理を先に行うことが好ましい。つまり、Ni2Siからなるゲート電極を形成した後に、NiSiからなるゲート電極を形成することが好ましい。この順序を逆にすると、Ni2Siからなるゲート電極を形成する際に、NiSiがNi2Siに変化する虞があるからである。

【0046】

また、ニッケルシリサイドのNi量を増やすことも可能である。この場合には、ニッケル膜の形成時の温度を高くしたり、時間を長くしたりすればよい。

【0047】

(第3の実施形態)

次に、第3の実施形態について説明する。図3A乃至図3Gは、第3の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【0048】

先ず、第1の実施形態と同様にして、ゲート絶縁膜14の形成(図1B)までの処理を行う。次いで、図3Aに示すように、nMOS領域2を覆うフォトレジスト膜41をゲート絶縁膜14の上に形成する。

【0049】

その後、図3Bに示すように、pMOS領域1内において、ゲート絶縁膜14上に、閾値制御膜として、厚さが10nm程度の窒化ハフニウム膜42を形成する。

【0050】

続いて、図3Cに示すように、フォトレジスト膜41を灰化処理等により除去する。次いで、pMOS領域1を覆うフォトレジスト膜43を窒化ハフニウム膜42の上に形成する。

【0051】

その後、図3Dに示すように、nMOS領域2内において、ゲート絶縁膜14上に、閾値制御膜として、厚さが10nm程度の炭化ハフニウム膜44を形成する。

【0052】

続いて、図3Eに示すように、フォトレジスト膜43を灰化処理等により除去する。次いで、図1Bに示すように、窒化ハフニウム膜42及び炭化ハフニウム膜44上に、多結晶シリコン膜15及びシリコン窒化膜16を順次形成する。このとき、多結晶シリコン膜15の厚さは、90nm程度とする。つまり、第1の実施形態と比較すると、窒化ハフニウム膜42及び炭化ハフニウム膜44の分だけ薄くする。

【0053】

その後、図3Fに示すように、ドライエッチングにより、シリコン窒化膜16、多結晶シリコン膜15、窒化ハフニウム膜42、炭化ハフニウム膜44及びゲート絶縁膜14をゲート電極の平面形状に加工する。

【0054】

続いて、図3Gに示すように、第1の実施形態と同様にして、不純物拡散層17p及び17nの形成(図1D)から配線25の形成までの処理を行い、更に上層の層間絶縁膜及び配線等を形成して、CMOSトランジスタを備えた半導体装置を完成させる。

【0055】

このような第3の実施形態によっても第1の実施形態と同様の効果が得られる。また、pチャネルMOSトランジスタ及びnチャネルMOSトランジスタに、互いに異なる材料からなる閾値制御膜(窒化ハフニウム膜42及び炭化ハフニウム膜44)を設けているので、仕事関数を所望のものとすることがより一層容易になる。

【0056】

なお、第3の実施形態を第2の実施形態に組み合わせてもよい。

【0057】

(第4の実施形態)

次に、第4の実施形態について説明する。図4A乃至図4Cは、第4の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【0058】

先ず、第3の実施形態と同様にして、窒化ハフニウム膜42及び炭化ハフニウム膜44の形成並びにフォトレジスト膜43の除去(図3E)までの処理を行う。次いで、図4Aに示すように、第3の実施形態よりも薄い多結晶シリコン膜15、及び第3の実施形態よりも厚いシリコン窒化膜16を窒化ハフニウム膜42及び炭化ハフニウム膜44上に順次形成する。

【0059】

その後、図4Bに示すように、ドライエッチングにより、シリコン窒化膜16、多結晶シリコン膜15、窒化ハフニウム膜42、炭化ハフニウム膜44及びゲート絶縁膜14をゲート電極の平面形状に加工する。

【0060】

続いて、図4Cに示すように、第1の実施形態と同様にして、不純物拡散層17p及び17nの形成(図1D)から配線25の形成までの処理を行い、更に上層の層間絶縁膜及び配線等を形成して、CMOSトランジスタを備えた半導体装置を完成させる。

【0061】

このような第4の実施形態によっても第3の実施形態と同様の効果が得られる。第3の実施形態では、ニッケルシリサイド膜22に不純物が含有されているため、この不純物が窒化ハフニウム膜42及び炭化ハフニウム膜44との界面近傍に偏析する虞がある。これに対し、第4の実施形態では、シリコン窒化膜16を厚くしているので、不純物拡散層19p及び19nの形成時にニッケルシリサイド膜22へ不純物が導入されにくく、このような偏析を回避することができる。

【0062】

なお、第4の実施形態を閾値制御膜(窒化ハフニウム膜42及び炭化ハフニウム膜44)が存在しない第1の実施形態及び第2の実施形態に組み合わせてもよい。このような組み合わせにより得られる方法は、ニッケルシリサイド膜22への不純物の導入を回避した方がよい場合に有効である。

【0063】

(第5の実施形態)

次に、第5の実施形態について説明する。図5A乃至図5Cは、第5の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【0064】

先ず、第1の実施形態と同様にして、シリコン窒化膜16の除去(図1H)までの処理を行う。次いで、図5Aに示すように、多結晶シリコン膜15を除去する。

【0065】

その後、図5Bに示すように、pMOS領域1内のゲート絶縁膜14上に窒化ハフニウム膜42を形成し、nMOS領域2内のゲート絶縁膜14上に炭化ハフニウム膜44を形成する。なお、多結晶シリコン膜15の除去の際にゲート絶縁膜14も除去されてしまった場合には、窒化ハフニウム膜42及び炭化ハフニウム膜44の形成の前にゲート絶縁膜14を形成し直せばよい。

【0066】

続いて、図5Cに示すように、窒化ハフニウム膜42上及び炭化ハフニウム膜44上に多結晶シリコン膜51を形成する。多結晶シリコン膜51の厚さは、第3の実施形態と同様に、90nm程度とする。

【0067】

そして、第1の実施形態と同様にして、ニッケル膜21の形成(図1I)以降の処理を行う。

【0068】

このような第5の実施形態によっても第3の実施形態と同様の効果が得られる。また、閾値制御膜(窒化ハフニウム膜42上及び炭化ハフニウム膜44)の形成を不純物拡散層中の不純物の活性化のための熱処理の後に行っているので、閾値制御膜として、比較的融点が低い金属からなる膜を用いることも可能である。

【0069】

なお、第5の実施形態を第4の実施形態に組み合わせてもよい。

【0070】

このように、これらの実施形態によれば、ニッケルシリサイド膜の形成に際して、多結晶シリコン膜を加熱した状態でニッケルの供給を行っているので、所望のニッケルシリサイド膜の組成を確実にNiSiとすることができる。従って、ゲート長が相違する複数のMOSトランジスタが形成される場合であっても、ゲート長の相違に起因する動作電圧の変動を抑えることができる。

【0071】

また、必要に応じて、ニッケルシリサイド膜の組成を調整したり、閾値制御膜を形成したり、不純物の導入を調整したりすることにより、ゲート電極の仕事関数を広い範囲内から選択することができる。

【0072】

なお、シリサイドの原料はニッケルに限定されず、例えば、コバルト(Co)、チタン(Ti)、タングステン(W)、モリブデン(Mo)、白金(Pt)又はハフニウム(Hf)を用いてもよい。

【0073】

また、シリコン窒化膜16の代わりにシリコン酸化膜を用いてもよく、シリコン酸化膜20の代わりにシリコン窒化膜を用いてもよい。他の絶縁膜等についてもその材料は特に限定されない。

【0074】

また、ゲート電極に含まれる不純物はホウ素及びリンに限定されず、n型の置換型不純物として砒素(As)及び/又はアンチモン(Sb)を用いてもよく、p型の置換型不純物としてガリウム(Ga)及び/又はインジウム(In)を用いてもよい。このような置換型不純物は、上述の実施形態のように、不純物拡散層の形成の際に導入されてもよく、多結晶シリコン膜の形成時に導入されてもよい。

【0075】

また、閾値制御膜の材料としては、ハフニウム(Hf)、白金、タングステン又はルテニウム(Ru)も挙げられる。また、これらの窒化物又は炭化物を用いてもよい。

【0076】

また、半導体として、シリコン以外に、ゲルマニウム(Ge)、SiGe又はSiC等を用いてもよい。これらの半導体を用いた場合、金属半導体化合物として、ゲリサイド又はシリサイドが得られる。

【0077】

なお、特許文献1には、ゲート電極の仕事関数を制御し易くするための技術が記載されているが、この技術によっても、上記の実施形態と比較すると、得られる仕事関数の範囲は限られており、ゲート電極の閾電圧の範囲も限定されている。

【図面の簡単な説明】

【0078】

【図1A】第1の実施形態に係る半導体装置の製造方法を示す断面図である。

【図1B】図1Aに引き続き、半導体装置の製造方法を示す断面図である。

【図1C】図1Bに引き続き、半導体装置の製造方法を示す断面図である。

【図1D】図1Cに引き続き、半導体装置の製造方法を示す断面図である。

【図1E】図1Dに引き続き、半導体装置の製造方法を示す断面図である。

【図1F】図1Eに引き続き、半導体装置の製造方法を示す断面図である。

【図1G】図1Fに引き続き、半導体装置の製造方法を示す断面図である。

【図1H】図1Gに引き続き、半導体装置の製造方法を示す断面図である。

【図1I】図1Hに引き続き、半導体装置の製造方法を示す断面図である。

【図1J】図1Iに引き続き、半導体装置の製造方法を示す断面図である。

【図1K】図1Jに引き続き、半導体装置の製造方法を示す断面図である。

【図2A】第2の実施形態に係る半導体装置の製造方法を示す断面図である。

【図2B】図2Aに引き続き、半導体装置の製造方法を示す断面図である。

【図2C】図2Bに引き続き、半導体装置の製造方法を示す断面図である。

【図2D】図2Cに引き続き、半導体装置の製造方法を示す断面図である。

【図2E】図2Dに引き続き、半導体装置の製造方法を示す断面図である。

【図2F】図2Eに引き続き、半導体装置の製造方法を示す断面図である。

【図2G】図2Fに引き続き、半導体装置の製造方法を示す断面図である。

【図2H】図2に引き続き、半導体装置の製造方法を示す断面図である。

【図3A】第3の実施形態に係る半導体装置の製造方法を示す断面図である。

【図3B】図3Aに引き続き、半導体装置の製造方法を示す断面図である。

【図3C】図3Bに引き続き、半導体装置の製造方法を示す断面図である。

【図3D】図3Cに引き続き、半導体装置の製造方法を示す断面図である。

【図3E】図3Dに引き続き、半導体装置の製造方法を示す断面図である。

【図3F】図3Eに引き続き、半導体装置の製造方法を示す断面図である。

【図3G】図3Fに引き続き、半導体装置の製造方法を示す断面図である。

【図4A】第4の実施形態に係る半導体装置の製造方法を示す断面図である。

【図4B】図4Aに引き続き、半導体装置の製造方法を示す断面図である。

【図4C】図4Bに引き続き、半導体装置の製造方法を示す断面図である。

【図5A】第5の実施形態に係る半導体装置の製造方法を示す断面図である。

【図5B】図5Aに引き続き、半導体装置の製造方法を示す断面図である。

【図5C】図5Bに引き続き、半導体装置の製造方法を示す断面図である。

【図6A】ゲート長が短いMOSトランジスタにおけるNiの拡散を示す模式図である。

【図6B】ゲート長が長いMOSトランジスタにおけるNiの拡散を示す模式図である。

【図7A】従来の方法を反映した方法により作製した試料のX線分析の結果を示す図である。

【図7B】本発明を反映した方法により作製した試料のX線分析の結果を示す図である。

【符号の説明】

【0079】

1:pMOS領域

2:nMOS領域

11:半導体基板

14:ゲート絶縁膜

15、51:多結晶シリコン膜

21、32、35:ニッケル膜

22、33、36:ニッケルシリサイド膜

42:窒化ハフニウム膜

44:炭化ハフニウム膜

【特許請求の範囲】

【請求項1】

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に半導体膜を形成する工程と、

前記半導体膜を所定の温度に加熱する工程と、

前記半導体膜が前記所定の温度に達している状態で、前記所定の温度下で前記半導体膜を構成する半導体と反応して金属半導体化合物を生成する金属を前記半導体膜上に供給することにより、前記半導体膜を金属半導体化合物膜に変化させる工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記金属として、ニッケル、コバルト、チタン、タングステン、モリブデン、白金及びハフニウムからなる群から選択された少なくとも1種を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記半導体膜として、置換型不純物を含有するものを用いることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記置換型不純物を、前記半導体膜を形成した後又は形成する際に導入することを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記ゲート絶縁膜を形成する工程と前記半導体膜を形成する工程との間に、

前記ゲート絶縁膜上に、金属元素を含有する導電膜を形成する工程を有することを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

【請求項1】

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に半導体膜を形成する工程と、

前記半導体膜を所定の温度に加熱する工程と、

前記半導体膜が前記所定の温度に達している状態で、前記所定の温度下で前記半導体膜を構成する半導体と反応して金属半導体化合物を生成する金属を前記半導体膜上に供給することにより、前記半導体膜を金属半導体化合物膜に変化させる工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記金属として、ニッケル、コバルト、チタン、タングステン、モリブデン、白金及びハフニウムからなる群から選択された少なくとも1種を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記半導体膜として、置換型不純物を含有するものを用いることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記置換型不純物を、前記半導体膜を形成した後又は形成する際に導入することを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記ゲート絶縁膜を形成する工程と前記半導体膜を形成する工程との間に、

前記ゲート絶縁膜上に、金属元素を含有する導電膜を形成する工程を有することを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図1J】

【図1K】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2H】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図3F】

【図3G】

【図4A】

【図4B】

【図4C】

【図5A】

【図5B】

【図5C】

【図6A】

【図6B】

【図7A】

【図7B】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図1J】

【図1K】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2H】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図3F】

【図3G】

【図4A】

【図4B】

【図4C】

【図5A】

【図5B】

【図5C】

【図6A】

【図6B】

【図7A】

【図7B】

【公開番号】特開2009−158596(P2009−158596A)

【公開日】平成21年7月16日(2009.7.16)

【国際特許分類】

【出願番号】特願2007−332797(P2007−332797)

【出願日】平成19年12月25日(2007.12.25)

【出願人】(308014341)富士通マイクロエレクトロニクス株式会社 (2,507)

【Fターム(参考)】

【公開日】平成21年7月16日(2009.7.16)

【国際特許分類】

【出願日】平成19年12月25日(2007.12.25)

【出願人】(308014341)富士通マイクロエレクトロニクス株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]