半導体装置の製造方法

【課題】 高誘電率ゲート絶縁膜とメタルゲート電極を用いたメタルゲートCMOSの製造方法を簡略化する。

【解決手段】 高誘電率ゲート絶縁膜6上にシリコン膜7を形成し、PMOS領域のシリコン膜7のみを選択的に窒化してSiN膜9に置換する。そしてNMOS領域上のシリコン膜7及びPMOS領域上のSiN膜9上にキャップ膜としてのLa(O)膜11及びメタル電極のW膜12を形成した後、加熱処理して、La(O)膜11のLa元素をNMOS領域の高誘電率ゲート絶縁膜に拡散させる。この際、PMOS領域においては、SiN膜9によりLa元素の拡散をブロックする。これにより、NMOSFETとPMOSFETの作りわけを容易に行える。また、窒化されやすい高誘電率ゲート絶縁膜6であれば、シリコン膜7を省略して、窒化処理によりPMOS領域の高誘電率ゲート絶縁膜6だけを選択的に窒化してもよい。

【解決手段】 高誘電率ゲート絶縁膜6上にシリコン膜7を形成し、PMOS領域のシリコン膜7のみを選択的に窒化してSiN膜9に置換する。そしてNMOS領域上のシリコン膜7及びPMOS領域上のSiN膜9上にキャップ膜としてのLa(O)膜11及びメタル電極のW膜12を形成した後、加熱処理して、La(O)膜11のLa元素をNMOS領域の高誘電率ゲート絶縁膜に拡散させる。この際、PMOS領域においては、SiN膜9によりLa元素の拡散をブロックする。これにより、NMOSFETとPMOSFETの作りわけを容易に行える。また、窒化されやすい高誘電率ゲート絶縁膜6であれば、シリコン膜7を省略して、窒化処理によりPMOS領域の高誘電率ゲート絶縁膜6だけを選択的に窒化してもよい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置、特にCMOS(Complementary Metal Oxide Semiconductor)トランジスタとその製造方法に関する。

【背景技術】

【0002】

近年の大規模集積回路の微細化に伴ってCMOSトランジスタにおいてもゲート絶縁膜の薄膜化が要求されている。しかし、ゲート絶縁膜の薄膜化が進むとゲート電極にポリシリコン膜を使用した場合には、ゲート電極の空乏化が無視出来なくなる。そのため、近年、ゲート電極にメタル電極を用いることが検討されており、NMOSトランジスタとPMOSトランジスタの両方において、低いしきい値電圧を実現するために、互いに異なる仕事関数を有する材料を使用してゲート電極を形成する、いわゆるデュアルゲート化が検討されている。

【0003】

また、ゲート絶縁膜として、Hf酸化物等の高誘電率絶縁膜を使用することによって物理的な膜厚を厚くしてリーク電流を抑制しつつ、電気的薄膜化を進めていくという提案もなされている。しかし、ゲート絶縁膜に高誘電率絶縁膜を用いても、ゲート電極にポリシリコンを用いた場合、ポリシリコンゲート電極が空乏化してしまい、電気的膜厚が上昇するという問題がある。そこで、高誘電率ゲート絶縁膜とメタルゲートの組み合わせて用いることが試みられている。

【0004】

次世代MOSFETの高誘電率ゲート絶縁膜として、ハフニウム(Hf)又はジルコニウム(Zr)を含む絶縁膜が有望視されているが、例えば、高誘電率ゲート絶縁膜としてハフニウム珪酸窒化膜(HfSiON)膜を用いたCMOSトランジスタにおいては、ピニングと呼ばれる現象のため、仕事関数の異なる材料を使用しても、フラットバンド電圧(Vfb)をバンドエッジに調整できずミッドギャップ近傍になってしまい、低いしきい値電圧を実現できないという問題がある。そこで、NMOSFETのVfbをバンドエッジに持っていくために、ランタノイドをはじめとするキャップ膜を使うことが有効とされている(例えば、特許文献1参照)。しかし、NMOS領域とPMOS領域でキャップ膜を作り分けるには、成膜とパターニング、エッチング等の工程を複数回繰り返す等、複雑かつ多数の工程が要求されてしまうという問題があった。

【特許文献1】特開2002−270821

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明は、上記の問題を鑑みなされたもので製造工程の簡略化が可能な高誘電率ゲート絶縁膜とメタルゲート電極を用いたメタルゲートCMOSの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するために、本発明の一態様による半導体装置の製造方法は、基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、前記高誘電率ゲート絶縁膜上にシリコン膜を形成する工程と、前記N型半導体領域上の前記シリコン膜を窒化して窒化シリコン膜に置換する工程と、前記P型半導体領域の前記シリコン膜上及び前記N型半導体領域の前記窒化シリコン膜上にキャップ膜を介してメタルゲート電極を形成する工程と、前記キャップ膜の構成元素を前記N型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程とを備えることを特徴とする。

【0007】

また、本発明の別態様による半導体装置の製造方法は、基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、前記N型半導体領域上の前記高誘電率ゲート絶縁膜を窒化して窒化高誘電率ゲート絶縁膜に置換する工程と、前記P型半導体領域の前記高誘電率ゲート絶縁膜上及び前記N型半導体領域の前記窒化高誘電率ゲート絶縁膜上にキャップ膜を介してメタルゲート電極を形成する工程と、前記キャップ膜の構成元素を前記P型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程とを備えることを特徴とする。

【0008】

さらに、本発明の別態様による半導体装置の製造方法は、基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、前記N型半導体領域上の前記高誘電率ゲート絶縁膜上にシリコン窒化膜を形成する工程と、前記P型半導体領域の前記高誘電率ゲート絶縁膜上及び前記N型半導体領域の前記シリコン窒化膜上にキャップ膜を介してメタルゲート電極を形成する工程と、前記キャップ膜の構成元素を前記P型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程と、を備えることを特徴とする

【発明の効果】

【0009】

本発明によれば、高誘電率ゲート絶縁膜とメタルゲート電極を用いたメタルゲートCMOSの製造方法を簡略化することができる。

【発明を実施するための最良の形態】

【0010】

以下、本発明の実施形態について図面を参照しながら説明する。

【0011】

(第1の実施形態)

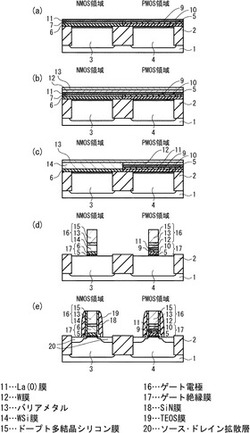

図1及び図2は本発明の第1の実施形態に係るCMOSFETの製造工程を示す断面図である。

【0012】

はじめに、図1(a)に示すように、シリコン(Si)基板1の主面上に既知の方法でPMOSFETの形成領域(以下、単にPMOS領域と称す)及びNMOSFETの形成領域(以下、単にNMOS領域と称す)を区画するためのSTI(Shallow Trench Isolation)構造の素子分離領域2を形成する。この素子分離領域2は、例えば、以下の方法を用いて形成される。まず、シリコン基板1の主面上にバッファ膜を介してマスクとなるシリコン窒化膜を堆積させる。次に、レジストによるパターン転写法を用いてシリコン窒化膜、及びバッファ膜をパターニングしてマスクを形成し、このマスクを用いてシリコン基板1を所定の深さまでエッチングしてトレンチを形成する。次に、レジストを除去した後、シリコン基板1の主面全面にシリコン酸化膜を堆積した後、CMP(Chemical Mechanical Polishing)等で平坦化するとともにトレンチ内にシリコン酸化膜を埋め込んだ後、マスクとして用いたシリコン窒化膜及びバッファ膜を除去することにより素子分離領域2を形成する。

【0013】

その後、既知の方法によってNMOS領域であるPウェル拡散層3及びPMOS領域であるNウェル拡散層4を形成する。次に、図1(b)に示すように、酸素雰囲気中における加熱処理等によりシリコン基板1の主面を酸化させ、PMOS領域及びNMOS領域にシリコン酸化(SiO2)膜5を形成する。

【0014】

図1(c)に示すように、SiO2膜5の形成に続いて、SiO2膜5上に高誘電率ゲート絶縁膜6としてHfSiO膜をテトラジメチルアミノシリコンとテトラジエチルアミノハフニウムを用いたMOCVD法により堆積し、さらにこのHfSiO膜6の上に、例えば、ALD法やスパッタリング法を用いて非常に薄いシリコン膜7を形成する。

【0015】

このシリコン膜7の厚さは、窒化した時に、後述するランタン元素の拡散を防止できる厚さ、具体的には0.5nm〜1.0nm程度あればよい。また、デバイスの特性に影響を与えない程度の厚さであれば、それよりも厚く形成しても構わない。なお、スパッタリング法で成膜を行う場合は、十分な条件出しを行った上で成膜を行なうことが望ましい。

【0016】

その後、図1(d)に示すように、フォトリソグラフィー法等を用いてNMOS領域をレジスト8でマスクし、図1(e)に示すように、例えば、プラズマ窒化法によって、PMOS領域のHfSiO膜6及びシリコン膜7を窒化してシリコン窒化(SiN)膜に置換する。本実施形態ではNMOS領域のシリコン膜7をレジスト8でマスクしているため、PMOS領域のHfSiO膜6及びシリコン膜7をレジストが劣化しない低温でプラズマ窒化することが可能である。これにより、PMOS領域にはSiN膜9及びHfSiON膜10が形成され、NMOS領域はレジスト8で覆われているため、シリコン膜7がそのまま残った状態となる。なお、レジスト8は有機物であり、プラズマ窒化を行うことにより特性があまり変化しないと考えられるので、レジスト8の除去に悪影響を及ぼすことは少ない。

【0017】

次に、図2(a)に示すように、有機溶剤等でレジスト8を除去し、NMOS領域のシリコン膜7及びPMOS領域のSiN膜9上にキャップ膜としてのランタン(La)膜を形成する。このLa膜はNMOSFETのしきい値Vthを低くするために形成される。キャップ膜として、ランタンの代わりに、イットリウム、テルビウム、エルビウム、イッテルビウム、マグネシウム、イットリウム、スカンジウム、その他ランタノイド、アクチノイド、アルカリ土類金属、希土類金属のいずれかを用いてもよい。通常、La膜は工程中で少し酸化され、少量の酸素を含むLa(O)膜11となった状態で存在する。また、ランタンの代わりにマグネシウムを用いた場合も同様に少し酸化された状態で存在すると考えられる。

【0018】

続いて、図2(b)に示すように、La(O)膜11の上にメタル電極としてW膜12、さらにそのW膜12上にバリア膜としてのTiN膜13を形成する。TiN膜13の形成後、加熱工程を行うことによってNMOS領域においては、La(O)膜11に含まれるLa元素はシリコン基板1とSiO2膜5との界面近くまで拡散するが、PMOS領域においては、SiN膜9がLa元素の拡散をブロックするため、シリコン基板1とSiO2膜5との界面方向にはLa元素は拡散しない。そして、この加熱工程において、図2(c)に示すように、NMOS領域では、W膜12とシリコン膜7が反応し、W膜12とシリコン膜7とがWSi膜14に置換されるが、PMOS領域では、W膜12、La(O)膜11、SiN膜9及びHfSiON膜10はそのまま存在する。

【0019】

ここで、SiN膜9がLa元素の拡散をブロックする理由を以下に述べる。例えば、SiN膜9に対してLa(O)膜11を接触させた場合、熱力学的に説明すると後述の式(1)に示すような反応が起こる。この反応がどちらに進むかは、ギブスの自由エネルギーの差分(ΔG)が負となるかどうかで決まる。

【0020】

SiN+La(O)=La(O)N+Si+ΔG ・・・・・式(1)

図3に示すように、式(1)の反応におけるΔGは通常の半導体装置の製造で行われる加熱工程の温度では正の値となるため、式(1)の反応は右辺には進まない。従って、La(O)膜11のLa元素はSiN膜9を通り抜けることができないため、PMOS領域のシリコン基板1界面方向へのLa元素の拡散が抑制される。

【0021】

その後、図2(d)に示すように、ゲート材料として多結晶シリコン膜15をバリアメタル13であるTiN膜上に堆積し、多結晶シリコン膜15にイオン注入を行った後、フォトリソグラフィー法により多結晶シリコン膜15、TiN膜13、WSi膜14、またはW膜12を順にエッチングしてゲート電極16を形成する。さらに、このゲート電極16をマスクにして、La(O)膜11、HfSiON膜10、SiN膜9、HfSiO膜6、SiO2膜5を順にエッチングしてゲート絶縁膜17を形成する。この時、必要に応じてエクステンションイオン注入と結晶回復のアニールを行ってもよい。

【0022】

ここで、PMOS領域のLa(O)膜11は、ゲート構造の一部としてそのまま存在しているが、デバイス特性に悪影響を及ぼすようなことはないため、存在していても構わない。

【0023】

次に、図2(e)に示すように、SiNからなるライナー膜をシリコン基板1の上面全面に堆積した後、そのSiN膜上に、TEOS(Tetraethoxysilane)を堆積し、異方性エッチングにより、TEOS及びSiN膜をエッチングしてゲート側壁となるSiN膜18及びTEOS膜19を形成する。続いてゲート電極16をマスクにしてシリコン基板1に導電型不純物のイオン注入と活性化アニールを行い、ソース・ドレイン拡散層20を形成する。

【0024】

上記した本実施形態によれば、次のような効果が得られる。すなわち、高誘電率ゲート絶縁膜6上にシリコン膜7を形成した後、窒化処理してNMOS領域上のシリコン膜7はそのままにして、PMOS領域上のシリコン膜をSiN膜9に置換する。これにより、NMOS領域においては、La(O)膜11に含まれるLa元素はシリコン基板1とSiO2膜5との界面近くまで拡散するが、PMOS領域においては、SiN膜9がLa元素の拡散をブロックするため、シリコン基板1とSiO2膜5との界面まではLa元素は拡散しない。そのため、製造工程数の増加を抑え、NMOSFET、PMOSFETそれぞれに適したフラットバンド電圧に調節することができる。

【0025】

本実施形態では、メタル電極にW膜12を用い、メタル電極の上に形成される多結晶シリコン膜15とW膜12の反応を防止するためにバリアメタル13としてTiN膜を形成した。メタル電極はTa等の遷移金属類、それらのシリサイド、窒化物、炭化物等を用いてもよく、多結晶シリコン膜15と反応しない組み合わせであれば、バリアメタル13を形成しなくても構わない。また、バリアメタル13はTiNに限らず、TaCやRu等のメタル電極と多結晶シリコンの反応を防止できるものであれば他のものを用いても構わない。

【0026】

なお、本実施形態では、La元素をシリコン基板とゲート絶縁膜との界面付近まで拡散させるため、図2(b)に示す工程において加熱処理を行ったが、ソース及びドレイン拡散層形成時の加熱処理工程でも十分に相分離及び拡散が起こるため、省略しても構わない。

【0027】

加えて、本実施形態において、高誘電率ゲート絶縁膜としてシリコン酸化膜やシリコン酸窒化膜よりも誘電率の高い高誘電率絶縁膜を用い、金属元素(例えばHf等)を含有するハフニウム珪酸化膜を用いたが、ハフニウム珪酸窒化膜、ジルコニウム酸化膜、ハフニウム酸化膜、ハフニウムジルコニウム酸化膜、ハフニウムジルコニウム酸化膜等の窒化されにくい、又は窒化されても窒素濃度が低い他のものを用いてもよい。

【0028】

また、本実施形態で用いる基板は、通常のシリコン基板の他にSOI(Silicon On Insulator)基板を用いてもよい。

【0029】

(第2の実施形態)

第2の実施形態は、第1の実施形態において、SiO2膜5を形成するのに先駆けて、PMOS領域にエピタキシャル成長等によりシリコンゲルマニウム(SiGe)層を形成したものである。なお、本実施形態は、前記第1の実施形態とSiGe層を形成する点以外は同じであるので第1の実施形態における構成と同様の部分には同じ符号を付してその説明は省略する。

【0030】

図4(a)に示すように、SiO2膜5を形成する前にSiGe層21を形成する。この後の工程においては第1の実施形態と同様であり、図4(b)に示すように、ゲート電極16を形成した後、ゲート電極16をマスクにしてシリコン基板1に導電型不純物のイオン注入と活性化アニールを行い、ソース・ドレイン拡散層20を形成する。

【0031】

SiGe層21を形成することによって通常のシリコンチャネルのトランジスタよりも低しきい値電圧(Vth)を実現することができる。SiGe層21の代わりに、MOCVD(Metal Organic Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法を用いてAl2O3層やAlN層を形成しても構わない。また、SiGe層を形成してからAl2O3層やAlN層を形成しても良い。

【0032】

上記した本実施形態によれば、前記した第1の実施形態の効果に加え、次のような効果が得られる。すなわち、PMOS領域にSiGe層を形成することによって第1の実施形態と比較して低しきい値を有するCMOSFETを実現することが可能となる。

【0033】

(第3の実施形態)

図5及び図6は本発明の第3の実施形態に係るCMOSFETを有する半導体装置の製造工程を示す断面図である。

【0034】

はじめに、図5(a)に示すように、シリコン基板22の主面上に既知の方法でPMOS領域及びNMOS領域を区画するためのSTI構造の素子分離領域23を形成する。その後、既知の方法によってNMOS領域であるPウェル拡散層24及びPMOS領域であるNウェル拡散層25を形成する。

【0035】

次に、図5(b)に示すように、酸素雰囲気中における加熱処理等によりシリコン基板22の主面を酸化させ、PMOS領域及びNMOS領域にシリコン酸化(SiO2)膜26を形成する。

【0036】

図5(c)に示すように、SiO2膜26の形成に続いて、SiO2膜26上に高誘電率ゲート絶縁膜27としてHfSiON膜をMOCVD法等により堆積する。HfSiON膜27の窒素濃度は後述するLa元素の拡散を完全にブロックしない範囲で任意に変化させて実施することができる。

【0037】

その後、図5(d)に示すように、フォトリソグラフィー法等を用いてNMOS領域をレジスト28でマスクし、図5(e)に示すように、例えば、プラズマ窒化法によって、PMOS領域のHfSiON膜27を窒化する。これにより、PMOS領域のHfSiON膜27は窒化HfSiON膜29に置換され、NMOS領域はレジスト28で覆われているためHfSiON膜27がそのまま残った状態となる。窒化HfSiON膜29はHfSiON膜27よりも高い窒素濃度を有する。

【0038】

なお、レジスト28は有機物であり、プラズマ窒化を行うことにより特性があまり変化しないと考えられるので、レジスト28の除去に悪影響を及ぼすことは少ない。

【0039】

次に、図6(a)に示すように、有機溶剤等でレジスト28を除去し、NMOS領域のHfSiON膜27及びPMOS領域の窒化HfSiON膜29上にキャップ膜としてのLa膜を形成する。このLa膜はNMOSFETのしきい値Vthを低くするために形成される。キャップ膜として、ランタンの代わりに、イットリウム、テルビウム、エルビウム、イッテルビウム、マグネシウム、イットリウム、スカンジウム、その他ランタノイド、アクチノイド、アルカリ土類金属、希土類金属のいずれかを用いてもよい。通常、La膜は工程中で少し酸化され、少量の酸素を含むLa(O)膜30となった状態で存在する。また、ランタンの代わりにマグネシウムを用いた場合も同様に少し酸化された状態で存在すると考えられる。

【0040】

続いて、図6(b)に示すように、La(O)膜30の上にメタル電極としてW膜31、さらにそのW膜31上にバリアメタル32としてのTiN膜を形成する。TiN膜32形成後、加熱工程を行うことによってNMOS領域においては、La(O)膜30に含まれるLa元素はシリコン基板22とSiO2膜26の界面近くまで拡散するが、PMOS領域においては、窒化されたHfSiON膜29がLa元素の拡散をブロックするため、シリコン基板22の界面方向にはLa元素は拡散しない。

【0041】

その後、図6(c)に示すように、ゲート材料として多結晶シリコン膜33をTiN膜32上に堆積し、多結晶シリコン膜33にイオン注入を行った後、フォトリソグラフィー法により、多結晶シリコン膜33、TiN膜32、W膜31を順にエッチングしてゲート電極34を形成する。さらに、このゲート電極34をマスクにして、La(O)膜30、窒化HfSiON膜29又はHfSiON膜27、SiO2膜26を順にエッチングしてゲート絶縁膜35を形成する。この時、必要に応じてエクステンションイオン注入と結晶回復のアニールを行ってもよい。

【0042】

ここで、PMOS領域のLa(O)膜30は、ゲート構造の一部としてそのまま存在しているが、デバイス特性に悪影響を及ぼすようなことはないため、存在していても構わない。

【0043】

次に、図6(d)に示すように、SiNからなるライナー膜をシリコン基板22の上面全面に堆積した後、そのSiN膜上に、TEOS(Tetraethoxysilane)を堆積し、異方性エッチングにより、TEOS及びSiN膜をエッチングしてゲート側壁となるSiN膜36及びTEOS膜37を形成する。続いてゲート電極34をマスクにしてイオン注入と活性化アニールを行い、ソース・ドレイン拡散層38を形成する。

【0044】

上記した本実施形態によれば、次のような効果が得られる。すなわち、PMOS領域及びNMOS領域上にHfSiON膜27を形成した後、窒化処理してNMOS領域上のHfSiON27はそのままにして、PMOS領域上のHfSiON膜を高窒素濃度の窒化HfSiON膜29に置換する。これにより、NMOS領域においては、La(O)膜30に含まれるLa元素はシリコン基板22とSiO2膜26との界面近くまで拡散するが、PMOS領域においては、窒化HfSiON膜29がLa元素の拡散をブロックするため、シリコン基板22とSiO2膜26との界面方向にはLa元素は拡散しない。そのため、製造工程数の増加を抑え、NMOSFET、PMOSFETそれぞれに適したメタル電極を形成することができる。

【0045】

また、本実施形態では、PMOS領域上の高誘電率ゲート絶縁膜であるHfSiO膜を直接、選択的に窒化することにより、PMOS領域においては、La元素の拡散をブロックしているため、第1の実施形態と比べてさらに製造工程数を低減することができる。

【0046】

本実施形態では、メタル電極にW膜31を用い、メタル電極の上に形成される多結晶シリコン膜33とW膜31の反応を防止するためにバリアメタル32としてTiN膜を形成した。メタル電極はTa等の遷移金属類、それらのシリサイド、窒化物、炭化物等を用いてもよく、多結晶シリコン膜33と反応しない組み合わせであれば、バリアメタル32を形成しなくても構わない。また、バリアメタル32はTiNに限らず、TaCやRu等のメタル電極と多結晶シリコンの反応を防止できるものであれば他のものを用いても構わない。

【0047】

なお、本実施形態では、La元素をシリコン基板とゲート絶縁膜との界面付近まで拡散させるため、図6(b)に示す工程において加熱処理を行ったが、ソース及びドレイン拡散層形成時の加熱処理工程でも十分に相分離及び拡散が起こるため、省略しても構わない。

【0048】

加えて、本実施形態において、高誘電率ゲート絶縁膜27にハフニウム珪酸窒化膜を用いたが、ハフニウム珪酸化膜、ジルコニウム珪酸化膜、ジルコニウム珪酸窒化膜、ハフニウムジルコニウム珪酸化膜、ハフニウムジルコニウム珪酸窒化膜等の窒化を行うことによりキャップ膜の拡散を防止可能な窒素濃度を実現可能なものであれば、他のものを用いてもよい。

【0049】

また、本実施形態で用いる基板は、通常のシリコン基板の他にSOI(Silicon On Insulator)基板を用いてもよい。

【0050】

(第4の実施形態)

第4の実施形態は、第3の実施形態において、SiO2膜26を形成するのに先駆けて、PMOS領域にエピタキシャル成長等によりSiGe層を形成したものである。なお、本実施形態は、前記第3の実施形態とSiGe層を形成する点以外は同じであるので第3の実施形態における構成と同様の部分には同じ符号を付してその説明は省略する。

【0051】

図7(a)に示すように、SiO2膜26を形成する前にSiGe層39を形成する。この後の工程においては第3の実施形態と同様であり、図7(b)に示すように、ゲート電極34を形成した後、ゲート電極34をマスクにしてシリコン基板22に導電型不純物のイオン注入と活性化アニールを行い、ソース・ドレイン拡散層38を形成する。

【0052】

SiGe層39を形成することによって通常のシリコンチャネルのトランジスタよりも低しきい値電圧(Vth)を実現することができる。SiGe層の代わりに、MOCVD(Metal Organic Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法を用いてAl2O3層やAlN層を形成しても構わない。また、SiGe層を形成してからAl2O3層やAlN層を形成しても良い。

【0053】

上記した本実施形態によれば、前記した第3の実施形態の効果に加え、次のような効果が得られる。すなわち、PMOS領域にSiGe層を形成することによって第3の実施形態と比較して低しきい値を有するCMOSFETを実現することが可能となる。

【0054】

(第5の実施形態)

続いて、本発明の第5の実施形態に係る半導体装置の製造方法の説明を行う。図8及び図9は本発明の第5の実施形態に係る半導体装置の製造方法を示す断面図である。図8及び図9を用いて製造工程について以下に説明する。

【0055】

はじめに、図8(a)に示すように、シリコン基板40の主面上に既知の方法でPMOS領域及びNMOS領域を区画するためのSTI構造の素子分離領域41を形成する。その後、既知の方法によってNMOS領域であるPウェル拡散層42及びPMOS領域であるNウェル拡散層43を形成する。

【0056】

次に、図8(b)に示すように、酸素雰囲気中における加熱処理等によりシリコン基板40の主面を酸化させ、PMOS領域及びNMOS領域にシリコン酸化(SiO2)膜44を形成する。

【0057】

SiO2膜44の形成に続いて、図8(c)に示すように、SiO2膜44上に高誘電率ゲート絶縁膜としてハフニウム珪酸化膜(HfSiO)膜をMOCVD法等により堆積する。SiO2膜44上に堆積したHfSiO膜に対して窒化、アニールの工程を経て、ハフニウム珪酸窒化(HfSiON)膜45を形成する。HfSiON膜45の窒素濃度は後述するLa元素の拡散を完全にブロックしない範囲で任意に変化させて実施することができる。また、HfSiO膜の窒化ではなく、MOCVD法等によりSiO2膜44上に直接HfSiON膜を堆積しても構わない。

【0058】

続いてHfSiON膜45の上にALD法やCVD法等を用いて非常に薄いシリコン窒化(SiN)膜46を形成する。このSiN膜46の厚さは、後述するランタン元素の拡散を防止できる厚さ、具体的には0.5nm〜1.0nm程度あればよい。また、デバイスの特性に影響を与えない程度の厚さであれば、それよりも厚く形成しても構わない。

【0059】

その後、図8(d)に示すように、フォトリソグラフィー法等を用いてPMOS領域をレジスト47でマスクし、図8(e)に示すように、例えば、リン酸を用いた選択エッチング等によりNMOS領域のSiN膜46を除去する。

【0060】

次に、図9(a)に示すように、有機溶剤等でレジスト47を除去し、NMOS領域のHfSiON膜45及びPMOS領域のSiN膜46上にキャップ膜としてのランタン酸化(La2O3)膜48を形成する。このLa2O3膜はNMOSFETのしきい値Vthを低くするために形成される。La2O3膜の代わりにランタン膜を形成しても構わない。また、ランタン膜の代わりに、イットリウム、テルビウム、エルビウム、イッテルビウム、マグネシウム、イットリウム、スカンジウム、その他ランタノイド、アクチノイド、アルカリ土類金属、希土類金属のいずれかを用いてもよい。その場合には通常、La膜は工程中で少し酸化され、少量の酸素を含むLa(O)膜となった状態で存在する。また、ランタンの代わりにマグネシウムを用いた場合も同様に少し酸化された状態で存在すると考えられる。

【0061】

続いて、図9(b)に示すように、La2O3膜48の上にメタル電極としてW膜49、さらにそのW膜49上にバリアメタル50としてのTiN膜を形成する。TiN膜50形成後、加熱工程を行うことによってNMOS領域においては、La2O3膜48に含まれるLa元素はシリコン基板40とSiO2膜44の界面近くまで拡散するが、PMOS領域においては、SiN膜46がLa元素の拡散をブロックするため、シリコン基板40の界面方向にはLa元素は拡散しない。

【0062】

その後、図9(c)に示すように、ゲート材料として多結晶シリコン膜51をTiN膜50上に堆積し、多結晶シリコン膜51にイオン注入を行った後、フォトリソグラフィー法により、多結晶シリコン膜51、TiN膜50、W膜49を順にエッチングしてゲート電極52を形成する。さらに、このゲート電極52をマスクにして、La2O3膜48、SiN膜46、HfSiON膜45、SiO2膜44を順にエッチングしてゲート絶縁膜53を形成する。この時、必要に応じてエクステンションイオン注入と結晶回復のアニールを行ってもよい。

【0063】

次に、図9(d)に示すように、SiNからなるライナー膜をシリコン基板40の上面全面に堆積した後、そのSiN膜上に、TEOS(Tetraethoxysilane)を堆積し、異方性エッチングにより、TEOS及びSiN膜をエッチングしてゲート側壁となるSiN膜54及びTEOS膜55を形成する。続いてゲート電極52をマスクにしてイオン注入と活性化アニールを行い、ソース・ドレイン拡散層56を形成する。

【0064】

上記した本実施形態によれば、次のような効果が得られる。すなわち、PMOS領域上にSiN膜46を形成する。これにより、NMOS領域においては、La2O3膜48に含まれるLa元素はシリコン基板40とSiO2膜44との界面近くまで拡散するが、PMOS領域においては、SiN膜46がLa元素の拡散をブロックするため、シリコン基板40とSiO2膜44との界面方向にはLa元素は拡散しない。そのため、製造工程数の増加を抑え、NMOSFET、PMOSFETそれぞれに適したメタル電極を形成することができる。

【0065】

また、上記した第1の実施形態では、シリコン膜7がNMOS領域上に残存するため、W膜12と反応してシリサイド電極14を形成するが、本実施形態ではW膜をシリサイド化させずに電極として用いることができるため、より高速な動作を実現することができる。加えて、第1乃至第4の実施形態と比較して、レジスト膜を窒化する工程がないため、窒化したレジスト膜と比較して、容易にレジスト膜を剥離することができると考えられる。

【0066】

本実施形態では、メタル電極にW膜49を用い、メタル電極の上に形成される多結晶シリコン膜51とW膜49の反応を防止するためにバリアメタル50としてTiN膜を形成した。メタル電極はTa等の遷移金属類、それらのシリサイド、窒化物、炭化物等を用いてもよく、多結晶シリコン膜51と反応しない組み合わせであれば、バリアメタル50を形成しなくても構わない。また、バリアメタル50はTiNに限らず、TaCやRu等のメタル電極と多結晶シリコンの反応を防止できるものであれば他のものを用いても構わない。

【0067】

なお、本実施形態では、La元素をシリコン基板とゲート絶縁膜との界面付近まで拡散させるため、図9(b)に示す工程において加熱処理を行ったが、ソース及びドレイン拡散層形成時の加熱処理工程でも十分に相分離及び拡散が起こるため、省略しても構わない。

【0068】

加えて、本実施形態において、高誘電率ゲート絶縁膜45にハフニウム珪酸窒化膜を用いたが、ハフニウム珪酸化膜、ジルコニウム珪酸化膜、ジルコニウム珪酸窒化膜、ハフニウムジルコニウム珪酸化膜、ハフニウムジルコニウム珪酸窒化膜等の窒化を行うことによりキャップ膜の拡散を防止可能な窒素濃度を実現可能なものであれば、他のものを用いてもよい。

【0069】

また、本実施形態で用いる基板は、通常のシリコン基板の他にSOI(Silicon On Insulator)基板を用いてもよい。

【0070】

(第6の実施形態)

第6の実施形態は、第5の実施形態において、SiO2膜44を形成するのに先駆けて、PMOS領域にエピタキシャル成長等によりSiGe層を形成したものである。なお、本実施形態は、前記第5の実施形態とSiGe層を形成する点以外は同じであるので第5の実施形態における構成と同様の部分には同じ符号を付してその説明は省略する。

【0071】

図10(a)に示すように、SiO2膜44を形成する前にSiGe層57を形成する。この後の工程においては第5の実施形態と同様であり、図10(b)に示すように、ゲート電極52を形成した後、ゲート電極52をマスクにしてシリコン基板40に導電型不純物のイオン注入と活性化アニールを行い、ソース・ドレイン拡散層56を形成する。

【0072】

SiGe層57を形成することによって通常のシリコンチャネルのトランジスタよりも低しきい値電圧(Vth)を実現することができる。SiGe層の代わりに、MOCVD法やALD法を用いてAl2O3層やAlN層を形成しても構わない。また、SiGe層を形成してからAl2O3層やAlN層を形成しても良い。

【0073】

上記した本実施形態によれば、前記した第5の実施形態の効果に加え、次のような効果が得られる。すなわち、PMOS領域にSiGe層を形成することによって第5の実施形態と比較して低しきい値を有するCMOSFETを実現することが可能となる。

【0074】

本発明は上記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲で種々に変形して実施することができる。

【図面の簡単な説明】

【0075】

【図1】本発明の第1の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図2】本発明の第1の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図3】本発明の第1の実施形態に係る反応におけるギブスの自由エネルギーの差分特性を示した断面図。

【図4】本発明の第2の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図5】本発明の第3の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図6】本発明の第3の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図7】本発明の第4の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図8】本発明の第5の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図9】本発明の第5の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図10】本発明の第6の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【符号の説明】

【0076】

1、22、40 シリコン基板

2、23、41 素子分離領域(STI)

3、24、42 Pウェル拡散層

4、25、43 Nウェル拡散層

5、26、44 シリコン酸化膜

6、27、45 高誘電率ゲート絶縁膜

7 シリコン膜

8、28、47 レジスト

9、18、36、46、54 SiN膜

10、23 HfSiON膜

11、30 La(O)膜

12、31、49 W膜

13、32、50 バリアメタル

14 WSi膜

15、33、51 ドープト多結晶シリコン膜

16、34、52 ゲート電極

17、35、53 ゲート絶縁膜

19、37、55 TEOS膜

20、38、56 ソース・ドレイン拡散層

21、39、57 SiGe層

29 窒化HfSiON膜

48 La2O3膜

【技術分野】

【0001】

本発明は、半導体装置、特にCMOS(Complementary Metal Oxide Semiconductor)トランジスタとその製造方法に関する。

【背景技術】

【0002】

近年の大規模集積回路の微細化に伴ってCMOSトランジスタにおいてもゲート絶縁膜の薄膜化が要求されている。しかし、ゲート絶縁膜の薄膜化が進むとゲート電極にポリシリコン膜を使用した場合には、ゲート電極の空乏化が無視出来なくなる。そのため、近年、ゲート電極にメタル電極を用いることが検討されており、NMOSトランジスタとPMOSトランジスタの両方において、低いしきい値電圧を実現するために、互いに異なる仕事関数を有する材料を使用してゲート電極を形成する、いわゆるデュアルゲート化が検討されている。

【0003】

また、ゲート絶縁膜として、Hf酸化物等の高誘電率絶縁膜を使用することによって物理的な膜厚を厚くしてリーク電流を抑制しつつ、電気的薄膜化を進めていくという提案もなされている。しかし、ゲート絶縁膜に高誘電率絶縁膜を用いても、ゲート電極にポリシリコンを用いた場合、ポリシリコンゲート電極が空乏化してしまい、電気的膜厚が上昇するという問題がある。そこで、高誘電率ゲート絶縁膜とメタルゲートの組み合わせて用いることが試みられている。

【0004】

次世代MOSFETの高誘電率ゲート絶縁膜として、ハフニウム(Hf)又はジルコニウム(Zr)を含む絶縁膜が有望視されているが、例えば、高誘電率ゲート絶縁膜としてハフニウム珪酸窒化膜(HfSiON)膜を用いたCMOSトランジスタにおいては、ピニングと呼ばれる現象のため、仕事関数の異なる材料を使用しても、フラットバンド電圧(Vfb)をバンドエッジに調整できずミッドギャップ近傍になってしまい、低いしきい値電圧を実現できないという問題がある。そこで、NMOSFETのVfbをバンドエッジに持っていくために、ランタノイドをはじめとするキャップ膜を使うことが有効とされている(例えば、特許文献1参照)。しかし、NMOS領域とPMOS領域でキャップ膜を作り分けるには、成膜とパターニング、エッチング等の工程を複数回繰り返す等、複雑かつ多数の工程が要求されてしまうという問題があった。

【特許文献1】特開2002−270821

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明は、上記の問題を鑑みなされたもので製造工程の簡略化が可能な高誘電率ゲート絶縁膜とメタルゲート電極を用いたメタルゲートCMOSの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するために、本発明の一態様による半導体装置の製造方法は、基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、前記高誘電率ゲート絶縁膜上にシリコン膜を形成する工程と、前記N型半導体領域上の前記シリコン膜を窒化して窒化シリコン膜に置換する工程と、前記P型半導体領域の前記シリコン膜上及び前記N型半導体領域の前記窒化シリコン膜上にキャップ膜を介してメタルゲート電極を形成する工程と、前記キャップ膜の構成元素を前記N型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程とを備えることを特徴とする。

【0007】

また、本発明の別態様による半導体装置の製造方法は、基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、前記N型半導体領域上の前記高誘電率ゲート絶縁膜を窒化して窒化高誘電率ゲート絶縁膜に置換する工程と、前記P型半導体領域の前記高誘電率ゲート絶縁膜上及び前記N型半導体領域の前記窒化高誘電率ゲート絶縁膜上にキャップ膜を介してメタルゲート電極を形成する工程と、前記キャップ膜の構成元素を前記P型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程とを備えることを特徴とする。

【0008】

さらに、本発明の別態様による半導体装置の製造方法は、基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、前記N型半導体領域上の前記高誘電率ゲート絶縁膜上にシリコン窒化膜を形成する工程と、前記P型半導体領域の前記高誘電率ゲート絶縁膜上及び前記N型半導体領域の前記シリコン窒化膜上にキャップ膜を介してメタルゲート電極を形成する工程と、前記キャップ膜の構成元素を前記P型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程と、を備えることを特徴とする

【発明の効果】

【0009】

本発明によれば、高誘電率ゲート絶縁膜とメタルゲート電極を用いたメタルゲートCMOSの製造方法を簡略化することができる。

【発明を実施するための最良の形態】

【0010】

以下、本発明の実施形態について図面を参照しながら説明する。

【0011】

(第1の実施形態)

図1及び図2は本発明の第1の実施形態に係るCMOSFETの製造工程を示す断面図である。

【0012】

はじめに、図1(a)に示すように、シリコン(Si)基板1の主面上に既知の方法でPMOSFETの形成領域(以下、単にPMOS領域と称す)及びNMOSFETの形成領域(以下、単にNMOS領域と称す)を区画するためのSTI(Shallow Trench Isolation)構造の素子分離領域2を形成する。この素子分離領域2は、例えば、以下の方法を用いて形成される。まず、シリコン基板1の主面上にバッファ膜を介してマスクとなるシリコン窒化膜を堆積させる。次に、レジストによるパターン転写法を用いてシリコン窒化膜、及びバッファ膜をパターニングしてマスクを形成し、このマスクを用いてシリコン基板1を所定の深さまでエッチングしてトレンチを形成する。次に、レジストを除去した後、シリコン基板1の主面全面にシリコン酸化膜を堆積した後、CMP(Chemical Mechanical Polishing)等で平坦化するとともにトレンチ内にシリコン酸化膜を埋め込んだ後、マスクとして用いたシリコン窒化膜及びバッファ膜を除去することにより素子分離領域2を形成する。

【0013】

その後、既知の方法によってNMOS領域であるPウェル拡散層3及びPMOS領域であるNウェル拡散層4を形成する。次に、図1(b)に示すように、酸素雰囲気中における加熱処理等によりシリコン基板1の主面を酸化させ、PMOS領域及びNMOS領域にシリコン酸化(SiO2)膜5を形成する。

【0014】

図1(c)に示すように、SiO2膜5の形成に続いて、SiO2膜5上に高誘電率ゲート絶縁膜6としてHfSiO膜をテトラジメチルアミノシリコンとテトラジエチルアミノハフニウムを用いたMOCVD法により堆積し、さらにこのHfSiO膜6の上に、例えば、ALD法やスパッタリング法を用いて非常に薄いシリコン膜7を形成する。

【0015】

このシリコン膜7の厚さは、窒化した時に、後述するランタン元素の拡散を防止できる厚さ、具体的には0.5nm〜1.0nm程度あればよい。また、デバイスの特性に影響を与えない程度の厚さであれば、それよりも厚く形成しても構わない。なお、スパッタリング法で成膜を行う場合は、十分な条件出しを行った上で成膜を行なうことが望ましい。

【0016】

その後、図1(d)に示すように、フォトリソグラフィー法等を用いてNMOS領域をレジスト8でマスクし、図1(e)に示すように、例えば、プラズマ窒化法によって、PMOS領域のHfSiO膜6及びシリコン膜7を窒化してシリコン窒化(SiN)膜に置換する。本実施形態ではNMOS領域のシリコン膜7をレジスト8でマスクしているため、PMOS領域のHfSiO膜6及びシリコン膜7をレジストが劣化しない低温でプラズマ窒化することが可能である。これにより、PMOS領域にはSiN膜9及びHfSiON膜10が形成され、NMOS領域はレジスト8で覆われているため、シリコン膜7がそのまま残った状態となる。なお、レジスト8は有機物であり、プラズマ窒化を行うことにより特性があまり変化しないと考えられるので、レジスト8の除去に悪影響を及ぼすことは少ない。

【0017】

次に、図2(a)に示すように、有機溶剤等でレジスト8を除去し、NMOS領域のシリコン膜7及びPMOS領域のSiN膜9上にキャップ膜としてのランタン(La)膜を形成する。このLa膜はNMOSFETのしきい値Vthを低くするために形成される。キャップ膜として、ランタンの代わりに、イットリウム、テルビウム、エルビウム、イッテルビウム、マグネシウム、イットリウム、スカンジウム、その他ランタノイド、アクチノイド、アルカリ土類金属、希土類金属のいずれかを用いてもよい。通常、La膜は工程中で少し酸化され、少量の酸素を含むLa(O)膜11となった状態で存在する。また、ランタンの代わりにマグネシウムを用いた場合も同様に少し酸化された状態で存在すると考えられる。

【0018】

続いて、図2(b)に示すように、La(O)膜11の上にメタル電極としてW膜12、さらにそのW膜12上にバリア膜としてのTiN膜13を形成する。TiN膜13の形成後、加熱工程を行うことによってNMOS領域においては、La(O)膜11に含まれるLa元素はシリコン基板1とSiO2膜5との界面近くまで拡散するが、PMOS領域においては、SiN膜9がLa元素の拡散をブロックするため、シリコン基板1とSiO2膜5との界面方向にはLa元素は拡散しない。そして、この加熱工程において、図2(c)に示すように、NMOS領域では、W膜12とシリコン膜7が反応し、W膜12とシリコン膜7とがWSi膜14に置換されるが、PMOS領域では、W膜12、La(O)膜11、SiN膜9及びHfSiON膜10はそのまま存在する。

【0019】

ここで、SiN膜9がLa元素の拡散をブロックする理由を以下に述べる。例えば、SiN膜9に対してLa(O)膜11を接触させた場合、熱力学的に説明すると後述の式(1)に示すような反応が起こる。この反応がどちらに進むかは、ギブスの自由エネルギーの差分(ΔG)が負となるかどうかで決まる。

【0020】

SiN+La(O)=La(O)N+Si+ΔG ・・・・・式(1)

図3に示すように、式(1)の反応におけるΔGは通常の半導体装置の製造で行われる加熱工程の温度では正の値となるため、式(1)の反応は右辺には進まない。従って、La(O)膜11のLa元素はSiN膜9を通り抜けることができないため、PMOS領域のシリコン基板1界面方向へのLa元素の拡散が抑制される。

【0021】

その後、図2(d)に示すように、ゲート材料として多結晶シリコン膜15をバリアメタル13であるTiN膜上に堆積し、多結晶シリコン膜15にイオン注入を行った後、フォトリソグラフィー法により多結晶シリコン膜15、TiN膜13、WSi膜14、またはW膜12を順にエッチングしてゲート電極16を形成する。さらに、このゲート電極16をマスクにして、La(O)膜11、HfSiON膜10、SiN膜9、HfSiO膜6、SiO2膜5を順にエッチングしてゲート絶縁膜17を形成する。この時、必要に応じてエクステンションイオン注入と結晶回復のアニールを行ってもよい。

【0022】

ここで、PMOS領域のLa(O)膜11は、ゲート構造の一部としてそのまま存在しているが、デバイス特性に悪影響を及ぼすようなことはないため、存在していても構わない。

【0023】

次に、図2(e)に示すように、SiNからなるライナー膜をシリコン基板1の上面全面に堆積した後、そのSiN膜上に、TEOS(Tetraethoxysilane)を堆積し、異方性エッチングにより、TEOS及びSiN膜をエッチングしてゲート側壁となるSiN膜18及びTEOS膜19を形成する。続いてゲート電極16をマスクにしてシリコン基板1に導電型不純物のイオン注入と活性化アニールを行い、ソース・ドレイン拡散層20を形成する。

【0024】

上記した本実施形態によれば、次のような効果が得られる。すなわち、高誘電率ゲート絶縁膜6上にシリコン膜7を形成した後、窒化処理してNMOS領域上のシリコン膜7はそのままにして、PMOS領域上のシリコン膜をSiN膜9に置換する。これにより、NMOS領域においては、La(O)膜11に含まれるLa元素はシリコン基板1とSiO2膜5との界面近くまで拡散するが、PMOS領域においては、SiN膜9がLa元素の拡散をブロックするため、シリコン基板1とSiO2膜5との界面まではLa元素は拡散しない。そのため、製造工程数の増加を抑え、NMOSFET、PMOSFETそれぞれに適したフラットバンド電圧に調節することができる。

【0025】

本実施形態では、メタル電極にW膜12を用い、メタル電極の上に形成される多結晶シリコン膜15とW膜12の反応を防止するためにバリアメタル13としてTiN膜を形成した。メタル電極はTa等の遷移金属類、それらのシリサイド、窒化物、炭化物等を用いてもよく、多結晶シリコン膜15と反応しない組み合わせであれば、バリアメタル13を形成しなくても構わない。また、バリアメタル13はTiNに限らず、TaCやRu等のメタル電極と多結晶シリコンの反応を防止できるものであれば他のものを用いても構わない。

【0026】

なお、本実施形態では、La元素をシリコン基板とゲート絶縁膜との界面付近まで拡散させるため、図2(b)に示す工程において加熱処理を行ったが、ソース及びドレイン拡散層形成時の加熱処理工程でも十分に相分離及び拡散が起こるため、省略しても構わない。

【0027】

加えて、本実施形態において、高誘電率ゲート絶縁膜としてシリコン酸化膜やシリコン酸窒化膜よりも誘電率の高い高誘電率絶縁膜を用い、金属元素(例えばHf等)を含有するハフニウム珪酸化膜を用いたが、ハフニウム珪酸窒化膜、ジルコニウム酸化膜、ハフニウム酸化膜、ハフニウムジルコニウム酸化膜、ハフニウムジルコニウム酸化膜等の窒化されにくい、又は窒化されても窒素濃度が低い他のものを用いてもよい。

【0028】

また、本実施形態で用いる基板は、通常のシリコン基板の他にSOI(Silicon On Insulator)基板を用いてもよい。

【0029】

(第2の実施形態)

第2の実施形態は、第1の実施形態において、SiO2膜5を形成するのに先駆けて、PMOS領域にエピタキシャル成長等によりシリコンゲルマニウム(SiGe)層を形成したものである。なお、本実施形態は、前記第1の実施形態とSiGe層を形成する点以外は同じであるので第1の実施形態における構成と同様の部分には同じ符号を付してその説明は省略する。

【0030】

図4(a)に示すように、SiO2膜5を形成する前にSiGe層21を形成する。この後の工程においては第1の実施形態と同様であり、図4(b)に示すように、ゲート電極16を形成した後、ゲート電極16をマスクにしてシリコン基板1に導電型不純物のイオン注入と活性化アニールを行い、ソース・ドレイン拡散層20を形成する。

【0031】

SiGe層21を形成することによって通常のシリコンチャネルのトランジスタよりも低しきい値電圧(Vth)を実現することができる。SiGe層21の代わりに、MOCVD(Metal Organic Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法を用いてAl2O3層やAlN層を形成しても構わない。また、SiGe層を形成してからAl2O3層やAlN層を形成しても良い。

【0032】

上記した本実施形態によれば、前記した第1の実施形態の効果に加え、次のような効果が得られる。すなわち、PMOS領域にSiGe層を形成することによって第1の実施形態と比較して低しきい値を有するCMOSFETを実現することが可能となる。

【0033】

(第3の実施形態)

図5及び図6は本発明の第3の実施形態に係るCMOSFETを有する半導体装置の製造工程を示す断面図である。

【0034】

はじめに、図5(a)に示すように、シリコン基板22の主面上に既知の方法でPMOS領域及びNMOS領域を区画するためのSTI構造の素子分離領域23を形成する。その後、既知の方法によってNMOS領域であるPウェル拡散層24及びPMOS領域であるNウェル拡散層25を形成する。

【0035】

次に、図5(b)に示すように、酸素雰囲気中における加熱処理等によりシリコン基板22の主面を酸化させ、PMOS領域及びNMOS領域にシリコン酸化(SiO2)膜26を形成する。

【0036】

図5(c)に示すように、SiO2膜26の形成に続いて、SiO2膜26上に高誘電率ゲート絶縁膜27としてHfSiON膜をMOCVD法等により堆積する。HfSiON膜27の窒素濃度は後述するLa元素の拡散を完全にブロックしない範囲で任意に変化させて実施することができる。

【0037】

その後、図5(d)に示すように、フォトリソグラフィー法等を用いてNMOS領域をレジスト28でマスクし、図5(e)に示すように、例えば、プラズマ窒化法によって、PMOS領域のHfSiON膜27を窒化する。これにより、PMOS領域のHfSiON膜27は窒化HfSiON膜29に置換され、NMOS領域はレジスト28で覆われているためHfSiON膜27がそのまま残った状態となる。窒化HfSiON膜29はHfSiON膜27よりも高い窒素濃度を有する。

【0038】

なお、レジスト28は有機物であり、プラズマ窒化を行うことにより特性があまり変化しないと考えられるので、レジスト28の除去に悪影響を及ぼすことは少ない。

【0039】

次に、図6(a)に示すように、有機溶剤等でレジスト28を除去し、NMOS領域のHfSiON膜27及びPMOS領域の窒化HfSiON膜29上にキャップ膜としてのLa膜を形成する。このLa膜はNMOSFETのしきい値Vthを低くするために形成される。キャップ膜として、ランタンの代わりに、イットリウム、テルビウム、エルビウム、イッテルビウム、マグネシウム、イットリウム、スカンジウム、その他ランタノイド、アクチノイド、アルカリ土類金属、希土類金属のいずれかを用いてもよい。通常、La膜は工程中で少し酸化され、少量の酸素を含むLa(O)膜30となった状態で存在する。また、ランタンの代わりにマグネシウムを用いた場合も同様に少し酸化された状態で存在すると考えられる。

【0040】

続いて、図6(b)に示すように、La(O)膜30の上にメタル電極としてW膜31、さらにそのW膜31上にバリアメタル32としてのTiN膜を形成する。TiN膜32形成後、加熱工程を行うことによってNMOS領域においては、La(O)膜30に含まれるLa元素はシリコン基板22とSiO2膜26の界面近くまで拡散するが、PMOS領域においては、窒化されたHfSiON膜29がLa元素の拡散をブロックするため、シリコン基板22の界面方向にはLa元素は拡散しない。

【0041】

その後、図6(c)に示すように、ゲート材料として多結晶シリコン膜33をTiN膜32上に堆積し、多結晶シリコン膜33にイオン注入を行った後、フォトリソグラフィー法により、多結晶シリコン膜33、TiN膜32、W膜31を順にエッチングしてゲート電極34を形成する。さらに、このゲート電極34をマスクにして、La(O)膜30、窒化HfSiON膜29又はHfSiON膜27、SiO2膜26を順にエッチングしてゲート絶縁膜35を形成する。この時、必要に応じてエクステンションイオン注入と結晶回復のアニールを行ってもよい。

【0042】

ここで、PMOS領域のLa(O)膜30は、ゲート構造の一部としてそのまま存在しているが、デバイス特性に悪影響を及ぼすようなことはないため、存在していても構わない。

【0043】

次に、図6(d)に示すように、SiNからなるライナー膜をシリコン基板22の上面全面に堆積した後、そのSiN膜上に、TEOS(Tetraethoxysilane)を堆積し、異方性エッチングにより、TEOS及びSiN膜をエッチングしてゲート側壁となるSiN膜36及びTEOS膜37を形成する。続いてゲート電極34をマスクにしてイオン注入と活性化アニールを行い、ソース・ドレイン拡散層38を形成する。

【0044】

上記した本実施形態によれば、次のような効果が得られる。すなわち、PMOS領域及びNMOS領域上にHfSiON膜27を形成した後、窒化処理してNMOS領域上のHfSiON27はそのままにして、PMOS領域上のHfSiON膜を高窒素濃度の窒化HfSiON膜29に置換する。これにより、NMOS領域においては、La(O)膜30に含まれるLa元素はシリコン基板22とSiO2膜26との界面近くまで拡散するが、PMOS領域においては、窒化HfSiON膜29がLa元素の拡散をブロックするため、シリコン基板22とSiO2膜26との界面方向にはLa元素は拡散しない。そのため、製造工程数の増加を抑え、NMOSFET、PMOSFETそれぞれに適したメタル電極を形成することができる。

【0045】

また、本実施形態では、PMOS領域上の高誘電率ゲート絶縁膜であるHfSiO膜を直接、選択的に窒化することにより、PMOS領域においては、La元素の拡散をブロックしているため、第1の実施形態と比べてさらに製造工程数を低減することができる。

【0046】

本実施形態では、メタル電極にW膜31を用い、メタル電極の上に形成される多結晶シリコン膜33とW膜31の反応を防止するためにバリアメタル32としてTiN膜を形成した。メタル電極はTa等の遷移金属類、それらのシリサイド、窒化物、炭化物等を用いてもよく、多結晶シリコン膜33と反応しない組み合わせであれば、バリアメタル32を形成しなくても構わない。また、バリアメタル32はTiNに限らず、TaCやRu等のメタル電極と多結晶シリコンの反応を防止できるものであれば他のものを用いても構わない。

【0047】

なお、本実施形態では、La元素をシリコン基板とゲート絶縁膜との界面付近まで拡散させるため、図6(b)に示す工程において加熱処理を行ったが、ソース及びドレイン拡散層形成時の加熱処理工程でも十分に相分離及び拡散が起こるため、省略しても構わない。

【0048】

加えて、本実施形態において、高誘電率ゲート絶縁膜27にハフニウム珪酸窒化膜を用いたが、ハフニウム珪酸化膜、ジルコニウム珪酸化膜、ジルコニウム珪酸窒化膜、ハフニウムジルコニウム珪酸化膜、ハフニウムジルコニウム珪酸窒化膜等の窒化を行うことによりキャップ膜の拡散を防止可能な窒素濃度を実現可能なものであれば、他のものを用いてもよい。

【0049】

また、本実施形態で用いる基板は、通常のシリコン基板の他にSOI(Silicon On Insulator)基板を用いてもよい。

【0050】

(第4の実施形態)

第4の実施形態は、第3の実施形態において、SiO2膜26を形成するのに先駆けて、PMOS領域にエピタキシャル成長等によりSiGe層を形成したものである。なお、本実施形態は、前記第3の実施形態とSiGe層を形成する点以外は同じであるので第3の実施形態における構成と同様の部分には同じ符号を付してその説明は省略する。

【0051】

図7(a)に示すように、SiO2膜26を形成する前にSiGe層39を形成する。この後の工程においては第3の実施形態と同様であり、図7(b)に示すように、ゲート電極34を形成した後、ゲート電極34をマスクにしてシリコン基板22に導電型不純物のイオン注入と活性化アニールを行い、ソース・ドレイン拡散層38を形成する。

【0052】

SiGe層39を形成することによって通常のシリコンチャネルのトランジスタよりも低しきい値電圧(Vth)を実現することができる。SiGe層の代わりに、MOCVD(Metal Organic Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法を用いてAl2O3層やAlN層を形成しても構わない。また、SiGe層を形成してからAl2O3層やAlN層を形成しても良い。

【0053】

上記した本実施形態によれば、前記した第3の実施形態の効果に加え、次のような効果が得られる。すなわち、PMOS領域にSiGe層を形成することによって第3の実施形態と比較して低しきい値を有するCMOSFETを実現することが可能となる。

【0054】

(第5の実施形態)

続いて、本発明の第5の実施形態に係る半導体装置の製造方法の説明を行う。図8及び図9は本発明の第5の実施形態に係る半導体装置の製造方法を示す断面図である。図8及び図9を用いて製造工程について以下に説明する。

【0055】

はじめに、図8(a)に示すように、シリコン基板40の主面上に既知の方法でPMOS領域及びNMOS領域を区画するためのSTI構造の素子分離領域41を形成する。その後、既知の方法によってNMOS領域であるPウェル拡散層42及びPMOS領域であるNウェル拡散層43を形成する。

【0056】

次に、図8(b)に示すように、酸素雰囲気中における加熱処理等によりシリコン基板40の主面を酸化させ、PMOS領域及びNMOS領域にシリコン酸化(SiO2)膜44を形成する。

【0057】

SiO2膜44の形成に続いて、図8(c)に示すように、SiO2膜44上に高誘電率ゲート絶縁膜としてハフニウム珪酸化膜(HfSiO)膜をMOCVD法等により堆積する。SiO2膜44上に堆積したHfSiO膜に対して窒化、アニールの工程を経て、ハフニウム珪酸窒化(HfSiON)膜45を形成する。HfSiON膜45の窒素濃度は後述するLa元素の拡散を完全にブロックしない範囲で任意に変化させて実施することができる。また、HfSiO膜の窒化ではなく、MOCVD法等によりSiO2膜44上に直接HfSiON膜を堆積しても構わない。

【0058】

続いてHfSiON膜45の上にALD法やCVD法等を用いて非常に薄いシリコン窒化(SiN)膜46を形成する。このSiN膜46の厚さは、後述するランタン元素の拡散を防止できる厚さ、具体的には0.5nm〜1.0nm程度あればよい。また、デバイスの特性に影響を与えない程度の厚さであれば、それよりも厚く形成しても構わない。

【0059】

その後、図8(d)に示すように、フォトリソグラフィー法等を用いてPMOS領域をレジスト47でマスクし、図8(e)に示すように、例えば、リン酸を用いた選択エッチング等によりNMOS領域のSiN膜46を除去する。

【0060】

次に、図9(a)に示すように、有機溶剤等でレジスト47を除去し、NMOS領域のHfSiON膜45及びPMOS領域のSiN膜46上にキャップ膜としてのランタン酸化(La2O3)膜48を形成する。このLa2O3膜はNMOSFETのしきい値Vthを低くするために形成される。La2O3膜の代わりにランタン膜を形成しても構わない。また、ランタン膜の代わりに、イットリウム、テルビウム、エルビウム、イッテルビウム、マグネシウム、イットリウム、スカンジウム、その他ランタノイド、アクチノイド、アルカリ土類金属、希土類金属のいずれかを用いてもよい。その場合には通常、La膜は工程中で少し酸化され、少量の酸素を含むLa(O)膜となった状態で存在する。また、ランタンの代わりにマグネシウムを用いた場合も同様に少し酸化された状態で存在すると考えられる。

【0061】

続いて、図9(b)に示すように、La2O3膜48の上にメタル電極としてW膜49、さらにそのW膜49上にバリアメタル50としてのTiN膜を形成する。TiN膜50形成後、加熱工程を行うことによってNMOS領域においては、La2O3膜48に含まれるLa元素はシリコン基板40とSiO2膜44の界面近くまで拡散するが、PMOS領域においては、SiN膜46がLa元素の拡散をブロックするため、シリコン基板40の界面方向にはLa元素は拡散しない。

【0062】

その後、図9(c)に示すように、ゲート材料として多結晶シリコン膜51をTiN膜50上に堆積し、多結晶シリコン膜51にイオン注入を行った後、フォトリソグラフィー法により、多結晶シリコン膜51、TiN膜50、W膜49を順にエッチングしてゲート電極52を形成する。さらに、このゲート電極52をマスクにして、La2O3膜48、SiN膜46、HfSiON膜45、SiO2膜44を順にエッチングしてゲート絶縁膜53を形成する。この時、必要に応じてエクステンションイオン注入と結晶回復のアニールを行ってもよい。

【0063】

次に、図9(d)に示すように、SiNからなるライナー膜をシリコン基板40の上面全面に堆積した後、そのSiN膜上に、TEOS(Tetraethoxysilane)を堆積し、異方性エッチングにより、TEOS及びSiN膜をエッチングしてゲート側壁となるSiN膜54及びTEOS膜55を形成する。続いてゲート電極52をマスクにしてイオン注入と活性化アニールを行い、ソース・ドレイン拡散層56を形成する。

【0064】

上記した本実施形態によれば、次のような効果が得られる。すなわち、PMOS領域上にSiN膜46を形成する。これにより、NMOS領域においては、La2O3膜48に含まれるLa元素はシリコン基板40とSiO2膜44との界面近くまで拡散するが、PMOS領域においては、SiN膜46がLa元素の拡散をブロックするため、シリコン基板40とSiO2膜44との界面方向にはLa元素は拡散しない。そのため、製造工程数の増加を抑え、NMOSFET、PMOSFETそれぞれに適したメタル電極を形成することができる。

【0065】

また、上記した第1の実施形態では、シリコン膜7がNMOS領域上に残存するため、W膜12と反応してシリサイド電極14を形成するが、本実施形態ではW膜をシリサイド化させずに電極として用いることができるため、より高速な動作を実現することができる。加えて、第1乃至第4の実施形態と比較して、レジスト膜を窒化する工程がないため、窒化したレジスト膜と比較して、容易にレジスト膜を剥離することができると考えられる。

【0066】

本実施形態では、メタル電極にW膜49を用い、メタル電極の上に形成される多結晶シリコン膜51とW膜49の反応を防止するためにバリアメタル50としてTiN膜を形成した。メタル電極はTa等の遷移金属類、それらのシリサイド、窒化物、炭化物等を用いてもよく、多結晶シリコン膜51と反応しない組み合わせであれば、バリアメタル50を形成しなくても構わない。また、バリアメタル50はTiNに限らず、TaCやRu等のメタル電極と多結晶シリコンの反応を防止できるものであれば他のものを用いても構わない。

【0067】

なお、本実施形態では、La元素をシリコン基板とゲート絶縁膜との界面付近まで拡散させるため、図9(b)に示す工程において加熱処理を行ったが、ソース及びドレイン拡散層形成時の加熱処理工程でも十分に相分離及び拡散が起こるため、省略しても構わない。

【0068】

加えて、本実施形態において、高誘電率ゲート絶縁膜45にハフニウム珪酸窒化膜を用いたが、ハフニウム珪酸化膜、ジルコニウム珪酸化膜、ジルコニウム珪酸窒化膜、ハフニウムジルコニウム珪酸化膜、ハフニウムジルコニウム珪酸窒化膜等の窒化を行うことによりキャップ膜の拡散を防止可能な窒素濃度を実現可能なものであれば、他のものを用いてもよい。

【0069】

また、本実施形態で用いる基板は、通常のシリコン基板の他にSOI(Silicon On Insulator)基板を用いてもよい。

【0070】

(第6の実施形態)

第6の実施形態は、第5の実施形態において、SiO2膜44を形成するのに先駆けて、PMOS領域にエピタキシャル成長等によりSiGe層を形成したものである。なお、本実施形態は、前記第5の実施形態とSiGe層を形成する点以外は同じであるので第5の実施形態における構成と同様の部分には同じ符号を付してその説明は省略する。

【0071】

図10(a)に示すように、SiO2膜44を形成する前にSiGe層57を形成する。この後の工程においては第5の実施形態と同様であり、図10(b)に示すように、ゲート電極52を形成した後、ゲート電極52をマスクにしてシリコン基板40に導電型不純物のイオン注入と活性化アニールを行い、ソース・ドレイン拡散層56を形成する。

【0072】

SiGe層57を形成することによって通常のシリコンチャネルのトランジスタよりも低しきい値電圧(Vth)を実現することができる。SiGe層の代わりに、MOCVD法やALD法を用いてAl2O3層やAlN層を形成しても構わない。また、SiGe層を形成してからAl2O3層やAlN層を形成しても良い。

【0073】

上記した本実施形態によれば、前記した第5の実施形態の効果に加え、次のような効果が得られる。すなわち、PMOS領域にSiGe層を形成することによって第5の実施形態と比較して低しきい値を有するCMOSFETを実現することが可能となる。

【0074】

本発明は上記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲で種々に変形して実施することができる。

【図面の簡単な説明】

【0075】

【図1】本発明の第1の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図2】本発明の第1の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図3】本発明の第1の実施形態に係る反応におけるギブスの自由エネルギーの差分特性を示した断面図。

【図4】本発明の第2の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図5】本発明の第3の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図6】本発明の第3の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図7】本発明の第4の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図8】本発明の第5の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図9】本発明の第5の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【図10】本発明の第6の実施形態に係る半導体装置の製造方法の一部を模式的に示した断面図。

【符号の説明】

【0076】

1、22、40 シリコン基板

2、23、41 素子分離領域(STI)

3、24、42 Pウェル拡散層

4、25、43 Nウェル拡散層

5、26、44 シリコン酸化膜

6、27、45 高誘電率ゲート絶縁膜

7 シリコン膜

8、28、47 レジスト

9、18、36、46、54 SiN膜

10、23 HfSiON膜

11、30 La(O)膜

12、31、49 W膜

13、32、50 バリアメタル

14 WSi膜

15、33、51 ドープト多結晶シリコン膜

16、34、52 ゲート電極

17、35、53 ゲート絶縁膜

19、37、55 TEOS膜

20、38、56 ソース・ドレイン拡散層

21、39、57 SiGe層

29 窒化HfSiON膜

48 La2O3膜

【特許請求の範囲】

【請求項1】

基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、

前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、

前記高誘電率ゲート絶縁膜上にシリコン膜を形成する工程と、

前記N型半導体領域上の前記シリコン膜を窒化して窒化シリコン膜に置換する工程と、

前記P型半導体領域の前記シリコン膜上及び前記N型半導体領域の前記窒化シリコン膜上にキャップ膜を介してメタルゲート電極を形成する工程と、

前記キャップ膜の構成元素を前記N型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項2】

前記高誘電率ゲート絶縁膜が、ハフニウム又はジルコニウムの少なくともどちらか一方を含有することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記N型半導体領域上の前記高誘電率ゲート絶縁膜の下部に、SiGe、Al2O3、またはAlNのいずれかの単層、或いはそれらの積層を形成する工程をさらに備えることを特徴とする請求項2記載の半導体装置の製造方法。

【請求項4】

基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、

前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、

前記N型半導体領域上の前記高誘電率ゲート絶縁膜を窒化して窒化高誘電率ゲート絶縁膜に置換する工程と、

前記P型半導体領域の前記高誘電率ゲート絶縁膜上及び前記N型半導体領域の前記窒化高誘電率ゲート絶縁膜上にキャップ膜を介してメタルゲート電極を形成する工程と、

前記キャップ膜の構成元素を前記P型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項5】

前記高誘電率ゲート絶縁膜が、ハフニウム又はジルコニウムの少なくともどちらか一方を含有することを特徴とする請求項4記載の半導体装置の製造方法。

【請求項6】

基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、

前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、

前記N型半導体領域上の前記高誘電率ゲート絶縁膜上にシリコン窒化膜を形成する工程と、

前記P型半導体領域の前記高誘電率ゲート絶縁膜上及び前記N型半導体領域の前記シリコン窒化膜上にキャップ膜を介してメタルゲート電極を形成する工程と、

前記キャップ膜の構成元素を前記P型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項1】

基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、

前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、

前記高誘電率ゲート絶縁膜上にシリコン膜を形成する工程と、

前記N型半導体領域上の前記シリコン膜を窒化して窒化シリコン膜に置換する工程と、

前記P型半導体領域の前記シリコン膜上及び前記N型半導体領域の前記窒化シリコン膜上にキャップ膜を介してメタルゲート電極を形成する工程と、

前記キャップ膜の構成元素を前記N型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項2】

前記高誘電率ゲート絶縁膜が、ハフニウム又はジルコニウムの少なくともどちらか一方を含有することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記N型半導体領域上の前記高誘電率ゲート絶縁膜の下部に、SiGe、Al2O3、またはAlNのいずれかの単層、或いはそれらの積層を形成する工程をさらに備えることを特徴とする請求項2記載の半導体装置の製造方法。

【請求項4】

基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、

前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、

前記N型半導体領域上の前記高誘電率ゲート絶縁膜を窒化して窒化高誘電率ゲート絶縁膜に置換する工程と、

前記P型半導体領域の前記高誘電率ゲート絶縁膜上及び前記N型半導体領域の前記窒化高誘電率ゲート絶縁膜上にキャップ膜を介してメタルゲート電極を形成する工程と、

前記キャップ膜の構成元素を前記P型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項5】

前記高誘電率ゲート絶縁膜が、ハフニウム又はジルコニウムの少なくともどちらか一方を含有することを特徴とする請求項4記載の半導体装置の製造方法。

【請求項6】

基板の主面にN型半導体領域及びP型半導体領域を形成する工程と、

前記N型半導体領域及びP型半導体領域上に高誘電率ゲート絶縁膜を形成する工程と、

前記N型半導体領域上の前記高誘電率ゲート絶縁膜上にシリコン窒化膜を形成する工程と、

前記P型半導体領域の前記高誘電率ゲート絶縁膜上及び前記N型半導体領域の前記シリコン窒化膜上にキャップ膜を介してメタルゲート電極を形成する工程と、

前記キャップ膜の構成元素を前記P型半導体領域の前記高誘電率ゲート絶縁膜中へ導入する加熱工程と、

を備えることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2009−194352(P2009−194352A)

【公開日】平成21年8月27日(2009.8.27)

【国際特許分類】

【出願番号】特願2008−114176(P2008−114176)

【出願日】平成20年4月24日(2008.4.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成21年8月27日(2009.8.27)

【国際特許分類】

【出願日】平成20年4月24日(2008.4.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]