半導体装置の製造方法

【課題】p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】第1および第2領域13、14にゲート絶縁膜17を介して第1金属を含む第1金属膜18を形成する工程と、第1領域13における第1金属膜18を保護膜で被覆し、第2領域14における第1金属膜18を除去してゲート絶縁膜17を露出させる工程と、第1金属膜18上およびゲート絶縁膜17上に第1金属と異なる第2金属を含む第2金属膜19を形成する工程と、ゲート電極パターンを有するマスク材を用いて第2金属膜19を異方性エッチングし、第2領域14に第2ゲート電極を形成する工程と、第1金属膜18および第2金属膜19の露出部に酸化処理を施す工程と、第1領域13における第1金属膜18を異方性エッチングし、第1領域13に第1ゲート電極を形成する工程とを具備する。

【解決手段】第1および第2領域13、14にゲート絶縁膜17を介して第1金属を含む第1金属膜18を形成する工程と、第1領域13における第1金属膜18を保護膜で被覆し、第2領域14における第1金属膜18を除去してゲート絶縁膜17を露出させる工程と、第1金属膜18上およびゲート絶縁膜17上に第1金属と異なる第2金属を含む第2金属膜19を形成する工程と、ゲート電極パターンを有するマスク材を用いて第2金属膜19を異方性エッチングし、第2領域14に第2ゲート電極を形成する工程と、第1金属膜18および第2金属膜19の露出部に酸化処理を施す工程と、第1領域13における第1金属膜18を異方性エッチングし、第1領域13に第1ゲート電極を形成する工程とを具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に係り、特に絶縁ゲート電界効果トランジスタを有する半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の高集積化に伴って、チップサイズの増大を抑制するために絶縁ゲート電界効果トランジスタ(MISトランジスタ)の微細化が求められている。

CMOS半導体装置では、短チャンネル効果を抑制しつつ、従来の閾値電圧を維持するために、金属層を有するゲート電極を備えたp−MISトランジスタとn−MISトランジスタとを同一半導体基板に形成した所謂デュアルゲート構造が用いられている。(例えば、特許文献1参照。)。

【0003】

特許文献1に開示された半導体装置は、第1金属層(Ru)と第2金属層(Hf)が積層されたゲート電極を有するp−MISトランジスタと、第2金属層(Hf)を有するゲート電極を備えたn−MISトランジスタとが、同一半導体基板に形成されたデュアルメタルゲート構造のCMOS半導体装置である。

【0004】

この半導体装置の製造は、半導体基板に、ゲート絶縁膜を介して第1金属層を形成し、n−MISトランジスタ形成領域における第1金属層を除去し、露出したゲート絶縁膜およびp−MISトランジスタ形成領域における第1金属層上に第2金属層を形成する。

【0005】

次に、第2金属層をRIE(Reactive Ion Etching)でエッチングしてn−MISトランジスタのゲート電極を形成し、続いて第1金属層をRIEでエッチングしてp−MISトランジスタのゲート電極を形成することにより行っている。

【0006】

然しながら、金属の種類により、RIEのエッチング速度が異なるため、p−MISトランジスタとn−MISトランジスタとで、得られるゲート電極の寸法や形状にばらつきが生じるという問題がある。

【0007】

その結果、p−MISトランジスタとn−MISトランジスタとに、特性のばらつきが生じ、安定した特性のCMOS半導体装置が得られないという問題がある。

従って、微細化が妨げられるという問題がある。

【特許文献1】特開2006−339210号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明は、p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明の一態様の半導体装置の製造方法では、半導体基板の主面の第1領域および第2領域に、ゲート絶縁膜を介して第1金属を含む第1金属膜を形成する工程と、前記第1領域における前記第1金属膜を保護膜で被覆し、前記第2領域における前記第1金属膜を除去して前記ゲート絶縁膜を露出させる工程と、前記第1領域における前記第1金属膜上、および前記第2領域における前記ゲート絶縁膜上に、前記第1金属と異なる第2金属を含む第2金属膜を形成する工程と、ゲート電極パターンを有するマスク材を用いて、前記第1領域および前記第2領域における前記第2金属膜を異方性エッチングし、前記第2領域に第2ゲート電極を形成する工程と、前記異方性エッチングした後、前記第1金属膜および前記第2金属膜の露出部に酸化処理を施す工程と、前記酸化処理を施した後、前記第1領域における前記第1金属膜を異方性エッチングして、前記第1領域に第1ゲート電極を形成する工程と、を具備することを特徴としている。

【発明の効果】

【0010】

本発明によれば、p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法が得られる。

【発明を実施するための最良の形態】

【0011】

以下、本発明の実施例について図面を参照しながら説明する。

【実施例】

【0012】

本発明の実施例に係る半導体装置の製造方法について、図1乃至図4を用いて説明する。図1は半導体装置を示す断面図、図2乃至図4は半導体装置の製造工程を順に示す断面図である。

【0013】

図1に示すように、本実施例の半導体装置10は、半導体基板11、例えばn型シリコン基板にSTI(Shallow Trench Isolation)12により絶縁分離された第1領域(n型ウェル領域)13および第2領域(p型ウェル領域)14と、第1領域13に形成されたp−MISトランジスタ15と、第2領域14に形成されたn−MISトランジスタ16とを具備している。

【0014】

p−MISトランジスタ15は、半導体基板11にゲート絶縁膜17を介して形成された第1金属を含む第1金属膜18と、第1金属膜18上に形成され、第1金属と異なる第2金属を含む第2金属膜19と、第2金属膜19上に形成されたバリア膜20と、バリア膜20上に形成されたポリシリコン膜21とを有する第1ゲート電極22と、第1ゲート電極22をゲート長方向に挟むように形成されたソース領域23およびドレイン領域24とを具備している。

【0015】

n−MISトランジスタ16は、半導体基板11にゲート絶縁膜17を介して形成された第2金属を含む第2金属膜19と、第2金属膜19上に形成されたバリア膜20と、バリア膜20上に形成されたポリシリコン膜21とを有する第2ゲート電極25と、第2ゲート電極25をゲート長方向に挟むように形成されたソース領域26およびドレイン領域27とを具備している。

【0016】

p−MISトランジスタ15の閾値電圧は第1金属膜18の仕事関数により変調され、n−MISトランジスタ16の閾値電圧は第2金属膜19の仕事関数により変調され、それぞれ所定の値に制御されている。

【0017】

ここで、第1金属を含む第1金属膜18とは、第1金属単体または第1金属の化合物、例えば窒化物、炭化物、硼化物、珪化物などを意味している。

第1金属は、例えばタングステン(W)であり、第1金属膜18は、例えば窒化タングステン(WN)である。

【0018】

同様に、第2金属を含む第2金属膜19とは、第2金属単体または第2金属の化合物、例えば窒化物、炭化物、硼化物、珪化物などを意味している。

第2金属は、例えばタンタル(Ta)であり、第2金属膜19は、例えば炭化タンタル(TaC)である。

【0019】

バリア膜20は、第2金属膜19とポリシリコン膜21が相互拡散してシリサイドを形成すると、第2金属膜19の仕事関数が変化し、n−MISトランジスタ16の閾値電圧が変動するのを防止するために形成されており、例えば窒化チタン(TiN)である。

【0020】

ポリシリコン膜21は、第1ゲート電極22および第2ゲート電極25を低抵抗化し、ゲート配線とのコンタクトを低抵抗化するために形成されている。

【0021】

第1ゲート電極22と第2ゲート電極25は、ゲート電極サイズ、例えばゲート長がそれぞれ30nm、第2金属膜19による高さの違いを除いてゲート高さがそれぞれ130nm程度であり、その形状は略等しく形成されている。

【0022】

これにより、半導体装置10は、第1ゲート電極22と第2ゲート電極25におけるゲート電極形状のばらつきが少ないp−MISトランジスタ15とn−MISトランジスタ16とを具備している。

【0023】

次に、半導体装置10の製造方法について図2乃至図4を用いて説明する。

始めに、周知の方法により、半導体基板11にトレンチを形成し、トレンチ内部に絶縁物を埋め込んでSTI12を形成し、イオン注入法により所定の導電型が与えられ、STI12により電気的に分離された第1領域13および第2領域14を形成する。

但し、図2乃至図4においては、STI12、第1領域13および第2領域14の表示を省略している。

【0024】

次に、図2(a)に示すように、半導体基板11の第1領域13および第2領域14上にゲート絶縁膜17として、例えばCVD(Chemical Vapor Deposition)法により厚さ2nm程度のHfSiON膜あるいはHfO2膜を形成する。

【0025】

次に、ゲート絶縁膜17上に第1金属膜18として、例えばCVD法により厚さ10nm程度の窒化タングステン(WN)膜を形成する。

【0026】

次に、図2(b)に示すように、フォトリソグラフィ法により、第2領域14に開口40aを有するレジスト膜40を形成する。これにより、第1領域13における第1金属膜18がレジスト膜40で被覆される。

【0027】

次に、図2(c)に示すように、例えばCl2、NF3等のガスを用いたRIE法により、第2領域14における第1金属膜18を除去し、ゲート絶縁膜17を露出させる。

【0028】

次に、図3(a)に示すように、レジスト膜40を、例えばアッシャーを用いて除去した後、第1領域13における第1金属膜18上、および第2領域14におけるゲート絶縁膜17上に、第2金属膜19として、例えばCVD法により厚さ10nm程度の炭化タンタル(TaC)膜を形成する。

【0029】

次に、図3(b)に示すように、第2金属膜19上にバリア膜20として、例えばスパッタリング法により厚さ2nm程度の窒化チタン(TiN)膜を形成する。

次に、バリア膜20上に、例えばCVD法により厚さ100nm程度の不純物を添加したポリシリコン膜21を形成する。

【0030】

次に、ポリシリコン膜21上に、マスク材となるシリコン窒化膜41を、例えばプラズマCVD法により厚さ20nm程度形成する。

次に、フォトリソグラフィ法により、第1領域13および第2領域14におけるシリコン窒化膜41上に、ゲート電極パターンを有するレジスト膜42を形成する。

【0031】

次に、図3(c)に示すように、例えばCH2F2、CHF3、Ar、O2等のガス用いたRIE法により、シリコン窒化膜41を異方性エッチングし、ゲート電極パターンをシリコン窒化膜41に転写する。

【0032】

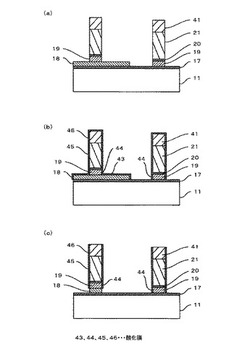

次に、図4(a)に示すように、ゲート電極パターンが転写されたシリコン窒化膜41をマスクとしてRIE法により、ポリシリコン膜21、バリア膜20、第2金属膜19をそれぞれ異方性エッチングする。

これにより、第2金属膜19、バリア膜20、ポリシリコン膜21が積層された第2ゲート電極25が形成される。

【0033】

ポリシリコン膜21のエッチングには、例えばHBr、Cl2、NF3、O2等のガスを用いる。バリア膜20のエッチングには、例えばHBr、Cl2等のガスを用いる。第2金属膜19のエッチングには、例えばCl2、NF3、CF4等のガスを用いる。

【0034】

次に、図4(b)に示すように、例えば酸素プラズマを照射するプラズマ酸化法により、第1金属膜18および第2金属膜19の露出部に酸化処理を施す。

【0035】

ここで、RIE装置から半導体基板11を一旦取り出し、第1金属膜18および第2金属膜19を大気に晒すと、酸化処理結果にばらつきが生じる、且つ処理能力が悪化するので、これを防止するために、RIE装置内で連続して酸化処理することが望ましい。

【0036】

これにより、第1金属膜18の側面および第2金属膜19が積層された領域を除く上面が酸化され、第1金属(W)と酸素(O2)が結合した酸化物(W―O)を含む酸化膜43が形成される。

同様に、第2金属膜19の側面が酸化され、第2金属(Ta)と酸素(O2)が結合した酸化物(Ta―O)を含む酸化膜44が形成される。

【0037】

タンタルと酸素の結合エネルギー(183±15kCal/mol)はタングステンと酸素の結合エネルギー(156±6kCal/mol)より大きいので、第2金属膜19の側面には、第1金属膜18の側面および上面より強固な酸化膜が形成される。

【0038】

同時に、ポリシリコン膜21およびシリコン窒化膜41も酸化されるので、ポリシリコン膜21の側面に酸化膜(シリコン酸化膜)45が形成され、シリコン窒化膜41の側面および上面に酸化膜(シリコン酸窒化膜)46が形成される。

【0039】

次に、図4(c)に示すように、例えばCl2、NF3、CF4等のガスを用いたRIE法により、基板11に高周波バイアス電圧を印加して第1領域13における第1金属膜18を異方性エッチングする。

これにより、第1金属膜18、第2金属膜19、バリア膜20、ポリシリコン膜21が積層された第1ゲート電極22が形成される。

【0040】

このとき、酸化膜44は酸化膜43より強固であること、且つ入射イオンに異方性があることから、第1領域13における第1金属膜18の上面に形成された酸化膜43はエッチングされ易く、第2領域14における第2金属膜19の側面に形成された酸化膜44はエッチングされ難い。

【0041】

その結果、酸化膜44は第2金属膜19の側壁保護膜として機能し、第2金属膜19のサイドエッチングを防止して、第1金属膜18のみをエッチングすることが可能である。従って、ゲート高さを除いて、形状が揃った第1ゲート電極22および第2ゲート電極25が形成される。

【0042】

次に、シリコン窒化膜41を、例えば熱リン酸を用いたウェットエッチングにより除去した後、第1ゲート電極22および第2ゲート電極25に側壁膜(図示せず)を形成し、イオン注入法により、第1領域13および第2領域14にそれぞれ不純物を導入し、第1ゲート電極22をゲート長方向に挟むようにソース領域23およびドレイン領域24を形成し、第2ゲート電極25をゲート長方向に挟むようにソース領域26およびドレイン領域27を形成する。

【0043】

これにより、図1に示す第1ゲート電極22を有するp−MISトランジスタ15および第2ゲート電極25を有するn−MISトランジスタ16を備えた半導体装置10、即ちゲート電極形状のばらつきが少ないデュアルメタルゲート構造のCMOS半導体装置が得られる。

【0044】

図5は本実施例の効果を、比較例と対比して示す図で、図5(a)が本実施例を示す図、図5(b)が比較例を示す図である。

ここで、比較例とは、図4(b)に示す第1金属膜18および第2金属膜19の露出部への酸化処理を施さない場合を意味している。始めに比較例について説明する。

【0045】

図5(b)に示すように、比較例では、第2領域14における第2金属膜19の側壁が露出し、且つ回りにエッチングされるものが無いので、第1領域13における第1金属膜18がエッチングされている間に、第2金属膜19の側壁のサイドエッチングが生じる。

【0046】

第1領域13における第2金属膜19の側壁も露出しているが、第1金属膜18のエッチングが優先的に進むため、第1領域13における第2金属膜19の側壁のサイドエッチングはおこりづらい。

【0047】

一方、図5(a)に示すように、本実施例では、上述したように第2領域14における第2金属膜19の側壁に強固な酸化膜44が形成されているので、第1領域13における第1金属膜18がエッチングされている間に、第2金属膜19の側壁のサイドエッチングは生じない。

【0048】

第1領域13における第1金属膜18の側面および上面の酸化膜43は、エッチングされるので、第1金属膜18のエッチングに支障をきたさない。

【0049】

以上説明したように、本実施例の半導体装置の製造方法は、第2金属膜19を異方性エッチングした後に、第1金属膜18および第2金属膜19の露出部に酸化処理を施す工程を具備している。

【0050】

その結果、第2領域14における第2金属膜19の側壁に強固な酸化膜44が形成されるので、第1領域13における第1金属膜18がエッチングされている間に、第2金属膜19の側壁がサイドエッチングされることを防止できる。

【0051】

従って、p−MISトランジスタ15とn−MISトランジスタ16とのゲート電極形状のばらつきが少ない半導体装置10が得られる。

【0052】

ここでは、第1金属がタングステン(W)、第1金属膜が窒化タングステン(WN)、第2金属がタンタル(Ta)、第2金属膜が炭化タンタル(TaC)である場合について説明したが、第1金属と酸素の結合エネルギーが第2金属と酸素の結合エネルギーより小さい条件を満たす他の金属および導電性を有するその金属化合物であっても構わない。

【0053】

例えば、図6に示すように、第1金属としてチタン(Ti)を用いることができる。チタンと酸素の結合エネルギーは、158±5kCal/mol程度である。

【0054】

第1金属膜18として、炭化タングステン(WC)、タングステンシリサイド(WSi)、白金タングステンシリサイド(PtWSi)、窒化チタン(TiN)、炭化チタン(TiC)、硼化チタン(TiB)、窒化アルミニウムチタン(TiAlN)などを用いることができる。

【0055】

第2金属として、ハフニウム(Hf)を用いることができる。ハフニウムと酸素の結合エネルギーは、185±10kCal/mol程度である。また、金属ではないが、半導体のポリシリコンを用いることも可能である。ポリシリコンと酸素の結合エネルギーは、184±3kCal/mol程度である。

【0056】

第2金属膜19として、窒化タンタル(TaN)、2窒化タンタル(Ta2N)硼化タンタル(TaB)、珪窒化タンタル(TaSiN)、窒化アルミニウムタンタル(TaAlN)、タンタルチタン(TaTi)、窒化ハフニウムアルミニウム(HfAlN)などを用いることができる。

【0057】

更に、硼化ハフニウム(HfB)、ハフニウムシリサイド(HfSi2)、ニッケルシリサイド(NiSi)、硼素添加ニッケルシリサイド(NiSi(B))、砒素添加ニッケルシリサイド(NiSi(As))などを、第1または第2金属膜として使用することができる可能性がある。

【図面の簡単な説明】

【0058】

【図1】本発明の実施例に係る半導体装置を示す断面図。

【図2】本発明の実施例に係る半導体装置の製造工程を順に示す断面図。

【図3】本発明の実施例に係る半導体装置の製造工程を順に示す断面図。

【図4】本発明の実施例に係る半導体装置の製造工程を順に示す断面図。

【図5】本発明の実施例に係る効果を比較例と対比して示す図で、図5(a)が本実施例を示す図、図5(b)が比較例を示す図。

【図6】本発明の実施例に係る他の第1金属、第1金属膜、第2金属および第2金属膜を示す図。

【符号の説明】

【0059】

10 半導体装置

11 半導体基板

12 STI

13 第1領域

14 第2領域

15 p−MISトランジスタ

16 n−MISトランジスタ

17 ゲート絶縁膜

18 第1金属膜

19 第2金属膜

20 バリア膜

21 ポリシリコン膜

22 第1ゲート電極

23、26 ソース領域

24、27 ドレイン領域

25 第2ゲート電極

40、42 レジスト膜

40a 開口

41 シリコン窒化膜

43、44、45、46 酸化膜

【技術分野】

【0001】

本発明は、半導体装置の製造方法に係り、特に絶縁ゲート電界効果トランジスタを有する半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の高集積化に伴って、チップサイズの増大を抑制するために絶縁ゲート電界効果トランジスタ(MISトランジスタ)の微細化が求められている。

CMOS半導体装置では、短チャンネル効果を抑制しつつ、従来の閾値電圧を維持するために、金属層を有するゲート電極を備えたp−MISトランジスタとn−MISトランジスタとを同一半導体基板に形成した所謂デュアルゲート構造が用いられている。(例えば、特許文献1参照。)。

【0003】

特許文献1に開示された半導体装置は、第1金属層(Ru)と第2金属層(Hf)が積層されたゲート電極を有するp−MISトランジスタと、第2金属層(Hf)を有するゲート電極を備えたn−MISトランジスタとが、同一半導体基板に形成されたデュアルメタルゲート構造のCMOS半導体装置である。

【0004】

この半導体装置の製造は、半導体基板に、ゲート絶縁膜を介して第1金属層を形成し、n−MISトランジスタ形成領域における第1金属層を除去し、露出したゲート絶縁膜およびp−MISトランジスタ形成領域における第1金属層上に第2金属層を形成する。

【0005】

次に、第2金属層をRIE(Reactive Ion Etching)でエッチングしてn−MISトランジスタのゲート電極を形成し、続いて第1金属層をRIEでエッチングしてp−MISトランジスタのゲート電極を形成することにより行っている。

【0006】

然しながら、金属の種類により、RIEのエッチング速度が異なるため、p−MISトランジスタとn−MISトランジスタとで、得られるゲート電極の寸法や形状にばらつきが生じるという問題がある。

【0007】

その結果、p−MISトランジスタとn−MISトランジスタとに、特性のばらつきが生じ、安定した特性のCMOS半導体装置が得られないという問題がある。

従って、微細化が妨げられるという問題がある。

【特許文献1】特開2006−339210号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明は、p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明の一態様の半導体装置の製造方法では、半導体基板の主面の第1領域および第2領域に、ゲート絶縁膜を介して第1金属を含む第1金属膜を形成する工程と、前記第1領域における前記第1金属膜を保護膜で被覆し、前記第2領域における前記第1金属膜を除去して前記ゲート絶縁膜を露出させる工程と、前記第1領域における前記第1金属膜上、および前記第2領域における前記ゲート絶縁膜上に、前記第1金属と異なる第2金属を含む第2金属膜を形成する工程と、ゲート電極パターンを有するマスク材を用いて、前記第1領域および前記第2領域における前記第2金属膜を異方性エッチングし、前記第2領域に第2ゲート電極を形成する工程と、前記異方性エッチングした後、前記第1金属膜および前記第2金属膜の露出部に酸化処理を施す工程と、前記酸化処理を施した後、前記第1領域における前記第1金属膜を異方性エッチングして、前記第1領域に第1ゲート電極を形成する工程と、を具備することを特徴としている。

【発明の効果】

【0010】

本発明によれば、p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法が得られる。

【発明を実施するための最良の形態】

【0011】

以下、本発明の実施例について図面を参照しながら説明する。

【実施例】

【0012】

本発明の実施例に係る半導体装置の製造方法について、図1乃至図4を用いて説明する。図1は半導体装置を示す断面図、図2乃至図4は半導体装置の製造工程を順に示す断面図である。

【0013】

図1に示すように、本実施例の半導体装置10は、半導体基板11、例えばn型シリコン基板にSTI(Shallow Trench Isolation)12により絶縁分離された第1領域(n型ウェル領域)13および第2領域(p型ウェル領域)14と、第1領域13に形成されたp−MISトランジスタ15と、第2領域14に形成されたn−MISトランジスタ16とを具備している。

【0014】

p−MISトランジスタ15は、半導体基板11にゲート絶縁膜17を介して形成された第1金属を含む第1金属膜18と、第1金属膜18上に形成され、第1金属と異なる第2金属を含む第2金属膜19と、第2金属膜19上に形成されたバリア膜20と、バリア膜20上に形成されたポリシリコン膜21とを有する第1ゲート電極22と、第1ゲート電極22をゲート長方向に挟むように形成されたソース領域23およびドレイン領域24とを具備している。

【0015】

n−MISトランジスタ16は、半導体基板11にゲート絶縁膜17を介して形成された第2金属を含む第2金属膜19と、第2金属膜19上に形成されたバリア膜20と、バリア膜20上に形成されたポリシリコン膜21とを有する第2ゲート電極25と、第2ゲート電極25をゲート長方向に挟むように形成されたソース領域26およびドレイン領域27とを具備している。

【0016】

p−MISトランジスタ15の閾値電圧は第1金属膜18の仕事関数により変調され、n−MISトランジスタ16の閾値電圧は第2金属膜19の仕事関数により変調され、それぞれ所定の値に制御されている。

【0017】

ここで、第1金属を含む第1金属膜18とは、第1金属単体または第1金属の化合物、例えば窒化物、炭化物、硼化物、珪化物などを意味している。

第1金属は、例えばタングステン(W)であり、第1金属膜18は、例えば窒化タングステン(WN)である。

【0018】

同様に、第2金属を含む第2金属膜19とは、第2金属単体または第2金属の化合物、例えば窒化物、炭化物、硼化物、珪化物などを意味している。

第2金属は、例えばタンタル(Ta)であり、第2金属膜19は、例えば炭化タンタル(TaC)である。

【0019】

バリア膜20は、第2金属膜19とポリシリコン膜21が相互拡散してシリサイドを形成すると、第2金属膜19の仕事関数が変化し、n−MISトランジスタ16の閾値電圧が変動するのを防止するために形成されており、例えば窒化チタン(TiN)である。

【0020】

ポリシリコン膜21は、第1ゲート電極22および第2ゲート電極25を低抵抗化し、ゲート配線とのコンタクトを低抵抗化するために形成されている。

【0021】

第1ゲート電極22と第2ゲート電極25は、ゲート電極サイズ、例えばゲート長がそれぞれ30nm、第2金属膜19による高さの違いを除いてゲート高さがそれぞれ130nm程度であり、その形状は略等しく形成されている。

【0022】

これにより、半導体装置10は、第1ゲート電極22と第2ゲート電極25におけるゲート電極形状のばらつきが少ないp−MISトランジスタ15とn−MISトランジスタ16とを具備している。

【0023】

次に、半導体装置10の製造方法について図2乃至図4を用いて説明する。

始めに、周知の方法により、半導体基板11にトレンチを形成し、トレンチ内部に絶縁物を埋め込んでSTI12を形成し、イオン注入法により所定の導電型が与えられ、STI12により電気的に分離された第1領域13および第2領域14を形成する。

但し、図2乃至図4においては、STI12、第1領域13および第2領域14の表示を省略している。

【0024】

次に、図2(a)に示すように、半導体基板11の第1領域13および第2領域14上にゲート絶縁膜17として、例えばCVD(Chemical Vapor Deposition)法により厚さ2nm程度のHfSiON膜あるいはHfO2膜を形成する。

【0025】

次に、ゲート絶縁膜17上に第1金属膜18として、例えばCVD法により厚さ10nm程度の窒化タングステン(WN)膜を形成する。

【0026】

次に、図2(b)に示すように、フォトリソグラフィ法により、第2領域14に開口40aを有するレジスト膜40を形成する。これにより、第1領域13における第1金属膜18がレジスト膜40で被覆される。

【0027】

次に、図2(c)に示すように、例えばCl2、NF3等のガスを用いたRIE法により、第2領域14における第1金属膜18を除去し、ゲート絶縁膜17を露出させる。

【0028】

次に、図3(a)に示すように、レジスト膜40を、例えばアッシャーを用いて除去した後、第1領域13における第1金属膜18上、および第2領域14におけるゲート絶縁膜17上に、第2金属膜19として、例えばCVD法により厚さ10nm程度の炭化タンタル(TaC)膜を形成する。

【0029】

次に、図3(b)に示すように、第2金属膜19上にバリア膜20として、例えばスパッタリング法により厚さ2nm程度の窒化チタン(TiN)膜を形成する。

次に、バリア膜20上に、例えばCVD法により厚さ100nm程度の不純物を添加したポリシリコン膜21を形成する。

【0030】

次に、ポリシリコン膜21上に、マスク材となるシリコン窒化膜41を、例えばプラズマCVD法により厚さ20nm程度形成する。

次に、フォトリソグラフィ法により、第1領域13および第2領域14におけるシリコン窒化膜41上に、ゲート電極パターンを有するレジスト膜42を形成する。

【0031】

次に、図3(c)に示すように、例えばCH2F2、CHF3、Ar、O2等のガス用いたRIE法により、シリコン窒化膜41を異方性エッチングし、ゲート電極パターンをシリコン窒化膜41に転写する。

【0032】

次に、図4(a)に示すように、ゲート電極パターンが転写されたシリコン窒化膜41をマスクとしてRIE法により、ポリシリコン膜21、バリア膜20、第2金属膜19をそれぞれ異方性エッチングする。

これにより、第2金属膜19、バリア膜20、ポリシリコン膜21が積層された第2ゲート電極25が形成される。

【0033】

ポリシリコン膜21のエッチングには、例えばHBr、Cl2、NF3、O2等のガスを用いる。バリア膜20のエッチングには、例えばHBr、Cl2等のガスを用いる。第2金属膜19のエッチングには、例えばCl2、NF3、CF4等のガスを用いる。

【0034】

次に、図4(b)に示すように、例えば酸素プラズマを照射するプラズマ酸化法により、第1金属膜18および第2金属膜19の露出部に酸化処理を施す。

【0035】

ここで、RIE装置から半導体基板11を一旦取り出し、第1金属膜18および第2金属膜19を大気に晒すと、酸化処理結果にばらつきが生じる、且つ処理能力が悪化するので、これを防止するために、RIE装置内で連続して酸化処理することが望ましい。

【0036】

これにより、第1金属膜18の側面および第2金属膜19が積層された領域を除く上面が酸化され、第1金属(W)と酸素(O2)が結合した酸化物(W―O)を含む酸化膜43が形成される。

同様に、第2金属膜19の側面が酸化され、第2金属(Ta)と酸素(O2)が結合した酸化物(Ta―O)を含む酸化膜44が形成される。

【0037】

タンタルと酸素の結合エネルギー(183±15kCal/mol)はタングステンと酸素の結合エネルギー(156±6kCal/mol)より大きいので、第2金属膜19の側面には、第1金属膜18の側面および上面より強固な酸化膜が形成される。

【0038】

同時に、ポリシリコン膜21およびシリコン窒化膜41も酸化されるので、ポリシリコン膜21の側面に酸化膜(シリコン酸化膜)45が形成され、シリコン窒化膜41の側面および上面に酸化膜(シリコン酸窒化膜)46が形成される。

【0039】

次に、図4(c)に示すように、例えばCl2、NF3、CF4等のガスを用いたRIE法により、基板11に高周波バイアス電圧を印加して第1領域13における第1金属膜18を異方性エッチングする。

これにより、第1金属膜18、第2金属膜19、バリア膜20、ポリシリコン膜21が積層された第1ゲート電極22が形成される。

【0040】

このとき、酸化膜44は酸化膜43より強固であること、且つ入射イオンに異方性があることから、第1領域13における第1金属膜18の上面に形成された酸化膜43はエッチングされ易く、第2領域14における第2金属膜19の側面に形成された酸化膜44はエッチングされ難い。

【0041】

その結果、酸化膜44は第2金属膜19の側壁保護膜として機能し、第2金属膜19のサイドエッチングを防止して、第1金属膜18のみをエッチングすることが可能である。従って、ゲート高さを除いて、形状が揃った第1ゲート電極22および第2ゲート電極25が形成される。

【0042】

次に、シリコン窒化膜41を、例えば熱リン酸を用いたウェットエッチングにより除去した後、第1ゲート電極22および第2ゲート電極25に側壁膜(図示せず)を形成し、イオン注入法により、第1領域13および第2領域14にそれぞれ不純物を導入し、第1ゲート電極22をゲート長方向に挟むようにソース領域23およびドレイン領域24を形成し、第2ゲート電極25をゲート長方向に挟むようにソース領域26およびドレイン領域27を形成する。

【0043】

これにより、図1に示す第1ゲート電極22を有するp−MISトランジスタ15および第2ゲート電極25を有するn−MISトランジスタ16を備えた半導体装置10、即ちゲート電極形状のばらつきが少ないデュアルメタルゲート構造のCMOS半導体装置が得られる。

【0044】

図5は本実施例の効果を、比較例と対比して示す図で、図5(a)が本実施例を示す図、図5(b)が比較例を示す図である。

ここで、比較例とは、図4(b)に示す第1金属膜18および第2金属膜19の露出部への酸化処理を施さない場合を意味している。始めに比較例について説明する。

【0045】

図5(b)に示すように、比較例では、第2領域14における第2金属膜19の側壁が露出し、且つ回りにエッチングされるものが無いので、第1領域13における第1金属膜18がエッチングされている間に、第2金属膜19の側壁のサイドエッチングが生じる。

【0046】

第1領域13における第2金属膜19の側壁も露出しているが、第1金属膜18のエッチングが優先的に進むため、第1領域13における第2金属膜19の側壁のサイドエッチングはおこりづらい。

【0047】

一方、図5(a)に示すように、本実施例では、上述したように第2領域14における第2金属膜19の側壁に強固な酸化膜44が形成されているので、第1領域13における第1金属膜18がエッチングされている間に、第2金属膜19の側壁のサイドエッチングは生じない。

【0048】

第1領域13における第1金属膜18の側面および上面の酸化膜43は、エッチングされるので、第1金属膜18のエッチングに支障をきたさない。

【0049】

以上説明したように、本実施例の半導体装置の製造方法は、第2金属膜19を異方性エッチングした後に、第1金属膜18および第2金属膜19の露出部に酸化処理を施す工程を具備している。

【0050】

その結果、第2領域14における第2金属膜19の側壁に強固な酸化膜44が形成されるので、第1領域13における第1金属膜18がエッチングされている間に、第2金属膜19の側壁がサイドエッチングされることを防止できる。

【0051】

従って、p−MISトランジスタ15とn−MISトランジスタ16とのゲート電極形状のばらつきが少ない半導体装置10が得られる。

【0052】

ここでは、第1金属がタングステン(W)、第1金属膜が窒化タングステン(WN)、第2金属がタンタル(Ta)、第2金属膜が炭化タンタル(TaC)である場合について説明したが、第1金属と酸素の結合エネルギーが第2金属と酸素の結合エネルギーより小さい条件を満たす他の金属および導電性を有するその金属化合物であっても構わない。

【0053】

例えば、図6に示すように、第1金属としてチタン(Ti)を用いることができる。チタンと酸素の結合エネルギーは、158±5kCal/mol程度である。

【0054】

第1金属膜18として、炭化タングステン(WC)、タングステンシリサイド(WSi)、白金タングステンシリサイド(PtWSi)、窒化チタン(TiN)、炭化チタン(TiC)、硼化チタン(TiB)、窒化アルミニウムチタン(TiAlN)などを用いることができる。

【0055】

第2金属として、ハフニウム(Hf)を用いることができる。ハフニウムと酸素の結合エネルギーは、185±10kCal/mol程度である。また、金属ではないが、半導体のポリシリコンを用いることも可能である。ポリシリコンと酸素の結合エネルギーは、184±3kCal/mol程度である。

【0056】

第2金属膜19として、窒化タンタル(TaN)、2窒化タンタル(Ta2N)硼化タンタル(TaB)、珪窒化タンタル(TaSiN)、窒化アルミニウムタンタル(TaAlN)、タンタルチタン(TaTi)、窒化ハフニウムアルミニウム(HfAlN)などを用いることができる。

【0057】

更に、硼化ハフニウム(HfB)、ハフニウムシリサイド(HfSi2)、ニッケルシリサイド(NiSi)、硼素添加ニッケルシリサイド(NiSi(B))、砒素添加ニッケルシリサイド(NiSi(As))などを、第1または第2金属膜として使用することができる可能性がある。

【図面の簡単な説明】

【0058】

【図1】本発明の実施例に係る半導体装置を示す断面図。

【図2】本発明の実施例に係る半導体装置の製造工程を順に示す断面図。

【図3】本発明の実施例に係る半導体装置の製造工程を順に示す断面図。

【図4】本発明の実施例に係る半導体装置の製造工程を順に示す断面図。

【図5】本発明の実施例に係る効果を比較例と対比して示す図で、図5(a)が本実施例を示す図、図5(b)が比較例を示す図。

【図6】本発明の実施例に係る他の第1金属、第1金属膜、第2金属および第2金属膜を示す図。

【符号の説明】

【0059】

10 半導体装置

11 半導体基板

12 STI

13 第1領域

14 第2領域

15 p−MISトランジスタ

16 n−MISトランジスタ

17 ゲート絶縁膜

18 第1金属膜

19 第2金属膜

20 バリア膜

21 ポリシリコン膜

22 第1ゲート電極

23、26 ソース領域

24、27 ドレイン領域

25 第2ゲート電極

40、42 レジスト膜

40a 開口

41 シリコン窒化膜

43、44、45、46 酸化膜

【特許請求の範囲】

【請求項1】

半導体基板の主面の第1領域および第2領域に、ゲート絶縁膜を介して第1金属を含む第1金属膜を形成する工程と、

前記第1領域における前記第1金属膜を保護膜で被覆し、前記第2領域における前記第1金属膜を除去して前記ゲート絶縁膜を露出させる工程と、

前記第1領域における前記第1金属膜上、および前記第2領域における前記ゲート絶縁膜上に、前記第1金属と異なる第2金属を含む第2金属膜を形成する工程と、

ゲート電極パターンを有するマスク材を用いて、前記第1領域および前記第2領域における前記第2金属膜を異方性エッチングし、前記第2領域に第2ゲート電極を形成する工程と、

前記異方性エッチングした後、前記第1金属膜および前記第2金属膜の露出部に酸化処理を施す工程と、

前記酸化処理を施した後、前記第1領域における前記第1金属膜を異方性エッチングし、前記第1領域に第1ゲート電極を形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項2】

前記第1金属と酸素の結合エネルギーが、前記第2金属と酸素の結合エネルギーより小さいことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1金属がタングステン、またはチタンであり、前記第2金属がタンタル、またはハフニウムであることを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1金属膜が前記第1金属単体、または前記第1金属の窒化物、炭化物、硼化物、珪化物のいずれかであり、前記第2金属膜が前記第2金属単体、または前記第2金属の窒化物、炭化物、硼化物、珪化物のいずれかであることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項5】

前記酸化処理は、酸素プラズマ処理であることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項1】

半導体基板の主面の第1領域および第2領域に、ゲート絶縁膜を介して第1金属を含む第1金属膜を形成する工程と、

前記第1領域における前記第1金属膜を保護膜で被覆し、前記第2領域における前記第1金属膜を除去して前記ゲート絶縁膜を露出させる工程と、

前記第1領域における前記第1金属膜上、および前記第2領域における前記ゲート絶縁膜上に、前記第1金属と異なる第2金属を含む第2金属膜を形成する工程と、

ゲート電極パターンを有するマスク材を用いて、前記第1領域および前記第2領域における前記第2金属膜を異方性エッチングし、前記第2領域に第2ゲート電極を形成する工程と、

前記異方性エッチングした後、前記第1金属膜および前記第2金属膜の露出部に酸化処理を施す工程と、

前記酸化処理を施した後、前記第1領域における前記第1金属膜を異方性エッチングし、前記第1領域に第1ゲート電極を形成する工程と、

を具備することを特徴とする半導体装置の製造方法。

【請求項2】

前記第1金属と酸素の結合エネルギーが、前記第2金属と酸素の結合エネルギーより小さいことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1金属がタングステン、またはチタンであり、前記第2金属がタンタル、またはハフニウムであることを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1金属膜が前記第1金属単体、または前記第1金属の窒化物、炭化物、硼化物、珪化物のいずれかであり、前記第2金属膜が前記第2金属単体、または前記第2金属の窒化物、炭化物、硼化物、珪化物のいずれかであることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項5】

前記酸化処理は、酸素プラズマ処理であることを特徴とする請求項1に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2009−94106(P2009−94106A)

【公開日】平成21年4月30日(2009.4.30)

【国際特許分類】

【出願番号】特願2007−260284(P2007−260284)

【出願日】平成19年10月3日(2007.10.3)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成21年4月30日(2009.4.30)

【国際特許分類】

【出願日】平成19年10月3日(2007.10.3)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]