半導体装置の製造方法

【課題】半導体装置の低コスト化を図る。

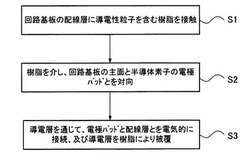

【解決手段】回路基板の主面に選択的に形成された配線層に、複数の導電性粒子を含む樹脂を接触させ(ステップS1)、前記樹脂を介して、回路基板の主面と半導体素子の主面に配置された電極パッドとを対向させる(ステップS2)。そして、導電性粒子の融点以上に導電性粒子を加熱して、複数の導電性粒子を一体化させた導電層を通じて、電極パッドと配線層とを電気的に接続する。それと共に、導電層を樹脂で被覆する(ステップS3)。これにより、電極接合及び封止用樹脂の形成工程が簡略化され、低コストで半導体装置を製造できる。

【解決手段】回路基板の主面に選択的に形成された配線層に、複数の導電性粒子を含む樹脂を接触させ(ステップS1)、前記樹脂を介して、回路基板の主面と半導体素子の主面に配置された電極パッドとを対向させる(ステップS2)。そして、導電性粒子の融点以上に導電性粒子を加熱して、複数の導電性粒子を一体化させた導電層を通じて、電極パッドと配線層とを電気的に接続する。それと共に、導電層を樹脂で被覆する(ステップS3)。これにより、電極接合及び封止用樹脂の形成工程が簡略化され、低コストで半導体装置を製造できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置の製造方法に関し、特に電極形成に係る半導体装置の製造方法に関する。

【背景技術】

【0002】

薄型テレビや携帯電話の小型・軽量化を実現させている要素技術の一つとして、パワーモジュールがある。

中でも、パワー半導体素子、制御用IC素子を、同じ支持基板上に2次元的に配置し、これらの素子間をリードフレームで配線したインテリジェントパワーモジュールが注目されている(例えば、特許文献1参照)。

【0003】

このようなパワーモジュールでは、素子を支持基板に実装する際に、素子に設けられたバンプ電極と支持基板に配設された配線とを、例えば、リフロー処理により接合させる。そして、当該素子と支持基板との間に、封止用樹脂を形成する方法が用いられている。

【特許文献1】特開2001−291823号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した実装、封止用樹脂の形成は、リフロー処理、アンダーフィル材の充填及び硬化という工程を経ている。

従って、これらの製造工程は多工程になってしまい、半導体装置の製造コストを低減できないという問題点があった。

【0005】

本発明はこのような点に鑑みてなされたものであり、電極接合及び封止用樹脂の形成工程を簡略化し、低コストで半導体装置を製造できる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題を解決するために、回路基板の主面に選択的に形成された配線層に、複数の導電性粒子を含む樹脂を接触させる工程と、前記樹脂を介して、前記回路基板の前記主面と半導体素子の主面に配置された電極パッドとを対向させる工程と、前記導電性粒子の融点以上に前記導電性粒子を加熱し、複数の前記導電性粒子を一体化させた導電層を通じて、前記電極パッドと前記配線層とを電気的に接続すると共に、前記導電層を前記樹脂で被覆する工程と、を有することを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0007】

上記手段によれば、電極接合及び封止用樹脂の形成工程が簡略化され、低コストで半導体装置を製造できる。

【発明を実施するための最良の形態】

【0008】

以下、本実施の形態に係る半導体装置の製造方法を、図面を参照しながら詳細に説明する。

図1は半導体装置の製造方法の製造工程のフロー図である。

【0009】

先ず、回路基板(支持基板)の主面に選択的に形成された配線層に、複数の導電性粒子を含む樹脂を接触させる(ステップS1)。

次に、前記樹脂を介して、回路基板の主面と半導体素子の主面に配置された電極パッドとを対向させる(ステップS2)。

【0010】

次に、導電性粒子の融点以上に導電性粒子を加熱して、複数の導電性粒子を一体化させた導電層を通じて、電極パッドと配線層とを電気的に接続する。それと共に、導電層を樹脂で被覆する(ステップS3)。

【0011】

このような製造方法により、半導体装置が製造される。

次に、図1に例示したフロー図をもとに、半導体装置の製造方法の具体例について説明する。

【0012】

図2〜図4は半導体装置の製造方法を説明するための要部断面図である。

先ず、図2(a)に示すように、配線(配線パターン)10ptが選択的に配置された回路基板(支持基板)10を準備する。当該配線10ptは、半導体装置の主回路、信号回路、電源用回路等の配線として用いられる。

【0013】

回路基板10は、所謂プリント配線基板であり、その樹脂材として、ガラス−エポキシ樹脂、ガラス−ビスマレイミドトリアジン、或いはポリイミド等の有機材絶縁性樹脂が用いられる。

【0014】

また、回路基板10としては、上記プリント配線基板に代えて、例えば、アルミナ(Al2O3)、窒化アルミニウム(AlN)、酸化シリコン(SiO2)、酸化マグネシウム(MgO)、酸化カルシウム(CaO)、或いは、これらの混合物等を主たる成分とするセラミック配線板を用いてもよい。

【0015】

また、配線10ptの材質としては、銅(Cu)が用いられる。

次に、図2(b)に示すように、回路基板10の主面及び配線10pt上に、導電性粒子12を樹脂11に含有させたペースト13を塗布する。ここで、配線10ptにペースト13が接触する。

【0016】

ここで、樹脂11の材質としては、熱硬化性のエポキシ樹脂が用いられる。また、当該樹脂11は、導電性粒子12の融点以上の温度に加熱されると硬化する性質を有している。

【0017】

また、導電性粒子12の材質としては、鉛フリーの半田が用いられる。そして、導電性粒子12の粒径は、30μm〜50μmであり、平均粒径は、40μmである。

尚、鉛フリーの半田としては、例えば、錫(Sn)−銅(Cu)半田、錫(Sn)−銀(Ag)半田、錫(Sn)−亜鉛(Zn)半田、錫(Sn)−銀(Ag)−銅(Cu)半田が用いられる。

【0018】

また、ペースト13の回路基板10の主面及び配線10pt上への選択的な塗布は、例えば、スクリーン印刷法、或いはディスペンス法により行う。尚、この段階では樹脂11は、硬化前の状態にある。

【0019】

次に、図3(a)に示すように、ペースト13上に、フェイスダウンによって半導体素子20を載置し、回路基板10の主面と半導体素子20の主面に配置された電極パッド20pとを対向させる。例えば、半導体素子20の主面に配置されている電極パッド20pがペースト13を介して、配線10ptに対向するように載置される。

【0020】

半導体素子20としては、例えば、パワーMOSFET(Metal Oxide Semiconductor Field Effect Transistor)、IGBT(Insulated Gate Bipolar Transistor)、FWD(Free Wheeling Diode)等が用いられる。また、半導体素子20に配置された電極パッド20pとしては、例えば、主電極用の端子、或いは制御電極用の端子等が該当する。

【0021】

尚、この図では、半導体素子20として縦型のパワー半導体素子を用いた場合が例示されている。従って、電極パッド20pが配置されている主面とは反対側の半導体素子20の主面に、裏面電極20bが配置された状態が示されている。

【0022】

尚、電極パッド20p、裏面電極20bの材質としては、例えば、アルミニウム(Al)、銅(Cu)を主成分とした金属が用いられる。

また、電極パッド20p及び裏面電極20bの表面には、下層からニッケル(Ni)/金(Au)鍍金、或いはニッケル(Ni)/錫(Sn)鍍金を施してもよい(図示しない)。また、当該鍍金層上に、フラックス材を塗布してもよい。

【0023】

次に、導電性粒子12のリフロー処理を開始する。例えば、図3(a)に例示する回路基板10、半導体素子20及びペースト13等のユニットをリフロー炉内に設置して(図示しない)、上記半田の融点以上の温度雰囲気で当該ユニットを加熱する。

【0024】

具体的には、当該ユニットを導電性粒子12の融点直下で予備加熱する(加熱時間:30秒間〜3分間)。その後、当該ユニットを導電性粒子12の融点より、10℃〜20℃高い温度で加熱する(加熱時間:5秒間〜2分間)。

【0025】

そして、導電性粒子12が融点以上になると、図3(b)に示すように、当該導電性粒子12の相互間に表面張力が作用して、導電性粒子12同士が自発的に凝集し始める。そして、リフロー処理を続けると、図3(c)に示すように、上記導電性粒子12が一体化し、ポスト状の導電層12aが形成する。また、半田と電極パッド20p及び配線10ptとの濡れ性は良好であることから、導電層12aは、電極パッド20p及び配線10ptに強く密着する。

【0026】

これにより、電極パッド20pと、当該電極パッド20pの直下に対向して配置された配線10ptとが導電層12aを通じて電気的に接続される。

また、上記樹脂11は、熱硬化性樹脂であることから、当該リフロー処理によって硬化し、封止用樹脂11aが形成する。

【0027】

即ち、この段階でのリフロー処理において、導電層12aが形成されると共に、当該導電層12aが封止用樹脂11aにより被覆される。尚、樹脂11を硬化させる温度は、半田の融点によって調整される。

【0028】

次に、図4(a)に示すように、導電性パターン(導体接続子)30pt,31ptが選択的に配置された配線支持基材30を準備する。

導電性パターン30pt,31ptは、配線支持基材30にラミネート接合法によって固着させた導電層がフォトリソグラフィ工程を経て形成される。また、配線支持基材30と導電性パターン30pt,31ptとの界面には、例えば、接着部材(図示しない)が介在している。

【0029】

また、導電性パターン31ptには、電極端子である半田ボール(導電層)32が接合している。

尚、配線支持基材30の材質としては、可撓性を有した有機材料が用いられる。例えば、その材質としては、ポリイミド樹脂(PI)、液晶ポリマ樹脂(LCP)、エポキシ樹脂(EP)、ポリエチレンテレフタレート樹脂(PET)、ポリフェニレンエーテル樹脂(PPE)の少なくとも一つを含む樹脂が用いられる。

【0030】

また、導電性パターン30pt,31ptの材質としては、銅(Cu)、銀(Ag)、金(Au)、アルミニウム(Al)、またはこれらの少なくとも一つを含む合金が用いられる。導電性パターン30pt,31ptの表面には、下層からニッケル(Ni)/金(Au)鍍金、或いはニッケル(Ni)/錫(Sn)鍍金を施してもよい(図示しない)。また、当該鍍金層上に、フラックス材を塗布してもよい。

【0031】

また、導電性パターン30pt,31ptについては、上記金属材で構成された導体性ペーストをスクリーン印刷にて配線支持基材30上に塗布した後、乾燥・硬化させることにより形成してもよい。また、スパッタ法、真空蒸着、或いは鍍金により、導電性パターン30pt,31ptを形成してもよい。

【0032】

尚、導電性パターン30pt,31ptの厚みは、5mm以下に構成されている。

また、半導体素子20の裏面電極20b上には、予め半田部材40を配置させておく。 半田部材40の材質としては、例えば、上記鉛フリーの半田が用いられる。また、その形状はシート状であってもよく、ペースト状であってもよい。

【0033】

そして、配線支持基材30を回路基板10側に降下させ(図中矢印の方向)、導電性パターン30ptと半田部材40、半田ボール32と回路基板10に配置させた別の配線11ptとを接触させる(図示しない)。そして、半田ボール32及び半田部材40のリフロー処理を開始する。リフロー処理条件は、上記と同じである。

【0034】

リフロー処理後の状態を、図4(b)に示す。

図示するように、半導体素子20の裏面電極20bと配線支持基材30の導電性パターン30ptとが半田部材40を通じて電気的に接続されている。

【0035】

また、配線支持基材30の導電性パターン31ptと回路基板10の配線11ptとが半田ボール32を通じて電気的に接続されている。

尚、上述した半田ボール32及び半田部材40のリフロー処理において、導電層12aの温度が融点以上になり、当該導電層12aが封止用樹脂11a内で溶融する場合がある。

【0036】

然るに、導電層12aは、硬化した封止用樹脂11aにより、その外周を覆われている。従って、溶融した導電層12aが封止用樹脂11a外に流出するということはない。これにより、配線10ptと電極パッド20p間の導電層12aを通じての導通が確実に確保される。

【0037】

或いは、溶融した導電層12aが他の電極間に流れ込み、当該電極間での短絡(ショート)が発生することもない。

また、本実施の形態に係る半導体装置の製造方法では、電極パッド20pよりも面積の大きい裏面電極20b側を上方に向け、当該裏面電極20bに配線支持基材30に配置した導電性パターン30ptを接合している。

【0038】

従って、本実施の形態では、電極パッド20p側を上方に向け、当該電極パッド20pに配線支持基材30の導電性パターン30ptを接合させる製法に比べ、配線支持基材30の位置精度が緩和される。

【0039】

このような製造工程により、半導体装置1が完成する。

次に、上記の半導体素子20、或いは制御用IC素子を複数個搭載したマルチチップモジュールを製造する方法について説明する。当該マルチチップモジュールの製造においても、上述した半導体装置の製造方法が適用される。

【0040】

尚、以下の図では、図2〜図4を用いて説明した部材には同一の符号を付している。

図5はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図5には、連続した回路基板(支持基板)10の表面側の形状が例示されている。

【0041】

図示するように、矩形状の回路基板10の主面には、主回路、信号回路、電源用回路等に組み込まれる配線(配線パターン)10ptが選択的に配置されている。

このような回路基板10は、電極、配線、樹脂層が多層構造となって積層された、プリント配線基板である。また、この段階の回路基板10は、ダイシング処理前の状態にあり、複数の回路基板10が縦横に連続している。

【0042】

また、配線10ptが配置されている回路基板10の主面の反対側の主面(裏面側)には、必要に応じて、ヒートスプレッダとして機能する金属製の放熱板(図示しない)を固着させてもよい。

【0043】

図6はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図6には、連続した回路基板10の表面側の形状が例示されている。

次に、回路基板10の所定部分にペースト13を選択的に配置する。例えば、スクリーン印刷法、或いはディスペンス法により、回路基板10のチップ搭載部分にペースト13を塗布する。

【0044】

図7及び図8はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図7には、回路基板10等の表面側の形状が例示され、図8(a)には、図7のX−Y断面が例示され、図8(b)には、図7のX’−Y’断面が例示されている。

【0045】

続いて、上記ペースト13上に、制御用IC素子21及びIGBT素子22を載置する(図7参照)。

ここで、制御用IC素子21には、電極パッド21pが複数個配置されている。そして、それぞれの電極パッド21pがペースト13を介し、配線10ptに対向して配置される(図8(a)参照)。

【0046】

また、IGBT素子22には、その主面にゲート電極22g及びエミッタ電極22eが配置されている。そして、ゲート電極22g、エミッタ電極22eがペースト13を介し、それぞれの配線10ptの先端部に対向して配置される(図8(b)参照)。

【0047】

尚、IGBT素子22においては、ゲート電極22g及びエミッタ電極22eが配置されている主面とは反対側に、裏面電極(コレクタ電極)22bが配置されている。

続いて、ペースト13内の導電性粒子12のリフロー処理を施す。リフロー処理の条件は、上記条件と同様である。

【0048】

図9はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図9(a)には、図7のX−Y断面が例示され、図9(b)には、図7のX’−Y’断面が例示されている。

【0049】

図示するように、リフロー処理後には、上記導電性粒子12が図3を用いて説明したように自発的に凝集して、導電性粒子12が一体化した導電層12aが形成する。

これにより、制御用IC素子21においては、電極パッド21pと、それぞれの電極パッド21pの直下に対向して配置された各配線10ptとが導電層12aを通じて電気的に接続される(図9(a)参照)。

【0050】

また、IGBT素子22においては、ゲート電極22gと、当該ゲート電極22gの直下に対向して配置された配線10ptとが導電層12aを通じて電気的に接続される。

また、エミッタ電極22eと、当該エミッタ電極22eの直下に対向して配置された配線10ptとが導電層12aを通じて電気的に接続される(図9(b)参照)。

【0051】

また、リフロー処理後には、導電層12aの形成と共に、上記樹脂11が硬化した封止用樹脂11aが形成する。そして、それぞれの導電層12aが封止用樹脂11aにより完全に被覆される。

【0052】

尚、IGBT素子22の裏面電極22b上には、上記リフロー処理後に半田部材40を配置しておく。

ここで、半田部材40は、シート状であってもよく、ペースト状であってもよい。尚、半田部材40の材質は、上記半田材と同様である。

【0053】

図10はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図10(a)には、配線支持基材30等の表面側の形状が例示され、図10(b)には、図10(a)のX−Y断面が例示されている。尚、図10(a)では、配線支持基材30の表面側から、導電性パターン30ptを透視した場合の例が示され、導電性パターン30ptの外形が破線で示されている。

【0054】

図示するように、配線支持基材30は、帯状の形状を有し、導電性パターン30ptが選択的に配置されている。導電性パターン30ptは、上記IGBT素子22の主電極(裏面電極22b)に接合させるための配線層である。

【0055】

また、導電性パターン30ptの一部には、上述したように、半田ボール32が接合されている。

続いて、当該配線支持基材30等の導電性パターン30ptが上記回路基板10に対向するように、当該配線支持基材30等を回路基板10上に載置する(図示しない)。

【0056】

そして、上記半田部材40及び半田ボール32のリフロー処理を施す。リフロー処理の条件は、上記条件と同様である。

リフロー後の状態を、図11及び図12に示す。

【0057】

図11及び図12はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図11には、連続した回路基板10、帯状の配線支持基材30の表面側の形状が例示されている。また、図12には、図11のX−Y断面図が例示されている。尚、図11では、配線支持基材30の表面側から、導電性パターン30pt、制御用IC素子21及びIGBT素子22等を透視した場合の例が示され、それらの外形が破線で示されている。

【0058】

リフロー処理後においては、導電性パターン30ptが回路基板10に配置した配線、IGBT素子22等に電気的に接続されている(図11参照)。

例えば、IGBT素子22の裏面電極22bと配線支持基材30の導電性パターン30ptとが半田部材40を通じて電気的に接続される(図12参照)。

【0059】

また、IGBT素子22が搭載された領域外の回路基板10に配置した配線11ptと、当該配線11pt上に対向する導電性パターン30ptとが半田ボール32を通じて電気的に接続される。

【0060】

尚、上述した半田部材40及び半田ボール32のリフロー処理において、導電層12aの温度が融点以上になり、当該導電層12aが封止用樹脂11a内で溶融する場合がある。

【0061】

然るに、導電層12aは、硬化した封止用樹脂11aにより、その外周を覆われている。従って、溶融した導電層12aが封止用樹脂11a外に流出するということはない。

これにより、配線10ptとゲート電極22g間、配線10ptとエミッタ電極22e間の導電層12aを通じての導通が確実に確保される。

【0062】

また、図9(a)に示す制御用IC素子21においても、溶融した導電層12aが封止用樹脂11a外に流出するということはない。従って、配線10ptと電極パッド21p間の導電層12aを通じての導通が確実に確保される。

【0063】

或いは、溶融した導電層12aが他の端子間に流れ込み、当該端子間での短絡(ショート)が発生することもない。

また、回路基板10と配線支持基材30との間隙には、半田ボール32を介在させていることから、配線支持基材30の撓みが抑制される。これにより、回路基板10と配線支持基材30とは平行に維持される。

【0064】

図13及び図14はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図13には、連続した配線支持基材30等の表面側の形状が例示されている。また、図14には、図13のX−Y断面図が例示されている。

【0065】

次に、回路基板10の主面の端部まで延在させた配線10ptに、棒状の入出力端子50を接合する(図13参照)。

ここで、入出力端子50は、その一端に、二股に分離するクリップ部50aを備えている(図14参照)。

【0066】

当該クリップ部50aは、回路基板10の上下の主面に配設された配線10ptに挟装されている。そして、クリップ部50aを回路基板10の端に嵌め込み、クリップ部50aと配線10ptとを半田部材51を介し接合することにより、入出力端子50は、回路基板10の端に強固に固定されている。更に、半田部材51は、クリップ部50aの端を被覆している。このような半田部材51の形成により、クリップ部50aと配線10ptとの接合強度が更に高くなる。

【0067】

尚、配線10pt或いはクリップ部50aの表面には、その下層から、ニッケル(Ni)/金(Au)膜、或いはニッケル(Ni)/錫(Sn)膜を鍍金により形成してもよい。

【0068】

図15はマルチチップモジュールの製造方法を説明するための要部図である。

入出力端子50を回路基板10に接合させた後、トランスファモールド装置を用いて当該回路基板10上に配置された配線支持基材30、及び半導体素子等を、封止用樹脂60により封止する。ここで、図中に示した封止用樹脂60上の破線は、ダイシングラインDLを表している。

【0069】

図16はマルチチップモジュールの製造方法を説明するための要部図である。

回路基板10及び封止用樹脂60等をダイシングラインDLに沿って切断し、個片化を行う。このような製造工程により、パワー半導体素子、制御用ICチップを複数個搭載したマルチチップモジュール1Mが完成する。

【0070】

尚、マルチチップモジュール1Mに搭載する素子については、上述したパワー半導体素子、制御用ICチップに限ることはない。例えば、CPU(Central Processing Unit)、DSP(Digital Signal Processor)、半導体メモリ、或いはアナログICチップの何れかを搭載してもよい。

【0071】

以上説明したように、本実施の形態によれば、リフロー処理によって上記導電層12aが形成すると共に、封止用樹脂11aが形成する。即ち、導電層12a、封止用樹脂11aを一括して形成することができる。

【0072】

また、ポスト状の導電層12aに関しては、レジスト塗布後、当該レジストのパターニングを行ってから鍍金工程を経て形成する必要がない。即ち、導電層12aは、導電性粒子12の自発的な凝集によって簡便に形成される。

【0073】

このように、本実施の形態によれば、半導体装置の製造コストが低減する。

また、導電性粒子12の自発的に凝集により導電層12aが形成するので、導電層12aに接合させる被接合部材(例えば、電極パッド20p、配線10pt等)の設計上の配置の自由度が増加する。

【図面の簡単な説明】

【0074】

【図1】半導体装置の製造方法の製造工程のフロー図である。

【図2】半導体装置の製造方法を説明するための要部断面図である(その1)。

【図3】半導体装置の製造方法を説明するための要部断面図である(その2)。

【図4】半導体装置の製造方法を説明するための要部断面図である(その3)。

【図5】マルチチップモジュールの製造方法を説明するための要部図である(その1)。

【図6】マルチチップモジュールの製造方法を説明するための要部図である(その2)。

【図7】マルチチップモジュールの製造方法を説明するための要部図である(その3)。

【図8】マルチチップモジュールの製造方法を説明するための要部図である(その4)。

【図9】マルチチップモジュールの製造方法を説明するための要部図である(その5)。

【図10】マルチチップモジュールの製造方法を説明するための要部図である(その6)。

【図11】マルチチップモジュールの製造方法を説明するための要部図である(その7)。

【図12】マルチチップモジュールの製造方法を説明するための要部図である(その8)。

【図13】マルチチップモジュールの製造方法を説明するための要部図である(その9)。

【図14】マルチチップモジュールの製造方法を説明するための要部図である(その10)。

【図15】マルチチップモジュールの製造方法を説明するための要部図である(その11)。

【図16】マルチチップモジュールの製造方法を説明するための要部図である(その12)。

【符号の説明】

【0075】

1 半導体装置

1M マルチチップモジュール

10 回路基板

10pt,11pt 配線

11 樹脂

11a,60 封止用樹脂

12 導電性粒子

12a 導電層

13 ペースト

20p,21p 電極パッド

20b,22b 裏面電極

20 半導体素子

21 制御用IC素子

22 IGBT素子

22e エミッタ電極

22g ゲート電極

30 配線支持基材

30pt,31pt 導電性パターン

32 半田ボール

40,51 半田部材

50 入出力端子

50a クリップ部

DL ダイシングライン

【技術分野】

【0001】

本発明は半導体装置の製造方法に関し、特に電極形成に係る半導体装置の製造方法に関する。

【背景技術】

【0002】

薄型テレビや携帯電話の小型・軽量化を実現させている要素技術の一つとして、パワーモジュールがある。

中でも、パワー半導体素子、制御用IC素子を、同じ支持基板上に2次元的に配置し、これらの素子間をリードフレームで配線したインテリジェントパワーモジュールが注目されている(例えば、特許文献1参照)。

【0003】

このようなパワーモジュールでは、素子を支持基板に実装する際に、素子に設けられたバンプ電極と支持基板に配設された配線とを、例えば、リフロー処理により接合させる。そして、当該素子と支持基板との間に、封止用樹脂を形成する方法が用いられている。

【特許文献1】特開2001−291823号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した実装、封止用樹脂の形成は、リフロー処理、アンダーフィル材の充填及び硬化という工程を経ている。

従って、これらの製造工程は多工程になってしまい、半導体装置の製造コストを低減できないという問題点があった。

【0005】

本発明はこのような点に鑑みてなされたものであり、電極接合及び封止用樹脂の形成工程を簡略化し、低コストで半導体装置を製造できる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題を解決するために、回路基板の主面に選択的に形成された配線層に、複数の導電性粒子を含む樹脂を接触させる工程と、前記樹脂を介して、前記回路基板の前記主面と半導体素子の主面に配置された電極パッドとを対向させる工程と、前記導電性粒子の融点以上に前記導電性粒子を加熱し、複数の前記導電性粒子を一体化させた導電層を通じて、前記電極パッドと前記配線層とを電気的に接続すると共に、前記導電層を前記樹脂で被覆する工程と、を有することを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0007】

上記手段によれば、電極接合及び封止用樹脂の形成工程が簡略化され、低コストで半導体装置を製造できる。

【発明を実施するための最良の形態】

【0008】

以下、本実施の形態に係る半導体装置の製造方法を、図面を参照しながら詳細に説明する。

図1は半導体装置の製造方法の製造工程のフロー図である。

【0009】

先ず、回路基板(支持基板)の主面に選択的に形成された配線層に、複数の導電性粒子を含む樹脂を接触させる(ステップS1)。

次に、前記樹脂を介して、回路基板の主面と半導体素子の主面に配置された電極パッドとを対向させる(ステップS2)。

【0010】

次に、導電性粒子の融点以上に導電性粒子を加熱して、複数の導電性粒子を一体化させた導電層を通じて、電極パッドと配線層とを電気的に接続する。それと共に、導電層を樹脂で被覆する(ステップS3)。

【0011】

このような製造方法により、半導体装置が製造される。

次に、図1に例示したフロー図をもとに、半導体装置の製造方法の具体例について説明する。

【0012】

図2〜図4は半導体装置の製造方法を説明するための要部断面図である。

先ず、図2(a)に示すように、配線(配線パターン)10ptが選択的に配置された回路基板(支持基板)10を準備する。当該配線10ptは、半導体装置の主回路、信号回路、電源用回路等の配線として用いられる。

【0013】

回路基板10は、所謂プリント配線基板であり、その樹脂材として、ガラス−エポキシ樹脂、ガラス−ビスマレイミドトリアジン、或いはポリイミド等の有機材絶縁性樹脂が用いられる。

【0014】

また、回路基板10としては、上記プリント配線基板に代えて、例えば、アルミナ(Al2O3)、窒化アルミニウム(AlN)、酸化シリコン(SiO2)、酸化マグネシウム(MgO)、酸化カルシウム(CaO)、或いは、これらの混合物等を主たる成分とするセラミック配線板を用いてもよい。

【0015】

また、配線10ptの材質としては、銅(Cu)が用いられる。

次に、図2(b)に示すように、回路基板10の主面及び配線10pt上に、導電性粒子12を樹脂11に含有させたペースト13を塗布する。ここで、配線10ptにペースト13が接触する。

【0016】

ここで、樹脂11の材質としては、熱硬化性のエポキシ樹脂が用いられる。また、当該樹脂11は、導電性粒子12の融点以上の温度に加熱されると硬化する性質を有している。

【0017】

また、導電性粒子12の材質としては、鉛フリーの半田が用いられる。そして、導電性粒子12の粒径は、30μm〜50μmであり、平均粒径は、40μmである。

尚、鉛フリーの半田としては、例えば、錫(Sn)−銅(Cu)半田、錫(Sn)−銀(Ag)半田、錫(Sn)−亜鉛(Zn)半田、錫(Sn)−銀(Ag)−銅(Cu)半田が用いられる。

【0018】

また、ペースト13の回路基板10の主面及び配線10pt上への選択的な塗布は、例えば、スクリーン印刷法、或いはディスペンス法により行う。尚、この段階では樹脂11は、硬化前の状態にある。

【0019】

次に、図3(a)に示すように、ペースト13上に、フェイスダウンによって半導体素子20を載置し、回路基板10の主面と半導体素子20の主面に配置された電極パッド20pとを対向させる。例えば、半導体素子20の主面に配置されている電極パッド20pがペースト13を介して、配線10ptに対向するように載置される。

【0020】

半導体素子20としては、例えば、パワーMOSFET(Metal Oxide Semiconductor Field Effect Transistor)、IGBT(Insulated Gate Bipolar Transistor)、FWD(Free Wheeling Diode)等が用いられる。また、半導体素子20に配置された電極パッド20pとしては、例えば、主電極用の端子、或いは制御電極用の端子等が該当する。

【0021】

尚、この図では、半導体素子20として縦型のパワー半導体素子を用いた場合が例示されている。従って、電極パッド20pが配置されている主面とは反対側の半導体素子20の主面に、裏面電極20bが配置された状態が示されている。

【0022】

尚、電極パッド20p、裏面電極20bの材質としては、例えば、アルミニウム(Al)、銅(Cu)を主成分とした金属が用いられる。

また、電極パッド20p及び裏面電極20bの表面には、下層からニッケル(Ni)/金(Au)鍍金、或いはニッケル(Ni)/錫(Sn)鍍金を施してもよい(図示しない)。また、当該鍍金層上に、フラックス材を塗布してもよい。

【0023】

次に、導電性粒子12のリフロー処理を開始する。例えば、図3(a)に例示する回路基板10、半導体素子20及びペースト13等のユニットをリフロー炉内に設置して(図示しない)、上記半田の融点以上の温度雰囲気で当該ユニットを加熱する。

【0024】

具体的には、当該ユニットを導電性粒子12の融点直下で予備加熱する(加熱時間:30秒間〜3分間)。その後、当該ユニットを導電性粒子12の融点より、10℃〜20℃高い温度で加熱する(加熱時間:5秒間〜2分間)。

【0025】

そして、導電性粒子12が融点以上になると、図3(b)に示すように、当該導電性粒子12の相互間に表面張力が作用して、導電性粒子12同士が自発的に凝集し始める。そして、リフロー処理を続けると、図3(c)に示すように、上記導電性粒子12が一体化し、ポスト状の導電層12aが形成する。また、半田と電極パッド20p及び配線10ptとの濡れ性は良好であることから、導電層12aは、電極パッド20p及び配線10ptに強く密着する。

【0026】

これにより、電極パッド20pと、当該電極パッド20pの直下に対向して配置された配線10ptとが導電層12aを通じて電気的に接続される。

また、上記樹脂11は、熱硬化性樹脂であることから、当該リフロー処理によって硬化し、封止用樹脂11aが形成する。

【0027】

即ち、この段階でのリフロー処理において、導電層12aが形成されると共に、当該導電層12aが封止用樹脂11aにより被覆される。尚、樹脂11を硬化させる温度は、半田の融点によって調整される。

【0028】

次に、図4(a)に示すように、導電性パターン(導体接続子)30pt,31ptが選択的に配置された配線支持基材30を準備する。

導電性パターン30pt,31ptは、配線支持基材30にラミネート接合法によって固着させた導電層がフォトリソグラフィ工程を経て形成される。また、配線支持基材30と導電性パターン30pt,31ptとの界面には、例えば、接着部材(図示しない)が介在している。

【0029】

また、導電性パターン31ptには、電極端子である半田ボール(導電層)32が接合している。

尚、配線支持基材30の材質としては、可撓性を有した有機材料が用いられる。例えば、その材質としては、ポリイミド樹脂(PI)、液晶ポリマ樹脂(LCP)、エポキシ樹脂(EP)、ポリエチレンテレフタレート樹脂(PET)、ポリフェニレンエーテル樹脂(PPE)の少なくとも一つを含む樹脂が用いられる。

【0030】

また、導電性パターン30pt,31ptの材質としては、銅(Cu)、銀(Ag)、金(Au)、アルミニウム(Al)、またはこれらの少なくとも一つを含む合金が用いられる。導電性パターン30pt,31ptの表面には、下層からニッケル(Ni)/金(Au)鍍金、或いはニッケル(Ni)/錫(Sn)鍍金を施してもよい(図示しない)。また、当該鍍金層上に、フラックス材を塗布してもよい。

【0031】

また、導電性パターン30pt,31ptについては、上記金属材で構成された導体性ペーストをスクリーン印刷にて配線支持基材30上に塗布した後、乾燥・硬化させることにより形成してもよい。また、スパッタ法、真空蒸着、或いは鍍金により、導電性パターン30pt,31ptを形成してもよい。

【0032】

尚、導電性パターン30pt,31ptの厚みは、5mm以下に構成されている。

また、半導体素子20の裏面電極20b上には、予め半田部材40を配置させておく。 半田部材40の材質としては、例えば、上記鉛フリーの半田が用いられる。また、その形状はシート状であってもよく、ペースト状であってもよい。

【0033】

そして、配線支持基材30を回路基板10側に降下させ(図中矢印の方向)、導電性パターン30ptと半田部材40、半田ボール32と回路基板10に配置させた別の配線11ptとを接触させる(図示しない)。そして、半田ボール32及び半田部材40のリフロー処理を開始する。リフロー処理条件は、上記と同じである。

【0034】

リフロー処理後の状態を、図4(b)に示す。

図示するように、半導体素子20の裏面電極20bと配線支持基材30の導電性パターン30ptとが半田部材40を通じて電気的に接続されている。

【0035】

また、配線支持基材30の導電性パターン31ptと回路基板10の配線11ptとが半田ボール32を通じて電気的に接続されている。

尚、上述した半田ボール32及び半田部材40のリフロー処理において、導電層12aの温度が融点以上になり、当該導電層12aが封止用樹脂11a内で溶融する場合がある。

【0036】

然るに、導電層12aは、硬化した封止用樹脂11aにより、その外周を覆われている。従って、溶融した導電層12aが封止用樹脂11a外に流出するということはない。これにより、配線10ptと電極パッド20p間の導電層12aを通じての導通が確実に確保される。

【0037】

或いは、溶融した導電層12aが他の電極間に流れ込み、当該電極間での短絡(ショート)が発生することもない。

また、本実施の形態に係る半導体装置の製造方法では、電極パッド20pよりも面積の大きい裏面電極20b側を上方に向け、当該裏面電極20bに配線支持基材30に配置した導電性パターン30ptを接合している。

【0038】

従って、本実施の形態では、電極パッド20p側を上方に向け、当該電極パッド20pに配線支持基材30の導電性パターン30ptを接合させる製法に比べ、配線支持基材30の位置精度が緩和される。

【0039】

このような製造工程により、半導体装置1が完成する。

次に、上記の半導体素子20、或いは制御用IC素子を複数個搭載したマルチチップモジュールを製造する方法について説明する。当該マルチチップモジュールの製造においても、上述した半導体装置の製造方法が適用される。

【0040】

尚、以下の図では、図2〜図4を用いて説明した部材には同一の符号を付している。

図5はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図5には、連続した回路基板(支持基板)10の表面側の形状が例示されている。

【0041】

図示するように、矩形状の回路基板10の主面には、主回路、信号回路、電源用回路等に組み込まれる配線(配線パターン)10ptが選択的に配置されている。

このような回路基板10は、電極、配線、樹脂層が多層構造となって積層された、プリント配線基板である。また、この段階の回路基板10は、ダイシング処理前の状態にあり、複数の回路基板10が縦横に連続している。

【0042】

また、配線10ptが配置されている回路基板10の主面の反対側の主面(裏面側)には、必要に応じて、ヒートスプレッダとして機能する金属製の放熱板(図示しない)を固着させてもよい。

【0043】

図6はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図6には、連続した回路基板10の表面側の形状が例示されている。

次に、回路基板10の所定部分にペースト13を選択的に配置する。例えば、スクリーン印刷法、或いはディスペンス法により、回路基板10のチップ搭載部分にペースト13を塗布する。

【0044】

図7及び図8はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図7には、回路基板10等の表面側の形状が例示され、図8(a)には、図7のX−Y断面が例示され、図8(b)には、図7のX’−Y’断面が例示されている。

【0045】

続いて、上記ペースト13上に、制御用IC素子21及びIGBT素子22を載置する(図7参照)。

ここで、制御用IC素子21には、電極パッド21pが複数個配置されている。そして、それぞれの電極パッド21pがペースト13を介し、配線10ptに対向して配置される(図8(a)参照)。

【0046】

また、IGBT素子22には、その主面にゲート電極22g及びエミッタ電極22eが配置されている。そして、ゲート電極22g、エミッタ電極22eがペースト13を介し、それぞれの配線10ptの先端部に対向して配置される(図8(b)参照)。

【0047】

尚、IGBT素子22においては、ゲート電極22g及びエミッタ電極22eが配置されている主面とは反対側に、裏面電極(コレクタ電極)22bが配置されている。

続いて、ペースト13内の導電性粒子12のリフロー処理を施す。リフロー処理の条件は、上記条件と同様である。

【0048】

図9はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図9(a)には、図7のX−Y断面が例示され、図9(b)には、図7のX’−Y’断面が例示されている。

【0049】

図示するように、リフロー処理後には、上記導電性粒子12が図3を用いて説明したように自発的に凝集して、導電性粒子12が一体化した導電層12aが形成する。

これにより、制御用IC素子21においては、電極パッド21pと、それぞれの電極パッド21pの直下に対向して配置された各配線10ptとが導電層12aを通じて電気的に接続される(図9(a)参照)。

【0050】

また、IGBT素子22においては、ゲート電極22gと、当該ゲート電極22gの直下に対向して配置された配線10ptとが導電層12aを通じて電気的に接続される。

また、エミッタ電極22eと、当該エミッタ電極22eの直下に対向して配置された配線10ptとが導電層12aを通じて電気的に接続される(図9(b)参照)。

【0051】

また、リフロー処理後には、導電層12aの形成と共に、上記樹脂11が硬化した封止用樹脂11aが形成する。そして、それぞれの導電層12aが封止用樹脂11aにより完全に被覆される。

【0052】

尚、IGBT素子22の裏面電極22b上には、上記リフロー処理後に半田部材40を配置しておく。

ここで、半田部材40は、シート状であってもよく、ペースト状であってもよい。尚、半田部材40の材質は、上記半田材と同様である。

【0053】

図10はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図10(a)には、配線支持基材30等の表面側の形状が例示され、図10(b)には、図10(a)のX−Y断面が例示されている。尚、図10(a)では、配線支持基材30の表面側から、導電性パターン30ptを透視した場合の例が示され、導電性パターン30ptの外形が破線で示されている。

【0054】

図示するように、配線支持基材30は、帯状の形状を有し、導電性パターン30ptが選択的に配置されている。導電性パターン30ptは、上記IGBT素子22の主電極(裏面電極22b)に接合させるための配線層である。

【0055】

また、導電性パターン30ptの一部には、上述したように、半田ボール32が接合されている。

続いて、当該配線支持基材30等の導電性パターン30ptが上記回路基板10に対向するように、当該配線支持基材30等を回路基板10上に載置する(図示しない)。

【0056】

そして、上記半田部材40及び半田ボール32のリフロー処理を施す。リフロー処理の条件は、上記条件と同様である。

リフロー後の状態を、図11及び図12に示す。

【0057】

図11及び図12はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図11には、連続した回路基板10、帯状の配線支持基材30の表面側の形状が例示されている。また、図12には、図11のX−Y断面図が例示されている。尚、図11では、配線支持基材30の表面側から、導電性パターン30pt、制御用IC素子21及びIGBT素子22等を透視した場合の例が示され、それらの外形が破線で示されている。

【0058】

リフロー処理後においては、導電性パターン30ptが回路基板10に配置した配線、IGBT素子22等に電気的に接続されている(図11参照)。

例えば、IGBT素子22の裏面電極22bと配線支持基材30の導電性パターン30ptとが半田部材40を通じて電気的に接続される(図12参照)。

【0059】

また、IGBT素子22が搭載された領域外の回路基板10に配置した配線11ptと、当該配線11pt上に対向する導電性パターン30ptとが半田ボール32を通じて電気的に接続される。

【0060】

尚、上述した半田部材40及び半田ボール32のリフロー処理において、導電層12aの温度が融点以上になり、当該導電層12aが封止用樹脂11a内で溶融する場合がある。

【0061】

然るに、導電層12aは、硬化した封止用樹脂11aにより、その外周を覆われている。従って、溶融した導電層12aが封止用樹脂11a外に流出するということはない。

これにより、配線10ptとゲート電極22g間、配線10ptとエミッタ電極22e間の導電層12aを通じての導通が確実に確保される。

【0062】

また、図9(a)に示す制御用IC素子21においても、溶融した導電層12aが封止用樹脂11a外に流出するということはない。従って、配線10ptと電極パッド21p間の導電層12aを通じての導通が確実に確保される。

【0063】

或いは、溶融した導電層12aが他の端子間に流れ込み、当該端子間での短絡(ショート)が発生することもない。

また、回路基板10と配線支持基材30との間隙には、半田ボール32を介在させていることから、配線支持基材30の撓みが抑制される。これにより、回路基板10と配線支持基材30とは平行に維持される。

【0064】

図13及び図14はマルチチップモジュールの製造方法を説明するための要部図である。ここで、図13には、連続した配線支持基材30等の表面側の形状が例示されている。また、図14には、図13のX−Y断面図が例示されている。

【0065】

次に、回路基板10の主面の端部まで延在させた配線10ptに、棒状の入出力端子50を接合する(図13参照)。

ここで、入出力端子50は、その一端に、二股に分離するクリップ部50aを備えている(図14参照)。

【0066】

当該クリップ部50aは、回路基板10の上下の主面に配設された配線10ptに挟装されている。そして、クリップ部50aを回路基板10の端に嵌め込み、クリップ部50aと配線10ptとを半田部材51を介し接合することにより、入出力端子50は、回路基板10の端に強固に固定されている。更に、半田部材51は、クリップ部50aの端を被覆している。このような半田部材51の形成により、クリップ部50aと配線10ptとの接合強度が更に高くなる。

【0067】

尚、配線10pt或いはクリップ部50aの表面には、その下層から、ニッケル(Ni)/金(Au)膜、或いはニッケル(Ni)/錫(Sn)膜を鍍金により形成してもよい。

【0068】

図15はマルチチップモジュールの製造方法を説明するための要部図である。

入出力端子50を回路基板10に接合させた後、トランスファモールド装置を用いて当該回路基板10上に配置された配線支持基材30、及び半導体素子等を、封止用樹脂60により封止する。ここで、図中に示した封止用樹脂60上の破線は、ダイシングラインDLを表している。

【0069】

図16はマルチチップモジュールの製造方法を説明するための要部図である。

回路基板10及び封止用樹脂60等をダイシングラインDLに沿って切断し、個片化を行う。このような製造工程により、パワー半導体素子、制御用ICチップを複数個搭載したマルチチップモジュール1Mが完成する。

【0070】

尚、マルチチップモジュール1Mに搭載する素子については、上述したパワー半導体素子、制御用ICチップに限ることはない。例えば、CPU(Central Processing Unit)、DSP(Digital Signal Processor)、半導体メモリ、或いはアナログICチップの何れかを搭載してもよい。

【0071】

以上説明したように、本実施の形態によれば、リフロー処理によって上記導電層12aが形成すると共に、封止用樹脂11aが形成する。即ち、導電層12a、封止用樹脂11aを一括して形成することができる。

【0072】

また、ポスト状の導電層12aに関しては、レジスト塗布後、当該レジストのパターニングを行ってから鍍金工程を経て形成する必要がない。即ち、導電層12aは、導電性粒子12の自発的な凝集によって簡便に形成される。

【0073】

このように、本実施の形態によれば、半導体装置の製造コストが低減する。

また、導電性粒子12の自発的に凝集により導電層12aが形成するので、導電層12aに接合させる被接合部材(例えば、電極パッド20p、配線10pt等)の設計上の配置の自由度が増加する。

【図面の簡単な説明】

【0074】

【図1】半導体装置の製造方法の製造工程のフロー図である。

【図2】半導体装置の製造方法を説明するための要部断面図である(その1)。

【図3】半導体装置の製造方法を説明するための要部断面図である(その2)。

【図4】半導体装置の製造方法を説明するための要部断面図である(その3)。

【図5】マルチチップモジュールの製造方法を説明するための要部図である(その1)。

【図6】マルチチップモジュールの製造方法を説明するための要部図である(その2)。

【図7】マルチチップモジュールの製造方法を説明するための要部図である(その3)。

【図8】マルチチップモジュールの製造方法を説明するための要部図である(その4)。

【図9】マルチチップモジュールの製造方法を説明するための要部図である(その5)。

【図10】マルチチップモジュールの製造方法を説明するための要部図である(その6)。

【図11】マルチチップモジュールの製造方法を説明するための要部図である(その7)。

【図12】マルチチップモジュールの製造方法を説明するための要部図である(その8)。

【図13】マルチチップモジュールの製造方法を説明するための要部図である(その9)。

【図14】マルチチップモジュールの製造方法を説明するための要部図である(その10)。

【図15】マルチチップモジュールの製造方法を説明するための要部図である(その11)。

【図16】マルチチップモジュールの製造方法を説明するための要部図である(その12)。

【符号の説明】

【0075】

1 半導体装置

1M マルチチップモジュール

10 回路基板

10pt,11pt 配線

11 樹脂

11a,60 封止用樹脂

12 導電性粒子

12a 導電層

13 ペースト

20p,21p 電極パッド

20b,22b 裏面電極

20 半導体素子

21 制御用IC素子

22 IGBT素子

22e エミッタ電極

22g ゲート電極

30 配線支持基材

30pt,31pt 導電性パターン

32 半田ボール

40,51 半田部材

50 入出力端子

50a クリップ部

DL ダイシングライン

【特許請求の範囲】

【請求項1】

回路基板の主面に選択的に形成された配線層に、複数の導電性粒子を含む樹脂を接触させる工程と、

前記樹脂を介して、前記回路基板の前記主面と半導体素子の主面に配置された電極パッドとを対向させる工程と、

前記導電性粒子の融点以上に前記導電性粒子を加熱し、複数の前記導電性粒子を一体化させた導電層を通じて、前記電極パッドと前記配線層とを電気的に接続すると共に、前記導電層を前記樹脂で被覆する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記樹脂として、熱硬化性の樹脂を用いることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記導電層を通じて前記電極パッドと前記配線層とを電気的に接続し、前記導電層を前記樹脂で被覆させた後、前記電極パッドが配置されている主面とは反対側の主面に配置されている前記半導体素子の別の電極パッドと、配線支持基材の主面に配置されている配線層とを、半田部材を介して接合することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項4】

前記別の電極パッドと、前記配線層とを接合すると共に、前記配線支持基材の前記主面に選択的に形成された導電層と、前記回路基板に配置されている別の配線層とを接合することを特徴とする請求項3記載の半導体装置の製造方法。

【請求項1】

回路基板の主面に選択的に形成された配線層に、複数の導電性粒子を含む樹脂を接触させる工程と、

前記樹脂を介して、前記回路基板の前記主面と半導体素子の主面に配置された電極パッドとを対向させる工程と、

前記導電性粒子の融点以上に前記導電性粒子を加熱し、複数の前記導電性粒子を一体化させた導電層を通じて、前記電極パッドと前記配線層とを電気的に接続すると共に、前記導電層を前記樹脂で被覆する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記樹脂として、熱硬化性の樹脂を用いることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記導電層を通じて前記電極パッドと前記配線層とを電気的に接続し、前記導電層を前記樹脂で被覆させた後、前記電極パッドが配置されている主面とは反対側の主面に配置されている前記半導体素子の別の電極パッドと、配線支持基材の主面に配置されている配線層とを、半田部材を介して接合することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項4】

前記別の電極パッドと、前記配線層とを接合すると共に、前記配線支持基材の前記主面に選択的に形成された導電層と、前記回路基板に配置されている別の配線層とを接合することを特徴とする請求項3記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2010−103382(P2010−103382A)

【公開日】平成22年5月6日(2010.5.6)

【国際特許分類】

【出願番号】特願2008−275014(P2008−275014)

【出願日】平成20年10月27日(2008.10.27)

【出願人】(591083244)富士電機システムズ株式会社 (1,717)

【Fターム(参考)】

【公開日】平成22年5月6日(2010.5.6)

【国際特許分類】

【出願日】平成20年10月27日(2008.10.27)

【出願人】(591083244)富士電機システムズ株式会社 (1,717)

【Fターム(参考)】

[ Back to top ]