半導体装置の製造方法

【課題】配線表面の酸化膜を除去する際の低誘電率絶縁膜の変質を抑える半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上のSiOC膜11表面に配線12を形成する工程と、配線12が表面に形成されたSiOC膜11を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝してSiOC膜11表面に緻密層14を形成する工程と、緻密層14が形成された後に、配線12の表面に形成された酸化膜13を除去する工程と、酸化膜13が除去された配線12、及び緻密層14上に絶縁膜としての拡散防止膜15を形成する工程と、を含み、酸化膜13を除去する工程から拡散防止膜15を形成する工程までが、大気に暴露されることなく行われる。

【解決手段】半導体装置の製造方法は、半導体基板10上のSiOC膜11表面に配線12を形成する工程と、配線12が表面に形成されたSiOC膜11を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝してSiOC膜11表面に緻密層14を形成する工程と、緻密層14が形成された後に、配線12の表面に形成された酸化膜13を除去する工程と、酸化膜13が除去された配線12、及び緻密層14上に絶縁膜としての拡散防止膜15を形成する工程と、を含み、酸化膜13を除去する工程から拡散防止膜15を形成する工程までが、大気に暴露されることなく行われる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の高性能化のために配線抵抗と配線間容量を低減する技術が開発され、配線抵抗を低減する技術として、ダマシンプロセスによるCu配線の形成方法がある。また、配線間容量を低減する技術として、Cu配線の周囲に形成される絶縁膜の低誘電率化が有効である。特に、低誘電率を有する絶縁膜として、微細な空孔を膜中に有するSiOC膜等の多孔性絶縁膜が知られている。

【0003】

この多孔性絶縁膜は、誘電率を低減させるために膜密度を減少させているため、例えば、多孔性絶縁膜の表面にCu配線を埋め込み形成するCMP(Chemical Mechanical Polishing)処理の後、露出したCu配線表面に形成された酸化膜をプラズマ処理によって除去する際における、多孔性絶縁膜の変質が顕著であった。

【0004】

そこで従来の技術として、SiOC膜表面に導電膜を埋め込む処理の後、露出した導電膜の表面に形成された酸化膜を、H2を主成分とした還元性ガスを用いた熱還元処理と還元性ガスを含むプラズマ処理とを併用することによって除去する半導体装置の製造方法が提案されている(例えば、特許文献1参照。)。

【0005】

この半導体装置の製造方法によると、H2を主成分とした還元性ガスを用いた熱還元処理後に、NH3とN2の還元性ガスを含むプラズマ処理が行われることから、上記熱還元処理による熱量の増加によってSiOC膜や導電膜にダメージを与えるほどに熱還元処理を行う必要がないので、SiOC膜の変質を抑えることができるとしている。

【0006】

しかし、還元性ガスを含むプラズマ処理による還元反応は、導電膜の表面と同時にSiOC膜に作用し、Si―O―Si結合、及びSi−CH3結合を分断し、Si−H、Si−OHを多く形成する変質がSiOC膜に発生するので、導電膜に含まれるCuの拡散を防止する拡散防止膜とSiOC膜の密着性不良、配線間容量及びリーク電流の増大等が発生するという問題がある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−67132号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、配線表面の酸化膜を除去する際の低誘電率絶縁膜の変質を抑える半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0009】

本発明の一態様は、半導体基板上のSiOC膜表面に配線を形成する工程と、前記配線が表面に形成された前記SiOC膜を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝して前記SiOC膜表面に緻密層を形成する工程と、前記緻密層が形成された後に、前記配線の表面に形成された酸化膜を除去する工程と、前記酸化膜が除去された前記配線、及び前記緻密層上に絶縁膜を形成する工程と、を含み、前記酸化膜を除去する工程から前記絶縁膜を形成する工程までが、大気に暴露されることなく行われる半導体装置の製造方法を提供する。

【発明の効果】

【0010】

本発明によれば、配線表面の酸化膜を除去する際の低誘電率絶縁膜の変質を抑えることができる。

【図面の簡単な説明】

【0011】

【図1】図1は、本発明の実施の形態に係る被処理体の要部断面図である。

【図2】図2は、本発明の実施の形態に係る半導体装置の製造方法において用いられるPECVD(Plasma-Enhanced Chemical Vapor Deposition)装置の要部断面図である。

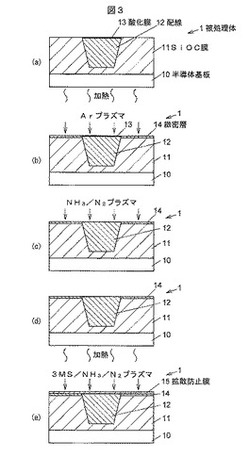

【図3】図3(a)〜(e)は、本発明の実施の形態に係る半導体装置の製造方法の工程を示す要部断面図である。

【図4】図4(a)〜(c)は、実施例に係る被処理体の要部断面図である。

【図5】図5(a)及び(b)は、比較例に係る被処理体の要部断面図である。

【図6】図6は、比誘電率に関するグラフである。

【図7】図7は、緻密層を含むSiOC膜表面からの深さとC濃度に関するグラフである。

【発明を実施するための形態】

【0012】

[実施の形態]

本発明の実施の形態に係る半導体装置の製造方法の一例を図面を参照して説明する。まず、被処理体を準備する。

【0013】

図1は、その被処理体の要部断面図である。この被処理体1は、例えば、図1に示すように、Siを主成分とするSi系基板からなる半導体基板10と、半導体基板10上に形成された多孔性絶縁膜であるSiOC膜11と、SiOC膜11の表面に露出し、Cuを主成分とするCu配線である配線12と、を備えて概略構成されている。なお、ここでは図示を省略したが、半導体基板10にはトランジスタ等の半導体素子が形成され、SiOC膜11には配線12を半導体素子に電気的に接続するためのプラグ等が形成されている。また、配線12の周囲には、配線12に含まれるCuのSiOC膜11中への拡散を防止するためのバリアメタル膜が形成されている。

【0014】

より具体的には、まず上記の半導体基板10上に、例えば、CVD(Chemical Vapor Deposition)法によってSiOC膜11を形成する。続いて、SiOC膜11に、例えば、フォトリソグラフィ法及びRIE(Reactive Ion Etching)法によって配線を形成するための溝を形成し、この溝に、例えばメッキ法によって金属膜を埋め込む。続いて、CMP法によってSiOC膜11上に形成された金属膜を除去して、SiOC膜11の表面に配線12が形成された被処理体1を得る。

【0015】

ここで、酸化膜13は、例えば、CMP処理等によってSiOC膜11の表面に配線12を埋め込み形成した後に、大気に暴露されることによって、配線12の露出した表面の酸化によって形成された膜である。

【0016】

図2は、本発明の実施の形態に係る半導体装置の製造方法に用いられるPECVD装置の要部断面図である。被処理体1は、このPECVD装置2の処理チャンバ20内にて後述する各工程が行われる。

【0017】

PECVD装置2は、例えば、図2に示すように、処理チャンバ20と、ガス流入口兼上部電極22と、ヒーター兼下部電極23と、を備えて概略構成されている。

【0018】

次に、この処理チャンバ20の内壁21に、保護膜としてSiCN膜を形成する。

具体的には、被処理体1を処理チャンバ20内に入れない状態で、ガス流入口兼上部電極22から3MS(Tri-Methyl-Silane)/NH3/N2混合ガスを処理チャンバ20内に導入し、処理チャンバ20内の圧力を7Torrに維持する。この3MS、NH3及びN2ガスの供給速度は、それぞれ400sccm、200sccm及び2000sccmである。続いて、ガス流入口兼上部電極22及びヒーター兼下部電極23間に、600W、13.56MHzの高周波電力を印加することによって処理チャンバ20内に3MS/NH3/N2プラズマを発生させ、処理チャンバ20の内壁21にSiCN膜を形成する。

【0019】

なお、処理チャンバ20の内壁21に形成される保護膜としては、SiCN膜の代わりに、例えば、SiN膜、SiC膜及びBN膜のうち少なくとも1つを含む絶縁膜等であっても良い。

【0020】

次に、被処理体1を上記のPECVD装置2のヒーター兼下部電極23の上に載せ、処理チャンバ20内を所定の雰囲気としての高真空状態にする。

【0021】

図3(a)〜(e)は、本発明の実施の形態に係る半導体装置の製造方法の工程を示す要部断面図である。

【0022】

次に、図3(a)に示すように、ヒーター兼下部電極23によって被処理体1を加熱する。

【0023】

次に、図3(b)に示すように、被処理体1を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝してSiOC膜11表面に緻密層14を形成する。

具体的には、ガス流入口兼上部電極22から希ガスとしてArガスを処理チャンバ20内に導入し、ガス流入口兼上部電極22及びヒーター兼下部電極23間に高周波電力を印加することによって処理チャンバ20内にArプラズマを発生させ、発生したArプラズマに被処理体1を5秒間曝す。SiOC膜11は、Arプラズマに曝されることによって、緻密層14が表面に形成される。続いて、高周波電力の供給とArガスの導入を停止する。

【0024】

ここで、緻密層14は、Arプラズマによって発生したArイオンが、SiOC膜11の表面に衝突することによってSiOC膜11の表面が緻密化されるとともに、Arプラズマによって内壁21の保護膜であるSiCN膜がスパッタされ、スパッタされたSiCNが、SiOC膜11の表面に付着することにより形成される。緻密層14は、後述する酸化膜13を除去する工程に用いられるNH3/N2プラズマによって発生したNH3イオン及びラジカル成分のSiOC膜11中への進入を阻害する。また、緻密層14の好ましい厚さは20nm以下、より好ましくは3〜10nmである。

【0025】

なお、上記のプラズマに曝す工程で用いる希ガスは、He、Ar、Ne及びXeのうち少なくとも1種のガスを含むガスであれば良い。また、Cu配線の場合、後述する拡散防止膜15としてSiN膜又はSiCN膜を用いるときは、Cu配線と拡散防止膜15との密着性の観点からSiOC膜11の緻密化処理と同時に、このCu配線の表面の窒化を行えるN2ガスを含むプラズマ処理が望ましい。

【0026】

次に、図3(c)に示すように、配線12の表面に形成された酸化膜13を除去する。

具体的には、ガス流入口兼上部電極22からNH3/N2混合ガスを処理チャンバ20内に導入し、ガス流入口兼上部電極22及びヒーター兼下部電極23間に高周波電力を印加することによって処理チャンバ20内にNH3/N2プラズマを発生させる。酸化膜13は、このNH3/N2プラズマによる還元反応によって除去される。

【0027】

なお、酸化膜13を除去する工程は、プラズマ又は加熱により活性化されたNH3、H2及びCOのうち少なくとも1種を含むガスに曝す工程でも良い。加熱の温度は、例えば、150〜400℃である。酸化膜13の除去が可能な処理であれば、上記の例に限定されず、例えば、NH3ガスの代わりとしてH2又はCO等の還元性ガスと、He、Ne、Xe等の希ガスからなる混合ガスでも良い。さらに、酸化膜13の除去が可能であれば、処理チャンバ20の外でプラズマ放電し、活性化された還元性ガスフロー処理でも良く、また活性化されていない還元性ガスフロー処理でも良い。

【0028】

次に、図3(d)に示すように、ヒーター兼下部電極23によって被処理体1を加熱する。

【0029】

次に、図3(e)に示すように、酸化膜13が除去された配線12、及び緻密層14上に絶縁膜として拡散防止膜15を形成する。

具体的には、この拡散防止膜15を形成する工程は、上記の内壁21にSiCN膜を形成する工程で用いた条件と同一の条件で処理チャンバ20内に3MS/NH3/N2プラズマを発生させ、SiCN膜からなる拡散防止膜15を形成する。ここで、先に配線12をNH3/N2プラズマに曝して配線12表面の酸化膜13を除去した場合は、拡散防止膜15の形成に当って処理チャンバ20内に3MSを追加導入するだけで良いため、スループットの点で有利である。

【0030】

なお、処理チャンバ20の内壁21の保護膜としては、配線間のリークの観点から絶縁膜が形成されるが、配線12の表面の酸化を防止するうえで、特に酸素を含まない膜であることが望ましい。また、配線12及びSiOC膜11と拡散防止膜15の密着性の観点から拡散防止膜15の組成に近い膜であることが望ましい。

【0031】

次に、所望の半導体装置を製造するための所定の工程を経て半導体装置を得る。

【0032】

なお、ここでは、図3(a)〜(e)に示した工程を高真空状態とした処理チャンバ20内で連続して行う場合を説明したが、少なくとも図3(c)に示した酸化膜13を除去する工程から図3(e)に示した拡散防止膜15を形成する工程までを大気に暴露されないよう上記の雰囲気中で連続して行えば良い。

【0033】

(実施の形態の効果)

上記の実施の形態における半導体装置の製造方法によると以下の効果が得られる。

(1)SiOC膜11の表面に緻密層14を形成することによって、配線12表面の酸化膜13を除去する際のSiOC膜11の変質を抑制することができ、SiOC膜11と拡散防止膜15の密着性の劣化、配線間容量及びリーク電流の増加を防止することができる。

(2)酸化膜13を除去する工程から拡散防止膜15を形成する工程まで、又は緻密層14を形成する工程から酸化膜13を除去する工程を経て拡散防止膜15を形成する工程までを同一の処理チャンバ20内で行うので、大気に暴露されずに各工程を行うことができ、歩留まり及びスループットが向上する。また、工程間の移動に伴うパーティクル等の付着を防止することができる。

(3)処理チャンバ20の内壁21に、拡散防止膜15の組成に近いSiCN膜を形成し、SiOC膜11の緻密化の際のArプラズマによってスパッタされたSiCNをSiOC膜11上に堆積させることで、よりSiOC膜11の変質を抑制する緻密層14を形成することができ、また拡散防止膜15との密着性が向上する。

【実施例】

【0034】

図4(a)〜(c)は、実施例に係る被処理体の要部断面図である。以下では、半導体基板10上に、厚さが100nm、比誘電率が2.6であるSiOC膜11が形成された実施例の被処理体3と比較例の被処理体4を用意し、上記の酸化膜13を除去する工程であるNH3/N2プラズマに曝す工程までを行った後の各SiOC膜11のC濃度を測定することによって、膜質変化の評価を行った。なお、処理チャンバ20の内壁21の保護膜は、実施の形態で保護膜を形成した条件と同一の条件で形成したSiCN膜を用いた。

【0035】

まず、図4(a)に示すように、被処理体3をヒーター兼下部電極23上に載せ、処理チャンバ20内の圧力を10Torr以下の高真空状態にし、ヒーター兼下部電極23によって被処理体3の温度が350〜400℃となるように加熱する。

【0036】

次に、Arガスをガス流入口兼上部電極22から処理チャンバ20内に導入し、処理チャンバ20内の圧力を5Torrに維持する。このArガスの供給速度は、1000sccmである。

【0037】

次に、図4(b)に示すように、ガス流入口兼上部電極22及びヒーター兼下部電極23間に500W、13.56MHzの高周波電力を印加し、処理チャンバ20内にArプラズマを発生させ、被処理体3をArプラズマに5秒間曝してプラズマ処理を行い、SiOC膜11の表面に緻密層14を形成する。この緻密層14の厚みは、およそ10nmである。続いて、高周波電力の供給とArガスの導入を停止する。

【0038】

次に、NH3とN2からなる混合ガスをガス流入口兼上部電極22から処理チャンバ20内に導入し、処理チャンバ20内の圧力を5Torrに維持する。この混合ガスの供給速度は、それぞれ2000sccmである。

【0039】

次に、図4(c)に示すように、ガス流入口兼上部電極22及びヒーター兼下部電極23間に200W、13.56MHzの高周波電力を印加し、処理チャンバ20内にNH3/N2プラズマを発生させ、被処理体3をNH3/N2プラズマに30秒間曝すプラズマ処理を行う。

【0040】

(比較例)

図5(a)及び(b)は、比較例に係る被処理体の要部断面図である。

【0041】

まず、図5(a)に示すように、実施例と同一の条件で被処理体4を加熱する。

【0042】

次に、実施例で行ったArプラズマ処理を行わずに、NH3とN2からなる混合ガスを、実施例と同一の条件で処理チャンバ20内に導入する。

【0043】

次に、図5(b)に示すように、実施例と同一の条件でNH3/N2プラズマによるプラズマ処理を行う。

【0044】

(評価)

上記の工程を経た被処理体3、4のSiOC膜11の比誘電率、及びSIMS(Secondary Ion-microprobe Mass Spectrometer:二次イオン質量分析計)分析によるC濃度のプロファイルを測定し、膜質変化の評価を行った。また、参照例として、実施例及び比較例と同様に、半導体基板上に比誘電率が2.6のSiOC膜が形成された被処理体を用意し、C濃度のプロファイルを測定した。

【0045】

図6は、比誘電率に関するグラフである。横軸には、比較例に対応する「NH3/N2プラズマ処理あり」、参照例として「NH3/N2プラズマ処理なし」、実施例に対応する「Arプラズマ処理後、NH3/N2プラズマ処理あり」を配し、縦軸は、それぞれの比誘電率を示している。

【0046】

測定の結果、比較例の比誘電率は、およそ3.1であり、参照例の比誘電率2.6に比べ、大きく上昇している。

【0047】

一方、実施例の比誘電率は、およそ2.7であり、参照例の比誘電率に比べて上昇するものの、比較例の比誘電率より値が小さく、比較例と比べて比誘電率の上昇が抑制されていることがわかる。

【0048】

図7は、緻密層を含むSiOC膜の表面からの深さとC濃度に関するグラフである。横軸は、緻密層を含むSiOC膜表面からの深さ(nm)であり、縦軸は、C濃度(a.u.)である。

【0049】

測定の結果、比較例の場合は、図7に示すように、参照例に比べ、SiOC膜11の表面からおよそ0〜50nmの深さまでのC濃度が低くなっている。これは、主に、SiOC膜11中のSi―CH3結合の破壊によってC濃度が低下したことを示している。

【0050】

一方、実施例の場合は、図7に示すように、参照例に比べ、SiOC膜11の表面からおよそ0〜30nmの深さまでのC濃度が低くなっており、特に最表面付近のC濃度が一時的に低下するものの、比較例に比べその後の低下は小さい。これは、C濃度の低下が、SiOC膜11の表面から浅い領域に抑制されていることを示している。つまり、緻密層14のおよその厚さが10nmであることから、この緻密層14が膜質の変化を抑制するので、特に緻密層14より深い領域において、C濃度の低下が抑制されていることがわかる。

【0051】

なお、本発明は、上記した実施の形態に限定されず、本発明の技術思想を逸脱あるいは変更しない範囲内で種々の変形および組み合わせが可能である。

【0052】

例えば、上記のArプラズマによるプラズマ処理の時間は5秒であったが、NH3/N2プラズマによるSiOC膜11の変質抑制効果が得られる条件であれば、これに限定されない。ただし、緻密化を目的としたプラズマ処理によってSiOC膜11が変質する可能性があるので、NH3/N2プラズマ処理の時間より短い方が望ましい。

【符号の説明】

【0053】

1、3、4…被処理体、10…半導体基板、11…SiOC膜、12…配線、13…酸化膜、14…緻密層、15…拡散防止膜、20…処理チャンバ

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の高性能化のために配線抵抗と配線間容量を低減する技術が開発され、配線抵抗を低減する技術として、ダマシンプロセスによるCu配線の形成方法がある。また、配線間容量を低減する技術として、Cu配線の周囲に形成される絶縁膜の低誘電率化が有効である。特に、低誘電率を有する絶縁膜として、微細な空孔を膜中に有するSiOC膜等の多孔性絶縁膜が知られている。

【0003】

この多孔性絶縁膜は、誘電率を低減させるために膜密度を減少させているため、例えば、多孔性絶縁膜の表面にCu配線を埋め込み形成するCMP(Chemical Mechanical Polishing)処理の後、露出したCu配線表面に形成された酸化膜をプラズマ処理によって除去する際における、多孔性絶縁膜の変質が顕著であった。

【0004】

そこで従来の技術として、SiOC膜表面に導電膜を埋め込む処理の後、露出した導電膜の表面に形成された酸化膜を、H2を主成分とした還元性ガスを用いた熱還元処理と還元性ガスを含むプラズマ処理とを併用することによって除去する半導体装置の製造方法が提案されている(例えば、特許文献1参照。)。

【0005】

この半導体装置の製造方法によると、H2を主成分とした還元性ガスを用いた熱還元処理後に、NH3とN2の還元性ガスを含むプラズマ処理が行われることから、上記熱還元処理による熱量の増加によってSiOC膜や導電膜にダメージを与えるほどに熱還元処理を行う必要がないので、SiOC膜の変質を抑えることができるとしている。

【0006】

しかし、還元性ガスを含むプラズマ処理による還元反応は、導電膜の表面と同時にSiOC膜に作用し、Si―O―Si結合、及びSi−CH3結合を分断し、Si−H、Si−OHを多く形成する変質がSiOC膜に発生するので、導電膜に含まれるCuの拡散を防止する拡散防止膜とSiOC膜の密着性不良、配線間容量及びリーク電流の増大等が発生するという問題がある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−67132号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、配線表面の酸化膜を除去する際の低誘電率絶縁膜の変質を抑える半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0009】

本発明の一態様は、半導体基板上のSiOC膜表面に配線を形成する工程と、前記配線が表面に形成された前記SiOC膜を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝して前記SiOC膜表面に緻密層を形成する工程と、前記緻密層が形成された後に、前記配線の表面に形成された酸化膜を除去する工程と、前記酸化膜が除去された前記配線、及び前記緻密層上に絶縁膜を形成する工程と、を含み、前記酸化膜を除去する工程から前記絶縁膜を形成する工程までが、大気に暴露されることなく行われる半導体装置の製造方法を提供する。

【発明の効果】

【0010】

本発明によれば、配線表面の酸化膜を除去する際の低誘電率絶縁膜の変質を抑えることができる。

【図面の簡単な説明】

【0011】

【図1】図1は、本発明の実施の形態に係る被処理体の要部断面図である。

【図2】図2は、本発明の実施の形態に係る半導体装置の製造方法において用いられるPECVD(Plasma-Enhanced Chemical Vapor Deposition)装置の要部断面図である。

【図3】図3(a)〜(e)は、本発明の実施の形態に係る半導体装置の製造方法の工程を示す要部断面図である。

【図4】図4(a)〜(c)は、実施例に係る被処理体の要部断面図である。

【図5】図5(a)及び(b)は、比較例に係る被処理体の要部断面図である。

【図6】図6は、比誘電率に関するグラフである。

【図7】図7は、緻密層を含むSiOC膜表面からの深さとC濃度に関するグラフである。

【発明を実施するための形態】

【0012】

[実施の形態]

本発明の実施の形態に係る半導体装置の製造方法の一例を図面を参照して説明する。まず、被処理体を準備する。

【0013】

図1は、その被処理体の要部断面図である。この被処理体1は、例えば、図1に示すように、Siを主成分とするSi系基板からなる半導体基板10と、半導体基板10上に形成された多孔性絶縁膜であるSiOC膜11と、SiOC膜11の表面に露出し、Cuを主成分とするCu配線である配線12と、を備えて概略構成されている。なお、ここでは図示を省略したが、半導体基板10にはトランジスタ等の半導体素子が形成され、SiOC膜11には配線12を半導体素子に電気的に接続するためのプラグ等が形成されている。また、配線12の周囲には、配線12に含まれるCuのSiOC膜11中への拡散を防止するためのバリアメタル膜が形成されている。

【0014】

より具体的には、まず上記の半導体基板10上に、例えば、CVD(Chemical Vapor Deposition)法によってSiOC膜11を形成する。続いて、SiOC膜11に、例えば、フォトリソグラフィ法及びRIE(Reactive Ion Etching)法によって配線を形成するための溝を形成し、この溝に、例えばメッキ法によって金属膜を埋め込む。続いて、CMP法によってSiOC膜11上に形成された金属膜を除去して、SiOC膜11の表面に配線12が形成された被処理体1を得る。

【0015】

ここで、酸化膜13は、例えば、CMP処理等によってSiOC膜11の表面に配線12を埋め込み形成した後に、大気に暴露されることによって、配線12の露出した表面の酸化によって形成された膜である。

【0016】

図2は、本発明の実施の形態に係る半導体装置の製造方法に用いられるPECVD装置の要部断面図である。被処理体1は、このPECVD装置2の処理チャンバ20内にて後述する各工程が行われる。

【0017】

PECVD装置2は、例えば、図2に示すように、処理チャンバ20と、ガス流入口兼上部電極22と、ヒーター兼下部電極23と、を備えて概略構成されている。

【0018】

次に、この処理チャンバ20の内壁21に、保護膜としてSiCN膜を形成する。

具体的には、被処理体1を処理チャンバ20内に入れない状態で、ガス流入口兼上部電極22から3MS(Tri-Methyl-Silane)/NH3/N2混合ガスを処理チャンバ20内に導入し、処理チャンバ20内の圧力を7Torrに維持する。この3MS、NH3及びN2ガスの供給速度は、それぞれ400sccm、200sccm及び2000sccmである。続いて、ガス流入口兼上部電極22及びヒーター兼下部電極23間に、600W、13.56MHzの高周波電力を印加することによって処理チャンバ20内に3MS/NH3/N2プラズマを発生させ、処理チャンバ20の内壁21にSiCN膜を形成する。

【0019】

なお、処理チャンバ20の内壁21に形成される保護膜としては、SiCN膜の代わりに、例えば、SiN膜、SiC膜及びBN膜のうち少なくとも1つを含む絶縁膜等であっても良い。

【0020】

次に、被処理体1を上記のPECVD装置2のヒーター兼下部電極23の上に載せ、処理チャンバ20内を所定の雰囲気としての高真空状態にする。

【0021】

図3(a)〜(e)は、本発明の実施の形態に係る半導体装置の製造方法の工程を示す要部断面図である。

【0022】

次に、図3(a)に示すように、ヒーター兼下部電極23によって被処理体1を加熱する。

【0023】

次に、図3(b)に示すように、被処理体1を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝してSiOC膜11表面に緻密層14を形成する。

具体的には、ガス流入口兼上部電極22から希ガスとしてArガスを処理チャンバ20内に導入し、ガス流入口兼上部電極22及びヒーター兼下部電極23間に高周波電力を印加することによって処理チャンバ20内にArプラズマを発生させ、発生したArプラズマに被処理体1を5秒間曝す。SiOC膜11は、Arプラズマに曝されることによって、緻密層14が表面に形成される。続いて、高周波電力の供給とArガスの導入を停止する。

【0024】

ここで、緻密層14は、Arプラズマによって発生したArイオンが、SiOC膜11の表面に衝突することによってSiOC膜11の表面が緻密化されるとともに、Arプラズマによって内壁21の保護膜であるSiCN膜がスパッタされ、スパッタされたSiCNが、SiOC膜11の表面に付着することにより形成される。緻密層14は、後述する酸化膜13を除去する工程に用いられるNH3/N2プラズマによって発生したNH3イオン及びラジカル成分のSiOC膜11中への進入を阻害する。また、緻密層14の好ましい厚さは20nm以下、より好ましくは3〜10nmである。

【0025】

なお、上記のプラズマに曝す工程で用いる希ガスは、He、Ar、Ne及びXeのうち少なくとも1種のガスを含むガスであれば良い。また、Cu配線の場合、後述する拡散防止膜15としてSiN膜又はSiCN膜を用いるときは、Cu配線と拡散防止膜15との密着性の観点からSiOC膜11の緻密化処理と同時に、このCu配線の表面の窒化を行えるN2ガスを含むプラズマ処理が望ましい。

【0026】

次に、図3(c)に示すように、配線12の表面に形成された酸化膜13を除去する。

具体的には、ガス流入口兼上部電極22からNH3/N2混合ガスを処理チャンバ20内に導入し、ガス流入口兼上部電極22及びヒーター兼下部電極23間に高周波電力を印加することによって処理チャンバ20内にNH3/N2プラズマを発生させる。酸化膜13は、このNH3/N2プラズマによる還元反応によって除去される。

【0027】

なお、酸化膜13を除去する工程は、プラズマ又は加熱により活性化されたNH3、H2及びCOのうち少なくとも1種を含むガスに曝す工程でも良い。加熱の温度は、例えば、150〜400℃である。酸化膜13の除去が可能な処理であれば、上記の例に限定されず、例えば、NH3ガスの代わりとしてH2又はCO等の還元性ガスと、He、Ne、Xe等の希ガスからなる混合ガスでも良い。さらに、酸化膜13の除去が可能であれば、処理チャンバ20の外でプラズマ放電し、活性化された還元性ガスフロー処理でも良く、また活性化されていない還元性ガスフロー処理でも良い。

【0028】

次に、図3(d)に示すように、ヒーター兼下部電極23によって被処理体1を加熱する。

【0029】

次に、図3(e)に示すように、酸化膜13が除去された配線12、及び緻密層14上に絶縁膜として拡散防止膜15を形成する。

具体的には、この拡散防止膜15を形成する工程は、上記の内壁21にSiCN膜を形成する工程で用いた条件と同一の条件で処理チャンバ20内に3MS/NH3/N2プラズマを発生させ、SiCN膜からなる拡散防止膜15を形成する。ここで、先に配線12をNH3/N2プラズマに曝して配線12表面の酸化膜13を除去した場合は、拡散防止膜15の形成に当って処理チャンバ20内に3MSを追加導入するだけで良いため、スループットの点で有利である。

【0030】

なお、処理チャンバ20の内壁21の保護膜としては、配線間のリークの観点から絶縁膜が形成されるが、配線12の表面の酸化を防止するうえで、特に酸素を含まない膜であることが望ましい。また、配線12及びSiOC膜11と拡散防止膜15の密着性の観点から拡散防止膜15の組成に近い膜であることが望ましい。

【0031】

次に、所望の半導体装置を製造するための所定の工程を経て半導体装置を得る。

【0032】

なお、ここでは、図3(a)〜(e)に示した工程を高真空状態とした処理チャンバ20内で連続して行う場合を説明したが、少なくとも図3(c)に示した酸化膜13を除去する工程から図3(e)に示した拡散防止膜15を形成する工程までを大気に暴露されないよう上記の雰囲気中で連続して行えば良い。

【0033】

(実施の形態の効果)

上記の実施の形態における半導体装置の製造方法によると以下の効果が得られる。

(1)SiOC膜11の表面に緻密層14を形成することによって、配線12表面の酸化膜13を除去する際のSiOC膜11の変質を抑制することができ、SiOC膜11と拡散防止膜15の密着性の劣化、配線間容量及びリーク電流の増加を防止することができる。

(2)酸化膜13を除去する工程から拡散防止膜15を形成する工程まで、又は緻密層14を形成する工程から酸化膜13を除去する工程を経て拡散防止膜15を形成する工程までを同一の処理チャンバ20内で行うので、大気に暴露されずに各工程を行うことができ、歩留まり及びスループットが向上する。また、工程間の移動に伴うパーティクル等の付着を防止することができる。

(3)処理チャンバ20の内壁21に、拡散防止膜15の組成に近いSiCN膜を形成し、SiOC膜11の緻密化の際のArプラズマによってスパッタされたSiCNをSiOC膜11上に堆積させることで、よりSiOC膜11の変質を抑制する緻密層14を形成することができ、また拡散防止膜15との密着性が向上する。

【実施例】

【0034】

図4(a)〜(c)は、実施例に係る被処理体の要部断面図である。以下では、半導体基板10上に、厚さが100nm、比誘電率が2.6であるSiOC膜11が形成された実施例の被処理体3と比較例の被処理体4を用意し、上記の酸化膜13を除去する工程であるNH3/N2プラズマに曝す工程までを行った後の各SiOC膜11のC濃度を測定することによって、膜質変化の評価を行った。なお、処理チャンバ20の内壁21の保護膜は、実施の形態で保護膜を形成した条件と同一の条件で形成したSiCN膜を用いた。

【0035】

まず、図4(a)に示すように、被処理体3をヒーター兼下部電極23上に載せ、処理チャンバ20内の圧力を10Torr以下の高真空状態にし、ヒーター兼下部電極23によって被処理体3の温度が350〜400℃となるように加熱する。

【0036】

次に、Arガスをガス流入口兼上部電極22から処理チャンバ20内に導入し、処理チャンバ20内の圧力を5Torrに維持する。このArガスの供給速度は、1000sccmである。

【0037】

次に、図4(b)に示すように、ガス流入口兼上部電極22及びヒーター兼下部電極23間に500W、13.56MHzの高周波電力を印加し、処理チャンバ20内にArプラズマを発生させ、被処理体3をArプラズマに5秒間曝してプラズマ処理を行い、SiOC膜11の表面に緻密層14を形成する。この緻密層14の厚みは、およそ10nmである。続いて、高周波電力の供給とArガスの導入を停止する。

【0038】

次に、NH3とN2からなる混合ガスをガス流入口兼上部電極22から処理チャンバ20内に導入し、処理チャンバ20内の圧力を5Torrに維持する。この混合ガスの供給速度は、それぞれ2000sccmである。

【0039】

次に、図4(c)に示すように、ガス流入口兼上部電極22及びヒーター兼下部電極23間に200W、13.56MHzの高周波電力を印加し、処理チャンバ20内にNH3/N2プラズマを発生させ、被処理体3をNH3/N2プラズマに30秒間曝すプラズマ処理を行う。

【0040】

(比較例)

図5(a)及び(b)は、比較例に係る被処理体の要部断面図である。

【0041】

まず、図5(a)に示すように、実施例と同一の条件で被処理体4を加熱する。

【0042】

次に、実施例で行ったArプラズマ処理を行わずに、NH3とN2からなる混合ガスを、実施例と同一の条件で処理チャンバ20内に導入する。

【0043】

次に、図5(b)に示すように、実施例と同一の条件でNH3/N2プラズマによるプラズマ処理を行う。

【0044】

(評価)

上記の工程を経た被処理体3、4のSiOC膜11の比誘電率、及びSIMS(Secondary Ion-microprobe Mass Spectrometer:二次イオン質量分析計)分析によるC濃度のプロファイルを測定し、膜質変化の評価を行った。また、参照例として、実施例及び比較例と同様に、半導体基板上に比誘電率が2.6のSiOC膜が形成された被処理体を用意し、C濃度のプロファイルを測定した。

【0045】

図6は、比誘電率に関するグラフである。横軸には、比較例に対応する「NH3/N2プラズマ処理あり」、参照例として「NH3/N2プラズマ処理なし」、実施例に対応する「Arプラズマ処理後、NH3/N2プラズマ処理あり」を配し、縦軸は、それぞれの比誘電率を示している。

【0046】

測定の結果、比較例の比誘電率は、およそ3.1であり、参照例の比誘電率2.6に比べ、大きく上昇している。

【0047】

一方、実施例の比誘電率は、およそ2.7であり、参照例の比誘電率に比べて上昇するものの、比較例の比誘電率より値が小さく、比較例と比べて比誘電率の上昇が抑制されていることがわかる。

【0048】

図7は、緻密層を含むSiOC膜の表面からの深さとC濃度に関するグラフである。横軸は、緻密層を含むSiOC膜表面からの深さ(nm)であり、縦軸は、C濃度(a.u.)である。

【0049】

測定の結果、比較例の場合は、図7に示すように、参照例に比べ、SiOC膜11の表面からおよそ0〜50nmの深さまでのC濃度が低くなっている。これは、主に、SiOC膜11中のSi―CH3結合の破壊によってC濃度が低下したことを示している。

【0050】

一方、実施例の場合は、図7に示すように、参照例に比べ、SiOC膜11の表面からおよそ0〜30nmの深さまでのC濃度が低くなっており、特に最表面付近のC濃度が一時的に低下するものの、比較例に比べその後の低下は小さい。これは、C濃度の低下が、SiOC膜11の表面から浅い領域に抑制されていることを示している。つまり、緻密層14のおよその厚さが10nmであることから、この緻密層14が膜質の変化を抑制するので、特に緻密層14より深い領域において、C濃度の低下が抑制されていることがわかる。

【0051】

なお、本発明は、上記した実施の形態に限定されず、本発明の技術思想を逸脱あるいは変更しない範囲内で種々の変形および組み合わせが可能である。

【0052】

例えば、上記のArプラズマによるプラズマ処理の時間は5秒であったが、NH3/N2プラズマによるSiOC膜11の変質抑制効果が得られる条件であれば、これに限定されない。ただし、緻密化を目的としたプラズマ処理によってSiOC膜11が変質する可能性があるので、NH3/N2プラズマ処理の時間より短い方が望ましい。

【符号の説明】

【0053】

1、3、4…被処理体、10…半導体基板、11…SiOC膜、12…配線、13…酸化膜、14…緻密層、15…拡散防止膜、20…処理チャンバ

【特許請求の範囲】

【請求項1】

半導体基板上のSiOC膜表面に配線を形成する工程と、

前記配線が表面に形成された前記SiOC膜を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝して前記SiOC膜表面に緻密層を形成する工程と、

前記緻密層が形成された後に、前記配線の表面に形成された酸化膜を除去する工程と、

前記酸化膜が除去された前記配線、及び前記緻密層上に絶縁膜を形成する工程と、

を含み、

前記酸化膜を除去する工程から前記絶縁膜を形成する工程までが、大気に暴露されることなく行われる半導体装置の製造方法。

【請求項2】

前記希ガスは、He、Ar、Ne及びXeのうち少なくとも1種のガスを含む請求項1に記載の半導体装置の製造方法。

【請求項3】

前記SiOC膜をプラズマに曝す処理の前に、SiN膜、SiCN膜、SiC膜及びBN膜のうち少なくとも1つを含む膜を処理チャンバの内壁に形成する工程を含む請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記酸化膜を除去する工程は、プラズマ又は加熱により活性化されたNH3、H2及びCOのうち少なくとも1種を含むガスに前記配線を曝す工程を含む請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記緻密層を形成する工程から前記絶縁膜を形成する工程までが、大気に暴露されることなく行われる請求項1〜4のいずれか1項に記載の半導体装置の製造方法。

【請求項1】

半導体基板上のSiOC膜表面に配線を形成する工程と、

前記配線が表面に形成された前記SiOC膜を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝して前記SiOC膜表面に緻密層を形成する工程と、

前記緻密層が形成された後に、前記配線の表面に形成された酸化膜を除去する工程と、

前記酸化膜が除去された前記配線、及び前記緻密層上に絶縁膜を形成する工程と、

を含み、

前記酸化膜を除去する工程から前記絶縁膜を形成する工程までが、大気に暴露されることなく行われる半導体装置の製造方法。

【請求項2】

前記希ガスは、He、Ar、Ne及びXeのうち少なくとも1種のガスを含む請求項1に記載の半導体装置の製造方法。

【請求項3】

前記SiOC膜をプラズマに曝す処理の前に、SiN膜、SiCN膜、SiC膜及びBN膜のうち少なくとも1つを含む膜を処理チャンバの内壁に形成する工程を含む請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記酸化膜を除去する工程は、プラズマ又は加熱により活性化されたNH3、H2及びCOのうち少なくとも1種を含むガスに前記配線を曝す工程を含む請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記緻密層を形成する工程から前記絶縁膜を形成する工程までが、大気に暴露されることなく行われる請求項1〜4のいずれか1項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2010−283136(P2010−283136A)

【公開日】平成22年12月16日(2010.12.16)

【国際特許分類】

【出願番号】特願2009−135118(P2009−135118)

【出願日】平成21年6月4日(2009.6.4)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成22年12月16日(2010.12.16)

【国際特許分類】

【出願日】平成21年6月4日(2009.6.4)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]