半導体装置の製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】シリコン基板1上に強誘電体キャパシタ37を形成する際、下部電極膜25の上に、アモルファス又は微結晶の酸化導電膜26を形成する。酸化導電膜26を熱処理により結晶化した後、強誘電体膜27の初期層27Aの形成時に酸化導電膜26を還元することにより、結晶粒が小さく且つ配向が整った第2の導電膜26Aを形成する。強誘電体膜27は、MOCVD法により形成し、その初期層27Aは第2の導電膜26Aの結晶配向に倣って成長する。これにより、強誘電体膜27の表面モフォロジが良好になる。

【解決手段】シリコン基板1上に強誘電体キャパシタ37を形成する際、下部電極膜25の上に、アモルファス又は微結晶の酸化導電膜26を形成する。酸化導電膜26を熱処理により結晶化した後、強誘電体膜27の初期層27Aの形成時に酸化導電膜26を還元することにより、結晶粒が小さく且つ配向が整った第2の導電膜26Aを形成する。強誘電体膜27は、MOCVD法により形成し、その初期層27Aは第2の導電膜26Aの結晶配向に倣って成長する。これにより、強誘電体膜27の表面モフォロジが良好になる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、強誘電体キャパシタを有する半導体装置の製造方法に関し、特に半導体基板上に形成され、記憶を保持するための強誘電体容量素子とメモリセルトランジスタとを備える強誘電体メモリの製造方法に関する。

【背景技術】

【0002】

近年、デジタル技術の進展に伴い、大容量のデータを高速に処理又は保存する傾向が高まっている。このため、電子機器に使用される半導体装置の高集積化及び高性能化が要求されている。

【0003】

そこで、半導体記憶装置に関しては、例えばDRAM(Dynamic Random Access Memory)の高集積化を実現するため、DRAMを構成する容量素子の容量絶縁膜として、従来のシリコン酸化物又はシリコン窒化物に代えて、強誘電体材料又は高誘電率材料を用いる技術が広く研究開発され始めている。このような、半導体記憶装置としては、電源を遮断しても記憶情報が消失しない不揮発性メモリであるフラッシュメモリや強誘電体メモリ(FeRAM)が知られている。

【0004】

FeRAMは、絶縁ゲート型電界効果トランジスタ(IGFET)のゲート絶縁膜中に埋め込まれたフローティングゲートを有し、フローティングゲートに記憶情報を表わす電荷を蓄積することによって情報を記憶する。このため、フラッシュメモリは、情報の書き込み及び消去の際に、絶縁膜を通過するトンネル電流を流す必要があり、比較的高い電圧が必要である。また、書き込み動作及び読み出し動作が可能な不揮発性RAMをさらに低電圧且つ高速で動作させるため、容量絶縁膜として自発分極特性を有する強誘電体膜を用いる技術も盛んに研究開発されている。

【0005】

FeRAMは、強誘電体キャパシタを構成する強誘電体のヒステリシス特性を利用して情報を記憶する。強誘電体キャパシタは、上部電極及び下部電極の一対の電極で強誘電体膜を挟んだ構成を有する。このような強誘電体キャパシタは、電極間の印加電圧に応じて分極を生じ、印加電圧を取り去っても自発分極を有することが知られている。このため、印加電圧の極性を反転させたときの自発分極の極性の反転を検出することで情報の読み出しが可能になる。このような、FeRAMは、フラッシュメモリに比べて低電圧で動作するので省電力で高速の書き込みが可能である。近年では、従来のロジック技術に、このFeRAMを取り入れたロジック混載チップ(SOC:System On Chip)が、ICカードなどの用途として検討されている。

【0006】

ここで、FeRAMに対しても一層の高集積化及び高性能化が要求されており、今後はセル面積の低減が必要になると考えられている。セル面積の低減には、従来のプレーナ構造に替えて、スタック構造を採用することが有効であることが知られている。なお、スタック構造とは、メモリセルを構成するトランジスタのドレイン上に形成されたプラグ(コンタクトプラグ)の直上にキャパシタを形成した構造をいう。

【0007】

従来のスタック構造のFeRAMにおいて、強誘電体キャパシタは、W(タングステン)製の導電性プラグの直上に、バリアメタル、下部電極、強誘電体膜及び上部電極がこの順で積層されて構成されている。バリアメタルは、導電性プラグの酸化を防止する役割を有する。バリアメタル及び下部電極は、通常、TiN膜、TiAlN膜、Ir膜、IrO2膜、Pt膜及びSRO(SrRuO3)膜のうちから選択された2以上の膜の組み合わせにより形成される。

【0008】

また、FeRAMの強誘電体キャパシタを構成する強誘電体膜は、チタン酸ジルコン酸鉛(PZT)、SrBi2Ta2O9(SBT、Y1)若しくはSrBi2(Ta、Nb)2O9(SBTN、YZ)、Bi4Ti3O9、(Bi,La)4Ti3O12、BiFeO3等のBi層状構造化合物等により形成されている。このような強誘電体膜は、例えば、ゾルゲル法や、スパッタ法、有機金属気相成長(MOCVD:Metal Organic Chemical Vapor Deposition)法等によって成膜される。

【0009】

FeRAMのような強誘電体メモリの電気特性を向上させ、かつ製品歩留まりを高めるためには、強誘電体を構成する膜の結晶の配向が均一になるように制御する必要がある。強誘電体膜の配向は、下部電極を構成する結晶の配向に大きく影響される。このため、下部電極の結晶の配向を均一にすれば、強誘電体膜の結晶の配向を均一にできる。従って、電気特性が良く、製品歩留まりの高い強誘電体メモリを作製するためには、下部電極の結晶の配向を均一にする必要がある。

【0010】

スタック構造の従来の強誘電体キャパシタの下部部電極として、例えば、上から順番にPt、IrO2、Irを積層させた構造が知られている。このような技術に関しては、例えば、特許文献1に開示されている。

また、下部電極の結晶性を向上させるために、下から順にIr、IrO、Pt、PtO、Ptの積層構造を形成することも検討されている。これに関連する技術としては、例えば、特許文献2や特許文献3に開示されている。この場合、導電性プラグの酸化を防止するために、Ir膜は200nm以上にすると良い。しかしながら、Ir膜を厚く堆積させると、エッチングが困難になる。

【0011】

酸素に対する安定性を増加させるためには、下部電極として例えば、Ir、IrOx、Pt、Pd、PdOx、Au、等の貴金属又は導電性酸化物を使用し、かつ下部電極の膜厚を30nm〜100nm程度の厚さにすることが検討されている。これに関連する技術としては、例えば、特許文献4に開示されている。

他のキャパシタの積層構造としては、密着層上に形成された下部電極と、下部電極上に形成された誘電体膜と、誘電体膜上に形成された浮遊電極と、浮遊電極上に形成され、誘電体膜とは配向方向が異なる別の誘電体膜と、別の誘電体膜上に形成された上部電極とを有するものが知れている。この場合、密着層としては、TiOx、Pt、Ti、PtOx、IrOx、ZrOx、TiN、TiAlNなどがあげられる。これに関連する技術としては、例えば、特許文献5に開示されている。

【0012】

ここで、下部電極又は上部電極は、複数の膜を積層させて製造することがある。この場合の積層構造としては、例えば、選択的な層(例えば酸素バリア層)、酸素源層(導電性酸化膜)、貴金属又は導電性酸化膜があげられる。これに関連する技術としては、例えば、特許文献6に開示されている。

【0013】

また、密着性の高い電極としては、第1の導電膜(IrO)と、第1の導電膜上に形成された第2の導電膜(Ir)と、第2の導電膜上に形成された第3の導電膜(Pt)とを有する積層構造が知られている。これに関連する技術としては、例えば、特許文献7に開示されている。また、導電性プラグの上に接着膜(Ti)、拡散防止膜(Ir、Ruなど)、金属酸化物膜(IrO2、RuO2、LSCO、SRO)、耐熱性金属膜(Ir、Pt、Ru、Rh、Os、Pa)を順番に積層した構造も開発されている。これに関連する技術としては、例えば、特許文献8に開示されている。

【0014】

また、酸素の拡散を防止する酸素バリア膜を下部電極に積層させた構造も知れている。このような積層構造としては、例えばIrO2/Ir/TiAlN/TiNがある。これに関連する技術としては、例えば、特許文献9に開示されている。さらに、下部電極の積層構造としては、TiAlN、Ti、Ptを順に形成することが知られている。これに関連する技術としては、例えば、特許文献10に開示されている。なお、電極の構造をIrにすると、電極上にPZT(チタン酸ジルコン酸鉛)を形成したときの疲労特性がPt電極上に比べて改善される。これに関連する技術としては、例えば、特許文献11に開示されている。

【0015】

また、下部電極を積層構造する場合には、例えば、Ir/Pt/Ir、Ir/Pt、Pt/Irのように、少なくともIr層を含めることが望ましいとされている。これに関連する技術としては、例えば、特許文献12に開示されている。

また、下部電極を構成する導電性膜の酸化を防止するために、導電性膜に貴金属膜を積層させ、貴金属膜上に強給電体膜を形成することがある。この場合の貴金属膜は少なくとも2層以上の積層構造として形成される。これに関連する技術としては、例えば、特許文献13に開示されている。

【0016】

さらに、誘電体キャパシタの製造方法には、密着膜上にPt製の下部電極膜を形成し、下部電極膜上に誘電体膜を形成し、誘電体膜上に上部電極を形成することが知られている。これに関連する技術としては、例えば、特許文献14に開示されている。なお、下部電極膜と誘電体膜の間に金属物質からなる拡散バリア膜を形成すると、下部電極と誘電体膜との間の元素の拡散を防止できる。これに関連する技術としては、例えば、特許文献15に開示されている。

【0017】

また、半導体記憶装置の構成としては、半導体基板上に形成した層間絶縁膜に導電性プラグを設け、導電性プラグに接続される電極を間絶縁膜上に形成した容量素子が知れている。電極には、酸素バリア膜として酸化イリジウム膜が設けられ、酸化イリジウム膜は平均結晶粒径が互いに異なる複数の層から構成する。例えば、酸化イリジウム膜を構成する複数の層のうち、上層の平均結晶粒径を上層の膜厚の1/2以下にし、下層の平均結晶粒径より小さくする。これに関連する技術としては、例えば、特許文献16に開示されている。

【0018】

さらに、下部電極を酸化物層と、その上に積層されたIr又はRuからなる金属膜との積層構造にすることもある。Ir又はRuからなる金属膜の上にさらに酸化物層を積層させることもある。これに関連する技術としては、例えば、特許文献17に開示されている。また、従来の電極は、Pt、Ir、Ru、IrO2、RuO2又はそれらの積層構造、或いは混合物から製造されている。これに関連する技術としては、例えば、特許文献18に開示されている。

【0019】

ところで、下部導体膜と誘電体膜との間に下部絶縁膜を形成すると、誘電体膜のリーク電流をより低減できる。これに関連する技術としては、例えば、特許文献19に開示されている。また、Ir膜の上に下部電極としてIrOx膜をスパッタしてから酸素雰囲気でアニールし、その上にPZT膜を成膜することが知られている。この場合、Irは450℃以上で成膜し、IrOxは、Ir膜の成膜温度以下、例えば300℃以上で成膜する。これに関連する技術としては、例えば、特許文献20に開示されている。

【0020】

PZTを成膜する際には、予めIrO2等の下部電極を形成してから急速熱処理(RTA)すると良い。下部電極を不活性ガス雰囲気中でアニールすることにより、PZT(111)の配向強度及びスイッチングチャージ(Qsw)が向上する。これに関連する技術としては、例えば、特許文献21に開示されている。

なお、下部電極のIrO2を成膜するとき、イリジウムフラックスと酸素の分圧比がQswに影響を与えることが知れている。これに関連する技術としては、例えば、特許文献22に開示されている。

【特許文献1】特開平9−22829号公報

【特許文献2】特開2003−92391号公報

【特許文献3】特開2004−153006号公報

【特許文献4】特開2003−318371号公報

【特許文献5】特開2003−209179号公報

【特許文献6】特開2000−357777号公報

【特許文献7】特開2001−91539号公報

【特許文献8】特開2001−111007号公報

【特許文献9】特開2005−159165号公報

【特許文献10】特開2004−95638号公報

【特許文献11】特開2000−164818号公報

【特許文献12】特開2003−298136号公報

【特許文献13】特開平11−145418号公報

【特許文献14】特開2002−151662号公報

【特許文献15】特許平06−326270号公報

【特許文献16】特開2003−51583号公報

【特許文献17】特開2000−239140号公報

【特許文献18】特開2005−104676号公報

【特許文献19】特開2003−264187号公報

【特許文献20】特開2003−68991号公報

【特許文献21】特開2000−91551号公報

【特許文献22】特開2000−91270号公報

【発明の開示】

【発明が解決しようとする課題】

【0021】

電気特性が良く、製品歩留まりの高い強誘電体メモリを作製するためには、強誘電体の配向を均一にする必要がある。しかしながら、MOCVD法で強誘電体膜を形成すると、強誘電体膜の結晶の配向が下層の結晶配向の影響を受け易かった。

この発明は、強誘電体膜の結晶の配向を均一にできる半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0022】

本願の一観点によれば、基板の上方に第1の導電膜を形成する工程と、前記第1の導電膜上にアモルファス又は微結晶からなる導電酸化膜を形成する工程と、前記導電酸化膜を熱処理によって結晶化させる工程と、前記導電酸化膜を還元して第2の導電膜を形成する工程と、前記第2の導電膜上に強誘電体膜を形成する工程と、前記強誘電体膜上に第3の導電膜を形成する工程と、有することを特徴とする半導体装置の製造方法とした。

【発明の効果】

【0023】

本発明によれば、アモルファス又は微結晶として形成した酸化導電膜を熱処理して結晶化させ、この後に還元して第2の導電膜を形成するので、第2の導電膜の結晶性が良好になる。このような第2の金属膜上に第1強誘電体膜を形成すると、第1強誘電体膜の結晶性が向上して表面のモフォロジが良好になる。これにより、信頼性の高い半導体装置が得られる。

【発明を実施するための最良の形態】

【0024】

(第1実施の形態)

本発明の第1実施の形態について図面を参照して詳細に説明する。

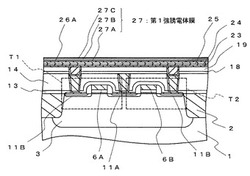

図1A〜図1Lは、本発明の第1実施形態に係る半導体装置の製造途中の断面図である。なお、本実施の形態に係る半導体装置は、スタック構造の強誘電体キャパシタを有する半導体記憶装置(強誘電体メモリ)である。

【0025】

最初に、図1Aに示す断面構造を得るまでの工程について説明する。

まず、n型又はp型のシリコン基板1(半導体基板)の表面に、トランジスタの活性領域を画定する素子分離絶縁膜2を形成する。この実施の形態では素子分離絶縁層2として、シャロートレンチアイソレーション(STI)を形成する。STIは、シリコン基板1の素子分離領域に溝を形成し、その中に酸化シリコン等の絶縁膜を埋め込むことにより形成される。なお、素子分離絶縁層2は、STIに限られず、LOCOS(Local Oxidation of Silicon)法で形成した絶縁膜であっても良い。

【0026】

次いで、シリコン基板1のメモリセル領域におけるトランジスタ活性領域にp型不純物、例えばボロンを導入してpウェル3を形成する。そして、トランジスタ活性領域の表面を熱酸化させてゲート絶縁膜5を形成する。この場合のゲート絶縁膜5は、熱酸化によるシリコン酸化膜であり、その厚さは約6〜7nmである。

【0027】

さらに、シリコン基板1の全面に、非晶質又は多結晶のシリコン膜を形成し、フォトリソグラフィ技術を用いてパターニングしてゲート電極6A,6Bを形成する。シリコン膜を例えば厚さ約50nmとする。

【0028】

ゲート電極6A,6Bは、pウェル3上に間隔をおいて互いに平行に二つ形成され、その各々がワード線の一部を構成する。さらに、ゲート電極6A,6Bをマスクにしたイオン注入により、ゲート電極6A,6Bの両側のシリコン基板1の表層にn型不純物、例えばリンを導入し、ソース/ドレインエクステンション8A,8Bを形成する。

この後に、ゲート電極6A,6Bを含むシリコン基板1の上側全面に絶縁膜を形成し、その絶縁膜をエッチバックしてゲート電極6A,6Bの両側部分のみを残して絶縁性サイドウォール10を形成する。絶縁膜には、例えばCVD法により形成された酸化シリコン膜が用いられる。

【0029】

続いて、絶縁性サイドウォール10とゲート電極6A,6Bをマスクにしてシリコン基板1の表層に砒素等のn型不純物を再びイオン注入し、各ゲート電極6A,6Bの側方のシリコン基板1にソース/ドレイン領域11A,11B(高濃度不純物拡散領域)を形成する。

さらに、ゲート電極6A,6Bを含むシリコン基板1の上側全面に金属膜をスパッタ法により形成する。金属膜は、例えば、コバルト膜等の高融点金属が好ましいが、比較的に融点が低い金属であっても良い。そして、この金属膜を加熱してシリコンと反応させることにより、ゲート電極6A,6Bの上面と、ソース/ドレイン領域11A,11Bにおけるシリコン基板1上にそれぞれにコバルトシリサイド層等の金属シリサイド層12a、12bを形成する。この熱処理によって、各ソース/ドレイン領域11A,11Bが活性化されて低抵抗化する。

【0030】

その後に、素子分離絶縁膜2上などで未反応となっている高融点金属膜をウエットエッチングによって除去する。

ここまでの工程で、シリコン基板1の活性領域ごとに、ゲート絶縁膜5、ゲート電極6A,6B、ソース/ドレイン領域11A,11B等によって構成される2つのMOSトランジスタT1,T2が形成される。

【0031】

次に、ゲート電極6A,6Bを含むシリコン基板1の上側全面に、酸化防止絶縁膜13(カバー膜)としてプラズマCVD法で酸窒化シリコン(SiON)膜を厚さ約200nmに形成する。さらに、TEOS(tetra ethoxy silane)ガスを使用するプラズマCVD法により、酸化防止絶縁膜13の上に第1層間絶縁膜14として酸化シリコン(SiO2)膜を厚さ約1000nmに形成する。なお、TEOSを用いてプラズマCVD法によって形成されるSiO2膜を以下においてTEOS膜という。

そして、第1層間絶縁膜14の表面を化学的機械研磨 (CMP:Chemical Mechanical Polishing)法で研磨して平坦化させ、シリコン基板1の表面から第1層間絶縁膜14の表面までの膜厚を所定値、例えば、約700nmに調整する。

【0032】

次に、図1Bに示す断面構造を得るまでの工程について説明する。

まず、酸化防止絶縁膜13と第1層間絶縁膜14とをフォトリソグラフィ法によってパターニングして、コンタクトホール15A,15B,15Cを形成する。コンタクトホール15A〜15Cの深さはソース/ドレイン領域11A,11Bのそれぞれの高融点金属シリサイド層12a、12bに到達するまでとし、その径は例えば0.25μmにする。

【0033】

そして、コンタクトホール15A〜15Cを用いてソース/ドレイン領域11A,11Bに電気的に接続される導電性プラグ16A,16B,16Cを形成する。具体的には、コンタクトホール15A〜15Cの内面に厚さが30nmのチタン(Ti)膜と、厚さが20nmの窒化チタン(TiN)膜とを順番にスパッタ法等により形成し、2層の積層構造を有する密着膜(グルー膜)17Aを作製する。さらに、密着膜17A上にタングステン(W)膜17BをCVD法により成長させる。この膜厚は、第1層間絶縁膜14上で、例えば300nmとし、W膜17Bでコンタクトホール15A〜15Cの空隙を埋める。第1層間絶縁膜14の上面上に成長した余分なW膜17B及び密着膜17BをCMP法で除去する。これにより、コンタクトホール15A〜15Cには、それぞれ導電性プラグ16A,16B,16Cが形成される。

【0034】

さらに、第1層間絶縁膜14上及び導電性プラグ16A〜16C上に、第1酸化防止膜18として、SiON膜を例えばプラズマCVD法により例えば130nmの膜厚に形成する。さらに、第1酸化防止膜18の上に第2層間絶縁膜19として、シリコン酸化膜を例えばTEOSを原料とするプラズマCVD法によって300nmの膜厚で形成する。なお、酸化窒化シリコン(SiON)膜の代わりに窒化シリコン(SiN)膜やアルミナ(Al2O3)膜を形成しても良い。

【0035】

次に、図1Cに示す断面構造を得るまでの工程について説明する。

第2層間絶縁膜19上に図示を省略するレジスト膜を第2層間絶縁膜19上にスピンコート法等により塗布し、フォトリソグラフィ技術によって導電性プラグ16A上と導電性プラグ16B上のそれぞれに開口部を1つずつ形成する。そして、このようなレジストパターンをマスクとして使い、第2層間絶縁膜19及び第1酸化防止膜18をドライエッチングし、コンタクトホール15A,15Bに接続されるビアホール20A,20Bを形成する。ビアホール20A,20Bには、導電性プラグ21A,21Bが埋め込まれる。導電性プラグ21A,21Bは、導電性プラグ16A、16Bと同様のプロセスで作製される密着層22AとW層22Bとから形成される。

【0036】

第2層間絶縁膜19の上に形成された余分な密着層22A及びW層22Bは、CMP法による研磨で除去する。CMP法では、研磨対象である密着層22A及びW層22Bの研磨速度が下地の第2層間絶縁膜19よりも速くなるようなスラリ、例えばキャボット・マイクロエレクトロニクス社製のSSW2000を使用する。そして、第2層間絶縁膜19上に研磨残を残さないために、このCMPの研磨量は密着層22A及びW層22Bの合計膜厚よりも厚く設定する。即ち、ここでのCMP研磨はオーバー研磨とする。

【0037】

次に、図1Dに示す断面構造を得るまでの工程について説明する。

第2層間絶縁膜19の表面をNH3プラズマで処理することにより、表面の酸素原子にNH基を結合させる。これによって、第2層間絶縁膜19上にTi原子をさらに堆積させてもTi原子が酸素原子に捕獲されてしまうことがなくなり、第2層間絶縁膜19の表面を自在に移動できるようになる。つまり、第2層間絶縁膜19上にTi膜が所定の結晶配向、例えば、(002)配向に自己組織化できるようになり、その上面の平坦性を改善できる。

【0038】

なお、アンモニアプラズマ処理は、例えばシリコン基板1に対して約9mm(350mils)離間した位置に対向電極を設置する構造を有する平行平板型のプラズマ処理装置を用いて実施する。処理条件は、例えば、266Pa(2Torr)の圧力下、400℃の基板温度に保持された処理容器中にアンモニアガスを350sccmの流量で供給し、シリコン基板1側に13.56MHzの高周波を100Wのパワーで、また対向電極に350kHzの高周波を55Wのパワーで、60秒間供給することにより実行する。

【0039】

次に、シリコン基板1とターゲットの間の距離を60mmに設定したスパッタ装置中で、0.15Paのアルゴン(Ar)雰囲気下、20℃の基板温度で2.6kWのスパッタDCパワーを5秒間供給した。これによって、第2層間絶縁膜19と導電性プラグ21A,21Bの上に、強い(002)配向のTi膜が約20nmの厚さに形成される。

【0040】

さらに、Ti膜を窒素の雰囲気中において基板温度650℃で60秒のRTAを行うことにより、Ti膜を(111)配向のTiN膜からなる下地導電膜23に変える。

次に、下地導電膜23の上に酸素拡散バリア膜24として窒化チタンアルミニウム(TiAlN)膜を形成する。TiAlN膜は、例えば、Ti及びAlの合金化したターゲットを使った反応性スパッタにより100nmの厚さに形成する。成膜条件は、例えばArを40sccm及び窒素を10sccmの流量で供給した混合雰囲気において、253.3Paの圧力、400℃の基板温度、1.0kWのスパッタパワーに設定する。

【0041】

さらに、酸素拡散バリア膜24上に第1の導電膜である下部電極膜25を形成する。下部電極膜25は、貴金属、例えばIrをAr雰囲気中で、0.2Paの圧力、450℃の基板温度、0.3kWのスパッタパワーで60nm〜100nmの厚さに形成する。下部電極膜25は、Irの代わりにRu、Rh又はPdで形成しても良い。

酸化拡散バリア層24と下部電極25は、TiNの下地導電膜23の結晶方位を受け継いで(111)に優先配向する。

【0042】

この後、図1Eに示すように、不活性ガス、例えばArガスの雰囲気中で、下部電極膜25に対して650℃〜750℃、60秒間、RTAを行う。この熱処理によってIrの結晶性が向上し、さらに、下地導電膜23、酸素拡散バリア膜24及び下部電極膜25の各層の密着性が向上する。

【0043】

次に、図1Fに示すように、下部電極膜25の上に、スパッタ法により酸化導電膜26を形成する。酸化導電膜26は、貴金属酸化膜、例えば、IrOx膜からなり、その厚さは5nm〜50nmとする。この場合、酸化導電膜26は下部電極25を構成する金属の酸化物である。IrOx膜の成膜条件は、例えば、Arと酸素の混合雰囲気中で、0.11Paの圧力、10℃〜100℃、より好ましくは50℃〜75℃の基板温度で、1kWのスパッタパワーに設定する。スパッタ用のターゲットはイリジウムである。

そのような条件で形成された酸化導電膜26は、少なくともアモルファス、微結晶のいずれかの状態、即ち、アモルファス、微結晶、又はアモルファスと微結晶が混在する状態となっている。

【0044】

ここで、IrOx膜の酸化度及び結晶性は、その上に成膜する強誘電体膜(PZT膜)の結晶性に影響を与える。そして、成膜時のArと酸素の混合雰囲気の酸素比率、成膜レート(スパッタパワー)、成膜温度、及び膜厚さは、IrOx膜の酸化度及び結晶性に大きな影響を与える。IrOx膜の酸化度が高すぎたり、或いは低すぎたりすると、熱処理するときに再酸化して結晶の異常成長を引き起こし易くなる。さらに、後に説明する還元工程で酸化導電膜26を均一に還元することが困難になる。

【0045】

そこで、IrOx膜の形成条件として、例えば成膜雰囲気にArと酸素(O2)をそれぞれ188sccmと12sccmの流量で導入するとともに、成膜パワーを0.5kW、成膜時間を15秒、成膜レートを1.6nm/秒、成膜温度を60℃とする。ここで、ArとO2の全流量中でのO2の流量比PO2は6流量%である。この条件により形成するIrOx膜の厚さを25nmとする。IrOx膜の形成条件の詳細については、後のPZT形成工程の説明に併せてさらに詳述する。

【0046】

次に、図1Gに示すように、そのような条件で形成したIrOx膜を大気圧下、又は1Paから大気圧までの範囲の圧力下でRTAにより加熱して結晶化する。加熱温度は600℃以上、750℃以下が望ましい。この加熱温度の詳細についてもPZT形成工程の説明に併せてさらに詳述する。

【0047】

続いて、図1Hに示すように、酸化導電膜26であるIrOx膜の上に、第1強誘電体膜27としてPZT膜を形成する。この実施の形態では、PZT膜として、最初にMOCVD法によって初期層27A及びコア層27Bを形成した後に、スパッタ法によってコア層27B上に表層部27Cを形成する。

より詳細には、酸化導電膜26を形成したシリコン基板1をMOCVD装置のチャンバにセットする。そして、図2に示すように、チャンバ内にO2ガスをチャンバ内に、例えば、2000sccm流してから、シリコン基板1を目標温度、即ち第1強誘電体膜27のうちの初期層27A及びコア層27Bの形成温度まで昇温させる。なお、この昇温過程では、熱処理で結晶化させた酸化導電膜26のIrOxが再度酸化されることはない。

【0048】

目標温度に到達したら、図2に示すように、第1強誘電体膜27の原料ガスを導入して初期層27Aの形成を開始する前にインターバルを設け、ArガスとO2ガスのそれぞれの流量を初期層27Aの形成に必要な流量に切り替える。具体的には、Arガスの流量を1375sccmに切り替え、O2ガスの流量を625sccmに切り替えた。この場合の酸素比率は0.33倍である。なお、酸素比率は、PZT形成に用いられる有機金属原料と反応させるために必要な酸素量に対する実際の酸素量の割合を示す。

【0049】

そして、インターバルにおいて、Arガス及びO2ガスのそれぞれの流量の調整を終えた後に、第1強誘電体膜27の原料ガスを導入し、初期層27Aの形成を開始する。

PZT膜を構成するPb,Zr,Tiは、それぞれが液体原料として予め調製されている。ここで、Pb原料としてテトラキスジメチルへプタンジオネート鉛(Pb(DMHD)2)を、Zr原料としてテトラキスジメチルへプタンジオネートジルコニウム(Zr(DMHD)4)を、Ti原料としてビスイソプロポキシビスジピバロイルメタネートチタン(Ti(O−iPr)2(DPM)2)をそれぞれ使用した。これらの原料を、それぞれ酢酸ブチルに0.2mol/L(モル/リットル)、0.1mol/L、0.1mol/Lの濃度で溶解させ、Pb,Zr,Tiの各液体原料を製造した。そして、これら原料ガスの流量は、Pbの原料ガスの流量と、Zrの原料ガスの流量と、Tiの原料ガスの流量と、酢酸ブチルの流量との総量が常に1.2mL(ミリリットル)/分になるように制御する。

【0050】

具体的には、各液体原料の流量を制御しながら、MOCVD装置の気化器へ供給する。PZTの堆積レートは、各液体原料の流量で制御できる。例えば、成膜レートを0.04nm/秒に制御したい場合は、流量0.95mL/分の酢酸ブチル溶媒と共に、Pb,Zr,Tiの液体原料をそれぞれ0.1mL/分、0.07mL/分、0.08mL/分の流量で供給して気化させる。これに対して、堆積レートを0.17nm/秒に制御したい場合は、流量0.30mL/分の酢酸ブチル溶媒と共に、Pb,Zr,Tiの原料液体をそれぞれ0.26mL/分、0.34mL/分、0.30mL/分の流量で供給して気化させる。

【0051】

このような流量で原料ガスをチャンバ内に導入し、初期層27Aを厚さ2.5nm〜10nmに形成する。初期層27Aの形成段階では、結晶化された酸化導電膜26が、原料ガス中の溶媒成分によって均一に還元される。その結果、酸化導電膜26が均一で、且つ粒子が小さい結晶からなる第2の導電膜26Aに改質される。

【0052】

この段階では、チャンバ内の酸素比率は、0.33であり、この値は、O2の量がPb等の有機金属の原料成分と反応するのに必要とされる量に比べて不足していることを意味する。このため、原料ガス中の有機金属原料成分は、チャンバ内にあるO2ガスに加えて、酸化導電膜26中の酸素原子とも反応する。これによって、初期層27の形成と同時に、酸化導電膜26が還元されて第2の導電膜26Aが形成される。

【0053】

酸化導電膜26を還元した後にX線回折を行ったところ、図3に示すように、矢印A1や矢印A2の付近に現れるはずのIrOxのピークは確認されなかった。このことから、酸化導電膜26のIrOxが還元されてIrが形成されたことが分かる。

【0054】

IrOx膜の還元により形成される第2の導電膜26Aは、下部電極膜25を構成するIrの配向性を制御することにより、Irの(111)面を優先的に配向させられる。このため、第2の導電膜26Aの上には、PZTの(111)面を優先的に配向させた初期層27Aを形成することが可能である。初期層27Aの膜厚は、膜厚2.5nm〜10nmであることが望ましい。初期層27Aの膜厚が2.5nmを下回ると、成膜時間が短くなるので酸化導電膜26が還元され難くなり、初期層27Aの配向性が悪くなる傾向がある。また、初期層27Aの膜厚が10nmを上回ると、PZTの酸素欠損等の影響によって最終的に得られる強誘電体キャパシタのスイッチング電荷量が低くなる傾向がある。

【0055】

ところで、酸化導電膜26を構成するIrOx膜を還元してIrからなる第2の導電膜26Aにするためには、IrOx膜を最適な条件で形成することが重要である。

【0056】

例えば、スパッタ法によりIrOx膜を形成する際のスパッタパワーを0.5kWに設定した場合には、ArとO2の混合雰囲気中の酸素流量比は4流量%以上且つ10流量%以下であることが望ましい。これに対して、スパッタパワーを0.5kWよりも大きくする場合は酸素流量比をさらに高くすることが好ましい。これに対してスパッタパワーを0.5kWよりも小さくする場合には酸素流量比をさらに低くする必要がある。

また、酸化導電膜26の膜厚は、10nm〜40nmが望ましい。酸化導電膜26がそれよりも薄くなると、その後の熱処理時に下部電極膜25が酸化し易くなる。これに対して酸化導電膜26がそれよりも厚すぎると、PZTの初期層27A形成時の還元工程で酸化導電膜26を十分に還元させることができなくなる。

【0057】

さらに、酸化導電膜26は、アモルファス又は均一な微結晶であることが望ましい。成膜時に結晶の酸化導電膜26を形成しようとすると、成膜初期状態で均一な膜質が得られ難い。また、そのような結晶質の膜は、図2に示した昇温時に再酸化され易く、上記の還元工程において膜を均一に還元することが困難になる。酸化導電膜26のように、アモルファス又は略均一な微結晶の膜を形成すれば、上記のような還元雰囲気中に曝したときに、IrOxを均一に形成し、且つIrOxの還元により結晶粒径が小さいIrを形成することができる。

【0058】

均一で、且つ結晶粒径の小さいIrを形成すれば、上記のようにPZTの結晶性を向上でき、PZT膜の表面のモフォロジを改善できる。これにより、製品の歩留まりを向上できる。これと当時に、下部電極膜25と強誘電体膜の界面が確実に形成され、電気特性に優れる。特に、低電圧で動作させたときの電気特性に優れる。

【0059】

そこで、この実施の形態では、酸化導電膜26の成膜条件を上記の条件に設定した。その条件で形成した酸化導電膜26のX線回折結果を図4Aに示す。図4Aによれば、(200)面のシリコンを示すピークのみが観測され、IrOxの結晶ピークは確認されなかった。このことから、酸化導電膜26がアモルファス又は微結晶で形成されたことが分かる。

【0060】

さらに、酸化導電膜26の成膜後に、シリコン基板1を600℃以上、より好ましくは700℃以上で、且つ750℃以下の温度でRTA処理した。

なお、熱処理温度が600℃より低い場合は、図2に示す昇温時に異常酸化が発生し易くなる。これに対し、熱処理温度が750℃を越えると、CMOSのトランジスタ特性が熱履歴の影響により初期状態から変化し易くなる。このため、この実施の形態では、酸化導電膜26形成後の熱処理の温度をその一例として650℃に設定する。また、このときの圧力は、常圧以下で0.1Paより高く設定した。これにより、酸化導電膜26のIrOxが均一に結晶化される。

【0061】

ここで、図4BにXRD(X-ray diffraction)回折測定結果を示す。XRD回折のデータは、酸化導電膜26を上記の条件により熱処理する前(Before Annealing)と後(Annealed)のそれぞれについて測定した結果である。熱処理前では、矢印B1に示すIr(111)のピークのみが確認された。矢印B1のピークは、下地である下部電極25のIrに起因するピークであると考えられる。これに対して、熱処理後では、矢印B1に示すIr(111)のピークと、矢印B2に示すIr(101)のピーク(28.06°)、矢印B3に示す(110)のピーク(34.76°)、矢印B4に示す(211)のピーク(54.02°)が確認された。この測定結果から熱処理によって酸化導電膜26が結晶化されたことがかわる。

【0062】

以上のように第2の導電膜26Aと初期層27Aを形成した後に、図2に示すように、原料ガスの導入を一旦停止する。そして、PZT成長再開までのインターバルに、ArガスとO2ガスの流量を、コア層27Bを形成するための流量条件に切り替える。この実施の形態では、Arガスの流量を0sccmに切り替え、O2ガスの流量を4500sccmに切り替えた。ここでの酸素比率は、有機金属原料と反応させるために必要な酸素量の6.77倍である。そして、ガス流量を切り替えた後に、原料ガスを再び導入してコア層27Bの形成を開始する。コア層27Bの形成段階では、O2量が過剰な状態で原料ガスを導入するので、酸素欠損の少ないコア層27Bが形成される。また、コア層27Bは、(111)面に優先配向された初期層27A上に形成されるので、(111)面に優先配向して形成される。

【0063】

以上のようなMOCVD法によるPZT成膜工程は、チャンバ内の圧力を665Paとし、基板温度を620℃に保持し、原料ガスをトータルで620秒間供給することにより実施され、全体として膜厚100nmの初期層27A及びコア層27Bを形成する。

【0064】

なお、第1強誘電体膜27の形成にあたっては、初期層27Aの堆積速度、即ち成膜レートを低い値に設定し、その後のコア層27Bの成膜レートを相対的に高い値に設定することが望ましい。例えば、初期層27Aの成膜レートは0.1nm/秒以下、好ましくは0.05nm/秒以下、より好ましくは0.04nm/秒以下に設定される。また、コア層27Bの成膜レートは、例えば0.17nm/秒に設定される。

【0065】

初期層27Aの成膜レートが0.1nm/秒を上回ると、その上に形成されるコア層27Bのモフォロジが悪化し、最終的に得られる強誘電体キャパシタのスイッチング電荷量が低くなる傾向がある。初期層27Aを0.1nm/秒以下の成膜レートで形成した強誘電体キャパシタのスイッチング電荷量が40μC/cm2であったのに対し、初期層27Aをコア層27Bと同じ0.17nm/秒の成膜レートで形成した強誘電体キャパシタのスイッチング電荷量は32μC/cm2と低かった。

【0066】

このようにして形成した第1強誘電体膜27は、その表面が平坦であった。また、従来のPZT膜のように、モフォロジの不均一さに起因して発生すると考えられる膜の白濁も解消された。

【0067】

ここで、下部電極膜25と酸化導電膜26を形成した後の熱処理条件が第1強誘電体膜27の結晶性に与える影響について再び検討する。下部電極膜25を形成した後の熱処理は、Ar雰囲気中、基板温度を650℃で60秒間実施した。さらに、酸化導電膜26を形成した後、熱処理の温度及び時間は650℃及び60秒とした。

【0068】

まず、酸化導電膜26の成膜温度が第1強誘電体膜27の結晶性に与える影響を調べた結果を図5A及び図5Bに示す。第1強誘電体膜27を形成した後に中央(Center)と、上側(Top)と、右側(Right)の3箇所でX線回折を行ったところ、酸化導電膜26の成膜温度が25℃から100℃の範囲では、第1強誘電体膜27のPZTの(100)面の配向強度は小さかった。図示を省略するがPZTの(101)面の配向強度も小さかった。これに対して、(111)面の配向強度は25℃から100℃の範囲で大きかった。したがって、酸化導電膜26の成膜温度を25℃から100℃の範囲内にすれば、(111)面に配向したPZTからなる第1強誘電体膜27を形成できる。なお、実験によればその製膜温度は、10℃以上〜25℃の範囲でも好ましいことがわかっている。

【0069】

次に、下部電極膜25及び酸化導電膜26の熱処理条件がPZTの結晶性に与える影響についてX線回折を用いて調査した結果を図6A〜図6Eに示す。図6Aの横軸は、下部電極膜25の熱処理条件(横軸下段の“Ir−AN”)と、酸化導電膜26の熱処理条件(横軸上段の“IrOx−AN”)とを示す。例えば、最も左欄の熱処理条件は、下部電極膜25を650℃で熱処理し、酸化導電膜26は熱処理しないことを示している。また、縦軸は、酸化導電膜26上の第1強誘電体膜27をX線回折したときの(100)面の配向強度を示している。データは、横軸に示す各熱処理条件に対して、前記した5箇所のそれぞれを測定している。図6Bは、縦軸が酸化導電膜26上の第1強誘電体膜27をX線回折したときの(101)面の配向強度を示している。図6Cは、縦軸が(111)面の配向強度を示している。図6D、縦軸が(222)面の配向率を示している。図6Eは、縦軸が第1強誘電体膜27を構成するPZTの(111)面のピークのロッキング半値幅を示している。なお、図6A〜図6Fにおいて、W/Oは、熱制御しないことを示している。

【0070】

なお、比較のため、熱処理の雰囲気は、100流量%のAr、1流量%のO2、20流量%のO2、100流量%のO2について調べた。それぞれの調査は、シリコン基板1のノッチを下として、シリコン基板1の上側であるTopと、左側であるLeftと、中心であるCenterと、右側より中心に10mmの位置のRight1と、右側のRight2との最大5箇所で実施し、そのそれぞれについて結晶性を調べた。

【0071】

図6A、図6B及び図6Dの横軸に示すIr−ANの熱処理を行い、且つIrOx−ANの熱処理を行わない場合、つまり下部電極膜25は熱処理したが酸化導電膜26は熱処理していない場合、PZTは(100)面、及び(101)面の配向強度が高く、(222)面の配向率は低かった。また、図6Cに示すように、この熱処理条件での(111)面の配向強度は他の熱処理条件と同等であった。同様に、図6Eに示すように、ロッキング半値幅は他の条件と同等であった。

【0072】

これに対して、図6A、図6B及び図6Dに示すように、横軸のIrOx−ANが100流量%のAr、つまり100流量%のArの雰囲気中でIrOxを熱処理した場合には、(100)面、(101)面の配向強度が高くなり、(222)面の配向率が低かった。これは、酸化導電膜26は結晶化されるが、酸化導電膜26の酸素欠損が多過ぎるため、MOCVD装置のチャンバ内の昇温過程中で再度異常酸化が生じたためであると考えられる。

【0073】

次に、酸化導電膜26を熱処理するときの雰囲気中の酸素の割合が結晶性に与える影響を検討する。図6A、図6B及び図6Dのそれぞれにおいて、酸素割合が多くなると(100)面及び(101)面の配向が弱くなり、(222)面の配向率が向上することが分かった。これは、酸素の割合が増え過ぎると、熱処理中に酸化導電膜26が異常酸化される可能性が高く、その傾向は酸素割合が増えるほど顕著になると考えられるからである。

【0074】

ここで、異常酸化の有無については、第1強誘電体膜27の表面の凹凸の数を計測することで確認できる。図6Fは、各条件で熱処理した酸化導電膜26の上に成膜した第1強誘電体膜27の基板中心に2.7×2.7μm2の範囲内で発生した表面突起の数の計測結果を示している。下部電極膜25を熱処理した場合、酸素比率を20流量%にして酸化導電膜26を熱処理したシリコン基板1の表面突起数が一番少なかった。

【0075】

また、下部電極膜25の熱処理を行わず、酸化導電膜26を成膜した後に熱処理を行ったところ、図6A及び図6Bに示すように(100)面及び(101)面の配向強度が低くなり、図6Dに示すように(222)配向率が高くなった。また、図6Fに示すように、酸素比率を20流量%にして熱処理したシリコン基板1の結晶性が一番良好であった。さらに、図6Eに示すように、第1強誘電体膜27の表面の突起数も少なかった。

【0076】

次に、下部電極膜25を熱処理すると共に、IrOxの酸化導電膜26を酸素が20流量%のAr雰囲気中で熱処理したときの第1強誘電体膜27の表面状態をSEM画像に基づいて図7Aに図に示す。また、比較例として、リファレンス方法で製造したPZT膜の表面状態をSEM画像に基づいて図7Bに示す。なお、リファレンス方法とは、IrOxの酸化導電膜の熱処理を行わずに、酸化導電膜26の上に第1強誘電体膜を形成する製造方法である。リファレンス方法によるPZT膜の表面に凹凸が多数確認されるのに対して、この実施の形態に係る製造方法で形成した第1強誘電体膜27の表面の凹凸は大幅に減少した。

【0077】

再現性を確認するために、リファレンス方法と、本実施形態に係る製造方法とを複数回ずつ実施して比較したところ、前記と同様の結果が得られた。本実施形態とリファレンス方法を採用した試料をそれぞれ3枚ずつ形成して2.7×2.7μm2の範囲の表面突起を比較したところ、図8に示す結果が得られた。本実施形態の方法によれば、リファレンス方法に比べて、PZT膜の表面の突起数が減少し、第1強誘電体膜27の表面のモフォロジの改善が確認された。

また、それらの試料についてPZT膜の結晶方位を調べたところ、図9A、図9B、図9Cに示すように、(100)面、(101)面の配向強度が低くなる一方、(222)配向強度が高くなった。

【0078】

次に、図1Iに示す断面構造を得るまでの工程について説明する。

第1強誘電体膜27の全面に、アモルファス状の第2強誘電体膜28を例えばスパッタ法により形成する。第2強誘電体膜28は、例えば膜厚が1nm〜30nm、より好ましくは20nmとする。

【0079】

さらに、第2強誘電体膜28上に第3の導電膜として第1上部電極膜29を形成する。第1上部電極膜29の形成に当たっては、先ず、第2強誘電体膜28上に、結晶性のIrOx膜をスパッタ法により厚さ25nmに形成する。例えば、このときの成膜温度を300℃とし、成膜ガスとしてAr及びO2を用い、流量はいずれも100sccmとする。また、スパッタパワーは、例えば1kW〜2kW程度とする。次いで、RTA法で725℃、20sccmの酸素と2000sccmのArを供給した雰囲気中で60秒間熱処理を行う。この熱処理によって第2強誘電体膜28が完全に結晶化すると共に、第1上部電極膜29のプラズマダメージが回復し、第1強誘電体膜27中の酸素欠損が補償される。

【0080】

さらに、膜厚が50nm〜150nmの第2上部電極膜30として、IrOY膜を形成する。IrOY膜は、例えば、Ar雰囲気中で、0.8Paの圧力下、1.0kWのスパッタパワーで45秒間堆積させ、その厚さを125nmにする。IrOY膜の異常成長を抑制するために、成膜温度は100℃以下にすることが望ましい。また、工程劣化を抑えるために酸化イリジウム膜をIrO2の化学量論組成に近い組成にすると、水素に対して触媒作用を生じることがなく、第2強誘電体膜28が水素ラジカルにより還元される問題が抑制され、キャパシタの水素耐性が向上する。

なお、第2上部電極30の材料として、IrO2の代わりにIr、Ru、Rh、Re、Os、Pd、これらの酸化物、SrRuO3などの導電性酸化物や、これらの積層構造を用いても良い。

【0081】

次に、図1Jに示す断面構造を得るまでの工程について説明する。

まず、第2上部電極膜30上に水素バリア膜31として、Ir膜をスパッタにより、Ar雰囲気中、1Paの圧力下、1.0kWのスパッタパワーで50nm〜100nmの厚さに堆積する。なお、水素バリア膜31は、導電性向上膜としても機能する。その材料は、Irに限定されず、Ru、Rh膜及びPd膜からなる群から選択された膜を使うことも可能である。

【0082】

そして、シリコン基板1の背面を洗浄した後、第1、第2上部電極膜29,30や、第1、第2強誘電体膜27,28、第1、第2下部電極膜29,30などをパターニングする際にハードマスクとして用いる第1のマスク材料層32と第2のマスク材料層33とを順次形成する。

第1のマスク材料層32は、水素バリア膜31の上に形成され、スパッタ法により成膜されたTiNからなる。第1のマスク材料層32は、TiAlNや、TaAlN、TaN膜及びこれらの積層膜でも良い。

第2のマスク材料層33は、第1のマスク材料層32の上に形成され、例えばTEOSガスを使用するCVD法で成膜された酸化シリコン膜からなる。

【0083】

この後、第2のマスク材料層33の上に図示を省略するフォトレジストを塗布し、次いでフォトレジストを露光、現像してキャパシタ平面形状となるレジストパターンを形成する。

【0084】

エッチングの際には、最初にレジストパターンをマスクに使用して第2のマスク材料層33を島状にパターニングし、第2のマスク材料層33をマスクにして第1のマスク材料層32をエッチングする。これにより、第2のマスク材料層33と、第1のマスク材料層32とからなるハードマスク34がキャパシタ形成領域に島状に形成される。

【0085】

次に、図1Kに示す断面構造を得るまでの工程について説明する。

HBr、O2、Ar、及びC4F8の混合ガスをエッチングガスとしてプラズマエッチングを行い、ハードマスク34で覆われていない部分の第1、第2上部電極膜29,30、第1、第2強誘電体膜27,28、第2の導電膜26A及び下部電極膜25をドライエッチングする。これによって、上部電極膜29,30がパターニングされてキャパシタ用の上部電極35が形成され、同様に第2の導電膜26A及び下部電極膜25がパターニングされてキャパシタ用の下部電極36が形成される。そして、上部電極80、強誘電体膜27,28、及び下部電極73を有する強誘電体キャパシタ37が形成される。パターニングが終了したら第2のマスク材料層33をドライエッチング又はウェットエッチにより除去する。

【0086】

次に、図1Lに示すように、強誘電体キャパシタ37で覆われていない部分の酸素拡散バリア膜24、下地導電膜23、及び第1のマスク材料層32をドライエッチングにより除去し、酸素拡散バリア膜24及び下地導電膜23を強誘電体キャパシタ37の下のみに島状に残す。

【0087】

次に、図1Mに示す断面構造を得るまでの工程について説明する。

強誘電体キャパシタ37及び第2層間絶縁膜19を覆う第1保護膜41としてAl2O3をスパッタ法により20nmの膜厚に形成する。又は、第1保護膜41としてMOCVD法又はALD法で2nm〜5nmのAl2O3膜を形成する。

【0088】

ここで、強誘電体膜27,28のダメージを回復させる目的で、酸素含有雰囲気中で回復アニールを施す。回復アニールの条件は特に限定されないが、例えば炉内において基板温度550℃〜700℃で実施する。また、強誘電体膜27,28がPZTの場合、600℃酸素の雰囲気中で60分アニールを行うことが好ましい。

【0089】

次に、第1保護膜41を覆うように、第2保護膜42としてAl2O3をCVD法により約38nmの膜厚に形成する。

第2保護膜42を構成するAl2O3膜は、水素や水分等の還元性物質が透過することを阻止する機能に優れている。このため、強誘電体膜27,28の強誘電体特性が還元性物質により劣化されることが防止される。

【0090】

さらに、第2保護膜42の全面に、第3層間絶縁膜43としてシリコン酸化物を例えばプラズマCVD法により膜厚1500nmで形成する。第3層間絶縁膜43としてシリコン酸化膜を形成する場合には、原料ガスとして、例えば、TEOSガスと酸素ガスとヘリウムガスとの混合ガスを用いる。なお、第3層間絶縁膜43として、例えば、無機ガスを用いて絶縁膜等を形成しても良い。第3層間絶縁膜43を形成したら、その表面を例えばCMP法で平坦化する。

続いて、N2Oガス又はN2ガス等を用いて発生させたプラズマ雰囲気で、熱処理を行って第3層間絶縁膜43中の水分を除去する。この際、第3層間絶縁膜43の膜質が改善されて膜中に水分が入り難くなる。

【0091】

次に、図1Nに示す断面構造を得るまでの工程について説明する。

まず、第3層間絶縁膜43の全面に、バリア膜として第3保護膜44を例えばスパッタ法又はCVD法により形成する。第3保護膜44としては、例えば、膜厚が20nm〜100nmのAl2O3膜が用いられる。平坦化された第3層間絶縁膜43上に第3保護膜44が形成されるため、第3保護膜44の表面は平坦になる。

【0092】

さらに、第3保護膜44の全面に第4層間絶縁膜45を例えばTEOSガスを用いるプラズマCVD法により形成する。第4層間絶縁膜45としては、例えば膜厚が300nm〜500nmのシリコン酸化膜が用いられる。なお、第4層間絶縁膜45として、SiON膜又はシリコン窒化膜等を形成しても良い。第4層間絶縁膜45を形成したら、その表面を例えばCMP法で平坦化する。

【0093】

続いて、レジストマスクを用いて第4層間絶縁膜45中にビアホール46A,46Bを形成する。ビアホール46A,46Bを形成する際には、キャパタ81の上部電極80を覆う水素バリア膜31を露出させた後、550℃で酸素雰囲気中において熱処理を行う。これによって、ビアホール46A,46Bの形成時に第1強誘電体膜27中に生じた酸素欠損が回復される。この後、それぞれのビアホール46A,46Bを介して強誘電体キャパシタ37の上部電極35に電気的に接続される導電性プラグ47A,47Bが形成される。

【0094】

次に、図1Oに示す断面構造を得るまでの工程について説明する。

pウェル3の中央の導電性プラグ16Bの上にビアホール48を形成する。ビアホール48に導電性プラグ49を形成する際には、ビアホール48の表面にTiN膜を単層で密着層として形成するのが好ましい。なお、密着層は、Ti膜をスパッタにより形成し、その上にTiN膜をMOCVD法により形成することで形成することも可能である。この場合、TiN膜から炭素除去を行うため、窒素と水素の混合ガスプラズマ中での処理が必要になるが、この実施の形態では、上部電極35上にIrからなる水素バリア膜31を形成しているので、上部電極35が還元されることはない。

【0095】

次に、図1Pに示す断面構造を得るまでの工程について説明する。

第4層間絶縁膜45上に導電性プラグ47A,47B,49に対応して配線パターンを形成する。即ち、例えばスパッタ法により、膜厚が60nmのTi膜と、膜厚が30nmのTiN膜と、膜厚が360nmのAlCu合金膜と、膜厚が5nmのTi膜と、膜厚が70nmのTiN膜とを順次形成する。これにより、Ti膜、TiN膜、AlCu合金膜、Ti膜及びTiN膜からなる積層膜を形成する。

【0096】

次に、フォトリソグラフィ技術を用い、積層膜をパターニングする。この結果、積層膜からなる配線(第1金属配線層)51A,51B,51Cが形成される。これにより、導電性プラグ47A,47Bを介して強誘電体キャパシタ37の上部電極膜35と配線51A,51Bとが電気的に接続される。同様に、導電性プラグ16B,49を介してソース/ドレイン領域11Aと配線51Cとが電気的に接続される。

その後、図示を省略するが層間絶縁膜を形成した後、導電性プラグの形成及び下から第2〜5層目以降の配線の形成等を行う。そして、例えばTEOS酸化膜及びSiN膜からなるカバー膜を形成すると、強誘電体キャパシタを有する強誘電体メモリが完成する。

【0097】

以上、説明したように、この実施の形態ではアモルファス又は微結晶の金属酸化膜である酸化導電膜26を形成し、酸化導電膜26をアニールした後、酸化導電膜26を還元して第2の導電膜26Aにしてから第1強誘電体膜27をMOCVD法により形成した。酸化導電膜26をアニールによって均一な結晶にした後に還元して金属膜を形成することで、結晶粒の小さい第2の導電膜26Aが得られる。これによって、第1強誘電体膜27が結晶粒の小さい第2の導電膜26A上に形成されるので、第1強誘電体膜27を構成するPZTのモフォロジが良好になる。このようにして強誘電体キャパシタ37を製造すると、キャパシタ構造の下部電極36及び強誘電体膜27,28の結晶性を向上できる。これによって、強誘電体膜27,28の面内分布が良くなってモフォロジが向上し、工程劣化を防止できる。その結果、高い反転電荷量を得られ、信頼性の高いキャパシタ構造を実現できる。また、リーク電流が低減され、信頼性の高い半導体装置が得られる。

【0098】

特に、酸化導電膜26を成膜温度が10℃〜100℃で、より好ましくは25℃〜50℃とすることで、IrOxのアモルファス又は微結晶を確実に形成できる。さらに、酸化導電膜26の成膜後の熱処理を1Paから大気圧までの範囲の値で、且つ酸素20流量%のAr雰囲気にすれば、結晶サイズの小さい均一な金属膜を形成することが可能になり、その上に成膜するPZTを所定の配向で、且つ良好なモフォロジにできる。

【0099】

なお、従来でMOCVD法により強誘電体膜を成膜するときは600℃以上の高温で成膜していたが、以下の課題が生じていた。即ち、PZT膜の結晶性は非常に不安定になり、非常に不均一なモフォロジ(表面凹凸)が発生し、基板周辺の膜が白濁することがあった。これは、昇温時に下部電極膜が異常酸化するためであると考えられる。異常酸化により形成されるIrOxは、強誘電体膜の形成時にMOCVDの溶媒であるTHF(TetraHydroFuran :C4H8O)液、又は酢酸ブチルによって還元されるが、このときに異相が出易くなる。この結果、その上に堆積される強誘電体膜の結晶性が悪くなる。この実施の形態に係る半導体装置の製造方法によれば、このような課題が解決され、信頼性の高い半導体装置が得られる。

【0100】

(第2実施の形態)

本発明の第2実施の形態について図10を参照して詳細に説明する。なお、第1実施の形態と同じ構成要素には同じ符号を付し、重複する説明は省略する。

本実施の形態に係る半導体装置は、スタック構造を有する半導体記憶装置(強誘電体メモリ)である。ビアホールを利用して導電性プラグ21A,21Bを形成した際、導電性プラグ21A,21Bの表面と周囲の第2層間絶縁膜19の両方を完全に平坦にするは困難である。一般的には、導電性プラグ21A,21Bの上面の高さが第2層間絶縁膜19の上面の高さより低くなり、第2層間絶縁膜19のうち導電性プラグ21A,21Bの上にリセスが形成される。このリセスの深さは20nm〜50nmであり、典型的には約50nm程度である。このリセスは、下部電極及び強誘電体膜の配向に影響を与える。

【0101】

そこで、この実施の形態では、シリコン基板1上の第2層間絶縁膜19の表面をアンモニア(NH3)プラズマで処理し、第2層間絶縁膜19の表面の酸素原子にNH基を結合させる。これにより、第2層間絶縁膜19上にTi原子がさらに堆積されても、堆積したTi原子は酸素原子に捕獲されてしまうことがなく、第2層間絶縁膜19の表面を自在に移動できるようになる。この結果、第2層間絶縁膜19上に(002)配向に自己組織化されたTi膜が形成される。

【0102】

そのアンモニアプラズマ処理は、例えばシリコン基板1に対して約9mm(350mils)離間した位置に対向電極を有する平行平板型のプラズマ処理装置を使いて実施する。処理条件は、例えば、266Pa(2Torr)の圧力下、400℃の基板温度に保持された処理容器中にアンモニアガスを350sccmの流量で供給し、シリコン基板1側に13.56MHzの高周波を100Wのパワーで、また対向電極に350kHzの高周波を55Wのパワーで、60秒間供給することにより実行する。

【0103】

次に、シリコン基板1とターゲットの間の距離を60mmに設定したスパッタ装置中で、0.15PaのAr雰囲気、20℃の基板温度で2.6kWのスパッタDCパワーを35秒間供給する。これによって、強い(002)配向のTi膜が約100nmの厚さに形成される。

この後、RTAで窒素の雰囲気中、650℃の基板温度で60秒の熱処理を行うと、(111)配向のTiNからなる導電性の下地膜23Aが得られる。下地膜23Aの厚さは100nm〜300nmであることが好ましく、この実施の形態では約100nmとした。なお、下地膜23Aは窒化チタン膜に限定されず、タングステン膜、シリコン膜、及び銅膜のいずれかを形成しても良い。

【0104】

導電性プラグ16A,16Bのリセスの影響によって、下地膜23Aの上面には凹部が形成されるので、CMP法で下地膜23Aの上面を研磨して平坦化することで凹部を除去する。CMPで使用されるスラリは特に限定されないが、例えば、キャボット・マイクロエレクトロニクス社製のSSW2000を使用できる。ところで、CMP後の下地膜23Aの厚さは、研磨誤差に起因して、シリコン基板1の面内や、複数のシリコン基板1間でばらつきが生じる。そのようなばらつきを考慮して研磨時間を制御すれば、CMP後の下地膜23Aの厚さの目標値を50nm〜100nm、より好ましくは50nmにできる。

【0105】

ところで、下地膜23Aに対してCMPを行った後では、下地膜23Aの上面付近の結晶が研磨によって歪んだ状態になっている。このように結晶に歪を有する下地膜23Aの上方に強誘電体キャパシタ37を形成すると、その歪みの影響が下部電極36に及んで下部電極膜25の結晶性が劣化し、下地導電膜23の上の強誘電体膜27,28の特性が劣化することがある。このような不都合を回避するために、下地膜23Aの上面を前記したNH3プラズマに曝すことで、下地膜23Aの結晶の歪みを解消させ、これ以降に堆積させる膜に影響を与えないようにする。

【0106】

そして、下地膜23Aの上に、結晶性を向上させた導電性膜Tiを形成し、窒素の雰囲気中で熱処理して窒化させ、下地導電膜23を形成する。

その後のプロセスは、第1実施の形態と同様である。即ち、酸素拡散バリア膜24、下部電極膜25及び酸化導電膜26を形成し、酸素とArガスの混合ガス雰囲気中で急速熱処理(RTA)する。その後、第1強誘電体膜27をMOCVD法で形成するときに酸化導電膜26を還元して第2の導電膜26Aを形成する。さらに、第2強誘電体膜28と上部電極膜29,30、水素バリア膜31を順番に形成してからハードマスクを使ってパターニングし、強誘電体キャパシタ37を形成する。さらに、その上に配線を形成する。

【0107】

この実施の形態に係る製造方法では、アモルファス又は微結晶の酸化導電膜26をRTA処理により結晶化してから第1強誘電体膜27を形成するようにしたにしたので、第1実施の形態と同様の効果が得られる。特に、導電性プラグ16A,16Bの形成時に生じるリセスが強誘電体キャパシタ37に与える影響を低減できるので、信頼性の高い半導体装置が得られる。

【0108】

なお、図11に示すように、下地膜23Aを形成したら、CMP法で研磨して第2層間絶縁膜19の上面から除去し、導電性プラグ21A,21Bの上のみ残しても良い。

【0109】

また、図12に示すように、この実施の形態に係る強誘電体メモリ(半導体装置)及びその製造方法では、導電性プラグの形成工程を1回だけ実施しても良い。即ち、第1層間絶縁膜14に導電性プラグ16A,16Bを形成したら、導電性プラグ16A,16Bに直接に電気的に接続されるように強誘電体キャパシタ37を形成する。さらに、第3層間絶縁膜43を形成した後、強誘電体キャパシタ37に連通する開口52を形成し、配線51A,51Bを形成する。さらに、強誘電体キャパシタ37に接続されない導電性プラグ16Aの上にコンタクトホールを形成し、その中に導電性プラグ49を形成する。

【0110】

(第3実施の形態)

本発明の第3実施の形態について図面を参照して詳細に説明する。なお、第1及び第2実施の形態と同じ構成要素には同じ符号を付し、重複する説明は省略する。

この実施の形態は、プレーナ構造のキャパシタを有する半導体装置及びその製造方法に関する。

【0111】

まず、図13Aに示す断面構造を得るまでの工程について説明する。

シリコン基板1の表面に素子分離絶縁膜2によってメモリ領域内の活性領域同士、即ちpウェル3同士を区画し、トランジスタT1,T2を形成する。さらに、各ソース/ドレイン領域11A,11Bの位置に対応して第1層間絶縁膜14に図示を省略する導電性プラグ16Aと、導電性プラグ16B,16Cを形成する。ここまでの工程の詳細は、第1実施の形態と同様である。

【0112】

次に、第1層間絶縁膜14上及び導電性プラグ16A〜16C上に、第1酸化防止膜18及び第2層間絶縁膜19を形成する。第2層間絶縁膜19は、例えば、SiON膜を約100nmの膜厚に形成し、さらにTEOSを使用するプラズマCVD方によりシリコン酸化膜を約130nmの膜厚で堆積させた構成を有する。

【0113】

第2層間絶縁膜81の上には、下部電極密着膜82としてAl2O3膜をスパッタ法で20nm程度の厚さに形成する。その後、RTAにより650℃の酸素雰囲気中で下部電極密着膜82を酸化させる。

【0114】

下部電極密着膜82の上に、第1の金属膜である下部電極膜83(下部導電膜)を形成する。下部電極膜83には、例えば、スパッタ法で形成したIr膜が用いられ、その厚さは約150nmとする。なお、下部電極膜83は、Ir膜の代わりにPt膜、Ru膜、RuO2膜、SrRuO3膜のいずれかの単層膜、或いはこれらの積層膜でも良い。この後、下部電極膜83をRTA処理する。熱処理条件は、第1実施の形態と同様であり、例えばAr雰囲気中650℃〜750℃、60秒間とする。これにより、各層の密着性が向上する。

【0115】

さらに、下部電極膜83の上に酸化導電膜26として、貴金属酸化膜、例えば、IrOxからアモルファス又は均一な微結晶の膜を5nm〜50nm、好ましくは10nm〜40nmの厚さに形成する。成膜条件は、例えば、Arと酸素の混合雰囲気中、0.11Paの圧力、20℃〜300℃の基板温度で、1kWのスパッタパワーに設定する。そして、酸化導電膜26の形成後に、RTAによって結晶化する。RTAの条件は、第1実施の形態と同様である。RTAによって、酸化導電膜26が均一で、且つ微細な結晶になる。

【0116】

次に、図13Bに示す断面構造を得るまでの工程について説明する。

酸化導電膜26上に第1強誘電体膜27としてPZT膜をMOCVD法により形成する。この実施の形態では、最初にMOCVD法によって初期層27A及びコア層27Bを形成した後、スパッタ法によって表層部27Cを形成する。成膜条件は、第1実施の形態と同様である。初期層27Aの形成時に原料ガスに含まれる溶媒成分によって酸化導電膜26が還元されて第2の導電膜26Aに改質される。第2の導電膜26Aは、その下層の下部電極膜83のIr膜の配向性に合わせてIr(111)面に優先的に配向する。これにより、1強誘電体膜27のPZTは、下地となる第2の導電膜26Aの結晶配向に合わせて(111)面が優先的に配向される。

【0117】

次に、図13Cに示す断面構造を得るまでの工程について説明する。

まず、第1実施形態と同様に、第1強誘電体膜27の全面に、アモルファス状の第2強誘電体膜28を形成する。さらに第2強誘電体膜28上に、第1上部電極膜29、第2上部電極膜30、水素バリア膜31、ハードマスクとして用いる第1のマスク材料層32及び第2のマスク材料層33を順次形成する。

【0118】

第1上部電極膜29として酸化イリジウム膜を順に形成する。さらに、第2上部電極膜30として例えばIr等の貴金属膜を形成する。第1のマスク材料層32として、スパッタ法によりTiN膜を形成する。また、第2のマスク材料層33としてCVD法によりSiO2膜を形成する。

その後に、第2のマスク材料層33上に、上部電極形状のレジストパターン(不図示)を形成する。さらに、レジストパターンをマスクにして、第1、第2のマスク材料層32、33をエッチングする。

【0119】

そして、レジストパターンの下に残された第1のマスク材料層32及び第2のマスク材料層33をハードマスクにしてHBr、O2、Ar、及びC4F8の混合ガスをエッチングガスとしてプラズマエッチングする。

これにより、図13Dに示すように、上部電極膜29,30がパターニングされてキャパシタ用の上部電極85が形成される。エッチング後、第1、第2のマスク材料層32、33を除去する。

【0120】

さらに、レジスト除去したシリコン基板1を酸素含有雰囲気中で熱処理する。熱処理の温度は600〜700℃とする。本実施の形態では、その一例として650℃で40分間熱処理を行った。この熱処理は、プロセス中に強誘電体膜27,28が受けたダメージを回復させるもので、このようなアニールは回復アニールとも呼ばれる。

【0121】

次に、図13Eに示す断面構造を得るまでの工程について説明する。

パターニングされたフォトレジストパターンをマスク(不図示)に使用して強誘電体膜27,28をエッチングによりストライプ状にパターニングする。強誘電体膜27,28は、複数の上部電極85の下を通る長方形の平面形状を有している。次いで、酸素雰囲気で例えば300℃〜400℃、30分間〜120分間、熱処理を行う。

【0122】

この後、水素バリア膜31、上部電極85、強誘電体膜27,28、及びに第2の導電膜26A上に第1保護膜41としてAl2O3膜を例えばスパッタ法又はCVD法、或いはALD法により形成する。

【0123】

さらに、図13Fに示す断面構造を得るまでの工程について説明する。

第1保護膜30の全面にフォトレジスト膜を例えばスピンコート法によって形成する。フォトリソグラフィ法でフォトレジスト膜を所定の平面形状、即ち強誘電体キャパシタの下部電極の平面形状にパターニングする。

続いて、フォトレジスト膜をマスクにして第1保護膜41及び第2の導電膜26A、下部電極膜83及び下部電極密着膜82をエッチングして下部電極86を形成する。下部電極86の平面形状は、略長方形であり、その端部は強誘電体膜27,28からはみ出す大きさである。このようにしてパターニングされた上部電極85、強誘電体膜27,28及び下部電極86によって、強誘電体キャパシタ87が形成される。

【0124】

さらに、強誘電体キャパシタ87及び第2層間絶縁膜19の上面に第2保護膜42を例えばスパッタ法又はCVD法、或いはALD法によりAl2O3膜を形成する。第2保護膜42を形成した後、例えば500℃〜700℃の酸素雰囲気にて、30分間〜120分間の熱処理を行う。この結果、強誘電体膜27,28に酸素が供給され、強誘電体キャパシタ87の電気的特性が回復する。

【0125】

次に、図13Gに示す断面構造を得るまでの工程について説明する。

第2保護膜42の全面に第3層間絶縁膜43として、例えばTEOSを用いるプラズマCVD法により膜厚が1400nmのシリコン酸化物を形成する。この後、例えばCMP法により、第3層間絶縁膜43の表面を平坦化する。

【0126】

次いで、N2Oガス又はN2ガスを用いて発生させたプラズマ雰囲気にて、例えば350℃、2分間の熱処理を行う。熱処理の結果、第3層間絶縁膜43中の水分が除去されると共に、第3層間絶縁膜43の膜質が変化して膜中に水分が入り難くなる。この熱処理によって、第3層間絶縁膜43の表面が窒化されてSiON膜が形成される。

【0127】

さらに、第3層間絶縁膜43の全面に、第3保護膜44を形成する。第3保護膜44は、例えばスパッタ法又はCVD法で成膜した膜厚20nm〜50nmのAl2O3膜からなる。さらに、第3保護膜44上の全面に、第4層間絶縁膜45として例えば膜厚が300nmのシリコン酸化物をTEOSを用いるプラズマCVD法で形成する。

【0128】

第4層間絶縁膜45の上面に図示を省略するフォトレジスト膜を形成し、フォトレジスト膜をマスクにしてエッチングし、第3保護膜44、第3層間絶縁膜43、第2保護膜42を経て強誘電体キャパシタ87の上部電極85まで達するビアホール91を形成する。同様に、第4層間絶縁膜45上に形成したフォトレジスト膜を用いてエッチングし、強誘電体キャパシタ87の下部電極86まで達するビアホール92を形成する。

【0129】

次いで、例えば400℃〜600℃の酸素雰囲気で、30分間〜120分間の熱処理を行う。この結果、強誘電体膜27,28に酸素が供給され、強誘電体キャパシタ87の電気的特性が回復する。なお、この熱処理を、酸素雰囲気中ではなく、オゾン雰囲気中で行っても良い。オゾン雰囲気中で熱処理を行った場合にも、強誘電体膜27,28に酸素が供給されて強誘電体キャパシタ87の電気的特性が回復する。

【0130】

次いで、第3及び第4層間絶縁膜43,45、第2及び第3保護膜42,44、第2層間絶縁膜19を貫通し、導電性プラグ16A〜16Cまで達するビアホール93A,93Bをフォトリソグラフィ及びエッチングを用いて形成する。

【0131】

次に、図13Hに示す断面構造を得るまでの工程について説明する。

ビアホール91内に例えば膜厚が20nmのTi膜と、膜厚が50nmのTiN膜と順番に例えばスパッタ法により形成する。これらのTi膜及びTiN膜によって、第2コンタクトホール91に密着膜94Aが形成される。さらに、密着膜94A上にW膜94BをCVD法により成長させ、W膜94Bでビアホール91を埋める導電性プラグ95を形成する。同様にして、ビアホール92に導電性プラグ96、ビアホール93A,93Bに導電性プラグ97A,97Bを形成する。

【0132】

そして、導電性プラグ95〜97の上に、第1層目の金属配線層を形成する。これにより、導電体プラグ95を介して上部電極85に電気的に接続される配線51Bと、導電体プラグ96を介して下部電極86に電気的に接続される配線51Bと、導電体プラグ97A,97Bを介してソース/ドレイン領域11A,11Bに電気的に接続される配線51Aとが形成される。

【0133】

以上、説明したように、この実施の形態に係る半導体装置の製造方法は、下部電極膜25を形成した後、アモルファス又は微結晶からなる金属酸化膜である酸化導電膜26を形成し、RTAにより結晶化するようにした。そして、第1の強誘電体膜27の初期層を形成する際に酸素含有率を不足させて酸化導電膜26を還元するようにした。

これにより、酸化導電膜26を還元したときに微小な結晶の第2導電膜26Aが得られるようになる。従って、第1強誘電体膜27のコア層27BをMOCVD法により形成するときにPZT膜のモフォロジを改善できる。このため、プレーナ構造のキャパシタを有する半導体装置の製造方法において、第1実施の形態と同様の効果が得られる。

【0134】

なお、強誘電体膜としては、例えば、熱処理により結晶構造がBi層状構造又はペロブスカイト構造となる膜を形成することができる。このような膜としては、PZT膜の他、La、Ca、Sr及び/又はSi等を微量ドープしたPZT、SBT(タンタル酸ビスマスストロンチウム)、BLT((Bi,La)4Ti3O12)並びにBi系層状化合物などの一般式ABO3で表される材料からなる膜が挙げられる。

【0135】

以下に、本発明の実施形態について付記する。

(付記1)基板の上方に第1の金属からなる第1の膜を形成する工程と、前記第1の膜上に、金属酸化物からなるアモルファス、微結晶のいずれかの第2の膜を形成する工程と、前記第2の膜を熱処理する工程と、前記第2の膜を熱処理した後に、第2の膜を還元する工程と、前記第2の膜上に強誘電体からなる第3の膜を形成する工程と、前記第3の膜上に第2の金属からなる第4の膜を形成する工程と、有することを特徴とする半導体装置の製造方法。

(付記2)付記1に記載の半導体装置の製造方法において、前記第2の膜の加熱処理は大気圧下で行うことを特徴とする半導体装置の製造方法。

(付記3)付記1又は付記2に記載の半導体装置の製造方法において、前記第2の膜の前記熱処理は、急速熱アニールであることを特徴とする半導体装置の製造方法。

(付記4)付記1乃至付記3のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜の前記熱処理は、酸素を含む雰囲気で行われることを特徴とする半導体装置の製造方法。

(付記5)付記1乃至付記4のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜の厚さは、10nm乃至40nmであることを特徴とする半導体装置の製造方法。

(付記6)付記1乃至付記5のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜は、10℃乃至100℃の温度下で形成されることを特徴とする半導体装置の製造方法。

(付記7)付記1乃至付記6のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜は、前記第3の原料ガスに含まれる溶媒成分により還元されることを特徴とする半導体装置の製造方法。

(付記8)付記1乃至付記7のいずれか1つに記載の半導体装置の製造方法において、前記金属酸化物は、前記第1の金属の酸化物であることを特徴とする半導体装置の製造方法。

(付記9)付記1乃至付記8のいずれか1つに記載の半導体装置の製造方法において、前記第1の金属は、イリジウム、ルテニウム、ロジウム及びパラジウムのうちのいずれかであることを特徴とする半導体装置の製造方法。

(付記10) 付記1乃至付記9に記載の半導体装置の製造方法において、前記第2の膜を熱処理する雰囲気内の酸素の含有量は0.1流量%以上100流量%以下であることを特徴とする半導体装置の製造方法。

(付記11)付記1乃至付記10のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜の熱処理温度は600℃以上、750℃以下であることを特徴とする半導体装置の製造方法。

(付記12)付記1乃至付記11のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜の熱処理は前記大気圧以下で1Pa以上であることを特徴とする半導体装置の製造方法。

(付記13)付記1乃至付記12のいずれか1つに記載の半導体装置の製造方法において、前記第1の膜の形成後であって前記第2の膜を形成する前に、不活性ガス雰囲気で前記第1の膜を熱処理することを特徴とする半導体装置の製造方法。

(付記14)付記13に記載の半導体装置の製造方法において、前記第1の膜を600℃以上、且つ750℃以下の温度で熱処理することを特徴とする半導体装置の製造方法。

(付記15)付記1乃至付記14のいずれか1つに記載の半導体装置の製造方法において、前記第3の膜の初期層を気相成長する期間に前記第2の膜を還元することを特徴とする半導体装置の製造方法。

(付記16)付記15に記載の半導体装置の製造方法において、前記強誘電体膜の形成は、前記初期層上に成膜レート及び膜厚が前記初期層に比べて高いコア層をCVD法により形成する工程を含むことを特徴とする半導体装置の製造方法。

(付記17)付記15又は付記16に記載の半導体装置の製造方法において、前記初期層は、2.5nm〜10nmの膜厚に形成することを特徴とする半導体装置の製造方法。

(付記18)付記1乃至付記17のいずれか1つに記載の半導体装置の製造方法において、前記強誘電体膜は、前記第2の膜の結晶配向と同じ結晶配向の膜を形成する工程であることを特徴とする半導体装置の製造方法。

(付記19)付記1乃至付記18のいずれか1つに記載の半導体装置の製造方法において、前記強誘電体膜は、形成雰囲気中に導入する酸素ガスの比率を変化させながら形成されることを特徴とする半導体装置の製造方法。

(付記20)付記1乃至付記18のいずれか1つに記載の半導体装置の製造方法において、前記第3の膜は、ペロブスカイト構造又はビスマス層状構造を有する強誘電体材料からなる膜であることを特徴とする半導体装置の製造方法。

【図面の簡単な説明】

【0136】

【図1A】図1Aは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その1)である。

【図1B】図1Bは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その2)である。

【図1C】図1Cは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その3)である。

【図1D】図1Dは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その4)である。

【図1E】図1Eは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その5)である。

【図1F】図1Fは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その6)である。

【図1G】図1Gは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その7)である。

【図1H】図1Hは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その8)である。

【図1I】図1Iは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その9)である。

【図1J】図1Jは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その10)である。

【図1K】図1Kは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その11)である。

【図1L】図1Lは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その12)である。

【図1M】図1Mは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その13)である。

【図1N】図1Nは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その14)である。

【図1O】図1Mは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その15)である。

【図1P】図1Nは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その16)である。

【図2】図2は、ArとO2の流量制御を示すタイミングチャートである。

【図3】図3は、酸化導電膜を還元した後にX線回折を行った図である。

【図4A】図4Aは、酸化導電膜のX線回折結果を示す図である。

【図4B】図4Bは、熱処理前と熱処理後の酸化導電膜のX線回折結果を示す図である。

【図5A】図5Aは、酸化導電膜の成膜温度が第1強誘電体膜の(100)面の結晶性に与える影響を調べたグラフである。

【図5B】図5Bは、酸化導電膜の成膜温度が第1強誘電体膜の(111)面の結晶性に与える影響を調べたグラフである。

【図6A】図6Aは、下部電極膜及び酸化導電膜の熱処理条件がPZTの(100)面の結晶性に与える影響についてX線回折を用いて調査した結果を示すグラフである。

【図6B】図6Bは、下部電極膜及び酸化導電膜の熱処理条件がPZTの(101)面の結晶性に与える影響についてX線回折を用いて調査した結果を示すグラフである。

【図6C】図6Cは、下部電極膜及び酸化導電膜の熱処理条件がPZTの(111)面の結晶性に与える影響についてX線回折を用いて調査した結果を示すグラフである。

【図6D】図6Dは、下部電極膜及び酸化導電膜の熱処理条件がPZTの(222)面の配向率に与える影響についてX線回折を用いて調査した結果を示すグラフである。

【図6E】図6Eは、下部電極膜及び酸化導電膜の熱処理条件によるPZTの(111)面のX線回折ピークの半値幅の変化を調べたグラフである。

【図6F】図6Fは、下部電極膜及び酸化導電膜の熱処理条件によるPZTの表面の突起数の変化を調べたグラフである。

【図7A】図7Aは、本実施の形態で形成したPZTの表面のSEM像を示す図である。

【図7B】図7Bは、比較例としてレファレンス方法で形成したPZTの表面のSEM像を示す図である。

【図8】図8は、本実施の形態とレファレンス方法とをそれぞれ複数回実施して計測したPZTの表面の突起数を示すグラフである。

【図9A】図9Aは、本実施の形態とレファレンス方法とをそれぞれ複数回実施してPZT膜の結晶方位を比較したグラフである。

【図9B】図9Bは、本実施の形態とレファレンス方法とをそれぞれ複数回実施してPZT膜の結晶方位を比較したグラフである。

【図9C】図9Cは、本実施の形態とレファレンス方法とをそれぞれ複数回実施してPZT膜の(222)面の配向率を比較したグラフである。

【図10】図10は、第2実施の形態に係る半導体装置の製造工程を説明する断面図である。

【図11】図11は、第2実施の形態の変形例に係る半導体装置の製造工程を説明する断面図である。

【図12】図12は、第2実施の形態の変形例に係る半導体装置の製造工程を説明する断面図である。

【図13A】図13Aは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その1)である。

【図13B】図13Bは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その2)である。

【図13C】図13Cは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その3)である。

【図13D】図13Dは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その4)である。

【図13E】図13Eは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その5)である。

【図13F】図13Fは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その6)である。

【図13G】図13Gは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その7)である。

【図13H】図13Hは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その8)である。

【符号の説明】

【0137】

1 シリコン基板

25 下部電極膜(第1の膜)

26 酸化導電膜(第2の膜)

26A 第2の導電膜

27 第1強誘電体膜(第3の膜)

27A 初期層

27B コア層

29 上部電極膜(第4の膜)

37 強誘電体キャパシタ

【技術分野】

【0001】

本発明は、強誘電体キャパシタを有する半導体装置の製造方法に関し、特に半導体基板上に形成され、記憶を保持するための強誘電体容量素子とメモリセルトランジスタとを備える強誘電体メモリの製造方法に関する。

【背景技術】

【0002】

近年、デジタル技術の進展に伴い、大容量のデータを高速に処理又は保存する傾向が高まっている。このため、電子機器に使用される半導体装置の高集積化及び高性能化が要求されている。

【0003】

そこで、半導体記憶装置に関しては、例えばDRAM(Dynamic Random Access Memory)の高集積化を実現するため、DRAMを構成する容量素子の容量絶縁膜として、従来のシリコン酸化物又はシリコン窒化物に代えて、強誘電体材料又は高誘電率材料を用いる技術が広く研究開発され始めている。このような、半導体記憶装置としては、電源を遮断しても記憶情報が消失しない不揮発性メモリであるフラッシュメモリや強誘電体メモリ(FeRAM)が知られている。

【0004】

FeRAMは、絶縁ゲート型電界効果トランジスタ(IGFET)のゲート絶縁膜中に埋め込まれたフローティングゲートを有し、フローティングゲートに記憶情報を表わす電荷を蓄積することによって情報を記憶する。このため、フラッシュメモリは、情報の書き込み及び消去の際に、絶縁膜を通過するトンネル電流を流す必要があり、比較的高い電圧が必要である。また、書き込み動作及び読み出し動作が可能な不揮発性RAMをさらに低電圧且つ高速で動作させるため、容量絶縁膜として自発分極特性を有する強誘電体膜を用いる技術も盛んに研究開発されている。

【0005】

FeRAMは、強誘電体キャパシタを構成する強誘電体のヒステリシス特性を利用して情報を記憶する。強誘電体キャパシタは、上部電極及び下部電極の一対の電極で強誘電体膜を挟んだ構成を有する。このような強誘電体キャパシタは、電極間の印加電圧に応じて分極を生じ、印加電圧を取り去っても自発分極を有することが知られている。このため、印加電圧の極性を反転させたときの自発分極の極性の反転を検出することで情報の読み出しが可能になる。このような、FeRAMは、フラッシュメモリに比べて低電圧で動作するので省電力で高速の書き込みが可能である。近年では、従来のロジック技術に、このFeRAMを取り入れたロジック混載チップ(SOC:System On Chip)が、ICカードなどの用途として検討されている。

【0006】

ここで、FeRAMに対しても一層の高集積化及び高性能化が要求されており、今後はセル面積の低減が必要になると考えられている。セル面積の低減には、従来のプレーナ構造に替えて、スタック構造を採用することが有効であることが知られている。なお、スタック構造とは、メモリセルを構成するトランジスタのドレイン上に形成されたプラグ(コンタクトプラグ)の直上にキャパシタを形成した構造をいう。

【0007】

従来のスタック構造のFeRAMにおいて、強誘電体キャパシタは、W(タングステン)製の導電性プラグの直上に、バリアメタル、下部電極、強誘電体膜及び上部電極がこの順で積層されて構成されている。バリアメタルは、導電性プラグの酸化を防止する役割を有する。バリアメタル及び下部電極は、通常、TiN膜、TiAlN膜、Ir膜、IrO2膜、Pt膜及びSRO(SrRuO3)膜のうちから選択された2以上の膜の組み合わせにより形成される。

【0008】

また、FeRAMの強誘電体キャパシタを構成する強誘電体膜は、チタン酸ジルコン酸鉛(PZT)、SrBi2Ta2O9(SBT、Y1)若しくはSrBi2(Ta、Nb)2O9(SBTN、YZ)、Bi4Ti3O9、(Bi,La)4Ti3O12、BiFeO3等のBi層状構造化合物等により形成されている。このような強誘電体膜は、例えば、ゾルゲル法や、スパッタ法、有機金属気相成長(MOCVD:Metal Organic Chemical Vapor Deposition)法等によって成膜される。

【0009】

FeRAMのような強誘電体メモリの電気特性を向上させ、かつ製品歩留まりを高めるためには、強誘電体を構成する膜の結晶の配向が均一になるように制御する必要がある。強誘電体膜の配向は、下部電極を構成する結晶の配向に大きく影響される。このため、下部電極の結晶の配向を均一にすれば、強誘電体膜の結晶の配向を均一にできる。従って、電気特性が良く、製品歩留まりの高い強誘電体メモリを作製するためには、下部電極の結晶の配向を均一にする必要がある。

【0010】

スタック構造の従来の強誘電体キャパシタの下部部電極として、例えば、上から順番にPt、IrO2、Irを積層させた構造が知られている。このような技術に関しては、例えば、特許文献1に開示されている。

また、下部電極の結晶性を向上させるために、下から順にIr、IrO、Pt、PtO、Ptの積層構造を形成することも検討されている。これに関連する技術としては、例えば、特許文献2や特許文献3に開示されている。この場合、導電性プラグの酸化を防止するために、Ir膜は200nm以上にすると良い。しかしながら、Ir膜を厚く堆積させると、エッチングが困難になる。

【0011】

酸素に対する安定性を増加させるためには、下部電極として例えば、Ir、IrOx、Pt、Pd、PdOx、Au、等の貴金属又は導電性酸化物を使用し、かつ下部電極の膜厚を30nm〜100nm程度の厚さにすることが検討されている。これに関連する技術としては、例えば、特許文献4に開示されている。

他のキャパシタの積層構造としては、密着層上に形成された下部電極と、下部電極上に形成された誘電体膜と、誘電体膜上に形成された浮遊電極と、浮遊電極上に形成され、誘電体膜とは配向方向が異なる別の誘電体膜と、別の誘電体膜上に形成された上部電極とを有するものが知れている。この場合、密着層としては、TiOx、Pt、Ti、PtOx、IrOx、ZrOx、TiN、TiAlNなどがあげられる。これに関連する技術としては、例えば、特許文献5に開示されている。

【0012】

ここで、下部電極又は上部電極は、複数の膜を積層させて製造することがある。この場合の積層構造としては、例えば、選択的な層(例えば酸素バリア層)、酸素源層(導電性酸化膜)、貴金属又は導電性酸化膜があげられる。これに関連する技術としては、例えば、特許文献6に開示されている。

【0013】

また、密着性の高い電極としては、第1の導電膜(IrO)と、第1の導電膜上に形成された第2の導電膜(Ir)と、第2の導電膜上に形成された第3の導電膜(Pt)とを有する積層構造が知られている。これに関連する技術としては、例えば、特許文献7に開示されている。また、導電性プラグの上に接着膜(Ti)、拡散防止膜(Ir、Ruなど)、金属酸化物膜(IrO2、RuO2、LSCO、SRO)、耐熱性金属膜(Ir、Pt、Ru、Rh、Os、Pa)を順番に積層した構造も開発されている。これに関連する技術としては、例えば、特許文献8に開示されている。

【0014】

また、酸素の拡散を防止する酸素バリア膜を下部電極に積層させた構造も知れている。このような積層構造としては、例えばIrO2/Ir/TiAlN/TiNがある。これに関連する技術としては、例えば、特許文献9に開示されている。さらに、下部電極の積層構造としては、TiAlN、Ti、Ptを順に形成することが知られている。これに関連する技術としては、例えば、特許文献10に開示されている。なお、電極の構造をIrにすると、電極上にPZT(チタン酸ジルコン酸鉛)を形成したときの疲労特性がPt電極上に比べて改善される。これに関連する技術としては、例えば、特許文献11に開示されている。

【0015】

また、下部電極を積層構造する場合には、例えば、Ir/Pt/Ir、Ir/Pt、Pt/Irのように、少なくともIr層を含めることが望ましいとされている。これに関連する技術としては、例えば、特許文献12に開示されている。

また、下部電極を構成する導電性膜の酸化を防止するために、導電性膜に貴金属膜を積層させ、貴金属膜上に強給電体膜を形成することがある。この場合の貴金属膜は少なくとも2層以上の積層構造として形成される。これに関連する技術としては、例えば、特許文献13に開示されている。

【0016】

さらに、誘電体キャパシタの製造方法には、密着膜上にPt製の下部電極膜を形成し、下部電極膜上に誘電体膜を形成し、誘電体膜上に上部電極を形成することが知られている。これに関連する技術としては、例えば、特許文献14に開示されている。なお、下部電極膜と誘電体膜の間に金属物質からなる拡散バリア膜を形成すると、下部電極と誘電体膜との間の元素の拡散を防止できる。これに関連する技術としては、例えば、特許文献15に開示されている。

【0017】

また、半導体記憶装置の構成としては、半導体基板上に形成した層間絶縁膜に導電性プラグを設け、導電性プラグに接続される電極を間絶縁膜上に形成した容量素子が知れている。電極には、酸素バリア膜として酸化イリジウム膜が設けられ、酸化イリジウム膜は平均結晶粒径が互いに異なる複数の層から構成する。例えば、酸化イリジウム膜を構成する複数の層のうち、上層の平均結晶粒径を上層の膜厚の1/2以下にし、下層の平均結晶粒径より小さくする。これに関連する技術としては、例えば、特許文献16に開示されている。

【0018】

さらに、下部電極を酸化物層と、その上に積層されたIr又はRuからなる金属膜との積層構造にすることもある。Ir又はRuからなる金属膜の上にさらに酸化物層を積層させることもある。これに関連する技術としては、例えば、特許文献17に開示されている。また、従来の電極は、Pt、Ir、Ru、IrO2、RuO2又はそれらの積層構造、或いは混合物から製造されている。これに関連する技術としては、例えば、特許文献18に開示されている。

【0019】

ところで、下部導体膜と誘電体膜との間に下部絶縁膜を形成すると、誘電体膜のリーク電流をより低減できる。これに関連する技術としては、例えば、特許文献19に開示されている。また、Ir膜の上に下部電極としてIrOx膜をスパッタしてから酸素雰囲気でアニールし、その上にPZT膜を成膜することが知られている。この場合、Irは450℃以上で成膜し、IrOxは、Ir膜の成膜温度以下、例えば300℃以上で成膜する。これに関連する技術としては、例えば、特許文献20に開示されている。

【0020】

PZTを成膜する際には、予めIrO2等の下部電極を形成してから急速熱処理(RTA)すると良い。下部電極を不活性ガス雰囲気中でアニールすることにより、PZT(111)の配向強度及びスイッチングチャージ(Qsw)が向上する。これに関連する技術としては、例えば、特許文献21に開示されている。

なお、下部電極のIrO2を成膜するとき、イリジウムフラックスと酸素の分圧比がQswに影響を与えることが知れている。これに関連する技術としては、例えば、特許文献22に開示されている。

【特許文献1】特開平9−22829号公報

【特許文献2】特開2003−92391号公報

【特許文献3】特開2004−153006号公報

【特許文献4】特開2003−318371号公報

【特許文献5】特開2003−209179号公報

【特許文献6】特開2000−357777号公報

【特許文献7】特開2001−91539号公報

【特許文献8】特開2001−111007号公報

【特許文献9】特開2005−159165号公報

【特許文献10】特開2004−95638号公報

【特許文献11】特開2000−164818号公報

【特許文献12】特開2003−298136号公報

【特許文献13】特開平11−145418号公報

【特許文献14】特開2002−151662号公報

【特許文献15】特許平06−326270号公報

【特許文献16】特開2003−51583号公報

【特許文献17】特開2000−239140号公報

【特許文献18】特開2005−104676号公報

【特許文献19】特開2003−264187号公報

【特許文献20】特開2003−68991号公報

【特許文献21】特開2000−91551号公報

【特許文献22】特開2000−91270号公報

【発明の開示】

【発明が解決しようとする課題】

【0021】

電気特性が良く、製品歩留まりの高い強誘電体メモリを作製するためには、強誘電体の配向を均一にする必要がある。しかしながら、MOCVD法で強誘電体膜を形成すると、強誘電体膜の結晶の配向が下層の結晶配向の影響を受け易かった。

この発明は、強誘電体膜の結晶の配向を均一にできる半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0022】

本願の一観点によれば、基板の上方に第1の導電膜を形成する工程と、前記第1の導電膜上にアモルファス又は微結晶からなる導電酸化膜を形成する工程と、前記導電酸化膜を熱処理によって結晶化させる工程と、前記導電酸化膜を還元して第2の導電膜を形成する工程と、前記第2の導電膜上に強誘電体膜を形成する工程と、前記強誘電体膜上に第3の導電膜を形成する工程と、有することを特徴とする半導体装置の製造方法とした。

【発明の効果】

【0023】

本発明によれば、アモルファス又は微結晶として形成した酸化導電膜を熱処理して結晶化させ、この後に還元して第2の導電膜を形成するので、第2の導電膜の結晶性が良好になる。このような第2の金属膜上に第1強誘電体膜を形成すると、第1強誘電体膜の結晶性が向上して表面のモフォロジが良好になる。これにより、信頼性の高い半導体装置が得られる。

【発明を実施するための最良の形態】

【0024】

(第1実施の形態)

本発明の第1実施の形態について図面を参照して詳細に説明する。

図1A〜図1Lは、本発明の第1実施形態に係る半導体装置の製造途中の断面図である。なお、本実施の形態に係る半導体装置は、スタック構造の強誘電体キャパシタを有する半導体記憶装置(強誘電体メモリ)である。

【0025】

最初に、図1Aに示す断面構造を得るまでの工程について説明する。

まず、n型又はp型のシリコン基板1(半導体基板)の表面に、トランジスタの活性領域を画定する素子分離絶縁膜2を形成する。この実施の形態では素子分離絶縁層2として、シャロートレンチアイソレーション(STI)を形成する。STIは、シリコン基板1の素子分離領域に溝を形成し、その中に酸化シリコン等の絶縁膜を埋め込むことにより形成される。なお、素子分離絶縁層2は、STIに限られず、LOCOS(Local Oxidation of Silicon)法で形成した絶縁膜であっても良い。

【0026】

次いで、シリコン基板1のメモリセル領域におけるトランジスタ活性領域にp型不純物、例えばボロンを導入してpウェル3を形成する。そして、トランジスタ活性領域の表面を熱酸化させてゲート絶縁膜5を形成する。この場合のゲート絶縁膜5は、熱酸化によるシリコン酸化膜であり、その厚さは約6〜7nmである。

【0027】

さらに、シリコン基板1の全面に、非晶質又は多結晶のシリコン膜を形成し、フォトリソグラフィ技術を用いてパターニングしてゲート電極6A,6Bを形成する。シリコン膜を例えば厚さ約50nmとする。

【0028】

ゲート電極6A,6Bは、pウェル3上に間隔をおいて互いに平行に二つ形成され、その各々がワード線の一部を構成する。さらに、ゲート電極6A,6Bをマスクにしたイオン注入により、ゲート電極6A,6Bの両側のシリコン基板1の表層にn型不純物、例えばリンを導入し、ソース/ドレインエクステンション8A,8Bを形成する。

この後に、ゲート電極6A,6Bを含むシリコン基板1の上側全面に絶縁膜を形成し、その絶縁膜をエッチバックしてゲート電極6A,6Bの両側部分のみを残して絶縁性サイドウォール10を形成する。絶縁膜には、例えばCVD法により形成された酸化シリコン膜が用いられる。

【0029】

続いて、絶縁性サイドウォール10とゲート電極6A,6Bをマスクにしてシリコン基板1の表層に砒素等のn型不純物を再びイオン注入し、各ゲート電極6A,6Bの側方のシリコン基板1にソース/ドレイン領域11A,11B(高濃度不純物拡散領域)を形成する。

さらに、ゲート電極6A,6Bを含むシリコン基板1の上側全面に金属膜をスパッタ法により形成する。金属膜は、例えば、コバルト膜等の高融点金属が好ましいが、比較的に融点が低い金属であっても良い。そして、この金属膜を加熱してシリコンと反応させることにより、ゲート電極6A,6Bの上面と、ソース/ドレイン領域11A,11Bにおけるシリコン基板1上にそれぞれにコバルトシリサイド層等の金属シリサイド層12a、12bを形成する。この熱処理によって、各ソース/ドレイン領域11A,11Bが活性化されて低抵抗化する。

【0030】

その後に、素子分離絶縁膜2上などで未反応となっている高融点金属膜をウエットエッチングによって除去する。

ここまでの工程で、シリコン基板1の活性領域ごとに、ゲート絶縁膜5、ゲート電極6A,6B、ソース/ドレイン領域11A,11B等によって構成される2つのMOSトランジスタT1,T2が形成される。

【0031】

次に、ゲート電極6A,6Bを含むシリコン基板1の上側全面に、酸化防止絶縁膜13(カバー膜)としてプラズマCVD法で酸窒化シリコン(SiON)膜を厚さ約200nmに形成する。さらに、TEOS(tetra ethoxy silane)ガスを使用するプラズマCVD法により、酸化防止絶縁膜13の上に第1層間絶縁膜14として酸化シリコン(SiO2)膜を厚さ約1000nmに形成する。なお、TEOSを用いてプラズマCVD法によって形成されるSiO2膜を以下においてTEOS膜という。

そして、第1層間絶縁膜14の表面を化学的機械研磨 (CMP:Chemical Mechanical Polishing)法で研磨して平坦化させ、シリコン基板1の表面から第1層間絶縁膜14の表面までの膜厚を所定値、例えば、約700nmに調整する。

【0032】

次に、図1Bに示す断面構造を得るまでの工程について説明する。

まず、酸化防止絶縁膜13と第1層間絶縁膜14とをフォトリソグラフィ法によってパターニングして、コンタクトホール15A,15B,15Cを形成する。コンタクトホール15A〜15Cの深さはソース/ドレイン領域11A,11Bのそれぞれの高融点金属シリサイド層12a、12bに到達するまでとし、その径は例えば0.25μmにする。

【0033】

そして、コンタクトホール15A〜15Cを用いてソース/ドレイン領域11A,11Bに電気的に接続される導電性プラグ16A,16B,16Cを形成する。具体的には、コンタクトホール15A〜15Cの内面に厚さが30nmのチタン(Ti)膜と、厚さが20nmの窒化チタン(TiN)膜とを順番にスパッタ法等により形成し、2層の積層構造を有する密着膜(グルー膜)17Aを作製する。さらに、密着膜17A上にタングステン(W)膜17BをCVD法により成長させる。この膜厚は、第1層間絶縁膜14上で、例えば300nmとし、W膜17Bでコンタクトホール15A〜15Cの空隙を埋める。第1層間絶縁膜14の上面上に成長した余分なW膜17B及び密着膜17BをCMP法で除去する。これにより、コンタクトホール15A〜15Cには、それぞれ導電性プラグ16A,16B,16Cが形成される。

【0034】

さらに、第1層間絶縁膜14上及び導電性プラグ16A〜16C上に、第1酸化防止膜18として、SiON膜を例えばプラズマCVD法により例えば130nmの膜厚に形成する。さらに、第1酸化防止膜18の上に第2層間絶縁膜19として、シリコン酸化膜を例えばTEOSを原料とするプラズマCVD法によって300nmの膜厚で形成する。なお、酸化窒化シリコン(SiON)膜の代わりに窒化シリコン(SiN)膜やアルミナ(Al2O3)膜を形成しても良い。

【0035】

次に、図1Cに示す断面構造を得るまでの工程について説明する。

第2層間絶縁膜19上に図示を省略するレジスト膜を第2層間絶縁膜19上にスピンコート法等により塗布し、フォトリソグラフィ技術によって導電性プラグ16A上と導電性プラグ16B上のそれぞれに開口部を1つずつ形成する。そして、このようなレジストパターンをマスクとして使い、第2層間絶縁膜19及び第1酸化防止膜18をドライエッチングし、コンタクトホール15A,15Bに接続されるビアホール20A,20Bを形成する。ビアホール20A,20Bには、導電性プラグ21A,21Bが埋め込まれる。導電性プラグ21A,21Bは、導電性プラグ16A、16Bと同様のプロセスで作製される密着層22AとW層22Bとから形成される。

【0036】

第2層間絶縁膜19の上に形成された余分な密着層22A及びW層22Bは、CMP法による研磨で除去する。CMP法では、研磨対象である密着層22A及びW層22Bの研磨速度が下地の第2層間絶縁膜19よりも速くなるようなスラリ、例えばキャボット・マイクロエレクトロニクス社製のSSW2000を使用する。そして、第2層間絶縁膜19上に研磨残を残さないために、このCMPの研磨量は密着層22A及びW層22Bの合計膜厚よりも厚く設定する。即ち、ここでのCMP研磨はオーバー研磨とする。

【0037】

次に、図1Dに示す断面構造を得るまでの工程について説明する。

第2層間絶縁膜19の表面をNH3プラズマで処理することにより、表面の酸素原子にNH基を結合させる。これによって、第2層間絶縁膜19上にTi原子をさらに堆積させてもTi原子が酸素原子に捕獲されてしまうことがなくなり、第2層間絶縁膜19の表面を自在に移動できるようになる。つまり、第2層間絶縁膜19上にTi膜が所定の結晶配向、例えば、(002)配向に自己組織化できるようになり、その上面の平坦性を改善できる。

【0038】

なお、アンモニアプラズマ処理は、例えばシリコン基板1に対して約9mm(350mils)離間した位置に対向電極を設置する構造を有する平行平板型のプラズマ処理装置を用いて実施する。処理条件は、例えば、266Pa(2Torr)の圧力下、400℃の基板温度に保持された処理容器中にアンモニアガスを350sccmの流量で供給し、シリコン基板1側に13.56MHzの高周波を100Wのパワーで、また対向電極に350kHzの高周波を55Wのパワーで、60秒間供給することにより実行する。

【0039】

次に、シリコン基板1とターゲットの間の距離を60mmに設定したスパッタ装置中で、0.15Paのアルゴン(Ar)雰囲気下、20℃の基板温度で2.6kWのスパッタDCパワーを5秒間供給した。これによって、第2層間絶縁膜19と導電性プラグ21A,21Bの上に、強い(002)配向のTi膜が約20nmの厚さに形成される。

【0040】

さらに、Ti膜を窒素の雰囲気中において基板温度650℃で60秒のRTAを行うことにより、Ti膜を(111)配向のTiN膜からなる下地導電膜23に変える。

次に、下地導電膜23の上に酸素拡散バリア膜24として窒化チタンアルミニウム(TiAlN)膜を形成する。TiAlN膜は、例えば、Ti及びAlの合金化したターゲットを使った反応性スパッタにより100nmの厚さに形成する。成膜条件は、例えばArを40sccm及び窒素を10sccmの流量で供給した混合雰囲気において、253.3Paの圧力、400℃の基板温度、1.0kWのスパッタパワーに設定する。

【0041】

さらに、酸素拡散バリア膜24上に第1の導電膜である下部電極膜25を形成する。下部電極膜25は、貴金属、例えばIrをAr雰囲気中で、0.2Paの圧力、450℃の基板温度、0.3kWのスパッタパワーで60nm〜100nmの厚さに形成する。下部電極膜25は、Irの代わりにRu、Rh又はPdで形成しても良い。

酸化拡散バリア層24と下部電極25は、TiNの下地導電膜23の結晶方位を受け継いで(111)に優先配向する。

【0042】

この後、図1Eに示すように、不活性ガス、例えばArガスの雰囲気中で、下部電極膜25に対して650℃〜750℃、60秒間、RTAを行う。この熱処理によってIrの結晶性が向上し、さらに、下地導電膜23、酸素拡散バリア膜24及び下部電極膜25の各層の密着性が向上する。

【0043】

次に、図1Fに示すように、下部電極膜25の上に、スパッタ法により酸化導電膜26を形成する。酸化導電膜26は、貴金属酸化膜、例えば、IrOx膜からなり、その厚さは5nm〜50nmとする。この場合、酸化導電膜26は下部電極25を構成する金属の酸化物である。IrOx膜の成膜条件は、例えば、Arと酸素の混合雰囲気中で、0.11Paの圧力、10℃〜100℃、より好ましくは50℃〜75℃の基板温度で、1kWのスパッタパワーに設定する。スパッタ用のターゲットはイリジウムである。

そのような条件で形成された酸化導電膜26は、少なくともアモルファス、微結晶のいずれかの状態、即ち、アモルファス、微結晶、又はアモルファスと微結晶が混在する状態となっている。

【0044】

ここで、IrOx膜の酸化度及び結晶性は、その上に成膜する強誘電体膜(PZT膜)の結晶性に影響を与える。そして、成膜時のArと酸素の混合雰囲気の酸素比率、成膜レート(スパッタパワー)、成膜温度、及び膜厚さは、IrOx膜の酸化度及び結晶性に大きな影響を与える。IrOx膜の酸化度が高すぎたり、或いは低すぎたりすると、熱処理するときに再酸化して結晶の異常成長を引き起こし易くなる。さらに、後に説明する還元工程で酸化導電膜26を均一に還元することが困難になる。

【0045】

そこで、IrOx膜の形成条件として、例えば成膜雰囲気にArと酸素(O2)をそれぞれ188sccmと12sccmの流量で導入するとともに、成膜パワーを0.5kW、成膜時間を15秒、成膜レートを1.6nm/秒、成膜温度を60℃とする。ここで、ArとO2の全流量中でのO2の流量比PO2は6流量%である。この条件により形成するIrOx膜の厚さを25nmとする。IrOx膜の形成条件の詳細については、後のPZT形成工程の説明に併せてさらに詳述する。

【0046】

次に、図1Gに示すように、そのような条件で形成したIrOx膜を大気圧下、又は1Paから大気圧までの範囲の圧力下でRTAにより加熱して結晶化する。加熱温度は600℃以上、750℃以下が望ましい。この加熱温度の詳細についてもPZT形成工程の説明に併せてさらに詳述する。

【0047】

続いて、図1Hに示すように、酸化導電膜26であるIrOx膜の上に、第1強誘電体膜27としてPZT膜を形成する。この実施の形態では、PZT膜として、最初にMOCVD法によって初期層27A及びコア層27Bを形成した後に、スパッタ法によってコア層27B上に表層部27Cを形成する。

より詳細には、酸化導電膜26を形成したシリコン基板1をMOCVD装置のチャンバにセットする。そして、図2に示すように、チャンバ内にO2ガスをチャンバ内に、例えば、2000sccm流してから、シリコン基板1を目標温度、即ち第1強誘電体膜27のうちの初期層27A及びコア層27Bの形成温度まで昇温させる。なお、この昇温過程では、熱処理で結晶化させた酸化導電膜26のIrOxが再度酸化されることはない。

【0048】

目標温度に到達したら、図2に示すように、第1強誘電体膜27の原料ガスを導入して初期層27Aの形成を開始する前にインターバルを設け、ArガスとO2ガスのそれぞれの流量を初期層27Aの形成に必要な流量に切り替える。具体的には、Arガスの流量を1375sccmに切り替え、O2ガスの流量を625sccmに切り替えた。この場合の酸素比率は0.33倍である。なお、酸素比率は、PZT形成に用いられる有機金属原料と反応させるために必要な酸素量に対する実際の酸素量の割合を示す。

【0049】

そして、インターバルにおいて、Arガス及びO2ガスのそれぞれの流量の調整を終えた後に、第1強誘電体膜27の原料ガスを導入し、初期層27Aの形成を開始する。

PZT膜を構成するPb,Zr,Tiは、それぞれが液体原料として予め調製されている。ここで、Pb原料としてテトラキスジメチルへプタンジオネート鉛(Pb(DMHD)2)を、Zr原料としてテトラキスジメチルへプタンジオネートジルコニウム(Zr(DMHD)4)を、Ti原料としてビスイソプロポキシビスジピバロイルメタネートチタン(Ti(O−iPr)2(DPM)2)をそれぞれ使用した。これらの原料を、それぞれ酢酸ブチルに0.2mol/L(モル/リットル)、0.1mol/L、0.1mol/Lの濃度で溶解させ、Pb,Zr,Tiの各液体原料を製造した。そして、これら原料ガスの流量は、Pbの原料ガスの流量と、Zrの原料ガスの流量と、Tiの原料ガスの流量と、酢酸ブチルの流量との総量が常に1.2mL(ミリリットル)/分になるように制御する。

【0050】

具体的には、各液体原料の流量を制御しながら、MOCVD装置の気化器へ供給する。PZTの堆積レートは、各液体原料の流量で制御できる。例えば、成膜レートを0.04nm/秒に制御したい場合は、流量0.95mL/分の酢酸ブチル溶媒と共に、Pb,Zr,Tiの液体原料をそれぞれ0.1mL/分、0.07mL/分、0.08mL/分の流量で供給して気化させる。これに対して、堆積レートを0.17nm/秒に制御したい場合は、流量0.30mL/分の酢酸ブチル溶媒と共に、Pb,Zr,Tiの原料液体をそれぞれ0.26mL/分、0.34mL/分、0.30mL/分の流量で供給して気化させる。

【0051】

このような流量で原料ガスをチャンバ内に導入し、初期層27Aを厚さ2.5nm〜10nmに形成する。初期層27Aの形成段階では、結晶化された酸化導電膜26が、原料ガス中の溶媒成分によって均一に還元される。その結果、酸化導電膜26が均一で、且つ粒子が小さい結晶からなる第2の導電膜26Aに改質される。

【0052】

この段階では、チャンバ内の酸素比率は、0.33であり、この値は、O2の量がPb等の有機金属の原料成分と反応するのに必要とされる量に比べて不足していることを意味する。このため、原料ガス中の有機金属原料成分は、チャンバ内にあるO2ガスに加えて、酸化導電膜26中の酸素原子とも反応する。これによって、初期層27の形成と同時に、酸化導電膜26が還元されて第2の導電膜26Aが形成される。

【0053】

酸化導電膜26を還元した後にX線回折を行ったところ、図3に示すように、矢印A1や矢印A2の付近に現れるはずのIrOxのピークは確認されなかった。このことから、酸化導電膜26のIrOxが還元されてIrが形成されたことが分かる。

【0054】

IrOx膜の還元により形成される第2の導電膜26Aは、下部電極膜25を構成するIrの配向性を制御することにより、Irの(111)面を優先的に配向させられる。このため、第2の導電膜26Aの上には、PZTの(111)面を優先的に配向させた初期層27Aを形成することが可能である。初期層27Aの膜厚は、膜厚2.5nm〜10nmであることが望ましい。初期層27Aの膜厚が2.5nmを下回ると、成膜時間が短くなるので酸化導電膜26が還元され難くなり、初期層27Aの配向性が悪くなる傾向がある。また、初期層27Aの膜厚が10nmを上回ると、PZTの酸素欠損等の影響によって最終的に得られる強誘電体キャパシタのスイッチング電荷量が低くなる傾向がある。

【0055】

ところで、酸化導電膜26を構成するIrOx膜を還元してIrからなる第2の導電膜26Aにするためには、IrOx膜を最適な条件で形成することが重要である。

【0056】

例えば、スパッタ法によりIrOx膜を形成する際のスパッタパワーを0.5kWに設定した場合には、ArとO2の混合雰囲気中の酸素流量比は4流量%以上且つ10流量%以下であることが望ましい。これに対して、スパッタパワーを0.5kWよりも大きくする場合は酸素流量比をさらに高くすることが好ましい。これに対してスパッタパワーを0.5kWよりも小さくする場合には酸素流量比をさらに低くする必要がある。

また、酸化導電膜26の膜厚は、10nm〜40nmが望ましい。酸化導電膜26がそれよりも薄くなると、その後の熱処理時に下部電極膜25が酸化し易くなる。これに対して酸化導電膜26がそれよりも厚すぎると、PZTの初期層27A形成時の還元工程で酸化導電膜26を十分に還元させることができなくなる。

【0057】

さらに、酸化導電膜26は、アモルファス又は均一な微結晶であることが望ましい。成膜時に結晶の酸化導電膜26を形成しようとすると、成膜初期状態で均一な膜質が得られ難い。また、そのような結晶質の膜は、図2に示した昇温時に再酸化され易く、上記の還元工程において膜を均一に還元することが困難になる。酸化導電膜26のように、アモルファス又は略均一な微結晶の膜を形成すれば、上記のような還元雰囲気中に曝したときに、IrOxを均一に形成し、且つIrOxの還元により結晶粒径が小さいIrを形成することができる。

【0058】

均一で、且つ結晶粒径の小さいIrを形成すれば、上記のようにPZTの結晶性を向上でき、PZT膜の表面のモフォロジを改善できる。これにより、製品の歩留まりを向上できる。これと当時に、下部電極膜25と強誘電体膜の界面が確実に形成され、電気特性に優れる。特に、低電圧で動作させたときの電気特性に優れる。

【0059】

そこで、この実施の形態では、酸化導電膜26の成膜条件を上記の条件に設定した。その条件で形成した酸化導電膜26のX線回折結果を図4Aに示す。図4Aによれば、(200)面のシリコンを示すピークのみが観測され、IrOxの結晶ピークは確認されなかった。このことから、酸化導電膜26がアモルファス又は微結晶で形成されたことが分かる。

【0060】

さらに、酸化導電膜26の成膜後に、シリコン基板1を600℃以上、より好ましくは700℃以上で、且つ750℃以下の温度でRTA処理した。

なお、熱処理温度が600℃より低い場合は、図2に示す昇温時に異常酸化が発生し易くなる。これに対し、熱処理温度が750℃を越えると、CMOSのトランジスタ特性が熱履歴の影響により初期状態から変化し易くなる。このため、この実施の形態では、酸化導電膜26形成後の熱処理の温度をその一例として650℃に設定する。また、このときの圧力は、常圧以下で0.1Paより高く設定した。これにより、酸化導電膜26のIrOxが均一に結晶化される。

【0061】

ここで、図4BにXRD(X-ray diffraction)回折測定結果を示す。XRD回折のデータは、酸化導電膜26を上記の条件により熱処理する前(Before Annealing)と後(Annealed)のそれぞれについて測定した結果である。熱処理前では、矢印B1に示すIr(111)のピークのみが確認された。矢印B1のピークは、下地である下部電極25のIrに起因するピークであると考えられる。これに対して、熱処理後では、矢印B1に示すIr(111)のピークと、矢印B2に示すIr(101)のピーク(28.06°)、矢印B3に示す(110)のピーク(34.76°)、矢印B4に示す(211)のピーク(54.02°)が確認された。この測定結果から熱処理によって酸化導電膜26が結晶化されたことがかわる。

【0062】

以上のように第2の導電膜26Aと初期層27Aを形成した後に、図2に示すように、原料ガスの導入を一旦停止する。そして、PZT成長再開までのインターバルに、ArガスとO2ガスの流量を、コア層27Bを形成するための流量条件に切り替える。この実施の形態では、Arガスの流量を0sccmに切り替え、O2ガスの流量を4500sccmに切り替えた。ここでの酸素比率は、有機金属原料と反応させるために必要な酸素量の6.77倍である。そして、ガス流量を切り替えた後に、原料ガスを再び導入してコア層27Bの形成を開始する。コア層27Bの形成段階では、O2量が過剰な状態で原料ガスを導入するので、酸素欠損の少ないコア層27Bが形成される。また、コア層27Bは、(111)面に優先配向された初期層27A上に形成されるので、(111)面に優先配向して形成される。

【0063】

以上のようなMOCVD法によるPZT成膜工程は、チャンバ内の圧力を665Paとし、基板温度を620℃に保持し、原料ガスをトータルで620秒間供給することにより実施され、全体として膜厚100nmの初期層27A及びコア層27Bを形成する。

【0064】

なお、第1強誘電体膜27の形成にあたっては、初期層27Aの堆積速度、即ち成膜レートを低い値に設定し、その後のコア層27Bの成膜レートを相対的に高い値に設定することが望ましい。例えば、初期層27Aの成膜レートは0.1nm/秒以下、好ましくは0.05nm/秒以下、より好ましくは0.04nm/秒以下に設定される。また、コア層27Bの成膜レートは、例えば0.17nm/秒に設定される。

【0065】

初期層27Aの成膜レートが0.1nm/秒を上回ると、その上に形成されるコア層27Bのモフォロジが悪化し、最終的に得られる強誘電体キャパシタのスイッチング電荷量が低くなる傾向がある。初期層27Aを0.1nm/秒以下の成膜レートで形成した強誘電体キャパシタのスイッチング電荷量が40μC/cm2であったのに対し、初期層27Aをコア層27Bと同じ0.17nm/秒の成膜レートで形成した強誘電体キャパシタのスイッチング電荷量は32μC/cm2と低かった。

【0066】

このようにして形成した第1強誘電体膜27は、その表面が平坦であった。また、従来のPZT膜のように、モフォロジの不均一さに起因して発生すると考えられる膜の白濁も解消された。

【0067】

ここで、下部電極膜25と酸化導電膜26を形成した後の熱処理条件が第1強誘電体膜27の結晶性に与える影響について再び検討する。下部電極膜25を形成した後の熱処理は、Ar雰囲気中、基板温度を650℃で60秒間実施した。さらに、酸化導電膜26を形成した後、熱処理の温度及び時間は650℃及び60秒とした。

【0068】

まず、酸化導電膜26の成膜温度が第1強誘電体膜27の結晶性に与える影響を調べた結果を図5A及び図5Bに示す。第1強誘電体膜27を形成した後に中央(Center)と、上側(Top)と、右側(Right)の3箇所でX線回折を行ったところ、酸化導電膜26の成膜温度が25℃から100℃の範囲では、第1強誘電体膜27のPZTの(100)面の配向強度は小さかった。図示を省略するがPZTの(101)面の配向強度も小さかった。これに対して、(111)面の配向強度は25℃から100℃の範囲で大きかった。したがって、酸化導電膜26の成膜温度を25℃から100℃の範囲内にすれば、(111)面に配向したPZTからなる第1強誘電体膜27を形成できる。なお、実験によればその製膜温度は、10℃以上〜25℃の範囲でも好ましいことがわかっている。

【0069】

次に、下部電極膜25及び酸化導電膜26の熱処理条件がPZTの結晶性に与える影響についてX線回折を用いて調査した結果を図6A〜図6Eに示す。図6Aの横軸は、下部電極膜25の熱処理条件(横軸下段の“Ir−AN”)と、酸化導電膜26の熱処理条件(横軸上段の“IrOx−AN”)とを示す。例えば、最も左欄の熱処理条件は、下部電極膜25を650℃で熱処理し、酸化導電膜26は熱処理しないことを示している。また、縦軸は、酸化導電膜26上の第1強誘電体膜27をX線回折したときの(100)面の配向強度を示している。データは、横軸に示す各熱処理条件に対して、前記した5箇所のそれぞれを測定している。図6Bは、縦軸が酸化導電膜26上の第1強誘電体膜27をX線回折したときの(101)面の配向強度を示している。図6Cは、縦軸が(111)面の配向強度を示している。図6D、縦軸が(222)面の配向率を示している。図6Eは、縦軸が第1強誘電体膜27を構成するPZTの(111)面のピークのロッキング半値幅を示している。なお、図6A〜図6Fにおいて、W/Oは、熱制御しないことを示している。

【0070】

なお、比較のため、熱処理の雰囲気は、100流量%のAr、1流量%のO2、20流量%のO2、100流量%のO2について調べた。それぞれの調査は、シリコン基板1のノッチを下として、シリコン基板1の上側であるTopと、左側であるLeftと、中心であるCenterと、右側より中心に10mmの位置のRight1と、右側のRight2との最大5箇所で実施し、そのそれぞれについて結晶性を調べた。

【0071】

図6A、図6B及び図6Dの横軸に示すIr−ANの熱処理を行い、且つIrOx−ANの熱処理を行わない場合、つまり下部電極膜25は熱処理したが酸化導電膜26は熱処理していない場合、PZTは(100)面、及び(101)面の配向強度が高く、(222)面の配向率は低かった。また、図6Cに示すように、この熱処理条件での(111)面の配向強度は他の熱処理条件と同等であった。同様に、図6Eに示すように、ロッキング半値幅は他の条件と同等であった。

【0072】

これに対して、図6A、図6B及び図6Dに示すように、横軸のIrOx−ANが100流量%のAr、つまり100流量%のArの雰囲気中でIrOxを熱処理した場合には、(100)面、(101)面の配向強度が高くなり、(222)面の配向率が低かった。これは、酸化導電膜26は結晶化されるが、酸化導電膜26の酸素欠損が多過ぎるため、MOCVD装置のチャンバ内の昇温過程中で再度異常酸化が生じたためであると考えられる。

【0073】

次に、酸化導電膜26を熱処理するときの雰囲気中の酸素の割合が結晶性に与える影響を検討する。図6A、図6B及び図6Dのそれぞれにおいて、酸素割合が多くなると(100)面及び(101)面の配向が弱くなり、(222)面の配向率が向上することが分かった。これは、酸素の割合が増え過ぎると、熱処理中に酸化導電膜26が異常酸化される可能性が高く、その傾向は酸素割合が増えるほど顕著になると考えられるからである。

【0074】

ここで、異常酸化の有無については、第1強誘電体膜27の表面の凹凸の数を計測することで確認できる。図6Fは、各条件で熱処理した酸化導電膜26の上に成膜した第1強誘電体膜27の基板中心に2.7×2.7μm2の範囲内で発生した表面突起の数の計測結果を示している。下部電極膜25を熱処理した場合、酸素比率を20流量%にして酸化導電膜26を熱処理したシリコン基板1の表面突起数が一番少なかった。

【0075】

また、下部電極膜25の熱処理を行わず、酸化導電膜26を成膜した後に熱処理を行ったところ、図6A及び図6Bに示すように(100)面及び(101)面の配向強度が低くなり、図6Dに示すように(222)配向率が高くなった。また、図6Fに示すように、酸素比率を20流量%にして熱処理したシリコン基板1の結晶性が一番良好であった。さらに、図6Eに示すように、第1強誘電体膜27の表面の突起数も少なかった。

【0076】

次に、下部電極膜25を熱処理すると共に、IrOxの酸化導電膜26を酸素が20流量%のAr雰囲気中で熱処理したときの第1強誘電体膜27の表面状態をSEM画像に基づいて図7Aに図に示す。また、比較例として、リファレンス方法で製造したPZT膜の表面状態をSEM画像に基づいて図7Bに示す。なお、リファレンス方法とは、IrOxの酸化導電膜の熱処理を行わずに、酸化導電膜26の上に第1強誘電体膜を形成する製造方法である。リファレンス方法によるPZT膜の表面に凹凸が多数確認されるのに対して、この実施の形態に係る製造方法で形成した第1強誘電体膜27の表面の凹凸は大幅に減少した。

【0077】

再現性を確認するために、リファレンス方法と、本実施形態に係る製造方法とを複数回ずつ実施して比較したところ、前記と同様の結果が得られた。本実施形態とリファレンス方法を採用した試料をそれぞれ3枚ずつ形成して2.7×2.7μm2の範囲の表面突起を比較したところ、図8に示す結果が得られた。本実施形態の方法によれば、リファレンス方法に比べて、PZT膜の表面の突起数が減少し、第1強誘電体膜27の表面のモフォロジの改善が確認された。

また、それらの試料についてPZT膜の結晶方位を調べたところ、図9A、図9B、図9Cに示すように、(100)面、(101)面の配向強度が低くなる一方、(222)配向強度が高くなった。

【0078】

次に、図1Iに示す断面構造を得るまでの工程について説明する。

第1強誘電体膜27の全面に、アモルファス状の第2強誘電体膜28を例えばスパッタ法により形成する。第2強誘電体膜28は、例えば膜厚が1nm〜30nm、より好ましくは20nmとする。

【0079】

さらに、第2強誘電体膜28上に第3の導電膜として第1上部電極膜29を形成する。第1上部電極膜29の形成に当たっては、先ず、第2強誘電体膜28上に、結晶性のIrOx膜をスパッタ法により厚さ25nmに形成する。例えば、このときの成膜温度を300℃とし、成膜ガスとしてAr及びO2を用い、流量はいずれも100sccmとする。また、スパッタパワーは、例えば1kW〜2kW程度とする。次いで、RTA法で725℃、20sccmの酸素と2000sccmのArを供給した雰囲気中で60秒間熱処理を行う。この熱処理によって第2強誘電体膜28が完全に結晶化すると共に、第1上部電極膜29のプラズマダメージが回復し、第1強誘電体膜27中の酸素欠損が補償される。

【0080】

さらに、膜厚が50nm〜150nmの第2上部電極膜30として、IrOY膜を形成する。IrOY膜は、例えば、Ar雰囲気中で、0.8Paの圧力下、1.0kWのスパッタパワーで45秒間堆積させ、その厚さを125nmにする。IrOY膜の異常成長を抑制するために、成膜温度は100℃以下にすることが望ましい。また、工程劣化を抑えるために酸化イリジウム膜をIrO2の化学量論組成に近い組成にすると、水素に対して触媒作用を生じることがなく、第2強誘電体膜28が水素ラジカルにより還元される問題が抑制され、キャパシタの水素耐性が向上する。

なお、第2上部電極30の材料として、IrO2の代わりにIr、Ru、Rh、Re、Os、Pd、これらの酸化物、SrRuO3などの導電性酸化物や、これらの積層構造を用いても良い。

【0081】

次に、図1Jに示す断面構造を得るまでの工程について説明する。

まず、第2上部電極膜30上に水素バリア膜31として、Ir膜をスパッタにより、Ar雰囲気中、1Paの圧力下、1.0kWのスパッタパワーで50nm〜100nmの厚さに堆積する。なお、水素バリア膜31は、導電性向上膜としても機能する。その材料は、Irに限定されず、Ru、Rh膜及びPd膜からなる群から選択された膜を使うことも可能である。

【0082】

そして、シリコン基板1の背面を洗浄した後、第1、第2上部電極膜29,30や、第1、第2強誘電体膜27,28、第1、第2下部電極膜29,30などをパターニングする際にハードマスクとして用いる第1のマスク材料層32と第2のマスク材料層33とを順次形成する。

第1のマスク材料層32は、水素バリア膜31の上に形成され、スパッタ法により成膜されたTiNからなる。第1のマスク材料層32は、TiAlNや、TaAlN、TaN膜及びこれらの積層膜でも良い。

第2のマスク材料層33は、第1のマスク材料層32の上に形成され、例えばTEOSガスを使用するCVD法で成膜された酸化シリコン膜からなる。

【0083】

この後、第2のマスク材料層33の上に図示を省略するフォトレジストを塗布し、次いでフォトレジストを露光、現像してキャパシタ平面形状となるレジストパターンを形成する。

【0084】

エッチングの際には、最初にレジストパターンをマスクに使用して第2のマスク材料層33を島状にパターニングし、第2のマスク材料層33をマスクにして第1のマスク材料層32をエッチングする。これにより、第2のマスク材料層33と、第1のマスク材料層32とからなるハードマスク34がキャパシタ形成領域に島状に形成される。

【0085】

次に、図1Kに示す断面構造を得るまでの工程について説明する。

HBr、O2、Ar、及びC4F8の混合ガスをエッチングガスとしてプラズマエッチングを行い、ハードマスク34で覆われていない部分の第1、第2上部電極膜29,30、第1、第2強誘電体膜27,28、第2の導電膜26A及び下部電極膜25をドライエッチングする。これによって、上部電極膜29,30がパターニングされてキャパシタ用の上部電極35が形成され、同様に第2の導電膜26A及び下部電極膜25がパターニングされてキャパシタ用の下部電極36が形成される。そして、上部電極80、強誘電体膜27,28、及び下部電極73を有する強誘電体キャパシタ37が形成される。パターニングが終了したら第2のマスク材料層33をドライエッチング又はウェットエッチにより除去する。

【0086】

次に、図1Lに示すように、強誘電体キャパシタ37で覆われていない部分の酸素拡散バリア膜24、下地導電膜23、及び第1のマスク材料層32をドライエッチングにより除去し、酸素拡散バリア膜24及び下地導電膜23を強誘電体キャパシタ37の下のみに島状に残す。

【0087】

次に、図1Mに示す断面構造を得るまでの工程について説明する。

強誘電体キャパシタ37及び第2層間絶縁膜19を覆う第1保護膜41としてAl2O3をスパッタ法により20nmの膜厚に形成する。又は、第1保護膜41としてMOCVD法又はALD法で2nm〜5nmのAl2O3膜を形成する。

【0088】

ここで、強誘電体膜27,28のダメージを回復させる目的で、酸素含有雰囲気中で回復アニールを施す。回復アニールの条件は特に限定されないが、例えば炉内において基板温度550℃〜700℃で実施する。また、強誘電体膜27,28がPZTの場合、600℃酸素の雰囲気中で60分アニールを行うことが好ましい。

【0089】

次に、第1保護膜41を覆うように、第2保護膜42としてAl2O3をCVD法により約38nmの膜厚に形成する。

第2保護膜42を構成するAl2O3膜は、水素や水分等の還元性物質が透過することを阻止する機能に優れている。このため、強誘電体膜27,28の強誘電体特性が還元性物質により劣化されることが防止される。

【0090】

さらに、第2保護膜42の全面に、第3層間絶縁膜43としてシリコン酸化物を例えばプラズマCVD法により膜厚1500nmで形成する。第3層間絶縁膜43としてシリコン酸化膜を形成する場合には、原料ガスとして、例えば、TEOSガスと酸素ガスとヘリウムガスとの混合ガスを用いる。なお、第3層間絶縁膜43として、例えば、無機ガスを用いて絶縁膜等を形成しても良い。第3層間絶縁膜43を形成したら、その表面を例えばCMP法で平坦化する。

続いて、N2Oガス又はN2ガス等を用いて発生させたプラズマ雰囲気で、熱処理を行って第3層間絶縁膜43中の水分を除去する。この際、第3層間絶縁膜43の膜質が改善されて膜中に水分が入り難くなる。

【0091】

次に、図1Nに示す断面構造を得るまでの工程について説明する。

まず、第3層間絶縁膜43の全面に、バリア膜として第3保護膜44を例えばスパッタ法又はCVD法により形成する。第3保護膜44としては、例えば、膜厚が20nm〜100nmのAl2O3膜が用いられる。平坦化された第3層間絶縁膜43上に第3保護膜44が形成されるため、第3保護膜44の表面は平坦になる。

【0092】

さらに、第3保護膜44の全面に第4層間絶縁膜45を例えばTEOSガスを用いるプラズマCVD法により形成する。第4層間絶縁膜45としては、例えば膜厚が300nm〜500nmのシリコン酸化膜が用いられる。なお、第4層間絶縁膜45として、SiON膜又はシリコン窒化膜等を形成しても良い。第4層間絶縁膜45を形成したら、その表面を例えばCMP法で平坦化する。

【0093】

続いて、レジストマスクを用いて第4層間絶縁膜45中にビアホール46A,46Bを形成する。ビアホール46A,46Bを形成する際には、キャパタ81の上部電極80を覆う水素バリア膜31を露出させた後、550℃で酸素雰囲気中において熱処理を行う。これによって、ビアホール46A,46Bの形成時に第1強誘電体膜27中に生じた酸素欠損が回復される。この後、それぞれのビアホール46A,46Bを介して強誘電体キャパシタ37の上部電極35に電気的に接続される導電性プラグ47A,47Bが形成される。

【0094】

次に、図1Oに示す断面構造を得るまでの工程について説明する。

pウェル3の中央の導電性プラグ16Bの上にビアホール48を形成する。ビアホール48に導電性プラグ49を形成する際には、ビアホール48の表面にTiN膜を単層で密着層として形成するのが好ましい。なお、密着層は、Ti膜をスパッタにより形成し、その上にTiN膜をMOCVD法により形成することで形成することも可能である。この場合、TiN膜から炭素除去を行うため、窒素と水素の混合ガスプラズマ中での処理が必要になるが、この実施の形態では、上部電極35上にIrからなる水素バリア膜31を形成しているので、上部電極35が還元されることはない。

【0095】

次に、図1Pに示す断面構造を得るまでの工程について説明する。

第4層間絶縁膜45上に導電性プラグ47A,47B,49に対応して配線パターンを形成する。即ち、例えばスパッタ法により、膜厚が60nmのTi膜と、膜厚が30nmのTiN膜と、膜厚が360nmのAlCu合金膜と、膜厚が5nmのTi膜と、膜厚が70nmのTiN膜とを順次形成する。これにより、Ti膜、TiN膜、AlCu合金膜、Ti膜及びTiN膜からなる積層膜を形成する。

【0096】

次に、フォトリソグラフィ技術を用い、積層膜をパターニングする。この結果、積層膜からなる配線(第1金属配線層)51A,51B,51Cが形成される。これにより、導電性プラグ47A,47Bを介して強誘電体キャパシタ37の上部電極膜35と配線51A,51Bとが電気的に接続される。同様に、導電性プラグ16B,49を介してソース/ドレイン領域11Aと配線51Cとが電気的に接続される。

その後、図示を省略するが層間絶縁膜を形成した後、導電性プラグの形成及び下から第2〜5層目以降の配線の形成等を行う。そして、例えばTEOS酸化膜及びSiN膜からなるカバー膜を形成すると、強誘電体キャパシタを有する強誘電体メモリが完成する。

【0097】

以上、説明したように、この実施の形態ではアモルファス又は微結晶の金属酸化膜である酸化導電膜26を形成し、酸化導電膜26をアニールした後、酸化導電膜26を還元して第2の導電膜26Aにしてから第1強誘電体膜27をMOCVD法により形成した。酸化導電膜26をアニールによって均一な結晶にした後に還元して金属膜を形成することで、結晶粒の小さい第2の導電膜26Aが得られる。これによって、第1強誘電体膜27が結晶粒の小さい第2の導電膜26A上に形成されるので、第1強誘電体膜27を構成するPZTのモフォロジが良好になる。このようにして強誘電体キャパシタ37を製造すると、キャパシタ構造の下部電極36及び強誘電体膜27,28の結晶性を向上できる。これによって、強誘電体膜27,28の面内分布が良くなってモフォロジが向上し、工程劣化を防止できる。その結果、高い反転電荷量を得られ、信頼性の高いキャパシタ構造を実現できる。また、リーク電流が低減され、信頼性の高い半導体装置が得られる。

【0098】

特に、酸化導電膜26を成膜温度が10℃〜100℃で、より好ましくは25℃〜50℃とすることで、IrOxのアモルファス又は微結晶を確実に形成できる。さらに、酸化導電膜26の成膜後の熱処理を1Paから大気圧までの範囲の値で、且つ酸素20流量%のAr雰囲気にすれば、結晶サイズの小さい均一な金属膜を形成することが可能になり、その上に成膜するPZTを所定の配向で、且つ良好なモフォロジにできる。

【0099】

なお、従来でMOCVD法により強誘電体膜を成膜するときは600℃以上の高温で成膜していたが、以下の課題が生じていた。即ち、PZT膜の結晶性は非常に不安定になり、非常に不均一なモフォロジ(表面凹凸)が発生し、基板周辺の膜が白濁することがあった。これは、昇温時に下部電極膜が異常酸化するためであると考えられる。異常酸化により形成されるIrOxは、強誘電体膜の形成時にMOCVDの溶媒であるTHF(TetraHydroFuran :C4H8O)液、又は酢酸ブチルによって還元されるが、このときに異相が出易くなる。この結果、その上に堆積される強誘電体膜の結晶性が悪くなる。この実施の形態に係る半導体装置の製造方法によれば、このような課題が解決され、信頼性の高い半導体装置が得られる。

【0100】

(第2実施の形態)

本発明の第2実施の形態について図10を参照して詳細に説明する。なお、第1実施の形態と同じ構成要素には同じ符号を付し、重複する説明は省略する。

本実施の形態に係る半導体装置は、スタック構造を有する半導体記憶装置(強誘電体メモリ)である。ビアホールを利用して導電性プラグ21A,21Bを形成した際、導電性プラグ21A,21Bの表面と周囲の第2層間絶縁膜19の両方を完全に平坦にするは困難である。一般的には、導電性プラグ21A,21Bの上面の高さが第2層間絶縁膜19の上面の高さより低くなり、第2層間絶縁膜19のうち導電性プラグ21A,21Bの上にリセスが形成される。このリセスの深さは20nm〜50nmであり、典型的には約50nm程度である。このリセスは、下部電極及び強誘電体膜の配向に影響を与える。

【0101】

そこで、この実施の形態では、シリコン基板1上の第2層間絶縁膜19の表面をアンモニア(NH3)プラズマで処理し、第2層間絶縁膜19の表面の酸素原子にNH基を結合させる。これにより、第2層間絶縁膜19上にTi原子がさらに堆積されても、堆積したTi原子は酸素原子に捕獲されてしまうことがなく、第2層間絶縁膜19の表面を自在に移動できるようになる。この結果、第2層間絶縁膜19上に(002)配向に自己組織化されたTi膜が形成される。

【0102】

そのアンモニアプラズマ処理は、例えばシリコン基板1に対して約9mm(350mils)離間した位置に対向電極を有する平行平板型のプラズマ処理装置を使いて実施する。処理条件は、例えば、266Pa(2Torr)の圧力下、400℃の基板温度に保持された処理容器中にアンモニアガスを350sccmの流量で供給し、シリコン基板1側に13.56MHzの高周波を100Wのパワーで、また対向電極に350kHzの高周波を55Wのパワーで、60秒間供給することにより実行する。

【0103】

次に、シリコン基板1とターゲットの間の距離を60mmに設定したスパッタ装置中で、0.15PaのAr雰囲気、20℃の基板温度で2.6kWのスパッタDCパワーを35秒間供給する。これによって、強い(002)配向のTi膜が約100nmの厚さに形成される。

この後、RTAで窒素の雰囲気中、650℃の基板温度で60秒の熱処理を行うと、(111)配向のTiNからなる導電性の下地膜23Aが得られる。下地膜23Aの厚さは100nm〜300nmであることが好ましく、この実施の形態では約100nmとした。なお、下地膜23Aは窒化チタン膜に限定されず、タングステン膜、シリコン膜、及び銅膜のいずれかを形成しても良い。

【0104】

導電性プラグ16A,16Bのリセスの影響によって、下地膜23Aの上面には凹部が形成されるので、CMP法で下地膜23Aの上面を研磨して平坦化することで凹部を除去する。CMPで使用されるスラリは特に限定されないが、例えば、キャボット・マイクロエレクトロニクス社製のSSW2000を使用できる。ところで、CMP後の下地膜23Aの厚さは、研磨誤差に起因して、シリコン基板1の面内や、複数のシリコン基板1間でばらつきが生じる。そのようなばらつきを考慮して研磨時間を制御すれば、CMP後の下地膜23Aの厚さの目標値を50nm〜100nm、より好ましくは50nmにできる。

【0105】

ところで、下地膜23Aに対してCMPを行った後では、下地膜23Aの上面付近の結晶が研磨によって歪んだ状態になっている。このように結晶に歪を有する下地膜23Aの上方に強誘電体キャパシタ37を形成すると、その歪みの影響が下部電極36に及んで下部電極膜25の結晶性が劣化し、下地導電膜23の上の強誘電体膜27,28の特性が劣化することがある。このような不都合を回避するために、下地膜23Aの上面を前記したNH3プラズマに曝すことで、下地膜23Aの結晶の歪みを解消させ、これ以降に堆積させる膜に影響を与えないようにする。

【0106】

そして、下地膜23Aの上に、結晶性を向上させた導電性膜Tiを形成し、窒素の雰囲気中で熱処理して窒化させ、下地導電膜23を形成する。

その後のプロセスは、第1実施の形態と同様である。即ち、酸素拡散バリア膜24、下部電極膜25及び酸化導電膜26を形成し、酸素とArガスの混合ガス雰囲気中で急速熱処理(RTA)する。その後、第1強誘電体膜27をMOCVD法で形成するときに酸化導電膜26を還元して第2の導電膜26Aを形成する。さらに、第2強誘電体膜28と上部電極膜29,30、水素バリア膜31を順番に形成してからハードマスクを使ってパターニングし、強誘電体キャパシタ37を形成する。さらに、その上に配線を形成する。

【0107】

この実施の形態に係る製造方法では、アモルファス又は微結晶の酸化導電膜26をRTA処理により結晶化してから第1強誘電体膜27を形成するようにしたにしたので、第1実施の形態と同様の効果が得られる。特に、導電性プラグ16A,16Bの形成時に生じるリセスが強誘電体キャパシタ37に与える影響を低減できるので、信頼性の高い半導体装置が得られる。

【0108】

なお、図11に示すように、下地膜23Aを形成したら、CMP法で研磨して第2層間絶縁膜19の上面から除去し、導電性プラグ21A,21Bの上のみ残しても良い。

【0109】

また、図12に示すように、この実施の形態に係る強誘電体メモリ(半導体装置)及びその製造方法では、導電性プラグの形成工程を1回だけ実施しても良い。即ち、第1層間絶縁膜14に導電性プラグ16A,16Bを形成したら、導電性プラグ16A,16Bに直接に電気的に接続されるように強誘電体キャパシタ37を形成する。さらに、第3層間絶縁膜43を形成した後、強誘電体キャパシタ37に連通する開口52を形成し、配線51A,51Bを形成する。さらに、強誘電体キャパシタ37に接続されない導電性プラグ16Aの上にコンタクトホールを形成し、その中に導電性プラグ49を形成する。

【0110】

(第3実施の形態)

本発明の第3実施の形態について図面を参照して詳細に説明する。なお、第1及び第2実施の形態と同じ構成要素には同じ符号を付し、重複する説明は省略する。

この実施の形態は、プレーナ構造のキャパシタを有する半導体装置及びその製造方法に関する。

【0111】

まず、図13Aに示す断面構造を得るまでの工程について説明する。

シリコン基板1の表面に素子分離絶縁膜2によってメモリ領域内の活性領域同士、即ちpウェル3同士を区画し、トランジスタT1,T2を形成する。さらに、各ソース/ドレイン領域11A,11Bの位置に対応して第1層間絶縁膜14に図示を省略する導電性プラグ16Aと、導電性プラグ16B,16Cを形成する。ここまでの工程の詳細は、第1実施の形態と同様である。

【0112】

次に、第1層間絶縁膜14上及び導電性プラグ16A〜16C上に、第1酸化防止膜18及び第2層間絶縁膜19を形成する。第2層間絶縁膜19は、例えば、SiON膜を約100nmの膜厚に形成し、さらにTEOSを使用するプラズマCVD方によりシリコン酸化膜を約130nmの膜厚で堆積させた構成を有する。

【0113】

第2層間絶縁膜81の上には、下部電極密着膜82としてAl2O3膜をスパッタ法で20nm程度の厚さに形成する。その後、RTAにより650℃の酸素雰囲気中で下部電極密着膜82を酸化させる。

【0114】

下部電極密着膜82の上に、第1の金属膜である下部電極膜83(下部導電膜)を形成する。下部電極膜83には、例えば、スパッタ法で形成したIr膜が用いられ、その厚さは約150nmとする。なお、下部電極膜83は、Ir膜の代わりにPt膜、Ru膜、RuO2膜、SrRuO3膜のいずれかの単層膜、或いはこれらの積層膜でも良い。この後、下部電極膜83をRTA処理する。熱処理条件は、第1実施の形態と同様であり、例えばAr雰囲気中650℃〜750℃、60秒間とする。これにより、各層の密着性が向上する。

【0115】

さらに、下部電極膜83の上に酸化導電膜26として、貴金属酸化膜、例えば、IrOxからアモルファス又は均一な微結晶の膜を5nm〜50nm、好ましくは10nm〜40nmの厚さに形成する。成膜条件は、例えば、Arと酸素の混合雰囲気中、0.11Paの圧力、20℃〜300℃の基板温度で、1kWのスパッタパワーに設定する。そして、酸化導電膜26の形成後に、RTAによって結晶化する。RTAの条件は、第1実施の形態と同様である。RTAによって、酸化導電膜26が均一で、且つ微細な結晶になる。

【0116】

次に、図13Bに示す断面構造を得るまでの工程について説明する。

酸化導電膜26上に第1強誘電体膜27としてPZT膜をMOCVD法により形成する。この実施の形態では、最初にMOCVD法によって初期層27A及びコア層27Bを形成した後、スパッタ法によって表層部27Cを形成する。成膜条件は、第1実施の形態と同様である。初期層27Aの形成時に原料ガスに含まれる溶媒成分によって酸化導電膜26が還元されて第2の導電膜26Aに改質される。第2の導電膜26Aは、その下層の下部電極膜83のIr膜の配向性に合わせてIr(111)面に優先的に配向する。これにより、1強誘電体膜27のPZTは、下地となる第2の導電膜26Aの結晶配向に合わせて(111)面が優先的に配向される。

【0117】

次に、図13Cに示す断面構造を得るまでの工程について説明する。

まず、第1実施形態と同様に、第1強誘電体膜27の全面に、アモルファス状の第2強誘電体膜28を形成する。さらに第2強誘電体膜28上に、第1上部電極膜29、第2上部電極膜30、水素バリア膜31、ハードマスクとして用いる第1のマスク材料層32及び第2のマスク材料層33を順次形成する。

【0118】

第1上部電極膜29として酸化イリジウム膜を順に形成する。さらに、第2上部電極膜30として例えばIr等の貴金属膜を形成する。第1のマスク材料層32として、スパッタ法によりTiN膜を形成する。また、第2のマスク材料層33としてCVD法によりSiO2膜を形成する。

その後に、第2のマスク材料層33上に、上部電極形状のレジストパターン(不図示)を形成する。さらに、レジストパターンをマスクにして、第1、第2のマスク材料層32、33をエッチングする。

【0119】

そして、レジストパターンの下に残された第1のマスク材料層32及び第2のマスク材料層33をハードマスクにしてHBr、O2、Ar、及びC4F8の混合ガスをエッチングガスとしてプラズマエッチングする。

これにより、図13Dに示すように、上部電極膜29,30がパターニングされてキャパシタ用の上部電極85が形成される。エッチング後、第1、第2のマスク材料層32、33を除去する。

【0120】

さらに、レジスト除去したシリコン基板1を酸素含有雰囲気中で熱処理する。熱処理の温度は600〜700℃とする。本実施の形態では、その一例として650℃で40分間熱処理を行った。この熱処理は、プロセス中に強誘電体膜27,28が受けたダメージを回復させるもので、このようなアニールは回復アニールとも呼ばれる。

【0121】

次に、図13Eに示す断面構造を得るまでの工程について説明する。

パターニングされたフォトレジストパターンをマスク(不図示)に使用して強誘電体膜27,28をエッチングによりストライプ状にパターニングする。強誘電体膜27,28は、複数の上部電極85の下を通る長方形の平面形状を有している。次いで、酸素雰囲気で例えば300℃〜400℃、30分間〜120分間、熱処理を行う。

【0122】

この後、水素バリア膜31、上部電極85、強誘電体膜27,28、及びに第2の導電膜26A上に第1保護膜41としてAl2O3膜を例えばスパッタ法又はCVD法、或いはALD法により形成する。

【0123】

さらに、図13Fに示す断面構造を得るまでの工程について説明する。

第1保護膜30の全面にフォトレジスト膜を例えばスピンコート法によって形成する。フォトリソグラフィ法でフォトレジスト膜を所定の平面形状、即ち強誘電体キャパシタの下部電極の平面形状にパターニングする。

続いて、フォトレジスト膜をマスクにして第1保護膜41及び第2の導電膜26A、下部電極膜83及び下部電極密着膜82をエッチングして下部電極86を形成する。下部電極86の平面形状は、略長方形であり、その端部は強誘電体膜27,28からはみ出す大きさである。このようにしてパターニングされた上部電極85、強誘電体膜27,28及び下部電極86によって、強誘電体キャパシタ87が形成される。

【0124】

さらに、強誘電体キャパシタ87及び第2層間絶縁膜19の上面に第2保護膜42を例えばスパッタ法又はCVD法、或いはALD法によりAl2O3膜を形成する。第2保護膜42を形成した後、例えば500℃〜700℃の酸素雰囲気にて、30分間〜120分間の熱処理を行う。この結果、強誘電体膜27,28に酸素が供給され、強誘電体キャパシタ87の電気的特性が回復する。

【0125】

次に、図13Gに示す断面構造を得るまでの工程について説明する。

第2保護膜42の全面に第3層間絶縁膜43として、例えばTEOSを用いるプラズマCVD法により膜厚が1400nmのシリコン酸化物を形成する。この後、例えばCMP法により、第3層間絶縁膜43の表面を平坦化する。

【0126】

次いで、N2Oガス又はN2ガスを用いて発生させたプラズマ雰囲気にて、例えば350℃、2分間の熱処理を行う。熱処理の結果、第3層間絶縁膜43中の水分が除去されると共に、第3層間絶縁膜43の膜質が変化して膜中に水分が入り難くなる。この熱処理によって、第3層間絶縁膜43の表面が窒化されてSiON膜が形成される。

【0127】

さらに、第3層間絶縁膜43の全面に、第3保護膜44を形成する。第3保護膜44は、例えばスパッタ法又はCVD法で成膜した膜厚20nm〜50nmのAl2O3膜からなる。さらに、第3保護膜44上の全面に、第4層間絶縁膜45として例えば膜厚が300nmのシリコン酸化物をTEOSを用いるプラズマCVD法で形成する。

【0128】

第4層間絶縁膜45の上面に図示を省略するフォトレジスト膜を形成し、フォトレジスト膜をマスクにしてエッチングし、第3保護膜44、第3層間絶縁膜43、第2保護膜42を経て強誘電体キャパシタ87の上部電極85まで達するビアホール91を形成する。同様に、第4層間絶縁膜45上に形成したフォトレジスト膜を用いてエッチングし、強誘電体キャパシタ87の下部電極86まで達するビアホール92を形成する。

【0129】

次いで、例えば400℃〜600℃の酸素雰囲気で、30分間〜120分間の熱処理を行う。この結果、強誘電体膜27,28に酸素が供給され、強誘電体キャパシタ87の電気的特性が回復する。なお、この熱処理を、酸素雰囲気中ではなく、オゾン雰囲気中で行っても良い。オゾン雰囲気中で熱処理を行った場合にも、強誘電体膜27,28に酸素が供給されて強誘電体キャパシタ87の電気的特性が回復する。

【0130】

次いで、第3及び第4層間絶縁膜43,45、第2及び第3保護膜42,44、第2層間絶縁膜19を貫通し、導電性プラグ16A〜16Cまで達するビアホール93A,93Bをフォトリソグラフィ及びエッチングを用いて形成する。

【0131】

次に、図13Hに示す断面構造を得るまでの工程について説明する。

ビアホール91内に例えば膜厚が20nmのTi膜と、膜厚が50nmのTiN膜と順番に例えばスパッタ法により形成する。これらのTi膜及びTiN膜によって、第2コンタクトホール91に密着膜94Aが形成される。さらに、密着膜94A上にW膜94BをCVD法により成長させ、W膜94Bでビアホール91を埋める導電性プラグ95を形成する。同様にして、ビアホール92に導電性プラグ96、ビアホール93A,93Bに導電性プラグ97A,97Bを形成する。

【0132】

そして、導電性プラグ95〜97の上に、第1層目の金属配線層を形成する。これにより、導電体プラグ95を介して上部電極85に電気的に接続される配線51Bと、導電体プラグ96を介して下部電極86に電気的に接続される配線51Bと、導電体プラグ97A,97Bを介してソース/ドレイン領域11A,11Bに電気的に接続される配線51Aとが形成される。

【0133】

以上、説明したように、この実施の形態に係る半導体装置の製造方法は、下部電極膜25を形成した後、アモルファス又は微結晶からなる金属酸化膜である酸化導電膜26を形成し、RTAにより結晶化するようにした。そして、第1の強誘電体膜27の初期層を形成する際に酸素含有率を不足させて酸化導電膜26を還元するようにした。

これにより、酸化導電膜26を還元したときに微小な結晶の第2導電膜26Aが得られるようになる。従って、第1強誘電体膜27のコア層27BをMOCVD法により形成するときにPZT膜のモフォロジを改善できる。このため、プレーナ構造のキャパシタを有する半導体装置の製造方法において、第1実施の形態と同様の効果が得られる。

【0134】

なお、強誘電体膜としては、例えば、熱処理により結晶構造がBi層状構造又はペロブスカイト構造となる膜を形成することができる。このような膜としては、PZT膜の他、La、Ca、Sr及び/又はSi等を微量ドープしたPZT、SBT(タンタル酸ビスマスストロンチウム)、BLT((Bi,La)4Ti3O12)並びにBi系層状化合物などの一般式ABO3で表される材料からなる膜が挙げられる。

【0135】

以下に、本発明の実施形態について付記する。

(付記1)基板の上方に第1の金属からなる第1の膜を形成する工程と、前記第1の膜上に、金属酸化物からなるアモルファス、微結晶のいずれかの第2の膜を形成する工程と、前記第2の膜を熱処理する工程と、前記第2の膜を熱処理した後に、第2の膜を還元する工程と、前記第2の膜上に強誘電体からなる第3の膜を形成する工程と、前記第3の膜上に第2の金属からなる第4の膜を形成する工程と、有することを特徴とする半導体装置の製造方法。

(付記2)付記1に記載の半導体装置の製造方法において、前記第2の膜の加熱処理は大気圧下で行うことを特徴とする半導体装置の製造方法。

(付記3)付記1又は付記2に記載の半導体装置の製造方法において、前記第2の膜の前記熱処理は、急速熱アニールであることを特徴とする半導体装置の製造方法。

(付記4)付記1乃至付記3のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜の前記熱処理は、酸素を含む雰囲気で行われることを特徴とする半導体装置の製造方法。

(付記5)付記1乃至付記4のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜の厚さは、10nm乃至40nmであることを特徴とする半導体装置の製造方法。

(付記6)付記1乃至付記5のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜は、10℃乃至100℃の温度下で形成されることを特徴とする半導体装置の製造方法。

(付記7)付記1乃至付記6のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜は、前記第3の原料ガスに含まれる溶媒成分により還元されることを特徴とする半導体装置の製造方法。

(付記8)付記1乃至付記7のいずれか1つに記載の半導体装置の製造方法において、前記金属酸化物は、前記第1の金属の酸化物であることを特徴とする半導体装置の製造方法。

(付記9)付記1乃至付記8のいずれか1つに記載の半導体装置の製造方法において、前記第1の金属は、イリジウム、ルテニウム、ロジウム及びパラジウムのうちのいずれかであることを特徴とする半導体装置の製造方法。

(付記10) 付記1乃至付記9に記載の半導体装置の製造方法において、前記第2の膜を熱処理する雰囲気内の酸素の含有量は0.1流量%以上100流量%以下であることを特徴とする半導体装置の製造方法。

(付記11)付記1乃至付記10のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜の熱処理温度は600℃以上、750℃以下であることを特徴とする半導体装置の製造方法。

(付記12)付記1乃至付記11のいずれか1つに記載の半導体装置の製造方法において、前記第2の膜の熱処理は前記大気圧以下で1Pa以上であることを特徴とする半導体装置の製造方法。

(付記13)付記1乃至付記12のいずれか1つに記載の半導体装置の製造方法において、前記第1の膜の形成後であって前記第2の膜を形成する前に、不活性ガス雰囲気で前記第1の膜を熱処理することを特徴とする半導体装置の製造方法。

(付記14)付記13に記載の半導体装置の製造方法において、前記第1の膜を600℃以上、且つ750℃以下の温度で熱処理することを特徴とする半導体装置の製造方法。

(付記15)付記1乃至付記14のいずれか1つに記載の半導体装置の製造方法において、前記第3の膜の初期層を気相成長する期間に前記第2の膜を還元することを特徴とする半導体装置の製造方法。

(付記16)付記15に記載の半導体装置の製造方法において、前記強誘電体膜の形成は、前記初期層上に成膜レート及び膜厚が前記初期層に比べて高いコア層をCVD法により形成する工程を含むことを特徴とする半導体装置の製造方法。

(付記17)付記15又は付記16に記載の半導体装置の製造方法において、前記初期層は、2.5nm〜10nmの膜厚に形成することを特徴とする半導体装置の製造方法。

(付記18)付記1乃至付記17のいずれか1つに記載の半導体装置の製造方法において、前記強誘電体膜は、前記第2の膜の結晶配向と同じ結晶配向の膜を形成する工程であることを特徴とする半導体装置の製造方法。

(付記19)付記1乃至付記18のいずれか1つに記載の半導体装置の製造方法において、前記強誘電体膜は、形成雰囲気中に導入する酸素ガスの比率を変化させながら形成されることを特徴とする半導体装置の製造方法。

(付記20)付記1乃至付記18のいずれか1つに記載の半導体装置の製造方法において、前記第3の膜は、ペロブスカイト構造又はビスマス層状構造を有する強誘電体材料からなる膜であることを特徴とする半導体装置の製造方法。

【図面の簡単な説明】

【0136】

【図1A】図1Aは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その1)である。

【図1B】図1Bは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その2)である。

【図1C】図1Cは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その3)である。

【図1D】図1Dは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その4)である。

【図1E】図1Eは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その5)である。

【図1F】図1Fは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その6)である。

【図1G】図1Gは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その7)である。

【図1H】図1Hは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その8)である。

【図1I】図1Iは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その9)である。

【図1J】図1Jは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その10)である。

【図1K】図1Kは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その11)である。

【図1L】図1Lは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その12)である。

【図1M】図1Mは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その13)である。

【図1N】図1Nは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その14)である。

【図1O】図1Mは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その15)である。

【図1P】図1Nは、本発明の第1実施の形態に係る半導体装置の製造工程を示す断面図(その16)である。

【図2】図2は、ArとO2の流量制御を示すタイミングチャートである。

【図3】図3は、酸化導電膜を還元した後にX線回折を行った図である。

【図4A】図4Aは、酸化導電膜のX線回折結果を示す図である。

【図4B】図4Bは、熱処理前と熱処理後の酸化導電膜のX線回折結果を示す図である。

【図5A】図5Aは、酸化導電膜の成膜温度が第1強誘電体膜の(100)面の結晶性に与える影響を調べたグラフである。

【図5B】図5Bは、酸化導電膜の成膜温度が第1強誘電体膜の(111)面の結晶性に与える影響を調べたグラフである。

【図6A】図6Aは、下部電極膜及び酸化導電膜の熱処理条件がPZTの(100)面の結晶性に与える影響についてX線回折を用いて調査した結果を示すグラフである。

【図6B】図6Bは、下部電極膜及び酸化導電膜の熱処理条件がPZTの(101)面の結晶性に与える影響についてX線回折を用いて調査した結果を示すグラフである。

【図6C】図6Cは、下部電極膜及び酸化導電膜の熱処理条件がPZTの(111)面の結晶性に与える影響についてX線回折を用いて調査した結果を示すグラフである。

【図6D】図6Dは、下部電極膜及び酸化導電膜の熱処理条件がPZTの(222)面の配向率に与える影響についてX線回折を用いて調査した結果を示すグラフである。

【図6E】図6Eは、下部電極膜及び酸化導電膜の熱処理条件によるPZTの(111)面のX線回折ピークの半値幅の変化を調べたグラフである。

【図6F】図6Fは、下部電極膜及び酸化導電膜の熱処理条件によるPZTの表面の突起数の変化を調べたグラフである。

【図7A】図7Aは、本実施の形態で形成したPZTの表面のSEM像を示す図である。

【図7B】図7Bは、比較例としてレファレンス方法で形成したPZTの表面のSEM像を示す図である。

【図8】図8は、本実施の形態とレファレンス方法とをそれぞれ複数回実施して計測したPZTの表面の突起数を示すグラフである。

【図9A】図9Aは、本実施の形態とレファレンス方法とをそれぞれ複数回実施してPZT膜の結晶方位を比較したグラフである。

【図9B】図9Bは、本実施の形態とレファレンス方法とをそれぞれ複数回実施してPZT膜の結晶方位を比較したグラフである。

【図9C】図9Cは、本実施の形態とレファレンス方法とをそれぞれ複数回実施してPZT膜の(222)面の配向率を比較したグラフである。

【図10】図10は、第2実施の形態に係る半導体装置の製造工程を説明する断面図である。

【図11】図11は、第2実施の形態の変形例に係る半導体装置の製造工程を説明する断面図である。

【図12】図12は、第2実施の形態の変形例に係る半導体装置の製造工程を説明する断面図である。

【図13A】図13Aは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その1)である。

【図13B】図13Bは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その2)である。

【図13C】図13Cは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その3)である。

【図13D】図13Dは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その4)である。

【図13E】図13Eは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その5)である。

【図13F】図13Fは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その6)である。

【図13G】図13Gは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その7)である。

【図13H】図13Hは、本発明の第3の実施の形態に係る半導体装置の製造工程を示す断面図(その8)である。

【符号の説明】

【0137】

1 シリコン基板

25 下部電極膜(第1の膜)

26 酸化導電膜(第2の膜)

26A 第2の導電膜

27 第1強誘電体膜(第3の膜)

27A 初期層

27B コア層

29 上部電極膜(第4の膜)

37 強誘電体キャパシタ

【特許請求の範囲】

【請求項1】

基板の上方に第1の金属からなる第1の膜を形成する工程と、

前記第1の膜上に、金属酸化物からなるアモルファス、微結晶のいずれかの第2の膜を形成する工程と、

前記第2の膜を熱処理する工程と、

前記第2の膜を熱処理した後に、第2の膜を還元する工程と、

前記第2の膜上に強誘電体からなる第3の膜を形成する工程と、

前記第3の膜上に第2の金属からなる第4の膜を形成する工程と、

有することを特徴とする半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法において、

前記第2の膜の加熱処理は大気圧下で行うことを特徴とする半導体装置の製造方法。

【請求項3】

請求項1又は請求項2に記載の半導体装置の製造方法において、

前記第2の膜の前記熱処理は、急速熱アニールであることを特徴とする半導体装置の製造方法。

【請求項4】

請求項1乃至請求項3のいずれか1項に記載の半導体装置の製造方法において、

前記第2の膜の前記熱処理は、酸素を含む雰囲気で行われることを特徴とする半導体装置の製造方法。

【請求項5】

請求項1乃至請求項4のいずれか1項に記載の半導体装置の製造方法において、

前記第2の膜の厚さは、10nm乃至40nmであることを特徴とする半導体装置の製造方法。

【請求項6】

請求項1乃至請求項5のいずれか1項に記載の半導体装置の製造方法において、

前記第2の膜は、10℃乃至100℃の温度下で形成されることを特徴とする半導体装置の製造方法。

【請求項7】

請求項1乃至請求項6のいずれか1項に記載の半導体装置の製造方法において、

前記第2の膜は、前記第3の原料ガスに含まれる溶媒成分により還元されることを特徴とする半導体装置の製造方法。

【請求項8】

請求項1乃至請求項7のいずれか1項に記載の半導体装置の製造方法において、

前記金属酸化物は、前記第1の金属の酸化物であることを特徴とする半導体装置の製造方法。

【請求項9】

請求項1乃至請求項8のいずれか1項に記載の半導体装置の製造方法において、

前記第1の金属は、イリジウム、ルテニウム、ロジウム及びパラジウムのうちのいずれかであることを特徴とする半導体装置の製造方法。

【請求項1】

基板の上方に第1の金属からなる第1の膜を形成する工程と、

前記第1の膜上に、金属酸化物からなるアモルファス、微結晶のいずれかの第2の膜を形成する工程と、

前記第2の膜を熱処理する工程と、

前記第2の膜を熱処理した後に、第2の膜を還元する工程と、

前記第2の膜上に強誘電体からなる第3の膜を形成する工程と、

前記第3の膜上に第2の金属からなる第4の膜を形成する工程と、

有することを特徴とする半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法において、

前記第2の膜の加熱処理は大気圧下で行うことを特徴とする半導体装置の製造方法。

【請求項3】

請求項1又は請求項2に記載の半導体装置の製造方法において、

前記第2の膜の前記熱処理は、急速熱アニールであることを特徴とする半導体装置の製造方法。

【請求項4】

請求項1乃至請求項3のいずれか1項に記載の半導体装置の製造方法において、

前記第2の膜の前記熱処理は、酸素を含む雰囲気で行われることを特徴とする半導体装置の製造方法。

【請求項5】

請求項1乃至請求項4のいずれか1項に記載の半導体装置の製造方法において、

前記第2の膜の厚さは、10nm乃至40nmであることを特徴とする半導体装置の製造方法。

【請求項6】

請求項1乃至請求項5のいずれか1項に記載の半導体装置の製造方法において、

前記第2の膜は、10℃乃至100℃の温度下で形成されることを特徴とする半導体装置の製造方法。

【請求項7】

請求項1乃至請求項6のいずれか1項に記載の半導体装置の製造方法において、