半導体装置の製造方法

【課題】Alを含む金属配線の形成において、サイドエッチ量を低減した微細な金属配線を形成でき、金属配線上に形成するビアホールが金属膜を突き抜けるのを抑制することができる半導体装置の製造方法を提供する。

【解決手段】基板上に第一TiN膜3、Alを含む金属膜4、第二TiN膜5を順次積層した金属配線層6を形成する工程と、前記金属配線層6の上にストッパー膜7、シリコン酸化膜8を順次積層したハードマスク層12を形成する工程と、前記ハードマスク層12を選択的にエッチングして前記金属配線層6の上にハードマスク12aを形成する工程と、前記ハードマスク12aをマスクとしてエッチングし金属配線6aを形成する工程と、前記ハードマスク12aおよび前記金属配線6aの上に層間絶縁膜14を形成する工程と、前記ストッパー膜7をエッチングストッパとして前記層間絶縁膜14にビアホール17aを形成する工程とを含む。

【解決手段】基板上に第一TiN膜3、Alを含む金属膜4、第二TiN膜5を順次積層した金属配線層6を形成する工程と、前記金属配線層6の上にストッパー膜7、シリコン酸化膜8を順次積層したハードマスク層12を形成する工程と、前記ハードマスク層12を選択的にエッチングして前記金属配線層6の上にハードマスク12aを形成する工程と、前記ハードマスク12aをマスクとしてエッチングし金属配線6aを形成する工程と、前記ハードマスク12aおよび前記金属配線6aの上に層間絶縁膜14を形成する工程と、前記ストッパー膜7をエッチングストッパとして前記層間絶縁膜14にビアホール17aを形成する工程とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置の製造方法に関し、特にアルミニウムを含む金属配線の形成方法に関する。

【背景技術】

【0002】

半導体装置の金属配線として、AlCu膜、AlSi膜、AlSiCu膜などのアルミニウムを含む金属配線が広く用いられている。また配線の信頼性を高めるため、これらの金属配線の上層および下層にTi膜やTiN膜を積層した構造も多く採用されている。

【0003】

これらの金属配線を形成する場合、アルミニウムを含む金属膜の上にレジストパターンを形成して、これをマスクとして塩素、炭素、不活性ガス、窒素のいずれか又は全てを含むガスを用いてエッチングしていた。

【0004】

しかし、近年のデザインルールの縮小化に伴いレジストパターンの膜厚を薄膜化せざるを得ないため、耐エッチング性は低くなる。このため、シリコン酸化膜やシリコン窒化膜等の無機絶縁膜をハードマスクとしてエッチングするハードマスクプロセスが用いられるようになってきた(例えば、特許文献1、2参照)。

【0005】

ハードマスクプロセスにおいては、サイドエッチ量を低減するための側壁保護効果を得るため、N2、CHF3などの添加ガスを用いていた。しかし、これらの添加ガスを用いると歩留まり低下の原因となるAlNXやAlFXなどが反応副生成物として発生する。これを避けるため、添加ガスとしてC2H4を用いるようにしていた(例えば、特許文献3参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2001−210468号公報

【特許文献2】特開2000−58507号公報

【特許文献3】特開2001−53059号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上記従来の半導体装置の製造方法において、アルミニウムを含む金属膜の上にハードマスクとなる無機絶縁膜を形成し、その上に直接レジストパターンを形成する方法では、配線ピッチが小さくなるとレジストパターンの寸法精度を満たすことが困難になるという問題があった。

【0008】

また、シリコン窒化膜のみをハードマスクとして形成して上記金属膜をエッチングする方法では、シリコン窒化膜が塩素ガスによりエッチングされやすい膜であるため、ハードマスクに適さないという問題があった。

【0009】

一方、シリコン酸化膜のみをハードマスクとして形成して上記金属膜をエッチングする方法では、後に金属配線上にビアホールを形成する工程において、ハードマスクがエッチングストッパー膜とならないため、ビアホールが金属膜を突き抜けてしまい、配線の歩留まりを低下させるという問題があった。

【0010】

また、配線ピッチが小さくなると、上記従来の技術ではサイドエッチ量を十分に低減できないという問題があった。

【0011】

本発明は上記課題を解決するためになされたもので、アルミニウムを含む金属配線の形成において、サイドエッチ量を低減した微細な金属配線を形成でき、この金属配線の上に形成するビアホールが金属膜を突き抜けるのを抑制することができ、優れた半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明に係る半導体装置の製造方法は、基板上に下層から第一TiN膜、アルミニウムを含む金属膜、第二TiN膜を順次積層した金属配線層を形成する工程と、前記金属配線層の上に下層からストッパー膜、シリコン酸化膜を順次積層したハードマスク層を形成する工程と、前記ハードマスク層を選択的にエッチングして前記金属配線層の上にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記金属配線層をエッチングして金属配線を形成する工程と、前記ハードマスクおよび前記金属配線の上に層間絶縁膜を形成する工程と、前記ストッパー膜をエッチングストッパとして前記層間絶縁膜にビアホールを形成する工程とを含むことを特徴とする。

【0013】

本発明のその他の特徴については、以下において詳細に説明する。

【発明の効果】

【0014】

本発明によれば、アルミニウムを含む金属膜の上に形成するハードマスクの積層構造を最適化することにより、サイドエッチ量を低減した微細な金属配線を形成でき、この金属配線の上に形成するビアホールが金属膜を突き抜けるのを抑制することができ、優れた半導体装置の製造方法を得ることができる。

【図面の簡単な説明】

【0015】

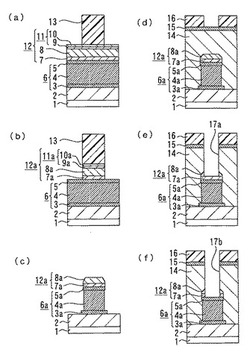

【図1】本発明の実施の形態1〜3に係る半導体装置の製造方法を示す断面図。

【図2】ハードマスクと金属配線の界面のノッチ量を説明する図。

【図3】本発明の実施の形態3に係る半導体装置の製造方法による効果を示す図。

【発明を実施するための形態】

【0016】

以下、本発明の実施の形態について図面を参照しながら説明する。同様の構成要素には同じ番号を付し、説明を省略する。

【0017】

以下、図面を参照しながら本発明の実施の形態について説明する。なお、各図において同一または相当する部分には同一符号を付して、その説明を簡略化ないし省略する。

【0018】

実施の形態1.

図1(a)〜(f)は、本実施の形態に係る半導体装置の製造方法を示す工程断面図である。

【0019】

まず、図1(a)に示すように、シリコン基板1の上にトランジスタなどの素子(図示しない)を形成した後、全面に層間絶縁膜2を形成する。例えば、化学気相成長(Chemical Vapor Deposition;以下、「CVD」という)法などにより、300〜400nm程度の膜厚で形成する。

【0020】

次に、層間絶縁膜2の上に、下層TiN膜3、AlCu膜4、上層TiN膜5を順次積層した金属配線層6を形成する。下層TiN膜3および上層TiN膜5は、スパッタ法などによりそれぞれ100nm程度の膜厚で形成する。AlCu膜4はアルミニウム膜に数%程度の銅を含むアルミニウム合金膜であり、スパッタ法などにより500nm程度の膜厚で形成する。

【0021】

このようにして、シリコン基板1の上にアルミニウムを含む金属配線層6を形成する。

【0022】

なお、上記の例では金属配線層6として下層からTiN膜3、AlCu膜4、TiN膜5を順次積層した積層膜を形成する例を示したが、これに置き換えて、下層からTi膜、TiN膜、AlCu膜、Ti膜、TiN膜を順次積層した積層膜を形成するようにしても良い。

【0023】

次に、金属配線層6の上に、ストッパー膜7およびシリコン酸化膜8を順次積層する。例えば、ストッパー膜7として、プラズマCVD法により50nm程度の膜厚でシリコン酸窒化膜(SiON膜)を形成する。そして、シリコン酸化膜8をプラズマCVD法により100〜200nm程度の膜厚で形成する。

【0024】

このとき、上記のシリコン酸窒化膜は窒素含有率を12%以上とする。また、シリコン酸窒化膜に置き換えて、プラズマCVD法により50nm程度の膜厚でシリコン窒化膜(SiN膜)を形成するようにしても良い。

【0025】

なお、シリコン酸化膜8は窒素(含有率11%以下)を含むようにしても良い。また、シリコン酸化膜8は後の工程で金属配線層6をエッチングするときのハードマスクとなるため、十分に厚い膜厚とする。

【0026】

次に、シリコン酸化膜8の上に二層のシリコン酸窒化膜、すなわち下層シリコン酸窒化膜9および上層シリコン酸窒化膜10を連続して形成する。例えば、プラズマCVD法により、それぞれ50nm程度の膜厚で形成する(以下、この二層のシリコン酸窒化膜を全体として「反射防止膜11」という。そして、ストッパー膜7、シリコン酸化膜8、反射防止膜11を全体として「ハードマスク層12」という)。

【0027】

このようにして、金属配線層6の上に、下層からストッパー膜7、シリコン酸化膜8、反射防止膜11を順次積層したハードマスク層12を形成する。

【0028】

前述したように、ハードマスク層12に含まれるストッパー膜7として、シリコン酸窒化膜又はシリコン窒化膜を用いるようにした。これにより、最終的に形成される金属配線の上にビアホールを形成するとき、ビアホールが金属配線を突き抜けるのを抑制することができる。

【0029】

また、ハードマスク層12に含まれる反射防止膜11として、二層のシリコン酸窒化膜を用いるようにしたので、後に反射防止膜11の上にレジストパターンを形成する工程において、下地膜からの反射を抑えて、微細なレジストパターンを制御性良く形成することができる。

【0030】

さらに、後の工程でハードマスクをマスクとして金属配線層6をエッチングすると、このハードマスクは上部の幅が狭くなった順テーパー形状となる。このような形状とすることにより、隣接する金属配線間に高密度プラズマCVDを用いたシリコン酸化膜を形成する場合には、埋め込み性を向上させることができる。

【0031】

また、ハードマスク層12に含まれる反射防止膜11として、有機膜を用いるようにしても良い。これにより、二層のシリコン酸窒化膜を用いた場合と比較して、下地膜からの反射をさらに効果的に抑制することができ、微細なレジストパターンをさらに制御性良く形成することができる。

【0032】

次に、ハードマスク層12の上に、リソグラフィによりレジストパターン13を形成する。このとき、レジストパターン13の下に反射防止膜11が形成されているので、微細なレジストパターン13を制御性良く形成することができる。

【0033】

次に、レジストパターン13をマスクとして図1(a)に示したハードマスク層12を選択的にエッチングして、図1(b)に示すように、金属配線層6の上にハードマスク12aを形成する。

【0034】

ここでは炭素および弗素を含むガス、酸素を含むガス、不活性ガスのうち少なくとも二つ以上のガスを含む混合ガス(例えば、CHF3/CF4/O2/Ar系混合ガス)を用いてエッチングを行う。

【0035】

さらに図示しないが、レジストパターン13をアッシングにより除去し、有機アミン系や有機リン酸系を中心とする剥離液によりポリマーなどのエッチング残渣を除去する。

【0036】

次に、図1(b)に示したハードマスク12aをマスクとして金属配線層6をエッチングして、図1(c)に示すように、金属配線6aを形成する。

【0037】

例えば、Cl2、BCl3、HCl、HIなどのハロゲン元素を含むガスに、Ar、Heなどの不活性ガス、CHF3、CH4、C2H4などのC(炭素)を含むデポジションガスを添加した混合ガスを用いてエッチングする。

【0038】

上記のデポジションガスを添加することにより、金属配線6aのサイドエッチ(配線の幅が細くなってしまうこと)量を低減することができる。

【0039】

また、上記デポジションガスの代わりに、CO、CO2、シクロアルカン(シクロブタン等)、シクロアルケン(シクロペンテン等)、1,3ブタジエン、ベンゼンなどの共役二重結合を有するものを含むデポジションガスを用いても良い。これにより、サイドエッチ量をさらに効果的に低減することができる。

【0040】

このとき反射防止膜11a(図1(b)参照)は、金属配線層6をエッチングする際に同時にエッチングされ、ハードマスク12aは、上部の幅が狭くなった順テーパー形状となる。

【0041】

また、ハードマスク12aはストッパー膜7aの上にシリコン酸化膜8aを積層した構造であるので、シリコン酸窒化膜(またはシリコン窒化膜)のみをハードマスクとしてエッチングした場合よりも耐エッチング性が優れ、サイドエッチ量を低減して金属配線6aを制御性良く形成することができる。

【0042】

次に、図1(d)に示すように、金属配線6aおよびハードマスク12aの上に、全面に層間絶縁膜14を形成する。例えば、高密度プラズマCVD法により、シリコン酸化膜を1000nm程度の膜厚で形成する。

【0043】

このとき、前述したようにハードマスク12aは、上部の幅が狭くなった順テーパー形状であるので、金属配線6aの配線ピッチが小さくなった場合でも、間口を大きくすることができ、隣接する金属配線6aの間を良好に埋め込むことができる。

【0044】

さらに、図示しないが、層間絶縁膜14の上にプラズマCVD法などによりシリコン酸化膜を300〜400nm程度の膜厚で形成する。そして、その表面を化学機械研磨(Chemical Mechanical Polishing;以下、「CMP」という)により研磨して、平坦化する。

【0045】

次に、平坦化されたシリコン酸化膜の上に、有機膜などからなる反射防止膜15を形成する。そして、反射防止膜15の上にリソグラフィによりレジストパターン16を形成する。

【0046】

次に、図1(d)に示したレジストパターン16をマスクとして反射防止膜15、層間絶縁膜14をエッチングして、図1(e)に示すように、金属配線6aの上にビアホール17aを形成して、ストッパー膜7aを露出させる。

【0047】

例えば、反射防止膜15をエッチングした後に、炭素および弗素を含むガス、酸素を含むガス、不活性ガスのうち少なくとも二つ以上のガスを含む混合ガス(例えば、C4F8/O2/Ar系混合ガス、又はC5F8/O2/Ar系混合ガス)を用いて層間絶縁膜14を選択的にエッチングする。

【0048】

次に、図1(e)に示したビアホール17aの底面に露出したストッパー膜7aをCHF3/O2/Ar系混合ガスを用いて選択的にエッチングして、図1(f)に示すように、ビアホール17bの底面に上層TiN膜5aを露出させる。

【0049】

このとき、前述したようにハードマスク層12(図1(a)参照)に含まれるストッパー膜7としてシリコン酸窒化膜又はシリコン窒化膜を用いるようにした。これにより、層間絶縁膜14の膜厚ばらつき、CMPによる削れ量のばらつきを吸収してビアホール17bが金属配線6aを突き抜けるのを抑制することができる。

【0050】

なお、ストッパー膜7aを選択的にエッチングする前に、上記のCHF3/O2/Ar系混合ガスを用いて、Arに対するCHF3/O2の流量比を上記ストッパー膜7aのエッチング条件よりも相対的に大きくして、図1(e)に示したビアホール17aの内面に付着したデポジション膜を除去するエッチングステップを入れるようにしても良い。これにより、ビアホール17bの底面に上層TiN膜5aを良好に露出させることができる。

【0051】

この後、図示しないが、図1(f)に示したビアホール17bの内面にTi膜、TiN膜の積層膜を形成する。さらに、この積層膜により形成された溝をタングステンなどの金属膜で埋め込み、溝の外部に形成したTi膜、TiN膜、金属膜をCMPなどにより除去して、ビアホール17bに金属膜を埋め込んだビアを形成する。

【0052】

以上説明したように、本実施の形態に係る半導体装置の製造方法は、まず、シリコン基板1の上にアルミニウムを含む金属配線層6を形成して、その上に、下層からストッパー膜7、シリコン酸化膜8、反射防止膜11を順次積層したハードマスク層12を形成するようにした。

【0053】

次にハードマスク層12を選択的にエッチングして金属配線層6の上にハードマスク12aを形成するようにした。

【0054】

そして、ハードマスク12aをマスクとして金属配線層6をエッチングして金属配線6aを形成するようにした。

【0055】

このように形成することにより、金属配線層6をエッチングして金属配線6aを形成するとき、シリコン酸窒化膜(またはシリコン窒化膜)のみをハードマスクとしてエッチングした場合よりも耐エッチング性が優れ、サイドエッチ量を低減して金属配線6aを制御性良く形成することができる。また、隣接する金属配線6aの間の埋め込み性を向上させ、これらの金属配線間の配線間容量や金属配線6aの上に形成するビア抵抗のばらつきを小さくすることができる。

【0056】

また、この配線の上に形成するビアホール17bが金属配線6aに突き抜けるのを抑制して、ビアホール形成の歩留まり低下を抑制することができる。

【0057】

実施の形態2.

本実施の形態に係る半導体装置の製造方法は、実施の形態1で示したハードマスク層12(図1(a)参照)に含まれるストッパー膜7として、金属膜を用いるようにしたものである。

【0058】

その他の構成については実施の形態1と同様であるので、図1(a)〜(f)を適宜参照して、実施の形態1と異なる点を中心に説明する。

【0059】

まず、シリコン基板1の上にトランジスタなどの素子(図示しない)を形成した後、全面に層間絶縁膜2を形成する工程から、アルミニウムを含む金属配線層6を形成するまでの工程(図1(a)参照)を、実施の形態1と同様にして行う。

【0060】

その後、金属配線層6の上にハードマスク層12を形成する。このとき、ハードマスク層12に含まれるストッパー膜7として、タングステン、タンタル、白金、銀、金、ニッケル、ルテニウム、コバルト、鉄、マンガン、イリジウム、ジルコニウム、インジウムのうち、いずれかの金属からなる金属膜を用いる。ここでは、タングステン膜を用いる。

【0061】

この後、ストッパー膜7の上にシリコン酸化膜8を形成する工程(図1(a)参照)から、反射防止膜15の上にレジストパターン16を形成するまでの工程(図1(d)参照)を、実施の形態1と同様にして行う。

【0062】

次に、図1(d)に示したレジストパターン16をマスクとして反射防止膜15、層間絶縁膜14をエッチングして、図1(e)に示すように、金属配線6aの上にビアホール17aを形成して、ストッパー膜7a(タングステン膜)を露出させる。

【0063】

このとき、ストッパー膜7aの被エッチング速度に対する層間絶縁膜14(シリコン酸化膜)の被エッチング速度を「エッチング選択比」と定義すると、タングステン膜をストッパー膜として用いた場合のエッチング選択比は、シリコン酸窒化膜(又はシリコン窒化膜)をストッパー膜として用いた場合のエッチング選択比より大きい。

【0064】

従って、金属配線6aの上にビアホール17aを形成するとき、ビアホール17aが金属配線6aに突き抜けるのを実施の形態1よりも効果的に抑制することができる。

【0065】

また、タングステン膜は金属膜であり、ビアホール17aの底面にストッパー膜7aを露出させた状態でビアホール17aの内部に金属膜を埋め込んでビアを形成しても導通性を失うことがないので、ストッパー膜7aを除去する工程を省略することができる。さらに、タングステン膜を金属配線6aの上に積層したので、金属配線6aの抵抗を低くすることができる。

【0066】

なお、前述したタングステン膜以外の金属膜をストッパー膜として用いた場合にも同様の効果を有する。

【0067】

なお、この後、実施の形態1と同様にストッパー膜7aをエッチングにより除去する(図1(f)参照)ようにしても良い。

【0068】

その他の構成については、実施の形態1と同様であるので、説明を省略する。

【0069】

以上説明したように、本実施の形態に係る半導体装置の製造方法は、実施の形態1で示したハードマスク層12に含まれるストッパー膜7として、タングステン、タンタル、白金、銀、金、ニッケル、ルテニウム、コバルト、鉄、マンガン、イリジウム、ジルコニウム、インジウムのうち、いずれかの金属からなる金属膜を用いるようにした。

【0070】

このように形成することにより、金属配線6aの上にビアホール17aを形成するとき、金属配線6aに突き抜けるのを実施の形態1よりも効果的に抑制することができる。

【0071】

また、ビアホール17aの底面にストッパー膜7aを露出させた状態で、ビアホール17aの内部に金属膜を埋め込んでビアを形成しても導通性を失うことがないので、ストッパー膜7aを除去する工程を省略することができる。さらに、タングステン膜を金属配線6aに積層したことにより、金属配線6aの抵抗を低くすることができる。

【0072】

実施の形態3.

本実施の形態に係る半導体装置の製造方法は、実施の形態1で示したシリコン酸化膜8を形成する工程(図1(a)参照)において、シリコンに対する酸素の組成比を特定範囲とし、形成温度を特定範囲として形成するようにしたものである。

【0073】

また、金属配線層6をエッチングして金属配線6aを形成する工程(図1(c)参照)を、別のシリコン基板上に形成した特定の膜のうち、いずれかの膜を予めエッチングしたエッチング装置を用いて行うようにしたものである。

【0074】

その他の構成については実施の形態1、2と同様であるので、図1(a)〜(f)を適宜参照して、実施の形態1、2と異なる点を中心に説明する。

【0075】

まず、シリコン基板1の上にトランジスタなどの素子(図示しない)を形成した後、全面に層間絶縁膜2を形成する工程から、金属配線層6の上にストッパー膜7を形成するまでの工程(図1(a)参照)を、実施の形態1(又は実施の形態2)と同様にして行う。

【0076】

その後、実施の形態1で示したハードマスク層12に含まれるシリコン酸化膜8を、シリコンに対する酸素の組成比が1.5〜2の範囲となるようにプラズマCVD法を用いて形成する。

【0077】

このように形成することにより、実施の形態1で示した金属配線層6をエッチングして金属配線6aを形成する工程(図1(c)参照)において、上層TiN膜5aがシリコン酸化膜8aと反応するのを抑え、ハードマスク12aと金属配線6aとの界面に発生するノッチ量を低減することができる。

【0078】

また、ハードマスク層12に含まれるシリコン酸化膜8を、290〜400℃の範囲の温度でプラズマCVD法を用いて形成するようにしても良い。

【0079】

このように形成することにより、上記と同様に、ハードマスク12aと金属配線6aとの界面に発生するノッチ量を低減することができる。

【0080】

この後、シリコン酸化膜8の上に反射防止膜11を形成する工程と、ハードマスク層12の上にレジストパターン13を形成する工程(図1(a)参照)を、実施の形態1と同様にして行う。

【0081】

次に、金属配線層6をエッチングする工程(図1(c)参照)を、シリコン基板1とは異なる別のシリコン基板上に形成したシリコン酸化膜、シリコン窒化膜、又は金属配線層6(図1(b)参照)に含まれる金属膜と同一種類の金属膜のうち、いずれかの膜をエッチングしたエッチング装置を用いて行うようにする。

【0082】

例えば、金属配線層6をエッチングする前に、金属配線層6を形成したシリコン基板1とは別のシリコン基板の上に形成したシリコン酸化膜、シリコン窒化膜、又は金属配線層6に含まれるTiN膜、AlCu膜などの金属膜のうち、いずれかの膜をエッチングする(以下、この処理を「シーズニング処理」という)。そして、シーズニング処理をしたエッチング装置を用いて金属配線層6をエッチングする。

【0083】

このように金属配線層6のエッチングを行うことにより、シーズニング処理においてエッチングした膜から供給される微量の酸素、窒素、金属を含有した反応生成物がエッチング装置内に残留して、金属配線層6のエッチング中に金属配線6aの側壁を保護するため、図2に示すハードマスク12aと金属配線6aの界面のノッチ量Aを低減することができる。

【0084】

これにより、ハードマスク12aと金属配線6aの界面のノッチ量Aを、さらに低減することができる。

【0085】

図3(a)は、金属配線層6をエッチングする前にシーズニング処理を行わなかった場合の、シリコン酸化膜8のシリコン(Si)に対する酸素(O)の組成比とノッチ量Aとの関係、およびシリコン酸化膜8の形成温度とノッチ量Aとの関係を示すデータである。

【0086】

これらのデータから、シリコン酸化膜8のシリコンに対する酸素の組成比を1.5〜2の範囲とすることにより、ノッチ量Aを低減する効果があることが分かる。また、形成温度を290〜400℃の範囲とすることにより、ノッチ量Aをさらに低減する効果があることが分かる。

【0087】

図3(b)は、金属配線層6をエッチングする前にシーズニング処理を行った場合、シリコン酸化膜8のシリコンに対する酸素の組成比を1.7、シリコン酸化膜8の生成温度を420℃とした場合のノッチ量Aを示すデータである。図3(a)との比較から、シーズニング処理を行うことにより、ノッチ量Aを低減する効果がさらに大きくなることが分かる。

【0088】

これらの結果から、本実施の形態の製造方法によりハードマスク12aと金属配線6aの界面のノッチ量を低減する効果があることが分かる。

【0089】

これにより、隣接する金属配線6aの間の埋め込み性が向上し、これらの金属配線の配線間容量ばらつきを小さくすることができる。また、金属配線6aの上層TiN膜5aの膜減りを防ぐことができ、金属配線6aの上に形成するビアの抵抗ばらつきを小さくすることができる。

【0090】

その他の構成については、実施の形態1(又は実施の形態2)と同様であるので、説明を省略する。

【0091】

以上説明したように、本実施の形態に係る半導体装置の製造方法は、実施の形態1(又は実施の形態2)で示したハードマスク層12に含まれるシリコン酸化膜8を、シリコンに対する酸素の組成比が1.5〜2の範囲となるようにプラズマCVD法を用いて形成するようにした。

【0092】

また、ハードマスク層12に含まれるシリコン酸化膜8を、290〜400℃の範囲の温度でプラズマCVD法を用いて形成するようにした。

【0093】

さらに、実施の形態1(又は実施の形態2)で示したハードマスク12aをマスクとして金属配線層6をエッチングして金属配線6aを形成する工程を、シリコン基板1とは異なる別のシリコン基板上に形成したシリコン酸化膜、シリコン窒化膜、又は金属配線層6に含まれる金属膜と同一種類の金属膜のうち、いずれかの膜をエッチングしたエッチング装置を用いて行うようにした。

【0094】

このように形成することにより、実施の形態1、2の効果に加えて、ハードマスク12aと金属配線6aの界面のノッチ量を低減することができる。

【0095】

これにより、隣接する金属配線6aの間の埋め込み性が向上し、これらの金属配線の配線間容量ばらつきを小さくすることができる。また、金属配線6aの上層TiN膜5aの膜減りを防ぐことができ、金属配線6aの上に形成するビアの抵抗ばらつきを小さくすることができる。

【符号の説明】

【0096】

1 シリコン基板、2 層間絶縁膜、3 下層TiN膜、4 AlCu膜、5 上層TiN膜、6 金属配線層、6a 金属配線、7a ストッパー膜、8 シリコン酸化膜、11 反射防止膜、12 ハードマスク層、12a ハードマスク、14 層間絶縁膜、17a、17b ビアホール。

【技術分野】

【0001】

本発明は半導体装置の製造方法に関し、特にアルミニウムを含む金属配線の形成方法に関する。

【背景技術】

【0002】

半導体装置の金属配線として、AlCu膜、AlSi膜、AlSiCu膜などのアルミニウムを含む金属配線が広く用いられている。また配線の信頼性を高めるため、これらの金属配線の上層および下層にTi膜やTiN膜を積層した構造も多く採用されている。

【0003】

これらの金属配線を形成する場合、アルミニウムを含む金属膜の上にレジストパターンを形成して、これをマスクとして塩素、炭素、不活性ガス、窒素のいずれか又は全てを含むガスを用いてエッチングしていた。

【0004】

しかし、近年のデザインルールの縮小化に伴いレジストパターンの膜厚を薄膜化せざるを得ないため、耐エッチング性は低くなる。このため、シリコン酸化膜やシリコン窒化膜等の無機絶縁膜をハードマスクとしてエッチングするハードマスクプロセスが用いられるようになってきた(例えば、特許文献1、2参照)。

【0005】

ハードマスクプロセスにおいては、サイドエッチ量を低減するための側壁保護効果を得るため、N2、CHF3などの添加ガスを用いていた。しかし、これらの添加ガスを用いると歩留まり低下の原因となるAlNXやAlFXなどが反応副生成物として発生する。これを避けるため、添加ガスとしてC2H4を用いるようにしていた(例えば、特許文献3参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2001−210468号公報

【特許文献2】特開2000−58507号公報

【特許文献3】特開2001−53059号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上記従来の半導体装置の製造方法において、アルミニウムを含む金属膜の上にハードマスクとなる無機絶縁膜を形成し、その上に直接レジストパターンを形成する方法では、配線ピッチが小さくなるとレジストパターンの寸法精度を満たすことが困難になるという問題があった。

【0008】

また、シリコン窒化膜のみをハードマスクとして形成して上記金属膜をエッチングする方法では、シリコン窒化膜が塩素ガスによりエッチングされやすい膜であるため、ハードマスクに適さないという問題があった。

【0009】

一方、シリコン酸化膜のみをハードマスクとして形成して上記金属膜をエッチングする方法では、後に金属配線上にビアホールを形成する工程において、ハードマスクがエッチングストッパー膜とならないため、ビアホールが金属膜を突き抜けてしまい、配線の歩留まりを低下させるという問題があった。

【0010】

また、配線ピッチが小さくなると、上記従来の技術ではサイドエッチ量を十分に低減できないという問題があった。

【0011】

本発明は上記課題を解決するためになされたもので、アルミニウムを含む金属配線の形成において、サイドエッチ量を低減した微細な金属配線を形成でき、この金属配線の上に形成するビアホールが金属膜を突き抜けるのを抑制することができ、優れた半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明に係る半導体装置の製造方法は、基板上に下層から第一TiN膜、アルミニウムを含む金属膜、第二TiN膜を順次積層した金属配線層を形成する工程と、前記金属配線層の上に下層からストッパー膜、シリコン酸化膜を順次積層したハードマスク層を形成する工程と、前記ハードマスク層を選択的にエッチングして前記金属配線層の上にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記金属配線層をエッチングして金属配線を形成する工程と、前記ハードマスクおよび前記金属配線の上に層間絶縁膜を形成する工程と、前記ストッパー膜をエッチングストッパとして前記層間絶縁膜にビアホールを形成する工程とを含むことを特徴とする。

【0013】

本発明のその他の特徴については、以下において詳細に説明する。

【発明の効果】

【0014】

本発明によれば、アルミニウムを含む金属膜の上に形成するハードマスクの積層構造を最適化することにより、サイドエッチ量を低減した微細な金属配線を形成でき、この金属配線の上に形成するビアホールが金属膜を突き抜けるのを抑制することができ、優れた半導体装置の製造方法を得ることができる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施の形態1〜3に係る半導体装置の製造方法を示す断面図。

【図2】ハードマスクと金属配線の界面のノッチ量を説明する図。

【図3】本発明の実施の形態3に係る半導体装置の製造方法による効果を示す図。

【発明を実施するための形態】

【0016】

以下、本発明の実施の形態について図面を参照しながら説明する。同様の構成要素には同じ番号を付し、説明を省略する。

【0017】

以下、図面を参照しながら本発明の実施の形態について説明する。なお、各図において同一または相当する部分には同一符号を付して、その説明を簡略化ないし省略する。

【0018】

実施の形態1.

図1(a)〜(f)は、本実施の形態に係る半導体装置の製造方法を示す工程断面図である。

【0019】

まず、図1(a)に示すように、シリコン基板1の上にトランジスタなどの素子(図示しない)を形成した後、全面に層間絶縁膜2を形成する。例えば、化学気相成長(Chemical Vapor Deposition;以下、「CVD」という)法などにより、300〜400nm程度の膜厚で形成する。

【0020】

次に、層間絶縁膜2の上に、下層TiN膜3、AlCu膜4、上層TiN膜5を順次積層した金属配線層6を形成する。下層TiN膜3および上層TiN膜5は、スパッタ法などによりそれぞれ100nm程度の膜厚で形成する。AlCu膜4はアルミニウム膜に数%程度の銅を含むアルミニウム合金膜であり、スパッタ法などにより500nm程度の膜厚で形成する。

【0021】

このようにして、シリコン基板1の上にアルミニウムを含む金属配線層6を形成する。

【0022】

なお、上記の例では金属配線層6として下層からTiN膜3、AlCu膜4、TiN膜5を順次積層した積層膜を形成する例を示したが、これに置き換えて、下層からTi膜、TiN膜、AlCu膜、Ti膜、TiN膜を順次積層した積層膜を形成するようにしても良い。

【0023】

次に、金属配線層6の上に、ストッパー膜7およびシリコン酸化膜8を順次積層する。例えば、ストッパー膜7として、プラズマCVD法により50nm程度の膜厚でシリコン酸窒化膜(SiON膜)を形成する。そして、シリコン酸化膜8をプラズマCVD法により100〜200nm程度の膜厚で形成する。

【0024】

このとき、上記のシリコン酸窒化膜は窒素含有率を12%以上とする。また、シリコン酸窒化膜に置き換えて、プラズマCVD法により50nm程度の膜厚でシリコン窒化膜(SiN膜)を形成するようにしても良い。

【0025】

なお、シリコン酸化膜8は窒素(含有率11%以下)を含むようにしても良い。また、シリコン酸化膜8は後の工程で金属配線層6をエッチングするときのハードマスクとなるため、十分に厚い膜厚とする。

【0026】

次に、シリコン酸化膜8の上に二層のシリコン酸窒化膜、すなわち下層シリコン酸窒化膜9および上層シリコン酸窒化膜10を連続して形成する。例えば、プラズマCVD法により、それぞれ50nm程度の膜厚で形成する(以下、この二層のシリコン酸窒化膜を全体として「反射防止膜11」という。そして、ストッパー膜7、シリコン酸化膜8、反射防止膜11を全体として「ハードマスク層12」という)。

【0027】

このようにして、金属配線層6の上に、下層からストッパー膜7、シリコン酸化膜8、反射防止膜11を順次積層したハードマスク層12を形成する。

【0028】

前述したように、ハードマスク層12に含まれるストッパー膜7として、シリコン酸窒化膜又はシリコン窒化膜を用いるようにした。これにより、最終的に形成される金属配線の上にビアホールを形成するとき、ビアホールが金属配線を突き抜けるのを抑制することができる。

【0029】

また、ハードマスク層12に含まれる反射防止膜11として、二層のシリコン酸窒化膜を用いるようにしたので、後に反射防止膜11の上にレジストパターンを形成する工程において、下地膜からの反射を抑えて、微細なレジストパターンを制御性良く形成することができる。

【0030】

さらに、後の工程でハードマスクをマスクとして金属配線層6をエッチングすると、このハードマスクは上部の幅が狭くなった順テーパー形状となる。このような形状とすることにより、隣接する金属配線間に高密度プラズマCVDを用いたシリコン酸化膜を形成する場合には、埋め込み性を向上させることができる。

【0031】

また、ハードマスク層12に含まれる反射防止膜11として、有機膜を用いるようにしても良い。これにより、二層のシリコン酸窒化膜を用いた場合と比較して、下地膜からの反射をさらに効果的に抑制することができ、微細なレジストパターンをさらに制御性良く形成することができる。

【0032】

次に、ハードマスク層12の上に、リソグラフィによりレジストパターン13を形成する。このとき、レジストパターン13の下に反射防止膜11が形成されているので、微細なレジストパターン13を制御性良く形成することができる。

【0033】

次に、レジストパターン13をマスクとして図1(a)に示したハードマスク層12を選択的にエッチングして、図1(b)に示すように、金属配線層6の上にハードマスク12aを形成する。

【0034】

ここでは炭素および弗素を含むガス、酸素を含むガス、不活性ガスのうち少なくとも二つ以上のガスを含む混合ガス(例えば、CHF3/CF4/O2/Ar系混合ガス)を用いてエッチングを行う。

【0035】

さらに図示しないが、レジストパターン13をアッシングにより除去し、有機アミン系や有機リン酸系を中心とする剥離液によりポリマーなどのエッチング残渣を除去する。

【0036】

次に、図1(b)に示したハードマスク12aをマスクとして金属配線層6をエッチングして、図1(c)に示すように、金属配線6aを形成する。

【0037】

例えば、Cl2、BCl3、HCl、HIなどのハロゲン元素を含むガスに、Ar、Heなどの不活性ガス、CHF3、CH4、C2H4などのC(炭素)を含むデポジションガスを添加した混合ガスを用いてエッチングする。

【0038】

上記のデポジションガスを添加することにより、金属配線6aのサイドエッチ(配線の幅が細くなってしまうこと)量を低減することができる。

【0039】

また、上記デポジションガスの代わりに、CO、CO2、シクロアルカン(シクロブタン等)、シクロアルケン(シクロペンテン等)、1,3ブタジエン、ベンゼンなどの共役二重結合を有するものを含むデポジションガスを用いても良い。これにより、サイドエッチ量をさらに効果的に低減することができる。

【0040】

このとき反射防止膜11a(図1(b)参照)は、金属配線層6をエッチングする際に同時にエッチングされ、ハードマスク12aは、上部の幅が狭くなった順テーパー形状となる。

【0041】

また、ハードマスク12aはストッパー膜7aの上にシリコン酸化膜8aを積層した構造であるので、シリコン酸窒化膜(またはシリコン窒化膜)のみをハードマスクとしてエッチングした場合よりも耐エッチング性が優れ、サイドエッチ量を低減して金属配線6aを制御性良く形成することができる。

【0042】

次に、図1(d)に示すように、金属配線6aおよびハードマスク12aの上に、全面に層間絶縁膜14を形成する。例えば、高密度プラズマCVD法により、シリコン酸化膜を1000nm程度の膜厚で形成する。

【0043】

このとき、前述したようにハードマスク12aは、上部の幅が狭くなった順テーパー形状であるので、金属配線6aの配線ピッチが小さくなった場合でも、間口を大きくすることができ、隣接する金属配線6aの間を良好に埋め込むことができる。

【0044】

さらに、図示しないが、層間絶縁膜14の上にプラズマCVD法などによりシリコン酸化膜を300〜400nm程度の膜厚で形成する。そして、その表面を化学機械研磨(Chemical Mechanical Polishing;以下、「CMP」という)により研磨して、平坦化する。

【0045】

次に、平坦化されたシリコン酸化膜の上に、有機膜などからなる反射防止膜15を形成する。そして、反射防止膜15の上にリソグラフィによりレジストパターン16を形成する。

【0046】

次に、図1(d)に示したレジストパターン16をマスクとして反射防止膜15、層間絶縁膜14をエッチングして、図1(e)に示すように、金属配線6aの上にビアホール17aを形成して、ストッパー膜7aを露出させる。

【0047】

例えば、反射防止膜15をエッチングした後に、炭素および弗素を含むガス、酸素を含むガス、不活性ガスのうち少なくとも二つ以上のガスを含む混合ガス(例えば、C4F8/O2/Ar系混合ガス、又はC5F8/O2/Ar系混合ガス)を用いて層間絶縁膜14を選択的にエッチングする。

【0048】

次に、図1(e)に示したビアホール17aの底面に露出したストッパー膜7aをCHF3/O2/Ar系混合ガスを用いて選択的にエッチングして、図1(f)に示すように、ビアホール17bの底面に上層TiN膜5aを露出させる。

【0049】

このとき、前述したようにハードマスク層12(図1(a)参照)に含まれるストッパー膜7としてシリコン酸窒化膜又はシリコン窒化膜を用いるようにした。これにより、層間絶縁膜14の膜厚ばらつき、CMPによる削れ量のばらつきを吸収してビアホール17bが金属配線6aを突き抜けるのを抑制することができる。

【0050】

なお、ストッパー膜7aを選択的にエッチングする前に、上記のCHF3/O2/Ar系混合ガスを用いて、Arに対するCHF3/O2の流量比を上記ストッパー膜7aのエッチング条件よりも相対的に大きくして、図1(e)に示したビアホール17aの内面に付着したデポジション膜を除去するエッチングステップを入れるようにしても良い。これにより、ビアホール17bの底面に上層TiN膜5aを良好に露出させることができる。

【0051】

この後、図示しないが、図1(f)に示したビアホール17bの内面にTi膜、TiN膜の積層膜を形成する。さらに、この積層膜により形成された溝をタングステンなどの金属膜で埋め込み、溝の外部に形成したTi膜、TiN膜、金属膜をCMPなどにより除去して、ビアホール17bに金属膜を埋め込んだビアを形成する。

【0052】

以上説明したように、本実施の形態に係る半導体装置の製造方法は、まず、シリコン基板1の上にアルミニウムを含む金属配線層6を形成して、その上に、下層からストッパー膜7、シリコン酸化膜8、反射防止膜11を順次積層したハードマスク層12を形成するようにした。

【0053】

次にハードマスク層12を選択的にエッチングして金属配線層6の上にハードマスク12aを形成するようにした。

【0054】

そして、ハードマスク12aをマスクとして金属配線層6をエッチングして金属配線6aを形成するようにした。

【0055】

このように形成することにより、金属配線層6をエッチングして金属配線6aを形成するとき、シリコン酸窒化膜(またはシリコン窒化膜)のみをハードマスクとしてエッチングした場合よりも耐エッチング性が優れ、サイドエッチ量を低減して金属配線6aを制御性良く形成することができる。また、隣接する金属配線6aの間の埋め込み性を向上させ、これらの金属配線間の配線間容量や金属配線6aの上に形成するビア抵抗のばらつきを小さくすることができる。

【0056】

また、この配線の上に形成するビアホール17bが金属配線6aに突き抜けるのを抑制して、ビアホール形成の歩留まり低下を抑制することができる。

【0057】

実施の形態2.

本実施の形態に係る半導体装置の製造方法は、実施の形態1で示したハードマスク層12(図1(a)参照)に含まれるストッパー膜7として、金属膜を用いるようにしたものである。

【0058】

その他の構成については実施の形態1と同様であるので、図1(a)〜(f)を適宜参照して、実施の形態1と異なる点を中心に説明する。

【0059】

まず、シリコン基板1の上にトランジスタなどの素子(図示しない)を形成した後、全面に層間絶縁膜2を形成する工程から、アルミニウムを含む金属配線層6を形成するまでの工程(図1(a)参照)を、実施の形態1と同様にして行う。

【0060】

その後、金属配線層6の上にハードマスク層12を形成する。このとき、ハードマスク層12に含まれるストッパー膜7として、タングステン、タンタル、白金、銀、金、ニッケル、ルテニウム、コバルト、鉄、マンガン、イリジウム、ジルコニウム、インジウムのうち、いずれかの金属からなる金属膜を用いる。ここでは、タングステン膜を用いる。

【0061】

この後、ストッパー膜7の上にシリコン酸化膜8を形成する工程(図1(a)参照)から、反射防止膜15の上にレジストパターン16を形成するまでの工程(図1(d)参照)を、実施の形態1と同様にして行う。

【0062】

次に、図1(d)に示したレジストパターン16をマスクとして反射防止膜15、層間絶縁膜14をエッチングして、図1(e)に示すように、金属配線6aの上にビアホール17aを形成して、ストッパー膜7a(タングステン膜)を露出させる。

【0063】

このとき、ストッパー膜7aの被エッチング速度に対する層間絶縁膜14(シリコン酸化膜)の被エッチング速度を「エッチング選択比」と定義すると、タングステン膜をストッパー膜として用いた場合のエッチング選択比は、シリコン酸窒化膜(又はシリコン窒化膜)をストッパー膜として用いた場合のエッチング選択比より大きい。

【0064】

従って、金属配線6aの上にビアホール17aを形成するとき、ビアホール17aが金属配線6aに突き抜けるのを実施の形態1よりも効果的に抑制することができる。

【0065】

また、タングステン膜は金属膜であり、ビアホール17aの底面にストッパー膜7aを露出させた状態でビアホール17aの内部に金属膜を埋め込んでビアを形成しても導通性を失うことがないので、ストッパー膜7aを除去する工程を省略することができる。さらに、タングステン膜を金属配線6aの上に積層したので、金属配線6aの抵抗を低くすることができる。

【0066】

なお、前述したタングステン膜以外の金属膜をストッパー膜として用いた場合にも同様の効果を有する。

【0067】

なお、この後、実施の形態1と同様にストッパー膜7aをエッチングにより除去する(図1(f)参照)ようにしても良い。

【0068】

その他の構成については、実施の形態1と同様であるので、説明を省略する。

【0069】

以上説明したように、本実施の形態に係る半導体装置の製造方法は、実施の形態1で示したハードマスク層12に含まれるストッパー膜7として、タングステン、タンタル、白金、銀、金、ニッケル、ルテニウム、コバルト、鉄、マンガン、イリジウム、ジルコニウム、インジウムのうち、いずれかの金属からなる金属膜を用いるようにした。

【0070】

このように形成することにより、金属配線6aの上にビアホール17aを形成するとき、金属配線6aに突き抜けるのを実施の形態1よりも効果的に抑制することができる。

【0071】

また、ビアホール17aの底面にストッパー膜7aを露出させた状態で、ビアホール17aの内部に金属膜を埋め込んでビアを形成しても導通性を失うことがないので、ストッパー膜7aを除去する工程を省略することができる。さらに、タングステン膜を金属配線6aに積層したことにより、金属配線6aの抵抗を低くすることができる。

【0072】

実施の形態3.

本実施の形態に係る半導体装置の製造方法は、実施の形態1で示したシリコン酸化膜8を形成する工程(図1(a)参照)において、シリコンに対する酸素の組成比を特定範囲とし、形成温度を特定範囲として形成するようにしたものである。

【0073】

また、金属配線層6をエッチングして金属配線6aを形成する工程(図1(c)参照)を、別のシリコン基板上に形成した特定の膜のうち、いずれかの膜を予めエッチングしたエッチング装置を用いて行うようにしたものである。

【0074】

その他の構成については実施の形態1、2と同様であるので、図1(a)〜(f)を適宜参照して、実施の形態1、2と異なる点を中心に説明する。

【0075】

まず、シリコン基板1の上にトランジスタなどの素子(図示しない)を形成した後、全面に層間絶縁膜2を形成する工程から、金属配線層6の上にストッパー膜7を形成するまでの工程(図1(a)参照)を、実施の形態1(又は実施の形態2)と同様にして行う。

【0076】

その後、実施の形態1で示したハードマスク層12に含まれるシリコン酸化膜8を、シリコンに対する酸素の組成比が1.5〜2の範囲となるようにプラズマCVD法を用いて形成する。

【0077】

このように形成することにより、実施の形態1で示した金属配線層6をエッチングして金属配線6aを形成する工程(図1(c)参照)において、上層TiN膜5aがシリコン酸化膜8aと反応するのを抑え、ハードマスク12aと金属配線6aとの界面に発生するノッチ量を低減することができる。

【0078】

また、ハードマスク層12に含まれるシリコン酸化膜8を、290〜400℃の範囲の温度でプラズマCVD法を用いて形成するようにしても良い。

【0079】

このように形成することにより、上記と同様に、ハードマスク12aと金属配線6aとの界面に発生するノッチ量を低減することができる。

【0080】

この後、シリコン酸化膜8の上に反射防止膜11を形成する工程と、ハードマスク層12の上にレジストパターン13を形成する工程(図1(a)参照)を、実施の形態1と同様にして行う。

【0081】

次に、金属配線層6をエッチングする工程(図1(c)参照)を、シリコン基板1とは異なる別のシリコン基板上に形成したシリコン酸化膜、シリコン窒化膜、又は金属配線層6(図1(b)参照)に含まれる金属膜と同一種類の金属膜のうち、いずれかの膜をエッチングしたエッチング装置を用いて行うようにする。

【0082】

例えば、金属配線層6をエッチングする前に、金属配線層6を形成したシリコン基板1とは別のシリコン基板の上に形成したシリコン酸化膜、シリコン窒化膜、又は金属配線層6に含まれるTiN膜、AlCu膜などの金属膜のうち、いずれかの膜をエッチングする(以下、この処理を「シーズニング処理」という)。そして、シーズニング処理をしたエッチング装置を用いて金属配線層6をエッチングする。

【0083】

このように金属配線層6のエッチングを行うことにより、シーズニング処理においてエッチングした膜から供給される微量の酸素、窒素、金属を含有した反応生成物がエッチング装置内に残留して、金属配線層6のエッチング中に金属配線6aの側壁を保護するため、図2に示すハードマスク12aと金属配線6aの界面のノッチ量Aを低減することができる。

【0084】

これにより、ハードマスク12aと金属配線6aの界面のノッチ量Aを、さらに低減することができる。

【0085】

図3(a)は、金属配線層6をエッチングする前にシーズニング処理を行わなかった場合の、シリコン酸化膜8のシリコン(Si)に対する酸素(O)の組成比とノッチ量Aとの関係、およびシリコン酸化膜8の形成温度とノッチ量Aとの関係を示すデータである。

【0086】

これらのデータから、シリコン酸化膜8のシリコンに対する酸素の組成比を1.5〜2の範囲とすることにより、ノッチ量Aを低減する効果があることが分かる。また、形成温度を290〜400℃の範囲とすることにより、ノッチ量Aをさらに低減する効果があることが分かる。

【0087】

図3(b)は、金属配線層6をエッチングする前にシーズニング処理を行った場合、シリコン酸化膜8のシリコンに対する酸素の組成比を1.7、シリコン酸化膜8の生成温度を420℃とした場合のノッチ量Aを示すデータである。図3(a)との比較から、シーズニング処理を行うことにより、ノッチ量Aを低減する効果がさらに大きくなることが分かる。

【0088】

これらの結果から、本実施の形態の製造方法によりハードマスク12aと金属配線6aの界面のノッチ量を低減する効果があることが分かる。

【0089】

これにより、隣接する金属配線6aの間の埋め込み性が向上し、これらの金属配線の配線間容量ばらつきを小さくすることができる。また、金属配線6aの上層TiN膜5aの膜減りを防ぐことができ、金属配線6aの上に形成するビアの抵抗ばらつきを小さくすることができる。

【0090】

その他の構成については、実施の形態1(又は実施の形態2)と同様であるので、説明を省略する。

【0091】

以上説明したように、本実施の形態に係る半導体装置の製造方法は、実施の形態1(又は実施の形態2)で示したハードマスク層12に含まれるシリコン酸化膜8を、シリコンに対する酸素の組成比が1.5〜2の範囲となるようにプラズマCVD法を用いて形成するようにした。

【0092】

また、ハードマスク層12に含まれるシリコン酸化膜8を、290〜400℃の範囲の温度でプラズマCVD法を用いて形成するようにした。

【0093】

さらに、実施の形態1(又は実施の形態2)で示したハードマスク12aをマスクとして金属配線層6をエッチングして金属配線6aを形成する工程を、シリコン基板1とは異なる別のシリコン基板上に形成したシリコン酸化膜、シリコン窒化膜、又は金属配線層6に含まれる金属膜と同一種類の金属膜のうち、いずれかの膜をエッチングしたエッチング装置を用いて行うようにした。

【0094】

このように形成することにより、実施の形態1、2の効果に加えて、ハードマスク12aと金属配線6aの界面のノッチ量を低減することができる。

【0095】

これにより、隣接する金属配線6aの間の埋め込み性が向上し、これらの金属配線の配線間容量ばらつきを小さくすることができる。また、金属配線6aの上層TiN膜5aの膜減りを防ぐことができ、金属配線6aの上に形成するビアの抵抗ばらつきを小さくすることができる。

【符号の説明】

【0096】

1 シリコン基板、2 層間絶縁膜、3 下層TiN膜、4 AlCu膜、5 上層TiN膜、6 金属配線層、6a 金属配線、7a ストッパー膜、8 シリコン酸化膜、11 反射防止膜、12 ハードマスク層、12a ハードマスク、14 層間絶縁膜、17a、17b ビアホール。

【特許請求の範囲】

【請求項1】

基板上に下層から第一TiN膜、アルミニウムを含む金属膜、第二TiN膜を順次積層した金属配線層を形成する工程と、

前記金属配線層の上に下層からストッパー膜、シリコン酸化膜を順次積層したハードマスク層を形成する工程と、

前記ハードマスク層を選択的にエッチングして前記金属配線層の上にハードマスクを形成する工程と、

前記ハードマスクをマスクとして前記金属配線層をエッチングして金属配線を形成する工程と、

前記ハードマスクおよび前記金属配線の上に層間絶縁膜を形成する工程と、

前記ストッパー膜をエッチングストッパとして前記層間絶縁膜にビアホールを形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記ハードマスク層に含まれる前記ストッパー膜として、シリコン酸窒化膜又はシリコン窒化膜を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記ハードマスク層に含まれる前記ストッパー膜として、タングステン、タンタル、白金、銀、金、ニッケル、ルテニウム、コバルト、鉄、マンガン、イリジウム、ジルコニウム、インジウムのうち、いずれかの金属からなる金属膜を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項4】

前記ハードマスク層に含まれる前記シリコン酸化膜を、シリコンに対する酸素の組成比が1.5〜2の範囲となるようにプラズマ化学気相成長法を用いて形成することを特徴とする請求項1〜3のいずれかに記載の半導体装置の製造方法。

【請求項5】

前記ハードマスク層は前記シリコン酸化膜上に設けられた反射防止層を更に有し、

前記ハードマスク層に含まれる前記シリコン酸化膜を、290〜400℃の範囲の温度でプラズマ化学気相成長法を用いて形成することを特徴とする請求項1〜4のいずれかに記載の半導体装置の製造方法。

【請求項6】

前記ハードマスク層は前記シリコン酸化膜上に設けられた反射防止層を更に有し、

前記ハードマスク層に含まれる前記反射防止膜として、二層のシリコン酸窒化膜を用いることを特徴とする請求項1〜5のいずれかに記載の半導体装置の製造方法。

【請求項7】

前記ハードマスク層に含まれる前記反射防止膜として、有機膜を用いることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項8】

前記金属配線層をエッチングする工程を、前記基板とは異なる別の基板上に形成したシリコン酸化膜、シリコン窒化膜、又は前記金属配線層に含まれる金属膜と同一種類の金属膜のうち、いずれかの膜をエッチングしたエッチング装置を用いて行うことを特徴とする請求項1〜7のいずれかに記載の半導体装置の製造方法。

【請求項9】

前記ビアホールを形成する工程において、炭素および弗素を含むガス、酸素を含むガス、不活性ガスのうち少なくとも二つ以上のガスを含む混合ガスを用いることを特徴とする請求項請求項1〜8のいずれかに記載の半導体装置の製造方法。

【請求項10】

前記混合ガスは炭素および弗素を含むガスを有することを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

前記混合ガスはC4F8/O2/Ar系混合ガス、又はC5F8/O2/Ar系混合ガスであることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項12】

基板上に下層から第一TiN膜、アルミニウムを含む金属膜、第二TiN膜を順次積層した金属配線材料を形成する工程と、

前記金属配線材料の上に下層からストッパー膜、シリコン酸化膜、反射防止膜を順次積層したハードマスク層を形成する工程と、

前記ハードマスク層を選択的にエッチングして前記金属配線材料の上にハードマスクを形成する工程と、

前記ハードマスクをマスクとして前記金属配線材料をエッチングして金属配線を形成する工程と、

前記金属配線の側面と上面を覆う層間絶縁膜を形成する工程と、

前記層間絶縁膜のコンタクトホールを前記ストッパー膜にて止めるエッチングにて形成する工程とを含み、

前記ハードマスク層に含まれる膜として、シリコン酸窒化膜又はシリコン窒化膜を用いることを特徴とする半導体装置の製造方法。

【請求項1】

基板上に下層から第一TiN膜、アルミニウムを含む金属膜、第二TiN膜を順次積層した金属配線層を形成する工程と、

前記金属配線層の上に下層からストッパー膜、シリコン酸化膜を順次積層したハードマスク層を形成する工程と、

前記ハードマスク層を選択的にエッチングして前記金属配線層の上にハードマスクを形成する工程と、

前記ハードマスクをマスクとして前記金属配線層をエッチングして金属配線を形成する工程と、

前記ハードマスクおよび前記金属配線の上に層間絶縁膜を形成する工程と、

前記ストッパー膜をエッチングストッパとして前記層間絶縁膜にビアホールを形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記ハードマスク層に含まれる前記ストッパー膜として、シリコン酸窒化膜又はシリコン窒化膜を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記ハードマスク層に含まれる前記ストッパー膜として、タングステン、タンタル、白金、銀、金、ニッケル、ルテニウム、コバルト、鉄、マンガン、イリジウム、ジルコニウム、インジウムのうち、いずれかの金属からなる金属膜を用いることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項4】

前記ハードマスク層に含まれる前記シリコン酸化膜を、シリコンに対する酸素の組成比が1.5〜2の範囲となるようにプラズマ化学気相成長法を用いて形成することを特徴とする請求項1〜3のいずれかに記載の半導体装置の製造方法。

【請求項5】

前記ハードマスク層は前記シリコン酸化膜上に設けられた反射防止層を更に有し、

前記ハードマスク層に含まれる前記シリコン酸化膜を、290〜400℃の範囲の温度でプラズマ化学気相成長法を用いて形成することを特徴とする請求項1〜4のいずれかに記載の半導体装置の製造方法。

【請求項6】

前記ハードマスク層は前記シリコン酸化膜上に設けられた反射防止層を更に有し、

前記ハードマスク層に含まれる前記反射防止膜として、二層のシリコン酸窒化膜を用いることを特徴とする請求項1〜5のいずれかに記載の半導体装置の製造方法。

【請求項7】

前記ハードマスク層に含まれる前記反射防止膜として、有機膜を用いることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項8】

前記金属配線層をエッチングする工程を、前記基板とは異なる別の基板上に形成したシリコン酸化膜、シリコン窒化膜、又は前記金属配線層に含まれる金属膜と同一種類の金属膜のうち、いずれかの膜をエッチングしたエッチング装置を用いて行うことを特徴とする請求項1〜7のいずれかに記載の半導体装置の製造方法。

【請求項9】

前記ビアホールを形成する工程において、炭素および弗素を含むガス、酸素を含むガス、不活性ガスのうち少なくとも二つ以上のガスを含む混合ガスを用いることを特徴とする請求項請求項1〜8のいずれかに記載の半導体装置の製造方法。

【請求項10】

前記混合ガスは炭素および弗素を含むガスを有することを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

前記混合ガスはC4F8/O2/Ar系混合ガス、又はC5F8/O2/Ar系混合ガスであることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項12】

基板上に下層から第一TiN膜、アルミニウムを含む金属膜、第二TiN膜を順次積層した金属配線材料を形成する工程と、

前記金属配線材料の上に下層からストッパー膜、シリコン酸化膜、反射防止膜を順次積層したハードマスク層を形成する工程と、

前記ハードマスク層を選択的にエッチングして前記金属配線材料の上にハードマスクを形成する工程と、

前記ハードマスクをマスクとして前記金属配線材料をエッチングして金属配線を形成する工程と、

前記金属配線の側面と上面を覆う層間絶縁膜を形成する工程と、

前記層間絶縁膜のコンタクトホールを前記ストッパー膜にて止めるエッチングにて形成する工程とを含み、

前記ハードマスク層に含まれる膜として、シリコン酸窒化膜又はシリコン窒化膜を用いることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2010−62578(P2010−62578A)

【公開日】平成22年3月18日(2010.3.18)

【国際特許分類】

【出願番号】特願2009−247650(P2009−247650)

【出願日】平成21年10月28日(2009.10.28)

【分割の表示】特願2004−335840(P2004−335840)の分割

【原出願日】平成16年11月19日(2004.11.19)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年3月18日(2010.3.18)

【国際特許分類】

【出願日】平成21年10月28日(2009.10.28)

【分割の表示】特願2004−335840(P2004−335840)の分割

【原出願日】平成16年11月19日(2004.11.19)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]