半導体装置の製造方法

【課題】凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有するウェハWの少なくとも凹部1aの底部1bおよび側壁部1cに、シード膜3を形成する工程と、シード膜3上に、少なくとも凹部1aの底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うようにめっき抑制膜4を形成する工程と、シード膜3に電流を供給して、めっき抑制膜4の形成された凹部1aに埋め込まれるように電解めっき法によりめっき膜5を形成する工程と、めっき膜5に熱処理を施す工程とを備え、めっき抑制膜4が、シード膜3の構成材料より抵抗率が高くかつめっき膜5の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有するウェハWの少なくとも凹部1aの底部1bおよび側壁部1cに、シード膜3を形成する工程と、シード膜3上に、少なくとも凹部1aの底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うようにめっき抑制膜4を形成する工程と、シード膜3に電流を供給して、めっき抑制膜4の形成された凹部1aに埋め込まれるように電解めっき法によりめっき膜5を形成する工程と、めっき膜5に熱処理を施す工程とを備え、めっき抑制膜4が、シード膜3の構成材料より抵抗率が高くかつめっき膜5の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の配線としては、配線抵抗の低減、配線不良の原因となるエレクトロマイグレーション(EM)及びストレスマイグレーション(SM)等のマイグレーションの耐性向上のために、Alの代わりにCuが用いられている。

【0003】

Cuは、AlのようなRIE(反応性イオンエッチング)による加工が困難であるため、Cuで配線を形成するには、絶縁膜の表面に予め溝やホールからなる凹部を形成しておき、その凹部にCuを埋め込み、その後CMP(化学的機械的研磨)により不要なCuを除去して配線を形成するダマシン法が用いられている(例えば、特許文献1参照)。

【0004】

ダマシン法におけるCuの埋め込み方法としては、主にめっき法が用いられている。しかしながら、凹部が微細になればなるほど、ボイド(空隙)が発生しやすい。この原因の一つは、現在のめっき技術では、凹部の底部側からめっきが成長するとともに側壁部側からもめっきが成長するためであると考えられる。

【0005】

現在、このようなボイドを低減させるために、例えば種々の添加剤をめっき液中に含ませて、凹部の底部側からめっきを成長させる技術(ボトムアップ成長)が開発されている。しかしながら、添加剤の組み合わせは無限に存在するため、添加剤の適切な組み合わせや濃度を見付けることが非常に困難であるとともに、量産時のコントロールも非常に困難である。また、添加剤によっては、めっき膜中に様々な不純物が取り込まれることがある。このような不純物は配線の抵抗値や信頼性を左右するため、埋め込み性能のみならず、この面からも、適切な添加剤の組み合わせを見付けることが重要である。このため、適切な添加剤の組み合わせを見付けることに多大な手間を要する。

【特許文献1】特開2007−318141号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、上記課題を解決するためになされたものである。すなわち、凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一の態様によれば、表面に凹部を有する基板の少なくとも前記凹部の底部および側壁部に、シード膜を形成する工程と、前記シード膜上に、少なくとも前記凹部の底部に位置する前記シード膜の部分が露出しかつ前記凹部の側壁部に位置する前記シード膜の部分を覆うようにめっき抑制膜を形成する工程と、前記シード膜に電流を供給して、前記めっき抑制膜の形成された前記凹部に埋め込まれるように電解めっき法によりめっき膜を形成する工程と、前記めっき膜に熱処理を施す工程とを備え、前記めっき抑制膜が、前記シード膜の構成材料より抵抗率が高くかつ前記めっき膜の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

【発明の効果】

【0008】

本発明の一の態様による半導体装置の製造方法によれば、凹部の側壁部側からのめっきの成長を抑制することができ、これにより、主に凹部の底部側からめっきが成長するので、ボイドの発生を低減することができる。

【発明を実施するための最良の形態】

【0009】

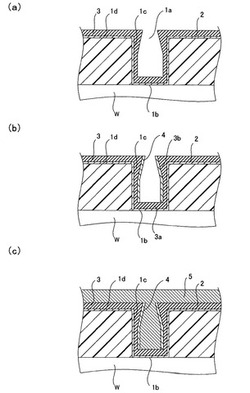

以下、図面を参照して、本発明の実施の形態を説明する。以下の図面において、同一の部材には同一の符号を付している。図1は本実施の形態に係る半導体装置の製造プロセスの流れを示したフローチャートであり、図2(a)〜図5は本実施の形態に係る半導体装置の模式的な製造プロセス図である。

【0010】

図2(a)に示されるように、図示しない半導体素子等が形成された半導体ウェハW(以下、単に「ウェハ」という。)上に、例えば化学気相成長法(Chemical Vapor Deposition:CVD法)あるいは塗布法により層間絶縁膜1を形成する(ステップ1)。層間絶縁膜1の構成材料としては、例えば、有機Si酸化膜、有機樹脂膜及びポーラスSi酸化膜等の低誘電率絶縁膜、SiO2膜等が挙げられる。

【0011】

層間絶縁膜1を形成した後、図2(b)に示されるようにフォトリソグラフィ技術および反応性イオンエッチング(RIE)により層間絶縁膜1に、凹部1aを形成する(ステップ2)。本実施の形態では、凹部1aは、配線溝として機能するが、凹部1aはこれに限定されない。すなわち、凹部1aには、配線溝の他、例えばビアホール、コンタクトホール、あるいはビアホールと配線溝の組み合わせ等が含まれるものとする。

【0012】

凹部1aを形成するには、まず、層間絶縁膜1上にレジストパターンを形成し、その後レジストパターンをマスクとして、RIEにより層間絶縁膜1をエッチングし、層間絶縁膜1に凹部1aを形成する。層間絶縁膜1に凹部1aを形成した後、アッシング等によりレジストパターンを除去する。

【0013】

層間絶縁膜1に凹部1aを形成した後、図2(c)に示されるように層間絶縁膜1上に、例えばスパッタ法あるいはCVD法により層間絶縁膜1への金属拡散を抑制するためのバリアメタル膜2を形成する(ステップ3)。バリアメタル膜2の構成材料としては、例えばTa、Ti、TaN、TiN、NbN、WN、あるいはVN等の導電性材料が挙げられる。なお、これらの材料を積層したものからバリアメタル膜2を形成してもよい。

【0014】

層間絶縁膜1上にバリアメタル膜2を形成した後、図3(a)に示されるようにバリアメタル膜2上に、例えばスパッタ法により電解めっき時に電流を流すためのシード膜3を形成する(ステップ4)。シード膜3は、凹部1aの底部1b、側壁部1c、層間絶縁膜1の凹部1a外の表面部であるフィールド部1d上に形成される。シード膜3の構成材料としては、例えばCu等の金属が挙げられる。

【0015】

バリアメタル膜2上にシード膜3を形成した後、図3(b)に示されるようにシード膜3上に、凹部1aの側壁部1c側からのめっきの成長を抑制するためのめっき抑制膜4を形成する(ステップ5)。

【0016】

めっき抑制膜4は、凹部1の底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うように形成される。本実施の形態では、めっき抑制膜4は、シード膜3の部分3bのみを覆うように形成されている。なお、本実施の形態では、フィールド部1d上にめっき抑制膜4が形成されていないが、めっき抑制膜4がシード膜3の部分3aが露出しかつ部分3bを覆うように形成されていれば、フィールド部1d上にめっき抑制膜4が形成されていてもよい。

【0017】

図3(b)に示されるめっき抑制膜4を形成するには、まず、CVD法によりシード膜3全体上にめっき抑制膜4を形成し、その後異方性のドライエッチングにより凹部1aの底部1bおよびフィールド部1d上に存在するめっき抑制膜4を除去して、凹部1aの側壁部1cのみにめっき抑制膜4を形成する。なお、フィールド部1d上にもめっき抑制膜4を形成する場合には、凹部1aの底部1b上に存在するめっき抑制膜4のみを除去する。

【0018】

めっき抑制膜4は、シード膜3の構成材料より抵抗率が高くかつ後述するめっき膜5の構成材料と異なる材料から構成される。また、めっき抑制膜4は、めっき液に対する溶解耐性がシード膜3の構成材料よりも大きい材料から構成されていることが好ましい。具体的には、シード膜3およびめっき膜5がCuから構成されている場合には、めっき抑制膜4は、例えば、Ru、Ti、Taまたはこれらの混合物、あるいは絶縁物から構成することが可能である。絶縁物としては、例えば、テトラエトキシシラン(TEOS)系SiO2等が挙げられる。

【0019】

めっき抑制膜4の膜厚は、1nm以上であることが好ましい。めっき抑制膜4の膜厚が1nm未満であると、めっき抑制膜4が不連続となってしまうおそれがあるからである。

【0020】

シード膜3の部分3b上にめっき抑制膜4を形成した後、図3(c)に示されるように、シード膜3に電流を供給して、電解めっき法によりめっき膜5を形成する(ステップ6)。めっき膜5は凹部1aの全体に埋め込まれるように形成される。めっき膜5の構成材料としては、例えばCu等の金属が挙げられる。また、めっき膜5の形成に使用されるめっき液としては、例えばめっき膜5をCuから形成する場合には、硫酸銅水溶液またはこの水溶液にサプレッサ、アクセラレータ、およびレベラ等の添加剤を添加したものが挙げられる。

【0021】

めっき膜5を形成した後、めっき膜5等に第1の熱処理(アニール)を施し、図4(a)に示されるようにシード膜3およびめっき膜5の結晶を成長させる(ステップ7)。結晶が成長したシード膜3とめっき膜5とは一体的な膜6(以下、この膜を配線膜6と称する)となる。なお、後述するように第2の熱処理を行う場合には、第1の熱処理は、省略することも可能である。

【0022】

めっき膜5等に熱処理を施した後、例えば化学的機械的研磨(Chemical Mechanical Polishing:CMP)により研磨して、凹部1a内に存在するバリアメタル膜2、めっき抑制膜4および配線膜6がそれぞれ残るように、層間絶縁膜1上の不要なバリアメタル膜2および配線膜6をそれぞれ除去する(ステップ8)。具体的には、ウェハWを研磨パッド(図示せず)に接触させた状態で、ウェハW及び研磨パッドを回転させるとともにウェハW上にスラリ(図示せず)を供給して、配線膜6等を研磨する。なお、CMPで研磨する場合に限らず、その他の手法で研磨してもよい。その他の手法としては、例えば電解研磨が挙げられる。これにより、図4(b)に示されるように凹部1a外の配線膜6等が除去されて、凹部1a内のみに配線膜6等が残存するとともに、めっき抑制膜4の上部が露出する。

【0023】

その後、図4(c)に示されるように例えばCF4等のガスを使用した等方性のドライエッチングによりめっき抑制膜4を選択的に除去する(ステップ9)。めっき抑制膜4が除去されると、その部分は空隙4aとなる。

【0024】

最後に、配線膜6に第2の熱処理を施す(ステップ10)。これにより、配線膜6を構成している金属がストレスマイグレーションにより移動して、空隙4aが埋められる。以上により、図5に示されるように凹部1a内に配線6aが形成される。なお、第1の熱処理を省略した場合には、この第2の熱処理で、シード膜3およびめっき膜5の結晶を成長させる。また、凹部1aがビアホールの場合にはビアが形成され、コンタクトホールである場合にはコンタクトが形成され、配線溝とビアホールとの組み合わせの場合には配線とビアが形成される。

【0025】

本実施の形態によれば、凹部1aの側壁部1cに位置するシード膜3の部分3bをめっき抑制膜4で覆っているので、凹部1aの側壁部1cから凹部1aの中央部に向かう方向の電流が流れ難くなる。したがって、凹部1aの側壁部1c側からはめっきが成長し難くなる。一方、凹部1aの底部1bに位置するシード膜3の部分3aは露出しているので、凹部1aの底部1bから凹部1aの開口面に向かう方向の電流は流れ易い。したがって、凹部1aの底部1b側からはめっきが成長し易い。これにより、確実にめっきをボトムアップ成長させることができるので、ボイドが低減した配線6aを得ることができる。

【0026】

また、本実施の形態によれば、確実にめっきをボトムアップ成長させることができるので、めっき液に含まれる添加剤を低減させることができる。これにより、添加剤の適切な組み合わせや濃度を見付けるという多大な手間を軽減させることができる。

【0027】

さらに、めっき液に含まれる添加剤を低減させた場合には、細幅の配線溝におけるめっきの盛り上がり(ハンプ)を抑制することができる。ここで、現在は、細幅の配線溝においてはハンプが形成されてしまうので、CMPによる研磨を考慮して層間絶縁膜のフィールド部上にもめっき膜を形成している。これに対して、本実施の形態によれば、ハンプを抑制することができ、しかもめっき抑制膜4をフィールド部1d上に残存させた場合には、フィールド部1d上にはめっき膜5がほぼ形成されないので、CMPに要する時間を短縮することができる。

【0028】

また、近年、配線やコンタクト(ビア)が微細化するにつれて、めっきでの埋め込みを可能にするために、凹部の開口をできる限り広く確保する必要がある。そのため、シード膜の膜厚は、ますます薄くなる傾向にある。その場合、凹部の側壁部に存在するシード膜の膜厚は、さらに薄くなってしまい、シード膜の成膜条件やバリアメタル膜との組み合わせによっては、シード膜の凝集およびめっき液との接触初期段階でのシード膜の溶解が生ずるおそれがある。シード膜が凝集、溶解した場合には、その部分にはめっきが成長しないので、結果としてボイドが発生してしまう。これに対し、本実施の形態によれば、凹部1aの側壁部1cに位置するシード膜3の部分3bをめっき抑制膜4で覆っているので、めっき液によるシード膜3の溶解を抑制することができる。これによりボイドの発生をより抑制することができる。さらに、めっき液に対する溶解耐性がCuより大きい材料からめっき抑制膜4を形成した場合には、めっき液によるシード膜3の溶解をさらに抑制することができる。

【0029】

本実施の形態によれば、CMP後、めっき抑制膜4を選択的に除去しているので、配線抵抗の上昇を抑制することができる。すなわち、例えばシード膜3およびめっき膜5がCuから構成されている場合には、めっき抑制膜4は、Cuよりも高い抵抗率を有する材料から構成されているので、配線6a中にめっき抑制膜4が残存していると、配線抵抗が上昇してしまう。これに対し、本実施の形態では、CMP後、めっき抑制膜4を選択的に除去しているので、配線抵抗の上昇を抑制することができる。なお、めっき抑制膜4がRu、Ti、Taまたはこれらの混合物から形成されている場合には、抵抗率が比較的低いので若干配線抵抗は上昇するものの、配線6a中に残存させておくことも可能である。

【0030】

本実施の形態によれば、めっき抑制膜4を絶縁物から構成した場合には、めっき抑制膜4には電流がほぼ流れないので、凹部1aの側壁部1c側からめっきがより成長し難い。

【実施例】

【0031】

以下、実施例について説明する。本実施例1〜3においては、上記実施の形態と同様の手法によりめっき抑制膜を形成した状態で、めっき膜を形成し、そのめっき膜の断面を観察した。なお、本実施例と比較するために、めっき抑制膜を形成せずにめっき膜を形成した比較例1〜4についても、めっき膜の断面を観察した。

【0032】

試料

(実施例1)

実施例1においては、次のような工程で試料を作製した。まず、基板上にCVD法により第1のTEOS膜(層間絶縁膜)を形成し、この第1のTEOS膜にフォトリソグラフィ技術およびRIE等により幅30nmおよび深さ180nmの溝(凹部)を形成した。その後、PVD法によりTaN膜(バリアメタル膜)を7nm形成し、次いでこの上にCuシード膜(シード膜)を15nm形成した。このCuシード膜の膜厚は、ブランケットの状態で成膜したときの膜厚で、溝内ではさらに薄くなっていた。

【0033】

次いで、Cuシード膜上にCVD法によりRu膜(めっき抑制膜)を5nm形成し、異方性のドライエッチングにより第1のTEOS膜のフィールド部と溝の底部のRu膜を除去して、溝の側壁部のRu膜のみを残存させた。そして、この状態で電解めっき法によりCuめっき膜(めっき膜)を溝に埋め込んだ。なお、このめっきの際に使用しためっき液は、硫酸銅水溶液に一般的に用いられているアクセラレータ、サプレッサおよびレベラ等の種々の添加剤を含ませたものであった。

【0034】

(実施例2)

実施例2においては、硫酸銅水溶液に必要最小限の添加剤(いわゆる光沢剤と呼ばれるものの一種)のみしか添加しなかった以外は、実施例1とほぼ同様の手法により試料を作製した。

【0035】

(実施例3)

実施例3においては、Ru膜に代えて第2のTEOS膜(めっき抑制膜)を5nm形成した。その後、同様に異方性エッチングにより第1のTEOS膜のフィールド部と溝の底部に位置する第2のTEOS膜を除去して、溝の側壁部の第2のTEOS膜のみを残存させた。また、めっき後CMPにより不要なCu等を除去した。このとき溝内部に存在する第2のTEOS膜の上部が露出した状態になった。そして、等方性のドライエッチングによりこの第2のTEOS膜を除去し、FG(水素・窒素)雰囲気中で、250℃で1時間の熱処理を施した。その他は、実施例1と同様であった。

【0036】

(比較例1〜4)

比較例1〜4においては、Ru膜を形成せずにCuめっき膜を形成した以外は、実施例1とほぼ同様の手法により試料を作製した。なお、Cuシード膜の膜厚は、比較例1では15nm、比較例2では25nm、比較例3では35nm、比較例4では45nmであった。

【0037】

観察

このような試料を用いて、めっき膜の断面を観察した。以下、結果について述べる。比較例1〜4においては、全てにおいてボイドが観察された。これは、Cuシード膜の膜厚が厚くなるにしたがって、めっき液によるCuシード膜の溶解が緩和するが、逆に膜厚が厚くなると、Cuめっき膜形成前の溝の開口幅が狭くなることで、溝内部が全て埋め込まれる前に、溝の側壁部側からのめっきの成長によって開口が塞がってしまうためであると考えられる。これに対し、実施例1〜3においては、ボイドは観察されなかった。なお、実施例3においては、第2のTEOS膜を除去することにより形成された空隙は熱処理後においては観察されなかった。これらの結果から、めっき抑制膜を形成した場合には、ボイドが低減することが確認された。

【0038】

なお、本発明は上記実施の形態の記載内容に限定されるものではなく、構造や材質、各部材の配置等は、本発明の要旨を逸脱しない範囲で適宜変更することが可能である。

【図面の簡単な説明】

【0039】

【図1】実施の形態に係る半導体装置の製造プロセスの流れを示したフローチャートである。

【図2】実施の形態に係る半導体装置の模式的な製造プロセス図である。

【図3】実施の形態に係る半導体装置の模式的な製造プロセス図である。

【図4】実施の形態に係る半導体装置の模式的な製造プロセス図である。

【図5】実施の形態に係る半導体装置の模式的な製造プロセス図である。

【符号の説明】

【0040】

W…ウェハ、1…層間絶縁膜、1a…凹部、1b…底部、1c…側壁部、2…バリアメタル膜、3…シード膜、4…めっき抑制膜、5…めっき膜、6a…配線。

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の配線としては、配線抵抗の低減、配線不良の原因となるエレクトロマイグレーション(EM)及びストレスマイグレーション(SM)等のマイグレーションの耐性向上のために、Alの代わりにCuが用いられている。

【0003】

Cuは、AlのようなRIE(反応性イオンエッチング)による加工が困難であるため、Cuで配線を形成するには、絶縁膜の表面に予め溝やホールからなる凹部を形成しておき、その凹部にCuを埋め込み、その後CMP(化学的機械的研磨)により不要なCuを除去して配線を形成するダマシン法が用いられている(例えば、特許文献1参照)。

【0004】

ダマシン法におけるCuの埋め込み方法としては、主にめっき法が用いられている。しかしながら、凹部が微細になればなるほど、ボイド(空隙)が発生しやすい。この原因の一つは、現在のめっき技術では、凹部の底部側からめっきが成長するとともに側壁部側からもめっきが成長するためであると考えられる。

【0005】

現在、このようなボイドを低減させるために、例えば種々の添加剤をめっき液中に含ませて、凹部の底部側からめっきを成長させる技術(ボトムアップ成長)が開発されている。しかしながら、添加剤の組み合わせは無限に存在するため、添加剤の適切な組み合わせや濃度を見付けることが非常に困難であるとともに、量産時のコントロールも非常に困難である。また、添加剤によっては、めっき膜中に様々な不純物が取り込まれることがある。このような不純物は配線の抵抗値や信頼性を左右するため、埋め込み性能のみならず、この面からも、適切な添加剤の組み合わせを見付けることが重要である。このため、適切な添加剤の組み合わせを見付けることに多大な手間を要する。

【特許文献1】特開2007−318141号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、上記課題を解決するためになされたものである。すなわち、凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一の態様によれば、表面に凹部を有する基板の少なくとも前記凹部の底部および側壁部に、シード膜を形成する工程と、前記シード膜上に、少なくとも前記凹部の底部に位置する前記シード膜の部分が露出しかつ前記凹部の側壁部に位置する前記シード膜の部分を覆うようにめっき抑制膜を形成する工程と、前記シード膜に電流を供給して、前記めっき抑制膜の形成された前記凹部に埋め込まれるように電解めっき法によりめっき膜を形成する工程と、前記めっき膜に熱処理を施す工程とを備え、前記めっき抑制膜が、前記シード膜の構成材料より抵抗率が高くかつ前記めっき膜の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

【発明の効果】

【0008】

本発明の一の態様による半導体装置の製造方法によれば、凹部の側壁部側からのめっきの成長を抑制することができ、これにより、主に凹部の底部側からめっきが成長するので、ボイドの発生を低減することができる。

【発明を実施するための最良の形態】

【0009】

以下、図面を参照して、本発明の実施の形態を説明する。以下の図面において、同一の部材には同一の符号を付している。図1は本実施の形態に係る半導体装置の製造プロセスの流れを示したフローチャートであり、図2(a)〜図5は本実施の形態に係る半導体装置の模式的な製造プロセス図である。

【0010】

図2(a)に示されるように、図示しない半導体素子等が形成された半導体ウェハW(以下、単に「ウェハ」という。)上に、例えば化学気相成長法(Chemical Vapor Deposition:CVD法)あるいは塗布法により層間絶縁膜1を形成する(ステップ1)。層間絶縁膜1の構成材料としては、例えば、有機Si酸化膜、有機樹脂膜及びポーラスSi酸化膜等の低誘電率絶縁膜、SiO2膜等が挙げられる。

【0011】

層間絶縁膜1を形成した後、図2(b)に示されるようにフォトリソグラフィ技術および反応性イオンエッチング(RIE)により層間絶縁膜1に、凹部1aを形成する(ステップ2)。本実施の形態では、凹部1aは、配線溝として機能するが、凹部1aはこれに限定されない。すなわち、凹部1aには、配線溝の他、例えばビアホール、コンタクトホール、あるいはビアホールと配線溝の組み合わせ等が含まれるものとする。

【0012】

凹部1aを形成するには、まず、層間絶縁膜1上にレジストパターンを形成し、その後レジストパターンをマスクとして、RIEにより層間絶縁膜1をエッチングし、層間絶縁膜1に凹部1aを形成する。層間絶縁膜1に凹部1aを形成した後、アッシング等によりレジストパターンを除去する。

【0013】

層間絶縁膜1に凹部1aを形成した後、図2(c)に示されるように層間絶縁膜1上に、例えばスパッタ法あるいはCVD法により層間絶縁膜1への金属拡散を抑制するためのバリアメタル膜2を形成する(ステップ3)。バリアメタル膜2の構成材料としては、例えばTa、Ti、TaN、TiN、NbN、WN、あるいはVN等の導電性材料が挙げられる。なお、これらの材料を積層したものからバリアメタル膜2を形成してもよい。

【0014】

層間絶縁膜1上にバリアメタル膜2を形成した後、図3(a)に示されるようにバリアメタル膜2上に、例えばスパッタ法により電解めっき時に電流を流すためのシード膜3を形成する(ステップ4)。シード膜3は、凹部1aの底部1b、側壁部1c、層間絶縁膜1の凹部1a外の表面部であるフィールド部1d上に形成される。シード膜3の構成材料としては、例えばCu等の金属が挙げられる。

【0015】

バリアメタル膜2上にシード膜3を形成した後、図3(b)に示されるようにシード膜3上に、凹部1aの側壁部1c側からのめっきの成長を抑制するためのめっき抑制膜4を形成する(ステップ5)。

【0016】

めっき抑制膜4は、凹部1の底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うように形成される。本実施の形態では、めっき抑制膜4は、シード膜3の部分3bのみを覆うように形成されている。なお、本実施の形態では、フィールド部1d上にめっき抑制膜4が形成されていないが、めっき抑制膜4がシード膜3の部分3aが露出しかつ部分3bを覆うように形成されていれば、フィールド部1d上にめっき抑制膜4が形成されていてもよい。

【0017】

図3(b)に示されるめっき抑制膜4を形成するには、まず、CVD法によりシード膜3全体上にめっき抑制膜4を形成し、その後異方性のドライエッチングにより凹部1aの底部1bおよびフィールド部1d上に存在するめっき抑制膜4を除去して、凹部1aの側壁部1cのみにめっき抑制膜4を形成する。なお、フィールド部1d上にもめっき抑制膜4を形成する場合には、凹部1aの底部1b上に存在するめっき抑制膜4のみを除去する。

【0018】

めっき抑制膜4は、シード膜3の構成材料より抵抗率が高くかつ後述するめっき膜5の構成材料と異なる材料から構成される。また、めっき抑制膜4は、めっき液に対する溶解耐性がシード膜3の構成材料よりも大きい材料から構成されていることが好ましい。具体的には、シード膜3およびめっき膜5がCuから構成されている場合には、めっき抑制膜4は、例えば、Ru、Ti、Taまたはこれらの混合物、あるいは絶縁物から構成することが可能である。絶縁物としては、例えば、テトラエトキシシラン(TEOS)系SiO2等が挙げられる。

【0019】

めっき抑制膜4の膜厚は、1nm以上であることが好ましい。めっき抑制膜4の膜厚が1nm未満であると、めっき抑制膜4が不連続となってしまうおそれがあるからである。

【0020】

シード膜3の部分3b上にめっき抑制膜4を形成した後、図3(c)に示されるように、シード膜3に電流を供給して、電解めっき法によりめっき膜5を形成する(ステップ6)。めっき膜5は凹部1aの全体に埋め込まれるように形成される。めっき膜5の構成材料としては、例えばCu等の金属が挙げられる。また、めっき膜5の形成に使用されるめっき液としては、例えばめっき膜5をCuから形成する場合には、硫酸銅水溶液またはこの水溶液にサプレッサ、アクセラレータ、およびレベラ等の添加剤を添加したものが挙げられる。

【0021】

めっき膜5を形成した後、めっき膜5等に第1の熱処理(アニール)を施し、図4(a)に示されるようにシード膜3およびめっき膜5の結晶を成長させる(ステップ7)。結晶が成長したシード膜3とめっき膜5とは一体的な膜6(以下、この膜を配線膜6と称する)となる。なお、後述するように第2の熱処理を行う場合には、第1の熱処理は、省略することも可能である。

【0022】

めっき膜5等に熱処理を施した後、例えば化学的機械的研磨(Chemical Mechanical Polishing:CMP)により研磨して、凹部1a内に存在するバリアメタル膜2、めっき抑制膜4および配線膜6がそれぞれ残るように、層間絶縁膜1上の不要なバリアメタル膜2および配線膜6をそれぞれ除去する(ステップ8)。具体的には、ウェハWを研磨パッド(図示せず)に接触させた状態で、ウェハW及び研磨パッドを回転させるとともにウェハW上にスラリ(図示せず)を供給して、配線膜6等を研磨する。なお、CMPで研磨する場合に限らず、その他の手法で研磨してもよい。その他の手法としては、例えば電解研磨が挙げられる。これにより、図4(b)に示されるように凹部1a外の配線膜6等が除去されて、凹部1a内のみに配線膜6等が残存するとともに、めっき抑制膜4の上部が露出する。

【0023】

その後、図4(c)に示されるように例えばCF4等のガスを使用した等方性のドライエッチングによりめっき抑制膜4を選択的に除去する(ステップ9)。めっき抑制膜4が除去されると、その部分は空隙4aとなる。

【0024】

最後に、配線膜6に第2の熱処理を施す(ステップ10)。これにより、配線膜6を構成している金属がストレスマイグレーションにより移動して、空隙4aが埋められる。以上により、図5に示されるように凹部1a内に配線6aが形成される。なお、第1の熱処理を省略した場合には、この第2の熱処理で、シード膜3およびめっき膜5の結晶を成長させる。また、凹部1aがビアホールの場合にはビアが形成され、コンタクトホールである場合にはコンタクトが形成され、配線溝とビアホールとの組み合わせの場合には配線とビアが形成される。

【0025】

本実施の形態によれば、凹部1aの側壁部1cに位置するシード膜3の部分3bをめっき抑制膜4で覆っているので、凹部1aの側壁部1cから凹部1aの中央部に向かう方向の電流が流れ難くなる。したがって、凹部1aの側壁部1c側からはめっきが成長し難くなる。一方、凹部1aの底部1bに位置するシード膜3の部分3aは露出しているので、凹部1aの底部1bから凹部1aの開口面に向かう方向の電流は流れ易い。したがって、凹部1aの底部1b側からはめっきが成長し易い。これにより、確実にめっきをボトムアップ成長させることができるので、ボイドが低減した配線6aを得ることができる。

【0026】

また、本実施の形態によれば、確実にめっきをボトムアップ成長させることができるので、めっき液に含まれる添加剤を低減させることができる。これにより、添加剤の適切な組み合わせや濃度を見付けるという多大な手間を軽減させることができる。

【0027】

さらに、めっき液に含まれる添加剤を低減させた場合には、細幅の配線溝におけるめっきの盛り上がり(ハンプ)を抑制することができる。ここで、現在は、細幅の配線溝においてはハンプが形成されてしまうので、CMPによる研磨を考慮して層間絶縁膜のフィールド部上にもめっき膜を形成している。これに対して、本実施の形態によれば、ハンプを抑制することができ、しかもめっき抑制膜4をフィールド部1d上に残存させた場合には、フィールド部1d上にはめっき膜5がほぼ形成されないので、CMPに要する時間を短縮することができる。

【0028】

また、近年、配線やコンタクト(ビア)が微細化するにつれて、めっきでの埋め込みを可能にするために、凹部の開口をできる限り広く確保する必要がある。そのため、シード膜の膜厚は、ますます薄くなる傾向にある。その場合、凹部の側壁部に存在するシード膜の膜厚は、さらに薄くなってしまい、シード膜の成膜条件やバリアメタル膜との組み合わせによっては、シード膜の凝集およびめっき液との接触初期段階でのシード膜の溶解が生ずるおそれがある。シード膜が凝集、溶解した場合には、その部分にはめっきが成長しないので、結果としてボイドが発生してしまう。これに対し、本実施の形態によれば、凹部1aの側壁部1cに位置するシード膜3の部分3bをめっき抑制膜4で覆っているので、めっき液によるシード膜3の溶解を抑制することができる。これによりボイドの発生をより抑制することができる。さらに、めっき液に対する溶解耐性がCuより大きい材料からめっき抑制膜4を形成した場合には、めっき液によるシード膜3の溶解をさらに抑制することができる。

【0029】

本実施の形態によれば、CMP後、めっき抑制膜4を選択的に除去しているので、配線抵抗の上昇を抑制することができる。すなわち、例えばシード膜3およびめっき膜5がCuから構成されている場合には、めっき抑制膜4は、Cuよりも高い抵抗率を有する材料から構成されているので、配線6a中にめっき抑制膜4が残存していると、配線抵抗が上昇してしまう。これに対し、本実施の形態では、CMP後、めっき抑制膜4を選択的に除去しているので、配線抵抗の上昇を抑制することができる。なお、めっき抑制膜4がRu、Ti、Taまたはこれらの混合物から形成されている場合には、抵抗率が比較的低いので若干配線抵抗は上昇するものの、配線6a中に残存させておくことも可能である。

【0030】

本実施の形態によれば、めっき抑制膜4を絶縁物から構成した場合には、めっき抑制膜4には電流がほぼ流れないので、凹部1aの側壁部1c側からめっきがより成長し難い。

【実施例】

【0031】

以下、実施例について説明する。本実施例1〜3においては、上記実施の形態と同様の手法によりめっき抑制膜を形成した状態で、めっき膜を形成し、そのめっき膜の断面を観察した。なお、本実施例と比較するために、めっき抑制膜を形成せずにめっき膜を形成した比較例1〜4についても、めっき膜の断面を観察した。

【0032】

試料

(実施例1)

実施例1においては、次のような工程で試料を作製した。まず、基板上にCVD法により第1のTEOS膜(層間絶縁膜)を形成し、この第1のTEOS膜にフォトリソグラフィ技術およびRIE等により幅30nmおよび深さ180nmの溝(凹部)を形成した。その後、PVD法によりTaN膜(バリアメタル膜)を7nm形成し、次いでこの上にCuシード膜(シード膜)を15nm形成した。このCuシード膜の膜厚は、ブランケットの状態で成膜したときの膜厚で、溝内ではさらに薄くなっていた。

【0033】

次いで、Cuシード膜上にCVD法によりRu膜(めっき抑制膜)を5nm形成し、異方性のドライエッチングにより第1のTEOS膜のフィールド部と溝の底部のRu膜を除去して、溝の側壁部のRu膜のみを残存させた。そして、この状態で電解めっき法によりCuめっき膜(めっき膜)を溝に埋め込んだ。なお、このめっきの際に使用しためっき液は、硫酸銅水溶液に一般的に用いられているアクセラレータ、サプレッサおよびレベラ等の種々の添加剤を含ませたものであった。

【0034】

(実施例2)

実施例2においては、硫酸銅水溶液に必要最小限の添加剤(いわゆる光沢剤と呼ばれるものの一種)のみしか添加しなかった以外は、実施例1とほぼ同様の手法により試料を作製した。

【0035】

(実施例3)

実施例3においては、Ru膜に代えて第2のTEOS膜(めっき抑制膜)を5nm形成した。その後、同様に異方性エッチングにより第1のTEOS膜のフィールド部と溝の底部に位置する第2のTEOS膜を除去して、溝の側壁部の第2のTEOS膜のみを残存させた。また、めっき後CMPにより不要なCu等を除去した。このとき溝内部に存在する第2のTEOS膜の上部が露出した状態になった。そして、等方性のドライエッチングによりこの第2のTEOS膜を除去し、FG(水素・窒素)雰囲気中で、250℃で1時間の熱処理を施した。その他は、実施例1と同様であった。

【0036】

(比較例1〜4)

比較例1〜4においては、Ru膜を形成せずにCuめっき膜を形成した以外は、実施例1とほぼ同様の手法により試料を作製した。なお、Cuシード膜の膜厚は、比較例1では15nm、比較例2では25nm、比較例3では35nm、比較例4では45nmであった。

【0037】

観察

このような試料を用いて、めっき膜の断面を観察した。以下、結果について述べる。比較例1〜4においては、全てにおいてボイドが観察された。これは、Cuシード膜の膜厚が厚くなるにしたがって、めっき液によるCuシード膜の溶解が緩和するが、逆に膜厚が厚くなると、Cuめっき膜形成前の溝の開口幅が狭くなることで、溝内部が全て埋め込まれる前に、溝の側壁部側からのめっきの成長によって開口が塞がってしまうためであると考えられる。これに対し、実施例1〜3においては、ボイドは観察されなかった。なお、実施例3においては、第2のTEOS膜を除去することにより形成された空隙は熱処理後においては観察されなかった。これらの結果から、めっき抑制膜を形成した場合には、ボイドが低減することが確認された。

【0038】

なお、本発明は上記実施の形態の記載内容に限定されるものではなく、構造や材質、各部材の配置等は、本発明の要旨を逸脱しない範囲で適宜変更することが可能である。

【図面の簡単な説明】

【0039】

【図1】実施の形態に係る半導体装置の製造プロセスの流れを示したフローチャートである。

【図2】実施の形態に係る半導体装置の模式的な製造プロセス図である。

【図3】実施の形態に係る半導体装置の模式的な製造プロセス図である。

【図4】実施の形態に係る半導体装置の模式的な製造プロセス図である。

【図5】実施の形態に係る半導体装置の模式的な製造プロセス図である。

【符号の説明】

【0040】

W…ウェハ、1…層間絶縁膜、1a…凹部、1b…底部、1c…側壁部、2…バリアメタル膜、3…シード膜、4…めっき抑制膜、5…めっき膜、6a…配線。

【特許請求の範囲】

【請求項1】

表面に凹部を有する基板の少なくとも前記凹部の底部および側壁部に、シード膜を形成する工程と、

前記シード膜上に、少なくとも前記凹部の底部に位置する前記シード膜の部分が露出しかつ前記凹部の側壁部に位置する前記シード膜の部分を覆うようにめっき抑制膜を形成する工程と、

前記シード膜に電流を供給して、前記めっき抑制膜の形成された前記凹部に埋め込まれるように電解めっき法によりめっき膜を形成する工程と、

前記めっき膜に熱処理を施す工程と

を備え、前記めっき抑制膜が、前記シード膜の構成材料より抵抗率が高くかつ前記めっき膜の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法。

【請求項2】

前記シード膜の構成材料がCuであり、かつ前記めっき抑制膜が前記めっき膜の形成で使用されるめっき液に対してCuよりも溶解耐性が大きい材料から構成される、請求項1項に記載の半導体装置の製造方法。

【請求項3】

前記シード膜の構成材料がCuであり、かつ前記めっき抑制膜がRu、TiおよびTaからなる群から選択される1以上の材料、あるいは絶縁物から構成される、請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記めっき抑制膜が、前記凹部の側壁部に位置する前記シード膜の部分のみを覆うように形成される、請求項1ないし3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記めっき膜を形成する工程で前記凹部外に形成されためっき膜を除去した後、前記めっき抑制膜を選択的に除去する工程をさらに備え、前記めっき膜に熱処理を施す工程の少なくとも一部を、前記めっき抑制膜を選択的に除去する工程の後に行う、請求項1ないし4のいずれか1項に記載の半導体装置の製造方法。

【請求項1】

表面に凹部を有する基板の少なくとも前記凹部の底部および側壁部に、シード膜を形成する工程と、

前記シード膜上に、少なくとも前記凹部の底部に位置する前記シード膜の部分が露出しかつ前記凹部の側壁部に位置する前記シード膜の部分を覆うようにめっき抑制膜を形成する工程と、

前記シード膜に電流を供給して、前記めっき抑制膜の形成された前記凹部に埋め込まれるように電解めっき法によりめっき膜を形成する工程と、

前記めっき膜に熱処理を施す工程と

を備え、前記めっき抑制膜が、前記シード膜の構成材料より抵抗率が高くかつ前記めっき膜の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法。

【請求項2】

前記シード膜の構成材料がCuであり、かつ前記めっき抑制膜が前記めっき膜の形成で使用されるめっき液に対してCuよりも溶解耐性が大きい材料から構成される、請求項1項に記載の半導体装置の製造方法。

【請求項3】

前記シード膜の構成材料がCuであり、かつ前記めっき抑制膜がRu、TiおよびTaからなる群から選択される1以上の材料、あるいは絶縁物から構成される、請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記めっき抑制膜が、前記凹部の側壁部に位置する前記シード膜の部分のみを覆うように形成される、請求項1ないし3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記めっき膜を形成する工程で前記凹部外に形成されためっき膜を除去した後、前記めっき抑制膜を選択的に除去する工程をさらに備え、前記めっき膜に熱処理を施す工程の少なくとも一部を、前記めっき抑制膜を選択的に除去する工程の後に行う、請求項1ないし4のいずれか1項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2010−80525(P2010−80525A)

【公開日】平成22年4月8日(2010.4.8)

【国際特許分類】

【出願番号】特願2008−244600(P2008−244600)

【出願日】平成20年9月24日(2008.9.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成22年4月8日(2010.4.8)

【国際特許分類】

【出願日】平成20年9月24日(2008.9.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]