半導体装置の製造方法

【課題】生産性を極端に落とすことなく、開口の形状悪化を抑止するエッチング方法を提供する。

【解決手段】半導体基板1上に絶縁層2を介して形成されたパッド電極3を被覆するように前記半導体基板1の表面に支持体5を接着する工程と、前記半導体基板1の裏面から前記パッド電極3の表面に到達するようにビアホールを形成する工程とを有するものにおいて、前記半導体基板1に対して前記絶縁層2が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板1に対して前記絶縁層2が露出する位置まで第2の開口8を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第2のエッチング工程は前記第1のエッチング工程よりも前記半導体基板に印加される交流電圧の周波数を低くする。

【解決手段】半導体基板1上に絶縁層2を介して形成されたパッド電極3を被覆するように前記半導体基板1の表面に支持体5を接着する工程と、前記半導体基板1の裏面から前記パッド電極3の表面に到達するようにビアホールを形成する工程とを有するものにおいて、前記半導体基板1に対して前記絶縁層2が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板1に対して前記絶縁層2が露出する位置まで第2の開口8を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第2のエッチング工程は前記第1のエッチング工程よりも前記半導体基板に印加される交流電圧の周波数を低くする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に半導体基板に形成するビアホールの形状悪化を抑止するエッチング方法に関する。

【背景技術】

【0002】

近年、三次元実装技術として、また新たなパッケージ技術として、CSP(Chip Size Package)が注目されている。CSPとは、半導体チップの外形寸法と略同サイズの外形寸法を有する小型パッケージをいう。

【0003】

従来より、CSPの一種として、BGA(Ball Grid Array)型の半導体装置が知られている。このBGA型の半導体装置は、半田等の金属部材からなるボール状の導電端子をパッケージの一主面上に格子状に複数配列し、パッケージの他の面上に搭載される半導体チップと電気的に接続したものである。

【0004】

そして、このBGA型の半導体装置を電子機器に組み込む際には、各導電端子をプリント基板上の配線パターンに圧着することで、半導体チップとプリント基板上に搭載される外部回路とを電気的に接続している。

【0005】

このようなBGA型の半導体装置は、側部に突出したリードピンを有するSOP(Small Outline Package)やQFP(Quad Flat Package)等の他のCSP型の半導体装置に比べて、多数の導電端子を設けることが出来、しかも小型化できるという長所を有する。このBGA型の半導体装置は、例えば携帯電話機に搭載されるデジタルカメラのイメージセンサチップとしての用途がある。この一例として、半導体チップの一主面上もしくは両主面上に、例えばガラスから成る支持体が接着されるものがある。尚、関連する技術文献として、以下の特許文献1が挙げられる。

【0006】

次に、半導体チップに1枚の支持体が接着された場合のBGA型の半導体装置の製造方法について、図面を参照して説明する。

【0007】

図7乃至図9は、イメージセンサチップに適用可能な従来例に係るBGA型の半導体装置の製造方法を示す断面図である。

【0008】

最初に図7に示すように半導体基板30上の表面に、シリコン酸化膜31またはシリコン窒化膜を介してアルミニウム層もしくはアルミニウム合金層から成るパッド電極32を形成する。そして、パッド電極32を含む半導体基板30上にエポキシ樹脂層から成る接着剤33を介して、例えばガラスから成る支持体34を接着する。

【0009】

次に、図8に示すようにパッド電極32に対応する半導体基板30の裏面に開口部を有したレジスト層35を形成し、これをマスクにしてドライエッチングを半導体基板30に対して行い、更にシリコン酸化膜31をエッチングして半導体基板30の裏面からパッド電極32に到達するビアホール36を形成する。本工程では、Siウエハから成る半導体基板30に対して、例えば、130μmの深さの開口を穿設するために比較的処理スピードの速いエッチング方法を採用している(例えば、エッチングレートが10μm/分)。

【0010】

そして、図9に示すようにビアホール36内を含む半導体基板30の裏面に、少なくともパッド電極32の表面が露出された絶縁層(図示せず)を介してバリア層37を形成する。さらに、バリア層37上に、メッキ用のシード層38を形成し、そのシード層38上でメッキ処理を行って、例えば銅(Cu)から成る再配線層39を形成する。さらに、再配線層39上に保護層(図示せず)を形成し、保護層の所定位置に開口を設けて再配線層39とコンタクトするボール状端子40を形成する。

【0011】

その後、図示しないが、半導体基板及びそれに積層された上記各層を切断して、個々の半導体チップに分離する。こうして、パッド電極32とボール状端子40とが電気的に接続されたBGA型の半導体装置が形成される。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特許公表2002−512436号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかし、上記ビアホール36の形成工程において、開口の形状が悪化するといった問題があった。即ち、図8に示した工程において、実際には図10に示すようなエッチング形状となっていた。即ち、半導体基板30上にシリコン酸化膜31またはシリコン窒化膜を介してパッド電極32が形成されており、半導体基板31の裏面からパッド電極32へエッチングでビアホール36を形成する際に、図10に示すようにビアホールの底部では前記シリコン酸化膜31またはシリコン窒化膜でエッチングが止まり、オーバーエッチングさせた際に横方向へのエッチング(ノッチ)が発生し、開口形状が悪化する。このノッチにより、前記パッド電極32の上面からはみ出すようにシリコン酸化膜31またはシリコン窒化膜が除去されることがあった。また、そのような形状のビアホール36aに対して絶縁層や再配線層を形成する場合の付き回りが悪くなり、導通不良を起こしたり、パッド電極との接続信頼性の低下等を引き起こすおそれがあった。

【0014】

なお、上述したようなノッチができないエッチング方法もあるが、処理スピードが極端に遅いという欠点があり(例えば、エッチングレートが5μm/分以下、場合によっては2〜1μm/分)、生産性が悪く採用できなかった。

【0015】

そこで、生産性を極端に落とすことなく、開口の形状悪化を抑止するエッチング方法を提供することを目的とする。

【課題を解決するための手段】

【0016】

そこで本発明の半導体装置の製造方法は、半導体基板上に絶縁層を介して形成されたパッド電極を被覆するように前記半導体基板の表面に支持体を接着する工程と、前記半導体基板の裏面から前記パッド電極の表面に到達するようにビアホールを形成する工程とを有するものにおいて、前記半導体基板に対して前記絶縁層が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板に対して前記絶縁層が露出する位置まで第2の開口を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第2のエッチング工程は前記第1のエッチング工程よりも前記半導体基板に印加される交流電圧の周波数が低いことを特徴とする。

【0017】

また、本発明の半導体装置の製造方法は、半導体基板上に絶縁層を介して形成されたパッド電極を被覆するように前記半導体基板の表面に支持体を接着する工程と、前記半導体基板の裏面から前記パッド電極の表面に到達するようにビアホールを形成する工程とを有する半導体装置の製造方法において、前記半導体基板に対して前記絶縁層が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板に対して前記絶縁層が露出する位置まで第2の開口を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第1及び第2のエッチング工程において、前記半導体基板に交流電圧が印加され、前記第2のエッチング工程における交流電圧の印加時間は前記第1のエッチング工程における交流電圧の印加時間に比して短いことを特徴とする。

【0018】

更に、前記第1及び第2の開口から露出した前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程を具備することを特徴とする。

【0019】

また、前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程は、前記半導体基板をエッチングする際に用いたレジスト層をマスクにして前記絶縁層をエッチングすることを特徴とする。

【0020】

更に、前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程は、前記レジスト層をマスクとして用いないエッチング工程であることを特徴とする。

【0021】

また、前記ビアホールに埋め込まれ前記パッド電極に接続される柱状端子を形成する工程を具備することを特徴とする。

【0022】

更に、前記柱状端子に接続されるボール状端子を形成する工程を具備することを特徴とする。

【0023】

また、前記柱状端子から前記半導体基板の裏面に延在し、前記柱状端子と前記ボール状端子を接続する再配線層を形成する工程を具備することを特徴とする。

【0024】

更に、前記半導体基板を複数の半導体チップに分割する工程を具備することを特徴とする。

【発明の効果】

【0025】

本発明によれば、ビアホールの形成時のSiウエハから成る半導体基板に開口を形成する際に、異なるエッチングガスに切り替えているため、極端に作業性を落とすことなく、開口形状が良好なビアホールを形成することができる。

【図面の簡単な説明】

【0026】

【図1】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図2】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図3】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図4】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図5】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図6】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】従来の半導体装置の製造方法を示す断面図である。

【図8】従来の半導体装置の製造方法を示す断面図である。

【図9】従来の半導体装置の製造方法を示す断面図である。

【図10】従来の半導体装置の製造方法の問題点を説明するための図である。

【発明を実施するための最良の形態】

【0027】

次に、本発明による半導体装置の製造方法を、図1乃至図6を参照しながら説明する。

【0028】

図1乃至図6は、イメージセンサチップに適用可能なBGA型の半導体装置の製造方法を示す断面図である。

【0029】

最初に、図1に示すように、例えばSiウエハから成る半導体基板1上の表面に、例えばシリコン酸化膜またはシリコン窒化膜等から成る絶縁層2を介してアルミニウム層もしくはアルミニウム合金層から成るパッド電極3を形成する。尚、前記パッド電極3を含む半導体基板1上は、シリコン酸化膜やシリコン窒化膜等から成るパッシベーション膜(図示せず)で被覆されている。そして、パッド電極3を含む半導体基板1上にエポキシ樹脂層から成る接着剤4を介して、例えばガラス板から成る支持体5を接着する。尚、前記支持体5は、ガラスに限定されるものではなく、例えばテープ形状のものでも良い。

【0030】

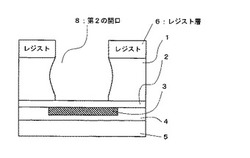

次に、パッド電極3に対応する半導体基板1の裏面に開口部を有したレジスト層6を形成し、これをマスクにしてドライエッチングを半導体基板1に対して行い、半導体基板1の裏面からパッド電極3に到達するビアホール9を形成する。

【0031】

先ず第1に、図2に示すように開口の所定深さ位置まで第1のエッチング方法により高速なエッチングを行う。本工程では、少なくともSF6とO2ガス等を含むエッチングガスを用いて、例えば全体で深さ130μmの開口を形成する場合において、この第1のエッチングにより120μmの深さの第1の開口7を形成する。この工程でのエッチングレートは、例えば10μm/分程度である。尚、図2では第1の開口7が、いわゆる樽状に横に広がるように形成されているが、ストレート形状をしていても構わない。

【0032】

続いて、図3に示すように、前記開口の残りの深さ位置まで第2のエッチング方法を行う。本工程では、少なくともSF6とCF(フッ化炭素)系ガス(例えば、C2F4、C4F8、CHF3等)を含むエッチングガスを用いて第1の開口7下に残り10μmの深さで開口された第2の開口8を形成する。この工程でのエッチングレートは、例えば5μm/分程度、場合によっては2〜1μm/分である。尚、第1、第2のエッチングガスとも、例えばAr等の希釈ガス等が含まれていても良い。

【0033】

従って、本実施形態では、全体で130μmの深さを有する開口をSiウエハに形成するために2つの工程を有し、エッチングレートの高いエッチング条件で第1のエッチングを行って第1の開口7を形成し、続いてエッチングレートの低いエッチング条件で第2のエッチングを行って第2の開口8を形成することで、極端に作業時間が長くなるといった問題が抑止される。尚、本実施形態では同一チャンバー内に供給するエッチングガスを切り替えることで、上記開口を形成しているが、本発明はこれに限定されることなく、例えば複数のチャンバーを備えた同一装置内で行われても良く、またエッチング工程毎に、別の装置に切り替えるものであっても構わない。

【0034】

そして、図4に示すようにパッド電極3上の絶縁層2を例えばCHF3やCF4等のエッチングガスを用いてエッチング除去してパッド電極3を露出させるビアホール9を形成する。尚、前記エッチングガスは、例えばAr等の希釈ガス等が含まれていても良い。また、ウェットエッチング法を用いても良い。

【0035】

また、前記絶縁層2をエッチング除去する工程は、前記半導体基板1上に形成されたレジスト層6をマスクにして前記パッド電極3上の絶縁層2を除去するものであってもよく、更には、前記レジスト層6をマスクとしないエッチング工程であっても良い。即ち、レジスト層6を除去した後に、半導体基板1をマスクとしてパッド電極3上の絶縁層2を除去する。

【0036】

以下、図5に示すようにビアホール9内を含む半導体基板1の裏面に酸化膜等から成る絶縁層(図示せず)を形成し、パッド電極3上の絶縁層を除去した後に、全面にバリア層10を形成する。このバリア層10は、例えばチタンナイトライド(TiN)層であることが好ましく、チタン(Ti)やタンタル(Ta)等の高融点金属やその化合物であるチタンタングステン(TiW)層、タンタルナイトライド(TaN)層等であればチタンナイトライド層以外の金属から成るものであってもよい。

【0037】

さらに、図6に示すようにバリア層10上にメッキ用のシード層11(例えば、Cu層)を形成し、そのシード層11上でメッキ処理を行って、例えば銅(Cu)から成る再配線層12を形成する。なお、この再配線層12はパターニングしても良いし、パターニングしないものでも良い。さらに、再配線層12上に保護層(図示せず)を形成し、保護層の所定位置に開口を設けて再配線層12とコンタクトするボール状端子13を形成する。

【0038】

尚、ここで、前記バリア層10やシード層11の形成法として、MOCVD法で形成することができるが、この場合、コスト高になるという問題があった。そこで、それよりも低コストであるロングスロースパッタ法等の指向性スパッタ法を用いることで、通常のスパッタ法に比べて被覆性を向上させることができる。この指向性スパッタ法を用いることで、例えば傾斜角度が90度未満であるとか、アスペクト比が3以上のビアホールに対しても被覆性良く、前記バリア層10やシード層11を形成することができる。

【0039】

その後、図示しないが、半導体基板及びそれに積層された上記各層を切断して、個々の半導体チップに分離する。こうして、パッド電極3とボール状端子13とが電気的に接続されたBGA型の半導体装置が形成される。

【0040】

このように本発明では、従来のように開口底部での横方向へのエッチング(ノッチ)が発生しないため、ビアホール内への絶縁層、バリア層、シード層及び再配線層の付き回りが悪くなるといった問題の発生を抑止でき、導通不良を起こしたり、パッド電極との接続信頼性の低下等を引き起こすことがなくなる。

【0041】

また、本実施形態では、エッチングガスを変更することで第1の開口7と第2の開口8を形成しているが、本発明はこれに限定されず、例えば第1の開口7を形成する第1のエッチング工程と、第2の開口8を形成する第2のエッチング工程を比較して、前記第2のエッチング工程は前記第1のエッチング工程よりも半導体基板1に印加される交流電圧の周波数が低い条件を用いるようにしても良い。

【0042】

第1及び第2のエッチング工程において、ドライエッチング装置として、例えば誘導結合型エッチング装置(Inductively Coupled Plasma Etching Machine)が用いられる。半導体基板1は交流電源からの交流電圧が印加されたテーブル上に載置される。この交流電圧の周波数を第1のエッチング工程では、13.56MHzとし、第2のエッチング工程では400KHzに低減することでエッチングレートが低減され、従来のようなノッチの発生を抑止できる。

【0043】

また、上述のように交流電圧の周波数を変更する代わりに、前記第2のエッチング工程における交流電圧の印加時間を前記第1のエッチング工程における交流電圧の印加時間に比して短くしても、ノッチ発生を防止できる。具体的には、第1及び第2のエッチング工程では交流電源を間欠的にオンするように制御することにより、交流電圧が間欠的に半導体基板1に印加される。即ち、交流電源がオンしている期間は交流電圧が半導体基板1に印加されることにより、エッチング装置内にプラズマが発生する。交流電源がオフしている期間は交流電圧が半導体基板1に印加されず、プラズマの発生が停止する。交流電源のオンオフ制御は周期的に繰り返される。例えば、第1のエッチング工程における交流電圧の印加時間を100%とすると、第2のエッチング工程における交流電圧の印加時間は10%と短く設定する。これにより、第2のエッチング工程は第1のエッチング工程に比してエッチングレートが低減されるので、従来のようなノッチの発生を抑止できる。

【0044】

この第2,第3の実施形態では第1,2のエッチング工程でエッチングガスを変更していないが、エッチングガスの変更と併せて、交流電圧の周波数を変更し、あるいは交流電圧の印加時間を調整するようにしても良い。

【0045】

尚、本実施形態では、再配線層12はメッキ処理により形成されるものとしたが、本発明はこれに制限されるものではなく、例えばメッキ用のシード層11を形成しないで、メッキ処理以外の方法により再配線層12が形成されるものであってもよい。例えば、アルミニウムやその合金から成る層をスパッタ形成するものでもよい。

【0046】

また、本実施形態はボール状端子13が形成された半導体装置に適用されるものとして説明しているが、本発明これに制限されるものではなく、例えば半導体基板を貫通するビアホールが形成されるものであれば、ボール状端子が形成されない半導体装置にも適用できるもので、例えばLGA(Land Grid Array)型の半導体装置にも適用される。

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に半導体基板に形成するビアホールの形状悪化を抑止するエッチング方法に関する。

【背景技術】

【0002】

近年、三次元実装技術として、また新たなパッケージ技術として、CSP(Chip Size Package)が注目されている。CSPとは、半導体チップの外形寸法と略同サイズの外形寸法を有する小型パッケージをいう。

【0003】

従来より、CSPの一種として、BGA(Ball Grid Array)型の半導体装置が知られている。このBGA型の半導体装置は、半田等の金属部材からなるボール状の導電端子をパッケージの一主面上に格子状に複数配列し、パッケージの他の面上に搭載される半導体チップと電気的に接続したものである。

【0004】

そして、このBGA型の半導体装置を電子機器に組み込む際には、各導電端子をプリント基板上の配線パターンに圧着することで、半導体チップとプリント基板上に搭載される外部回路とを電気的に接続している。

【0005】

このようなBGA型の半導体装置は、側部に突出したリードピンを有するSOP(Small Outline Package)やQFP(Quad Flat Package)等の他のCSP型の半導体装置に比べて、多数の導電端子を設けることが出来、しかも小型化できるという長所を有する。このBGA型の半導体装置は、例えば携帯電話機に搭載されるデジタルカメラのイメージセンサチップとしての用途がある。この一例として、半導体チップの一主面上もしくは両主面上に、例えばガラスから成る支持体が接着されるものがある。尚、関連する技術文献として、以下の特許文献1が挙げられる。

【0006】

次に、半導体チップに1枚の支持体が接着された場合のBGA型の半導体装置の製造方法について、図面を参照して説明する。

【0007】

図7乃至図9は、イメージセンサチップに適用可能な従来例に係るBGA型の半導体装置の製造方法を示す断面図である。

【0008】

最初に図7に示すように半導体基板30上の表面に、シリコン酸化膜31またはシリコン窒化膜を介してアルミニウム層もしくはアルミニウム合金層から成るパッド電極32を形成する。そして、パッド電極32を含む半導体基板30上にエポキシ樹脂層から成る接着剤33を介して、例えばガラスから成る支持体34を接着する。

【0009】

次に、図8に示すようにパッド電極32に対応する半導体基板30の裏面に開口部を有したレジスト層35を形成し、これをマスクにしてドライエッチングを半導体基板30に対して行い、更にシリコン酸化膜31をエッチングして半導体基板30の裏面からパッド電極32に到達するビアホール36を形成する。本工程では、Siウエハから成る半導体基板30に対して、例えば、130μmの深さの開口を穿設するために比較的処理スピードの速いエッチング方法を採用している(例えば、エッチングレートが10μm/分)。

【0010】

そして、図9に示すようにビアホール36内を含む半導体基板30の裏面に、少なくともパッド電極32の表面が露出された絶縁層(図示せず)を介してバリア層37を形成する。さらに、バリア層37上に、メッキ用のシード層38を形成し、そのシード層38上でメッキ処理を行って、例えば銅(Cu)から成る再配線層39を形成する。さらに、再配線層39上に保護層(図示せず)を形成し、保護層の所定位置に開口を設けて再配線層39とコンタクトするボール状端子40を形成する。

【0011】

その後、図示しないが、半導体基板及びそれに積層された上記各層を切断して、個々の半導体チップに分離する。こうして、パッド電極32とボール状端子40とが電気的に接続されたBGA型の半導体装置が形成される。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特許公表2002−512436号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかし、上記ビアホール36の形成工程において、開口の形状が悪化するといった問題があった。即ち、図8に示した工程において、実際には図10に示すようなエッチング形状となっていた。即ち、半導体基板30上にシリコン酸化膜31またはシリコン窒化膜を介してパッド電極32が形成されており、半導体基板31の裏面からパッド電極32へエッチングでビアホール36を形成する際に、図10に示すようにビアホールの底部では前記シリコン酸化膜31またはシリコン窒化膜でエッチングが止まり、オーバーエッチングさせた際に横方向へのエッチング(ノッチ)が発生し、開口形状が悪化する。このノッチにより、前記パッド電極32の上面からはみ出すようにシリコン酸化膜31またはシリコン窒化膜が除去されることがあった。また、そのような形状のビアホール36aに対して絶縁層や再配線層を形成する場合の付き回りが悪くなり、導通不良を起こしたり、パッド電極との接続信頼性の低下等を引き起こすおそれがあった。

【0014】

なお、上述したようなノッチができないエッチング方法もあるが、処理スピードが極端に遅いという欠点があり(例えば、エッチングレートが5μm/分以下、場合によっては2〜1μm/分)、生産性が悪く採用できなかった。

【0015】

そこで、生産性を極端に落とすことなく、開口の形状悪化を抑止するエッチング方法を提供することを目的とする。

【課題を解決するための手段】

【0016】

そこで本発明の半導体装置の製造方法は、半導体基板上に絶縁層を介して形成されたパッド電極を被覆するように前記半導体基板の表面に支持体を接着する工程と、前記半導体基板の裏面から前記パッド電極の表面に到達するようにビアホールを形成する工程とを有するものにおいて、前記半導体基板に対して前記絶縁層が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板に対して前記絶縁層が露出する位置まで第2の開口を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第2のエッチング工程は前記第1のエッチング工程よりも前記半導体基板に印加される交流電圧の周波数が低いことを特徴とする。

【0017】

また、本発明の半導体装置の製造方法は、半導体基板上に絶縁層を介して形成されたパッド電極を被覆するように前記半導体基板の表面に支持体を接着する工程と、前記半導体基板の裏面から前記パッド電極の表面に到達するようにビアホールを形成する工程とを有する半導体装置の製造方法において、前記半導体基板に対して前記絶縁層が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板に対して前記絶縁層が露出する位置まで第2の開口を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第1及び第2のエッチング工程において、前記半導体基板に交流電圧が印加され、前記第2のエッチング工程における交流電圧の印加時間は前記第1のエッチング工程における交流電圧の印加時間に比して短いことを特徴とする。

【0018】

更に、前記第1及び第2の開口から露出した前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程を具備することを特徴とする。

【0019】

また、前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程は、前記半導体基板をエッチングする際に用いたレジスト層をマスクにして前記絶縁層をエッチングすることを特徴とする。

【0020】

更に、前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程は、前記レジスト層をマスクとして用いないエッチング工程であることを特徴とする。

【0021】

また、前記ビアホールに埋め込まれ前記パッド電極に接続される柱状端子を形成する工程を具備することを特徴とする。

【0022】

更に、前記柱状端子に接続されるボール状端子を形成する工程を具備することを特徴とする。

【0023】

また、前記柱状端子から前記半導体基板の裏面に延在し、前記柱状端子と前記ボール状端子を接続する再配線層を形成する工程を具備することを特徴とする。

【0024】

更に、前記半導体基板を複数の半導体チップに分割する工程を具備することを特徴とする。

【発明の効果】

【0025】

本発明によれば、ビアホールの形成時のSiウエハから成る半導体基板に開口を形成する際に、異なるエッチングガスに切り替えているため、極端に作業性を落とすことなく、開口形状が良好なビアホールを形成することができる。

【図面の簡単な説明】

【0026】

【図1】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図2】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図3】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図4】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図5】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図6】本発明の実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】従来の半導体装置の製造方法を示す断面図である。

【図8】従来の半導体装置の製造方法を示す断面図である。

【図9】従来の半導体装置の製造方法を示す断面図である。

【図10】従来の半導体装置の製造方法の問題点を説明するための図である。

【発明を実施するための最良の形態】

【0027】

次に、本発明による半導体装置の製造方法を、図1乃至図6を参照しながら説明する。

【0028】

図1乃至図6は、イメージセンサチップに適用可能なBGA型の半導体装置の製造方法を示す断面図である。

【0029】

最初に、図1に示すように、例えばSiウエハから成る半導体基板1上の表面に、例えばシリコン酸化膜またはシリコン窒化膜等から成る絶縁層2を介してアルミニウム層もしくはアルミニウム合金層から成るパッド電極3を形成する。尚、前記パッド電極3を含む半導体基板1上は、シリコン酸化膜やシリコン窒化膜等から成るパッシベーション膜(図示せず)で被覆されている。そして、パッド電極3を含む半導体基板1上にエポキシ樹脂層から成る接着剤4を介して、例えばガラス板から成る支持体5を接着する。尚、前記支持体5は、ガラスに限定されるものではなく、例えばテープ形状のものでも良い。

【0030】

次に、パッド電極3に対応する半導体基板1の裏面に開口部を有したレジスト層6を形成し、これをマスクにしてドライエッチングを半導体基板1に対して行い、半導体基板1の裏面からパッド電極3に到達するビアホール9を形成する。

【0031】

先ず第1に、図2に示すように開口の所定深さ位置まで第1のエッチング方法により高速なエッチングを行う。本工程では、少なくともSF6とO2ガス等を含むエッチングガスを用いて、例えば全体で深さ130μmの開口を形成する場合において、この第1のエッチングにより120μmの深さの第1の開口7を形成する。この工程でのエッチングレートは、例えば10μm/分程度である。尚、図2では第1の開口7が、いわゆる樽状に横に広がるように形成されているが、ストレート形状をしていても構わない。

【0032】

続いて、図3に示すように、前記開口の残りの深さ位置まで第2のエッチング方法を行う。本工程では、少なくともSF6とCF(フッ化炭素)系ガス(例えば、C2F4、C4F8、CHF3等)を含むエッチングガスを用いて第1の開口7下に残り10μmの深さで開口された第2の開口8を形成する。この工程でのエッチングレートは、例えば5μm/分程度、場合によっては2〜1μm/分である。尚、第1、第2のエッチングガスとも、例えばAr等の希釈ガス等が含まれていても良い。

【0033】

従って、本実施形態では、全体で130μmの深さを有する開口をSiウエハに形成するために2つの工程を有し、エッチングレートの高いエッチング条件で第1のエッチングを行って第1の開口7を形成し、続いてエッチングレートの低いエッチング条件で第2のエッチングを行って第2の開口8を形成することで、極端に作業時間が長くなるといった問題が抑止される。尚、本実施形態では同一チャンバー内に供給するエッチングガスを切り替えることで、上記開口を形成しているが、本発明はこれに限定されることなく、例えば複数のチャンバーを備えた同一装置内で行われても良く、またエッチング工程毎に、別の装置に切り替えるものであっても構わない。

【0034】

そして、図4に示すようにパッド電極3上の絶縁層2を例えばCHF3やCF4等のエッチングガスを用いてエッチング除去してパッド電極3を露出させるビアホール9を形成する。尚、前記エッチングガスは、例えばAr等の希釈ガス等が含まれていても良い。また、ウェットエッチング法を用いても良い。

【0035】

また、前記絶縁層2をエッチング除去する工程は、前記半導体基板1上に形成されたレジスト層6をマスクにして前記パッド電極3上の絶縁層2を除去するものであってもよく、更には、前記レジスト層6をマスクとしないエッチング工程であっても良い。即ち、レジスト層6を除去した後に、半導体基板1をマスクとしてパッド電極3上の絶縁層2を除去する。

【0036】

以下、図5に示すようにビアホール9内を含む半導体基板1の裏面に酸化膜等から成る絶縁層(図示せず)を形成し、パッド電極3上の絶縁層を除去した後に、全面にバリア層10を形成する。このバリア層10は、例えばチタンナイトライド(TiN)層であることが好ましく、チタン(Ti)やタンタル(Ta)等の高融点金属やその化合物であるチタンタングステン(TiW)層、タンタルナイトライド(TaN)層等であればチタンナイトライド層以外の金属から成るものであってもよい。

【0037】

さらに、図6に示すようにバリア層10上にメッキ用のシード層11(例えば、Cu層)を形成し、そのシード層11上でメッキ処理を行って、例えば銅(Cu)から成る再配線層12を形成する。なお、この再配線層12はパターニングしても良いし、パターニングしないものでも良い。さらに、再配線層12上に保護層(図示せず)を形成し、保護層の所定位置に開口を設けて再配線層12とコンタクトするボール状端子13を形成する。

【0038】

尚、ここで、前記バリア層10やシード層11の形成法として、MOCVD法で形成することができるが、この場合、コスト高になるという問題があった。そこで、それよりも低コストであるロングスロースパッタ法等の指向性スパッタ法を用いることで、通常のスパッタ法に比べて被覆性を向上させることができる。この指向性スパッタ法を用いることで、例えば傾斜角度が90度未満であるとか、アスペクト比が3以上のビアホールに対しても被覆性良く、前記バリア層10やシード層11を形成することができる。

【0039】

その後、図示しないが、半導体基板及びそれに積層された上記各層を切断して、個々の半導体チップに分離する。こうして、パッド電極3とボール状端子13とが電気的に接続されたBGA型の半導体装置が形成される。

【0040】

このように本発明では、従来のように開口底部での横方向へのエッチング(ノッチ)が発生しないため、ビアホール内への絶縁層、バリア層、シード層及び再配線層の付き回りが悪くなるといった問題の発生を抑止でき、導通不良を起こしたり、パッド電極との接続信頼性の低下等を引き起こすことがなくなる。

【0041】

また、本実施形態では、エッチングガスを変更することで第1の開口7と第2の開口8を形成しているが、本発明はこれに限定されず、例えば第1の開口7を形成する第1のエッチング工程と、第2の開口8を形成する第2のエッチング工程を比較して、前記第2のエッチング工程は前記第1のエッチング工程よりも半導体基板1に印加される交流電圧の周波数が低い条件を用いるようにしても良い。

【0042】

第1及び第2のエッチング工程において、ドライエッチング装置として、例えば誘導結合型エッチング装置(Inductively Coupled Plasma Etching Machine)が用いられる。半導体基板1は交流電源からの交流電圧が印加されたテーブル上に載置される。この交流電圧の周波数を第1のエッチング工程では、13.56MHzとし、第2のエッチング工程では400KHzに低減することでエッチングレートが低減され、従来のようなノッチの発生を抑止できる。

【0043】

また、上述のように交流電圧の周波数を変更する代わりに、前記第2のエッチング工程における交流電圧の印加時間を前記第1のエッチング工程における交流電圧の印加時間に比して短くしても、ノッチ発生を防止できる。具体的には、第1及び第2のエッチング工程では交流電源を間欠的にオンするように制御することにより、交流電圧が間欠的に半導体基板1に印加される。即ち、交流電源がオンしている期間は交流電圧が半導体基板1に印加されることにより、エッチング装置内にプラズマが発生する。交流電源がオフしている期間は交流電圧が半導体基板1に印加されず、プラズマの発生が停止する。交流電源のオンオフ制御は周期的に繰り返される。例えば、第1のエッチング工程における交流電圧の印加時間を100%とすると、第2のエッチング工程における交流電圧の印加時間は10%と短く設定する。これにより、第2のエッチング工程は第1のエッチング工程に比してエッチングレートが低減されるので、従来のようなノッチの発生を抑止できる。

【0044】

この第2,第3の実施形態では第1,2のエッチング工程でエッチングガスを変更していないが、エッチングガスの変更と併せて、交流電圧の周波数を変更し、あるいは交流電圧の印加時間を調整するようにしても良い。

【0045】

尚、本実施形態では、再配線層12はメッキ処理により形成されるものとしたが、本発明はこれに制限されるものではなく、例えばメッキ用のシード層11を形成しないで、メッキ処理以外の方法により再配線層12が形成されるものであってもよい。例えば、アルミニウムやその合金から成る層をスパッタ形成するものでもよい。

【0046】

また、本実施形態はボール状端子13が形成された半導体装置に適用されるものとして説明しているが、本発明これに制限されるものではなく、例えば半導体基板を貫通するビアホールが形成されるものであれば、ボール状端子が形成されない半導体装置にも適用できるもので、例えばLGA(Land Grid Array)型の半導体装置にも適用される。

【特許請求の範囲】

【請求項1】

半導体基板上に絶縁層を介して形成されたパッド電極を被覆するように前記半導体基板の表面に支持体を接着する工程と、前記半導体基板の裏面から前記パッド電極の表面に到達するようにビアホールを形成する工程とを有する半導体装置の製造方法において、

前記半導体基板に対して前記絶縁層が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板に対して前記絶縁層が露出する位置まで第2の開口を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第2のエッチング工程は前記第1のエッチング工程よりも前記半導体基板に印加される交流電圧の周波数が低いことを特徴とする半導体装置の製造方法。

【請求項2】

半導体基板上に絶縁層を介して形成されたパッド電極を被覆するように前記半導体基板の表面に支持体を接着する工程と、前記半導体基板の裏面から前記パッド電極の表面に到達するようにビアホールを形成する工程とを有する半導体装置の製造方法において、

前記半導体基板に対して前記絶縁層が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板に対して前記絶縁層が露出する位置まで第2の開口を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第1及び第2のエッチング工程において、前記半導体基板に交流電圧が印加され、前記第2のエッチング工程における交流電圧の印加時間は前記第1のエッチング工程における交流電圧の印加時間に比して短いことを特徴とする半導体装置の製造方法。

【請求項3】

前記第1及び第2の開口から露出した前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程を具備することを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程は、前記半導体基板をエッチングする際に用いたレジスト層をマスクにして前記絶縁層をエッチングすることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程は、前記レジスト層をマスクとして用いないエッチング工程であることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項6】

前記ビアホールに埋め込まれ前記パッド電極に接続される柱状端子を形成する工程を具備することを特徴とする請求項3乃至請求項5のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記柱状端子に接続されるボール状端子を形成する工程を具備することを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記柱状端子から前記半導体基板の裏面に延在し、前記柱状端子と前記ボール状端子を接続する再配線層を形成する工程を具備することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記半導体基板を複数の半導体チップに分割する工程を具備することを特徴とする請求項1乃至請求項8のいずれか1項に記載の半導体装置の製造方法。

【請求項1】

半導体基板上に絶縁層を介して形成されたパッド電極を被覆するように前記半導体基板の表面に支持体を接着する工程と、前記半導体基板の裏面から前記パッド電極の表面に到達するようにビアホールを形成する工程とを有する半導体装置の製造方法において、

前記半導体基板に対して前記絶縁層が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板に対して前記絶縁層が露出する位置まで第2の開口を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第2のエッチング工程は前記第1のエッチング工程よりも前記半導体基板に印加される交流電圧の周波数が低いことを特徴とする半導体装置の製造方法。

【請求項2】

半導体基板上に絶縁層を介して形成されたパッド電極を被覆するように前記半導体基板の表面に支持体を接着する工程と、前記半導体基板の裏面から前記パッド電極の表面に到達するようにビアホールを形成する工程とを有する半導体装置の製造方法において、

前記半導体基板に対して前記絶縁層が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板に対して前記絶縁層が露出する位置まで第2の開口を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第1及び第2のエッチング工程において、前記半導体基板に交流電圧が印加され、前記第2のエッチング工程における交流電圧の印加時間は前記第1のエッチング工程における交流電圧の印加時間に比して短いことを特徴とする半導体装置の製造方法。

【請求項3】

前記第1及び第2の開口から露出した前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程を具備することを特徴とする請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程は、前記半導体基板をエッチングする際に用いたレジスト層をマスクにして前記絶縁層をエッチングすることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記絶縁層をエッチングして前記パッド電極を露出させるビアホールを形成する工程は、前記レジスト層をマスクとして用いないエッチング工程であることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項6】

前記ビアホールに埋め込まれ前記パッド電極に接続される柱状端子を形成する工程を具備することを特徴とする請求項3乃至請求項5のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記柱状端子に接続されるボール状端子を形成する工程を具備することを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記柱状端子から前記半導体基板の裏面に延在し、前記柱状端子と前記ボール状端子を接続する再配線層を形成する工程を具備することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記半導体基板を複数の半導体チップに分割する工程を具備することを特徴とする請求項1乃至請求項8のいずれか1項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2010−93284(P2010−93284A)

【公開日】平成22年4月22日(2010.4.22)

【国際特許分類】

【出願番号】特願2009−279144(P2009−279144)

【出願日】平成21年12月9日(2009.12.9)

【分割の表示】特願2005−38132(P2005−38132)の分割

【原出願日】平成17年2月15日(2005.2.15)

【国等の委託研究の成果に係る記載事項】(出願人による申告)国等の委託研究の成果に係る特許出願(平成13年度新エネルギー・産業技術総合開発機構からの委託研究「超高密度電子SI技術の研究開発(エネルギー使用合理化技術開発)」)、産業活力再生特別措置法30条の適用を受けるもの

【出願人】(000001889)三洋電機株式会社 (18,308)

【Fターム(参考)】

【公開日】平成22年4月22日(2010.4.22)

【国際特許分類】

【出願日】平成21年12月9日(2009.12.9)

【分割の表示】特願2005−38132(P2005−38132)の分割

【原出願日】平成17年2月15日(2005.2.15)

【国等の委託研究の成果に係る記載事項】(出願人による申告)国等の委託研究の成果に係る特許出願(平成13年度新エネルギー・産業技術総合開発機構からの委託研究「超高密度電子SI技術の研究開発(エネルギー使用合理化技術開発)」)、産業活力再生特別措置法30条の適用を受けるもの

【出願人】(000001889)三洋電機株式会社 (18,308)

【Fターム(参考)】

[ Back to top ]