半導体装置の製造方法

【課題】フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる位置合わせ用の目合わせパターンを形成することを課題とする。

【解決手段】基板1上に第1絶縁層2を形成する工程と、第1絶縁層2に、1つ以上の接続孔4と、接続孔4よりも幅が広い位置合わせ用の目合わせパターンを形成するための目合わせ孔3と、を形成する工程と、第1絶縁層2の上に、接続孔4が金属で完全に埋まり、かつ、目合わせ孔3が金属で完全に埋まらないよう金属膜5を形成する工程と、金属膜5の上に、少なくとも目合わせ孔3が完全に埋まるように第1フォトレジスト膜6を形成する工程と、第1絶縁層2をストッパーとしてCMP処理を行うことで、第1フォトレジスト膜6及び金属膜5の一部を除去する工程と、を有する半導体装置の製造方法を提供する。

【解決手段】基板1上に第1絶縁層2を形成する工程と、第1絶縁層2に、1つ以上の接続孔4と、接続孔4よりも幅が広い位置合わせ用の目合わせパターンを形成するための目合わせ孔3と、を形成する工程と、第1絶縁層2の上に、接続孔4が金属で完全に埋まり、かつ、目合わせ孔3が金属で完全に埋まらないよう金属膜5を形成する工程と、金属膜5の上に、少なくとも目合わせ孔3が完全に埋まるように第1フォトレジスト膜6を形成する工程と、第1絶縁層2をストッパーとしてCMP処理を行うことで、第1フォトレジスト膜6及び金属膜5の一部を除去する工程と、を有する半導体装置の製造方法を提供する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の製造方法として利用されるフォトリソグラフィでは、基板上にレジスト層を形成した後、所定の位置に配置されたフォトマスク越しにこのレジスト層を露光する。フォトマスクを所定の位置に配置する手段としては、基板上に形成された位置合わせ用の目合わせパターンを利用する手段が、一般的に利用される。例えば、目合わせパターンとして孔を形成し、このパターンエッジからの反射光を用いた光学的手法により目合わせを行う。または、異なる材料でコントラストを形成した目合わせパターンを形成し、この目合わせパターンの膜種の違いによるコントラストにより位置合わせを行うものもある。

【0003】

このような目合わせパターンを形成する方法としては、特許文献1に記載された技術などがある。特許文献1には、特許文献1に記載された技術を用いることで、図7に示すような目合わせパターンを形成できると記載されている。図7は、特許文献1に記載されていた図であり、符号を変更して表示してある。

【0004】

特許文献1に記載された技術では、基板11上に層間絶縁膜12を形成し、通常の露光とドライエッチングプロセスによって溝部13を形成する。その後、金属層15を形成し、続いてシリコン酸化膜16を形成した後、CMP(Chemical Mechanical Polishing)処理によって表面を平坦化する。特許文献1には、これらの工程により、図7に示すような、膜種の違いによるコントラストを形成した目合わせパターンを形成できると記載されている。なお、特許文献1には、図7の構造が得られた後、シリコン酸化膜16を除去する工程を設けることで、孔を形成した目合わせパターンを形成してもよいことが記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2001−284204号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

半導体装置の製造過程においては、多層配線のコンタクトプラグやビアプラグを形成するため、第1の層(SiO2などの層間膜など)に孔(以下、「接続孔」という)を形成後、接続孔を完全に埋めるように第1の層の上にW(タングステン)などの金属の層を形成し、その後、平坦化のため、CMP処理により接続孔外部の第1の層の上の金属を除去する工程が行われる。

【0007】

このような工程において、目合わせパターンを形成する場合、接続孔を形成する工程において、同一層内に、目合わせパターンを形成するための孔(以下、「目合わせ孔」という)を形成する。この目合わせ孔は、接続孔よりも幅広に形成される。そして、金属層を形成する工程において、接続孔を完全に埋め、かつ、目合わせ孔を完全に埋めない金属層を形成する。このようにすれば、金属層を形成した後においても、目合わせ孔が維持されることとなり、フォトリソグラフィ時のフォトマスクの位置合わせに利用することができる。また、この目合わせ孔に任意の材料を埋めることで、膜種の違いによるコントラストを形成した目合わせパターンを形成することもできる。

【0008】

しかし、上記工程の場合、金属層を形成した後のCMP処理において発生するリテーナリングの異物、研磨パッドからの異物、スラリー等の残渣などが、目合わせ孔内部に蓄積してしまう可能性がある。そして、この異物が目合わせ孔内に残存したままの状態では、フォトマスクの位置合わせの精度が低下してしまう。また、露光時の反射光が乱れ、露光不良の原因になるようなケースも生じうる。このため、CMP処理により、目合わせ孔内に異物が蓄積しないようにする必要がある。

【0009】

目合わせ孔が大きくて、目合わせ孔のアスペクト比(深さ/幅)が小さい場合は、CMP処理により目合わせ孔内部に異物が蓄積しても、比較的容易にその異物を除去することができた。しかし、基板の微細化が進むとともに目合わせパターンのアスペクト比が0.5を超えるようになると、目合わせ孔内に蓄積した異物を十分に取り除くのは困難になることを、本発明者は発見した。

【0010】

ここで、特許文献1に記載の技術では、金属層15とシリコン酸化膜16により、溝部13を埋めた後に、溝部13の外部の金属層15およびシリコン酸化膜16を除去するためのCMP処理を行っている。そして、このような構成により、CMP処理の際に、溝部13の内部に研磨剤が残留するのを防止することができると記載されている。

【0011】

しかし、特許文献1に記載の技術の場合、以下のような問題が残る。特許文献1には、CMP処理の詳細な条件について記載されていないが、Wなどの金属層のCMP処理は、一般的には、酸化膜などに対して高い選択比を維持して行われることが多い。かかる場合、CMP処理によって、溝部13の外部の金属層15およびシリコン酸化膜16を除去した後、図7に示すような構造は得られず、シリコン酸化膜16が突き出した構造になると考えられる。このような構造の目合わせパターンの場合、フォトマスクの位置合わせの精度が低下してしまう。

【0012】

なお、CMP処理の後、埋め込まれた(突き出した)シリコン酸化膜16を除去し、孔を形成した目合わせパターンを形成する手段も考えられる。しかし、層間絶縁膜12と金属層15の形状を維持し、高い選択比で内部に埋め込まれたシリコン酸化膜16を除去する(除去できるような材料の組み合わせを選ぶ)ことは容易ではない。

【課題を解決するための手段】

【0013】

本発明によれば、基板上に第1絶縁層を形成する第1絶縁層形成工程と、前記第1絶縁層に、1つ以上の接続孔と、前記接続孔よりも幅が広い位置合わせ用の目合わせパターンを形成するための目合わせ孔と、を形成する孔形成工程と、前記第1絶縁層の上に、前記接続孔が金属で完全に埋まり、かつ、前記目合わせ孔が前記金属で完全に埋まらないよう金属膜を形成する金属膜形成工程と、前記金属膜の上に、少なくとも前記目合わせ孔が完全に埋まるように第1フォトレジスト膜を形成する第1フォトレジスト膜形成工程と、前記第1絶縁層をストッパーとしてCMP処理を行うことで、前記第1フォトレジスト膜及び前記金属膜の一部を除去する研磨工程と、を有する半導体装置の製造方法が提供される。

【0014】

本発明によれば、ビアやコンタクトを形成するため第1絶縁層に形成された接続孔に金属を埋め、平坦化のためにCMP処理を行う際、第1絶縁層に形成された目合わせ孔は、第1フォトレジスト膜および金属膜で埋まっている。このため、このCMP処理により発生するリテーナリングの異物、研磨パッドからの異物、スラリー等の残渣などが、目合わせ孔内部に蓄積することはない。

【0015】

また、フォトレジスト膜は金属膜に比べて柔らかいので、CMP処理により金属膜を除去し平坦化する処理と同一処理により、第1フォトレジスト膜を除去することができる。この際、フォトレジスト膜は金属膜に比べて柔らかいので、研磨後の第1フォトレジスト膜が、表面から一部が突き出したような形状になることはない。このように、本発明によれば、フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる、膜種の違いによるコントラストを形成した目合わせパターン形成することができる。

【発明の効果】

【0016】

本発明によれば、フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる位置合わせ用の目合わせパターンを形成することができる。

【図面の簡単な説明】

【0017】

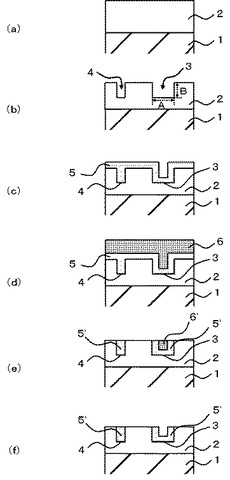

【図1】実施形態1の半導体装置の製造方法の一例を模式的に示す工程図である。

【図2】実施形態1の半導体装置の製造方法の一例を示すフローチャート図である。

【図3】実施形態1の半導体装置の製造方法の一例を示すフローチャート図である。

【図4】実施形態2の半導体装置の製造方法の一例を模式的に示す工程図の一部である。

【図5】実施形態2の半導体装置の製造方法の一例を示すフローチャート図である。

【図6】実施形態2の半導体装置の製造方法の一例を示すフローチャート図である。

【図7】従来の半導体装置の製造方法の一例を模式的に示す工程図の一部である。

【発明を実施するための形態】

【0018】

以下、本発明の実施の形態について、図面を用いて説明する。すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

<実施形態1>

【0019】

本実施形態の半導体装置の製造方法は、図2のフローチャート図に示すように、第1絶縁層形成工程S10と、孔形成工程S20と、金属膜形成工程S30と、第1フォトレジスト膜形成工程S40と、研磨工程S50と、を有する。なお、第1フォトレジスト膜除去工程S60をさらに有してもよい。以下、図1の製造工程図を用いて、本実施形態の半導体装置の製造方法について、説明する。

【0020】

第1絶縁層形成工程S10では、図1(a)に示すように、基板1上に、第1絶縁層2を形成する。第1絶縁層2は、例えば、CVD(Chemical Vapor Deposition)法によって形成された酸化膜からなる層間絶縁層であってもよい。

【0021】

孔形成工程S20では、図1(b)に示すように、第1絶縁層2に、1つ以上の接続孔4と、接続孔4よりも幅Aが広い位置合わせ用の目合わせパターンを形成するための目合わせ孔3と、を形成する。例えば、フォトリソグラフィとエッチングを用い、同一処理で、接続孔4および目合わせ孔3を形成してもよい。このような方法の場合、接続孔4と目合わせ孔3の深さBは略同一となる。その結果、幅Aが広い目合わせ孔3、すなわち、開口面積が大きい目合わせ孔3の内部容量は、接続孔4の内部容量よりも大きくなる。

【0022】

金属膜形成工程S30では、図1(c)に示すように、第1絶縁層2の上に、接続孔4が金属で完全に埋まり、かつ、目合わせ孔3が金属で完全に埋まらないよう、金属膜5を形成する。金属としては、例えば、W(タングステン)、Al(アルミニウム)などを使用することができる。このような金属膜5は、例えば、CVD法やPVD(Physical Vapor Deposition)法を用い、膜厚を制御することで形成することができる。この工程によれば、目合わせ孔3内に形成される金属膜5は、目合わせ孔3の底面および壁面に沿って形成される。このため、金属膜5が形成された後の目合わせ孔3を利用しても、フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことができる。

【0023】

第1フォトレジスト膜形成工程S40では、図1(d)に示すように、金属膜5の上に、少なくとも目合わせ孔3が完全に埋まるように第1フォトレジスト膜6を形成する。第1フォトレジスト膜6を形成後、ベーキング処理を行ってもよい。

【0024】

研磨工程S50では、図1(e)に示すように、第1絶縁層2をストッパーとしてCMP処理を行うことで、第1フォトレジスト膜6および金属膜5の一部を除去する。すなわち、接続孔4および目合わせ孔3に埋められている第1フォトレジスト膜6´および金属膜5´を除いた、第1フォトレジスト膜6および金属膜5を除去する。フォトレジスト膜は柔らかいので、例えば、金属膜5のCMP処理と同一処理により、第1フォトレジスト膜6を除去することができる。この際、フォトレジスト膜は金属膜に比べて柔らかいので、研磨後の第1フォトレジスト膜6´が、表面から突き出したような形状になることはない。

【0025】

第1フォトレジスト膜除去工程S60では、図1(f)に示すように、目合わせ孔3に埋まっている第1フォトレジスト膜6´を除去する。例えば、レジスト剥離液を利用して、第1フォトレジスト膜6´を溶出除去することができる。このような手段によれば、目合わせ孔3に埋まっている第1フォトレジスト膜6´を、十分に除去することができる。

【0026】

このような本実施形態の半導体装置の製造方法によれば、ビアやコンタクトを形成するため、接続孔4に金属を埋め、平坦化のためにCMP処理を行う際、目合わせ孔3は、第1フォトレジスト膜6および金属膜5で埋まっているので、このCMP処理により発生するリテーナリングの異物、研磨パッドからの異物、スラリー等の残渣などが、目合わせ孔3内部に蓄積することはない。

【0027】

また、フォトレジスト膜は金属膜に比べて柔らかいので、本実施形態の半導体装置の製造方法によれば、CMP処理により金属膜5を除去し平坦化する処理と同一処理により、第1フォトレジスト膜6を除去することができる。この際、フォトレジスト膜は金属膜に比べて柔らかいので、研磨後の第1フォトレジスト膜6´が、表面から突き出したような形状になることはない。このように、本実施形態によれば、フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる、膜種の違いによるコントラストを形成した目合わせパターン形成することができる。

【0028】

また、フォトレジスト膜は、レジスト剥離液を利用するなどの手段により、容易にフォトレジスト層のみを選択的に除去することができる。このため、研磨工程S50の後に第1フォトレジスト膜除去工程S60を設けた場合には、目合わせ孔3に埋まっている第1フォトレジスト膜6´を、除去残りなどが生じることなく、また、目合わせ孔3に埋まっている金属膜5を同時に除去することなく、十分に除去することができる。

【0029】

さらに、本実施形態の半導体装置の製造方法では、目合わせ孔3に埋まっている金属膜5´は、例えばCVD法やPVD法を用いて薄膜に形成される。このため、目合わせ孔3内に形成される金属膜5´は、目合わせ孔3の底面および壁面に沿って形成される。その結果、金属膜´5が埋まった状態の目合わせ孔3を利用しても、フォトリソグラフィ時のフォトマスクの位置合わせを光学的手法により十分な精度で行うことができる。

【0030】

上述のような本実施形態の半導体装置の製造方法によれば、アスペクト比(深さ/幅)が3以上の目合わせ孔であっても、フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる位置合わせ用の目合わせパターンを形成することができる。

【0031】

なお、本実施形態の半導体装置の製造方法は、図3のフローチャート図に示すように、第1フォトレジスト膜除去工程S60の後、さらに、前記目合わせ孔が形成された領域を除く第1絶縁層の上に、第2絶縁層を形成する第2絶縁層形成工程S70と、前記第2絶縁層の上に、第2フォトレジスト膜を形成する第2フォトレジスト膜形成工程S80と、前記目合わせ孔を利用してフォトマスクの位置合わせを行い、前記フォトマスクを通して前記第2フォトレジスト膜を露光する露光工程S90と、前記第2フォトレジスト膜を現像して、レジストパターンを形成する現像工程S100と、を有してもよい。

<実施形態2>

【0032】

本実施形態の半導体装置の製造方法のフローチャート図の一例を図5に示す。図に示すように、本実施形態の半導体装置の製造方法は、実施形態1の半導体装置の製造方法を基本とし、第1フォトレジスト膜形成工程S40の後、かつ、研磨工程S50の前に、フォトレジスト膜薄膜化工程S41を有する点が異なる。また、本実施形態の半導体装置の製造方法は、孔形成工程S20の構成が実施形態1の半導体装置の製造方法とは異なる。以下、実施形態1の半導体装置の製造方法とは異なる点を説明し、共通する点の説明は省略する。

【0033】

接続孔4および目合わせ孔3を形成する孔形成工程S40では、深さと幅とのアスペクト比(深さ/幅)が2ないし3以上である目合わせ孔3を形成する。そして、フォトレジスト薄膜化工程S41では、図4の模式図に示すように、第1フォトレジスト膜6をプラズマ剥離により薄膜化する。どの程度まで薄膜化するかは任意の設計事項である。

【0034】

目合わせ孔3のアスペクト比が、2ないし3以上であるような場合には、目合わせ孔3内部の第1フォトレジスト膜6´の埋込み状態を維持したまま、プラズマ剥離により、第1フォトレジスト膜6を薄膜化することができる。このようにすれば、研磨工程S50におけるCMP処理時間を短縮することができ、半導体装置の製造効率を向上させることができる。

【0035】

なお、本実施形態の半導体装置の製造方法は実施形態1と同様に、図6のフローチャート図に示すように、第1フォトレジスト膜除去工程S60の後、さらに、前記目合わせ孔が形成された領域を除く第1絶縁層の上に、第2絶縁層を形成する第2絶縁層形成工程S70と、前記第2絶縁層の上に、第2フォトレジスト膜を形成する第2フォトレジスト膜形成工程S80と、前記目合わせ孔を利用してフォトマスクの位置合わせを行い、前記フォトマスクを通して前記第2フォトレジスト膜を露光する露光工程S90と、前記第2フォトレジスト膜を現像して、レジストパターンを形成する現像工程S100と、を有してもよい。

【符号の説明】

【0036】

1 基板

2 第1絶縁層

3 目合わせ孔

4 接続孔

5 金属膜

5´ 目合わせ孔に埋められた金属膜

6 第1フォトレジスト膜

6´ 目合わせ孔に埋められた第1フォトレジスト膜

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体装置の製造方法として利用されるフォトリソグラフィでは、基板上にレジスト層を形成した後、所定の位置に配置されたフォトマスク越しにこのレジスト層を露光する。フォトマスクを所定の位置に配置する手段としては、基板上に形成された位置合わせ用の目合わせパターンを利用する手段が、一般的に利用される。例えば、目合わせパターンとして孔を形成し、このパターンエッジからの反射光を用いた光学的手法により目合わせを行う。または、異なる材料でコントラストを形成した目合わせパターンを形成し、この目合わせパターンの膜種の違いによるコントラストにより位置合わせを行うものもある。

【0003】

このような目合わせパターンを形成する方法としては、特許文献1に記載された技術などがある。特許文献1には、特許文献1に記載された技術を用いることで、図7に示すような目合わせパターンを形成できると記載されている。図7は、特許文献1に記載されていた図であり、符号を変更して表示してある。

【0004】

特許文献1に記載された技術では、基板11上に層間絶縁膜12を形成し、通常の露光とドライエッチングプロセスによって溝部13を形成する。その後、金属層15を形成し、続いてシリコン酸化膜16を形成した後、CMP(Chemical Mechanical Polishing)処理によって表面を平坦化する。特許文献1には、これらの工程により、図7に示すような、膜種の違いによるコントラストを形成した目合わせパターンを形成できると記載されている。なお、特許文献1には、図7の構造が得られた後、シリコン酸化膜16を除去する工程を設けることで、孔を形成した目合わせパターンを形成してもよいことが記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2001−284204号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

半導体装置の製造過程においては、多層配線のコンタクトプラグやビアプラグを形成するため、第1の層(SiO2などの層間膜など)に孔(以下、「接続孔」という)を形成後、接続孔を完全に埋めるように第1の層の上にW(タングステン)などの金属の層を形成し、その後、平坦化のため、CMP処理により接続孔外部の第1の層の上の金属を除去する工程が行われる。

【0007】

このような工程において、目合わせパターンを形成する場合、接続孔を形成する工程において、同一層内に、目合わせパターンを形成するための孔(以下、「目合わせ孔」という)を形成する。この目合わせ孔は、接続孔よりも幅広に形成される。そして、金属層を形成する工程において、接続孔を完全に埋め、かつ、目合わせ孔を完全に埋めない金属層を形成する。このようにすれば、金属層を形成した後においても、目合わせ孔が維持されることとなり、フォトリソグラフィ時のフォトマスクの位置合わせに利用することができる。また、この目合わせ孔に任意の材料を埋めることで、膜種の違いによるコントラストを形成した目合わせパターンを形成することもできる。

【0008】

しかし、上記工程の場合、金属層を形成した後のCMP処理において発生するリテーナリングの異物、研磨パッドからの異物、スラリー等の残渣などが、目合わせ孔内部に蓄積してしまう可能性がある。そして、この異物が目合わせ孔内に残存したままの状態では、フォトマスクの位置合わせの精度が低下してしまう。また、露光時の反射光が乱れ、露光不良の原因になるようなケースも生じうる。このため、CMP処理により、目合わせ孔内に異物が蓄積しないようにする必要がある。

【0009】

目合わせ孔が大きくて、目合わせ孔のアスペクト比(深さ/幅)が小さい場合は、CMP処理により目合わせ孔内部に異物が蓄積しても、比較的容易にその異物を除去することができた。しかし、基板の微細化が進むとともに目合わせパターンのアスペクト比が0.5を超えるようになると、目合わせ孔内に蓄積した異物を十分に取り除くのは困難になることを、本発明者は発見した。

【0010】

ここで、特許文献1に記載の技術では、金属層15とシリコン酸化膜16により、溝部13を埋めた後に、溝部13の外部の金属層15およびシリコン酸化膜16を除去するためのCMP処理を行っている。そして、このような構成により、CMP処理の際に、溝部13の内部に研磨剤が残留するのを防止することができると記載されている。

【0011】

しかし、特許文献1に記載の技術の場合、以下のような問題が残る。特許文献1には、CMP処理の詳細な条件について記載されていないが、Wなどの金属層のCMP処理は、一般的には、酸化膜などに対して高い選択比を維持して行われることが多い。かかる場合、CMP処理によって、溝部13の外部の金属層15およびシリコン酸化膜16を除去した後、図7に示すような構造は得られず、シリコン酸化膜16が突き出した構造になると考えられる。このような構造の目合わせパターンの場合、フォトマスクの位置合わせの精度が低下してしまう。

【0012】

なお、CMP処理の後、埋め込まれた(突き出した)シリコン酸化膜16を除去し、孔を形成した目合わせパターンを形成する手段も考えられる。しかし、層間絶縁膜12と金属層15の形状を維持し、高い選択比で内部に埋め込まれたシリコン酸化膜16を除去する(除去できるような材料の組み合わせを選ぶ)ことは容易ではない。

【課題を解決するための手段】

【0013】

本発明によれば、基板上に第1絶縁層を形成する第1絶縁層形成工程と、前記第1絶縁層に、1つ以上の接続孔と、前記接続孔よりも幅が広い位置合わせ用の目合わせパターンを形成するための目合わせ孔と、を形成する孔形成工程と、前記第1絶縁層の上に、前記接続孔が金属で完全に埋まり、かつ、前記目合わせ孔が前記金属で完全に埋まらないよう金属膜を形成する金属膜形成工程と、前記金属膜の上に、少なくとも前記目合わせ孔が完全に埋まるように第1フォトレジスト膜を形成する第1フォトレジスト膜形成工程と、前記第1絶縁層をストッパーとしてCMP処理を行うことで、前記第1フォトレジスト膜及び前記金属膜の一部を除去する研磨工程と、を有する半導体装置の製造方法が提供される。

【0014】

本発明によれば、ビアやコンタクトを形成するため第1絶縁層に形成された接続孔に金属を埋め、平坦化のためにCMP処理を行う際、第1絶縁層に形成された目合わせ孔は、第1フォトレジスト膜および金属膜で埋まっている。このため、このCMP処理により発生するリテーナリングの異物、研磨パッドからの異物、スラリー等の残渣などが、目合わせ孔内部に蓄積することはない。

【0015】

また、フォトレジスト膜は金属膜に比べて柔らかいので、CMP処理により金属膜を除去し平坦化する処理と同一処理により、第1フォトレジスト膜を除去することができる。この際、フォトレジスト膜は金属膜に比べて柔らかいので、研磨後の第1フォトレジスト膜が、表面から一部が突き出したような形状になることはない。このように、本発明によれば、フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる、膜種の違いによるコントラストを形成した目合わせパターン形成することができる。

【発明の効果】

【0016】

本発明によれば、フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる位置合わせ用の目合わせパターンを形成することができる。

【図面の簡単な説明】

【0017】

【図1】実施形態1の半導体装置の製造方法の一例を模式的に示す工程図である。

【図2】実施形態1の半導体装置の製造方法の一例を示すフローチャート図である。

【図3】実施形態1の半導体装置の製造方法の一例を示すフローチャート図である。

【図4】実施形態2の半導体装置の製造方法の一例を模式的に示す工程図の一部である。

【図5】実施形態2の半導体装置の製造方法の一例を示すフローチャート図である。

【図6】実施形態2の半導体装置の製造方法の一例を示すフローチャート図である。

【図7】従来の半導体装置の製造方法の一例を模式的に示す工程図の一部である。

【発明を実施するための形態】

【0018】

以下、本発明の実施の形態について、図面を用いて説明する。すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

<実施形態1>

【0019】

本実施形態の半導体装置の製造方法は、図2のフローチャート図に示すように、第1絶縁層形成工程S10と、孔形成工程S20と、金属膜形成工程S30と、第1フォトレジスト膜形成工程S40と、研磨工程S50と、を有する。なお、第1フォトレジスト膜除去工程S60をさらに有してもよい。以下、図1の製造工程図を用いて、本実施形態の半導体装置の製造方法について、説明する。

【0020】

第1絶縁層形成工程S10では、図1(a)に示すように、基板1上に、第1絶縁層2を形成する。第1絶縁層2は、例えば、CVD(Chemical Vapor Deposition)法によって形成された酸化膜からなる層間絶縁層であってもよい。

【0021】

孔形成工程S20では、図1(b)に示すように、第1絶縁層2に、1つ以上の接続孔4と、接続孔4よりも幅Aが広い位置合わせ用の目合わせパターンを形成するための目合わせ孔3と、を形成する。例えば、フォトリソグラフィとエッチングを用い、同一処理で、接続孔4および目合わせ孔3を形成してもよい。このような方法の場合、接続孔4と目合わせ孔3の深さBは略同一となる。その結果、幅Aが広い目合わせ孔3、すなわち、開口面積が大きい目合わせ孔3の内部容量は、接続孔4の内部容量よりも大きくなる。

【0022】

金属膜形成工程S30では、図1(c)に示すように、第1絶縁層2の上に、接続孔4が金属で完全に埋まり、かつ、目合わせ孔3が金属で完全に埋まらないよう、金属膜5を形成する。金属としては、例えば、W(タングステン)、Al(アルミニウム)などを使用することができる。このような金属膜5は、例えば、CVD法やPVD(Physical Vapor Deposition)法を用い、膜厚を制御することで形成することができる。この工程によれば、目合わせ孔3内に形成される金属膜5は、目合わせ孔3の底面および壁面に沿って形成される。このため、金属膜5が形成された後の目合わせ孔3を利用しても、フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことができる。

【0023】

第1フォトレジスト膜形成工程S40では、図1(d)に示すように、金属膜5の上に、少なくとも目合わせ孔3が完全に埋まるように第1フォトレジスト膜6を形成する。第1フォトレジスト膜6を形成後、ベーキング処理を行ってもよい。

【0024】

研磨工程S50では、図1(e)に示すように、第1絶縁層2をストッパーとしてCMP処理を行うことで、第1フォトレジスト膜6および金属膜5の一部を除去する。すなわち、接続孔4および目合わせ孔3に埋められている第1フォトレジスト膜6´および金属膜5´を除いた、第1フォトレジスト膜6および金属膜5を除去する。フォトレジスト膜は柔らかいので、例えば、金属膜5のCMP処理と同一処理により、第1フォトレジスト膜6を除去することができる。この際、フォトレジスト膜は金属膜に比べて柔らかいので、研磨後の第1フォトレジスト膜6´が、表面から突き出したような形状になることはない。

【0025】

第1フォトレジスト膜除去工程S60では、図1(f)に示すように、目合わせ孔3に埋まっている第1フォトレジスト膜6´を除去する。例えば、レジスト剥離液を利用して、第1フォトレジスト膜6´を溶出除去することができる。このような手段によれば、目合わせ孔3に埋まっている第1フォトレジスト膜6´を、十分に除去することができる。

【0026】

このような本実施形態の半導体装置の製造方法によれば、ビアやコンタクトを形成するため、接続孔4に金属を埋め、平坦化のためにCMP処理を行う際、目合わせ孔3は、第1フォトレジスト膜6および金属膜5で埋まっているので、このCMP処理により発生するリテーナリングの異物、研磨パッドからの異物、スラリー等の残渣などが、目合わせ孔3内部に蓄積することはない。

【0027】

また、フォトレジスト膜は金属膜に比べて柔らかいので、本実施形態の半導体装置の製造方法によれば、CMP処理により金属膜5を除去し平坦化する処理と同一処理により、第1フォトレジスト膜6を除去することができる。この際、フォトレジスト膜は金属膜に比べて柔らかいので、研磨後の第1フォトレジスト膜6´が、表面から突き出したような形状になることはない。このように、本実施形態によれば、フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる、膜種の違いによるコントラストを形成した目合わせパターン形成することができる。

【0028】

また、フォトレジスト膜は、レジスト剥離液を利用するなどの手段により、容易にフォトレジスト層のみを選択的に除去することができる。このため、研磨工程S50の後に第1フォトレジスト膜除去工程S60を設けた場合には、目合わせ孔3に埋まっている第1フォトレジスト膜6´を、除去残りなどが生じることなく、また、目合わせ孔3に埋まっている金属膜5を同時に除去することなく、十分に除去することができる。

【0029】

さらに、本実施形態の半導体装置の製造方法では、目合わせ孔3に埋まっている金属膜5´は、例えばCVD法やPVD法を用いて薄膜に形成される。このため、目合わせ孔3内に形成される金属膜5´は、目合わせ孔3の底面および壁面に沿って形成される。その結果、金属膜´5が埋まった状態の目合わせ孔3を利用しても、フォトリソグラフィ時のフォトマスクの位置合わせを光学的手法により十分な精度で行うことができる。

【0030】

上述のような本実施形態の半導体装置の製造方法によれば、アスペクト比(深さ/幅)が3以上の目合わせ孔であっても、フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる位置合わせ用の目合わせパターンを形成することができる。

【0031】

なお、本実施形態の半導体装置の製造方法は、図3のフローチャート図に示すように、第1フォトレジスト膜除去工程S60の後、さらに、前記目合わせ孔が形成された領域を除く第1絶縁層の上に、第2絶縁層を形成する第2絶縁層形成工程S70と、前記第2絶縁層の上に、第2フォトレジスト膜を形成する第2フォトレジスト膜形成工程S80と、前記目合わせ孔を利用してフォトマスクの位置合わせを行い、前記フォトマスクを通して前記第2フォトレジスト膜を露光する露光工程S90と、前記第2フォトレジスト膜を現像して、レジストパターンを形成する現像工程S100と、を有してもよい。

<実施形態2>

【0032】

本実施形態の半導体装置の製造方法のフローチャート図の一例を図5に示す。図に示すように、本実施形態の半導体装置の製造方法は、実施形態1の半導体装置の製造方法を基本とし、第1フォトレジスト膜形成工程S40の後、かつ、研磨工程S50の前に、フォトレジスト膜薄膜化工程S41を有する点が異なる。また、本実施形態の半導体装置の製造方法は、孔形成工程S20の構成が実施形態1の半導体装置の製造方法とは異なる。以下、実施形態1の半導体装置の製造方法とは異なる点を説明し、共通する点の説明は省略する。

【0033】

接続孔4および目合わせ孔3を形成する孔形成工程S40では、深さと幅とのアスペクト比(深さ/幅)が2ないし3以上である目合わせ孔3を形成する。そして、フォトレジスト薄膜化工程S41では、図4の模式図に示すように、第1フォトレジスト膜6をプラズマ剥離により薄膜化する。どの程度まで薄膜化するかは任意の設計事項である。

【0034】

目合わせ孔3のアスペクト比が、2ないし3以上であるような場合には、目合わせ孔3内部の第1フォトレジスト膜6´の埋込み状態を維持したまま、プラズマ剥離により、第1フォトレジスト膜6を薄膜化することができる。このようにすれば、研磨工程S50におけるCMP処理時間を短縮することができ、半導体装置の製造効率を向上させることができる。

【0035】

なお、本実施形態の半導体装置の製造方法は実施形態1と同様に、図6のフローチャート図に示すように、第1フォトレジスト膜除去工程S60の後、さらに、前記目合わせ孔が形成された領域を除く第1絶縁層の上に、第2絶縁層を形成する第2絶縁層形成工程S70と、前記第2絶縁層の上に、第2フォトレジスト膜を形成する第2フォトレジスト膜形成工程S80と、前記目合わせ孔を利用してフォトマスクの位置合わせを行い、前記フォトマスクを通して前記第2フォトレジスト膜を露光する露光工程S90と、前記第2フォトレジスト膜を現像して、レジストパターンを形成する現像工程S100と、を有してもよい。

【符号の説明】

【0036】

1 基板

2 第1絶縁層

3 目合わせ孔

4 接続孔

5 金属膜

5´ 目合わせ孔に埋められた金属膜

6 第1フォトレジスト膜

6´ 目合わせ孔に埋められた第1フォトレジスト膜

【特許請求の範囲】

【請求項1】

基板上に第1絶縁層を形成する第1絶縁層形成工程と、

前記第1絶縁層に、1つ以上の接続孔と、前記接続孔よりも幅が広い位置合わせ用の目合わせパターンを形成するための目合わせ孔と、を形成する孔形成工程と、

前記第1絶縁層の上に、前記接続孔が金属で完全に埋まり、かつ、前記目合わせ孔が前記金属で完全に埋まらないよう金属膜を形成する金属膜形成工程と、

前記金属膜の上に、少なくとも前記目合わせ孔が完全に埋まるように第1フォトレジスト膜を形成する第1フォトレジスト膜形成工程と、

前記第1絶縁層をストッパーとしてCMP処理を行うことで、前記第1フォトレジスト膜及び前記金属膜の一部を除去する研磨工程と、

を有する半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法において、

前記研磨工程の後、さらに、

前記目合わせ孔に埋まっている前記第1フォトレジスト膜を除去する第1フォトレジスト膜除去工程、

を有する半導体装置の製造方法。

【請求項3】

請求項1または2に記載の半導体装置の製造方法において、

前記孔形成工程では、深さと幅とのアスペクト比(深さ/幅)が3以上である前記目合わせ孔を形成し、

前記第1フォトレジスト膜形成工程の後、かつ、前記研磨工程の前に、前記第1フォトレジスト膜をプラズマ剥離により薄膜化するフォトレジスト膜薄膜化工程をさらに有する半導体装置の製造方法。

【請求項4】

請求項2または3に記載の半導体装置の製造方法において、

前記第1フォトレジスト膜除去工程の後、さらに、

前記目合わせ孔が形成された領域を除く前記第1絶縁層の上に、第2絶縁層を形成する第2絶縁層形成工程と、

前記第2絶縁層の上に、第2フォトレジスト膜を形成する第2フォトレジスト膜形成工程と、

前記目合わせ孔を利用してフォトマスクの位置合わせを行い、前記フォトマスクを通して前記第2フォトレジスト膜を露光する露光工程と、

前記第2フォトレジスト膜を現像して、レジストパターンを形成する現像工程と、

を有する半導体装置の製造方法。

【請求項1】

基板上に第1絶縁層を形成する第1絶縁層形成工程と、

前記第1絶縁層に、1つ以上の接続孔と、前記接続孔よりも幅が広い位置合わせ用の目合わせパターンを形成するための目合わせ孔と、を形成する孔形成工程と、

前記第1絶縁層の上に、前記接続孔が金属で完全に埋まり、かつ、前記目合わせ孔が前記金属で完全に埋まらないよう金属膜を形成する金属膜形成工程と、

前記金属膜の上に、少なくとも前記目合わせ孔が完全に埋まるように第1フォトレジスト膜を形成する第1フォトレジスト膜形成工程と、

前記第1絶縁層をストッパーとしてCMP処理を行うことで、前記第1フォトレジスト膜及び前記金属膜の一部を除去する研磨工程と、

を有する半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法において、

前記研磨工程の後、さらに、

前記目合わせ孔に埋まっている前記第1フォトレジスト膜を除去する第1フォトレジスト膜除去工程、

を有する半導体装置の製造方法。

【請求項3】

請求項1または2に記載の半導体装置の製造方法において、

前記孔形成工程では、深さと幅とのアスペクト比(深さ/幅)が3以上である前記目合わせ孔を形成し、

前記第1フォトレジスト膜形成工程の後、かつ、前記研磨工程の前に、前記第1フォトレジスト膜をプラズマ剥離により薄膜化するフォトレジスト膜薄膜化工程をさらに有する半導体装置の製造方法。

【請求項4】

請求項2または3に記載の半導体装置の製造方法において、

前記第1フォトレジスト膜除去工程の後、さらに、

前記目合わせ孔が形成された領域を除く前記第1絶縁層の上に、第2絶縁層を形成する第2絶縁層形成工程と、

前記第2絶縁層の上に、第2フォトレジスト膜を形成する第2フォトレジスト膜形成工程と、

前記目合わせ孔を利用してフォトマスクの位置合わせを行い、前記フォトマスクを通して前記第2フォトレジスト膜を露光する露光工程と、

前記第2フォトレジスト膜を現像して、レジストパターンを形成する現像工程と、

を有する半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−124427(P2011−124427A)

【公開日】平成23年6月23日(2011.6.23)

【国際特許分類】

【出願番号】特願2009−281651(P2009−281651)

【出願日】平成21年12月11日(2009.12.11)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年6月23日(2011.6.23)

【国際特許分類】

【出願日】平成21年12月11日(2009.12.11)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]