半導体装置の製造方法

【課題】絶縁膜のストレスに耐え、絶縁膜からの酸素や水分の影響を抑制しつつ、エレクトロマイグレーションの耐性や配線間の耐圧も改善することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、(a)凹部102が形成された絶縁膜101上に、TaN膜103を成膜する工程と、(b)TaN膜103上に、Taよりも熱膨張係数が大きいTiを主成分とするTi膜104を成膜する工程と、(c)Ti膜104上に、Tiよりも熱膨張係数が大きいCuを主成分とするCu膜105を成膜する工程と、(d)Cuを、電解めっきにより、凹部102内に埋め込む工程とを含む。

【解決手段】半導体装置の製造方法では、(a)凹部102が形成された絶縁膜101上に、TaN膜103を成膜する工程と、(b)TaN膜103上に、Taよりも熱膨張係数が大きいTiを主成分とするTi膜104を成膜する工程と、(c)Ti膜104上に、Tiよりも熱膨張係数が大きいCuを主成分とするCu膜105を成膜する工程と、(d)Cuを、電解めっきにより、凹部102内に埋め込む工程とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に、微細加工された半導体装置の信頼性や配線間耐圧を向上させる半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体集積回路(以下、半導体装置と呼称する。)では、高集積化、高機能化、高速化に伴って、低容量化、Cu配線の低抵抗化、高信頼性化に関する技術が色々と提案されている。その1つとして、バリア膜の薄膜化が提案されている。例えば、Ta/TaNバリア膜を、従来の30nmから20nmに薄膜化したとする。この場合において、Cu配線内のバリア膜の割合が減少する。これによって、配線抵抗を低下させることができる。

【0003】

また、そのような半導体集積回路では、微細化による側壁のバリア膜の薄膜化、層間膜のLow−K化により、バリア膜の水分や酸素のバリア性が低下し、バリア膜とCu膜との間に酸化膜が形成される。このため、バリア膜とCu膜との密着性が劣化し、配線やビアのエレクトロマイグレーション(以下、EMと呼称する。)やストレスマイグレーション(以下、SMと呼称する。)の耐性が、低下していくという現象が報告されている。

【0004】

そこで、バリア膜とCu膜との密着性を向上させることで、配線やビアの信頼性を向上させる成膜方法が提案されている(例えば、特許文献1参照。)。

具体的には、図7(A)〜図7(E)に示すように、その成膜方法では、半導体基板(不図示)上に絶縁膜11を成膜する。リソグラフィーおよびドライエッチングにより、絶縁膜11に凹部12を形成する。凹部12が形成された絶縁膜11中およびその表面から酸化種を熱処理により放出する。その後、Tiを窒素雰囲気中にてスパッタすることにより、絶縁膜11上にTiN膜13を成膜する。次に、順次、TiN膜13上にTi膜14を成膜し、Ti膜14上にCu膜15を成膜する。電解めっきにより、Cu膜15上にCuのめっき膜16を成膜し、凹部12内をCuで埋設する。次に、アニール処理により、膜質を安定させた後、化学機械研磨法(以下、CMP法と呼称する。)を用いて平坦化処理を行う。

【0005】

以上のような工程を繰り返すことで、半導体装置を製造することができる。このようにして製造した半導体装置では、従来のTa/TaNバリア膜の半導体装置と比較して、Ti、TiNバリア膜とCu膜との密着性が良好なため、EMやSMの耐性が優れている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−47886号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、Ti、TiNバリア膜では、原子間の結合強度が弱い。このため、さらなる微細化に伴い、Ti、TiNバリア膜がさらに薄膜化すると、絶縁膜からのストレスにTi、TiNバリア膜が耐えれなくなる。結果、原子間の結合が切れて、Ti、TiNバリア膜に欠陥が発生する。Ti、TiNバリア膜に発生した欠陥が安定状態になるにあたり、酸化チタンやチタンシリサイド酸化物が形成される。Ti、TiNバリア膜に発生した欠陥から水分や酸素がCu膜中へさらに拡散し、配線の信頼性が劣化する。

【0008】

そこで、本発明は、絶縁膜のストレスに耐え、絶縁膜からの酸素や水分の影響を抑制しつつ、エレクトロマイグレーションの耐性や配線間の耐圧も改善することが可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明に係わる半導体装置の製造方法は、下記に示す特徴を備える。

(CL1)本発明に係わる半導体装置の製造方法では、(a)Siを主成分とする絶縁膜と、前記絶縁膜に形成された凹部に設けられた配線との間にバリア構造を有する半導体装置の製造方法であって、(b)前記凹部が形成された前記絶縁膜上に、金属を主成分とする第1のバリア膜を成膜する工程と、(c)前記第1のバリア膜上に、前記第1のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とする第2のバリア膜を成膜する工程と、(d)前記第2の金属膜上に、前記第2のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とするめっきのシード膜を成膜する工程と、(e)前記めっきのシード膜の主成分よりも熱膨張係数が同じまたは大きい金属を、めっきにより、前記凹部内に埋め込む工程とを含む。

【0010】

(CL2)上記(CL1)に記載の半導体装置の製造方法では、前記第1のバリア膜上に前記第2のバリア膜を成膜する前に、逆スパッタにより、前記第1のバリア膜の前記凹部底部分をエッチングする。

【0011】

(CL3)上記(CL1)または(CL2)に記載の半導体装置の製造方法では、前記凹部が形成された前記絶縁膜上に前記第1の金属膜を成膜する前に、窒素を含むガス雰囲気中において、前記絶縁膜に形成された前記凹部の側壁をプラズマ処理する。

【0012】

(CL4)上記(CL1)から(CL3)のいずれかに記載の半導体装置の製造方法では、(a)前記凹部が形成された前記絶縁膜上に、前記第1のバリア膜として金属窒化膜を成膜し、(b)前記金属窒化膜上に前記第2の金属膜を成膜する前に、窒素を含むガス雰囲気中において、前記金属窒化膜をプラズマ処理する。

【0013】

(CL5)上記(CL1)から(CL4)のいずれかに記載の半導体装置の製造方法では、前記第1のバリア膜、前記第2のバリア膜、前記めっきのシード膜を、真空を維持した状態で、成膜する。

【0014】

なお、本発明は、半導体装置の製造方法以外に、下記に示す半導体装置として実現されるとしてもよい。

(CL6)本発明に係わる半導体装置は、(a)Siを主成分とする絶縁膜と、前記絶縁膜に形成された凹部に設けられた配線との間にバリア構造を有する半導体装置であって、(b)前記絶縁膜と接し、金属を主成分とする第1のバリア膜と、(c)前記第1のバリア膜と接し、前記第1のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とする第2のバリア膜と、(d)前記第2のバリア膜と接し、前記第2のバリア膜の主成分よりも熱膨張係数が大きく、かつ前記配線の主成分よりも熱膨張係数が同じまたは小さい金属を主成分とするめっきのシード膜とを備える。

【発明の効果】

【0015】

本発明によれば、絶縁膜からの酸素や水分がCu配線内に拡散することを抑制することができる。EM、SMに優れ、配線間耐圧を向上させることができる。配線の信頼性が向上し、配線間隔が狭くなっても、耐圧を向上させることができる。高信頼性の半導体装置を実現することができる。

【図面の簡単な説明】

【0016】

【図1】実施の形態1における半導体装置に使用される金属の物性データの表を示す図である。

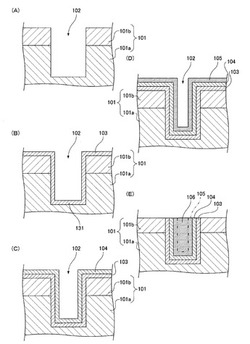

【図2】(A)〜(E)は、実施の形態1における半導体装置の製造方法の各工程を示す断面図である。

【図3】(A)は、Cu/TaN膜の積層構造の断面TEM像であり、(B)は、Cu/Ti膜の積層構造の断面TEM像であり、(C)は、Cu/Ti/TaN膜の積層構造の断面TEM像である。

【図4】各バリア構造の半導体装置のEM試験結果を示すグラフである。

【図5】(A)〜(F)は、実施の形態2における半導体装置の製造方法の各工程を示す断面図である。

【図6】(A)〜(F)は、実施の形態3における半導体装置の製造方法の各工程を示す断面図である。

【図7】(A)〜(E)は、従来の形態における半導体装置の製造方法の各工程を示す断面図である。

【発明を実施するための形態】

【0017】

(実施の形態1)

以下、本発明に係わる実施の形態1について、図面を参照しながら説明する。

<概要>

本実施の形態における半導体装置では、バリア膜の構造が、絶縁膜と接する第1のバリア膜と、Cu膜(めっきのシート膜)と接する第2のバリア膜との積層構造である。第1のバリア膜が、金属結合の強い金属、すなわち、熱膨張係数が小さい金属を主成分とする金属膜である。第2のバリア膜が、Cu膜(めっきのシート膜)の主成分(Cu)と第1のバリア膜の主成分との間の結合強度を有する金属を主成分とする金属膜である。

【0018】

例えば、図1に示すように、第1のバリア膜として、熱膨張係数が小さい金属であるTaやWを主成分とする金属膜が望ましい。これは、絶縁膜の変形に伴い、第1のバリア膜が変形しても、第1のバリア膜の欠陥が増加することを抑制することができるからである。さらに、絶縁膜からの酸素や水分の浸透を抑制するために、TaやWに、N(窒素)を結合させるとしてもよい。

【0019】

また、第2のバリア膜として、Cu膜(めっきのシート膜)の主成分(Cu)と第1のバリア膜の主成分との間の結合強度を有する金属を主成分とする金属膜が望ましい。これは、配線主材料であるCu膜(めっきのシート膜)との応力を緩和することができるからである。

【0020】

以上の点を踏まえて、本実施の形態における半導体装置では、バリア膜の構造として、Cu/Ti/TaN膜の積層構造を適用する。すなわち、絶縁膜上に、熱膨張係数の小さい順に、TaN膜(第1のバリア膜)、Ti膜(第2のバリア膜)、Cu膜(めっきのシート膜)が積層されている。

【0021】

なお、金属結合の強度の順が保たれていれば、バリア膜の構造が、Cu/Ru/TaN膜の積層構造であるとしてもよいし、Cu/Ti/WN膜の積層構造であるとしてもよい。

【0022】

<半導体装置の製造方法>

本実施の形態における半導体装置の製造方法では、図2(A)〜図2(E)に示すように、下記の工程を経て、半導体装置を製造する。

【0023】

(工程1)まず、トランジスター等の素子が形成された半導体基板上に、絶縁膜101を成膜する。このとき、半導体基板上に、誘電率K=2.5の絶縁膜101aを、CVD法により、190nm、成膜する。さらに、絶縁膜101a上に、K=3.5の絶縁膜101bを、CVD法により、80nm、成膜する。

【0024】

(工程2)次に、リソグラフィー及びドライエッチングにより、絶縁膜101に、ビア部または溝部になる凹部102を形成する。

(工程3)次に、絶縁膜101に凹部102を形成した段階の半導体装置を、スパッタ装置の真空チェンバーにおいて、350℃、60secで加熱し、絶縁膜101の表面の水分などを蒸発させる。

【0025】

(工程4)次に、絶縁膜101の表面の水分などを蒸発させた段階の半導体装置を、真空を維持した状態で、Ta成膜用チェンバーに移動する。Ta成膜用チェンバーにおいて、ターゲットバイアス10KW、N2=20sccmで、絶縁膜101上に、TaN膜103を、5nm、成膜する。

【0026】

(工程5)その後、TaN膜103を成膜した段階の半導体装置を、真空を維持した状態で、Ti成膜用チェンバーに移動する。Ti成膜用チェンバーにおいて、ターゲットバイアス10KWで、TaN膜103上に、Ti膜104を、10nm、成膜する。

【0027】

(工程6)次に、Ti膜104を成膜した段階の半導体装置を、真空を維持した状態で、Cu成膜用チェンバーに移動する。Cu成膜用チェンバーにおいて、ターゲットバイアス20KWで、Ti膜104上に、Cu膜105を、40nm、成膜する。

【0028】

(工程7)その後、電解めっきにより、Cu膜105上に、Cuのめっき膜106を、1000nm、成膜し、凹部102内をCuで埋設する。

(工程8)次に、化学機械研磨により、めっき膜106を1000nm、Cu膜105を40nm、Ti膜104を10nm、TaN膜103を5nm、絶縁膜101bを50nm研磨する。これによって、ダマシン配線を形成する。

【0029】

<バリア膜の構造>

ここで、透過型電子顕微鏡(TEM)を使用して、Cu/TaN膜、Cu/Ti膜、Cu/Ti/TaN膜の各積層構造について説明する。

【0030】

まず、図3(A)に示すように、Cu/TaN膜の積層構造では、Cu膜とTaN膜との境界にボイドが見られる。これは、Cu膜とTaN膜とのストレス差が大きく密着性が悪いためである。

【0031】

次に、図3(B)に示すように、Cu/Ti膜の積層構造では、膜厚5nmに成膜したTi膜の代わりに、TiO2やTiSiO2膜(酸化膜)が、5nm程度、形成されている。これは、Ti膜が、絶縁膜(Low−K膜)中の酸素や水分と結合して、TiO2やTiSiO2膜(酸化膜)になるためである。すなわち、Cu/Ti膜の積層構造では、Cu膜が酸素と接する。

【0032】

次に、図3(C)に示すように、Cu/Ti/TaN膜の積層構造では、Cu膜とTaN膜(バリア膜)との間にボイドが見られず、Ti膜(バリア膜)上下にTiO2やTiSiO2膜(酸化膜)も見られない。すなわち、Cu/Ti/TaN膜の積層構造では、Cu膜が酸素と直接接しない。

【0033】

これによって、半導体装置の信頼性に影響するバリア膜の界面に酸化膜ができない。このため、TaN膜とTi膜との濡れ性、Ti膜とCu膜との濡れ性も良好である。

さらに、図4に示すように、バリア構造が、Tiの単層構造、TiNの単層構造よりも、Ti/TaNの積層構造の方が、EM耐性が優れている。バリア構造をTi/TaNの積層構造にすることにより、配線間耐圧やEM耐性が大幅に向上する。

【0034】

なお、図4においては、Ta/TaN(図中の三角印)、Ti(図中の黒塗り菱形印)、TiN(図中の丸印)、Ti/TaN(図中の白塗り菱形印)の各構造について、ビアEM調べた結果である。縦軸が累積確率(Cumulative Probability)であり、横軸が故障時間(Failure Time)である。

【0035】

<まとめ>

以上、本実施の形態によれば、TaN膜103(第1のバリア膜)とTi膜104(第2のバリア膜)とでバリア膜の構造を形成した。

【0036】

これによって、絶縁膜からの酸素や水分がCu配線内に拡散することを抑制することができる。EM、SMに優れ、配線間耐圧を向上させることができる。配線の信頼性が向上し、配線間隔が狭くなっても、耐圧を向上させることができる。高信頼性の半導体装置を実現することができる。

【0037】

なお、TaN膜103(第1のバリア膜)の成膜後、逆スパッタにより、TaN膜103の凹部底部分107をエッチングしたのち、Ti膜104(第2のバリア膜)を成膜するとしてもよい。

【0038】

なお、めっき膜106として、Cuの代わりに、Cu膜105の主成分(Cu)よりも熱膨張係数が同じまたは大きい金属を主成分としてもよい。

(実施の形態2)

以下、本発明に係わる実施の形態2について、図面を参照しながら説明する。なお、実施の形態1と同一の構成要素については、同一の参照符号を付す。

【0039】

<半導体装置の製造方法>

本実施の形態における半導体装置の製造方法では、図5(A)〜図5(F)に示すように、下記の工程を経て、半導体装置を製造する。

【0040】

(工程1)まず、トランジスター等の素子が形成された半導体基板上に、絶縁膜101を成膜する。このとき、半導体基板上に、誘電率K=2.5の絶縁膜101aを、CVD法により、190nm、成膜する。さらに、絶縁膜101a上に、K=3.5の絶縁膜101bを、CVD法により、80nm成膜する。

【0041】

(工程2)次に、リソグラフィー及びドライエッチングにより、絶縁膜101に、ビア部または溝部になる凹部102を形成する。

(工程3)次に、絶縁膜101に凹部102を形成した段階の半導体装置を、真空装置内に設置する。He−N2やNH3雰囲気中において、放電する、すなわち、プラズマ処理することにより、絶縁膜101の凹部側壁部分211に存在する欠陥を修復する。

【0042】

(工程4)次に、絶縁膜101の凹部側壁部分211に存在する欠陥を修復した段階の半導体装置を、真空を維持した状態で、Ta成膜用チェンバーに移動する。Ta成膜用チェンバーにおいて、ターゲットバイアス10KW、N2=20sccmで、絶縁膜101上に、TaN膜103を、5nm、成膜する。

【0043】

(工程5)その後、TaN膜103を成膜した段階の半導体装置を、真空を維持した状態で、Ti成膜用チェンバーに移動する。Ti成膜用チェンバーにおいて、ターゲットバイアス10KWで、TaN膜103上に、Ti膜104を、10nm、成膜する。

【0044】

(工程6)次に、Ti膜104を成膜した段階の半導体装置を、真空を維持した状態で、Cu成膜用チェンバーに移動する。Cu成膜用チェンバーにおいて、ターゲットバイアス20KWで、Ti膜104上に、Cu膜105を、40nm、成膜する。

【0045】

(工程7)その後、電解めっきにより、Cu膜105上に、Cuのめっき膜106を、1000nm、成膜し、凹部102内をCuで埋設する。

(工程8)次に、化学機械研磨により、めっき膜106を1000nm、Cu膜105を40nm、Ti膜104を10nm、TaN膜103を5nm、絶縁膜101bを50nm研磨する。これによって、ダマシン配線を形成する。

【0046】

<まとめ>

以上、本実施の形態によれば、絶縁膜101の凹部側壁部分211の欠陥を修復することにより、絶縁膜101(Low−K膜)中に存在する酸素や水分の放出を抑制することができる。さらに、欠陥が修復された絶縁膜101の凹部側壁部分211とTaN膜103との密着性を向上させることができる。これに伴い、欠陥が修復された絶縁膜101の凹部側壁部分211とTaN膜103との境界に生じるストレスを緩和することができる。これによって、実施の形態1と比較して、さらなる配線間耐圧やEM、SMを改善することができる。

【0047】

(実施の形態3)

以下、本発明に係わる実施の形態3について、図面を参照しながら説明する。なお、実施の形態1と同一の構成要素については、同一の参照符号を付す。

【0048】

<半導体装置の製造方法>

本実施の形態における半導体装置の製造方法では、図6(A)〜図6(F)に示すように、下記の工程を経て、半導体装置を製造する。

【0049】

(工程1)まず、トランジスター等の素子が形成された半導体基板上に、絶縁膜101を成膜する。このとき、半導体基板上に、誘電率K=2.5の絶縁膜101aを、CVD法により、190nm、成膜する。さらに、絶縁膜101a上に、K=3.5の絶縁膜101bを、CVD法により、80nm、成膜する。

【0050】

(工程2)次に、リソグラフィー及びドライエッチングにより、絶縁膜101に、ビア部または溝部になる凹部102を形成する。

(工程3)次に、絶縁膜101に凹部102を形成した段階の半導体装置を、スパッタ装置の真空チェンバーにおいて、350℃、60secで加熱し、絶縁膜101の表面の水分などを蒸発させる。

【0051】

(工程4)次に、絶縁膜101の表面の水分などを蒸発させた段階の半導体装置を、真空を維持した状態で、Ta成膜用チェンバーに移動する。Ta成膜用チェンバーにおいて、ターゲットバイアス10KW、N2=20sccmで、絶縁膜101上に、TaN膜103を、5nm、成膜する。

【0052】

(工程5)次に、TaN膜103を成膜した段階の半導体装置を、N2やNH3雰囲気中にて、プラズマ処理あるいはアニール処理を行い、TaN膜103の表面部分331のスパッタ等による欠陥を修復する。

【0053】

(工程6)その後、TaN膜103の表面部分331の欠陥を修復した段階の半導体装置を、真空を維持した状態で、Ti成膜用チェンバーに移動する。Ti成膜用チェンバーにおいて、ターゲットバイアス10KWで、欠陥を修復したTaN膜103上に、Ti膜104を、10nm、成膜する。

【0054】

(工程7)次に、Ti膜104を成膜した段階の半導体装置を、真空を維持した状態で、Cu成膜用チェンバーに移動する。Cu成膜用チェンバーにおいて、ターゲットバイアス20KWで、Ti膜104上に、Cu膜105を、40nm、成膜する。

【0055】

(工程8)その後、電解めっきにより、Cu膜105上に、Cuのめっき膜106を、1000nm、成膜し、凹部102内をCuで埋設する。

(工程9)次に、化学機械研磨により、めっき膜106を1000nm、Cu膜105を40nm、Ti膜104を10nm、TaN膜103を5nm、絶縁膜101bを50nm研磨する。これによって、ダマシン配線を形成する。

【0056】

<まとめ>

以上、本実施の形態によれば、TaN膜103の表面部分331の欠陥を修復することにより、絶縁膜101からの水分や酸素が、TaN膜103(第1のバリア膜)を浸透し難くなる。これによって、実施の形態1と比較して、さらなる配線間耐圧やEM、SM対背を改善することができる。

【0057】

なお、実施の形態2において、本実施の形態のように、TaN膜103の表面部分331の欠陥を修復するとしてもよい。

【産業上の利用可能性】

【0058】

本発明は、半導体装置の製造方法として、特に、微細加工された半導体装置の信頼性や配線間耐圧を向上させる半導体装置の製造方法として、利用することができる。

【符号の説明】

【0059】

11 絶縁膜

12 凹部

13 TiN膜

14 Ti膜

15 Cu膜

16 めっき膜

101 絶縁膜

101a 絶縁膜

101b 絶縁膜

102 凹部

103 TaN膜

104 Ti膜

105 Cu膜

106 めっき膜

131 凹部底部分

211 凹部側壁部分

331 表面部分

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に、微細加工された半導体装置の信頼性や配線間耐圧を向上させる半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体集積回路(以下、半導体装置と呼称する。)では、高集積化、高機能化、高速化に伴って、低容量化、Cu配線の低抵抗化、高信頼性化に関する技術が色々と提案されている。その1つとして、バリア膜の薄膜化が提案されている。例えば、Ta/TaNバリア膜を、従来の30nmから20nmに薄膜化したとする。この場合において、Cu配線内のバリア膜の割合が減少する。これによって、配線抵抗を低下させることができる。

【0003】

また、そのような半導体集積回路では、微細化による側壁のバリア膜の薄膜化、層間膜のLow−K化により、バリア膜の水分や酸素のバリア性が低下し、バリア膜とCu膜との間に酸化膜が形成される。このため、バリア膜とCu膜との密着性が劣化し、配線やビアのエレクトロマイグレーション(以下、EMと呼称する。)やストレスマイグレーション(以下、SMと呼称する。)の耐性が、低下していくという現象が報告されている。

【0004】

そこで、バリア膜とCu膜との密着性を向上させることで、配線やビアの信頼性を向上させる成膜方法が提案されている(例えば、特許文献1参照。)。

具体的には、図7(A)〜図7(E)に示すように、その成膜方法では、半導体基板(不図示)上に絶縁膜11を成膜する。リソグラフィーおよびドライエッチングにより、絶縁膜11に凹部12を形成する。凹部12が形成された絶縁膜11中およびその表面から酸化種を熱処理により放出する。その後、Tiを窒素雰囲気中にてスパッタすることにより、絶縁膜11上にTiN膜13を成膜する。次に、順次、TiN膜13上にTi膜14を成膜し、Ti膜14上にCu膜15を成膜する。電解めっきにより、Cu膜15上にCuのめっき膜16を成膜し、凹部12内をCuで埋設する。次に、アニール処理により、膜質を安定させた後、化学機械研磨法(以下、CMP法と呼称する。)を用いて平坦化処理を行う。

【0005】

以上のような工程を繰り返すことで、半導体装置を製造することができる。このようにして製造した半導体装置では、従来のTa/TaNバリア膜の半導体装置と比較して、Ti、TiNバリア膜とCu膜との密着性が良好なため、EMやSMの耐性が優れている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−47886号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、Ti、TiNバリア膜では、原子間の結合強度が弱い。このため、さらなる微細化に伴い、Ti、TiNバリア膜がさらに薄膜化すると、絶縁膜からのストレスにTi、TiNバリア膜が耐えれなくなる。結果、原子間の結合が切れて、Ti、TiNバリア膜に欠陥が発生する。Ti、TiNバリア膜に発生した欠陥が安定状態になるにあたり、酸化チタンやチタンシリサイド酸化物が形成される。Ti、TiNバリア膜に発生した欠陥から水分や酸素がCu膜中へさらに拡散し、配線の信頼性が劣化する。

【0008】

そこで、本発明は、絶縁膜のストレスに耐え、絶縁膜からの酸素や水分の影響を抑制しつつ、エレクトロマイグレーションの耐性や配線間の耐圧も改善することが可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明に係わる半導体装置の製造方法は、下記に示す特徴を備える。

(CL1)本発明に係わる半導体装置の製造方法では、(a)Siを主成分とする絶縁膜と、前記絶縁膜に形成された凹部に設けられた配線との間にバリア構造を有する半導体装置の製造方法であって、(b)前記凹部が形成された前記絶縁膜上に、金属を主成分とする第1のバリア膜を成膜する工程と、(c)前記第1のバリア膜上に、前記第1のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とする第2のバリア膜を成膜する工程と、(d)前記第2の金属膜上に、前記第2のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とするめっきのシード膜を成膜する工程と、(e)前記めっきのシード膜の主成分よりも熱膨張係数が同じまたは大きい金属を、めっきにより、前記凹部内に埋め込む工程とを含む。

【0010】

(CL2)上記(CL1)に記載の半導体装置の製造方法では、前記第1のバリア膜上に前記第2のバリア膜を成膜する前に、逆スパッタにより、前記第1のバリア膜の前記凹部底部分をエッチングする。

【0011】

(CL3)上記(CL1)または(CL2)に記載の半導体装置の製造方法では、前記凹部が形成された前記絶縁膜上に前記第1の金属膜を成膜する前に、窒素を含むガス雰囲気中において、前記絶縁膜に形成された前記凹部の側壁をプラズマ処理する。

【0012】

(CL4)上記(CL1)から(CL3)のいずれかに記載の半導体装置の製造方法では、(a)前記凹部が形成された前記絶縁膜上に、前記第1のバリア膜として金属窒化膜を成膜し、(b)前記金属窒化膜上に前記第2の金属膜を成膜する前に、窒素を含むガス雰囲気中において、前記金属窒化膜をプラズマ処理する。

【0013】

(CL5)上記(CL1)から(CL4)のいずれかに記載の半導体装置の製造方法では、前記第1のバリア膜、前記第2のバリア膜、前記めっきのシード膜を、真空を維持した状態で、成膜する。

【0014】

なお、本発明は、半導体装置の製造方法以外に、下記に示す半導体装置として実現されるとしてもよい。

(CL6)本発明に係わる半導体装置は、(a)Siを主成分とする絶縁膜と、前記絶縁膜に形成された凹部に設けられた配線との間にバリア構造を有する半導体装置であって、(b)前記絶縁膜と接し、金属を主成分とする第1のバリア膜と、(c)前記第1のバリア膜と接し、前記第1のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とする第2のバリア膜と、(d)前記第2のバリア膜と接し、前記第2のバリア膜の主成分よりも熱膨張係数が大きく、かつ前記配線の主成分よりも熱膨張係数が同じまたは小さい金属を主成分とするめっきのシード膜とを備える。

【発明の効果】

【0015】

本発明によれば、絶縁膜からの酸素や水分がCu配線内に拡散することを抑制することができる。EM、SMに優れ、配線間耐圧を向上させることができる。配線の信頼性が向上し、配線間隔が狭くなっても、耐圧を向上させることができる。高信頼性の半導体装置を実現することができる。

【図面の簡単な説明】

【0016】

【図1】実施の形態1における半導体装置に使用される金属の物性データの表を示す図である。

【図2】(A)〜(E)は、実施の形態1における半導体装置の製造方法の各工程を示す断面図である。

【図3】(A)は、Cu/TaN膜の積層構造の断面TEM像であり、(B)は、Cu/Ti膜の積層構造の断面TEM像であり、(C)は、Cu/Ti/TaN膜の積層構造の断面TEM像である。

【図4】各バリア構造の半導体装置のEM試験結果を示すグラフである。

【図5】(A)〜(F)は、実施の形態2における半導体装置の製造方法の各工程を示す断面図である。

【図6】(A)〜(F)は、実施の形態3における半導体装置の製造方法の各工程を示す断面図である。

【図7】(A)〜(E)は、従来の形態における半導体装置の製造方法の各工程を示す断面図である。

【発明を実施するための形態】

【0017】

(実施の形態1)

以下、本発明に係わる実施の形態1について、図面を参照しながら説明する。

<概要>

本実施の形態における半導体装置では、バリア膜の構造が、絶縁膜と接する第1のバリア膜と、Cu膜(めっきのシート膜)と接する第2のバリア膜との積層構造である。第1のバリア膜が、金属結合の強い金属、すなわち、熱膨張係数が小さい金属を主成分とする金属膜である。第2のバリア膜が、Cu膜(めっきのシート膜)の主成分(Cu)と第1のバリア膜の主成分との間の結合強度を有する金属を主成分とする金属膜である。

【0018】

例えば、図1に示すように、第1のバリア膜として、熱膨張係数が小さい金属であるTaやWを主成分とする金属膜が望ましい。これは、絶縁膜の変形に伴い、第1のバリア膜が変形しても、第1のバリア膜の欠陥が増加することを抑制することができるからである。さらに、絶縁膜からの酸素や水分の浸透を抑制するために、TaやWに、N(窒素)を結合させるとしてもよい。

【0019】

また、第2のバリア膜として、Cu膜(めっきのシート膜)の主成分(Cu)と第1のバリア膜の主成分との間の結合強度を有する金属を主成分とする金属膜が望ましい。これは、配線主材料であるCu膜(めっきのシート膜)との応力を緩和することができるからである。

【0020】

以上の点を踏まえて、本実施の形態における半導体装置では、バリア膜の構造として、Cu/Ti/TaN膜の積層構造を適用する。すなわち、絶縁膜上に、熱膨張係数の小さい順に、TaN膜(第1のバリア膜)、Ti膜(第2のバリア膜)、Cu膜(めっきのシート膜)が積層されている。

【0021】

なお、金属結合の強度の順が保たれていれば、バリア膜の構造が、Cu/Ru/TaN膜の積層構造であるとしてもよいし、Cu/Ti/WN膜の積層構造であるとしてもよい。

【0022】

<半導体装置の製造方法>

本実施の形態における半導体装置の製造方法では、図2(A)〜図2(E)に示すように、下記の工程を経て、半導体装置を製造する。

【0023】

(工程1)まず、トランジスター等の素子が形成された半導体基板上に、絶縁膜101を成膜する。このとき、半導体基板上に、誘電率K=2.5の絶縁膜101aを、CVD法により、190nm、成膜する。さらに、絶縁膜101a上に、K=3.5の絶縁膜101bを、CVD法により、80nm、成膜する。

【0024】

(工程2)次に、リソグラフィー及びドライエッチングにより、絶縁膜101に、ビア部または溝部になる凹部102を形成する。

(工程3)次に、絶縁膜101に凹部102を形成した段階の半導体装置を、スパッタ装置の真空チェンバーにおいて、350℃、60secで加熱し、絶縁膜101の表面の水分などを蒸発させる。

【0025】

(工程4)次に、絶縁膜101の表面の水分などを蒸発させた段階の半導体装置を、真空を維持した状態で、Ta成膜用チェンバーに移動する。Ta成膜用チェンバーにおいて、ターゲットバイアス10KW、N2=20sccmで、絶縁膜101上に、TaN膜103を、5nm、成膜する。

【0026】

(工程5)その後、TaN膜103を成膜した段階の半導体装置を、真空を維持した状態で、Ti成膜用チェンバーに移動する。Ti成膜用チェンバーにおいて、ターゲットバイアス10KWで、TaN膜103上に、Ti膜104を、10nm、成膜する。

【0027】

(工程6)次に、Ti膜104を成膜した段階の半導体装置を、真空を維持した状態で、Cu成膜用チェンバーに移動する。Cu成膜用チェンバーにおいて、ターゲットバイアス20KWで、Ti膜104上に、Cu膜105を、40nm、成膜する。

【0028】

(工程7)その後、電解めっきにより、Cu膜105上に、Cuのめっき膜106を、1000nm、成膜し、凹部102内をCuで埋設する。

(工程8)次に、化学機械研磨により、めっき膜106を1000nm、Cu膜105を40nm、Ti膜104を10nm、TaN膜103を5nm、絶縁膜101bを50nm研磨する。これによって、ダマシン配線を形成する。

【0029】

<バリア膜の構造>

ここで、透過型電子顕微鏡(TEM)を使用して、Cu/TaN膜、Cu/Ti膜、Cu/Ti/TaN膜の各積層構造について説明する。

【0030】

まず、図3(A)に示すように、Cu/TaN膜の積層構造では、Cu膜とTaN膜との境界にボイドが見られる。これは、Cu膜とTaN膜とのストレス差が大きく密着性が悪いためである。

【0031】

次に、図3(B)に示すように、Cu/Ti膜の積層構造では、膜厚5nmに成膜したTi膜の代わりに、TiO2やTiSiO2膜(酸化膜)が、5nm程度、形成されている。これは、Ti膜が、絶縁膜(Low−K膜)中の酸素や水分と結合して、TiO2やTiSiO2膜(酸化膜)になるためである。すなわち、Cu/Ti膜の積層構造では、Cu膜が酸素と接する。

【0032】

次に、図3(C)に示すように、Cu/Ti/TaN膜の積層構造では、Cu膜とTaN膜(バリア膜)との間にボイドが見られず、Ti膜(バリア膜)上下にTiO2やTiSiO2膜(酸化膜)も見られない。すなわち、Cu/Ti/TaN膜の積層構造では、Cu膜が酸素と直接接しない。

【0033】

これによって、半導体装置の信頼性に影響するバリア膜の界面に酸化膜ができない。このため、TaN膜とTi膜との濡れ性、Ti膜とCu膜との濡れ性も良好である。

さらに、図4に示すように、バリア構造が、Tiの単層構造、TiNの単層構造よりも、Ti/TaNの積層構造の方が、EM耐性が優れている。バリア構造をTi/TaNの積層構造にすることにより、配線間耐圧やEM耐性が大幅に向上する。

【0034】

なお、図4においては、Ta/TaN(図中の三角印)、Ti(図中の黒塗り菱形印)、TiN(図中の丸印)、Ti/TaN(図中の白塗り菱形印)の各構造について、ビアEM調べた結果である。縦軸が累積確率(Cumulative Probability)であり、横軸が故障時間(Failure Time)である。

【0035】

<まとめ>

以上、本実施の形態によれば、TaN膜103(第1のバリア膜)とTi膜104(第2のバリア膜)とでバリア膜の構造を形成した。

【0036】

これによって、絶縁膜からの酸素や水分がCu配線内に拡散することを抑制することができる。EM、SMに優れ、配線間耐圧を向上させることができる。配線の信頼性が向上し、配線間隔が狭くなっても、耐圧を向上させることができる。高信頼性の半導体装置を実現することができる。

【0037】

なお、TaN膜103(第1のバリア膜)の成膜後、逆スパッタにより、TaN膜103の凹部底部分107をエッチングしたのち、Ti膜104(第2のバリア膜)を成膜するとしてもよい。

【0038】

なお、めっき膜106として、Cuの代わりに、Cu膜105の主成分(Cu)よりも熱膨張係数が同じまたは大きい金属を主成分としてもよい。

(実施の形態2)

以下、本発明に係わる実施の形態2について、図面を参照しながら説明する。なお、実施の形態1と同一の構成要素については、同一の参照符号を付す。

【0039】

<半導体装置の製造方法>

本実施の形態における半導体装置の製造方法では、図5(A)〜図5(F)に示すように、下記の工程を経て、半導体装置を製造する。

【0040】

(工程1)まず、トランジスター等の素子が形成された半導体基板上に、絶縁膜101を成膜する。このとき、半導体基板上に、誘電率K=2.5の絶縁膜101aを、CVD法により、190nm、成膜する。さらに、絶縁膜101a上に、K=3.5の絶縁膜101bを、CVD法により、80nm成膜する。

【0041】

(工程2)次に、リソグラフィー及びドライエッチングにより、絶縁膜101に、ビア部または溝部になる凹部102を形成する。

(工程3)次に、絶縁膜101に凹部102を形成した段階の半導体装置を、真空装置内に設置する。He−N2やNH3雰囲気中において、放電する、すなわち、プラズマ処理することにより、絶縁膜101の凹部側壁部分211に存在する欠陥を修復する。

【0042】

(工程4)次に、絶縁膜101の凹部側壁部分211に存在する欠陥を修復した段階の半導体装置を、真空を維持した状態で、Ta成膜用チェンバーに移動する。Ta成膜用チェンバーにおいて、ターゲットバイアス10KW、N2=20sccmで、絶縁膜101上に、TaN膜103を、5nm、成膜する。

【0043】

(工程5)その後、TaN膜103を成膜した段階の半導体装置を、真空を維持した状態で、Ti成膜用チェンバーに移動する。Ti成膜用チェンバーにおいて、ターゲットバイアス10KWで、TaN膜103上に、Ti膜104を、10nm、成膜する。

【0044】

(工程6)次に、Ti膜104を成膜した段階の半導体装置を、真空を維持した状態で、Cu成膜用チェンバーに移動する。Cu成膜用チェンバーにおいて、ターゲットバイアス20KWで、Ti膜104上に、Cu膜105を、40nm、成膜する。

【0045】

(工程7)その後、電解めっきにより、Cu膜105上に、Cuのめっき膜106を、1000nm、成膜し、凹部102内をCuで埋設する。

(工程8)次に、化学機械研磨により、めっき膜106を1000nm、Cu膜105を40nm、Ti膜104を10nm、TaN膜103を5nm、絶縁膜101bを50nm研磨する。これによって、ダマシン配線を形成する。

【0046】

<まとめ>

以上、本実施の形態によれば、絶縁膜101の凹部側壁部分211の欠陥を修復することにより、絶縁膜101(Low−K膜)中に存在する酸素や水分の放出を抑制することができる。さらに、欠陥が修復された絶縁膜101の凹部側壁部分211とTaN膜103との密着性を向上させることができる。これに伴い、欠陥が修復された絶縁膜101の凹部側壁部分211とTaN膜103との境界に生じるストレスを緩和することができる。これによって、実施の形態1と比較して、さらなる配線間耐圧やEM、SMを改善することができる。

【0047】

(実施の形態3)

以下、本発明に係わる実施の形態3について、図面を参照しながら説明する。なお、実施の形態1と同一の構成要素については、同一の参照符号を付す。

【0048】

<半導体装置の製造方法>

本実施の形態における半導体装置の製造方法では、図6(A)〜図6(F)に示すように、下記の工程を経て、半導体装置を製造する。

【0049】

(工程1)まず、トランジスター等の素子が形成された半導体基板上に、絶縁膜101を成膜する。このとき、半導体基板上に、誘電率K=2.5の絶縁膜101aを、CVD法により、190nm、成膜する。さらに、絶縁膜101a上に、K=3.5の絶縁膜101bを、CVD法により、80nm、成膜する。

【0050】

(工程2)次に、リソグラフィー及びドライエッチングにより、絶縁膜101に、ビア部または溝部になる凹部102を形成する。

(工程3)次に、絶縁膜101に凹部102を形成した段階の半導体装置を、スパッタ装置の真空チェンバーにおいて、350℃、60secで加熱し、絶縁膜101の表面の水分などを蒸発させる。

【0051】

(工程4)次に、絶縁膜101の表面の水分などを蒸発させた段階の半導体装置を、真空を維持した状態で、Ta成膜用チェンバーに移動する。Ta成膜用チェンバーにおいて、ターゲットバイアス10KW、N2=20sccmで、絶縁膜101上に、TaN膜103を、5nm、成膜する。

【0052】

(工程5)次に、TaN膜103を成膜した段階の半導体装置を、N2やNH3雰囲気中にて、プラズマ処理あるいはアニール処理を行い、TaN膜103の表面部分331のスパッタ等による欠陥を修復する。

【0053】

(工程6)その後、TaN膜103の表面部分331の欠陥を修復した段階の半導体装置を、真空を維持した状態で、Ti成膜用チェンバーに移動する。Ti成膜用チェンバーにおいて、ターゲットバイアス10KWで、欠陥を修復したTaN膜103上に、Ti膜104を、10nm、成膜する。

【0054】

(工程7)次に、Ti膜104を成膜した段階の半導体装置を、真空を維持した状態で、Cu成膜用チェンバーに移動する。Cu成膜用チェンバーにおいて、ターゲットバイアス20KWで、Ti膜104上に、Cu膜105を、40nm、成膜する。

【0055】

(工程8)その後、電解めっきにより、Cu膜105上に、Cuのめっき膜106を、1000nm、成膜し、凹部102内をCuで埋設する。

(工程9)次に、化学機械研磨により、めっき膜106を1000nm、Cu膜105を40nm、Ti膜104を10nm、TaN膜103を5nm、絶縁膜101bを50nm研磨する。これによって、ダマシン配線を形成する。

【0056】

<まとめ>

以上、本実施の形態によれば、TaN膜103の表面部分331の欠陥を修復することにより、絶縁膜101からの水分や酸素が、TaN膜103(第1のバリア膜)を浸透し難くなる。これによって、実施の形態1と比較して、さらなる配線間耐圧やEM、SM対背を改善することができる。

【0057】

なお、実施の形態2において、本実施の形態のように、TaN膜103の表面部分331の欠陥を修復するとしてもよい。

【産業上の利用可能性】

【0058】

本発明は、半導体装置の製造方法として、特に、微細加工された半導体装置の信頼性や配線間耐圧を向上させる半導体装置の製造方法として、利用することができる。

【符号の説明】

【0059】

11 絶縁膜

12 凹部

13 TiN膜

14 Ti膜

15 Cu膜

16 めっき膜

101 絶縁膜

101a 絶縁膜

101b 絶縁膜

102 凹部

103 TaN膜

104 Ti膜

105 Cu膜

106 めっき膜

131 凹部底部分

211 凹部側壁部分

331 表面部分

【特許請求の範囲】

【請求項1】

Siを主成分とする絶縁膜と、前記絶縁膜に形成された凹部に設けられた配線との間にバリア構造を有する半導体装置の製造方法であって、

前記凹部が形成された前記絶縁膜上に、金属を主成分とする第1のバリア膜を成膜する工程と、

前記第1のバリア膜上に、前記第1のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とする第2のバリア膜を成膜する工程と、

前記第2の金属膜上に、前記第2のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とするめっきのシード膜を成膜する工程と、

前記めっきのシード膜の主成分よりも熱膨張係数が同じまたは大きい金属を、めっきにより、前記凹部内に埋め込む工程とを含む

半導体装置の製造方法。

【請求項2】

前記第1のバリア膜上に前記第2のバリア膜を成膜する前に、逆スパッタにより、前記第1のバリア膜の前記凹部底部分をエッチングする

請求項1に記載の半導体装置の製造方法。

【請求項3】

前記凹部が形成された前記絶縁膜上に前記第1の金属膜を成膜する前に、窒素を含むガス雰囲気中において、前記絶縁膜に形成された前記凹部の側壁をプラズマ処理する

請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記凹部が形成された前記絶縁膜上に、前記第1のバリア膜として金属窒化膜を成膜し、

前記金属窒化膜上に前記第2の金属膜を成膜する前に、窒素を含むガス雰囲気中において、前記金属窒化膜をプラズマ処理する

請求項1から請求項3のいずれかに記載の半導体装置の製造方法。

【請求項5】

前記第1のバリア膜、前記第2のバリア膜、前記めっきのシード膜を、真空を維持した状態で、成膜する

請求項1から請求項4のいずれかに記載の半導体装置の製造方法。

【請求項6】

Siを主成分とする絶縁膜と、前記絶縁膜に形成された凹部に設けられた配線との間にバリア構造を有する半導体装置であって、

前記絶縁膜と接し、金属を主成分とする第1のバリア膜と、

前記第1のバリア膜と接し、前記第1のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とする第2のバリア膜と、

前記第2のバリア膜と接し、前記第2のバリア膜の主成分よりも熱膨張係数が大きく、かつ前記配線の主成分よりも熱膨張係数が同じまたは小さい金属を主成分とするめっきのシード膜とを備える

半導体装置。

【請求項1】

Siを主成分とする絶縁膜と、前記絶縁膜に形成された凹部に設けられた配線との間にバリア構造を有する半導体装置の製造方法であって、

前記凹部が形成された前記絶縁膜上に、金属を主成分とする第1のバリア膜を成膜する工程と、

前記第1のバリア膜上に、前記第1のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とする第2のバリア膜を成膜する工程と、

前記第2の金属膜上に、前記第2のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とするめっきのシード膜を成膜する工程と、

前記めっきのシード膜の主成分よりも熱膨張係数が同じまたは大きい金属を、めっきにより、前記凹部内に埋め込む工程とを含む

半導体装置の製造方法。

【請求項2】

前記第1のバリア膜上に前記第2のバリア膜を成膜する前に、逆スパッタにより、前記第1のバリア膜の前記凹部底部分をエッチングする

請求項1に記載の半導体装置の製造方法。

【請求項3】

前記凹部が形成された前記絶縁膜上に前記第1の金属膜を成膜する前に、窒素を含むガス雰囲気中において、前記絶縁膜に形成された前記凹部の側壁をプラズマ処理する

請求項1または請求項2に記載の半導体装置の製造方法。

【請求項4】

前記凹部が形成された前記絶縁膜上に、前記第1のバリア膜として金属窒化膜を成膜し、

前記金属窒化膜上に前記第2の金属膜を成膜する前に、窒素を含むガス雰囲気中において、前記金属窒化膜をプラズマ処理する

請求項1から請求項3のいずれかに記載の半導体装置の製造方法。

【請求項5】

前記第1のバリア膜、前記第2のバリア膜、前記めっきのシード膜を、真空を維持した状態で、成膜する

請求項1から請求項4のいずれかに記載の半導体装置の製造方法。

【請求項6】

Siを主成分とする絶縁膜と、前記絶縁膜に形成された凹部に設けられた配線との間にバリア構造を有する半導体装置であって、

前記絶縁膜と接し、金属を主成分とする第1のバリア膜と、

前記第1のバリア膜と接し、前記第1のバリア膜の主成分よりも熱膨張係数が大きい金属を主成分とする第2のバリア膜と、

前記第2のバリア膜と接し、前記第2のバリア膜の主成分よりも熱膨張係数が大きく、かつ前記配線の主成分よりも熱膨張係数が同じまたは小さい金属を主成分とするめっきのシード膜とを備える

半導体装置。

【図1】

【図2】

【図4】

【図5】

【図6】

【図7】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図3】

【公開番号】特開2011−151217(P2011−151217A)

【公開日】平成23年8月4日(2011.8.4)

【国際特許分類】

【出願番号】特願2010−11511(P2010−11511)

【出願日】平成22年1月22日(2010.1.22)

【出願人】(000005821)パナソニック株式会社 (73,050)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年8月4日(2011.8.4)

【国際特許分類】

【出願日】平成22年1月22日(2010.1.22)

【出願人】(000005821)パナソニック株式会社 (73,050)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]