半導体装置の製造方法

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

車載用デバイスにおいて用いられるパワーMOS(Metal Oxide Semiconductor)−FET(Field effect transistor)としては、LDMOS(Laterally Diffused MOS)が用いられている。

【0003】

LDMOSの構成の一例は、特許文献1に記載されている。具体的には、図1にLDMOSのソース部の断面図を示す。LDMOSは、半導体基板101の深い側から順に、N型層102、P型ボディ層103を形成し、更に半導体基板101の表面にN+層104とP+層105を形成し、半導体基板101の表面に形成された絶縁膜106に開口部を形成し、P+層105と接続されるソース電極107が形成されている構造のものである。尚、絶縁膜106内には、絶縁膜106の一部をゲート絶縁膜とするゲート電極108が形成されている。

【0004】

一方、LDMOSでは、車載用デバイスにおける低損失化を目的として、低オン抵抗化が求められている。このような低オン抵抗化を達成するためには、LDMOSの素子サイズを縮小化する方法が考えられる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第6538281号明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、引用文献1に記載されている構造のLDMOSを製造する場合、半導体基板101の表面にN+層104となる領域とP+層105となる領域とを形成する必要がある。図2は、半導体基板101の表面に形成されるN+層104となる領域とP+層105となる領域を示すものである。このようにN+層104となる領域とP+層105となる領域とを形成する場合、一般的には、半導体基板101の表面に、N+層104となる領域が形成される部分に開口部を有するレジストパターンを形成し、N+層104を形成するための不純物元素のイオン注入を行う。この後、このレジストパターンを除去し、P+層105となる領域が形成される部分に開口部を有する別のレジストパターンを形成し、P+層105を形成するための不純物元素のイオン注入を行う。即ち、基板101の表面にN+層104となる領域とP+層105となる領域とを形成する場合、2回レジストパターンを形成する必要がある。尚、レジストパターンは、基板101表面に、フォトレジストを塗布し、露光装置による露光、現像を行うことにより形成される。このようなレジストパターンを形成する際、形成されるレジストパターンの位置の位置合せ精度により、図3に示すように、N+層104となる領域とP+層105となる領域との間に、N+層104を形成するための不純物元素とP+層105を形成するための不純物元素とが共に注入された無効領域110が形成されてしまう。このため、実際の設計では、無効領域110を考慮して大きめに設計する必要があり、このような設計によりLDMOSが大型化してしまい、オン抵抗を低減させることができなかった。尚、無効領域110の幅Aは、通常、露光装置による精度マージンが2乗平均を用いて見積もられているため、露光装置による位置合せ精度をBとした場合、A=B×21/2×2として見積もられる。よって、位置合せ精度の高い露光装置を用いることにより対応する方法も考えられるが、位置合せ精度の高い露光装置は極めて高価であり、製造される半導体装置のコストアップにつながるため、望まし方法とはいえない。

【0007】

よって、本発明は、製造される半導体装置をコストアップさせることなく、無効領域が形成されることのない、オン抵抗の低い半導体装置の製造方法を提供することを目的とするものである。

【課題を解決するための手段】

【0008】

本発明は、半導体基板上に形成されるソース領域は、第2の導電型の半導体領域が第1の導電型の半導体領域により挟まれた形状のストライプ状に形成されており、ソース電極が前記第2の導電型の半導体領域に物理的に接続されるとともに、電気的に前記第1の導電型の半導体領域にも接続されている構造の半導体装置の製造方法において、前記半導体基板上に、ゲート酸化膜を介しゲート電極を形成するゲート電極形成工程と、前記ゲート電極間を含む領域であって、前記ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する第1のレジストパターン形成工程と、前記第1の開口部において露出している前記半導体基板の表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、前記ゲート電極間において、前記ゲート電極間よりも狭い第2の開口部を有する層間絶縁膜を形成する層間絶縁膜形成工程と、前記第2の開口部を含む領域であって、前記第2の開口部よりも広い第3の開口部を有する第2のレジストパターンを形成する第2のレジストパターン形成工程と、前記第3の開口部において露出している前記半導体基板の表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、前記第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、前記第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

【0009】

また、本発明は、前記第2のイオン注入工程において注入される第2の導電型の不純物元素の注入エネルギーは、前記第1のイオン注入工程において注入される第1の導電型の不純物元素の注入エネルギーよりも高い値であることを特徴とする。

【0010】

また、本発明は、前記第1のイオン注入工程と前記層間絶縁膜形成工程との間に行われ、前記半導体基板の前記ゲート電極間にシリサイド層を形成するシリサイド層形成工程と、前記第2のイオン注入工程の後に、前記シリサイド層が露出している領域に前記ソース電極を形成するソース電極形成工程と、を有することを特徴とする。

【発明の効果】

【0011】

本発明によれば、製造される半導体装置をコストアップさせることなく、無効領域が形成されることのない半導体装置の製造方法を提供することができる。これにより、製造される半導体装置を小型化させることができ、オン抵抗を低くすることができる。

【図面の簡単な説明】

【0012】

【図1】LDMOSの構造図

【図2】LDMOSに形成されるN+層とP+層の配置図

【図3】N+層とP+層との間に形成される無効領域の説明図

【図4】本実施の形態における半導体装置の製造方法の工程図(1)

【図5】本実施の形態における半導体装置の製造方法の工程図(2)

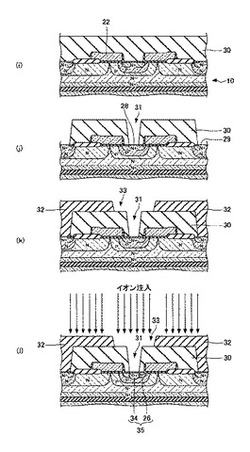

【図6】本実施の形態における半導体装置の製造方法の工程図(3)

【図7】本実施の形態における半導体装置の製造方法の工程図(4)

【発明を実施するための形態】

【0013】

本発明を実施するための形態について、以下に説明する。

【0014】

本実施の形態は、半導体装置の製造方法であり、小型化されたON抵抗の低いLDMOSの製造方法である。

【0015】

図4から図7に基づき、本実施の形態における半導体装置の製造方法について説明する。

【0016】

最初に、図4(a)に示すように、SOI(Silicon on Insulator)基板10を準備する。SOI基板10は、支持基板11上に、酸化シリコンからなるBOX層12が形成され、更に、その上に、N+型埋め込み層13、N−型活性層14が形成されている。尚、本実施の形態の説明の都合上、SOI基板10を用いた場合について説明するが、SOI基板以外の通常のシリコン基板等の半導体基板を用いた場合においても、本実施の形態を実施することは可能である。

【0017】

次に、図4(b)に示すように、SOI基板10の表面、即ち、N−型活性層14の表面の一部に、LOCOS(Local Oxidation of Silicon)15構造の素子分離領域を形成する。LOCOS15は、N−型活性層14の表面の一部を熱酸化することにより形成する。尚、素子分離領域は、上述したLOCOS15構造以外にも、STI(Shallow Trench Isolation)構造により形成してもよい。

【0018】

次に、図4(c)に示すように、SOI基板10の表面、即ち、N−型活性層14のLOCOS15が形成されていない領域に犠牲酸化膜16を形成し、不純物元素のイオン注入及び熱処理を行うことにより、N型ドリフト層17、P型ボディ層18、LVPW(Low Voltage P-Well)領域19、LVNW(Low Voltage N-Well)領域20を形成する。

【0019】

次に、図4(d)に示すように、犠牲酸化膜16を除去し、ゲート酸化膜21及びゲートポリサイドからなるゲート電極22を形成する。具体的には、犠牲酸化膜16を除去した後に、ゲート酸化膜となる酸化膜を形成し、さらに、ポリシリコンの成膜及びWSiのスパッタリング成膜を行う。この後、フォトレジストを塗布し、露光装置による露光、現像を行うことにより、ゲート酸化膜21及びポリシリコンとWSiからなるゲート電極22が形成される領域に開口部を有するレジストパターンを形成する。この後、RIE(Reactive Ion Etching)等によるドライエッチングを行うことにより、ゲート酸化膜21及びゲート電極22を形成する。尚、ドライエッチングを行った後に、レジストパターンは除去される。

【0020】

次に、図5(e)に示すように、サイドウォール23を形成する。具体的には、サイドウォール形成前に、不純物元素のイオン注入(LDD注入)を行うことにより、LDD(Lightly Doped Drain)構造を形成する(図中のLDD拡散層は省略されている。)。そして、ゲート電極22の側面に酸化シリコン等の絶縁膜からなるサイドウォール23を形成する。

【0021】

次に、図5(f)に示すように、N型の不純物元素のイオン注入するためのレジストパターン(第1のレジストパターン)24を形成する。具体的には、SOI基板10上のゲート電極22の形成されている面に、フォトレジストを塗布し、露光装置による露光、現像を行う。これにより、後にN型の不純物元素をイオン注入するための開口部(第1の開口部)25を有するレジストパターン24を形成する。尚、レジストパターン24の開口部25は、サイドウォール23の形成されているゲート電極22間よりも広い領域であって、サイドウォール23の形成されているゲート電極22間を含む領域に形成される。よって、レジストパターン24の開口部25には、ゲート電極22とサイドウォール23の一部が露出している。

【0022】

次に、図5(g)に示すように、イオン注入を行いN+型ソース領域26及びN+型ドレイン領域27を形成する。具体的には、不純物元素としてAsを2×1015cm−2、70KeVでイオン注入する。これにより、N+型ソース領域26及びN+型ドレイン領域27を形成する。尚、実際にイオン注入される領域は、レジストパターン24の開口部25よりも狭く、ゲート電極22とサイドウォール23の形成されている領域間の領域である。よって、レジストパターン24が形成される位置の位置合せ精度が多少ずれたとしても、形成されるN+型ソース領域26の位置に影響を与えることはない。また、N+型ドレイン領域27についても同様であり、図に示すように、LOCOS15の外側の領域に形成されるため、レジストパターン24が形成される位置の位置合せ精度が多少ずれたとしても、形成されるN+型ドレイン領域27の位置に影響を与えることはない。

【0023】

次に、図5(h)に示すように、N+型ソース領域26及びN+型ドレイン領域27上にシリサイド層28及び29を形成する。シリサイド層28及び29を形成するシリサイド材料としては、TiSi、CoSi等のWSi以外の材料が好ましい。これらのシリサイド材料は、これらのシリサイド材料を介して、イオン注入を行うことが可能であるからである。

【0024】

次に、図6(i)に示すように、層間絶縁膜30を形成する。層間絶縁膜30は、SOI基板10上のゲート電極22の形成されている面に成膜する。具体的には、層間絶縁膜30は、CVD(Chemical Vapor Deposition)により酸化シリコン等の絶縁膜をゲート電極22の高さよりも十分厚く成膜し、この後、酸化膜CMP(Chemical Mechanical Polishing)により平坦化を行うことにより形成する。

【0025】

次に、図6(j)に示すように、層間絶縁膜30に開口部(第2の開口部)31を形成する。具体的には、層間絶縁膜30上に開口部31の形成される領域に開口領域を有する不図示のマスクを形成し、RIE等のドライエッチングにより、マスクの開口領域における層間絶縁膜30を除去する。RIE等による層間絶縁膜30のドライエッチングは、シリサイド層28及び29の表面が露出するまで行う。これにより層間絶縁膜30に開口部31を形成する。

【0026】

次に、図6(k)に示すように、P型の不純物元素のイオン注入するためのレジストパターン(第2のレジストパターン)32を形成する。具体的には、SOI基板10上の層間絶縁膜30の形成されている面に、フォトレジストを塗布し、露光装置による露光、現像を行う。これにより、後の工程においてP型の不純物元素をイオン注入するための開口部(第3の開口部)33を有するレジストパターン32を形成する。尚、レジストパターン(第2のレジストパターン)32に形成される開口部(第3の開口部)33は、層間絶縁膜30に形成される開口部(第2の開口部)31よりも広い領域であって、開口部(第2の開口部)31を含む領域に形成される。このため、開口部(第3の開口部)33において、層間絶縁膜30の一部が露出している。

【0027】

次に、図6(l)に示すように、イオン注入を行いP+型バックゲート領域34を形成する。具体的には、不純物としてBF2を1×1016cm−2、100KeVでイオン注入する。これにより、P+型バックゲート領域34を形成する。尚、実際にイオン注入される領域は、レジストパターン32の開口部33よりも狭い、層間絶縁膜30の開口部31である。よって、レジストパターン32が形成される位置の位置合せ精度が多少ずれたとしても、P+型バックゲート領域34の形成される位置に影響を与えることはない。また、P+型バックゲート領域34は、N+型ソース領域26が形成されている領域の一部に形成されるものであるため、N+型ソース領域26を形成するために注入された不純物濃度の2倍以上の不純物元素をイオン注入することが好ましい。少なくとも2倍以上であれば、イオン注入された領域は、P+型の領域とすることができるものと考えられるからである。また、より好ましくは5倍以上の不純物元素をイオン注入することが好ましい。5倍以上であれば、ほぼ確実にP+型の領域とすることができるものと考えられるからである。また、P+型バックゲート領域34は、N+型ソース領域26よりも深い位置に形成されることが好ましいため、P+型バックゲート領域34を形成するためのイオン注入のエネルギーは、N+型ソース領域26を形成するためのイオン注入のエネルギーよりも高い値であることが好ましい。尚、N+型ソース領域26とP+型バックゲート領域34とによりソース領域35が形成される。これによりソース領域35は、P+型バックゲート領域34がN+型ソース領域26により挟まれたストライプ状に形成される。

【0028】

次に、図7(m)に示すように、W(タングステン)プラグコンタクト層36及び37を形成する。具体的には、レジストパターン32を除去した後、SOI基板10上の層間絶縁膜30の形成されている面に、CVDにより開口部31が完全に埋め込まれるまでW膜を成膜し、この後、CMP(Chemical Mechanical Polishing)により層間絶縁膜30の表面に形成されているW膜を除去する。これにより、層間絶縁膜30の開口部31に、埋め込みW層となるWプラグコンタクト層36及び37を形成する。このようにして、シリサイド層28を介しソース領域35におけるP+型バックゲート領域34と物理的に接続され、電気的にはN+型ソース領域26とも接続されているWプラグコンタクト層36と、シリサイド層29を介しN+型ドレイン領域27と接続されるWプラグコンタクト層37とが形成される。

【0029】

次に、図7(n)に示すように、Wプラグコンタクト層36と接続されるソース電極38及びWプラグコンタクト層37と接続されるドレイン電極39を形成する。ソース電極38及びドレイン電極39は、例えば、アルミニウム(Al)により形成されるものであり、Alの成膜工程とフォトレジストと露光装置を用いたフォトリソグラフィ工程とエッチング等の工程とを組み合わせた工程により形成することができる。

【0030】

以上より、本実施の形態における半導体装置の製造方法により半導体装置を製造することができる。

【0031】

本実施の形態における半導体装置では、レジストパターンの形成を2回行うことにより、N+型ソース領域26及びP+型バックゲート領域34を形成するものであるが、図5(g)、図6(l)に示されるように、N+型ソース領域26及びP+型バックゲート領域34の形成される領域は、形成されたレジストパターンにより画定されるものではない。即ち、N+型ソース領域26については、LOCOS15、ゲート電極22及びサイドウォール23の形成されていない領域に自己整合的に形成され、P+型バックゲート領域34については、層間絶縁膜30の形成されていない開口部31に自己整合的に形成される。

【0032】

よって、本実施の形態では、形成されるレジストパターンの位置の位置合せ精度に依存することなく、所望の領域に正確にN+型ソース領域26及びP+型バックゲート領域34を形成することができ無効領域が形成されない。従って、従来技術に記載されているような無効領域を考慮した半導体装置の設計をする必要がなく、オン抵抗の低い半導体装置を製造することが可能である。

【0033】

以上、本発明の実施に係る形態について説明したが、上記内容は、発明の内容を限定するものではない。

【符号の説明】

【0034】

10 SOI基板

11 支持基板

12 BOX層

13 N+型埋め込み層

14 N−型活性層

15 LOCOS

16 犠牲酸化膜

17 N型ドリフト層

18 P型ボディ層

19 LVPW領域

20 LVNW領域

21 ゲート酸化膜

22 ゲート電極

23 サイドウォール

24 レジストパターン(第1のレジストパターン)

25 開口部(第1の開口部)

26 N+型ソース領域

27 N+型ドレイン領域

28 シリサイド層

29 シリサイド層

30 層間絶縁膜

31 開口部(第2の開口部)

32 レジストパターン(第2のレジストパターン)

33 開口部(第3の開口部)

34 P+型バックゲート領域

35 ソース領域

36 Wプラグコンタクト層

37 Wプラグコンタクト層

38 ソース電極

39 ドレイン電極

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

車載用デバイスにおいて用いられるパワーMOS(Metal Oxide Semiconductor)−FET(Field effect transistor)としては、LDMOS(Laterally Diffused MOS)が用いられている。

【0003】

LDMOSの構成の一例は、特許文献1に記載されている。具体的には、図1にLDMOSのソース部の断面図を示す。LDMOSは、半導体基板101の深い側から順に、N型層102、P型ボディ層103を形成し、更に半導体基板101の表面にN+層104とP+層105を形成し、半導体基板101の表面に形成された絶縁膜106に開口部を形成し、P+層105と接続されるソース電極107が形成されている構造のものである。尚、絶縁膜106内には、絶縁膜106の一部をゲート絶縁膜とするゲート電極108が形成されている。

【0004】

一方、LDMOSでは、車載用デバイスにおける低損失化を目的として、低オン抵抗化が求められている。このような低オン抵抗化を達成するためには、LDMOSの素子サイズを縮小化する方法が考えられる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第6538281号明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、引用文献1に記載されている構造のLDMOSを製造する場合、半導体基板101の表面にN+層104となる領域とP+層105となる領域とを形成する必要がある。図2は、半導体基板101の表面に形成されるN+層104となる領域とP+層105となる領域を示すものである。このようにN+層104となる領域とP+層105となる領域とを形成する場合、一般的には、半導体基板101の表面に、N+層104となる領域が形成される部分に開口部を有するレジストパターンを形成し、N+層104を形成するための不純物元素のイオン注入を行う。この後、このレジストパターンを除去し、P+層105となる領域が形成される部分に開口部を有する別のレジストパターンを形成し、P+層105を形成するための不純物元素のイオン注入を行う。即ち、基板101の表面にN+層104となる領域とP+層105となる領域とを形成する場合、2回レジストパターンを形成する必要がある。尚、レジストパターンは、基板101表面に、フォトレジストを塗布し、露光装置による露光、現像を行うことにより形成される。このようなレジストパターンを形成する際、形成されるレジストパターンの位置の位置合せ精度により、図3に示すように、N+層104となる領域とP+層105となる領域との間に、N+層104を形成するための不純物元素とP+層105を形成するための不純物元素とが共に注入された無効領域110が形成されてしまう。このため、実際の設計では、無効領域110を考慮して大きめに設計する必要があり、このような設計によりLDMOSが大型化してしまい、オン抵抗を低減させることができなかった。尚、無効領域110の幅Aは、通常、露光装置による精度マージンが2乗平均を用いて見積もられているため、露光装置による位置合せ精度をBとした場合、A=B×21/2×2として見積もられる。よって、位置合せ精度の高い露光装置を用いることにより対応する方法も考えられるが、位置合せ精度の高い露光装置は極めて高価であり、製造される半導体装置のコストアップにつながるため、望まし方法とはいえない。

【0007】

よって、本発明は、製造される半導体装置をコストアップさせることなく、無効領域が形成されることのない、オン抵抗の低い半導体装置の製造方法を提供することを目的とするものである。

【課題を解決するための手段】

【0008】

本発明は、半導体基板上に形成されるソース領域は、第2の導電型の半導体領域が第1の導電型の半導体領域により挟まれた形状のストライプ状に形成されており、ソース電極が前記第2の導電型の半導体領域に物理的に接続されるとともに、電気的に前記第1の導電型の半導体領域にも接続されている構造の半導体装置の製造方法において、前記半導体基板上に、ゲート酸化膜を介しゲート電極を形成するゲート電極形成工程と、前記ゲート電極間を含む領域であって、前記ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する第1のレジストパターン形成工程と、前記第1の開口部において露出している前記半導体基板の表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、前記ゲート電極間において、前記ゲート電極間よりも狭い第2の開口部を有する層間絶縁膜を形成する層間絶縁膜形成工程と、前記第2の開口部を含む領域であって、前記第2の開口部よりも広い第3の開口部を有する第2のレジストパターンを形成する第2のレジストパターン形成工程と、前記第3の開口部において露出している前記半導体基板の表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、前記第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、前記第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

【0009】

また、本発明は、前記第2のイオン注入工程において注入される第2の導電型の不純物元素の注入エネルギーは、前記第1のイオン注入工程において注入される第1の導電型の不純物元素の注入エネルギーよりも高い値であることを特徴とする。

【0010】

また、本発明は、前記第1のイオン注入工程と前記層間絶縁膜形成工程との間に行われ、前記半導体基板の前記ゲート電極間にシリサイド層を形成するシリサイド層形成工程と、前記第2のイオン注入工程の後に、前記シリサイド層が露出している領域に前記ソース電極を形成するソース電極形成工程と、を有することを特徴とする。

【発明の効果】

【0011】

本発明によれば、製造される半導体装置をコストアップさせることなく、無効領域が形成されることのない半導体装置の製造方法を提供することができる。これにより、製造される半導体装置を小型化させることができ、オン抵抗を低くすることができる。

【図面の簡単な説明】

【0012】

【図1】LDMOSの構造図

【図2】LDMOSに形成されるN+層とP+層の配置図

【図3】N+層とP+層との間に形成される無効領域の説明図

【図4】本実施の形態における半導体装置の製造方法の工程図(1)

【図5】本実施の形態における半導体装置の製造方法の工程図(2)

【図6】本実施の形態における半導体装置の製造方法の工程図(3)

【図7】本実施の形態における半導体装置の製造方法の工程図(4)

【発明を実施するための形態】

【0013】

本発明を実施するための形態について、以下に説明する。

【0014】

本実施の形態は、半導体装置の製造方法であり、小型化されたON抵抗の低いLDMOSの製造方法である。

【0015】

図4から図7に基づき、本実施の形態における半導体装置の製造方法について説明する。

【0016】

最初に、図4(a)に示すように、SOI(Silicon on Insulator)基板10を準備する。SOI基板10は、支持基板11上に、酸化シリコンからなるBOX層12が形成され、更に、その上に、N+型埋め込み層13、N−型活性層14が形成されている。尚、本実施の形態の説明の都合上、SOI基板10を用いた場合について説明するが、SOI基板以外の通常のシリコン基板等の半導体基板を用いた場合においても、本実施の形態を実施することは可能である。

【0017】

次に、図4(b)に示すように、SOI基板10の表面、即ち、N−型活性層14の表面の一部に、LOCOS(Local Oxidation of Silicon)15構造の素子分離領域を形成する。LOCOS15は、N−型活性層14の表面の一部を熱酸化することにより形成する。尚、素子分離領域は、上述したLOCOS15構造以外にも、STI(Shallow Trench Isolation)構造により形成してもよい。

【0018】

次に、図4(c)に示すように、SOI基板10の表面、即ち、N−型活性層14のLOCOS15が形成されていない領域に犠牲酸化膜16を形成し、不純物元素のイオン注入及び熱処理を行うことにより、N型ドリフト層17、P型ボディ層18、LVPW(Low Voltage P-Well)領域19、LVNW(Low Voltage N-Well)領域20を形成する。

【0019】

次に、図4(d)に示すように、犠牲酸化膜16を除去し、ゲート酸化膜21及びゲートポリサイドからなるゲート電極22を形成する。具体的には、犠牲酸化膜16を除去した後に、ゲート酸化膜となる酸化膜を形成し、さらに、ポリシリコンの成膜及びWSiのスパッタリング成膜を行う。この後、フォトレジストを塗布し、露光装置による露光、現像を行うことにより、ゲート酸化膜21及びポリシリコンとWSiからなるゲート電極22が形成される領域に開口部を有するレジストパターンを形成する。この後、RIE(Reactive Ion Etching)等によるドライエッチングを行うことにより、ゲート酸化膜21及びゲート電極22を形成する。尚、ドライエッチングを行った後に、レジストパターンは除去される。

【0020】

次に、図5(e)に示すように、サイドウォール23を形成する。具体的には、サイドウォール形成前に、不純物元素のイオン注入(LDD注入)を行うことにより、LDD(Lightly Doped Drain)構造を形成する(図中のLDD拡散層は省略されている。)。そして、ゲート電極22の側面に酸化シリコン等の絶縁膜からなるサイドウォール23を形成する。

【0021】

次に、図5(f)に示すように、N型の不純物元素のイオン注入するためのレジストパターン(第1のレジストパターン)24を形成する。具体的には、SOI基板10上のゲート電極22の形成されている面に、フォトレジストを塗布し、露光装置による露光、現像を行う。これにより、後にN型の不純物元素をイオン注入するための開口部(第1の開口部)25を有するレジストパターン24を形成する。尚、レジストパターン24の開口部25は、サイドウォール23の形成されているゲート電極22間よりも広い領域であって、サイドウォール23の形成されているゲート電極22間を含む領域に形成される。よって、レジストパターン24の開口部25には、ゲート電極22とサイドウォール23の一部が露出している。

【0022】

次に、図5(g)に示すように、イオン注入を行いN+型ソース領域26及びN+型ドレイン領域27を形成する。具体的には、不純物元素としてAsを2×1015cm−2、70KeVでイオン注入する。これにより、N+型ソース領域26及びN+型ドレイン領域27を形成する。尚、実際にイオン注入される領域は、レジストパターン24の開口部25よりも狭く、ゲート電極22とサイドウォール23の形成されている領域間の領域である。よって、レジストパターン24が形成される位置の位置合せ精度が多少ずれたとしても、形成されるN+型ソース領域26の位置に影響を与えることはない。また、N+型ドレイン領域27についても同様であり、図に示すように、LOCOS15の外側の領域に形成されるため、レジストパターン24が形成される位置の位置合せ精度が多少ずれたとしても、形成されるN+型ドレイン領域27の位置に影響を与えることはない。

【0023】

次に、図5(h)に示すように、N+型ソース領域26及びN+型ドレイン領域27上にシリサイド層28及び29を形成する。シリサイド層28及び29を形成するシリサイド材料としては、TiSi、CoSi等のWSi以外の材料が好ましい。これらのシリサイド材料は、これらのシリサイド材料を介して、イオン注入を行うことが可能であるからである。

【0024】

次に、図6(i)に示すように、層間絶縁膜30を形成する。層間絶縁膜30は、SOI基板10上のゲート電極22の形成されている面に成膜する。具体的には、層間絶縁膜30は、CVD(Chemical Vapor Deposition)により酸化シリコン等の絶縁膜をゲート電極22の高さよりも十分厚く成膜し、この後、酸化膜CMP(Chemical Mechanical Polishing)により平坦化を行うことにより形成する。

【0025】

次に、図6(j)に示すように、層間絶縁膜30に開口部(第2の開口部)31を形成する。具体的には、層間絶縁膜30上に開口部31の形成される領域に開口領域を有する不図示のマスクを形成し、RIE等のドライエッチングにより、マスクの開口領域における層間絶縁膜30を除去する。RIE等による層間絶縁膜30のドライエッチングは、シリサイド層28及び29の表面が露出するまで行う。これにより層間絶縁膜30に開口部31を形成する。

【0026】

次に、図6(k)に示すように、P型の不純物元素のイオン注入するためのレジストパターン(第2のレジストパターン)32を形成する。具体的には、SOI基板10上の層間絶縁膜30の形成されている面に、フォトレジストを塗布し、露光装置による露光、現像を行う。これにより、後の工程においてP型の不純物元素をイオン注入するための開口部(第3の開口部)33を有するレジストパターン32を形成する。尚、レジストパターン(第2のレジストパターン)32に形成される開口部(第3の開口部)33は、層間絶縁膜30に形成される開口部(第2の開口部)31よりも広い領域であって、開口部(第2の開口部)31を含む領域に形成される。このため、開口部(第3の開口部)33において、層間絶縁膜30の一部が露出している。

【0027】

次に、図6(l)に示すように、イオン注入を行いP+型バックゲート領域34を形成する。具体的には、不純物としてBF2を1×1016cm−2、100KeVでイオン注入する。これにより、P+型バックゲート領域34を形成する。尚、実際にイオン注入される領域は、レジストパターン32の開口部33よりも狭い、層間絶縁膜30の開口部31である。よって、レジストパターン32が形成される位置の位置合せ精度が多少ずれたとしても、P+型バックゲート領域34の形成される位置に影響を与えることはない。また、P+型バックゲート領域34は、N+型ソース領域26が形成されている領域の一部に形成されるものであるため、N+型ソース領域26を形成するために注入された不純物濃度の2倍以上の不純物元素をイオン注入することが好ましい。少なくとも2倍以上であれば、イオン注入された領域は、P+型の領域とすることができるものと考えられるからである。また、より好ましくは5倍以上の不純物元素をイオン注入することが好ましい。5倍以上であれば、ほぼ確実にP+型の領域とすることができるものと考えられるからである。また、P+型バックゲート領域34は、N+型ソース領域26よりも深い位置に形成されることが好ましいため、P+型バックゲート領域34を形成するためのイオン注入のエネルギーは、N+型ソース領域26を形成するためのイオン注入のエネルギーよりも高い値であることが好ましい。尚、N+型ソース領域26とP+型バックゲート領域34とによりソース領域35が形成される。これによりソース領域35は、P+型バックゲート領域34がN+型ソース領域26により挟まれたストライプ状に形成される。

【0028】

次に、図7(m)に示すように、W(タングステン)プラグコンタクト層36及び37を形成する。具体的には、レジストパターン32を除去した後、SOI基板10上の層間絶縁膜30の形成されている面に、CVDにより開口部31が完全に埋め込まれるまでW膜を成膜し、この後、CMP(Chemical Mechanical Polishing)により層間絶縁膜30の表面に形成されているW膜を除去する。これにより、層間絶縁膜30の開口部31に、埋め込みW層となるWプラグコンタクト層36及び37を形成する。このようにして、シリサイド層28を介しソース領域35におけるP+型バックゲート領域34と物理的に接続され、電気的にはN+型ソース領域26とも接続されているWプラグコンタクト層36と、シリサイド層29を介しN+型ドレイン領域27と接続されるWプラグコンタクト層37とが形成される。

【0029】

次に、図7(n)に示すように、Wプラグコンタクト層36と接続されるソース電極38及びWプラグコンタクト層37と接続されるドレイン電極39を形成する。ソース電極38及びドレイン電極39は、例えば、アルミニウム(Al)により形成されるものであり、Alの成膜工程とフォトレジストと露光装置を用いたフォトリソグラフィ工程とエッチング等の工程とを組み合わせた工程により形成することができる。

【0030】

以上より、本実施の形態における半導体装置の製造方法により半導体装置を製造することができる。

【0031】

本実施の形態における半導体装置では、レジストパターンの形成を2回行うことにより、N+型ソース領域26及びP+型バックゲート領域34を形成するものであるが、図5(g)、図6(l)に示されるように、N+型ソース領域26及びP+型バックゲート領域34の形成される領域は、形成されたレジストパターンにより画定されるものではない。即ち、N+型ソース領域26については、LOCOS15、ゲート電極22及びサイドウォール23の形成されていない領域に自己整合的に形成され、P+型バックゲート領域34については、層間絶縁膜30の形成されていない開口部31に自己整合的に形成される。

【0032】

よって、本実施の形態では、形成されるレジストパターンの位置の位置合せ精度に依存することなく、所望の領域に正確にN+型ソース領域26及びP+型バックゲート領域34を形成することができ無効領域が形成されない。従って、従来技術に記載されているような無効領域を考慮した半導体装置の設計をする必要がなく、オン抵抗の低い半導体装置を製造することが可能である。

【0033】

以上、本発明の実施に係る形態について説明したが、上記内容は、発明の内容を限定するものではない。

【符号の説明】

【0034】

10 SOI基板

11 支持基板

12 BOX層

13 N+型埋め込み層

14 N−型活性層

15 LOCOS

16 犠牲酸化膜

17 N型ドリフト層

18 P型ボディ層

19 LVPW領域

20 LVNW領域

21 ゲート酸化膜

22 ゲート電極

23 サイドウォール

24 レジストパターン(第1のレジストパターン)

25 開口部(第1の開口部)

26 N+型ソース領域

27 N+型ドレイン領域

28 シリサイド層

29 シリサイド層

30 層間絶縁膜

31 開口部(第2の開口部)

32 レジストパターン(第2のレジストパターン)

33 開口部(第3の開口部)

34 P+型バックゲート領域

35 ソース領域

36 Wプラグコンタクト層

37 Wプラグコンタクト層

38 ソース電極

39 ドレイン電極

【特許請求の範囲】

【請求項1】

半導体基板上に形成されるソース領域は、第2の導電型の半導体領域が第1の導電型の半導体領域により挟まれた形状のストライプ状に形成されており、ソース電極が前記第2の導電型の半導体領域に物理的に接続されるとともに、電気的には前記第1の導電型の半導体領域にも接続されている構造の半導体装置の製造方法において、

前記半導体基板上に、ゲート酸化膜を介しゲート電極を形成するゲート電極形成工程と、

前記ゲート電極間を含む領域であって、前記ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する第1のレジストパターン形成工程と、

前記第1の開口部において露出している前記半導体基板の表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、

前記ゲート電極間において、前記ゲート電極間よりも狭い第2の開口部を有する層間絶縁膜を形成する層間絶縁膜形成工程と、

前記第2の開口部を含む領域であって、前記第2の開口部よりも広い第3の開口部を有する第2のレジストパターンを形成する第2のレジストパターン形成工程と、

前記第3の開口部において露出している前記半導体基板の表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、

を有し、

前記第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、前記第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする半導体装置の製造方法。

【請求項2】

前記第2のイオン注入工程において注入される第2の導電型の不純物元素の注入エネルギーは、前記第1のイオン注入工程において注入される第1の導電型の不純物元素の注入エネルギーよりも高い値であることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1のイオン注入工程と前記層間絶縁膜形成工程との間に行われ、前記半導体基板の前記ゲート電極間にシリサイド層を形成するシリサイド層形成工程と、

前記第2のイオン注入工程の後に、前記シリサイド層が露出している領域に前記ソース電極を形成するソース電極形成工程と、

を有することを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項1】

半導体基板上に形成されるソース領域は、第2の導電型の半導体領域が第1の導電型の半導体領域により挟まれた形状のストライプ状に形成されており、ソース電極が前記第2の導電型の半導体領域に物理的に接続されるとともに、電気的には前記第1の導電型の半導体領域にも接続されている構造の半導体装置の製造方法において、

前記半導体基板上に、ゲート酸化膜を介しゲート電極を形成するゲート電極形成工程と、

前記ゲート電極間を含む領域であって、前記ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する第1のレジストパターン形成工程と、

前記第1の開口部において露出している前記半導体基板の表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、

前記ゲート電極間において、前記ゲート電極間よりも狭い第2の開口部を有する層間絶縁膜を形成する層間絶縁膜形成工程と、

前記第2の開口部を含む領域であって、前記第2の開口部よりも広い第3の開口部を有する第2のレジストパターンを形成する第2のレジストパターン形成工程と、

前記第3の開口部において露出している前記半導体基板の表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、

を有し、

前記第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、前記第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする半導体装置の製造方法。

【請求項2】

前記第2のイオン注入工程において注入される第2の導電型の不純物元素の注入エネルギーは、前記第1のイオン注入工程において注入される第1の導電型の不純物元素の注入エネルギーよりも高い値であることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1のイオン注入工程と前記層間絶縁膜形成工程との間に行われ、前記半導体基板の前記ゲート電極間にシリサイド層を形成するシリサイド層形成工程と、

前記第2のイオン注入工程の後に、前記シリサイド層が露出している領域に前記ソース電極を形成するソース電極形成工程と、

を有することを特徴とする請求項1または2に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−181582(P2011−181582A)

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願番号】特願2010−42185(P2010−42185)

【出願日】平成22年2月26日(2010.2.26)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願日】平成22年2月26日(2010.2.26)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

[ Back to top ]