半導体装置の製造方法

【課題】半導体素子の破損を抑制すること。

【解決手段】上面に凹部18を備える基板10の前記凹部18内に第1半導体素子30を実装する工程と、前記第1半導体素子30の上面上に弾性体40を配置する工程と、第2半導体素子50の下面が前記弾性体40の上面に接するように前記第2半導体素子50の上面に荷重をかけて前記第2半導体素子50を前記基板10に接合する工程と、を含む半導体装置の製造方法。

【解決手段】上面に凹部18を備える基板10の前記凹部18内に第1半導体素子30を実装する工程と、前記第1半導体素子30の上面上に弾性体40を配置する工程と、第2半導体素子50の下面が前記弾性体40の上面に接するように前記第2半導体素子50の上面に荷重をかけて前記第2半導体素子50を前記基板10に接合する工程と、を含む半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、例えば、半導体素子を実装する半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体素子を3次元に実装する技術が開発されている。例えば、基板上面の凹部に第1の電子部品を実装し、凹部上に第2の電子部品を実装する技術が知られている(例えば、特許文献1)。例えば、基板上面の凹部内にICチップを実装し、凹部上にICモジュールを実装する技術が知られている(例えば、特許文献2)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】実開平7−42165号公報

【特許文献2】特開2004−265955号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体素子を3次元に実装する場合、低コストで半導体素子を実装することが求められている。例えば、低コスト化のため、凹部上の半導体素子に荷重をかけて半導体素子を実装する場合、半導体素子が破損してしまう場合がある。本半導体装置の製造方法は、半導体素子の破損を抑制することを目的とする。

【課題を解決するための手段】

【0005】

例えば、上面に凹部を備える基板の前記凹部内に第1半導体素子を実装する工程と、前記第1半導体素子の上面上に弾性体を配置する工程と、第2半導体素子の下面が前記弾性体の上面に接するように前記第2半導体素子の上面に荷重をかけて前記第2半導体素子を前記基板に接合する工程と、を含むことを特徴とする半導体装置の製造方法を用いることができる。

【発明の効果】

【0006】

本半導体装置の製造方法によれば、半導体素子の破損を抑制することができる。

【図面の簡単な説明】

【0007】

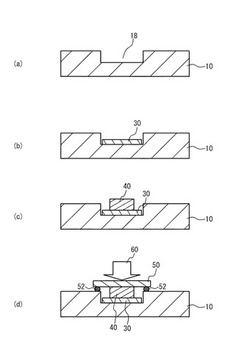

【図1】図1(a)から図1(d)は、実施例1に係る半導体装置の製造方法を示す図である。

【図2】図2(a)から図2(d)は、実施例2に係る半導体装置の製造方法を示す断面図(その1)である。

【図3】図3(a)から図3(c)は、実施例2に係る半導体装置の製造方法を示す断面図(その2)である。

【図4】図4(a)から図4(d)は、実施例3に係る半導体装置の製造方法を示す断面図である。

【発明を実施するための形態】

【0008】

以下、図面を参照に実施例について説明する。

【実施例1】

【0009】

図1(a)から図1(d)は、実施例1に係る半導体装置の製造方法を示す図である。図1(a)のように、絶縁性の基板10の上面に凹部18を形成する。基板10は、例えばセラミック基板または樹脂基板である。図1(b)のように、凹部18内に第1半導体素子30を実装する。例えば、第1半導体素子30を凹部18の底面にフェースアップ実装する。図1(c)のように、第1半導体素子30の上面上に弾性体40を配置する。図1(d)のように、第2半導体素子50の下面が弾性体40の上面に接するように第2半導体素子50の上面に荷重60をかけて第2半導体素子50を基板10に接合する。例えば、第2半導体素子50をバンプ52を用い基板10にフリップチップ実装する。第1半導体素子30および第2半導体素子50は、例えばLSI(Large Scale Integrated Circuit)等のシリコンチップとすることができる。

【0010】

実施例1によれば、第2半導体素子50の上面に荷重60をかけ第2半導体素子50と基板10とを接合させるため、低コストに第2半導体素子50を凹部18上に実装することができる。さらに、第1半導体素子30と第2半導体素子50との間に弾性体が配置されているため、図1(d)における荷重60に起因し、第2半導体素子50が破損することを抑制することができる。特に、半導体装置を小型化する場合、第2半導体素子50の膜厚を薄くすることなり、第2半導体素子50が破損し易くなる。実施例1においては、このような場合においても第2半導体素子50の破損を抑制し、半導体装置の小型化が可能となる。

【0011】

基板10としては、セラミック基板または樹脂基板を用いることができる。第2半導体素子50の上面に荷重をかけ第2半導体素子50を基板10に接合させる場合、基板10の反発力があることが好ましい。よって、基板10は樹脂層を含むことが好ましい。より好ましくは、基板10のうち少なくとも凹部18の底面より上部は、樹脂層であることが好ましい。

【0012】

また、図1(d)のように、第2半導体素子50の上面に荷重をかけ、第2半導体素子50を基板10にフリップチップ接合することにより、低コストの接合が可能となる。

【実施例2】

【0013】

実施例2は、弾性体として樹脂シートを用いる例である。図2(a)から図3(c)は、実施例2に係る半導体装置の製造方法を示す断面図である。図2(a)のように、基板10は、多層配線層12、コア層14および多層配線層16が積層し設けられている。ここで、多層配線層12の表面および内部と、多層配線層12の内部に形成されている配線層は省略している。また、多層配線層12は、配線が表面に1層のみ形成されているものも含むものである。多層配線層12、コア層14および多層配線層16の膜厚はそれぞれ、例えば0.4mm、0.3mmおよび0.6mmとすることができる。基板10には凹部18が設けられている。凹部18は上側の幅が下側の幅より大きい段差を含んでいる。凹部18の下側の大きさは例えば6mm×6mmであり、上側の大きさは8mm×8mmである。凹部18は、ルータ加工法またはレーザ加工法を用い形成することができる。例えばレーザ法を用いることができる。その後、削り残りを洗浄する。表面に露出している基板10の配線および凹部18の底面26のコア層14上にNiをめっきし、次いでAuめっきする。基板10の上面上の凹部18の外側にパッドとして金属層20が設けられている。凹部18内の段差の段差面24にパッドとして金属層22が設けられている。多層配線層12および16は、例えばセラミック層または樹脂層であり、好ましくは樹脂層である。コア層14は、例えば第1半導体素子30の放熱用金属層であり、例えばCuを含む金属である。コア層14を放熱用に用いるため、凹部18の底面26は例えばコア層14に達していることが好ましい。金属層20および22は、例えばAuを含む金属である。

【0014】

図2(b)のように、凹部18の底面26にダイボンド剤28として、例えば接着剤を塗布する。図2(c)のように、凹部18の底面26にダイボンド剤28を介して第1半導体素子30をフェースアップ実装する。第1半導体素子30の大きさは例えば5mm×5mmであり、厚さは例えば200μmである。第1半導体素子30のパッドおよび金属層20および22上を例えば酸素アッシャを用い洗浄する。第1半導体素子30のパッドと基板10の金属層22とをボンディングワイヤ32を用い接続する。第1半導体素子30のパッドは、第1半導体素子30に電源や入出力信号を入出力するための端子である。ワイヤ32としては、例えばAuまたはCuを少なくとも含むワイヤを用いることができる。ワイヤ32の直径は例えば25μmとすることができる。凹部18の深さは例えば600μm、底面26から段差面24までの高さは、例えば200μmである。凹部18の深さは、ボンディングワイヤ32の最上部が基板10の上面より高くならないような深さとすることが好ましい。これにより、ワイヤ32の上部が第2半導体素子50等に接触することを抑制することができる。

【0015】

図2(d)のように、第1半導体素子30上に、シート状の弾性体40を配置し、必要に応じて、硬化させる。硬化条件は、例えば温度が150℃〜250℃、時間が10分〜60分であり、例えば200℃、30分である。弾性体40の大きさは例えば2mm×2mmである。弾性体40は第1半導体素子30の中央部に配置することにより、第1半導体素子30の周辺に配置されたワイヤ32を破損させることを抑制できる。弾性体40の膜厚は、凹部18の底面26から図3(b)で説明する第2半導体素子50の下面までの高さとほぼ等しいことが好ましい。例えば、400μmとすることができる。弾性体40としては、ポリイミド樹脂、エポキシ樹脂、アクリル樹脂の少なくとも一つを含む樹脂シートまたはこれらの樹脂を硬化させた樹脂シートを用いることができる。また、ポリイミド樹脂、エポキシ樹脂、アクリル樹脂の少なくとも一つの樹脂にゴム系フィラーを含ませてもよい。さらに、無機系フィラーを含ませてもよい。例えば、樹脂シートの弾性率が5GPa以上の場合、第2半導体素子50を基板10に接合させる際に、第2半導体素子50が破損することがある。そこで、弾性体40の弾性率は5GPa未満が好ましい。

【0016】

図3(a)のように、金属層20を覆うようにNCP42(Non Conductive Paste)を塗布する。NCPは、例えばアンダーフィル剤であり、エポキシ等の絶縁性の樹脂に無機フィラーを含有させたものである。また、NCPとして横方向に絶縁性が確保された導電性樹脂を用いることもできる。

【0017】

図3(b)のように、第2半導体素子50の下面にはバンプ52が形成されている。第2半導体素子50の大きさは例えば11mm×11mmであり、厚さは例えば200μmである。バンプ52は、第2半導体素子50に電源や入出力信号を入出力するための端子である。バンプ52は、例えばAuバンプ等の金属バンプであり、スタッドバンプ法またはメッキ法により形成されたバンプである。バンプ52としてはAu以外にも例えばCuを用いることができる。バンプ52の高さは、例えば50μmである。バンプ52と金属層20とを位置合わせする。第2半導体素子50の上面に荷重60を加える。荷重60の大きさは、例えば1つのバンプ52あたり10〜50gfとする。例えば1つのバンプあたり35gfとする。また、例えば第2半導体素子50を、120〜250℃の温度で3〜30秒間加熱する。例えば210℃の温度で20秒間加熱する。これにより、第2半導体素子50と基板10とを、バンプ52と金属層20とを介し電気的に接合させることができる。また、NCP42を熱硬化型樹脂とすることにより、第2半導体素子50の加熱の際にNCP42を硬化させ、第2半導体素子50と基板10との機械的接合を強化することもできる。第2半導体素子50の上面から荷重60をかけ第2半導体素子50を基板10に接合する方法としては、例えば超音波接合、圧接接合または熱圧着接合を用いることができる。以上により、図3(c)のように、実施例2に係る半導体装置が完成する。

【0018】

実施例2のように、第1半導体素子30上に弾性体40として弾性体シートを配置することができる。これにより、簡単に、第2半導体素子50の破損を抑制することができる。

【0019】

また、第2半導体素子50を基板10に接合する際は、第2半導体素子50に形成された金属バンプ52と基板10の凹部18の外側の上面に形成された金属層20とを接続する。このように、荷重60により金属バンプ52と金属層20とを接合させることにより、第2半導体素子50と基板10との電気的および機械的な接合がより簡単に可能となる。なお、第2半導体素子50に金属層(例えばバッド)を設け、基板10の凹部18の外側に金属バンプを設けてもよい。つまり、第2半導体素子50の下面と基板10の凹部18の外側の上面との一方に形成された金属バンプ52と、第2半導体素子50の下面と基板10の凹部18の外側の上面との他方に形成された金属層20と、を接合すればよい。

【0020】

さらに、第1半導体素子30を凹部18に実装する際は、凹部18の底面26上に第1半導体素子30をフェースアップで実装することができる。これにより、第1半導体素子30の下面は凹部18の底面26に全面に渡り接合している。よって、弾性体40を介し荷重60が第1半導体素子30に加わっても第1半導体素子30が破損することを抑制することができる。

【0021】

さらに、凹部18は、上側の幅が下側の幅より大きい段差を含み、第1半導体素子30と段差に形成された段差面24とをワイヤ32を用い接続することができる。これにより、短いワイヤ32を用い第1半導体素子30と基板10とを電気的に接続させることができる。

【0022】

さらに、基板10は、コア層14と、コア層14上に形成された多層配線層16と、を含み、凹部18はコア層14に達しており、第1半導体素子30をコア層14上に実装することが好ましい。これにより、コア層14を介し、第1半導体素子30の熱を放出させることができる。なお、コア層14下の多層配線層12は設けられていなくともよい。

【実施例3】

【0023】

実施例3は弾性体としてポッティング剤を用いる例である。図4(a)から図4(d)は、実施例3に係る半導体装置の製造方法を示す断面図である。図2(a)から図2(c)と同様の工程を行う。図2(a)において、ルータ法を用い凹部18を形成する。凹部18の下側の大きさは例えば7mm×7mmであり上側の大きさは例えば9mm×9mmとする。図2(b)において、大きさが6mm×6mmあり厚さが300μmである第1半導体素子30を底面26にフェースアップ実装する。その他の工程は、実施例1の図2(a)から図2(c)と同様であり説明を省略する。図4(a)のように第1半導体素子30上に液状の熱硬化型樹脂である液状部材41を配置する。液状部材41としては、例えば、ポリイミド樹脂、エポキシ樹脂およびアクリル樹脂の少なくとも一つの樹脂等のポッティング剤を用いることができる。例えばエポキシ樹脂を含む液状部材41を用いる。液状部材41はワイヤ32を覆うように配置する。液状部材41を例えば150℃の温度で30分熱処理し硬化させる。これにより、液状部材41から弾性体40が形成される。図4(b)のように、実施例2の図3(a)と同様に、金属層20を覆うようにNCP42を設ける。

【0024】

図4(c)のように、実施例2の図3(b)と同様に、第2半導体素子50の上面に荷重60を加える。第2半導体素子50の大きさは例えば11.5mm×11.5mmであり、厚さは例えば200μmである。荷重60の大きさは、例えば1つのバンプあたり40gfとする。第2半導体素子50をNCP42を介して、例えば200℃の温度で10秒間加熱する。これにより、第2半導体素子50と基板10とをバンプ52を介し接続することができる。以上により、図4(d)のように、実施例3に係る半導体装置が完成する。

【0025】

図4(a)から図4(d)において、液状部材41を塗布せず、その他の工程は実施例3で例示した方法と同じとした比較例に係る半導体装置を作製した。比較例においては、図4(c)の荷重60をかけた際に、第2半導体素子50に割れが発生した。一方、実施例3において例示した方法で作製した半導体装置においては、第2半導体素子50の割れは発生しなかった。このように、実施例3によれば、第2半導体素子50の破損を抑制することができる。

【0026】

さらに、図4(a)のように、第1半導体素子30上に熱硬化型樹脂を配置する。熱硬化樹脂に熱を加えることにより熱硬化樹脂を硬化させ弾性体40を形成することができる。これにより、弾性体40を形成することができる。また、図4(a)のように、液状部材41がワイヤ32を覆うことにより、ワイヤ32を保護することができる。

【0027】

実施例1から実施例3において、第2半導体素子50の上面に熱放出用の導電層を接触させてもよい。さらに、第1半導体素子30上に1または複数の半導体素子を積層させてもよい。例えば、第1半導体素子30上に1または複数の別の半導体素子をフェースアップで積層し、最上の半導体素子の上に弾性体40を配置してもよい。第2半導体素子50上に1または複数の半導体素子を積層させてもよい。例えば第2半導体素子50の上面上に1または複数の別の半導体素子をフェースアップで積層してもよい。

【0028】

以上、本発明の実施例について詳述したが、本発明は係る特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【0029】

実施例1〜3を含む実施形態に関し、さらに以下の付記を開示する。

(付記1):上面に凹部を備える基板の前記凹部内に第1半導体素子を実装する工程と、前記第1半導体素子の上面上に弾性体を配置する工程と、第2半導体素子の下面が前記弾性体の上面に接するように前記第2半導体素子の上面に荷重をかけて前記第2半導体素子を前記基板に接合する工程と、を含むことを特徴とする半導体装置の製造方法。

(付記2):前記基板は樹脂層を含むことを特徴とする付記1記載の半導体装置の製造方法。

(付記3):前記第2半導体素子を前記基板に接合する工程は、前記第2半導体素子を前記基板にフリップチップ接合する工程を含むことを特徴とする付記1または2記載の半導体装置の製造方法。

(付記4):前記第2半導体素子を前記基板に接合する工程は、前記第2半導体素子の下面と前記基板の前記凹部の外側の上面との一方に形成された金属バンプと、前記第2半導体素子の下面と前記基板の前記凹部の外側の上面との他方に形成された金属層と、を接合する工程を含むことを特徴とする付記1から3のいずれか一項記載の半導体装置の製造方法。

(付記5):前記第1半導体素子上に弾性体を配置する工程は、前記第1半導体上に弾性体シートを配置する工程を含むことを特徴とする付記1から4のいずれか一項記載の半導体装置の製造方法。

(付記6):前記第1半導体素子上に弾性体を配置する工程は、前記第1半導体上に熱硬化型樹脂を配置する工程と、前記熱硬化樹脂に熱を加えることにより前記熱硬化樹脂を硬化させ前記弾性体を形成する工程と、を含むことを特徴とする付記1から4のいずれか一項記載の半導体装置の製造方法。

(付記7):前記第1半導体素子を実装する工程は、前記凹部の底面上に前記第1半導体素子をフェースアップで実装する工程であることを特徴とする付記1から6のいずれか一項記載の半導体装置の製造方法。

(付記8):前記凹部は、上側の幅が下側の幅より大きい段差を含み、前記第1半導体素子と前記段差に形成された段差面とをワイヤを用い接続する工程を含むことを特徴とする付記7記載の半導体装置の製造方法。

(付記9):前記基板は、コア層と、前記コア層上に形成された多層配線層と、を含み、前記凹部は前記コア層に達しており、前記第1半導体素子を実装する工程は、前記第1半導体素子を前記コア層上に実装する工程を含むことを特徴とする付記1から8のいずれか一項記載の半導体装置の製造方法。

【符号の説明】

【0030】

10 基板

12、16 多層配線層

14 コア層

18 凹部

20、22 金属層

24 段差面

30 第1半導体素子

32 ワイヤ

40 弾性体

50 第2半導体素子

52 バンプ

60 荷重

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、例えば、半導体素子を実装する半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体素子を3次元に実装する技術が開発されている。例えば、基板上面の凹部に第1の電子部品を実装し、凹部上に第2の電子部品を実装する技術が知られている(例えば、特許文献1)。例えば、基板上面の凹部内にICチップを実装し、凹部上にICモジュールを実装する技術が知られている(例えば、特許文献2)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】実開平7−42165号公報

【特許文献2】特開2004−265955号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体素子を3次元に実装する場合、低コストで半導体素子を実装することが求められている。例えば、低コスト化のため、凹部上の半導体素子に荷重をかけて半導体素子を実装する場合、半導体素子が破損してしまう場合がある。本半導体装置の製造方法は、半導体素子の破損を抑制することを目的とする。

【課題を解決するための手段】

【0005】

例えば、上面に凹部を備える基板の前記凹部内に第1半導体素子を実装する工程と、前記第1半導体素子の上面上に弾性体を配置する工程と、第2半導体素子の下面が前記弾性体の上面に接するように前記第2半導体素子の上面に荷重をかけて前記第2半導体素子を前記基板に接合する工程と、を含むことを特徴とする半導体装置の製造方法を用いることができる。

【発明の効果】

【0006】

本半導体装置の製造方法によれば、半導体素子の破損を抑制することができる。

【図面の簡単な説明】

【0007】

【図1】図1(a)から図1(d)は、実施例1に係る半導体装置の製造方法を示す図である。

【図2】図2(a)から図2(d)は、実施例2に係る半導体装置の製造方法を示す断面図(その1)である。

【図3】図3(a)から図3(c)は、実施例2に係る半導体装置の製造方法を示す断面図(その2)である。

【図4】図4(a)から図4(d)は、実施例3に係る半導体装置の製造方法を示す断面図である。

【発明を実施するための形態】

【0008】

以下、図面を参照に実施例について説明する。

【実施例1】

【0009】

図1(a)から図1(d)は、実施例1に係る半導体装置の製造方法を示す図である。図1(a)のように、絶縁性の基板10の上面に凹部18を形成する。基板10は、例えばセラミック基板または樹脂基板である。図1(b)のように、凹部18内に第1半導体素子30を実装する。例えば、第1半導体素子30を凹部18の底面にフェースアップ実装する。図1(c)のように、第1半導体素子30の上面上に弾性体40を配置する。図1(d)のように、第2半導体素子50の下面が弾性体40の上面に接するように第2半導体素子50の上面に荷重60をかけて第2半導体素子50を基板10に接合する。例えば、第2半導体素子50をバンプ52を用い基板10にフリップチップ実装する。第1半導体素子30および第2半導体素子50は、例えばLSI(Large Scale Integrated Circuit)等のシリコンチップとすることができる。

【0010】

実施例1によれば、第2半導体素子50の上面に荷重60をかけ第2半導体素子50と基板10とを接合させるため、低コストに第2半導体素子50を凹部18上に実装することができる。さらに、第1半導体素子30と第2半導体素子50との間に弾性体が配置されているため、図1(d)における荷重60に起因し、第2半導体素子50が破損することを抑制することができる。特に、半導体装置を小型化する場合、第2半導体素子50の膜厚を薄くすることなり、第2半導体素子50が破損し易くなる。実施例1においては、このような場合においても第2半導体素子50の破損を抑制し、半導体装置の小型化が可能となる。

【0011】

基板10としては、セラミック基板または樹脂基板を用いることができる。第2半導体素子50の上面に荷重をかけ第2半導体素子50を基板10に接合させる場合、基板10の反発力があることが好ましい。よって、基板10は樹脂層を含むことが好ましい。より好ましくは、基板10のうち少なくとも凹部18の底面より上部は、樹脂層であることが好ましい。

【0012】

また、図1(d)のように、第2半導体素子50の上面に荷重をかけ、第2半導体素子50を基板10にフリップチップ接合することにより、低コストの接合が可能となる。

【実施例2】

【0013】

実施例2は、弾性体として樹脂シートを用いる例である。図2(a)から図3(c)は、実施例2に係る半導体装置の製造方法を示す断面図である。図2(a)のように、基板10は、多層配線層12、コア層14および多層配線層16が積層し設けられている。ここで、多層配線層12の表面および内部と、多層配線層12の内部に形成されている配線層は省略している。また、多層配線層12は、配線が表面に1層のみ形成されているものも含むものである。多層配線層12、コア層14および多層配線層16の膜厚はそれぞれ、例えば0.4mm、0.3mmおよび0.6mmとすることができる。基板10には凹部18が設けられている。凹部18は上側の幅が下側の幅より大きい段差を含んでいる。凹部18の下側の大きさは例えば6mm×6mmであり、上側の大きさは8mm×8mmである。凹部18は、ルータ加工法またはレーザ加工法を用い形成することができる。例えばレーザ法を用いることができる。その後、削り残りを洗浄する。表面に露出している基板10の配線および凹部18の底面26のコア層14上にNiをめっきし、次いでAuめっきする。基板10の上面上の凹部18の外側にパッドとして金属層20が設けられている。凹部18内の段差の段差面24にパッドとして金属層22が設けられている。多層配線層12および16は、例えばセラミック層または樹脂層であり、好ましくは樹脂層である。コア層14は、例えば第1半導体素子30の放熱用金属層であり、例えばCuを含む金属である。コア層14を放熱用に用いるため、凹部18の底面26は例えばコア層14に達していることが好ましい。金属層20および22は、例えばAuを含む金属である。

【0014】

図2(b)のように、凹部18の底面26にダイボンド剤28として、例えば接着剤を塗布する。図2(c)のように、凹部18の底面26にダイボンド剤28を介して第1半導体素子30をフェースアップ実装する。第1半導体素子30の大きさは例えば5mm×5mmであり、厚さは例えば200μmである。第1半導体素子30のパッドおよび金属層20および22上を例えば酸素アッシャを用い洗浄する。第1半導体素子30のパッドと基板10の金属層22とをボンディングワイヤ32を用い接続する。第1半導体素子30のパッドは、第1半導体素子30に電源や入出力信号を入出力するための端子である。ワイヤ32としては、例えばAuまたはCuを少なくとも含むワイヤを用いることができる。ワイヤ32の直径は例えば25μmとすることができる。凹部18の深さは例えば600μm、底面26から段差面24までの高さは、例えば200μmである。凹部18の深さは、ボンディングワイヤ32の最上部が基板10の上面より高くならないような深さとすることが好ましい。これにより、ワイヤ32の上部が第2半導体素子50等に接触することを抑制することができる。

【0015】

図2(d)のように、第1半導体素子30上に、シート状の弾性体40を配置し、必要に応じて、硬化させる。硬化条件は、例えば温度が150℃〜250℃、時間が10分〜60分であり、例えば200℃、30分である。弾性体40の大きさは例えば2mm×2mmである。弾性体40は第1半導体素子30の中央部に配置することにより、第1半導体素子30の周辺に配置されたワイヤ32を破損させることを抑制できる。弾性体40の膜厚は、凹部18の底面26から図3(b)で説明する第2半導体素子50の下面までの高さとほぼ等しいことが好ましい。例えば、400μmとすることができる。弾性体40としては、ポリイミド樹脂、エポキシ樹脂、アクリル樹脂の少なくとも一つを含む樹脂シートまたはこれらの樹脂を硬化させた樹脂シートを用いることができる。また、ポリイミド樹脂、エポキシ樹脂、アクリル樹脂の少なくとも一つの樹脂にゴム系フィラーを含ませてもよい。さらに、無機系フィラーを含ませてもよい。例えば、樹脂シートの弾性率が5GPa以上の場合、第2半導体素子50を基板10に接合させる際に、第2半導体素子50が破損することがある。そこで、弾性体40の弾性率は5GPa未満が好ましい。

【0016】

図3(a)のように、金属層20を覆うようにNCP42(Non Conductive Paste)を塗布する。NCPは、例えばアンダーフィル剤であり、エポキシ等の絶縁性の樹脂に無機フィラーを含有させたものである。また、NCPとして横方向に絶縁性が確保された導電性樹脂を用いることもできる。

【0017】

図3(b)のように、第2半導体素子50の下面にはバンプ52が形成されている。第2半導体素子50の大きさは例えば11mm×11mmであり、厚さは例えば200μmである。バンプ52は、第2半導体素子50に電源や入出力信号を入出力するための端子である。バンプ52は、例えばAuバンプ等の金属バンプであり、スタッドバンプ法またはメッキ法により形成されたバンプである。バンプ52としてはAu以外にも例えばCuを用いることができる。バンプ52の高さは、例えば50μmである。バンプ52と金属層20とを位置合わせする。第2半導体素子50の上面に荷重60を加える。荷重60の大きさは、例えば1つのバンプ52あたり10〜50gfとする。例えば1つのバンプあたり35gfとする。また、例えば第2半導体素子50を、120〜250℃の温度で3〜30秒間加熱する。例えば210℃の温度で20秒間加熱する。これにより、第2半導体素子50と基板10とを、バンプ52と金属層20とを介し電気的に接合させることができる。また、NCP42を熱硬化型樹脂とすることにより、第2半導体素子50の加熱の際にNCP42を硬化させ、第2半導体素子50と基板10との機械的接合を強化することもできる。第2半導体素子50の上面から荷重60をかけ第2半導体素子50を基板10に接合する方法としては、例えば超音波接合、圧接接合または熱圧着接合を用いることができる。以上により、図3(c)のように、実施例2に係る半導体装置が完成する。

【0018】

実施例2のように、第1半導体素子30上に弾性体40として弾性体シートを配置することができる。これにより、簡単に、第2半導体素子50の破損を抑制することができる。

【0019】

また、第2半導体素子50を基板10に接合する際は、第2半導体素子50に形成された金属バンプ52と基板10の凹部18の外側の上面に形成された金属層20とを接続する。このように、荷重60により金属バンプ52と金属層20とを接合させることにより、第2半導体素子50と基板10との電気的および機械的な接合がより簡単に可能となる。なお、第2半導体素子50に金属層(例えばバッド)を設け、基板10の凹部18の外側に金属バンプを設けてもよい。つまり、第2半導体素子50の下面と基板10の凹部18の外側の上面との一方に形成された金属バンプ52と、第2半導体素子50の下面と基板10の凹部18の外側の上面との他方に形成された金属層20と、を接合すればよい。

【0020】

さらに、第1半導体素子30を凹部18に実装する際は、凹部18の底面26上に第1半導体素子30をフェースアップで実装することができる。これにより、第1半導体素子30の下面は凹部18の底面26に全面に渡り接合している。よって、弾性体40を介し荷重60が第1半導体素子30に加わっても第1半導体素子30が破損することを抑制することができる。

【0021】

さらに、凹部18は、上側の幅が下側の幅より大きい段差を含み、第1半導体素子30と段差に形成された段差面24とをワイヤ32を用い接続することができる。これにより、短いワイヤ32を用い第1半導体素子30と基板10とを電気的に接続させることができる。

【0022】

さらに、基板10は、コア層14と、コア層14上に形成された多層配線層16と、を含み、凹部18はコア層14に達しており、第1半導体素子30をコア層14上に実装することが好ましい。これにより、コア層14を介し、第1半導体素子30の熱を放出させることができる。なお、コア層14下の多層配線層12は設けられていなくともよい。

【実施例3】

【0023】

実施例3は弾性体としてポッティング剤を用いる例である。図4(a)から図4(d)は、実施例3に係る半導体装置の製造方法を示す断面図である。図2(a)から図2(c)と同様の工程を行う。図2(a)において、ルータ法を用い凹部18を形成する。凹部18の下側の大きさは例えば7mm×7mmであり上側の大きさは例えば9mm×9mmとする。図2(b)において、大きさが6mm×6mmあり厚さが300μmである第1半導体素子30を底面26にフェースアップ実装する。その他の工程は、実施例1の図2(a)から図2(c)と同様であり説明を省略する。図4(a)のように第1半導体素子30上に液状の熱硬化型樹脂である液状部材41を配置する。液状部材41としては、例えば、ポリイミド樹脂、エポキシ樹脂およびアクリル樹脂の少なくとも一つの樹脂等のポッティング剤を用いることができる。例えばエポキシ樹脂を含む液状部材41を用いる。液状部材41はワイヤ32を覆うように配置する。液状部材41を例えば150℃の温度で30分熱処理し硬化させる。これにより、液状部材41から弾性体40が形成される。図4(b)のように、実施例2の図3(a)と同様に、金属層20を覆うようにNCP42を設ける。

【0024】

図4(c)のように、実施例2の図3(b)と同様に、第2半導体素子50の上面に荷重60を加える。第2半導体素子50の大きさは例えば11.5mm×11.5mmであり、厚さは例えば200μmである。荷重60の大きさは、例えば1つのバンプあたり40gfとする。第2半導体素子50をNCP42を介して、例えば200℃の温度で10秒間加熱する。これにより、第2半導体素子50と基板10とをバンプ52を介し接続することができる。以上により、図4(d)のように、実施例3に係る半導体装置が完成する。

【0025】

図4(a)から図4(d)において、液状部材41を塗布せず、その他の工程は実施例3で例示した方法と同じとした比較例に係る半導体装置を作製した。比較例においては、図4(c)の荷重60をかけた際に、第2半導体素子50に割れが発生した。一方、実施例3において例示した方法で作製した半導体装置においては、第2半導体素子50の割れは発生しなかった。このように、実施例3によれば、第2半導体素子50の破損を抑制することができる。

【0026】

さらに、図4(a)のように、第1半導体素子30上に熱硬化型樹脂を配置する。熱硬化樹脂に熱を加えることにより熱硬化樹脂を硬化させ弾性体40を形成することができる。これにより、弾性体40を形成することができる。また、図4(a)のように、液状部材41がワイヤ32を覆うことにより、ワイヤ32を保護することができる。

【0027】

実施例1から実施例3において、第2半導体素子50の上面に熱放出用の導電層を接触させてもよい。さらに、第1半導体素子30上に1または複数の半導体素子を積層させてもよい。例えば、第1半導体素子30上に1または複数の別の半導体素子をフェースアップで積層し、最上の半導体素子の上に弾性体40を配置してもよい。第2半導体素子50上に1または複数の半導体素子を積層させてもよい。例えば第2半導体素子50の上面上に1または複数の別の半導体素子をフェースアップで積層してもよい。

【0028】

以上、本発明の実施例について詳述したが、本発明は係る特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【0029】

実施例1〜3を含む実施形態に関し、さらに以下の付記を開示する。

(付記1):上面に凹部を備える基板の前記凹部内に第1半導体素子を実装する工程と、前記第1半導体素子の上面上に弾性体を配置する工程と、第2半導体素子の下面が前記弾性体の上面に接するように前記第2半導体素子の上面に荷重をかけて前記第2半導体素子を前記基板に接合する工程と、を含むことを特徴とする半導体装置の製造方法。

(付記2):前記基板は樹脂層を含むことを特徴とする付記1記載の半導体装置の製造方法。

(付記3):前記第2半導体素子を前記基板に接合する工程は、前記第2半導体素子を前記基板にフリップチップ接合する工程を含むことを特徴とする付記1または2記載の半導体装置の製造方法。

(付記4):前記第2半導体素子を前記基板に接合する工程は、前記第2半導体素子の下面と前記基板の前記凹部の外側の上面との一方に形成された金属バンプと、前記第2半導体素子の下面と前記基板の前記凹部の外側の上面との他方に形成された金属層と、を接合する工程を含むことを特徴とする付記1から3のいずれか一項記載の半導体装置の製造方法。

(付記5):前記第1半導体素子上に弾性体を配置する工程は、前記第1半導体上に弾性体シートを配置する工程を含むことを特徴とする付記1から4のいずれか一項記載の半導体装置の製造方法。

(付記6):前記第1半導体素子上に弾性体を配置する工程は、前記第1半導体上に熱硬化型樹脂を配置する工程と、前記熱硬化樹脂に熱を加えることにより前記熱硬化樹脂を硬化させ前記弾性体を形成する工程と、を含むことを特徴とする付記1から4のいずれか一項記載の半導体装置の製造方法。

(付記7):前記第1半導体素子を実装する工程は、前記凹部の底面上に前記第1半導体素子をフェースアップで実装する工程であることを特徴とする付記1から6のいずれか一項記載の半導体装置の製造方法。

(付記8):前記凹部は、上側の幅が下側の幅より大きい段差を含み、前記第1半導体素子と前記段差に形成された段差面とをワイヤを用い接続する工程を含むことを特徴とする付記7記載の半導体装置の製造方法。

(付記9):前記基板は、コア層と、前記コア層上に形成された多層配線層と、を含み、前記凹部は前記コア層に達しており、前記第1半導体素子を実装する工程は、前記第1半導体素子を前記コア層上に実装する工程を含むことを特徴とする付記1から8のいずれか一項記載の半導体装置の製造方法。

【符号の説明】

【0030】

10 基板

12、16 多層配線層

14 コア層

18 凹部

20、22 金属層

24 段差面

30 第1半導体素子

32 ワイヤ

40 弾性体

50 第2半導体素子

52 バンプ

60 荷重

【特許請求の範囲】

【請求項1】

上面に凹部を備える基板の前記凹部内に第1半導体素子を実装する工程と、

前記第1半導体素子の上面上に弾性体を配置する工程と、

第2半導体素子の下面が前記弾性体の上面に接するように前記第2半導体素子の上面に荷重をかけて前記第2半導体素子を前記基板に接合する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記基板は樹脂層を含むことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記第2半導体素子を前記基板に接合する工程は、前記第2半導体素子を前記基板にフリップチップ接合する工程を含むことを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項4】

前記第1半導体素子を実装する工程は、前記凹部の底面上に前記第1半導体素子をフェースアップで実装する工程であることを特徴とする請求項1から3のいずれか一項記載の半導体装置の製造方法。

【請求項5】

前記凹部は、上側の幅が下側の幅より大きい段差を含み、前記第1半導体素子と前記段差に形成された段差面とをワイヤを用い接続する工程を含むことを特徴とする請求項4記載の半導体装置の製造方法。

【請求項1】

上面に凹部を備える基板の前記凹部内に第1半導体素子を実装する工程と、

前記第1半導体素子の上面上に弾性体を配置する工程と、

第2半導体素子の下面が前記弾性体の上面に接するように前記第2半導体素子の上面に荷重をかけて前記第2半導体素子を前記基板に接合する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記基板は樹脂層を含むことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記第2半導体素子を前記基板に接合する工程は、前記第2半導体素子を前記基板にフリップチップ接合する工程を含むことを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項4】

前記第1半導体素子を実装する工程は、前記凹部の底面上に前記第1半導体素子をフェースアップで実装する工程であることを特徴とする請求項1から3のいずれか一項記載の半導体装置の製造方法。

【請求項5】

前記凹部は、上側の幅が下側の幅より大きい段差を含み、前記第1半導体素子と前記段差に形成された段差面とをワイヤを用い接続する工程を含むことを特徴とする請求項4記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2011−228521(P2011−228521A)

【公開日】平成23年11月10日(2011.11.10)

【国際特許分類】

【出願番号】特願2010−97754(P2010−97754)

【出願日】平成22年4月21日(2010.4.21)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成23年11月10日(2011.11.10)

【国際特許分類】

【出願日】平成22年4月21日(2010.4.21)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]