半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法、特に高誘電率膜及びメタルゲート電極を備える半導体装置の製造方法に係わる。

【背景技術】

【0002】

MOSトランジスタの動作速度は、容量の増加により低下する。このため、駆動電流に寄与しない寄生容量、特に、フリンジ容量を低減する必要がある。寄生容量を低下させる方法としては、オフセットスペーサの下部に空洞部を設け、ゲート電極とサイドウォールとの間に空間を形成した構造の半導体装置が提案されている(例えば、特許文献1参照)。この方法では、ゲート電極の側壁にオフセットスペーサを形成した後、オフセットスペーサの下部を局所的にウェットエッチングにより除去し、オフセットスペーサ下部に空間を形成する。そして、この空間を埋めこまない方法でサイドウォールを形成する。この結果、ゲート電極とサイドウォールとの間で、オフセットスペーサの下部に局所的に空洞部を形成することができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2004−95888号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、ウェットエッチングにより、オフセットスペーサの下部のみに空洞を選択的に形成する場合には、所定の形状に空洞部を制御よく実現することが難しい。

また、高誘電率(High−k)材料を用いたゲート絶縁膜(HK)、及び、金属(Metal)材料を用いたゲート電極(MG)からなる半導体装置が提案されている。このような構成の半導体装置を製造する際に、一般的に適用されるゲートラスト(Gate Last)製造プロセスでは、上述の製造方法を適用することが難しい。例えば、上述の特許文献1に記載された半導体装置では、オフセットスペーサがシリコン酸化膜により構成されている。しかし、ゲートラストプロセスでは、ウェットエッチングにより、ダミーゲート絶縁膜を除去する工程がある。この工程において、シリコン酸化膜からなるオフセットスペーサが同時に除去されるため、オフセットスペーサ下部の空洞部も消失してしまう。

【0005】

上述のように、ゲート電極とサイドウォールとの間に空洞部を設けて寄生容量を抑制する構造の半導体装置において、従来の製造方法では空洞部を制御性よく形成することが難しい。

【0006】

上述した問題の解決のため、本発明においては、制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0007】

本発明の半導体装置の製造方法は、半導体基体上にダミーゲート絶縁膜及びダミーゲート電極を形成する工程を有する。そして、ダミーゲート電極上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極の側壁下部にオフセットスペーサを形成する工程を有する。オフセットスペーサ上を覆って、ダミーゲート電極の側壁にサイドウォールを形成する工程と、サイドウォールを埋め込み、かつダミーゲート電極の上面を露出させる層間絶縁層を形成する工程とを有する。さらに、ダミーゲート電極を除去する工程と、ダミーゲート絶縁膜を除去する工程と、オフセットスペーサを除去する工程と、半導体基体上に高誘電率材料からなるゲート絶縁膜を形成する工程を有する。そして、ゲート絶縁膜上に、異方性の高い堆積方法を用いてメタルゲート電極を形成する工程を有する。

【0008】

また、本発明の半導体装置の製造方法は、半導体基体上に高誘電率材料からなるゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属材料層からなるゲート電極を形成する工程と、金属材料層上にダミーゲート電極を形成する工程とを有する。そして、ダミーゲート電極上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ゲート電極及びダミーゲート電極の側壁に、オフセットスペーサを形成する工程を有する。さらに、オフセットスペーサ上を覆って、ダミーゲート電極の側壁にサイドウォールを形成する工程と、サイドウォールを埋め込み、かつダミーゲート電極の上面を露出させる層間絶縁層を形成する工程とを有する。そして、ダミーゲート電極、及び、オフセットスペーサを除去する工程と、ゲート電極上に、導電体層を形成する工程とを有する。

【0009】

本発明の半導体装置の製造方法によれば、ダミーゲート電極上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極の側壁下部にオフセットスペーサを形成する。そして、サイドウォールの形成後、ダミーゲート電極とオフセットスペーサを除去し、高誘電率材料からなるゲート絶縁膜とメタルゲート電極とを異方性の高い堆積方法を用いて形成する。このため、オフセットスペーサ24が除去された部分に、オフセットスペーサ24と同じ形状の空洞部16が形成される。

オフセットスペーサは、形成する厚さとエッチング量を調整することにより、任意の形状に制御性よく形成することができる。従って、半導体装置の空洞部の形状を、オフセットスペーサの形成工程に依存して、任意の形状に制御性よく形成することができる。

【発明の効果】

【0010】

本発明によれば、空洞部の形成を制御よく行うことが可能な半導体装置の製造方法を提供することができる。

【図面の簡単な説明】

【0011】

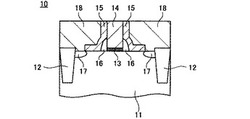

【図1】本発明の半導体装置の製造方法の第1実施形態に係わる半導体装置の構成を示す図である。

【図2】A〜Dは、本発明の第1実施形態の半導体装置の製造工程を示す図である。

【図3】E〜Hは、本発明の第1実施形態の半導体装置の製造工程を示す図である。

【図4】A〜Eは、本発明の第1実施形態の半導体装置の製造工程を示す図である。

【図5】本発明の半導体装置の製造方法の第1実施形態に係わる半導体装置の構成を示す図である。

【図6】本発明の半導体装置の製造方法の第2実施形態に係わる半導体装置の構成を示す図である。

【図7】A〜Dは、本発明の第2実施形態の半導体装置の製造工程を示す図である。

【図8】E〜Hは、本発明の第2実施形態の半導体装置の製造工程を示す図である。

【図9】I〜Kは、本発明の第2実施形態の半導体装置の製造工程を示す図である。

【図10】本発明の半導体装置の製造方法の第3実施形態に係わる半導体装置の構成を示す図である。

【図11】A〜Dは、本発明の第3実施形態の半導体装置の製造工程を示す図である。

【図12】E〜Hは、本発明の第3実施形態の半導体装置の製造工程を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明を実施するための最良の形態の例を説明するが、本発明は以下の例に限定されるものではない。

なお、説明は以下の順序で行う。

1.半導体装置の製造方法の第1実施形態

2.半導体装置の製造方法の第2実施形態

3.半導体装置の製造方法の第3実施形態

【0013】

〈1.半導体装置の製造方法の第1実施形態〉

[半導体装置の構成例]

以下本発明の半導体装置の具体的な実施の形態について説明する。

図1に、第1実施形態の製造方法に係わる半導体装置の概略構成図を示す。図1に示す半導体装置10は、例えば、シリコン基板等からなる半導体基体11に、活性領域を区画する酸化シリコン等からなる素子分離12が形成されている。そして、半導体基体11上に、高誘電率(High−k)材料からなる酸化膜(HK酸化膜)13を介してメタルゲート(MG)電極14が形成されている。そして、MG電極14の側壁に、サイドウォール15が形成されている。MG電極の側壁下部には、MG電極とサイドウォール15との間に設けられた空間からなる空洞部16が形成されている。

【0014】

また、半導体基体11には、図示しないソース・ドレイン、エクステンション領域及びHalo等の不純物領域が形成され、サイドウォール15から露出されている不純物領域(ソース・ドレイン)の表面にシリサイド17が形成されている。さらに、半導体基体11上に、MG電極14及びサイドウォール15を覆って、層間絶縁層18が形成されている。

【0015】

HK酸化膜13は、酸化シリコンよりも誘電率の高い高誘電率材料から形成される。高誘電率材料としては、HfO、HfSiO、LaO、ZrO、ZrSiO、TaO、TiO、BaSrTiO、BaTiO、StTiO、YO、AlO、及び、PbScTaO等を用いることができる。

MG電極14は、純金属材料、合金又は金属化合物からなり、例えば、Ti、Al、Cu、W、HfSi及びTiN等からなる。また、例えば、MG電極14は、半導体装置の駆動に適した仕事関数WF(work function)を有するWFメタル層をHK酸化膜13上に形成し、このWFメタル層上に金属材料からなる導電体層を形成する構成としてもよい。

【0016】

空洞部16は、MG電極14の側の下部に局所的に形成されている。そして、空洞部16により、半導体基体11上でのMG電極14とサイドウォール15との接触が妨げられている。この構造により、半導体基体11とMG電極14との間で生じるフリンジ容量を低減することができる。フリンジ容量は、MG電極14の側面端部と、半導体基体11との間における寄生容量であるため、この寄生容量の発生に最も寄与する部分を空洞化することにより、MG電極14と半導体基体11の間の誘電率を下げることができる。

【0017】

[半導体装置の製造方法の第1実施形態]

次に、半導体装置の製造方法の第1実施形態として、上述の半導体装置10の製造方法を説明する。

(1)素子分離形成

まず、シリコン基板からなる半導体基体11上に、例えば、SiO2を10nm、SiNを20nm程度順次形成する。そして、活性領域を形成する部分にレジストパターニングを行う。形成したレジストパターンをマスクにして、SiN、SiO2、及び、半導体基体11を順次エッチングし、トレンチ(トレンチ領域)を100〜200nmの深さで形成する。エッチングしたトレンチの表面に、例えば、800度、20minで酸化膜を形成した後、SiO2等の絶縁膜を埋め込む。このSiO2の埋め込みは、例えば、高密度プラズマ(HDP)CVDやHARP(High Aspect Ratio Process)等を用いて行う。SiO2の埋め込み後、CMP(Chemical Mechanical Polish)法により表面を平坦化する。そして、例えば、熱リン酸等を用いてSiNを除去する。

以上の工程により、半導体基体11に素子分離12を形成する。

【0018】

(2)ウェル領域及びチャネルのイオン注入

次に、半導体基体11のウェル領域とチャネル領域にイオン注入を行う。

ウェル領域の形成やパンチスルーの阻止を目的とした埋め込み層を形成するため、及び、閾値電圧(Vth)調整のため、イオン注入を行いチャネル領域を形成する。

例えば、半導体装置10がNMOSの場合には、ウェル領域はBを230keV、2.0×1013/cm2、チャネルはBを20keV、1.0×1013/cm2の条件で注入する。また、半導体装置10がPMOSの場合には、ウェル領域はPを500keV、3.0×1013/cm2、チャネルはPを50keV、6.0×1012/cm2の条件で注入する。

【0019】

(3)ダミーゲート電極の形成

次に、フッ酸を用いて半導体基体11表面のSiO2膜を除去した後、ダミーゲート絶縁膜21を形成する。ダミーゲート絶縁膜21は、例えば、ドライ酸化等を用いて半導体基体11の活性領域の表面にSiO2膜を3〜5nm形成する。そして、ダミーゲート絶縁膜21上にダミーゲート電極22を形成する。例えば、CVD法を用いて半導体基体11表面にダミーゲート電極22を形成するため、ポリシリコンやアモルファスシリコン等からなる層を形成する。そして、例えばLP−CVD(Low Pressure-Chemical Vapor Deposition)法を用いてエッチング用のハードマスク層23をSiNで形成し、リソグラフィによりハードマスク層23の電極のパターンを形成する。

次に、このハードマスク層23のパターンを用いてダミーゲート絶縁膜21とダミーゲート電極22の材料層に異方性エッチングを行う。この工程により、半導体基体11上に、ダミーゲート絶縁膜21とダミーゲート電極22を形成する。

【0020】

(4)オフセットスペーサ形成

次に、ダミーゲート電極22の側壁にオフセットスペーサ24を形成する。

オフセットスペーサ24は、ダミーゲート絶縁膜21と同じ材料、又は、ダミーゲート絶縁膜21と同じ薬液でウェットエッチングにより除去できる材料、例えばSiO2を用いて形成することが好ましい。

【0021】

半導体基体11及びダミーゲート電極22を覆って、オフセットスペーサ用材料層を4〜8nm程度形成する。そして、異方性エッチングにより、形成したオフセットスペーサ用材料層をエッチバックすることにより、ダミーゲート電極22の側壁に、オフセットスペーサ24を形成する。このとき、オフセットスペーサ24の高さが、ダミーゲート電極22高さよりも低くなるようにエッチングを行う。

【0022】

上述の図1に示す半導体装置10の空洞部16は、後述する工程においてオフセットスペーサ24を除去して形成する。つまり、形成されたオフセットスペーサ24の形状が、ほぼ保持されて空洞部16が形成される。このため、オフセットスペーサ24の形状を、半導体装置10の空洞部16の形状に加工することにより、空洞部16を任意の形状及び大きさに形成することができる。

【0023】

オフセットスペーサ24の形状は、オフセットスペーサ用材料層を形成する厚さと、エッチング量により決定される。例えば、エッチング量を少なくすることにより、オフセットスペーサ24の残存量が多くなるため、ダミーゲート電極22の側壁の高い位置までオフセットスペーサ24を形成することができる。また、エッチング量を多くすることにより、オフセットスペーサ24の残存量が少なくなり、ダミーゲート電極22の側壁の低い位置にオフセットスペーサ24を形成することができる。

【0024】

また、例えば、オフセットスペーサ用材料層を形成する厚さを大きくすることにより、半導体基体11上でオフセットスペーサ24が形成される範囲を大きくすることができる。また、オフセットスペーサ用材料層を形成する厚さを小さくすることにより、半導体基体11上でオフセットスペーサ24が形成される範囲を小さくすることができる。このように、ダミーゲート電極22の側壁部分に形成するオフセットスペーサ用材料層の厚さを調整することで、半導体基体11上でのオフセットスペーサ24の面積を調整することができる。

【0025】

(5)ハロー領域及びエクステンション領域のイオン注入

オフセットスペーサ24形成後、半導体基体11に、ハロー(Halo)領域及びエクステンション(Extension)領域を形成するためのイオン注入を行う。

例えば、半導体装置10がNMOSの場合には、Halo領域の形成はBF2を40keV、2×1013/cm2、Extension領域はAsを1.5keV、6×1014/cm2の条件で注入する。また、半導体装置10がPMOSの場合には、Haloの形成はAsを50keV、2×1013/cm2、Extension領域はBF2を1.5keV、6E×1014/cm2の条件で注入する。

【0026】

以上の工程により、図2Aに示すように、半導体基体11に、素子分離12、ダミーゲート絶縁膜21、ダミーゲート電極22、及び、オフセットスペーサ24を形成する。

【0027】

(6)サイドウォール形成

次に、図2Bに示すように、ダミーゲート電極22の側壁に、サイドウォール15,25を形成する。

例えば、プラズマCVD法を用いて、ダミーゲート電極22及びオフセットスペーサ24を覆って、半導体基体11上に、SiN層を20nm堆積する。さらに、SiN層上にSiO2層を35nm堆積する。そして、異方性エッチングを行い、SiO2層をエッチバックすることによりダミーゲート電極22の側壁にサイドウォール25を形成する。さらに、サイドウォール25をマスクにしてSiN層をエッチングすることにより、サイドウォール15を形成する。

【0028】

(7)ソース・ドレイン形成

次に、図2Cに示すように、サイドウォール15,25をマスクとして、半導体基体11に、ソース・ドレインを形成するためのイオン注入を行う。

例えば、半導体装置10がNMOSの場合には、Pを20keV、4×1013/cm2の条件で注入する。また、半導体装置10がPMOSの場合には、Bを4keV、4×1015/cmの条件で注入する。イオン注入後、不純物領域の活性化のために、1030〜1070℃程度のSpike RTA(Rapid Thermal Anneal)を行う。

【0029】

また、シリサイド化を行い、ソース・ドレインを低抵抗化する。

例えば、シリサイド化の前処理として、半導体基体11の表面をフッ酸(HF)で洗浄する。このとき、SiO2からなるサイドウォール25が除去される。

そして、ソース・ドレイン領域を覆って半導体基体11上に、スパッタによりNi層等の金属層を2〜8nm程度形成する。そして、RTAによりソース・ドレイン上にシリサイド17を形成する。シリサイド化後、ウェットエッチングにより見反応の金属層を除去する。

【0030】

(8)ダミーゲート電極除去

次に、図2Dに示すように、ダミーゲート電極22及びサイドウォール15を覆って半導体基体11上に、例えば、SiO2を150〜200nm程度堆積して層間絶縁層18を形成する。そして、図3Eに示すように、CMP法により平坦化を行うと同時に、ダミーゲート電極22上部を露出する。このとき、ダミーゲート電極22上に形成されていたハードマスク層23も、CMPにより同時に除去する。

【0031】

そして、図3Fに示すようにダミーゲート電極22を、ドライエッチング等を用いて除去する。ダミーゲート電極22と、ダミーゲート絶縁膜21及びオフセットスペーサ24とは、エッチングに選択性のある材料により形成されている。例えば、ダミーゲート電極22をポリシリコンで形成し、ダミーゲート絶縁膜21及びオフセットスペーサ24をSiO2で形成する。このため、ダミーゲート電極22のエッチング時に、ダミーゲート絶縁膜21が保護膜となり、半導体基体11の損傷を防ぐことができる。

【0032】

(9)ダミーゲート絶縁膜及びオフセットスペーサの除去

ダミーゲート電極22を除去した後、図3Gに示すように、フッ酸を用いたウェットエッチングにより、ダミーゲート絶縁膜21と、オフセットスペーサ24とを除去する。ダミーゲート電極22とオフセットスペーサ24とを同じ材料、例えば、SiO2で構成することにより、一度のウェットエッチングにより両方を除去することができる。

【0033】

なお、異なる材料を用いて、別工程でダミーゲート絶縁膜21とオフセットスペーサ24とをエッチングしてもよい。但し、サイドウォール15は残存させる必要があるため、ダミーゲート絶縁膜21及びオフセットスペーサ24は、サイドウォール15とはエッチングに選択性のある材料を用いる。

【0034】

オフセットスペーサ24を除去することにより、サイドウォール15の内壁側下部に、凹部が形成される。凹部の形状は、形成されていたオフセットスペーサ24の形状に依存する。この凹部が半導体装置10の空洞部16となる。

【0035】

(10)HK酸化膜及びMG電極形成

次に、図3Hに示すように、HK酸化膜13とMG電極14を形成する。

HK酸化膜13は、例えば、PVD(Physical Vapor Deposition)等の異方性の高い堆積方法を用いて形成する。HK酸化膜13は、例えば、HfO、HfSiO、LaO、ZrO、ZrSiO、TaO、TiO、BaSrTiO、BaTiO、StTiO、YO、AlO、及び、PbScTaO等を用いて形成する。

【0036】

また、MG電極14もHK酸化膜13と同様に、例えば、PVD(Physical Vapor Deposition)等の異方性の高い堆積方法を用いて形成する。MG電極14は、純金属材料、合金又は金属化合物から形成する。例えば、Ti、Al、Cu、W、HfSi及びTiN等により形成する。また、MG電極14は、例えば、HK酸化膜13上にHfSiやTiN等の半導体装置10に適した仕事関数を有するWF(Work Function)メタル層を形成した後、WFメタル層上に導電性の高いTi、Al、Cu、W等の材料を形成してもよい。

【0037】

HK酸化膜13及びMG電極14を、異方性の高い堆積方法で形成することにより、図3Hに示すように、オフセットスペーサ24が形成されていた部分には、HK酸化膜及びMG電極を形成することなく、空洞部16を形成することができる。

サイドウォール15の開口部の形状は、ダミーゲート電極が形成されていた形状と、同一形状である。このため、異方性の高い堆積方法を用いてHK酸化膜を形成することにより、サイドウォール15の開口部の形状とほぼ同じ形状のHK酸化膜を半導体基体上に形成することができる。

さらに、MG電極14も、PVD(Physical Vapor Deposition)等の異方性の高い堆積方法を用いて形成する。MG電極も異方性の高い堆積方法を用いて形成することにより、開口部の形状とほぼ同じ形状、つまり、ダミーゲート電極と同じ形状に形成することができる。

【0038】

次に、HK酸化膜13及びMG電極14を形成する際に、層間絶縁層18上にもHK酸化膜13の材料及びMG電極14の材料が堆積する。このため、CMP法等を用いて、層間絶縁層18上のHK酸化膜13の材料及びMG電極14の材料を除去する。

そして、層間絶縁層18上にMG電極14を覆うように、さらに層関絶縁層を形成し、Ti,TiN,W等から構成されるコンタクトを形成する。

以上の工程により半導体装置10を製造することができる。

【0039】

[作用]

上述の半導体装置の製造方法によれば、異方性の高い堆積方法を用いてサイドウォール15の開口部からMG電極14及びHK酸化膜13を形成することにより、MG電極14及びHK酸化膜13がダミーゲート電極及びダミーゲート絶縁膜と同じ形状となる。

ダミーゲート電極及びダミーゲート絶縁膜と同じ形状で形成することにより、オフセットスペーサ24が除去された部分に、オフセットスペーサ24と同じ形状の空洞部16が形成される。

オフセットスペーサ24は、上述の図2Aに示す工程において、形成する厚さとエッチング量を調整することにより、任意の形状に制御性よく形成することができる。このため、半導体装置10の空洞部16の形状は、オフセットスペーサ24の形成工程に依存して任意の形状に制御性よく形成される。

この結果、空洞部16の形状を制御性よく任意の形状に形成することができる。

【0040】

また、オフセットスペーサ24の形成位置は、ダミーゲート電極22の高さよりも低くすることが好ましい。ダミーゲート電極22と同じ高さにオフセットスペーサ24を形成すると、サイドウォール15を形成した場合に、サイドウォールとダミーゲート電極22との接触位置が、上部のわずかな部分のみとなる。この場合、サイドウォール15の内壁上部に、半導体基体11面に対して垂直な面が形成されない。

【0041】

ダミーゲート電極22、ダミーゲート絶縁層12及びオフセットスペーサ24を除去した後、サイドウォール15の内壁側に、異方性の高い堆積方法により、HK酸化膜13とMG電極14とを形成する。このとき、サイドウォール15の内壁に半導体基体11面に対して垂直な面が形成されていると、内壁側の空間で、横方法(基体面に平行な方向)への拡散を抑制することができる。特に、サイドウォール15の垂直面が基体面付近まで形成されていることにより、HK酸化膜13及びMG電極14の制御が容易になる。従って、オフセットスペーサ24をダミーゲート電極22よりも低い位置まで形成し、サイドウォール15の垂直面を充分に確保することが好ましい。

【0042】

[変形例1:CMOS]

次に、上述の半導体装置の製造方法の第1実施形態を適用して、第1導電型のMOSトンジスタと第2導電型のMOSトランジスタとを同時に形成する方法ついて説明する。なお、以下の説明では、一例として、第1導電型をP型、第2導電型をN型として説明している。PMOSとNMOSとを同時に形成する場合にも、上述の製造方法において、図3Gに示すダミーゲート絶縁膜21及びオフセットスペーサ24の除去工程までは、同様に行うことができる。このため、以下の説明では、ダミーゲート絶縁膜21及びオフセットスペーサ24の除去工程以降の製造方法について説明する。

【0043】

図4Aに示すように、ダミーゲート電極22、ダミーゲート絶縁膜21、サイドウォール15、及び、オフセットスペーサ24を除去した空洞部16を形成する。これは、上述の第1実施形態と同様の方法により形成することができる。

【0044】

次に、図4Bに示すように、異方性の高い堆積方法によりHK酸化膜13を形成する。HK酸化膜13は、サイドウォール15内の半導体基体11上に、所定の形状で形成される。また、図示しないが、層間絶縁層18上にも同様にもHK酸化膜13が形成される。

そして、全面にNMOS用のWFメタル層26を例えばHfSiにより形成する。

【0045】

図4Cに示すように、NMOS側のみにレジスト層27を形成し、ウェットエッチングにより、PMOSに形成されたNMOS用のWFメタル層26を除去する。

【0046】

図4Dに示すように、NMOS側のレジスト層27を除去した後、全面にPMOS用のWFメタル層28を例えばTiNにより形成する。

このとき、NMOSでは、HK酸化膜13上にNMOS用WFメタル層26が形成され、さらに、NMOS用WFメタル層26上にPMOS用WFメタル層28が形成される。また、PMOSでは、HK酸化膜13上にPMOS用WFメタル層28のみが形成される。

【0047】

次に、図4Eに示すように、WFメタル層26,28上に導電性の高い材料、例えば、Ti、Al、Cu、及び、W等を用いて、サイドウォール15内を埋め込み、上記WFメタル層26,28上に導電体層29を形成する。このとき、空洞部内に導電体が形成されないように導電体の埋め込みを行う。導電体層29とWFメタル層26,28とは、電気的に接続されていればよく、サイドウォール15内を完全に埋めこむ必要ない。

【0048】

上述の工程により、NMOSとPMOSとが混在している場合にも、上述の半導体装置の製造方法を適用することができる。また、NMOSとPMOSとで、ゲート電極にそれぞれ適した仕事関数を有する材料を用いた半導体装置20を製造することができる。

【0049】

[変形例2:ALD(Atomic Layer Deposition)]

次に、上述の半導体装置の製造方法において、HK酸化膜の形成に等方性の堆積方法、例えばALD法やCVD法を適用した場合について説明する。なお、ALD法やCVD法を用いてHK酸化膜を形成する場合にも、上述の製造方法において、図3Gに示すダミーゲート絶縁膜21及びオフセットスペーサ24の除去工程までは、同様に行うことができる。このため、以下の説明では、ダミーゲート絶縁膜21及びオフセットスペーサ24の除去工程以降の製造方法について説明する。

【0050】

図5に、HK酸化膜の形成に等方性の堆積方法を適用した半導体装置30の構成例を示す。図5に示す半導体装置30は、ALD法等を用いることにより、サイドウォール15の内壁、及び、サイドウォール15内の半導体基体11の全面に、HK酸化膜31が形成される。

【0051】

半導体装置30は、例えば、ダミーゲート絶縁膜21及びオフセットスペーサ24を除去した後、ALD法等の等方性の堆積方法を用いて、サイドウォール15内及び層間絶縁層18上にHK酸化膜13を形成する。HK酸化膜13は、例えば、HfO、HfSiO、LaO、ZrO、ZrSiO、TaO、TiO、BaSrTiO、BaTiO、StTiO、YO、AlO、及び、PbScTaO等を用いて形成する。

【0052】

さらに、HK酸化膜13を形成した後、上述の半導体装置の製造方法と同様に、PVD等の異方性の高い堆積方法を用いてMG電極14を形成する。MG電極14の形成は、空洞部16を確保するため、異方性の高い堆積方法を用いる。

【0053】

空洞部16の形状は、HK酸化膜31がサイドウォール15内壁に形成されている分、オフセットスペーサ24が形成されていた形状からの差が発生する。しかし、HK酸化膜31が形成される膜厚分を予め考慮してオフセットスペーサ24を形成することにより、所定の形状の空洞部16を有する半導体装置30を製造することができる。

【0054】

オフセットスペーサ24の形成は、上述のように膜厚とエッチバック量を調整することにより、制御性よく行うことができる。さらに、ALD法のように制御性の高い膜形成方法を用いることにより、空洞部16の形状の制御を容易に行うことができる。

【0055】

〈2.半導体装置の製造方法の第2実施形態〉

次に、半導体装置の製造方法の第2実施形態を説明する。なお、第2実施形態では、上述の第1実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

[半導体装置の構成例]

図6に、第2実施形態の製造方法に係わる半導体装置の構成図を示す。図6に示す半導体装置40は、例えば、シリコン基板等からなる半導体基体11に、活性領域を区画する酸化シリコン等からなる素子分離12が形成されている。そして、半導体基体11上に、高誘電率材料(High−k)からなる酸化膜(HK酸化膜)13を介してメタルゲート(MG)電極14が形成されている。MG電極14は、膜状のWFメタル層14Aと、WFメタル層14Aに接続された導電体層14Bとからなる。そして、HK酸化膜13とWFメタル層14Aの側壁に第1オフセットスペーサ32が形成されている。

【0056】

また、導電体層14Bの側壁から半導体基体11上まで連なるサイドウォール15が形成されている。そして、MG電極14の側壁下部とサイドウォール15との間に空洞部16が形成されている。

【0057】

また、半導体基体11には、図示しないソース・ドレイン、エクステンション領域及びHalo等の不純物領域が形成され、サイドウォール15から露出されている不純物領域(ソース・ドレイン)の表面にシリサイド17が形成されている。さらに、半導体基体11上に、MG電極14及びサイドウォール15を覆って、層間絶縁層18が形成されている。

【0058】

WFメタル層14Aは、HK酸化膜上に膜状に形成され、半導体装置の駆動に適した仕事関数WF(work function)を有する金属材料、例えば、HfSi及びTiN等からなる。導電体層14Bは、例えば、Ti、Al、Cu及びW等からなる。

また、第1オフセットスペーサは、例えば、SiN等の材料を用いて薄膜上に形成される。

【0059】

空洞部16は、サイドウォール15の内側、且つ、MG電極14を構成する導電体層14Bの側壁下部において、半導体基体11上に設けられている。HK酸化膜及びWFメタル層14Aの側壁には、第1オフセットスペーサ32が形成されている。このため、第1オフセットスペーサ32の外周に空洞部16が設けられている。

【0060】

上記のように空洞部16を形成することにより、半導体基体11上でのMG電極14とサイドウォール15との接触が妨げられている。この構造により、半導体基体11とMG電極14との間で生じるフリンジ容量を低減することができる。

【0061】

[半導体装置の製造方法の第2実施形態]

次に、半導体装置の製造方法の第2実施形態として、上述の半導体装置40の製造方法を説明する。

(1)素子分離〜オフセットスペーサ形成

まず、上述の半導体装置の製造方法の第1実施形態と同様に、素子分離12を形成し、ウェル領域及びチャネルを形成するためのイオン注入を行う。さらに、同様に、半導体基体11上に、ダミーゲート絶縁膜21とダミーゲート電極22を形成する。

【0062】

次に、ダミーゲート電極22の側壁に第1オフセットスペーサ32と、第2オフセットスペーサ24を形成する。第2オフセットスペーサ24は、上述の半導体装置の製造方法の第1実施形態におけるオフセットスペーサ24に該当する。

第1オフセットスペーサ32は、例えば、半導体基体11及びダミーゲート電極22を覆って、第1オフセットスペーサ用材料層を2〜4nm程度形成する。そして、異方性エッチングを用いて、形成した第1オフセットスペーサ用材料層をエッチバックすることにより、ダミーゲート電極22の側壁に、薄膜上の第1オフセットスペーサ32を形成する。このとき、第1オフセットスペーサ32は、ダミーゲート電極22の側壁全面を覆うように形成する。

【0063】

第1オフセットスペーサ32と第2オフセットスペーサ24とは、互いにウェットエッチングにおける選択性のある材料を用いる。例えば、第1オフセットスペーサ32をSiNから形成し、第2オフセットスペーサ24をSiO2から形成する。また、第1オフセットスペーサ32は、ダミーゲート電極22のエッチングの際、例えば、ダミーゲート電極22をドライエッチングで除去した後に、形状を維持して残存するような材料及び条件により形成する。

【0064】

次に、半導体基体11、ダミーゲート電極22、及び、第1オフセットスペーサ32を覆って、第1オフセットスペーサ用材料層を4〜8nm程度形成する。そして、異方性エッチングを用いて、形成したオフセットスペーサ用材料層をエッチバックすることにより、第1オフセットスペーサ32の側面に、第2オフセットスペーサ24を形成する。このとき、第2オフセットスペーサ24の高さが、ダミーゲート電極22よりも低くなるようにエッチングを行う。また、第2オフセットスペーサ24を、半導体装置40に形成する空洞部の形状に形成する。

【0065】

次に、第1オフセットスペーサ32及び第2オフセットスペーサ24を形成後、第1実施形態と同様に半導体基体11に、ハロー(Halo)領域及びエクステンション(Extension)領域を形成するためのイオン注入を行う。

以上の工程により、図7Aに示すように、半導体基体11に、素子分離12、ダミーゲート絶縁膜21、ダミーゲート電極22、第1オフセットスペーサ32、及び、第2オフセットスペーサ24を形成する。

【0066】

(2)サイドウォール形成〜層間絶縁層形成

次に、図7Bに示すように、ダミーゲート電極22の側壁に、第1オフセットスペーサ32及び第2オフセットスペーサ24を介してサイドウォール15,25を形成する。そして、図7Cに示すように、サイドウォール15,25をマスクとして、半導体基体11に、ソース・ドレインを形成するためのイオン注入を行う。また、図7Dに示すように、ダミーゲート電極22及びサイドウォール15を覆って、半導体基体11に層間絶縁層18を形成する。続けて、図8Eに示すように、層間絶縁層18の平坦化し、ダミーゲート電極22の上部を露出する。

上記各工程は、オフセットスペーサが、第1オフセットスペーサ32と第2オフセットスペーサ24とから構成されている以外は、上述の第1実施形態と同様の方法で行うことができる。

【0067】

(3)ダミーゲート電極除去

次に、図8Fに示すように、ダミーゲート電極22を、ドライエッチング等を用いて除去する。このとき、ダミーゲート電極22と、ダミーゲート絶縁膜21及び第1オフセットスペーサ32とは、エッチングに選択性のある材料から形成されている。例えば、ダミーゲート電極22をポリシリコンで形成し、第1オフセットスペーサ32をSiN、ダミーゲート絶縁膜21をSiO2で形成する。このため、ダミーゲート電極22のエッチング時に第1オフセットスペーサ32が、サイドウォール15及び第2オフセットスペーサ24の保護膜となる。また、ダミーゲート絶縁膜21が保護膜となり、半導体基体11への損傷を防ぐことができる。

【0068】

(4)ダミーゲート絶縁膜の除去

ダミーゲート電極22を除去した後、図8Gに示すように、フッ酸を用いたウェットエッチングにより、ダミーゲート絶縁膜21を除去する。このとき、第1オフセットスペーサ32が、ダミーゲート電極22とエッチング選択性のある材料で形成されているため残存する。このため、第2オフセットスペーサ24がダミーゲート電極22と同じ材料で形成されている場合にも、第1オフセットスペーサ32が保護膜となり、ダミーゲート絶縁膜21のみを除去し、第2オフセットスペーサ24を残存させることができる。

【0069】

(5)HK酸化膜及びWFメタル層形成

次に、図8Hに示すように、HK酸化膜13とWFメタル層14Aを形成する。サイドウォール15の開口部の内壁全面には、第2オフセットスペーサ24が形成されている。このため、第2オフセットスペーサ24内において、半導体基体11上にHK酸化膜13を形成する。

HK酸化膜13は、第1実施形態と同様に、PVD法等の異方性の高い堆積方法を用いて形成してもよく、また、ALD法やCVD法等の堆積方法を用いてもよい。

【0070】

HK酸化膜13を形成した後、HK酸化膜13上にWFメタル層14Aを形成する。WFメタル層14Aは、例えば、PVD(Physical Vapor Deposition)等の異方性の高い堆積方法を用いて形成し、HK酸化膜13上のみに形成する。

後の工程において第1オフセットスペーサ32を除去する必要があるため、異方性の高い堆積方法でWFメタル層14Aを形成し、第2オフセットスペーサ24内壁への金属材料の堆積を抑制する。

【0071】

なお、ALD法やCVD法等の堆積方法で、HK酸化膜13を形成した場合には、WFメタル層14Aを形成した後、WFメタル層14A上のHK酸化膜をフッ酸等によるウェットエッチングで除去する。このとき、WFメタル層14Aを保護層とすることにより、WFメタル層14Aの下部で半導体基体11上に形成されているHK酸化膜13のみが残存する。

【0072】

(6)オフセットスペーサの除去

図9Iに示すように、第1オフセットスペーサ32を除去する。第1オフセットスペーサ32の除去は、例えば、ホットリン酸を用いたウェットエッチングにより行う。第1オフセットスペーサ32を除去することにより、第2オフセットスペーサ24の内面上部が露出される。また、HK酸化膜13及びWFメタル層14Aの側壁に第1オフセットスペーサ32が部分的に残存する。

【0073】

そして、第1オフセットスペーサ32を除去した後、露出した第2オフセットスペーサ24を、フッ酸を用いたウェットエッチングにより除去する。第2オフセットスペーサ24を除去ことにより、第2オフセットスペーサ24が形成されていた領域が、半導体装置40の空洞部16となる。

このとき、HK酸化膜13及びWFメタル層14Aの側壁に残存している第1オフセットスペーサ32が保護膜となり、HK酸化膜13へのウェットエッチングによる損傷を防ぐことができる。

【0074】

なお、第1オフセットスペーサ32をエッチングした後も、HK酸化膜13及びWFメタル層14Aの側壁に第1オフセットスペーサ32が部分的に残存する。このように、第1オフセットスペーサ32が残存していても、空洞部16の形状に影響がなく、また、半導体装置の特性にもほとんど影響を与えないため、第1オフセットスペーサ32の残存部を改めて除去する必要はない。

【0075】

また、第1オフセットスペーサ32をウェットエッチングで除去する際に、同じ材料で形成されているサイドウォール15の露出面も、エッチングの影響を受ける。このため、第1オフセットスペーサ32を充分に薄く形成し、第1オフセットスペーサ32のエッチングを短時間で行うことにより、サイドウォール15への影響を最小限にすることが好ましい。

【0076】

(7)導電体層形成

次に、図9Kに示すように、WFメタル層14A上に導電性の高い材料、例えば、Ti、Al、Cu、W、及び、これらを含む合金を用いて、サイドウォール15内を埋め込み、上記WFメタル層14A上に導電体層14Bを形成する。このとき、空洞部内に導電体が形成されないように導電体の埋め込みを行う。導電体層14BとWFメタル層14Aとは、電気的に接続されていればよく、サイドウォール15内を完全に埋めこむ必要ない。

このように、WFメタル層14Aと導電体層14BとからMG電極14を形成する。

【0077】

以上の工程により、サイドウォール15内壁に形成された薄膜上の第1オフセットスペーサ32を用いて、HK酸化膜13及びMG電極14が所定に位置に正確に形成された半導体装置40を製造することができる。

【0078】

[作用]

上述の第2実施形態では、ダミーゲート電極22の側壁の全面に、第1オフセットスペーサ32を形成する

第1オフセットスペーサ32を残存させた状態で、HK酸化膜13とWFメタル層14Aを形成する。このため、第1オフセットスペーサ32内に、HK酸化膜13とWFメタル層14Aとが形成される。従って、HK酸化膜13とWFメタル層14Aとを所定の領域に制御性よく形成することができる。そして、HK酸化膜13とWFメタル層14Aを形成後、WFメタル層14Aよりも上方の第1オフセットスペーサ32を除去して、露出した第2オフセットスペーサ24を除去する。そして、第2オフセットスペーサ24を除去したのち、WFメタル層14Aに接続する導電体層14Bを形成することにより、半導体装置40に空洞部16が形成される。

以上の工程によれば、空洞部16が形成された後には、半導体基体11上にHK酸化膜13とWFメタル層14Aが形成されない。また、導電体層14Bは、WFメタル層14Aとの電気的な接続が形成されていればよく、ゲート長全域に精密に形成する必要がない。このため、導電体層14Bの形成による空洞部16の形状変化は考慮しなくてよい。

【0079】

上述の第1実施形態では、異方性の高い堆積方法を用いてHK酸化膜及びMG電極を形成する。異方性の高い堆積方法を用いることにより、空洞部を確保することができる。そして、第2実施形態では、第2オフセットスペーサの内側に第1オフセットスペーサを設ける。このため、ダミーゲート絶縁膜と、第2オフセットスペーサとが同じ材料から形成されている場合にも、ダミーゲート絶縁膜を除去する際に、第1オフセットスペーサが保護膜となり、第2オフセットスペーサが残存する。

【0080】

第2オフセットスペーサの除去による空洞部の形成工程以前に、ダミーゲート絶縁膜の除去と、HK酸化膜の形成が可能となる。このため、空洞部が形成された後に、空洞部の形状を変化させる膜形成等が行われない。従って、半導体装置に形成される空洞部は、第2オフセットスペーサの形状がより正確に保持される。

さらに、第2オフセットスペーサ内のHK酸化膜上に、WFメタル層を形成することにより、WFメタル層の形成領域が、HK酸化膜上に限定される。従って、精密なゲート電極形成が可能となる。

【0081】

なお、上述の第2実施形態では、MG電極をWFメタル層により形成したが、他の金属材料により形成してもよい。例えば、導電体層と同じ材料をHK酸化膜上に形成してもよい。

【0082】

〈3.半導体装置の製造方法の第3実施形態〉

次に、半導体装置の製造方法の第3実施形態を説明する。なお、第3実施形態では、上述の第1実施形態及び第2実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

[半導体装置の構成例]

図10に、第3実施形態の製造方法に係わる半導体装置の構成図を示す。図10に示す半導体装置50は、例えば、シリコン基板等からなる半導体基体11に、活性領域を区画する酸化シリコン等からなる素子分離12が形成されている。そして、半導体基体11上に、高誘電率材料(High−k)からなる酸化膜(HK酸化膜)13を介してメタルゲート(MG)電極14が形成されている。MG電極14は、膜状のWFメタル層14Aと、WFメタル層14Aに接続された導電体層14Bとからなる。

また、導電体層14Bの側壁から半導体基体11上まで連なるサイドウォール15が形成されている。そして、MG電極14の側壁下部とサイドウォール15との間に空洞部16が形成されている。

【0083】

また、半導体基体11には、図示しないソース・ドレイン、エクステンション領域及びHalo領域等の不純物領域が形成され、サイドウォール15から露出されている不純物領域(ソース・ドレイン)の表面にシリサイド17が形成されている。さらに、半導体基体11上に、MG電極14及びサイドウォール15を覆って、層間絶縁層18が形成されている。

【0084】

空洞部16は、サイドウォール15の内側、且つ、MG電極14を構成する導電体層14Bの側壁下部において、半導体基体11上に設けられている。HK酸化膜及びWFメタル層14Aの側壁には、第1オフセットスペーサ32が形成されている。このため、第1オフセットスペーサ32の外周に空洞部16が設けられている。

【0085】

上記のように空洞部16を形成することにより、半導体基体11上でのMG電極14とサイドウォール15との接触が妨げられている。この構造により、半導体基体11とMG電極14との間で生じるフリンジ容量を低減することができる。

【0086】

[半導体装置の製造方法の第3実施形態]

次に、半導体装置の製造方法の第3実施形態として、上述の半導体装置50の製造方法を説明する。

(1)素子分離〜ウェル領域及びチャネルのイオン注入

まず、上述の半導体装置の製造方法の第1実施形態と同様に、素子分離12を形成し、ウェル領域及びチャネルを形成するためのイオン注入を行う。

【0087】

(2)HK酸化膜、WFメタル層、及び、ダミーゲート電極の形成

次に、フッ酸を用いて半導体基体11表面のSiO2膜を除去した後、半導体基体11の上の全面に、HK酸化膜13、WFメタル層14A及びダミーゲート電極22からなる積層体を形成する。

HK酸化膜13は、例えば、上述のHK材料をPVD法、ALD法及びCVD法等の堆積方法を用いて、半導体基体11の上の全面に1〜3nm形成する。そして、同様に金属材料を用いて、HK酸化膜13上にWFメタル層14Aを形成する。さらに、WFメタル層14A上に、ポリシリコン等によりダミーゲート電極22を形成する。

【0088】

次に、上述の積層体上に、ハードマスク層23をSiNで形成し、リソグラフィにより所定のゲート電極形状にハードマスク層23のパターンを形成する。そして、このハードマスク層23のパターンを用いてHK酸化膜13、WFメタル層14A及びダミーゲート電極22からなる積層体に異方性エッチングを行う。この工程により、半導体基体11上に、図11Aに示す、HK酸化膜13、WFメタル層14A及びダミーゲート電極22からなるゲート電極状の積層体を形成する。

【0089】

(3)オフセットスペーサの形成

次に、ダミーゲート電極22の側壁にオフセットスペーサ24を形成する。オフセットスペーサ24は上述の第1実施形態と同様の方法により形成することができる。また、オフセットスペーサ24は、HK酸化膜13とウェットエッチングにおける選択性のある材料、例えばSiO2を用いて形成することが好ましい。

【0090】

(4)ハロー領域及びエクステンション領域のイオン注入

次に、オフセットスペーサ24を形成後、第1実施形態と同様に半導体基体11に、ハロー(Halo)領域及びエクステンション(Extension)領域を形成するためのイオン注入を行う。

以上の工程により、図11Aに示すように、半導体基体11に、素子分離12、HK酸化膜13、WFメタル層14A、ダミーゲート電極22、及び、オフセットスペーサ24を形成する。

【0091】

(5)サイドウォール形成〜ダミーゲート電極除去

次に、図11Bに示すように、ダミーゲート電極22の側壁に、オフセットスペーサ24を介してサイドウォール15,25を形成する。そして、図11Cに示すように、サイドウォール15,25をマスクとして、半導体基体11に、ソース・ドレインを形成するためのイオン注入を行う。また、図11Dに示すように、ダミーゲート電極22及びサイドウォール15を覆って、半導体基体11に層間絶縁層18を形成する。続けて、図12Eに示すように、層間絶縁層18を平坦化し、ダミーゲート電極22上部を露出する。

そして、図12Fに示すように、ダミーゲート電極22を、ドライエッチング等を用いて除去する。このとき、WFメタル層14Aがマスクとなり、HK酸化膜13へのエッチングによる損傷を防ぐことができる。

【0092】

上記各工程は、ダミーゲート絶縁膜に換えてHK酸化膜13が形成され、さらに、ダミーゲート電極22の下部にWFメタル層14Aが形成されている以外は、上述の第1実施形態と同様の方法で行うことができる。

【0093】

(6)オフセットスペーサの除去

次に、図12Gに示すように、フッ酸を用いたウェットエッチングにより、オフセットスペーサ24を除去する。このとき、WFメタル層14Aがマスクとなり、HK酸化膜13へのエッチングによる損傷を防ぐことができる。

オフセットスペーサ24を除去することにより、サイドウォール15の内壁側下部に、凹部が形成される。凹部の形状は、形成されていたオフセットスペーサ24の形状に依存する。第2オフセットスペーサ24を除去することにより、第2オフセットスペーサ24が形成されていた領域、つまり上記凹部が半導体装置50の空洞部16となる。

【0094】

(7)導電体層形成

次に、図12Hに示すように、WFメタル層14A上に導電性の高い材料、例えば、Ti、Al、Cu、W、及び、これらを含む合金を用いて、サイドウォール15内を埋め込み、上記WFメタル層14A上に導電体層14Bを形成する。このとき、空洞部内に導電体が形成されないように埋め込みを行う。導電体層14BとWFメタル層14Aとは、電気的に接続されていればよいため、サイドウォール15内を完全に導電体で埋めこむ必要ない。

このように、WFメタル層14Aと導電体層14BとからMG電極14を形成する。

【0095】

以上の工程により、HK酸化膜13、及び、MG電極14となるWFメタル層14Aを、ダミーゲート電極22よりも前に形成する方法により、半導体装置50を製造することができる。

【0096】

サイドウォール15内壁に形成された薄膜上の第1オフセットスペーサ32を用いて、HK酸化膜13及びMG電極14が、所定の位置に正確に形成された半導体装置40を製造することができる。この製造方法によれば、予めゲート電極の形状にHK酸化膜とWFメタル層を形成することにより、第1実施形態のようにサイドウォール開口部から異方性の高い堆積方法によるゲート絶縁膜及びゲート電極の形成が不要となる。このため、空洞部形成後に、空洞部と隣接する領域にHK酸化膜及びゲート電極を形成しない。従って、より適正なHK酸化膜、ゲート電極、及び、空洞部を形成することができる。

【0097】

なお、本発明は上述の実施形態例において説明した構成に限定されるものではなく、その他本発明構成を逸脱しない範囲において種々の変形、変更が可能である。

【符号の説明】

【0098】

10,20,30,40,50 半導体装置、11 半導体基体、12 素子分離、13,31 HK酸化膜、14 MG電極、14A,26,28 WFメタル層、14B,29 導電体層、15,25 サイドウォール、16 空洞部、17 シリサイド、18 層間絶縁層、21 ダミーゲート絶縁膜、22 ダミーゲート電極、23 ハードマスク層、24 オフセットスペーサ(第2オフセットスペーサ)、27 レジスト層、32 第1オフセットスペーサ

【技術分野】

【0001】

本発明は、半導体装置の製造方法、特に高誘電率膜及びメタルゲート電極を備える半導体装置の製造方法に係わる。

【背景技術】

【0002】

MOSトランジスタの動作速度は、容量の増加により低下する。このため、駆動電流に寄与しない寄生容量、特に、フリンジ容量を低減する必要がある。寄生容量を低下させる方法としては、オフセットスペーサの下部に空洞部を設け、ゲート電極とサイドウォールとの間に空間を形成した構造の半導体装置が提案されている(例えば、特許文献1参照)。この方法では、ゲート電極の側壁にオフセットスペーサを形成した後、オフセットスペーサの下部を局所的にウェットエッチングにより除去し、オフセットスペーサ下部に空間を形成する。そして、この空間を埋めこまない方法でサイドウォールを形成する。この結果、ゲート電極とサイドウォールとの間で、オフセットスペーサの下部に局所的に空洞部を形成することができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2004−95888号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、ウェットエッチングにより、オフセットスペーサの下部のみに空洞を選択的に形成する場合には、所定の形状に空洞部を制御よく実現することが難しい。

また、高誘電率(High−k)材料を用いたゲート絶縁膜(HK)、及び、金属(Metal)材料を用いたゲート電極(MG)からなる半導体装置が提案されている。このような構成の半導体装置を製造する際に、一般的に適用されるゲートラスト(Gate Last)製造プロセスでは、上述の製造方法を適用することが難しい。例えば、上述の特許文献1に記載された半導体装置では、オフセットスペーサがシリコン酸化膜により構成されている。しかし、ゲートラストプロセスでは、ウェットエッチングにより、ダミーゲート絶縁膜を除去する工程がある。この工程において、シリコン酸化膜からなるオフセットスペーサが同時に除去されるため、オフセットスペーサ下部の空洞部も消失してしまう。

【0005】

上述のように、ゲート電極とサイドウォールとの間に空洞部を設けて寄生容量を抑制する構造の半導体装置において、従来の製造方法では空洞部を制御性よく形成することが難しい。

【0006】

上述した問題の解決のため、本発明においては、制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0007】

本発明の半導体装置の製造方法は、半導体基体上にダミーゲート絶縁膜及びダミーゲート電極を形成する工程を有する。そして、ダミーゲート電極上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極の側壁下部にオフセットスペーサを形成する工程を有する。オフセットスペーサ上を覆って、ダミーゲート電極の側壁にサイドウォールを形成する工程と、サイドウォールを埋め込み、かつダミーゲート電極の上面を露出させる層間絶縁層を形成する工程とを有する。さらに、ダミーゲート電極を除去する工程と、ダミーゲート絶縁膜を除去する工程と、オフセットスペーサを除去する工程と、半導体基体上に高誘電率材料からなるゲート絶縁膜を形成する工程を有する。そして、ゲート絶縁膜上に、異方性の高い堆積方法を用いてメタルゲート電極を形成する工程を有する。

【0008】

また、本発明の半導体装置の製造方法は、半導体基体上に高誘電率材料からなるゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属材料層からなるゲート電極を形成する工程と、金属材料層上にダミーゲート電極を形成する工程とを有する。そして、ダミーゲート電極上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ゲート電極及びダミーゲート電極の側壁に、オフセットスペーサを形成する工程を有する。さらに、オフセットスペーサ上を覆って、ダミーゲート電極の側壁にサイドウォールを形成する工程と、サイドウォールを埋め込み、かつダミーゲート電極の上面を露出させる層間絶縁層を形成する工程とを有する。そして、ダミーゲート電極、及び、オフセットスペーサを除去する工程と、ゲート電極上に、導電体層を形成する工程とを有する。

【0009】

本発明の半導体装置の製造方法によれば、ダミーゲート電極上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極の側壁下部にオフセットスペーサを形成する。そして、サイドウォールの形成後、ダミーゲート電極とオフセットスペーサを除去し、高誘電率材料からなるゲート絶縁膜とメタルゲート電極とを異方性の高い堆積方法を用いて形成する。このため、オフセットスペーサ24が除去された部分に、オフセットスペーサ24と同じ形状の空洞部16が形成される。

オフセットスペーサは、形成する厚さとエッチング量を調整することにより、任意の形状に制御性よく形成することができる。従って、半導体装置の空洞部の形状を、オフセットスペーサの形成工程に依存して、任意の形状に制御性よく形成することができる。

【発明の効果】

【0010】

本発明によれば、空洞部の形成を制御よく行うことが可能な半導体装置の製造方法を提供することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の半導体装置の製造方法の第1実施形態に係わる半導体装置の構成を示す図である。

【図2】A〜Dは、本発明の第1実施形態の半導体装置の製造工程を示す図である。

【図3】E〜Hは、本発明の第1実施形態の半導体装置の製造工程を示す図である。

【図4】A〜Eは、本発明の第1実施形態の半導体装置の製造工程を示す図である。

【図5】本発明の半導体装置の製造方法の第1実施形態に係わる半導体装置の構成を示す図である。

【図6】本発明の半導体装置の製造方法の第2実施形態に係わる半導体装置の構成を示す図である。

【図7】A〜Dは、本発明の第2実施形態の半導体装置の製造工程を示す図である。

【図8】E〜Hは、本発明の第2実施形態の半導体装置の製造工程を示す図である。

【図9】I〜Kは、本発明の第2実施形態の半導体装置の製造工程を示す図である。

【図10】本発明の半導体装置の製造方法の第3実施形態に係わる半導体装置の構成を示す図である。

【図11】A〜Dは、本発明の第3実施形態の半導体装置の製造工程を示す図である。

【図12】E〜Hは、本発明の第3実施形態の半導体装置の製造工程を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明を実施するための最良の形態の例を説明するが、本発明は以下の例に限定されるものではない。

なお、説明は以下の順序で行う。

1.半導体装置の製造方法の第1実施形態

2.半導体装置の製造方法の第2実施形態

3.半導体装置の製造方法の第3実施形態

【0013】

〈1.半導体装置の製造方法の第1実施形態〉

[半導体装置の構成例]

以下本発明の半導体装置の具体的な実施の形態について説明する。

図1に、第1実施形態の製造方法に係わる半導体装置の概略構成図を示す。図1に示す半導体装置10は、例えば、シリコン基板等からなる半導体基体11に、活性領域を区画する酸化シリコン等からなる素子分離12が形成されている。そして、半導体基体11上に、高誘電率(High−k)材料からなる酸化膜(HK酸化膜)13を介してメタルゲート(MG)電極14が形成されている。そして、MG電極14の側壁に、サイドウォール15が形成されている。MG電極の側壁下部には、MG電極とサイドウォール15との間に設けられた空間からなる空洞部16が形成されている。

【0014】

また、半導体基体11には、図示しないソース・ドレイン、エクステンション領域及びHalo等の不純物領域が形成され、サイドウォール15から露出されている不純物領域(ソース・ドレイン)の表面にシリサイド17が形成されている。さらに、半導体基体11上に、MG電極14及びサイドウォール15を覆って、層間絶縁層18が形成されている。

【0015】

HK酸化膜13は、酸化シリコンよりも誘電率の高い高誘電率材料から形成される。高誘電率材料としては、HfO、HfSiO、LaO、ZrO、ZrSiO、TaO、TiO、BaSrTiO、BaTiO、StTiO、YO、AlO、及び、PbScTaO等を用いることができる。

MG電極14は、純金属材料、合金又は金属化合物からなり、例えば、Ti、Al、Cu、W、HfSi及びTiN等からなる。また、例えば、MG電極14は、半導体装置の駆動に適した仕事関数WF(work function)を有するWFメタル層をHK酸化膜13上に形成し、このWFメタル層上に金属材料からなる導電体層を形成する構成としてもよい。

【0016】

空洞部16は、MG電極14の側の下部に局所的に形成されている。そして、空洞部16により、半導体基体11上でのMG電極14とサイドウォール15との接触が妨げられている。この構造により、半導体基体11とMG電極14との間で生じるフリンジ容量を低減することができる。フリンジ容量は、MG電極14の側面端部と、半導体基体11との間における寄生容量であるため、この寄生容量の発生に最も寄与する部分を空洞化することにより、MG電極14と半導体基体11の間の誘電率を下げることができる。

【0017】

[半導体装置の製造方法の第1実施形態]

次に、半導体装置の製造方法の第1実施形態として、上述の半導体装置10の製造方法を説明する。

(1)素子分離形成

まず、シリコン基板からなる半導体基体11上に、例えば、SiO2を10nm、SiNを20nm程度順次形成する。そして、活性領域を形成する部分にレジストパターニングを行う。形成したレジストパターンをマスクにして、SiN、SiO2、及び、半導体基体11を順次エッチングし、トレンチ(トレンチ領域)を100〜200nmの深さで形成する。エッチングしたトレンチの表面に、例えば、800度、20minで酸化膜を形成した後、SiO2等の絶縁膜を埋め込む。このSiO2の埋め込みは、例えば、高密度プラズマ(HDP)CVDやHARP(High Aspect Ratio Process)等を用いて行う。SiO2の埋め込み後、CMP(Chemical Mechanical Polish)法により表面を平坦化する。そして、例えば、熱リン酸等を用いてSiNを除去する。

以上の工程により、半導体基体11に素子分離12を形成する。

【0018】

(2)ウェル領域及びチャネルのイオン注入

次に、半導体基体11のウェル領域とチャネル領域にイオン注入を行う。

ウェル領域の形成やパンチスルーの阻止を目的とした埋め込み層を形成するため、及び、閾値電圧(Vth)調整のため、イオン注入を行いチャネル領域を形成する。

例えば、半導体装置10がNMOSの場合には、ウェル領域はBを230keV、2.0×1013/cm2、チャネルはBを20keV、1.0×1013/cm2の条件で注入する。また、半導体装置10がPMOSの場合には、ウェル領域はPを500keV、3.0×1013/cm2、チャネルはPを50keV、6.0×1012/cm2の条件で注入する。

【0019】

(3)ダミーゲート電極の形成

次に、フッ酸を用いて半導体基体11表面のSiO2膜を除去した後、ダミーゲート絶縁膜21を形成する。ダミーゲート絶縁膜21は、例えば、ドライ酸化等を用いて半導体基体11の活性領域の表面にSiO2膜を3〜5nm形成する。そして、ダミーゲート絶縁膜21上にダミーゲート電極22を形成する。例えば、CVD法を用いて半導体基体11表面にダミーゲート電極22を形成するため、ポリシリコンやアモルファスシリコン等からなる層を形成する。そして、例えばLP−CVD(Low Pressure-Chemical Vapor Deposition)法を用いてエッチング用のハードマスク層23をSiNで形成し、リソグラフィによりハードマスク層23の電極のパターンを形成する。

次に、このハードマスク層23のパターンを用いてダミーゲート絶縁膜21とダミーゲート電極22の材料層に異方性エッチングを行う。この工程により、半導体基体11上に、ダミーゲート絶縁膜21とダミーゲート電極22を形成する。

【0020】

(4)オフセットスペーサ形成

次に、ダミーゲート電極22の側壁にオフセットスペーサ24を形成する。

オフセットスペーサ24は、ダミーゲート絶縁膜21と同じ材料、又は、ダミーゲート絶縁膜21と同じ薬液でウェットエッチングにより除去できる材料、例えばSiO2を用いて形成することが好ましい。

【0021】

半導体基体11及びダミーゲート電極22を覆って、オフセットスペーサ用材料層を4〜8nm程度形成する。そして、異方性エッチングにより、形成したオフセットスペーサ用材料層をエッチバックすることにより、ダミーゲート電極22の側壁に、オフセットスペーサ24を形成する。このとき、オフセットスペーサ24の高さが、ダミーゲート電極22高さよりも低くなるようにエッチングを行う。

【0022】

上述の図1に示す半導体装置10の空洞部16は、後述する工程においてオフセットスペーサ24を除去して形成する。つまり、形成されたオフセットスペーサ24の形状が、ほぼ保持されて空洞部16が形成される。このため、オフセットスペーサ24の形状を、半導体装置10の空洞部16の形状に加工することにより、空洞部16を任意の形状及び大きさに形成することができる。

【0023】

オフセットスペーサ24の形状は、オフセットスペーサ用材料層を形成する厚さと、エッチング量により決定される。例えば、エッチング量を少なくすることにより、オフセットスペーサ24の残存量が多くなるため、ダミーゲート電極22の側壁の高い位置までオフセットスペーサ24を形成することができる。また、エッチング量を多くすることにより、オフセットスペーサ24の残存量が少なくなり、ダミーゲート電極22の側壁の低い位置にオフセットスペーサ24を形成することができる。

【0024】

また、例えば、オフセットスペーサ用材料層を形成する厚さを大きくすることにより、半導体基体11上でオフセットスペーサ24が形成される範囲を大きくすることができる。また、オフセットスペーサ用材料層を形成する厚さを小さくすることにより、半導体基体11上でオフセットスペーサ24が形成される範囲を小さくすることができる。このように、ダミーゲート電極22の側壁部分に形成するオフセットスペーサ用材料層の厚さを調整することで、半導体基体11上でのオフセットスペーサ24の面積を調整することができる。

【0025】

(5)ハロー領域及びエクステンション領域のイオン注入

オフセットスペーサ24形成後、半導体基体11に、ハロー(Halo)領域及びエクステンション(Extension)領域を形成するためのイオン注入を行う。

例えば、半導体装置10がNMOSの場合には、Halo領域の形成はBF2を40keV、2×1013/cm2、Extension領域はAsを1.5keV、6×1014/cm2の条件で注入する。また、半導体装置10がPMOSの場合には、Haloの形成はAsを50keV、2×1013/cm2、Extension領域はBF2を1.5keV、6E×1014/cm2の条件で注入する。

【0026】

以上の工程により、図2Aに示すように、半導体基体11に、素子分離12、ダミーゲート絶縁膜21、ダミーゲート電極22、及び、オフセットスペーサ24を形成する。

【0027】

(6)サイドウォール形成

次に、図2Bに示すように、ダミーゲート電極22の側壁に、サイドウォール15,25を形成する。

例えば、プラズマCVD法を用いて、ダミーゲート電極22及びオフセットスペーサ24を覆って、半導体基体11上に、SiN層を20nm堆積する。さらに、SiN層上にSiO2層を35nm堆積する。そして、異方性エッチングを行い、SiO2層をエッチバックすることによりダミーゲート電極22の側壁にサイドウォール25を形成する。さらに、サイドウォール25をマスクにしてSiN層をエッチングすることにより、サイドウォール15を形成する。

【0028】

(7)ソース・ドレイン形成

次に、図2Cに示すように、サイドウォール15,25をマスクとして、半導体基体11に、ソース・ドレインを形成するためのイオン注入を行う。

例えば、半導体装置10がNMOSの場合には、Pを20keV、4×1013/cm2の条件で注入する。また、半導体装置10がPMOSの場合には、Bを4keV、4×1015/cmの条件で注入する。イオン注入後、不純物領域の活性化のために、1030〜1070℃程度のSpike RTA(Rapid Thermal Anneal)を行う。

【0029】

また、シリサイド化を行い、ソース・ドレインを低抵抗化する。

例えば、シリサイド化の前処理として、半導体基体11の表面をフッ酸(HF)で洗浄する。このとき、SiO2からなるサイドウォール25が除去される。

そして、ソース・ドレイン領域を覆って半導体基体11上に、スパッタによりNi層等の金属層を2〜8nm程度形成する。そして、RTAによりソース・ドレイン上にシリサイド17を形成する。シリサイド化後、ウェットエッチングにより見反応の金属層を除去する。

【0030】

(8)ダミーゲート電極除去

次に、図2Dに示すように、ダミーゲート電極22及びサイドウォール15を覆って半導体基体11上に、例えば、SiO2を150〜200nm程度堆積して層間絶縁層18を形成する。そして、図3Eに示すように、CMP法により平坦化を行うと同時に、ダミーゲート電極22上部を露出する。このとき、ダミーゲート電極22上に形成されていたハードマスク層23も、CMPにより同時に除去する。

【0031】

そして、図3Fに示すようにダミーゲート電極22を、ドライエッチング等を用いて除去する。ダミーゲート電極22と、ダミーゲート絶縁膜21及びオフセットスペーサ24とは、エッチングに選択性のある材料により形成されている。例えば、ダミーゲート電極22をポリシリコンで形成し、ダミーゲート絶縁膜21及びオフセットスペーサ24をSiO2で形成する。このため、ダミーゲート電極22のエッチング時に、ダミーゲート絶縁膜21が保護膜となり、半導体基体11の損傷を防ぐことができる。

【0032】

(9)ダミーゲート絶縁膜及びオフセットスペーサの除去

ダミーゲート電極22を除去した後、図3Gに示すように、フッ酸を用いたウェットエッチングにより、ダミーゲート絶縁膜21と、オフセットスペーサ24とを除去する。ダミーゲート電極22とオフセットスペーサ24とを同じ材料、例えば、SiO2で構成することにより、一度のウェットエッチングにより両方を除去することができる。

【0033】

なお、異なる材料を用いて、別工程でダミーゲート絶縁膜21とオフセットスペーサ24とをエッチングしてもよい。但し、サイドウォール15は残存させる必要があるため、ダミーゲート絶縁膜21及びオフセットスペーサ24は、サイドウォール15とはエッチングに選択性のある材料を用いる。

【0034】

オフセットスペーサ24を除去することにより、サイドウォール15の内壁側下部に、凹部が形成される。凹部の形状は、形成されていたオフセットスペーサ24の形状に依存する。この凹部が半導体装置10の空洞部16となる。

【0035】

(10)HK酸化膜及びMG電極形成

次に、図3Hに示すように、HK酸化膜13とMG電極14を形成する。

HK酸化膜13は、例えば、PVD(Physical Vapor Deposition)等の異方性の高い堆積方法を用いて形成する。HK酸化膜13は、例えば、HfO、HfSiO、LaO、ZrO、ZrSiO、TaO、TiO、BaSrTiO、BaTiO、StTiO、YO、AlO、及び、PbScTaO等を用いて形成する。

【0036】

また、MG電極14もHK酸化膜13と同様に、例えば、PVD(Physical Vapor Deposition)等の異方性の高い堆積方法を用いて形成する。MG電極14は、純金属材料、合金又は金属化合物から形成する。例えば、Ti、Al、Cu、W、HfSi及びTiN等により形成する。また、MG電極14は、例えば、HK酸化膜13上にHfSiやTiN等の半導体装置10に適した仕事関数を有するWF(Work Function)メタル層を形成した後、WFメタル層上に導電性の高いTi、Al、Cu、W等の材料を形成してもよい。

【0037】

HK酸化膜13及びMG電極14を、異方性の高い堆積方法で形成することにより、図3Hに示すように、オフセットスペーサ24が形成されていた部分には、HK酸化膜及びMG電極を形成することなく、空洞部16を形成することができる。

サイドウォール15の開口部の形状は、ダミーゲート電極が形成されていた形状と、同一形状である。このため、異方性の高い堆積方法を用いてHK酸化膜を形成することにより、サイドウォール15の開口部の形状とほぼ同じ形状のHK酸化膜を半導体基体上に形成することができる。

さらに、MG電極14も、PVD(Physical Vapor Deposition)等の異方性の高い堆積方法を用いて形成する。MG電極も異方性の高い堆積方法を用いて形成することにより、開口部の形状とほぼ同じ形状、つまり、ダミーゲート電極と同じ形状に形成することができる。

【0038】

次に、HK酸化膜13及びMG電極14を形成する際に、層間絶縁層18上にもHK酸化膜13の材料及びMG電極14の材料が堆積する。このため、CMP法等を用いて、層間絶縁層18上のHK酸化膜13の材料及びMG電極14の材料を除去する。

そして、層間絶縁層18上にMG電極14を覆うように、さらに層関絶縁層を形成し、Ti,TiN,W等から構成されるコンタクトを形成する。

以上の工程により半導体装置10を製造することができる。

【0039】

[作用]

上述の半導体装置の製造方法によれば、異方性の高い堆積方法を用いてサイドウォール15の開口部からMG電極14及びHK酸化膜13を形成することにより、MG電極14及びHK酸化膜13がダミーゲート電極及びダミーゲート絶縁膜と同じ形状となる。

ダミーゲート電極及びダミーゲート絶縁膜と同じ形状で形成することにより、オフセットスペーサ24が除去された部分に、オフセットスペーサ24と同じ形状の空洞部16が形成される。

オフセットスペーサ24は、上述の図2Aに示す工程において、形成する厚さとエッチング量を調整することにより、任意の形状に制御性よく形成することができる。このため、半導体装置10の空洞部16の形状は、オフセットスペーサ24の形成工程に依存して任意の形状に制御性よく形成される。

この結果、空洞部16の形状を制御性よく任意の形状に形成することができる。

【0040】

また、オフセットスペーサ24の形成位置は、ダミーゲート電極22の高さよりも低くすることが好ましい。ダミーゲート電極22と同じ高さにオフセットスペーサ24を形成すると、サイドウォール15を形成した場合に、サイドウォールとダミーゲート電極22との接触位置が、上部のわずかな部分のみとなる。この場合、サイドウォール15の内壁上部に、半導体基体11面に対して垂直な面が形成されない。

【0041】

ダミーゲート電極22、ダミーゲート絶縁層12及びオフセットスペーサ24を除去した後、サイドウォール15の内壁側に、異方性の高い堆積方法により、HK酸化膜13とMG電極14とを形成する。このとき、サイドウォール15の内壁に半導体基体11面に対して垂直な面が形成されていると、内壁側の空間で、横方法(基体面に平行な方向)への拡散を抑制することができる。特に、サイドウォール15の垂直面が基体面付近まで形成されていることにより、HK酸化膜13及びMG電極14の制御が容易になる。従って、オフセットスペーサ24をダミーゲート電極22よりも低い位置まで形成し、サイドウォール15の垂直面を充分に確保することが好ましい。

【0042】

[変形例1:CMOS]

次に、上述の半導体装置の製造方法の第1実施形態を適用して、第1導電型のMOSトンジスタと第2導電型のMOSトランジスタとを同時に形成する方法ついて説明する。なお、以下の説明では、一例として、第1導電型をP型、第2導電型をN型として説明している。PMOSとNMOSとを同時に形成する場合にも、上述の製造方法において、図3Gに示すダミーゲート絶縁膜21及びオフセットスペーサ24の除去工程までは、同様に行うことができる。このため、以下の説明では、ダミーゲート絶縁膜21及びオフセットスペーサ24の除去工程以降の製造方法について説明する。

【0043】

図4Aに示すように、ダミーゲート電極22、ダミーゲート絶縁膜21、サイドウォール15、及び、オフセットスペーサ24を除去した空洞部16を形成する。これは、上述の第1実施形態と同様の方法により形成することができる。

【0044】

次に、図4Bに示すように、異方性の高い堆積方法によりHK酸化膜13を形成する。HK酸化膜13は、サイドウォール15内の半導体基体11上に、所定の形状で形成される。また、図示しないが、層間絶縁層18上にも同様にもHK酸化膜13が形成される。

そして、全面にNMOS用のWFメタル層26を例えばHfSiにより形成する。

【0045】

図4Cに示すように、NMOS側のみにレジスト層27を形成し、ウェットエッチングにより、PMOSに形成されたNMOS用のWFメタル層26を除去する。

【0046】

図4Dに示すように、NMOS側のレジスト層27を除去した後、全面にPMOS用のWFメタル層28を例えばTiNにより形成する。

このとき、NMOSでは、HK酸化膜13上にNMOS用WFメタル層26が形成され、さらに、NMOS用WFメタル層26上にPMOS用WFメタル層28が形成される。また、PMOSでは、HK酸化膜13上にPMOS用WFメタル層28のみが形成される。

【0047】

次に、図4Eに示すように、WFメタル層26,28上に導電性の高い材料、例えば、Ti、Al、Cu、及び、W等を用いて、サイドウォール15内を埋め込み、上記WFメタル層26,28上に導電体層29を形成する。このとき、空洞部内に導電体が形成されないように導電体の埋め込みを行う。導電体層29とWFメタル層26,28とは、電気的に接続されていればよく、サイドウォール15内を完全に埋めこむ必要ない。

【0048】

上述の工程により、NMOSとPMOSとが混在している場合にも、上述の半導体装置の製造方法を適用することができる。また、NMOSとPMOSとで、ゲート電極にそれぞれ適した仕事関数を有する材料を用いた半導体装置20を製造することができる。

【0049】

[変形例2:ALD(Atomic Layer Deposition)]

次に、上述の半導体装置の製造方法において、HK酸化膜の形成に等方性の堆積方法、例えばALD法やCVD法を適用した場合について説明する。なお、ALD法やCVD法を用いてHK酸化膜を形成する場合にも、上述の製造方法において、図3Gに示すダミーゲート絶縁膜21及びオフセットスペーサ24の除去工程までは、同様に行うことができる。このため、以下の説明では、ダミーゲート絶縁膜21及びオフセットスペーサ24の除去工程以降の製造方法について説明する。

【0050】

図5に、HK酸化膜の形成に等方性の堆積方法を適用した半導体装置30の構成例を示す。図5に示す半導体装置30は、ALD法等を用いることにより、サイドウォール15の内壁、及び、サイドウォール15内の半導体基体11の全面に、HK酸化膜31が形成される。

【0051】

半導体装置30は、例えば、ダミーゲート絶縁膜21及びオフセットスペーサ24を除去した後、ALD法等の等方性の堆積方法を用いて、サイドウォール15内及び層間絶縁層18上にHK酸化膜13を形成する。HK酸化膜13は、例えば、HfO、HfSiO、LaO、ZrO、ZrSiO、TaO、TiO、BaSrTiO、BaTiO、StTiO、YO、AlO、及び、PbScTaO等を用いて形成する。

【0052】

さらに、HK酸化膜13を形成した後、上述の半導体装置の製造方法と同様に、PVD等の異方性の高い堆積方法を用いてMG電極14を形成する。MG電極14の形成は、空洞部16を確保するため、異方性の高い堆積方法を用いる。

【0053】

空洞部16の形状は、HK酸化膜31がサイドウォール15内壁に形成されている分、オフセットスペーサ24が形成されていた形状からの差が発生する。しかし、HK酸化膜31が形成される膜厚分を予め考慮してオフセットスペーサ24を形成することにより、所定の形状の空洞部16を有する半導体装置30を製造することができる。

【0054】

オフセットスペーサ24の形成は、上述のように膜厚とエッチバック量を調整することにより、制御性よく行うことができる。さらに、ALD法のように制御性の高い膜形成方法を用いることにより、空洞部16の形状の制御を容易に行うことができる。

【0055】

〈2.半導体装置の製造方法の第2実施形態〉

次に、半導体装置の製造方法の第2実施形態を説明する。なお、第2実施形態では、上述の第1実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

[半導体装置の構成例]

図6に、第2実施形態の製造方法に係わる半導体装置の構成図を示す。図6に示す半導体装置40は、例えば、シリコン基板等からなる半導体基体11に、活性領域を区画する酸化シリコン等からなる素子分離12が形成されている。そして、半導体基体11上に、高誘電率材料(High−k)からなる酸化膜(HK酸化膜)13を介してメタルゲート(MG)電極14が形成されている。MG電極14は、膜状のWFメタル層14Aと、WFメタル層14Aに接続された導電体層14Bとからなる。そして、HK酸化膜13とWFメタル層14Aの側壁に第1オフセットスペーサ32が形成されている。

【0056】

また、導電体層14Bの側壁から半導体基体11上まで連なるサイドウォール15が形成されている。そして、MG電極14の側壁下部とサイドウォール15との間に空洞部16が形成されている。

【0057】

また、半導体基体11には、図示しないソース・ドレイン、エクステンション領域及びHalo等の不純物領域が形成され、サイドウォール15から露出されている不純物領域(ソース・ドレイン)の表面にシリサイド17が形成されている。さらに、半導体基体11上に、MG電極14及びサイドウォール15を覆って、層間絶縁層18が形成されている。

【0058】

WFメタル層14Aは、HK酸化膜上に膜状に形成され、半導体装置の駆動に適した仕事関数WF(work function)を有する金属材料、例えば、HfSi及びTiN等からなる。導電体層14Bは、例えば、Ti、Al、Cu及びW等からなる。

また、第1オフセットスペーサは、例えば、SiN等の材料を用いて薄膜上に形成される。

【0059】

空洞部16は、サイドウォール15の内側、且つ、MG電極14を構成する導電体層14Bの側壁下部において、半導体基体11上に設けられている。HK酸化膜及びWFメタル層14Aの側壁には、第1オフセットスペーサ32が形成されている。このため、第1オフセットスペーサ32の外周に空洞部16が設けられている。

【0060】

上記のように空洞部16を形成することにより、半導体基体11上でのMG電極14とサイドウォール15との接触が妨げられている。この構造により、半導体基体11とMG電極14との間で生じるフリンジ容量を低減することができる。

【0061】

[半導体装置の製造方法の第2実施形態]

次に、半導体装置の製造方法の第2実施形態として、上述の半導体装置40の製造方法を説明する。

(1)素子分離〜オフセットスペーサ形成

まず、上述の半導体装置の製造方法の第1実施形態と同様に、素子分離12を形成し、ウェル領域及びチャネルを形成するためのイオン注入を行う。さらに、同様に、半導体基体11上に、ダミーゲート絶縁膜21とダミーゲート電極22を形成する。

【0062】

次に、ダミーゲート電極22の側壁に第1オフセットスペーサ32と、第2オフセットスペーサ24を形成する。第2オフセットスペーサ24は、上述の半導体装置の製造方法の第1実施形態におけるオフセットスペーサ24に該当する。

第1オフセットスペーサ32は、例えば、半導体基体11及びダミーゲート電極22を覆って、第1オフセットスペーサ用材料層を2〜4nm程度形成する。そして、異方性エッチングを用いて、形成した第1オフセットスペーサ用材料層をエッチバックすることにより、ダミーゲート電極22の側壁に、薄膜上の第1オフセットスペーサ32を形成する。このとき、第1オフセットスペーサ32は、ダミーゲート電極22の側壁全面を覆うように形成する。

【0063】

第1オフセットスペーサ32と第2オフセットスペーサ24とは、互いにウェットエッチングにおける選択性のある材料を用いる。例えば、第1オフセットスペーサ32をSiNから形成し、第2オフセットスペーサ24をSiO2から形成する。また、第1オフセットスペーサ32は、ダミーゲート電極22のエッチングの際、例えば、ダミーゲート電極22をドライエッチングで除去した後に、形状を維持して残存するような材料及び条件により形成する。

【0064】

次に、半導体基体11、ダミーゲート電極22、及び、第1オフセットスペーサ32を覆って、第1オフセットスペーサ用材料層を4〜8nm程度形成する。そして、異方性エッチングを用いて、形成したオフセットスペーサ用材料層をエッチバックすることにより、第1オフセットスペーサ32の側面に、第2オフセットスペーサ24を形成する。このとき、第2オフセットスペーサ24の高さが、ダミーゲート電極22よりも低くなるようにエッチングを行う。また、第2オフセットスペーサ24を、半導体装置40に形成する空洞部の形状に形成する。

【0065】

次に、第1オフセットスペーサ32及び第2オフセットスペーサ24を形成後、第1実施形態と同様に半導体基体11に、ハロー(Halo)領域及びエクステンション(Extension)領域を形成するためのイオン注入を行う。

以上の工程により、図7Aに示すように、半導体基体11に、素子分離12、ダミーゲート絶縁膜21、ダミーゲート電極22、第1オフセットスペーサ32、及び、第2オフセットスペーサ24を形成する。

【0066】

(2)サイドウォール形成〜層間絶縁層形成

次に、図7Bに示すように、ダミーゲート電極22の側壁に、第1オフセットスペーサ32及び第2オフセットスペーサ24を介してサイドウォール15,25を形成する。そして、図7Cに示すように、サイドウォール15,25をマスクとして、半導体基体11に、ソース・ドレインを形成するためのイオン注入を行う。また、図7Dに示すように、ダミーゲート電極22及びサイドウォール15を覆って、半導体基体11に層間絶縁層18を形成する。続けて、図8Eに示すように、層間絶縁層18の平坦化し、ダミーゲート電極22の上部を露出する。

上記各工程は、オフセットスペーサが、第1オフセットスペーサ32と第2オフセットスペーサ24とから構成されている以外は、上述の第1実施形態と同様の方法で行うことができる。

【0067】

(3)ダミーゲート電極除去

次に、図8Fに示すように、ダミーゲート電極22を、ドライエッチング等を用いて除去する。このとき、ダミーゲート電極22と、ダミーゲート絶縁膜21及び第1オフセットスペーサ32とは、エッチングに選択性のある材料から形成されている。例えば、ダミーゲート電極22をポリシリコンで形成し、第1オフセットスペーサ32をSiN、ダミーゲート絶縁膜21をSiO2で形成する。このため、ダミーゲート電極22のエッチング時に第1オフセットスペーサ32が、サイドウォール15及び第2オフセットスペーサ24の保護膜となる。また、ダミーゲート絶縁膜21が保護膜となり、半導体基体11への損傷を防ぐことができる。

【0068】

(4)ダミーゲート絶縁膜の除去

ダミーゲート電極22を除去した後、図8Gに示すように、フッ酸を用いたウェットエッチングにより、ダミーゲート絶縁膜21を除去する。このとき、第1オフセットスペーサ32が、ダミーゲート電極22とエッチング選択性のある材料で形成されているため残存する。このため、第2オフセットスペーサ24がダミーゲート電極22と同じ材料で形成されている場合にも、第1オフセットスペーサ32が保護膜となり、ダミーゲート絶縁膜21のみを除去し、第2オフセットスペーサ24を残存させることができる。

【0069】

(5)HK酸化膜及びWFメタル層形成

次に、図8Hに示すように、HK酸化膜13とWFメタル層14Aを形成する。サイドウォール15の開口部の内壁全面には、第2オフセットスペーサ24が形成されている。このため、第2オフセットスペーサ24内において、半導体基体11上にHK酸化膜13を形成する。

HK酸化膜13は、第1実施形態と同様に、PVD法等の異方性の高い堆積方法を用いて形成してもよく、また、ALD法やCVD法等の堆積方法を用いてもよい。

【0070】

HK酸化膜13を形成した後、HK酸化膜13上にWFメタル層14Aを形成する。WFメタル層14Aは、例えば、PVD(Physical Vapor Deposition)等の異方性の高い堆積方法を用いて形成し、HK酸化膜13上のみに形成する。

後の工程において第1オフセットスペーサ32を除去する必要があるため、異方性の高い堆積方法でWFメタル層14Aを形成し、第2オフセットスペーサ24内壁への金属材料の堆積を抑制する。

【0071】

なお、ALD法やCVD法等の堆積方法で、HK酸化膜13を形成した場合には、WFメタル層14Aを形成した後、WFメタル層14A上のHK酸化膜をフッ酸等によるウェットエッチングで除去する。このとき、WFメタル層14Aを保護層とすることにより、WFメタル層14Aの下部で半導体基体11上に形成されているHK酸化膜13のみが残存する。

【0072】

(6)オフセットスペーサの除去

図9Iに示すように、第1オフセットスペーサ32を除去する。第1オフセットスペーサ32の除去は、例えば、ホットリン酸を用いたウェットエッチングにより行う。第1オフセットスペーサ32を除去することにより、第2オフセットスペーサ24の内面上部が露出される。また、HK酸化膜13及びWFメタル層14Aの側壁に第1オフセットスペーサ32が部分的に残存する。

【0073】

そして、第1オフセットスペーサ32を除去した後、露出した第2オフセットスペーサ24を、フッ酸を用いたウェットエッチングにより除去する。第2オフセットスペーサ24を除去ことにより、第2オフセットスペーサ24が形成されていた領域が、半導体装置40の空洞部16となる。

このとき、HK酸化膜13及びWFメタル層14Aの側壁に残存している第1オフセットスペーサ32が保護膜となり、HK酸化膜13へのウェットエッチングによる損傷を防ぐことができる。

【0074】

なお、第1オフセットスペーサ32をエッチングした後も、HK酸化膜13及びWFメタル層14Aの側壁に第1オフセットスペーサ32が部分的に残存する。このように、第1オフセットスペーサ32が残存していても、空洞部16の形状に影響がなく、また、半導体装置の特性にもほとんど影響を与えないため、第1オフセットスペーサ32の残存部を改めて除去する必要はない。

【0075】

また、第1オフセットスペーサ32をウェットエッチングで除去する際に、同じ材料で形成されているサイドウォール15の露出面も、エッチングの影響を受ける。このため、第1オフセットスペーサ32を充分に薄く形成し、第1オフセットスペーサ32のエッチングを短時間で行うことにより、サイドウォール15への影響を最小限にすることが好ましい。

【0076】

(7)導電体層形成

次に、図9Kに示すように、WFメタル層14A上に導電性の高い材料、例えば、Ti、Al、Cu、W、及び、これらを含む合金を用いて、サイドウォール15内を埋め込み、上記WFメタル層14A上に導電体層14Bを形成する。このとき、空洞部内に導電体が形成されないように導電体の埋め込みを行う。導電体層14BとWFメタル層14Aとは、電気的に接続されていればよく、サイドウォール15内を完全に埋めこむ必要ない。

このように、WFメタル層14Aと導電体層14BとからMG電極14を形成する。

【0077】

以上の工程により、サイドウォール15内壁に形成された薄膜上の第1オフセットスペーサ32を用いて、HK酸化膜13及びMG電極14が所定に位置に正確に形成された半導体装置40を製造することができる。

【0078】

[作用]

上述の第2実施形態では、ダミーゲート電極22の側壁の全面に、第1オフセットスペーサ32を形成する

第1オフセットスペーサ32を残存させた状態で、HK酸化膜13とWFメタル層14Aを形成する。このため、第1オフセットスペーサ32内に、HK酸化膜13とWFメタル層14Aとが形成される。従って、HK酸化膜13とWFメタル層14Aとを所定の領域に制御性よく形成することができる。そして、HK酸化膜13とWFメタル層14Aを形成後、WFメタル層14Aよりも上方の第1オフセットスペーサ32を除去して、露出した第2オフセットスペーサ24を除去する。そして、第2オフセットスペーサ24を除去したのち、WFメタル層14Aに接続する導電体層14Bを形成することにより、半導体装置40に空洞部16が形成される。

以上の工程によれば、空洞部16が形成された後には、半導体基体11上にHK酸化膜13とWFメタル層14Aが形成されない。また、導電体層14Bは、WFメタル層14Aとの電気的な接続が形成されていればよく、ゲート長全域に精密に形成する必要がない。このため、導電体層14Bの形成による空洞部16の形状変化は考慮しなくてよい。

【0079】

上述の第1実施形態では、異方性の高い堆積方法を用いてHK酸化膜及びMG電極を形成する。異方性の高い堆積方法を用いることにより、空洞部を確保することができる。そして、第2実施形態では、第2オフセットスペーサの内側に第1オフセットスペーサを設ける。このため、ダミーゲート絶縁膜と、第2オフセットスペーサとが同じ材料から形成されている場合にも、ダミーゲート絶縁膜を除去する際に、第1オフセットスペーサが保護膜となり、第2オフセットスペーサが残存する。

【0080】

第2オフセットスペーサの除去による空洞部の形成工程以前に、ダミーゲート絶縁膜の除去と、HK酸化膜の形成が可能となる。このため、空洞部が形成された後に、空洞部の形状を変化させる膜形成等が行われない。従って、半導体装置に形成される空洞部は、第2オフセットスペーサの形状がより正確に保持される。

さらに、第2オフセットスペーサ内のHK酸化膜上に、WFメタル層を形成することにより、WFメタル層の形成領域が、HK酸化膜上に限定される。従って、精密なゲート電極形成が可能となる。

【0081】

なお、上述の第2実施形態では、MG電極をWFメタル層により形成したが、他の金属材料により形成してもよい。例えば、導電体層と同じ材料をHK酸化膜上に形成してもよい。

【0082】

〈3.半導体装置の製造方法の第3実施形態〉

次に、半導体装置の製造方法の第3実施形態を説明する。なお、第3実施形態では、上述の第1実施形態及び第2実施形態と同様の構成には、同じ符号を付して詳細な説明を省略する。

[半導体装置の構成例]

図10に、第3実施形態の製造方法に係わる半導体装置の構成図を示す。図10に示す半導体装置50は、例えば、シリコン基板等からなる半導体基体11に、活性領域を区画する酸化シリコン等からなる素子分離12が形成されている。そして、半導体基体11上に、高誘電率材料(High−k)からなる酸化膜(HK酸化膜)13を介してメタルゲート(MG)電極14が形成されている。MG電極14は、膜状のWFメタル層14Aと、WFメタル層14Aに接続された導電体層14Bとからなる。

また、導電体層14Bの側壁から半導体基体11上まで連なるサイドウォール15が形成されている。そして、MG電極14の側壁下部とサイドウォール15との間に空洞部16が形成されている。

【0083】

また、半導体基体11には、図示しないソース・ドレイン、エクステンション領域及びHalo領域等の不純物領域が形成され、サイドウォール15から露出されている不純物領域(ソース・ドレイン)の表面にシリサイド17が形成されている。さらに、半導体基体11上に、MG電極14及びサイドウォール15を覆って、層間絶縁層18が形成されている。

【0084】

空洞部16は、サイドウォール15の内側、且つ、MG電極14を構成する導電体層14Bの側壁下部において、半導体基体11上に設けられている。HK酸化膜及びWFメタル層14Aの側壁には、第1オフセットスペーサ32が形成されている。このため、第1オフセットスペーサ32の外周に空洞部16が設けられている。

【0085】

上記のように空洞部16を形成することにより、半導体基体11上でのMG電極14とサイドウォール15との接触が妨げられている。この構造により、半導体基体11とMG電極14との間で生じるフリンジ容量を低減することができる。

【0086】

[半導体装置の製造方法の第3実施形態]

次に、半導体装置の製造方法の第3実施形態として、上述の半導体装置50の製造方法を説明する。

(1)素子分離〜ウェル領域及びチャネルのイオン注入

まず、上述の半導体装置の製造方法の第1実施形態と同様に、素子分離12を形成し、ウェル領域及びチャネルを形成するためのイオン注入を行う。

【0087】

(2)HK酸化膜、WFメタル層、及び、ダミーゲート電極の形成

次に、フッ酸を用いて半導体基体11表面のSiO2膜を除去した後、半導体基体11の上の全面に、HK酸化膜13、WFメタル層14A及びダミーゲート電極22からなる積層体を形成する。

HK酸化膜13は、例えば、上述のHK材料をPVD法、ALD法及びCVD法等の堆積方法を用いて、半導体基体11の上の全面に1〜3nm形成する。そして、同様に金属材料を用いて、HK酸化膜13上にWFメタル層14Aを形成する。さらに、WFメタル層14A上に、ポリシリコン等によりダミーゲート電極22を形成する。

【0088】

次に、上述の積層体上に、ハードマスク層23をSiNで形成し、リソグラフィにより所定のゲート電極形状にハードマスク層23のパターンを形成する。そして、このハードマスク層23のパターンを用いてHK酸化膜13、WFメタル層14A及びダミーゲート電極22からなる積層体に異方性エッチングを行う。この工程により、半導体基体11上に、図11Aに示す、HK酸化膜13、WFメタル層14A及びダミーゲート電極22からなるゲート電極状の積層体を形成する。

【0089】

(3)オフセットスペーサの形成

次に、ダミーゲート電極22の側壁にオフセットスペーサ24を形成する。オフセットスペーサ24は上述の第1実施形態と同様の方法により形成することができる。また、オフセットスペーサ24は、HK酸化膜13とウェットエッチングにおける選択性のある材料、例えばSiO2を用いて形成することが好ましい。

【0090】

(4)ハロー領域及びエクステンション領域のイオン注入

次に、オフセットスペーサ24を形成後、第1実施形態と同様に半導体基体11に、ハロー(Halo)領域及びエクステンション(Extension)領域を形成するためのイオン注入を行う。

以上の工程により、図11Aに示すように、半導体基体11に、素子分離12、HK酸化膜13、WFメタル層14A、ダミーゲート電極22、及び、オフセットスペーサ24を形成する。

【0091】

(5)サイドウォール形成〜ダミーゲート電極除去

次に、図11Bに示すように、ダミーゲート電極22の側壁に、オフセットスペーサ24を介してサイドウォール15,25を形成する。そして、図11Cに示すように、サイドウォール15,25をマスクとして、半導体基体11に、ソース・ドレインを形成するためのイオン注入を行う。また、図11Dに示すように、ダミーゲート電極22及びサイドウォール15を覆って、半導体基体11に層間絶縁層18を形成する。続けて、図12Eに示すように、層間絶縁層18を平坦化し、ダミーゲート電極22上部を露出する。

そして、図12Fに示すように、ダミーゲート電極22を、ドライエッチング等を用いて除去する。このとき、WFメタル層14Aがマスクとなり、HK酸化膜13へのエッチングによる損傷を防ぐことができる。

【0092】

上記各工程は、ダミーゲート絶縁膜に換えてHK酸化膜13が形成され、さらに、ダミーゲート電極22の下部にWFメタル層14Aが形成されている以外は、上述の第1実施形態と同様の方法で行うことができる。

【0093】

(6)オフセットスペーサの除去

次に、図12Gに示すように、フッ酸を用いたウェットエッチングにより、オフセットスペーサ24を除去する。このとき、WFメタル層14Aがマスクとなり、HK酸化膜13へのエッチングによる損傷を防ぐことができる。

オフセットスペーサ24を除去することにより、サイドウォール15の内壁側下部に、凹部が形成される。凹部の形状は、形成されていたオフセットスペーサ24の形状に依存する。第2オフセットスペーサ24を除去することにより、第2オフセットスペーサ24が形成されていた領域、つまり上記凹部が半導体装置50の空洞部16となる。

【0094】

(7)導電体層形成

次に、図12Hに示すように、WFメタル層14A上に導電性の高い材料、例えば、Ti、Al、Cu、W、及び、これらを含む合金を用いて、サイドウォール15内を埋め込み、上記WFメタル層14A上に導電体層14Bを形成する。このとき、空洞部内に導電体が形成されないように埋め込みを行う。導電体層14BとWFメタル層14Aとは、電気的に接続されていればよいため、サイドウォール15内を完全に導電体で埋めこむ必要ない。

このように、WFメタル層14Aと導電体層14BとからMG電極14を形成する。

【0095】

以上の工程により、HK酸化膜13、及び、MG電極14となるWFメタル層14Aを、ダミーゲート電極22よりも前に形成する方法により、半導体装置50を製造することができる。

【0096】

サイドウォール15内壁に形成された薄膜上の第1オフセットスペーサ32を用いて、HK酸化膜13及びMG電極14が、所定の位置に正確に形成された半導体装置40を製造することができる。この製造方法によれば、予めゲート電極の形状にHK酸化膜とWFメタル層を形成することにより、第1実施形態のようにサイドウォール開口部から異方性の高い堆積方法によるゲート絶縁膜及びゲート電極の形成が不要となる。このため、空洞部形成後に、空洞部と隣接する領域にHK酸化膜及びゲート電極を形成しない。従って、より適正なHK酸化膜、ゲート電極、及び、空洞部を形成することができる。

【0097】

なお、本発明は上述の実施形態例において説明した構成に限定されるものではなく、その他本発明構成を逸脱しない範囲において種々の変形、変更が可能である。

【符号の説明】

【0098】

10,20,30,40,50 半導体装置、11 半導体基体、12 素子分離、13,31 HK酸化膜、14 MG電極、14A,26,28 WFメタル層、14B,29 導電体層、15,25 サイドウォール、16 空洞部、17 シリサイド、18 層間絶縁層、21 ダミーゲート絶縁膜、22 ダミーゲート電極、23 ハードマスク層、24 オフセットスペーサ(第2オフセットスペーサ)、27 レジスト層、32 第1オフセットスペーサ

【特許請求の範囲】

【請求項1】

半導体基体上にダミーゲート絶縁膜及びダミーゲート電極を形成する工程と、

前記ダミーゲート電極上にオフセットスペーサ材料層を形成し、前記オフセットスペーサ材料層に異方性エッチングを行い、前記ダミーゲート電極の側壁下部にオフセットスペーサを形成する工程と、

前記オフセットスペーサ上を覆って、前記ダミーゲート電極の側壁にサイドウォールを形成する工程と、

前記サイドウォールを埋め込み、かつ前記ダミーゲート電極の上面を露出させる層間絶縁層を形成する工程と、

前記ダミーゲート電極を除去する工程と、

前記ダミーゲート絶縁膜を除去する工程と、

前記オフセットスペーサを除去する工程と、

前記半導体基体上に高誘電率材料からなるゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、異方性の高い堆積方法を用いてメタルゲート電極を形成する工程と、を有する

半導体装置の製造方法。

【請求項2】

前記オフセットスペーサを形成する工程が、ダミーゲート電極の側壁の全面に第1オフセットスペーサを形成する工程と、前記第1オフセットスペーサの側壁下部に第2オフセットスペーサを形成する工程と、からなる請求項1に記載の半導体装置の製造方法。

【請求項3】

前記ダミーゲート電極及び前記ダミーゲート絶縁膜を除去する工程の後、前記第1オフセットスペーサの内側に、前記ゲート絶縁膜を形成する工程、及び、前記第2オフセットスペーサの上端よりも低い位置に前記メタルゲート電極を形成する工程、並びに、前記メタルゲート電極の上方で露出する前記第1オフセットスペーサと、前記第2オフセットスペーサを除去する工程とを行う請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1オフセットスペーサと前記第2オフセットスペーサとをウェットエッチングに選択性のある材料を用いて形成する請求項3に記載の半導体装置の製造方法。

【請求項5】

前記メタルゲート電極を形成する工程は、前記ゲート絶縁膜上にワークファンクションメタル層を形成する工程と、前記ワークファンクションメタル層に接続する導電体層を形成する工程とからなる請求項1に記載の半導体装置の製造方法。

【請求項6】

前記メタルゲート電極を形成する工程は、第1導電型のMOSトランジスタに、第1導電型MOSトランジスタ用のワークファンクションメタル層を形成する工程と、第2導電型のMOSトランジスタに、第2導電型MOSトランジスタ用のワークファンクションメタル層を形成する工程と、前記第1導電型のMOSトランジスタ用のワークファンクションメタル層、及び、前記第2導電型のMOSトランジスタ用のワークファンクションメタル層に接続する前記導電体層を形成する工程とからなる請求項5に記載の半導体装置の製造方法。

【請求項7】

ウェットエッチング法を用いて、前記ダミーゲート絶縁膜と前記オフセットスペーサとを同時に除去する請求項1に記載の半導体装置の製造方法。

【請求項8】

前記異方性の高い堆積方法として、PVDを用いる請求項1に記載の半導体装置の製造方法。

【請求項9】

前記半導体基体上に高誘電率材料からなるゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に金属材料層からなるゲート電極を形成する工程と、

前記金属材料層上にダミーゲート電極を形成する工程と、

前記ダミーゲート電極上にオフセットスペーサ材料層を形成し、前記オフセットスペーサ材料層に異方性エッチングを行い、前記ゲート電極及び前記ダミーゲート電極の側壁に、オフセットスペーサを形成する工程と、

前記オフセットスペーサ上を覆って、前記ダミーゲート電極の側壁にサイドウォールを形成する工程と、

前記サイドウォールを埋め込み、かつ前記ダミーゲート電極の上面を露出させる層間絶縁層を形成する工程と、

前記ダミーゲート電極、及び、前記オフセットスペーサを除去する工程と、

前記ゲート電極上に、導電体層を形成する工程と、を有する

半導体装置の製造方法。

【請求項10】

前記ゲート電極を形成する工程が前記ゲート絶縁膜上にワークファンクションメタル層を形成するからなり、前記ワークファンクションメタル層上に前記導電体層を形成する請求項9に記載の半導体装置の製造方法。

【請求項1】

半導体基体上にダミーゲート絶縁膜及びダミーゲート電極を形成する工程と、

前記ダミーゲート電極上にオフセットスペーサ材料層を形成し、前記オフセットスペーサ材料層に異方性エッチングを行い、前記ダミーゲート電極の側壁下部にオフセットスペーサを形成する工程と、

前記オフセットスペーサ上を覆って、前記ダミーゲート電極の側壁にサイドウォールを形成する工程と、

前記サイドウォールを埋め込み、かつ前記ダミーゲート電極の上面を露出させる層間絶縁層を形成する工程と、

前記ダミーゲート電極を除去する工程と、

前記ダミーゲート絶縁膜を除去する工程と、

前記オフセットスペーサを除去する工程と、

前記半導体基体上に高誘電率材料からなるゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、異方性の高い堆積方法を用いてメタルゲート電極を形成する工程と、を有する

半導体装置の製造方法。

【請求項2】

前記オフセットスペーサを形成する工程が、ダミーゲート電極の側壁の全面に第1オフセットスペーサを形成する工程と、前記第1オフセットスペーサの側壁下部に第2オフセットスペーサを形成する工程と、からなる請求項1に記載の半導体装置の製造方法。

【請求項3】

前記ダミーゲート電極及び前記ダミーゲート絶縁膜を除去する工程の後、前記第1オフセットスペーサの内側に、前記ゲート絶縁膜を形成する工程、及び、前記第2オフセットスペーサの上端よりも低い位置に前記メタルゲート電極を形成する工程、並びに、前記メタルゲート電極の上方で露出する前記第1オフセットスペーサと、前記第2オフセットスペーサを除去する工程とを行う請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第1オフセットスペーサと前記第2オフセットスペーサとをウェットエッチングに選択性のある材料を用いて形成する請求項3に記載の半導体装置の製造方法。

【請求項5】

前記メタルゲート電極を形成する工程は、前記ゲート絶縁膜上にワークファンクションメタル層を形成する工程と、前記ワークファンクションメタル層に接続する導電体層を形成する工程とからなる請求項1に記載の半導体装置の製造方法。

【請求項6】

前記メタルゲート電極を形成する工程は、第1導電型のMOSトランジスタに、第1導電型MOSトランジスタ用のワークファンクションメタル層を形成する工程と、第2導電型のMOSトランジスタに、第2導電型MOSトランジスタ用のワークファンクションメタル層を形成する工程と、前記第1導電型のMOSトランジスタ用のワークファンクションメタル層、及び、前記第2導電型のMOSトランジスタ用のワークファンクションメタル層に接続する前記導電体層を形成する工程とからなる請求項5に記載の半導体装置の製造方法。

【請求項7】

ウェットエッチング法を用いて、前記ダミーゲート絶縁膜と前記オフセットスペーサとを同時に除去する請求項1に記載の半導体装置の製造方法。

【請求項8】

前記異方性の高い堆積方法として、PVDを用いる請求項1に記載の半導体装置の製造方法。

【請求項9】

前記半導体基体上に高誘電率材料からなるゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に金属材料層からなるゲート電極を形成する工程と、

前記金属材料層上にダミーゲート電極を形成する工程と、

前記ダミーゲート電極上にオフセットスペーサ材料層を形成し、前記オフセットスペーサ材料層に異方性エッチングを行い、前記ゲート電極及び前記ダミーゲート電極の側壁に、オフセットスペーサを形成する工程と、

前記オフセットスペーサ上を覆って、前記ダミーゲート電極の側壁にサイドウォールを形成する工程と、

前記サイドウォールを埋め込み、かつ前記ダミーゲート電極の上面を露出させる層間絶縁層を形成する工程と、

前記ダミーゲート電極、及び、前記オフセットスペーサを除去する工程と、

前記ゲート電極上に、導電体層を形成する工程と、を有する

半導体装置の製造方法。

【請求項10】

前記ゲート電極を形成する工程が前記ゲート絶縁膜上にワークファンクションメタル層を形成するからなり、前記ワークファンクションメタル層上に前記導電体層を形成する請求項9に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2012−146891(P2012−146891A)

【公開日】平成24年8月2日(2012.8.2)

【国際特許分類】

【出願番号】特願2011−5523(P2011−5523)

【出願日】平成23年1月14日(2011.1.14)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成24年8月2日(2012.8.2)

【国際特許分類】

【出願日】平成23年1月14日(2011.1.14)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]