半導体装置の製造方法

【課題】めっき膜厚の制御を精度よく行う。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の凹部が形成された絶縁膜において、めっき処理により導電性膜を形成する際の半導体装置の製造方法およびめっき処理装置に関する。

【背景技術】

【0002】

銅配線を用いる半導体装置において、設計ルールの縮小に伴う配線パターン微細化が進むにつれ、銅めっきプロセスにおけるビアやトレンチへの埋設性能の向上が要求されている。

【0003】

特許文献1(米国特許第6319831号明細書)および特許文献2(米国特許第6140241号明細書)には、低い電流密度で第1のめっき処理を行い、その後に高い電流密度で第2のめっき処理を行う手順が記載されている。

【0004】

特許文献3(特開2001−123298号公報)には、被めっき対象物と同じ材料からなる電極を用い、電極電位と電流密度の関係式を予め求めておき、一方、めっき浴中にて被めっき対象物を任意の電位または電流値で分極させ、そのときの電流値および電位値を求め、上記関係式と前記電流値および電位値から、被めっき対象部分の面積を算出し、この算出した面積に基づいて、所定の膜厚のめっきを行うことの電流値で電解めっきを行う技術が記載されている。具体的には、基板に感光性のめっきレジストを用いてフォトリソグラフ法により配線パターンを形成し、感光性のめっきレジストにより保護されていない露出部分である被めっき対象となる電極の面積を、当該基板を分極させて電流値を測定する。次いで、電流値に基づき、基板の被めっき対象部の面積を算出する。この面積に基づき、めっき処理の電流値を決定する。

【0005】

特許文献4(特開2005−264271号公報)には、複数の凹部が形成された層における第1の基準幅以下の幅を有する微細凹部が当該層に占める割合を取得する工程と、その割合に応じて、導電性材料で凹部を埋め込む際の積算電流量を決定する工程と、その積算電流量に基づき、電解めっき法により、導電性パターンを形成する工程とを含む半導体装置の製造方法が記載されている。これにより、適切な膜厚の電解めっき膜を形成することができる。

【0006】

特許文献5(特開2006−60011号公報)には、絶縁膜表面と開口部とに形成されたシード膜を電極として第1の電流密度となる電流を流し、開口部に導電性材料をめっき法により堆積させる第1のめっき工程と、前記第1のめっき工程後、第1の電流密度より小さい電流密度となる電流を流し、絶縁膜表面上に導電性材料をめっき法により堆積させる第2のめっき工程と、第2のめっき工程後にアニール処理するアニール工程とを含む半導体装置の製造方法が記載されている。

【0007】

特許文献6(特開2005−39142号公報)には、半導体基板上の絶縁膜に形成された、配線用溝およびビア孔のうち少なくともいずれか一方に導電層を埋め込むための電解めっき法は、導電層の材料を含んだめっき液の単位面積あたりに流れる電流値である電流密度とめっき時間との積である積算電流密度が所定の値となる条件でめっき処理を行う第1のステップと、第1のステップよりも電流密度が小さい条件でめっき処理を行う第2のステップとを有する半導体装置の製造方法が記載されている。これにより、電解めっき法により、配線用溝やビア孔に形成された導電層の埋設性が向上し、かつボトムアップ性がウェハ面内でより均一となる、と記載されている。

【0008】

特許文献7(特開2004−270028号公報)には、ダマシン法銅めっきにおいて、めっきを成長させる処理の間に、めっきを成長させる方向とは逆の方向にのみ電流を流すステップを含む方法が記載されている。これにより、配線の密なところにめっきの盛り上がりが生じて、CMP研磨時間の増大によるコストアップ等が生じるのを防ぐことができる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】米国特許第6319831号明細書

【特許文献2】米国特許第6140241号明細書

【特許文献3】特開2001−123298号公報

【特許文献4】特開2005−264271号公報

【特許文献5】特開2006−60011号公報

【特許文献6】特開2005−39142号公報

【特許文献7】特開2004−270028号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

ところで、めっき処理装置においては、予め、めっき処理対象の半導体装置に印加する所定の基準電流密度およびめっき処理時間がレシピとして設定されている。一方、めっき処理対象の半導体装置は、設計に応じて様々な配線パターンを有する。微細パターンを多く含む半導体装置では、微細パターンをあまり含まない半導体装置に比べてめっき時間が長く必要になる。そのため、設計の異なる種々の半導体装置に同じ基準電流密度で同じ時間だけめっき処理を行おうとした場合に、微細パターンを多く含む半導体装置を基準にすると、微細パターンをあまり含まない半導体装置においてはめっき成膜が過剰に行われるという問題が生じる。めっき成膜が過剰に行われると、めっき材料が無駄に使われ無駄なコストがかかるとともに、その後のCMP等の処理において時間がかかり、スループットが低下するという問題が生じる。一方、微細パターンをあまり含まない半導体装置を基準にすると、微細パターンを多く含む半導体装置において、めっき成膜が充分に行えないという問題が生じる。とくに微細な凹部でのめっき成膜が充分に行えず、凹部中に空孔等が形成されてしまう。しかし、従来、このような問題が解決されていなかった。

【0011】

本発明者らは、上記のような現象を種々検討した結果、めっき処理により半導体装置の凹部内を導電性材料で埋め込む場合、配線パターンの密度によって凹部の側壁の面積が大きく異なることにより、めっき処理の実効的な表面積が大きく異なることが、上記のような問題が生じる原因であることを見出した。

【0012】

しかし、従来、このような問題が解決されていなかった。たとえば、特許文献3においては、被めっき対象となる電極の面積に基づきめっき処理の電流値を決定しているが、めっき処理により凹部内を導電性材料で埋め込む場合の特性が考慮されていない。すなわち、凹部の側壁の面積が考慮されていないため、精度のよい補正ができていない。また、特許文献4に記載の技術では、微細凹部が層に占める割合に応じて積算電流量が決定されているが、めっき処理の実効的な表面積が考慮されていないため、精度のよい補正ができていない。

【課題を解決するための手段】

【0013】

本発明によれば、

基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含み、

前記めっき工程は、前記複数の凹部のうち所定幅以下の微細な凹部が前記導電性材料で埋め込まれる際に、所定の第1の基準電流密度を前記基板全面における各前記複数の凹部の側壁の面積を含む第1の表面積S1と各前記複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度を用いてめっき処理を行う工程を含む半導体装置の製造方法が提供される。めっき工程は、前記凹部内にシード膜を形成する工程を含むことができ、第1の電流密度を用いてめっき処理を行う工程は、シード膜を形成する工程の後に行うことができる。

【0014】

本発明によれば、

基板上に形成された絶縁膜に設けられた複数の凹部を含む半導体装置の前記凹部をめっき処理により導電性材料で埋め込むめっき処理を行うめっき処理装置であって、

めっき対象の前記半導体装置に印加する第1の基準電流密度を記憶するデータ記憶部と、

前記めっき対象の前記半導体装置の前記基板全面における各前記複数の凹部の側壁の面積を含む第1の表面積S1と各前記複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2を取得し、当該表面積比Srに基づき、前記第1の基準電流密度を補正して第1の電流密度を算出する演算部と、

前記演算部で算出された前記第1の電流密度を用いて前記めっき対象の前記半導体装置へめっき処理を行うめっき処理部と、

を含むめっき処理装置が提供される。

【0015】

ここで、第1の表面積S1は、基板上の複数の凹部それぞれの周囲長の和に凹部深さを乗じた値と基板全面の表面積(第2の表面積S2)との和とすることができる。

【0016】

本発明の半導体装置の製造方法によれば、所定幅以下の微細な凹部が前記導電性材料で埋め込まれる際に、凹部の側壁の面積を考慮して電流密度が補正される。そのため、半導体装置において形成される凹部のパターンにかかわらず、電流密度を略一定にすることができる。これにより、めっき処理時のボトムアップ性を良好にすることができ、微細な凹部においても、めっき膜を制御性よく形成することができる。また、電流密度を略一定にすることができるため、成膜されるめっき膜のたとえば粒径や配向等の性質も一定にすることができ、膜特性を良好にすることができる。

【0017】

なお、微細な凹部が埋め込まれるまでのめっき処理の大部分をこのように補正した電流密度を用いて行うことにより、上記の効果が得られる。すなわち、めっき処理の最初や途中の段階の短い時間、このように補正した電流密度を用いることなくめっき処理を行うことを排除するものではない。さらに、微細な凹部を埋め込んだ後は、このような補正を行うことなく、より大きい電流密度を用いてめっき処理を行うこともできる。これにより、スループットを高めることができる。

【発明の効果】

【0018】

本発明によれば、めっき膜厚の制御を精度よく行うことができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態における半導体装置の製造手順を示す工程断面図である。

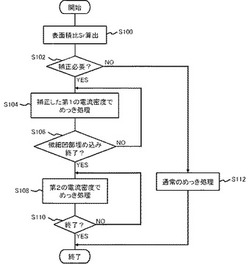

【図2】本発明の実施の形態におけるめっき処理手順を示すフローチャートである。

【図3】半導体装置を模式的に示す図である。

【図4】複数のグループと、各グループにおける表面積比Srの範囲、および用いる電流密度との関係を示す図である。

【図5】本発明の実施の形態における表面積比Srの算出手順を説明する模式図である。

【図6】本発明の実施の形態におけるめっき処理装置の構成を示すブロック図である。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0021】

(第1の実施の形態)

図1は、本実施の形態における半導体装置100の製造手順を示す工程断面図である。本実施の形態において、層間絶縁膜106に配線を形成する工程を説明する。本実施の形態において、ダマシン法により銅配線を形成する手順を説明する。

【0022】

半導体装置100は、トランジスタ等が形成された半導体基板(基板)102と、半導体基板102上に形成された層間絶縁膜104と、その上に形成された層間絶縁膜106とを含む。層間絶縁膜104および層間絶縁膜106中には、配線やビアが形成されている。

【0023】

このように構成された半導体装置100において、まず、層間絶縁膜106に配線溝を形成する。ここで、図示したように、層間絶縁膜106には、第1の配線溝108、第2の配線溝110、第3の配線溝112、第4の配線溝114、第5の配線溝116、第6の配線溝118、および第7の配線溝120が形成される。

【0024】

第1の配線溝108は配線幅D1、第5の配線溝116は配線幅D2、第6の配線溝118は配線幅D3、第7の配線溝120は配線幅D4を有する。第5の配線溝116の配線幅D2、第6の配線溝118の配線幅D3は略等しく、たとえば0.3μmとする。第1の配線溝108の配線幅D1および第7の配線溝120の配線幅D4は、配線幅D2および配線幅D3よりも幅広である。また、第2の配線溝110、第3の配線溝112、および第4の配線溝114は、配線幅D2および配線幅D3よりも幅狭である。

【0025】

このような配線溝(凹部)を配線材料で埋め込む手順は、以下のようになる。まず、層間絶縁膜106の凹部内にバリアメタル膜を形成する。バリアメタル膜は、たとえばTaN/Ta等、通常の銅配線のバリアメタル膜として用いられるものとすることができる。つづいて、バリア膜上にめっきのシード膜を形成する。ここで、シード膜は、CVD法等により形成された銅膜等とすることができる。

【0026】

その後、めっき処理を行う。本実施の形態において、めっき処理が通常の手順と異なる。本実施の形態において、めっき液は、通常の銅配線形成時のめっき膜を形成するのに用いるものと同様とすることができる。めっき液は、たとえば、硫酸、銅、および塩素を含むことができる。また、めっき液は、サプレッサー、アクセラレーター(キャリア)、レベラー等の添加剤を含むことができる。本実施の形態におけるめっき処理は、ボトムアップ堆積される。

【0027】

図2は、本実施の形態におけるめっき処理手順を示すフローチャートである。

本実施の形態において、所定の基準電流密度およびめっき処理時間が予め設定されている。なお、本実施の形態において、基準電流密度として、第1の基準電流密度と第1の基準電流密度よりも大きい第2の基準電流密度が設定されている。めっき処理は、2ステップで行われる。配線パターンにおける微細な凹部を埋め込むまでは、第1の基準電流密度に基づくめっき処理が行われ、その後は、第2の基準電流密度に基づくめっき処理が行われる。所定の基準電流密度とは、後述する表面積比Sr=1のときに半導体装置100に印加される実効電流密度のことである。

【0028】

本実施の形態において、第1の基準電流密度は、後述する表面積比Sr=1のときに半導体装置100に印加される実効電流密度が2mA/cm2以上6.5mA/cm2以下、より好ましくは3.5mA/cm2以上5mA/cm2以下となるように設定する。これにより、埋設不良やめっき焼け不良が起こらない領域でめっき処理を行うことができる。

【0029】

このような状態で、まず、半導体基板(ウェハ)全面における、各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2を算出する(S100)。上記の基準電流密度は、第2の表面積S2を基準として設定される。ここで、半導体基板が直径300mm(半径14.8cm)のシリコンウェハであれば、S2は688cm2になる。

【0030】

図3を参照して、表面積比Srの算出手順を説明する。図3は、半導体装置100を模式的に示す図である。図中、白抜き部分は、凹部が形成された箇所とすることができる。まず、レチクル上のパターンに基づき、半導体基板102(ウェハ)全体に形成された複数の凹部の周囲長lを算出する。たとえば、ある凹部Aの周囲長は(a+b+c+d)である。また、他の凹部Bの周囲長は(e+f+g+h)である。このように、半導体基板102上に形成された凹部すべての周囲長l=(a+b+c+d+e+f+g+h・・)を算出する。つづいて、周囲長lに凹部の深さmを乗じて側壁面積(l×m)を算出する。このようにして算出した側壁面積をウェハ面積S2に加えることにより、めっき処理をする表面全体の実面積S1(=l×m+S2)を算出する。表面積比Srは、実面積S1を基板の表面積S2で除すことにより算出される。

【0031】

図2に戻り、表面積比Srの値に基づき、補正が必要か否かを判断する(S102)。本実施の形態において、表面積比Srが所定範囲内か否かを判断し、表面積比Srが所定範囲内の場合に、補正が必要と判断する。ここで、所定の範囲は、たとえば、1.4以上とすることができる。これにより、表面積比Srがあまり大きくない場合には、補正処理を行うことなく、スムーズにめっき処理を行うことができるとともに、表面積比Srがある程度大きい場合に、補正処理を行うことにより、ボトムアップ性を良好にすることができる。

【0032】

すなわち、半導体基板102上に微細な凹部が多数形成されている場合は、側壁面積が大きくなり、表面積比Srの値が大きくなる。本実施の形態において、表面積比Srが大きく、凹部の側壁面積の影響が無視できない時に、表面積比Srに基づき第1の電流密度を補正して第1のめっき処理を行う。ボトムアップ堆積されるめっき処理の場合、凹部の側壁の面積の大小により、実効電流密度が異なってくる。本実施の形態において、表面積比Srに応じて適宜電流密度が補正されるので、様々なパターン密度の半導体装置の膜厚の制御を精度よく行うことができる。

【0033】

補正が必要な場合(S102のYES)、所定の第1の基準電流密度を表面積比Srに基づいて補正した第1の電流密度を用いてめっき処理を行う(S104)。第1の電流密度は、表面積比Srが大きいほど大きくなるように設定される。本実施の形態において、第1の電流密度は、側壁面積を考慮しない第1の基準電流密度(Sr=1)に対して、表面積比Srを乗じることによって算出される。上述したように、本実施の形態において、第1の基準電流密度は、Sr=1のときに、実効電流密度がたとえば2mA/cm2以上6.5mA/cm2以下、より好ましくは3.5mA/cm2以上5mA/cm2以下の範囲内になるように設定される。このような第1の基準電流値を表面積比Srに基づいて補正した場合、半導体装置100の配線パターンに関わらず、実効電流密度を、たとえば2mA/cm2以上6.5mA/cm2以下、より好ましくは3.5mA/cm2以上5mA/cm2以下の範囲内にすることができる。これにより、凹部を良好に埋設することができるとともに、めっき焼けが生じないようにすることができる。

【0034】

以下、このめっき処理を第1のめっき処理という。第1のめっき処理は、層間絶縁膜106上に形成された複数の凹部のうち所定幅以下の微細な凹部(以下、単に微細凹部という。)が導電性材料で埋め込まれるまで行う。本実施の形態において、所定幅は、たとえば0.3μmとすることができる。このような微細凹部において、表面積比Srを考慮して第1の基準電流密度を補正することにより、ボトムアップ性を良好にすることができる。

【0035】

なお、微細凹部への導電性材料による埋め込みが終了するまでの時間を予め設定しておき、その時間が経過したか否かに基づき、ステップS106の判断を行うことができる。この時間は、たとえば以下のようにして算出することができる。まず、複数のサンプルを準備する。つづいて、これらのサンプルについて、同様の処理条件で、いくつかの時間間隔でめっき処理を行なう。その後、複数のサンプルをへき開し、微細凹部が埋め込まれているサンプルを検出する。そのサンプルに施しためっき処理時間が、微細凹部への導電性材料による埋め込みが終了するまでの時間となる。また、単位時間あたりの成膜量が把握できれば、凹部の幅に基づき、微細凹部への導電性材料による埋め込みが終了するまでの時間を算出することもできる。

【0036】

微細凹部の埋め込みが終了すると(S106のYES)、第1のめっき処理を終了する。この工程を図1(b)に示す。第1のめっき処理により、第5の配線溝116および第6の配線溝118ならびにこれらよりも微細な微細凹部が第1のめっき膜130により埋め込まれる。

【0037】

図2に戻り、第2の電流密度を用いてめっき処理を行う(S108)。第2の電流密度は、表面積比Srに基づく補正を行わないものとすることができる。本実施の形態において、第2の電流密度としては、第2の基準電流密度を用いることができる。第2の電流密度は、第1の基準電流密度に比べて、大きい値とすることができる。以下、このめっき処理を第2のめっき処理という。第2の電流密度は、たとえば、28mA/cm2以上57mA/cm2以下(20−40A/wfで換算)とすることができる。より好ましくは、第2の電流密度は、42mA/cm2以上57mA/cm2以下(30−40A/wfで換算)とすることができる。これにより、生産性を良好にすることができる。第2の電流密度でのめっき処理が終了すると(S110のYES)、めっき処理を終了する。この工程を図1(c)に示す。第2の電流密度でのめっき処理により、第5の配線溝116および第6の配線溝118よりも幅広な凹部が第2のめっき膜132により埋め込まれる。

【0038】

図2に戻り、ステップS102において、補正が必要でない場合(S102のNO)、第1の基準電流密度を用いた通常のめっき処理を行い(S112)、めっき処理を終了する。

【0039】

なお、第1のめっき処理と第2のめっき処理の処理時間は、予め算出しておくことができる。第1のめっき処理の処理時間は、上述した微細凹部への導電性材料による埋め込みが終了するまでの時間とすることができる。たとえば、第1のめっき処理は50秒〜80秒程度、第2のめっき処理は20秒〜50秒程度とすることができる。これらの処理時間は一例であり、所望の膜厚を得るための適切な値に設定することができる。

【0040】

以上のめっき処理の終了後、CMPにより、配線溝外部に露出した第2のめっき膜132を除去して平坦化する。この後、さらに層間絶縁膜形成、凹部形成、金属膜形成を繰り返すことにより、多層配線構造が得られる。

【0041】

なお、第1のめっき処理と第2のめっき処理との間(図2のステップS106とステップS108との間)に、めっき成膜を行う際とは逆方向に電流をかける処理を行うことができる。この手順は、特許文献7に記載されたのと同様にして行うことができる。このような処理により、成膜された第1のめっき膜130の一部を溶かすことができる。これにより、めっき膜上の添加剤の濃淡をキャンセルすることができ、めっき膜の面内均一性を向上することができる。

【0042】

以上のように、本実施の形態における半導体装置の製造手順によれば、微細凹部が埋め込まれるまでは、表面積比Srに基づき補正した第1の電流密度によりめっき処理が行われる。そのため、各凹部内において、実効電流密度が等しい条件で、めっき処理を行うことができる。これにより、めっき成膜とボトムアップを効率よく行うことができる。また、微細凹部が埋め込まれた後は、第2のめっき処理により、効率よく成膜を行うことができる。これにより、めっき処理装置のスループットを向上することができる。また、ボトムアップを良好に行うことができるため、めっき処理後のCMP工程での処理時間減少によるスループット向上を行うこともできる。

【0043】

以上の手順により、微細パターンが含まれる半導体装置と大パターンが形成された半導体装置との間でのめっき膜厚差を減少することができる。また、面内均一性も向上する。

なお、実際には配線パターン密度はレチクルにより決まっている。このため図2に示した手順およびめっき処理の適切な時間をあるレチクルにつきめっき装置に一旦設定すれば、同じレチクルを使用して形成された凹部のめっき処理はこの設定に基づいて行うことができる。

【0044】

(第2の実施の形態)

本実施の形態において、第1のめっき処理における第1の電流密度の補正方法が、第1の実施の形態で説明したのと異なる。

【0045】

本実施の形態において、表面積比Srを所定範囲毎にグループ化し、各グループに対して、補正値を設定する。すなわち、グループ毎に第1の電流密度を設定する。そして、第1の電流密度でめっき処理を行う際に、当該半導体装置の表面積比Srが含まれるグループに設定された第1の電流密度でめっき処理を行う。このようにすることにより、めっき処理時のレシピを簡略化することができるとともに、ボトムアップを良好に行うことができる。

【0046】

図4は、複数のグループと、各グループにおける表面積比Srの範囲、および用いる電流密度との関係を示す図である。

【0047】

たとえば、表面積比Srが1.0≦Sr<1.2の範囲にある場合、グループAに分類される。同様に、表面積比Srが1.2≦Sr<1.4の範囲にある場合グループBというように、たとえばSrの大きさ0.2ごとにグループ分けを行う。

【0048】

めっき装置の設定電流値は、各グループに対して、実効電流密度が所定範囲内となるように設定される。すなわち、各グループの第1の電流密度は、当該第1の電流密度を表面積比Srで除して得られる実効電流密度が所定範囲内となるように設定される。ここで、所定範囲は、たとえば2mA/cm2以上6.5mA/cm2以下、より好ましくは3.5mA/cm2以上5mA/cm2以下とすることができる。このような範囲とすることにより、凹部を良好に埋設することができるとともに、めっき焼けが生じないようにすることができる。

【0049】

たとえば、グループAの表面積比が1.0≦Sr<1.2の範囲にあるものは、めっき装置の電流値を3Aで処理すると定める。このようにすると、第1の電流密度は、4.4A/cm2となる。この場合、表面積比Srを考慮した実効電流密度は、表面積比Sr=1の場合には4.4mA/cm2、表面積比Sr=1.2の場合には3.6mA/cm2となる。このように、同じグループに属する場合でも表面積比Srの値によって実効電流密度が異なるが、グループ分けを適切に行うことにより、好ましい範囲におさめることができる。

【0050】

図4に示したように、表面積比Srが大きいグループほど、めっき装置の電流値を高く定める必要がある。このような表面積比Srに基づく電流密度の補正は、表面積比Srが大きい場合に、とくに有効に用いることができる。たとえば、表面積比Srが2.0の場合、グループFに属する。この場合、めっき装置の電流値を5.5Aで処理すると定める。このようにすると、第1の電流密度は、8.0mA/cm2となる。この場合、表面積比Srを考慮した実効電流密度は、4.0mA/cm2となる。

【0051】

以上の第1のめっき処理を行った後、第1の実施の形態で説明したのと同様の第2のめっき処理を行う。

【0052】

本実施の形態においても、第1の実施の形態と同様の効果が得られる。また、処理やレシピを簡略化することができる。

【0053】

(第3の実施の形態)

本実施の形態において、めっき処理の途中で、表面積の変化に応じて、補正値を設定し直す点で、第1の実施の形態および第2の実施の形態で説明したのと異なる。めっき処理をすすめると、徐々に凹部が埋められていくので、表面積比Srの値が小さくなっていく。本実施の形態においては、予めパターン密度の異なるウェハごとに、めっき処理の進行状況と、その時点での表面積比Srの値との関係を予め求めておく。この関係に基づき、電流密度を変化させる。

【0054】

たとえば、第1の電流密度でめっき処理を行う工程は、当該めっき処理の進行状況に応じて第1の表面積S1が変化することを考慮して、途中の段階で当該段階における第1の表面積S1の値を第2の表面積S2で除して表面積比Srを算出し、当該表面積比Srに基づき第1の基準電流密度を補正した第1の電流密度でめっき処理を行う工程を含む。たとえば、第1のめっき処理において、めっき処理前の第1の表面積S1を用いて第1の基準電流密度を補正しためっき処理と、めっき処理途中の第1の表面積S1を用いて第1の基準電流密度を補正しためっき処理とを順次行うようにすることができる。

【0055】

図5は、本実施の形態における表面積比Srの算出手順を説明する模式図である。

ここでは、凹部Aおよび凹部Bを例として説明する。めっき処理前の凹部Aおよび凹部Bを破線で示す。めっき処理前、凹部Aは、図3に示したのと同様、周辺長が(a+b+c+d)となる。また、めっき処理前、凹部Bは、周辺長が(e+f+g+h)となる。このとき、凹部Aおよび凹部Bともに、深さはmである。

【0056】

めっき処理途中のある段階において、凹部Aの周辺長l1'はl1'=(a'+b'+c'+d')となる。このとき凹部Aの深さはm1'となる。このとき、凹部Aの側壁面積は、l1'×m1'となる。また、同じ段階において、凹部Bの周辺長l2'はl2'=(e'+f'+g'+h')となる。このとき、凹部Bの深さはm2'となる。このとき、凹部Bの側壁面積は、l2'×m2'となる。他の凹部についても、パターンごとに同様に予め側壁面積を算出しておく。ここで、パターンごとに、周辺長を(l1'、l2'、l3'・・・)、深さを(m1'、m2'、m3'・・・)、パターンの数を(p1'、p2'、p3'・・・)とする。この場合、この段階でのめっき処理をする表面全体の実面積S3(=l1'×m1'× p1'+l2'×m2'× p2'・・・+S2)となる。この段階での表面積比Srは、実面積S3を基板の表面積S2で除すことにより算出される。以上の処理を、めっき処理の段階毎に行う。これにより、めっき処理過程全般において、実効電流密度を均一にすることができ、成膜を良好に行うことができる。

【0057】

なお、第2の電流密度でめっき処理を行う第2のめっき処理においても、その段階における表面積比Srを考慮した補正を行うようにしてもよい。本実施の形態におけるめっき処理は、以下の手順のいずれを採用してもよい。

(1)第1のめっき処理を複数回行った後、第1の実施の形態および第2の実施の形態と同様に、表面積比Srを考慮することなく、第2のめっき処理を行う。

(2)第1のめっき処理を複数回行った後、第2のめっき処理を行う際にも、表面積比Srを考慮して第2の電流密度を設定する。

(3)第1のめっき処理を1回行った後、第2のめっき処理を行う際にも、表面積比Srを考慮して第2の電流密度を設定する。

【0058】

上記(2)および(3)の場合、第2の電流密度は、第2の基準電流密度を複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれた時点での半導体基板全面における各複数の凹部の側壁の面積を含む第3の表面積S3と各複数の凹部の側壁の面積を含まない第4の表面積S4との表面積比Sr=S3/S4に基づき補正することにより算出することができる。

【0059】

本実施の形態において、めっき処理の進行に応じて変化する表面積比に応じて、補正を細かく行うことにより、膜厚制御および均一性制御を精度よく行うことができる。

本実施の形態の場合においても第1の実施の形態と同様に、めっき処理の適切な時間をあるレチクルにつきめっき装置に一旦設定すれば、同じレチクルを使用して形成された凹部のめっき処理はこの設定に基づいて行えばよい。

【0060】

(第4の実施の形態)

本実施の形態において、第1〜第3の実施の形態で説明しためっき処理を行うめっき処理装置200の構成を説明する。

図6は、本実施の形態におけるめっき処理装置200の構成を示すブロック図である。

めっき処理装置200は、めっき処理制御部202と、めっき処理部208とを含む。めっき処理制御部202は、演算部204およびデータ記憶部206を含む。製品情報管理装置210は、製品ごとに決まっている処理条件および処理結果を一元管理する。

【0061】

めっき処理装置200は、製品情報管理装置210からめっき対象基板の表面積比Srを取得する。データ記憶部206は、表面積比Srが1の場合の電流値を記憶する。演算部204は、データ記憶部206から表面積比Srが1の場合の電流値を読み出し、当該電流値と製品情報管理装置210から取得した表面積比Srの値とに基づき、適切な電流密度を算出する。めっき処理制御部202は、演算部204が算出した電流値をめっき処理部208に出力する。めっき処理部208は、めっき処理制御部202から出力された電流値でめっき処理を行う。

【0062】

なお、このような装置を用いて電流密度補正を行う場合に、各製品情報に応じてめっき処理装置200で補正を行うためには、製品種類の数×めっき層の数分行う必要があり、非常に煩雑である。そのため、予め設定されている製品情報が製品情報管理装置210からめっき処理装置200へ自動的に伝達されるよう構成されることが好ましい。また、これにより、この補正が自動的に行なわれることが好ましい。

【実施例】

【0063】

以下の実施例および比較例において、表面積比Sr=2.7となる半導体装置へのめっき処理を行った。なお、補正を行わない場合のウェハ電流密度(第1の基準電流密度)が4.2mA/cm2となるようにした。また、めっき処理開始前の表面積比Sr=2.7であった。

【0064】

(実施例)

第1のめっき処理:第1の基準電流密度を表面積比Srで補正し、第1の電流密度を4.2mA/cm2×2.7=11.34mA/cm2とした。60秒成膜処理を行った。

第2のめっき処理:第2の電流密度を28mA/cm2とした。40秒成膜処理を行った。

【0065】

(比較例)

第1のめっき処理:第1の基準電流密度への補正を行うことなく、第1の基準電流密度をそのまま第1の電流密度として、4.2mA/cm2とした。60秒成膜処理を行った。

第2のめっき処理:第2の電流密度を28mA/cm2とした。40秒成膜処理を行った。

【0066】

上記のめっき処理後、実施例および比較例の半導体装置について、へき開して、めっき膜の膜厚を観察した。実施例では、凹部形成箇所上方において、余剰膜厚が200〜1000Åとなった。一方、比較例の場合、めっき膜が充分に埋まっておらず、凹部内に空孔が形成された箇所が見られた。これは、第1のめっき処理が不充分なために、微細凹部が充分埋まる前に第2のめっき処理に移行したため、凹部に空孔が形成されたと考えられる。

【0067】

比較例においては、表面積比Srに基づく補正を行っていない。そのため、ウェハ電流密度4.2mA/cm2の場合、凹部の側壁の面積を考慮すると、実効電流密度が4.2mA/cm2を2.7で割った値(約1.56mA/cm2)と小さくなる。実効電流密度が小さくなると、めっき膜の膜厚も比例して薄くなる。そのため、これを補償するためには第1のめっき処理の時間を60秒よりも長くする必要が生じる。しかしながら、処理時間を長くしても、実効電流密度が2mA/cm2より小さいと、ボトムアップ性が悪くなるため、埋設不良は解消されない。

【0068】

以上、本発明を実施の形態および実施例に基づいて説明した。この実施の形態および実施例はあくまで例示であり、種々の変形例が可能なこと、またそうした変形例および組合せも本発明の範囲にあることは当業者に理解されるところである。

【符号の説明】

【0069】

100 半導体装置

102 半導体基板

104 層間絶縁膜

106 層間絶縁膜

108 第1の配線溝

110 第2の配線溝

112 第3の配線溝

114 第4の配線溝

116 第5の配線溝

118 第6の配線溝

120 第7の配線溝

130 第1のめっき膜

132 第2のめっき膜

200 めっき処理装置

202 めっき処理制御部

204 演算部

206 データ記憶部

208 めっき処理部

210 製品情報管理装置

【技術分野】

【0001】

本発明は、複数の凹部が形成された絶縁膜において、めっき処理により導電性膜を形成する際の半導体装置の製造方法およびめっき処理装置に関する。

【背景技術】

【0002】

銅配線を用いる半導体装置において、設計ルールの縮小に伴う配線パターン微細化が進むにつれ、銅めっきプロセスにおけるビアやトレンチへの埋設性能の向上が要求されている。

【0003】

特許文献1(米国特許第6319831号明細書)および特許文献2(米国特許第6140241号明細書)には、低い電流密度で第1のめっき処理を行い、その後に高い電流密度で第2のめっき処理を行う手順が記載されている。

【0004】

特許文献3(特開2001−123298号公報)には、被めっき対象物と同じ材料からなる電極を用い、電極電位と電流密度の関係式を予め求めておき、一方、めっき浴中にて被めっき対象物を任意の電位または電流値で分極させ、そのときの電流値および電位値を求め、上記関係式と前記電流値および電位値から、被めっき対象部分の面積を算出し、この算出した面積に基づいて、所定の膜厚のめっきを行うことの電流値で電解めっきを行う技術が記載されている。具体的には、基板に感光性のめっきレジストを用いてフォトリソグラフ法により配線パターンを形成し、感光性のめっきレジストにより保護されていない露出部分である被めっき対象となる電極の面積を、当該基板を分極させて電流値を測定する。次いで、電流値に基づき、基板の被めっき対象部の面積を算出する。この面積に基づき、めっき処理の電流値を決定する。

【0005】

特許文献4(特開2005−264271号公報)には、複数の凹部が形成された層における第1の基準幅以下の幅を有する微細凹部が当該層に占める割合を取得する工程と、その割合に応じて、導電性材料で凹部を埋め込む際の積算電流量を決定する工程と、その積算電流量に基づき、電解めっき法により、導電性パターンを形成する工程とを含む半導体装置の製造方法が記載されている。これにより、適切な膜厚の電解めっき膜を形成することができる。

【0006】

特許文献5(特開2006−60011号公報)には、絶縁膜表面と開口部とに形成されたシード膜を電極として第1の電流密度となる電流を流し、開口部に導電性材料をめっき法により堆積させる第1のめっき工程と、前記第1のめっき工程後、第1の電流密度より小さい電流密度となる電流を流し、絶縁膜表面上に導電性材料をめっき法により堆積させる第2のめっき工程と、第2のめっき工程後にアニール処理するアニール工程とを含む半導体装置の製造方法が記載されている。

【0007】

特許文献6(特開2005−39142号公報)には、半導体基板上の絶縁膜に形成された、配線用溝およびビア孔のうち少なくともいずれか一方に導電層を埋め込むための電解めっき法は、導電層の材料を含んだめっき液の単位面積あたりに流れる電流値である電流密度とめっき時間との積である積算電流密度が所定の値となる条件でめっき処理を行う第1のステップと、第1のステップよりも電流密度が小さい条件でめっき処理を行う第2のステップとを有する半導体装置の製造方法が記載されている。これにより、電解めっき法により、配線用溝やビア孔に形成された導電層の埋設性が向上し、かつボトムアップ性がウェハ面内でより均一となる、と記載されている。

【0008】

特許文献7(特開2004−270028号公報)には、ダマシン法銅めっきにおいて、めっきを成長させる処理の間に、めっきを成長させる方向とは逆の方向にのみ電流を流すステップを含む方法が記載されている。これにより、配線の密なところにめっきの盛り上がりが生じて、CMP研磨時間の増大によるコストアップ等が生じるのを防ぐことができる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】米国特許第6319831号明細書

【特許文献2】米国特許第6140241号明細書

【特許文献3】特開2001−123298号公報

【特許文献4】特開2005−264271号公報

【特許文献5】特開2006−60011号公報

【特許文献6】特開2005−39142号公報

【特許文献7】特開2004−270028号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

ところで、めっき処理装置においては、予め、めっき処理対象の半導体装置に印加する所定の基準電流密度およびめっき処理時間がレシピとして設定されている。一方、めっき処理対象の半導体装置は、設計に応じて様々な配線パターンを有する。微細パターンを多く含む半導体装置では、微細パターンをあまり含まない半導体装置に比べてめっき時間が長く必要になる。そのため、設計の異なる種々の半導体装置に同じ基準電流密度で同じ時間だけめっき処理を行おうとした場合に、微細パターンを多く含む半導体装置を基準にすると、微細パターンをあまり含まない半導体装置においてはめっき成膜が過剰に行われるという問題が生じる。めっき成膜が過剰に行われると、めっき材料が無駄に使われ無駄なコストがかかるとともに、その後のCMP等の処理において時間がかかり、スループットが低下するという問題が生じる。一方、微細パターンをあまり含まない半導体装置を基準にすると、微細パターンを多く含む半導体装置において、めっき成膜が充分に行えないという問題が生じる。とくに微細な凹部でのめっき成膜が充分に行えず、凹部中に空孔等が形成されてしまう。しかし、従来、このような問題が解決されていなかった。

【0011】

本発明者らは、上記のような現象を種々検討した結果、めっき処理により半導体装置の凹部内を導電性材料で埋め込む場合、配線パターンの密度によって凹部の側壁の面積が大きく異なることにより、めっき処理の実効的な表面積が大きく異なることが、上記のような問題が生じる原因であることを見出した。

【0012】

しかし、従来、このような問題が解決されていなかった。たとえば、特許文献3においては、被めっき対象となる電極の面積に基づきめっき処理の電流値を決定しているが、めっき処理により凹部内を導電性材料で埋め込む場合の特性が考慮されていない。すなわち、凹部の側壁の面積が考慮されていないため、精度のよい補正ができていない。また、特許文献4に記載の技術では、微細凹部が層に占める割合に応じて積算電流量が決定されているが、めっき処理の実効的な表面積が考慮されていないため、精度のよい補正ができていない。

【課題を解決するための手段】

【0013】

本発明によれば、

基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含み、

前記めっき工程は、前記複数の凹部のうち所定幅以下の微細な凹部が前記導電性材料で埋め込まれる際に、所定の第1の基準電流密度を前記基板全面における各前記複数の凹部の側壁の面積を含む第1の表面積S1と各前記複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度を用いてめっき処理を行う工程を含む半導体装置の製造方法が提供される。めっき工程は、前記凹部内にシード膜を形成する工程を含むことができ、第1の電流密度を用いてめっき処理を行う工程は、シード膜を形成する工程の後に行うことができる。

【0014】

本発明によれば、

基板上に形成された絶縁膜に設けられた複数の凹部を含む半導体装置の前記凹部をめっき処理により導電性材料で埋め込むめっき処理を行うめっき処理装置であって、

めっき対象の前記半導体装置に印加する第1の基準電流密度を記憶するデータ記憶部と、

前記めっき対象の前記半導体装置の前記基板全面における各前記複数の凹部の側壁の面積を含む第1の表面積S1と各前記複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2を取得し、当該表面積比Srに基づき、前記第1の基準電流密度を補正して第1の電流密度を算出する演算部と、

前記演算部で算出された前記第1の電流密度を用いて前記めっき対象の前記半導体装置へめっき処理を行うめっき処理部と、

を含むめっき処理装置が提供される。

【0015】

ここで、第1の表面積S1は、基板上の複数の凹部それぞれの周囲長の和に凹部深さを乗じた値と基板全面の表面積(第2の表面積S2)との和とすることができる。

【0016】

本発明の半導体装置の製造方法によれば、所定幅以下の微細な凹部が前記導電性材料で埋め込まれる際に、凹部の側壁の面積を考慮して電流密度が補正される。そのため、半導体装置において形成される凹部のパターンにかかわらず、電流密度を略一定にすることができる。これにより、めっき処理時のボトムアップ性を良好にすることができ、微細な凹部においても、めっき膜を制御性よく形成することができる。また、電流密度を略一定にすることができるため、成膜されるめっき膜のたとえば粒径や配向等の性質も一定にすることができ、膜特性を良好にすることができる。

【0017】

なお、微細な凹部が埋め込まれるまでのめっき処理の大部分をこのように補正した電流密度を用いて行うことにより、上記の効果が得られる。すなわち、めっき処理の最初や途中の段階の短い時間、このように補正した電流密度を用いることなくめっき処理を行うことを排除するものではない。さらに、微細な凹部を埋め込んだ後は、このような補正を行うことなく、より大きい電流密度を用いてめっき処理を行うこともできる。これにより、スループットを高めることができる。

【発明の効果】

【0018】

本発明によれば、めっき膜厚の制御を精度よく行うことができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図2】本発明の実施の形態におけるめっき処理手順を示すフローチャートである。

【図3】半導体装置を模式的に示す図である。

【図4】複数のグループと、各グループにおける表面積比Srの範囲、および用いる電流密度との関係を示す図である。

【図5】本発明の実施の形態における表面積比Srの算出手順を説明する模式図である。

【図6】本発明の実施の形態におけるめっき処理装置の構成を示すブロック図である。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0021】

(第1の実施の形態)

図1は、本実施の形態における半導体装置100の製造手順を示す工程断面図である。本実施の形態において、層間絶縁膜106に配線を形成する工程を説明する。本実施の形態において、ダマシン法により銅配線を形成する手順を説明する。

【0022】

半導体装置100は、トランジスタ等が形成された半導体基板(基板)102と、半導体基板102上に形成された層間絶縁膜104と、その上に形成された層間絶縁膜106とを含む。層間絶縁膜104および層間絶縁膜106中には、配線やビアが形成されている。

【0023】

このように構成された半導体装置100において、まず、層間絶縁膜106に配線溝を形成する。ここで、図示したように、層間絶縁膜106には、第1の配線溝108、第2の配線溝110、第3の配線溝112、第4の配線溝114、第5の配線溝116、第6の配線溝118、および第7の配線溝120が形成される。

【0024】

第1の配線溝108は配線幅D1、第5の配線溝116は配線幅D2、第6の配線溝118は配線幅D3、第7の配線溝120は配線幅D4を有する。第5の配線溝116の配線幅D2、第6の配線溝118の配線幅D3は略等しく、たとえば0.3μmとする。第1の配線溝108の配線幅D1および第7の配線溝120の配線幅D4は、配線幅D2および配線幅D3よりも幅広である。また、第2の配線溝110、第3の配線溝112、および第4の配線溝114は、配線幅D2および配線幅D3よりも幅狭である。

【0025】

このような配線溝(凹部)を配線材料で埋め込む手順は、以下のようになる。まず、層間絶縁膜106の凹部内にバリアメタル膜を形成する。バリアメタル膜は、たとえばTaN/Ta等、通常の銅配線のバリアメタル膜として用いられるものとすることができる。つづいて、バリア膜上にめっきのシード膜を形成する。ここで、シード膜は、CVD法等により形成された銅膜等とすることができる。

【0026】

その後、めっき処理を行う。本実施の形態において、めっき処理が通常の手順と異なる。本実施の形態において、めっき液は、通常の銅配線形成時のめっき膜を形成するのに用いるものと同様とすることができる。めっき液は、たとえば、硫酸、銅、および塩素を含むことができる。また、めっき液は、サプレッサー、アクセラレーター(キャリア)、レベラー等の添加剤を含むことができる。本実施の形態におけるめっき処理は、ボトムアップ堆積される。

【0027】

図2は、本実施の形態におけるめっき処理手順を示すフローチャートである。

本実施の形態において、所定の基準電流密度およびめっき処理時間が予め設定されている。なお、本実施の形態において、基準電流密度として、第1の基準電流密度と第1の基準電流密度よりも大きい第2の基準電流密度が設定されている。めっき処理は、2ステップで行われる。配線パターンにおける微細な凹部を埋め込むまでは、第1の基準電流密度に基づくめっき処理が行われ、その後は、第2の基準電流密度に基づくめっき処理が行われる。所定の基準電流密度とは、後述する表面積比Sr=1のときに半導体装置100に印加される実効電流密度のことである。

【0028】

本実施の形態において、第1の基準電流密度は、後述する表面積比Sr=1のときに半導体装置100に印加される実効電流密度が2mA/cm2以上6.5mA/cm2以下、より好ましくは3.5mA/cm2以上5mA/cm2以下となるように設定する。これにより、埋設不良やめっき焼け不良が起こらない領域でめっき処理を行うことができる。

【0029】

このような状態で、まず、半導体基板(ウェハ)全面における、各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2を算出する(S100)。上記の基準電流密度は、第2の表面積S2を基準として設定される。ここで、半導体基板が直径300mm(半径14.8cm)のシリコンウェハであれば、S2は688cm2になる。

【0030】

図3を参照して、表面積比Srの算出手順を説明する。図3は、半導体装置100を模式的に示す図である。図中、白抜き部分は、凹部が形成された箇所とすることができる。まず、レチクル上のパターンに基づき、半導体基板102(ウェハ)全体に形成された複数の凹部の周囲長lを算出する。たとえば、ある凹部Aの周囲長は(a+b+c+d)である。また、他の凹部Bの周囲長は(e+f+g+h)である。このように、半導体基板102上に形成された凹部すべての周囲長l=(a+b+c+d+e+f+g+h・・)を算出する。つづいて、周囲長lに凹部の深さmを乗じて側壁面積(l×m)を算出する。このようにして算出した側壁面積をウェハ面積S2に加えることにより、めっき処理をする表面全体の実面積S1(=l×m+S2)を算出する。表面積比Srは、実面積S1を基板の表面積S2で除すことにより算出される。

【0031】

図2に戻り、表面積比Srの値に基づき、補正が必要か否かを判断する(S102)。本実施の形態において、表面積比Srが所定範囲内か否かを判断し、表面積比Srが所定範囲内の場合に、補正が必要と判断する。ここで、所定の範囲は、たとえば、1.4以上とすることができる。これにより、表面積比Srがあまり大きくない場合には、補正処理を行うことなく、スムーズにめっき処理を行うことができるとともに、表面積比Srがある程度大きい場合に、補正処理を行うことにより、ボトムアップ性を良好にすることができる。

【0032】

すなわち、半導体基板102上に微細な凹部が多数形成されている場合は、側壁面積が大きくなり、表面積比Srの値が大きくなる。本実施の形態において、表面積比Srが大きく、凹部の側壁面積の影響が無視できない時に、表面積比Srに基づき第1の電流密度を補正して第1のめっき処理を行う。ボトムアップ堆積されるめっき処理の場合、凹部の側壁の面積の大小により、実効電流密度が異なってくる。本実施の形態において、表面積比Srに応じて適宜電流密度が補正されるので、様々なパターン密度の半導体装置の膜厚の制御を精度よく行うことができる。

【0033】

補正が必要な場合(S102のYES)、所定の第1の基準電流密度を表面積比Srに基づいて補正した第1の電流密度を用いてめっき処理を行う(S104)。第1の電流密度は、表面積比Srが大きいほど大きくなるように設定される。本実施の形態において、第1の電流密度は、側壁面積を考慮しない第1の基準電流密度(Sr=1)に対して、表面積比Srを乗じることによって算出される。上述したように、本実施の形態において、第1の基準電流密度は、Sr=1のときに、実効電流密度がたとえば2mA/cm2以上6.5mA/cm2以下、より好ましくは3.5mA/cm2以上5mA/cm2以下の範囲内になるように設定される。このような第1の基準電流値を表面積比Srに基づいて補正した場合、半導体装置100の配線パターンに関わらず、実効電流密度を、たとえば2mA/cm2以上6.5mA/cm2以下、より好ましくは3.5mA/cm2以上5mA/cm2以下の範囲内にすることができる。これにより、凹部を良好に埋設することができるとともに、めっき焼けが生じないようにすることができる。

【0034】

以下、このめっき処理を第1のめっき処理という。第1のめっき処理は、層間絶縁膜106上に形成された複数の凹部のうち所定幅以下の微細な凹部(以下、単に微細凹部という。)が導電性材料で埋め込まれるまで行う。本実施の形態において、所定幅は、たとえば0.3μmとすることができる。このような微細凹部において、表面積比Srを考慮して第1の基準電流密度を補正することにより、ボトムアップ性を良好にすることができる。

【0035】

なお、微細凹部への導電性材料による埋め込みが終了するまでの時間を予め設定しておき、その時間が経過したか否かに基づき、ステップS106の判断を行うことができる。この時間は、たとえば以下のようにして算出することができる。まず、複数のサンプルを準備する。つづいて、これらのサンプルについて、同様の処理条件で、いくつかの時間間隔でめっき処理を行なう。その後、複数のサンプルをへき開し、微細凹部が埋め込まれているサンプルを検出する。そのサンプルに施しためっき処理時間が、微細凹部への導電性材料による埋め込みが終了するまでの時間となる。また、単位時間あたりの成膜量が把握できれば、凹部の幅に基づき、微細凹部への導電性材料による埋め込みが終了するまでの時間を算出することもできる。

【0036】

微細凹部の埋め込みが終了すると(S106のYES)、第1のめっき処理を終了する。この工程を図1(b)に示す。第1のめっき処理により、第5の配線溝116および第6の配線溝118ならびにこれらよりも微細な微細凹部が第1のめっき膜130により埋め込まれる。

【0037】

図2に戻り、第2の電流密度を用いてめっき処理を行う(S108)。第2の電流密度は、表面積比Srに基づく補正を行わないものとすることができる。本実施の形態において、第2の電流密度としては、第2の基準電流密度を用いることができる。第2の電流密度は、第1の基準電流密度に比べて、大きい値とすることができる。以下、このめっき処理を第2のめっき処理という。第2の電流密度は、たとえば、28mA/cm2以上57mA/cm2以下(20−40A/wfで換算)とすることができる。より好ましくは、第2の電流密度は、42mA/cm2以上57mA/cm2以下(30−40A/wfで換算)とすることができる。これにより、生産性を良好にすることができる。第2の電流密度でのめっき処理が終了すると(S110のYES)、めっき処理を終了する。この工程を図1(c)に示す。第2の電流密度でのめっき処理により、第5の配線溝116および第6の配線溝118よりも幅広な凹部が第2のめっき膜132により埋め込まれる。

【0038】

図2に戻り、ステップS102において、補正が必要でない場合(S102のNO)、第1の基準電流密度を用いた通常のめっき処理を行い(S112)、めっき処理を終了する。

【0039】

なお、第1のめっき処理と第2のめっき処理の処理時間は、予め算出しておくことができる。第1のめっき処理の処理時間は、上述した微細凹部への導電性材料による埋め込みが終了するまでの時間とすることができる。たとえば、第1のめっき処理は50秒〜80秒程度、第2のめっき処理は20秒〜50秒程度とすることができる。これらの処理時間は一例であり、所望の膜厚を得るための適切な値に設定することができる。

【0040】

以上のめっき処理の終了後、CMPにより、配線溝外部に露出した第2のめっき膜132を除去して平坦化する。この後、さらに層間絶縁膜形成、凹部形成、金属膜形成を繰り返すことにより、多層配線構造が得られる。

【0041】

なお、第1のめっき処理と第2のめっき処理との間(図2のステップS106とステップS108との間)に、めっき成膜を行う際とは逆方向に電流をかける処理を行うことができる。この手順は、特許文献7に記載されたのと同様にして行うことができる。このような処理により、成膜された第1のめっき膜130の一部を溶かすことができる。これにより、めっき膜上の添加剤の濃淡をキャンセルすることができ、めっき膜の面内均一性を向上することができる。

【0042】

以上のように、本実施の形態における半導体装置の製造手順によれば、微細凹部が埋め込まれるまでは、表面積比Srに基づき補正した第1の電流密度によりめっき処理が行われる。そのため、各凹部内において、実効電流密度が等しい条件で、めっき処理を行うことができる。これにより、めっき成膜とボトムアップを効率よく行うことができる。また、微細凹部が埋め込まれた後は、第2のめっき処理により、効率よく成膜を行うことができる。これにより、めっき処理装置のスループットを向上することができる。また、ボトムアップを良好に行うことができるため、めっき処理後のCMP工程での処理時間減少によるスループット向上を行うこともできる。

【0043】

以上の手順により、微細パターンが含まれる半導体装置と大パターンが形成された半導体装置との間でのめっき膜厚差を減少することができる。また、面内均一性も向上する。

なお、実際には配線パターン密度はレチクルにより決まっている。このため図2に示した手順およびめっき処理の適切な時間をあるレチクルにつきめっき装置に一旦設定すれば、同じレチクルを使用して形成された凹部のめっき処理はこの設定に基づいて行うことができる。

【0044】

(第2の実施の形態)

本実施の形態において、第1のめっき処理における第1の電流密度の補正方法が、第1の実施の形態で説明したのと異なる。

【0045】

本実施の形態において、表面積比Srを所定範囲毎にグループ化し、各グループに対して、補正値を設定する。すなわち、グループ毎に第1の電流密度を設定する。そして、第1の電流密度でめっき処理を行う際に、当該半導体装置の表面積比Srが含まれるグループに設定された第1の電流密度でめっき処理を行う。このようにすることにより、めっき処理時のレシピを簡略化することができるとともに、ボトムアップを良好に行うことができる。

【0046】

図4は、複数のグループと、各グループにおける表面積比Srの範囲、および用いる電流密度との関係を示す図である。

【0047】

たとえば、表面積比Srが1.0≦Sr<1.2の範囲にある場合、グループAに分類される。同様に、表面積比Srが1.2≦Sr<1.4の範囲にある場合グループBというように、たとえばSrの大きさ0.2ごとにグループ分けを行う。

【0048】

めっき装置の設定電流値は、各グループに対して、実効電流密度が所定範囲内となるように設定される。すなわち、各グループの第1の電流密度は、当該第1の電流密度を表面積比Srで除して得られる実効電流密度が所定範囲内となるように設定される。ここで、所定範囲は、たとえば2mA/cm2以上6.5mA/cm2以下、より好ましくは3.5mA/cm2以上5mA/cm2以下とすることができる。このような範囲とすることにより、凹部を良好に埋設することができるとともに、めっき焼けが生じないようにすることができる。

【0049】

たとえば、グループAの表面積比が1.0≦Sr<1.2の範囲にあるものは、めっき装置の電流値を3Aで処理すると定める。このようにすると、第1の電流密度は、4.4A/cm2となる。この場合、表面積比Srを考慮した実効電流密度は、表面積比Sr=1の場合には4.4mA/cm2、表面積比Sr=1.2の場合には3.6mA/cm2となる。このように、同じグループに属する場合でも表面積比Srの値によって実効電流密度が異なるが、グループ分けを適切に行うことにより、好ましい範囲におさめることができる。

【0050】

図4に示したように、表面積比Srが大きいグループほど、めっき装置の電流値を高く定める必要がある。このような表面積比Srに基づく電流密度の補正は、表面積比Srが大きい場合に、とくに有効に用いることができる。たとえば、表面積比Srが2.0の場合、グループFに属する。この場合、めっき装置の電流値を5.5Aで処理すると定める。このようにすると、第1の電流密度は、8.0mA/cm2となる。この場合、表面積比Srを考慮した実効電流密度は、4.0mA/cm2となる。

【0051】

以上の第1のめっき処理を行った後、第1の実施の形態で説明したのと同様の第2のめっき処理を行う。

【0052】

本実施の形態においても、第1の実施の形態と同様の効果が得られる。また、処理やレシピを簡略化することができる。

【0053】

(第3の実施の形態)

本実施の形態において、めっき処理の途中で、表面積の変化に応じて、補正値を設定し直す点で、第1の実施の形態および第2の実施の形態で説明したのと異なる。めっき処理をすすめると、徐々に凹部が埋められていくので、表面積比Srの値が小さくなっていく。本実施の形態においては、予めパターン密度の異なるウェハごとに、めっき処理の進行状況と、その時点での表面積比Srの値との関係を予め求めておく。この関係に基づき、電流密度を変化させる。

【0054】

たとえば、第1の電流密度でめっき処理を行う工程は、当該めっき処理の進行状況に応じて第1の表面積S1が変化することを考慮して、途中の段階で当該段階における第1の表面積S1の値を第2の表面積S2で除して表面積比Srを算出し、当該表面積比Srに基づき第1の基準電流密度を補正した第1の電流密度でめっき処理を行う工程を含む。たとえば、第1のめっき処理において、めっき処理前の第1の表面積S1を用いて第1の基準電流密度を補正しためっき処理と、めっき処理途中の第1の表面積S1を用いて第1の基準電流密度を補正しためっき処理とを順次行うようにすることができる。

【0055】

図5は、本実施の形態における表面積比Srの算出手順を説明する模式図である。

ここでは、凹部Aおよび凹部Bを例として説明する。めっき処理前の凹部Aおよび凹部Bを破線で示す。めっき処理前、凹部Aは、図3に示したのと同様、周辺長が(a+b+c+d)となる。また、めっき処理前、凹部Bは、周辺長が(e+f+g+h)となる。このとき、凹部Aおよび凹部Bともに、深さはmである。

【0056】

めっき処理途中のある段階において、凹部Aの周辺長l1'はl1'=(a'+b'+c'+d')となる。このとき凹部Aの深さはm1'となる。このとき、凹部Aの側壁面積は、l1'×m1'となる。また、同じ段階において、凹部Bの周辺長l2'はl2'=(e'+f'+g'+h')となる。このとき、凹部Bの深さはm2'となる。このとき、凹部Bの側壁面積は、l2'×m2'となる。他の凹部についても、パターンごとに同様に予め側壁面積を算出しておく。ここで、パターンごとに、周辺長を(l1'、l2'、l3'・・・)、深さを(m1'、m2'、m3'・・・)、パターンの数を(p1'、p2'、p3'・・・)とする。この場合、この段階でのめっき処理をする表面全体の実面積S3(=l1'×m1'× p1'+l2'×m2'× p2'・・・+S2)となる。この段階での表面積比Srは、実面積S3を基板の表面積S2で除すことにより算出される。以上の処理を、めっき処理の段階毎に行う。これにより、めっき処理過程全般において、実効電流密度を均一にすることができ、成膜を良好に行うことができる。

【0057】

なお、第2の電流密度でめっき処理を行う第2のめっき処理においても、その段階における表面積比Srを考慮した補正を行うようにしてもよい。本実施の形態におけるめっき処理は、以下の手順のいずれを採用してもよい。

(1)第1のめっき処理を複数回行った後、第1の実施の形態および第2の実施の形態と同様に、表面積比Srを考慮することなく、第2のめっき処理を行う。

(2)第1のめっき処理を複数回行った後、第2のめっき処理を行う際にも、表面積比Srを考慮して第2の電流密度を設定する。

(3)第1のめっき処理を1回行った後、第2のめっき処理を行う際にも、表面積比Srを考慮して第2の電流密度を設定する。

【0058】

上記(2)および(3)の場合、第2の電流密度は、第2の基準電流密度を複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれた時点での半導体基板全面における各複数の凹部の側壁の面積を含む第3の表面積S3と各複数の凹部の側壁の面積を含まない第4の表面積S4との表面積比Sr=S3/S4に基づき補正することにより算出することができる。

【0059】

本実施の形態において、めっき処理の進行に応じて変化する表面積比に応じて、補正を細かく行うことにより、膜厚制御および均一性制御を精度よく行うことができる。

本実施の形態の場合においても第1の実施の形態と同様に、めっき処理の適切な時間をあるレチクルにつきめっき装置に一旦設定すれば、同じレチクルを使用して形成された凹部のめっき処理はこの設定に基づいて行えばよい。

【0060】

(第4の実施の形態)

本実施の形態において、第1〜第3の実施の形態で説明しためっき処理を行うめっき処理装置200の構成を説明する。

図6は、本実施の形態におけるめっき処理装置200の構成を示すブロック図である。

めっき処理装置200は、めっき処理制御部202と、めっき処理部208とを含む。めっき処理制御部202は、演算部204およびデータ記憶部206を含む。製品情報管理装置210は、製品ごとに決まっている処理条件および処理結果を一元管理する。

【0061】

めっき処理装置200は、製品情報管理装置210からめっき対象基板の表面積比Srを取得する。データ記憶部206は、表面積比Srが1の場合の電流値を記憶する。演算部204は、データ記憶部206から表面積比Srが1の場合の電流値を読み出し、当該電流値と製品情報管理装置210から取得した表面積比Srの値とに基づき、適切な電流密度を算出する。めっき処理制御部202は、演算部204が算出した電流値をめっき処理部208に出力する。めっき処理部208は、めっき処理制御部202から出力された電流値でめっき処理を行う。

【0062】

なお、このような装置を用いて電流密度補正を行う場合に、各製品情報に応じてめっき処理装置200で補正を行うためには、製品種類の数×めっき層の数分行う必要があり、非常に煩雑である。そのため、予め設定されている製品情報が製品情報管理装置210からめっき処理装置200へ自動的に伝達されるよう構成されることが好ましい。また、これにより、この補正が自動的に行なわれることが好ましい。

【実施例】

【0063】

以下の実施例および比較例において、表面積比Sr=2.7となる半導体装置へのめっき処理を行った。なお、補正を行わない場合のウェハ電流密度(第1の基準電流密度)が4.2mA/cm2となるようにした。また、めっき処理開始前の表面積比Sr=2.7であった。

【0064】

(実施例)

第1のめっき処理:第1の基準電流密度を表面積比Srで補正し、第1の電流密度を4.2mA/cm2×2.7=11.34mA/cm2とした。60秒成膜処理を行った。

第2のめっき処理:第2の電流密度を28mA/cm2とした。40秒成膜処理を行った。

【0065】

(比較例)

第1のめっき処理:第1の基準電流密度への補正を行うことなく、第1の基準電流密度をそのまま第1の電流密度として、4.2mA/cm2とした。60秒成膜処理を行った。

第2のめっき処理:第2の電流密度を28mA/cm2とした。40秒成膜処理を行った。

【0066】

上記のめっき処理後、実施例および比較例の半導体装置について、へき開して、めっき膜の膜厚を観察した。実施例では、凹部形成箇所上方において、余剰膜厚が200〜1000Åとなった。一方、比較例の場合、めっき膜が充分に埋まっておらず、凹部内に空孔が形成された箇所が見られた。これは、第1のめっき処理が不充分なために、微細凹部が充分埋まる前に第2のめっき処理に移行したため、凹部に空孔が形成されたと考えられる。

【0067】

比較例においては、表面積比Srに基づく補正を行っていない。そのため、ウェハ電流密度4.2mA/cm2の場合、凹部の側壁の面積を考慮すると、実効電流密度が4.2mA/cm2を2.7で割った値(約1.56mA/cm2)と小さくなる。実効電流密度が小さくなると、めっき膜の膜厚も比例して薄くなる。そのため、これを補償するためには第1のめっき処理の時間を60秒よりも長くする必要が生じる。しかしながら、処理時間を長くしても、実効電流密度が2mA/cm2より小さいと、ボトムアップ性が悪くなるため、埋設不良は解消されない。

【0068】

以上、本発明を実施の形態および実施例に基づいて説明した。この実施の形態および実施例はあくまで例示であり、種々の変形例が可能なこと、またそうした変形例および組合せも本発明の範囲にあることは当業者に理解されるところである。

【符号の説明】

【0069】

100 半導体装置

102 半導体基板

104 層間絶縁膜

106 層間絶縁膜

108 第1の配線溝

110 第2の配線溝

112 第3の配線溝

114 第4の配線溝

116 第5の配線溝

118 第6の配線溝

120 第7の配線溝

130 第1のめっき膜

132 第2のめっき膜

200 めっき処理装置

202 めっき処理制御部

204 演算部

206 データ記憶部

208 めっき処理部

210 製品情報管理装置

【特許請求の範囲】

【請求項1】

基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含み、

前記めっき工程は、前記複数の凹部のうち所定幅以下の微細な凹部が前記導電性材料で埋め込まれる際に、所定の第1の基準電流密度を前記基板全面における各前記複数の凹部の側壁の面積を含む第1の表面積S1と各前記複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度を用いてめっき処理を行う工程を含む半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法において、

前記第1の基準電流密度は、前記第2の表面積S2を基準として設定され、

前記第1の電流密度は、前記第1の基準電流密度と、前記表面積比Srとの積である半導体装置の製造方法。

【請求項3】

請求項1または2に記載の半導体装置の製造方法において、

前記第1の電流密度は、当該第1の電流密度を前記表面積比Srで除して得られる実効電流密度が所定範囲内となるように設定される半導体装置の製造方法。

【請求項4】

請求項3に記載の半導体装置の製造方法において、

前記所定範囲が、2mA/cm2以上6.5mA/cm2以下である半導体装置の製造方法。

【請求項5】

請求項3または4に記載の半導体装置の製造方法において、

前記表面積比Srを所定範囲毎にグループ化し、前記グループ毎に前記第1の電流密度を設定する工程をさらに含み、

前記第1の電流密度を用いてめっき処理を行う工程において、前記表面積比Srが含まれる前記グループに設定された前記第1の電流密度を用いてめっき処理を行う半導体装置の製造方法。

【請求項6】

請求項1から5いずれかに記載の半導体装置の製造方法において、

前記めっき工程は、前記複数の凹部のうち所定幅以下の微細な凹部が前記導電性材料で埋め込まれた後に、前記第1の電流密度とは異なる第2の電流密度を用いてめっき処理を行い、前記複数の凹部を前記導電性材料で埋め込む工程をさらに含む半導体装置の製造方法。

【請求項7】

請求項6に記載の半導体装置の製造方法において、

前記第1の基準電流密度は、前記第2の電流密度よりも小さいことを特徴とする半導体装置の製造方法。

【請求項8】

請求項6または7に記載の半導体装置の製造方法において、

前記第2の電流密度は、前記第2の表面積S2を基準として設定された第2の基準電流密度である半導体装置の製造方法。

【請求項9】

請求項6または7に記載の半導体装置の製造方法において、

前記第2の電流密度は、前記第2の表面積S2を基準として設定された第2の基準電流密度を前記複数の凹部のうち所定幅以下の微細な凹部が前記導電性材料で埋め込まれた時点での前記基板全面における各前記複数の凹部の側壁の面積を含む第3の表面積S3と各前記複数の凹部の側壁の面積を含まない第4の表面積S4との表面積比Sr=S3/S4に基づき補正したものである半導体装置の製造方法。

【請求項10】

請求項1から9いずれかに記載の半導体装置の製造方法において、

前記第1の電流密度を用いてめっき処理を行う工程は、当該めっき処理の進行状況に応じて前記第1の表面積S1が変化することを考慮して、途中の段階で当該段階における前記第1の表面積S1の値を前記第2の表面積S2で除して前記表面積比Srを算出し、当該表面積比Srに基づき前記第1の基準電流密度を補正した前記第1の電流密度を用いてめっき処理を行う工程を含む半導体装置の製造方法。

【請求項11】

請求項1から10いずれかに記載の半導体装置の製造方法において、

前記所定幅が、0.3μmである半導体装置の製造方法。

【請求項12】

請求項1から11いずれかに記載の半導体装置の製造方法において、

前記第1の電流密度を用いてめっき処理を行う工程の前に、前記表面積比Srが所定範囲か否かを判断し、所定範囲内の場合に、前記第1の電流密度を用いてめっき処理を行うとともに、所定範囲外の場合、前記第1の基準電流密度を用いてめっき処理を行う半導体装置の製造方法。

【請求項13】

請求項12に記載の半導体装置の製造方法において、

前記所定範囲は、1.4以上である半導体装置の製造方法。

【請求項14】

請求項1から13いずれかに記載の半導体装置の製造方法において、

前記第1の電流密度は、前記表面積比Srが大きいほど大きくなるように設定される半導体装置の製造方法。

【請求項15】

基板上に形成された絶縁膜に設けられた複数の凹部を含む半導体装置の前記凹部をめっき処理により導電性材料で埋め込むめっき処理を行うめっき処理装置であって、

めっき対象の前記半導体装置に印加する第1の基準電流密度を記憶するデータ記憶部と、

前記めっき対象の前記半導体装置の前記基板全面における各前記複数の凹部の側壁の面積を含む第1の表面積S1と各前記複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2を取得し、当該表面積比Srに基づき、前記第1の基準電流密度を補正して第1の電流密度を算出する演算部と、

前記演算部で算出された前記第1の電流密度を用いて前記めっき対象の前記半導体装置へめっき処理を行うめっき処理部と、

を含むめっき処理装置。

【請求項1】

基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含み、

前記めっき工程は、前記複数の凹部のうち所定幅以下の微細な凹部が前記導電性材料で埋め込まれる際に、所定の第1の基準電流密度を前記基板全面における各前記複数の凹部の側壁の面積を含む第1の表面積S1と各前記複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度を用いてめっき処理を行う工程を含む半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法において、

前記第1の基準電流密度は、前記第2の表面積S2を基準として設定され、

前記第1の電流密度は、前記第1の基準電流密度と、前記表面積比Srとの積である半導体装置の製造方法。

【請求項3】

請求項1または2に記載の半導体装置の製造方法において、

前記第1の電流密度は、当該第1の電流密度を前記表面積比Srで除して得られる実効電流密度が所定範囲内となるように設定される半導体装置の製造方法。

【請求項4】

請求項3に記載の半導体装置の製造方法において、

前記所定範囲が、2mA/cm2以上6.5mA/cm2以下である半導体装置の製造方法。

【請求項5】

請求項3または4に記載の半導体装置の製造方法において、

前記表面積比Srを所定範囲毎にグループ化し、前記グループ毎に前記第1の電流密度を設定する工程をさらに含み、

前記第1の電流密度を用いてめっき処理を行う工程において、前記表面積比Srが含まれる前記グループに設定された前記第1の電流密度を用いてめっき処理を行う半導体装置の製造方法。

【請求項6】

請求項1から5いずれかに記載の半導体装置の製造方法において、

前記めっき工程は、前記複数の凹部のうち所定幅以下の微細な凹部が前記導電性材料で埋め込まれた後に、前記第1の電流密度とは異なる第2の電流密度を用いてめっき処理を行い、前記複数の凹部を前記導電性材料で埋め込む工程をさらに含む半導体装置の製造方法。

【請求項7】

請求項6に記載の半導体装置の製造方法において、

前記第1の基準電流密度は、前記第2の電流密度よりも小さいことを特徴とする半導体装置の製造方法。

【請求項8】

請求項6または7に記載の半導体装置の製造方法において、

前記第2の電流密度は、前記第2の表面積S2を基準として設定された第2の基準電流密度である半導体装置の製造方法。

【請求項9】

請求項6または7に記載の半導体装置の製造方法において、

前記第2の電流密度は、前記第2の表面積S2を基準として設定された第2の基準電流密度を前記複数の凹部のうち所定幅以下の微細な凹部が前記導電性材料で埋め込まれた時点での前記基板全面における各前記複数の凹部の側壁の面積を含む第3の表面積S3と各前記複数の凹部の側壁の面積を含まない第4の表面積S4との表面積比Sr=S3/S4に基づき補正したものである半導体装置の製造方法。

【請求項10】

請求項1から9いずれかに記載の半導体装置の製造方法において、

前記第1の電流密度を用いてめっき処理を行う工程は、当該めっき処理の進行状況に応じて前記第1の表面積S1が変化することを考慮して、途中の段階で当該段階における前記第1の表面積S1の値を前記第2の表面積S2で除して前記表面積比Srを算出し、当該表面積比Srに基づき前記第1の基準電流密度を補正した前記第1の電流密度を用いてめっき処理を行う工程を含む半導体装置の製造方法。

【請求項11】

請求項1から10いずれかに記載の半導体装置の製造方法において、

前記所定幅が、0.3μmである半導体装置の製造方法。

【請求項12】

請求項1から11いずれかに記載の半導体装置の製造方法において、

前記第1の電流密度を用いてめっき処理を行う工程の前に、前記表面積比Srが所定範囲か否かを判断し、所定範囲内の場合に、前記第1の電流密度を用いてめっき処理を行うとともに、所定範囲外の場合、前記第1の基準電流密度を用いてめっき処理を行う半導体装置の製造方法。

【請求項13】

請求項12に記載の半導体装置の製造方法において、

前記所定範囲は、1.4以上である半導体装置の製造方法。

【請求項14】

請求項1から13いずれかに記載の半導体装置の製造方法において、

前記第1の電流密度は、前記表面積比Srが大きいほど大きくなるように設定される半導体装置の製造方法。

【請求項15】

基板上に形成された絶縁膜に設けられた複数の凹部を含む半導体装置の前記凹部をめっき処理により導電性材料で埋め込むめっき処理を行うめっき処理装置であって、

めっき対象の前記半導体装置に印加する第1の基準電流密度を記憶するデータ記憶部と、

前記めっき対象の前記半導体装置の前記基板全面における各前記複数の凹部の側壁の面積を含む第1の表面積S1と各前記複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2を取得し、当該表面積比Srに基づき、前記第1の基準電流密度を補正して第1の電流密度を算出する演算部と、

前記演算部で算出された前記第1の電流密度を用いて前記めっき対象の前記半導体装置へめっき処理を行うめっき処理部と、

を含むめっき処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−167377(P2012−167377A)

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願番号】特願2012−91548(P2012−91548)

【出願日】平成24年4月13日(2012.4.13)

【分割の表示】特願2006−204535(P2006−204535)の分割

【原出願日】平成18年7月27日(2006.7.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願日】平成24年4月13日(2012.4.13)

【分割の表示】特願2006−204535(P2006−204535)の分割

【原出願日】平成18年7月27日(2006.7.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]