半導体装置の製造方法

【課題】半導体チップと配線基板との間にNCPを配した態様の半導体装置に関して、NCPと配線基板の密着力を向上させる。

【解決手段】まず、片面に、半導体チップの搭載領域に対応させた開口部を有する絶縁膜10が形成され、該開口部が、該半導体チップの主面の電極パッドが接続される接続パッド7とこれに繋がる配線パターン8とを露出させた配線基板1−1を用意する。次に、上記開口部内の接続パッド7を除いた場所にある、配線パターン8の表面および配線基板1の基材表面にコート材12を吹き付ける。コート材12は、NCP11との密着力が該NCP11と配線パターン8の表面との密着力より優れている。次に上記の開口部の、半導体チップを搭載する領域全体にNCP11を塗布する。次にフリップチップ実装方式で半導体チップ2の電極パッド5と配線基板1の接続パッド7とを電気接続しながら、半導体チップ2を配線基板1にNCP11を介して接合する。

【解決手段】まず、片面に、半導体チップの搭載領域に対応させた開口部を有する絶縁膜10が形成され、該開口部が、該半導体チップの主面の電極パッドが接続される接続パッド7とこれに繋がる配線パターン8とを露出させた配線基板1−1を用意する。次に、上記開口部内の接続パッド7を除いた場所にある、配線パターン8の表面および配線基板1の基材表面にコート材12を吹き付ける。コート材12は、NCP11との密着力が該NCP11と配線パターン8の表面との密着力より優れている。次に上記の開口部の、半導体チップを搭載する領域全体にNCP11を塗布する。次にフリップチップ実装方式で半導体チップ2の電極パッド5と配線基板1の接続パッド7とを電気接続しながら、半導体チップ2を配線基板1にNCP11を介して接合する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線が形成された配線基板の主面に非導電性接着材を介して半導体チップをフリップチップ実装方式で搭載してなる半導体装置の製造方法に関する。

【背景技術】

【0002】

主面に、半導体チップの電極パッドが接続される接続パッドを含む配線パターンが形成された配線基板を用意し、該配線基板の主面に半導体チップをフリップチップ実装方式で搭載する半導体装置の製造方法が知られている。この半導体装置の製造方法に関して、特許文献1には、半導体チップが搭載される側の面に該半導体チップが搭載される領域を取り囲むようにソルダーレジストが形成されている配線基板を用いて、フリップチップ実装を行う技術が開示されている。

【0003】

このような配線基板のチップ搭載領域には接続パッドの他に配線が露出されているため、配線基板のチップ搭載領域と半導体チップとの間にNCP(Non Conductive Paste)を配することがよくある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平09−82760号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

上記の配線基板に搭載される半導体チップが、メモリチップのように、該半導体チップの主面の中央領域に複数の電極パッドが配列されたものである場合には、該半導体チップの中央領域の電極パッドに対応して、配線基板上の接続パッドも中央領域に列状に配置される。このため、配線基板のチップ搭載領域の配線パターンは配線基板中央領域の接続パッドに向かって延びることとなり、チップ搭載領域内で配線が密集する領域が出来るという問題がある。

【0006】

また、配線パターンは一般に、Cu層にNi/Auのメッキ層が形成されている。このため、配線基板のチップ搭載領域と半導体チップとの間に配されたNCPに接触する面がAuとなる。NCPとAuの密着力はNCPと配線基板材料の密着力に比べて劣っている。なお、「密着力」とは、接着した2つの部材間の密着状態を維持するのに必要な力をいい、密着力が小さいほど2つの部材間が剥がれやすくなる。

【0007】

以上の事から、配線基板におけるNCPの塗布面積に対してAuメッキ配線の占有率が高くなればなるほど、半導体装置の信頼性試験などでの高温付加時に、配線が密集する領域のNCPとAuの界面で剥離が発生するおそれがある。

【0008】

このようなNCPの剥離は半導体装置の信頼性を低下させる。

【課題を解決するための手段】

【0009】

本発明による半導体装置の製造方法の一つの態様は、以下の工程を含む。

【0010】

まず、半導体チップを搭載するための配線基板であり、少なくとも片面に、該半導体チップを搭載する領域に対応させた開口部を有する絶縁膜が形成され、該開口部が、該半導体チップの主面の電極パッドが接続される接続パッドと該接続パッドに繋がる配線パターンとを露出させている、配線基板を用意する。

【0011】

続いて、上記の開口部内の接続パッドを除いた場所にある、配線パターンの表面にコート材層を形成する。このコート材は、非導電性ペースト(NCP)に対する密着力が該非導電性ペーストと前記配線パターンの表面との密着力よりも優れたものである。

【0012】

さらに、上記の開口部の、半導体チップを搭載する領域全体に、前記非導電性ペーストを塗布する。

【0013】

その後、フリップチップ実装方式で半導体チップの電極パッドと配線基板の接続パッドとを電気接続しながら、半導体チップを配線基板に非導電性ペーストを介して接合する。

【0014】

このような製造方法によれば、フリップチップ実装前に、配線基板におけるチップ搭載領域の配線パターンの表面に上記のコート材層(例えばソルダーレジスト)を設けたことにより、配線基板とNCPとの密着力が従来技術よりも向上する。結果、完成した半導体装置への加熱付加時において配線基板とNCPとの剥離を抑制することができる。

【0015】

さらに詳述すると、例えばガラスエポキシ配線基板におけるチップ搭載領域の配線パターンの表面が、Auのメッキ層で形成されている場合がある。この表面の材質は、NCPとガラスエポキシ配線基板との密着力に比べてNCPとの密着力が劣る。また、回路面の中央領域に電極パッドが列状に配設されているDRAMチップ等の半導体チップが搭載される配線基板では、該電極パッドに対応する接続パッドが列状に並び、これらの接続パッドに向かって配線パターンが延びるので、Auメッキ配線の密集箇所が出来やすい。このAu密集箇所はチップ搭載領域内でNCPとの密着性が相対的に低い所となる。以上の事を踏まえて、フリップチップ実装前に、チップ搭載領域の配線パターン上にソルダーレジストのコート材を付与しておくと、Au密集箇所とNCPとの密着力を増すことができる。

【発明の効果】

【0016】

したがって、本発明によれば、フリップチップ実装方式で配線基板上に電気接続された半導体チップとその配線基板との間に非導電性ペースト(NCP)を配した態様の半導体装置に関して、NCPと配線基板の密着力が従来よりも高いものを提供することができる。

【図面の簡単な説明】

【0017】

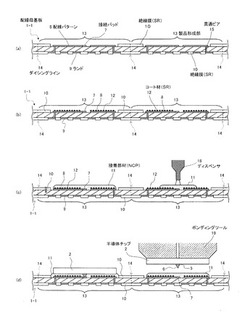

【図1】本発明の第一実施例による半導体装置の組立工程の様子を示した断面図。

【図2】図1の(a)の段階における半導体基板の製品形成部の平面図。

【図3】本発明の第一実施例による半導体装置の組立工程の様子を示した断面図。

【図4】本発明の第一実施例による半導体装置の組立工程の様子を示した断面図。

【図5】本発明の第二実施例による半導体装置の組立工程の様子を示した断面図。

【図6】本発明の第二実施例による半導体装置の組立工程の様子を示した断面図。

【図7】本発明の第二実施例による半導体装置の組立工程の様子を示した断面図。

【図8】本発明の第三実施例による半導体装置の製造方法を示す平面図。

【図9】本発明の第三実施例による半導体装置の製造方法を示す平面図。

【発明を実施するための形態】

【0018】

(実施例1)

図1、図3及び図4は、本発明の第一実施例による半導体装置の組立工程の様子を断面図で示している。図2は図1の(a)の段階における半導体基板の製品形成部の平面図を示している。

【0019】

まず、本実施例で製造される半導体装置について説明する。完成した半導体装置は、図4(c)に示されているとおり、配線基板1と、配線基板1の第一面に搭載された半導体チップ2と、配線基板1の第一面側において半導体チップ2を封止する封止樹脂3と、配線基板1の第一面とは反対側の第二面に搭載された外部端子である半田ボール4と、を有する。

【0020】

配線基板1は、基板面内にマトリックス状に区画された複数の製品形成部を有する略矩形の配線基板(以下、配線母基板と呼ぶ。)を製品形成部毎に分割して個片化したものである。

【0021】

半導体チップ2の主面には回路(不図示)が形成され、該回路は該主面の中央領域に複数の電極パッド5を配置している。配線基板1の第一面には、半導体チップ2の電極パッド5がスタッドバンプ6を介して電気接続される接続パッド7を含む配線パターン8が形成されている。一方、配線基板1の第二面には、半田ボール4を搭載するランド9が形成されている。接続パッド7とこれに対応するランド9とは、配線基板1の内部に形成された配線を介して電気的に接続されている。

【0022】

配線基板1の第一面は、半導体チップ2を搭載する領域を取り囲むようにソルダーレジストなどの絶縁膜10で被覆され、配線基板1の第二面のランド9を除いた領域も絶縁膜10で被覆されている。

【0023】

半導体チップ2は、いわゆるフリップチップ実装方式で配線基板1の第一面に電気接続されるとともに、接着部材11を介して配線基板1の第一面に接着されている。

【0024】

接着部材11としては、NCPが用いられる。NCPには通常、エポキシ樹脂が使用される。また、配線基板1の配線パターン8と接着部材11との界面には、ソルダーレジストからなるコート材12が存在する。このコート材12はNCPとの密着力がNCPと配線パターン8の表面との密着力よりも優れたものである。

【0025】

このような態様の半導体装置を製造するため、本願は、以下に説明する材料を用いた作り方を提案する。この方法によれば、従来技術よりも加熱付加に耐えられる製品が得られる。

【0026】

まず、図1(a)に示すような配線母基板1−1が準備される。

【0027】

配線母基板1−1は、基板面内にマトリックス状に区画された複数の製品形成部13(切断後に配線基板1となる部分)を有しており、それぞれの製品形成部13間の境界には、製品形成部13毎に分割する際のダイシングライン14が設けられている。配線母基板1−1は、例えば0.14mm厚のガラスエポキシ配線基板である。配線母基板1−1は、図1(a)に示すように、絶縁基材の上下面に所定の配線パターン8を形成し、配線パターン8を部分的に絶縁膜10、例えばソルダーレジストで被覆してなる。

【0028】

それぞれの製品形成部13について言うと、図2に示すように、配線基板1の第一面側の絶縁膜(ソルダーレジスト)10には、半導体チップが搭載される領域(以下、チップ搭載領域と称す)Xに対応して開口部10aが形成されている。開口部10aからは、複数の接続パッド7と、各接続パッド7に繋がった配線パターン8が露出されている。また、配線基板1の第二面側の絶縁膜(ソルダーレジスト)10から露出された部位にはランド9が配置されている。ランド9は配線基板1の第二面側に格子状に配置されている。

【0029】

接続パッド7とこれに対応するランド9とは、それぞれ配線パターン8および貫通ビア15により電気的に接続されている。配線パターン8は、例えばCuの導体層から構成されており、この導体層の表面にはNi/Auのメッキ層が形成されている。

【0030】

上記のような配線母基板1−1を用意した後、図3(a)に示すように、配線母基板1−1の、接続パッド7が形成されている側の面にマスク16を配置する。マスク16には、絶縁膜10の開口部10aに対応して開口16aが形成されている。開口16aは、絶縁膜10の開口部10a内の配線パターン6を露出するように形成されているが、接続パッド7はマスク16の一部によって覆われている。

【0031】

そして、図3(b)に示すように、マスク16の開口16aと絶縁膜10の開口部10aの両方から露出された領域に、例えばスプレーディスペンサのような噴射機構17によって、フィラーを含むソルダーレジストからなるコート材12をまばらに吹き付ける。いわゆるスプレーコート法が採用される。コート材12の層の厚さは絶縁膜(ソルダーレジスト)10の厚さより薄くされている。

【0032】

このコート材12としては、所定の大きさ、例えば10μm以上の粒径のフィラーが除去されたソルダーレジストが使用される。ソルダーレジストに含まれているフィラーの粒径が所定の大きさ以下になるように、例えばメッシュ材料で該ソルダーレジストを漉すことで、所定の大きさ以上のフィラーを除去する。

【0033】

これにより、所定の大きさ以上のフィラーはソルダーレジスト内に混在しなくなるとともに、ソルダーレジスト内のフィラー粒径のばらつきも低減できる。コート材12に含まれるフィラーの粒径を、フリップチップ実装時の配線基板と半導体チップとの間隔より小さいものに制限できるため、フリップチップ実装時にコート材12が半導体チップと接触するリスクを低減できる。なお、上記の「粒径」とは、ふるい分け法によって測定したふるいの目開きで表したものをいう。

【0034】

その後、図3(c)に示すように、マスク16を配線母基板1−1から除去し、コート材12が塗布された配線母基板1−1を所定温度、例えば120〜150℃程度でベークし、コート材12の層を硬化させる。このコート材12のベークは、フリップチップ実装前の配線母基板1−1のプリベークを兼ねるように実施されても良い。

【0035】

これにより、図1(b)に示すように、配線母基板1−1の接続パッド7が形成されている側の面において、接続パッド7を除いて配線パターン8の表面にコート材12が付与されたものが出来る。

【0036】

次に、図1(c)に示すように、ディスペンサ18で配線母基板1−1の各々の製品形成部13に、絶縁性の接着部材11、例えばエポキシ樹脂からなるNCPを供給する。これにより、各製品形成部13のチップ搭載領域XにNCPが塗布される。

【0037】

次に、図1(d)に示すように、第一面に所定の回路、例えばメモリ回路が形成されて、その第一面の電極パッド5にスタッドバンプ6が形成された半導体チップ2が準備される。そして、例えば300℃程度の高温に加熱されたボンディングツール19により、半導体チップ2の第一面とは反対側の第二面を保持し、半導体チップ2を配線母基板1−1に向けて押し付けることで、製品形成部13に半導体チップ2を搭載する。このようなフリップチップ実装により、半導体チップ2に配設された複数のスタッドバンプ(バンプ電極)6は、配線母基板1−1の複数の接続パッド7にそれぞれ接続される。

【0038】

ここで、コート材12の効果について説明しておく。

【0039】

上述したとおり、配線母基板1−1におけるチップ搭載領域Xの配線パターン8の表面が、例えばNi/Au、またはAuのメッキ層で形成されている場合がある。この表面の材質は、NCPとガラスエポキシ配線基板との密着力に比べてNCPとの密着力が劣る。そこで本発明では、フリップチップ実装前に、そのチップ搭載領域Xの配線パターン8上にコート材12が設けられた。コート材12にはソルダーレジストが使用された。これにより。配線基板1とNCPとの密着性が従来技術よりも向上した。結果、完成した半導体装置への加熱付加時において配線基板1とNCPとの剥離を抑制することができる。

【0040】

例えば、回路面の中央領域に電極パッドが列状に配設されているDRAMチップ等の半導体チップが搭載される配線基板では、該電極パッドに対応する接続パッドが列状に並び、これらの接続パッドに向かって配線パターンが延びるので、Auメッキ配線の密集箇所が出来やすい。このAu密集箇所はチップ搭載領域内でNCPとの密着性が相対的に低い所となる。しかし本願発明では、チップ搭載領域Xの配線パターン8上にソルダーレジストコートを行ったことで、Au密集箇所とNCPとの密着力を増すことができる。

【0041】

さらに本願では、コート材12をチップ搭載領域の配線パターン8上に設ける前に、コート材12に含まれるフィラーの粒径を、メッシュ材を用いて、フリップチップ実装時の配線基板と半導体チップとの間隔より小さいものに制限している。このため、フリップチップ実装の際に半導体チップ2とコート材12とが接触するおそれが無くなる。

【0042】

詳述すると、配線基板1とこの主面に搭載される半導体チップ2との距離は、配線基板主面の接続パッド7に接続する半導体チップ2の電極パッド5上のスタッドバンプ6の高さによって決まる。半導体装置の小型化に伴ってスタッドバンプ6の微細化が進むと、配線基板主面と半導体チップとの距離が狭くなる。こうした傾向では、チップ搭載領域Xの配線パターン8の表面へ塗布するソルダーレジストの厚みを管理しないと、該ソルダーレジストが、フリップチップ実装時に半導体チップ2の回路面と接触してしまう可能性がある。半導体チップの回路面へのソルダーレジストの接触は完成した半導体装置の電気特性に影響を及ぼすおそれがある。このため、コート材12に含まれるフィラー粒径が制限されている。

【0043】

再び、上記半導体装置の製造工程について説明する。

【0044】

前述のように半導体チップ2が実装された配線母基板1−1は、モールド工程に移行される。

【0045】

モールド工程では、図4(a)に示すように、半導体チップ2が搭載された第一面側の複数の製品形成部13を一括的に覆う封止樹脂3が形成される。具体的には、上型と下型からなる成形金型(不図示)を有するトランスファモールド装置などの成型装置を用いてモールド工程が実行される。上型には複数の製品形成部13を一括して覆う大きさのキャビティが形成されており、下型には配線母基板1−1を配置するための凹部が形成されている。半導体チップ2が実装された配線母基板1−1は、下型の凹部にセットされる。そして上型と下型で配線母基板2−1の周縁部をクランプすることで、配線母基板2−1の上方に、上記の大きさのキャビティが形成される。その後、熱硬化性の封止樹脂(例えばエポキシ樹脂)を該キャビティの中へ充填し、所定の温度(例えば180℃)でキュアすることで、封止樹脂が硬化する。その後、封止樹脂3が形成された配線母基板1−1は所定の温度でベークされることで、封止樹脂3が完全に硬化される。

【0046】

次に、封止樹脂3が形成された配線母基板1−1はボールマウント工程に移される。具体的には図4(b)に示すように、配線母基板1−1の第二面の製品形成部13毎に格子状に配置された複数のランド9の上に、導電性の半田ボール4が接合される。ボールマウント工程では、配線母基板1−1上のランド9の配置に合わせて複数の吸着孔が形成されたボールマウンターのマウントツール20が用いられる。具体的には、半田ボール4が前記吸着孔に保持され、フラックスを介して、複数のランド9に一括的に接合される。すべての製品形成部13に半田ボール4が搭載された後、配線母基板1−1のリフローが行われる。

【0047】

その後、配線母基板1−1はダイシング工程に移される。具体的には、図4(c)に示すように、配線母基板1−1の封止樹脂4側にダイシングテープ21が接着される。そして、ダイシング装置のダイシングブレード22により配線母基板1−1を縦横にダイシングライン14に沿って切断することで、各製品形成部13の間が分離される。その後、ダイシングテープ21から各製品形成部13をピックアップすることで、BGA型の半導体装置が得られる。

【0048】

(実施例2)

図5、図6及び図7は、本発明の第二実施例による半導体装置の組立工程の様子を断面図で示している。尚、これらの図において、第一実施例と同じ構成要素には同じ符号を用いている。

【0049】

まず、本実施例で製造される半導体装置について説明する。完成した半導体装置は、図7(c)に示されているとおり、貫通電極26を有する複数の半導体チップ24が積載されたチップ積層体31を有し、チップ積層体31が配線基板1に接続固定された構成である。チップ積層体31は、例えばメモリ回路が形成された4つの半導体チップ24を積載した構成である。

【0050】

半導体チップ24は、回路が形成された一方の面及び回路が形成されない他方の面にそれぞれ複数のバンプ電極25を備え、一方の面のバンプ電極25と他方の面のバンプ電極25とがそれぞれ貫通電極26によって接続されている。各半導体チップ24はバンプ電極25を介して各々の貫通電極26により互いに接続される。

【0051】

上記チップ積層体31は、各半導体チップ24間の隙間を埋めると共に、側面から見た断面が略台形状となる第一の封止樹脂27Aを備えている。第1の封止樹脂27Aは、例えば周知のアンダーフィル材を用いて形成される。

【0052】

上記チップ積層体31の最上段の半導体チップ24上には、第一実施例で説明した構成からなる配線基板1が接続されている。配線基板1は、基板面内にマトリックス状に区画された複数の製品形成部を有する略矩形の配線母基板を製品形成部毎に分割して個片化したものである。配線基板1の詳細な構成については第一実施例で述べたとおりなので割愛する。

【0053】

配線基板1の、チップ積層体31が搭載される面の接続パッド7には、例えばAuやCu等から成るスタッドバンプ6が形成されている。スタッドバンプ6は、最上段の半導体チップ24のバンプ電極25と接続されている。

【0054】

また、上記チップ積層体31と配線基板1とは、NCP等の接着部材11によって接着固定され、接着部材11により、スタッドバンプ6と配線基板1の接続パッド7とを接合した部位が保護されている。

【0055】

配線基板1上のチップ積層体31は第2の封止樹脂27Bによって封止されている。配線基板1の、該チップ積層体31が搭載されない側の面の複数のランド9には、半導体装置1の外部端子となる半田ボール4がそれぞれ接続されている。

【0056】

次に、第二実施例の半導体装置の製造方法について説明する。ここでは、上記チップ積層体の形成工程と、該チップ積層体の配線基板への実装工程およびそれ以降の工程を順番に述べる。

【0057】

図5は、上記チップ積層体の形成工程を示す断面図である。

【0058】

まず、貫通電極26を有する複数の半導体チップ24を準備する。半導体チップ24は、略四角形のSi等からなる板状の半導体基板の一方の面にメモリ回路等の所定の回路が形成された構成である。

【0059】

半導体チップ10は、図5(a)に示す吸着ステージ28上に、所定の回路が形成された一方の面を上方に向けて載置される。そして、半導体チップ10は、吸着ステージ28に設けられた吸着孔28aを介して不図示の真空装置により真空吸引されることで、吸着ステージ28上に固定される

吸着ステージ28上に保持された1段目の半導体チップ24上に、ボンディングツール19を用いて2段目の半導体チップ24を積層する。このとき、例えば300℃程度の高温に加熱されたボンディングツール19により、2段目の半導体チップ24を吸着孔19aを介して保持しながら、1段目の半導体チップ24に向けて押し付ける。このような熱圧着により、上記1段目の半導体チップ24の上面のバンプ電極25と、これに対応する上記2段目の半導体チップ24の下面のバンプ電極25とが電気的に接続される

2段目の半導体チップ10上には、上記と同様の手順で3段目の半導体チップ24を接続固定し、3段目の半導体チップ24上には、上記と同様の手順で4段目の半導体チップ10を接続固定する。このようにそれぞれの半導体チップ24をバンプ電極25で接続することで、半導体チップ24間に隙間が形成される。

【0060】

以上の手順で積層された複数の半導体チップ24は、図5(b)に示すように塗布ステージ29に貼付された塗布用シート30上に載置される。塗布用シート30には、フッ素系シートやシリコーン系接着材が塗布されたシート等のように、第1の封止樹脂27A(例えばアンダーフィル材)に対する濡れ性が悪い材料が用いられる。なお、塗布用シート30は、塗布ステージ29上に直接貼る必要はなく、平坦な面上であればどこでもよく、例えば塗布ステージ29上に載置した所定の治具等に貼ってもよい。

【0061】

塗布用シート30に載置された複数の半導体チップ24からなるチップ積層体31に対し、図5(b)に示すように、チップ積層体31の端部近傍からディスペンサ18により第1の封止樹脂27を供給する。供給されたアンダーフィル材27は、積載された複数の半導体チップ24の周囲にフィレットを形成しつつ、半導体チップ24どうしの隙間へ毛細管現象によって進入し、半導体チップ24間の隙間を埋める。

【0062】

そして、チップ積層体31への第1の封止樹脂27Aの充填が完了した後、塗布用シート30と共にチップ積層体31を所定の温度、例えば150℃程度でキュアすることで、第1の封止樹脂27Aが硬化される。この結果、図5(c)に示すように、チップ積層体31の周囲を覆うと共に半導体チップ24間の隙間を埋めるアンダーフィル材から成る第1の封止樹脂27Aが形成される。このとき、第1の封止樹脂27Aは、チップ積層体31の側面から見た断面が略台形状となる。また本実施例では、第1の封止樹脂27Aに対する濡れ性が悪い材料からなる塗布用シート30を用いるため、熱硬化時における塗布用シート30へのアンダーフィル材27の付着が防止される。

【0063】

第1の封止樹脂27Aの熱硬化後、該第1の封止樹脂27Aを含むチップ積層体31は、塗布用シート30からピックアップされる。本実施例では、第1の封止樹脂27Aに対する濡れ性が悪い材料からなる塗布用シート30を用いるため、チップ積層体31を塗布用シート30から容易にピックアップできる。

【0064】

さらに、上記チップ積層体31の配線基板1への実装工程、ならびに、それ以降の工程を説明していく。

【0065】

図6は上記チップ積層体31の配線基板1への実装工程を示す断面図であり、図7は、該実装工程以降の工程を示す断面図である。

【0066】

まず、図6(a)に示すような配線母基板1−1が準備される。この配線母基板1−1の構成は、上述した第一実施例において図1(a)に基づいて説明したとおりである。

【0067】

次いで、第一実施例と同様、図6(b)に示すように、配線母基板1−1の接続パッド7が形成されている側の面におけるチップ搭載領域であって、接続パッド7を除いた領域に、例えばスプレーディスペンサによりソルダーレジストからなるコート材12をまばらに噴射する(図3(a)〜(c)参照)。これにより、該チップ搭載領域に接続パッド7を除いてコート材12を吹き付けた配線母基板1−1が出来る。コート材12の態様および効果は第一実施例と同じである。

【0068】

次に、図6(c)に示すように、配線母基板1−1のそれぞれの製品形成部13の接続パッド7上に、スタッドバンプ6を形成する。

【0069】

スタッドバンプ6は、図示しないワイヤボンディング装置を用いて、溶融して先端がボール状となったAuやCu等のワイヤを配線母基板1−1の接続パッド7上に、例えば超音波熱圧着法で接続し、その後、該ワイヤの後端を引き切ることで形成される。

【0070】

尚、スタッドバンプ6は接続パッド7に凸状に形成されるため、該スタッドバンプを介して配線母基板1−1に接続されるチップ積層体31のバンプ電極25及び貫通電極16を小径化することができる。さらに、貫通電極16の小径化により、半導体チップ24に関する、貫通電極16を基点としたクラックの発生を抑制できる。

【0071】

次に、図6(d)に示すように、ディスペンサ18で配線母基板1−1の各々の製品形成部13に、絶縁性の接着部材11、例えばエポキシ樹脂のNCPを供給する。これにより、各製品形成部13のチップ搭載領域にNCPが塗布される。

【0072】

その後、接着部材11が塗布された配線母基板1−1のそれぞれの製品形成部13に、チップ積層体31が実装される。このとき、図6(e)に示すように、チップ積層体31はボンディングツール19によって吸着保持され、ボンディングツール19の加熱機構により、チップ積層体31が所定の温度(例えば300℃)まで加熱される。そして、ボンディングツール19が下降して、チップ積層体31の、ボンディングツール19とは反対側に位置する最下段の半導体チップ24が、配線母基板1−1に対して押し付けられることで、製品形成部13にチップ積層体31が実装される。この実装時に、配線母基板1の接続パッド7上に設けられたスタッドバンプ(バンプ電極)6が、チップ積層体31の最端の半導体チップ24上のバンプ電極25と接続される。

【0073】

このようなチップ積層体31と配線母基板1−1との接合により、接着部材11が広がり、チップ積層体31と配線母基板1−1との間に充填される。なお、前述したようにチップ積層体31は第一の封止樹脂27Aのために側面から見た断面が略台形状となっており、このチップ積層体31を配線母基板1−1に接合するとき、台形状の側断面を持ったチップ積層体31の側断面が狭くなっていく側の端部が、配線母基板1−1の絶縁膜10の開口部内に配置される。そのため、チップ積層体31の第一の封止樹脂27Aと配線母基板1−1の絶縁膜10とが干渉することなく、チップ積層体31と配線母基板1−1とを良好に接続することができる。

【0074】

また第一実施例と同様、チップ積層体31を配線母基板1−1に接合する前に、そのチップ積層体31が搭載される領域の配線パターン8上にコート材12が設けられた。これにより。配線基板1とNCPとの密着性が従来技術よりも向上した。結果、完成した半導体装置への加熱付加時において配線基板1とNCPとの剥離を抑制することができる。

【0075】

さらに第一実施例と同様、コート材12を配線パターン8上に設ける前に、コート材12に含まれるフィラーの粒径を、メッシュ材を用いて、接合後の配線基板1とチップ積層体31との間隔より小さいものに制限している。このため、チップ積層体31を配線基板1に接合した際に、チップ積層体31の最下段の半導体チップ24とコート材12とが接触するおそれが無くなる。

【0076】

次に、チップ積層体31が実装された配線母基板1−1は、モールド工程に移行される。

【0077】

モールド工程では、図7(a)に示すように、チップ積層体31が実装された第一面側の複数の製品形成部13を一括的に覆う第二の封止樹脂27Bが形成される。具体的には、第一実施例と同様、上型と下型からなる成形金型(不図示)を有するトランスファモールド装置などの成型装置を用いてモールド工程が実行される。上型には、チップ積層体31が実装された複数の製品形成部13を一括して覆う大きさのキャビティが形成されており、下型には配線母基板1−1を配置するための凹部が形成されている。チップ積層体31が実装された配線母基板1−1は、下型の凹部にセットされる。そして上型と下型で配線母基板2−1の周縁部をクランプすることで、配線母基板2−1の上方に、上記の大きさのキャビティが形成される。その後、熱硬化性の封止樹脂(例えばエポキシ樹脂)を該キャビティの中へ充填し、所定の温度(例えば180℃)でキュアすることで、封止樹脂が硬化する。その後、封止樹脂27Bが形成された配線母基板1−1は所定の温度でベークされることで、封止樹脂27Bが完全に硬化される。

【0078】

次に、第二の封止樹脂27Bが形成された配線母基板1−1はボールマウント工程に移される。具体的には図7(b)に示すように、配線母基板1−1の第二面の製品形成部13毎に格子状に配置された複数のランド9の上に、導電性の半田ボール4が接合される。ボールマウント工程では、第一実施例と同様、配線母基板1−1上のランド9の配置に合わせて複数の吸着孔が形成されたボールマウンターのマウントツール20が用いられる。

【0079】

その後、半田ボール4が搭載された配線母基板1−1はダイシング工程に移される。具体的には、図7(c)に示すように、配線母基板1−1の封止樹脂27B側にダイシングテープ21が接着される。そして、ダイシング装置のダイシングブレード22により配線母基板1−1を縦横にダイシングライン14に沿って切断することで、各製品形成部13の間が分離される。以上により、CoC(Chip on Chip)型の半導体装置が得られる。

【0080】

(実施例3)

図8及び図9は、第三実施例による半導体装置の製造方法を示す平面図である。これらの図では上述した実施例と同じ構成要素には同一の符号を用いている。

【0081】

上記第一及び第二実施例では、図2に示したように、半導体チップ2又はチップ積層体31が搭載される領域、すなわち絶縁膜10の開口部10aの内側領域に、貫通ビア15、接続パッド7および配線パターン8だけが設けられた配線基板が使用されていた。

【0082】

本実施例では、配線基板1の基板材料、配線材料、絶縁膜材料等は同じであるが、図8に示すように、絶縁膜10の開口部10aの内側領域の基板面に形成された配線パターン8の間の領域に、ダミーパターン32が形成されている。このダミーパターン32は、配線基板1の基材表面において配線パターン8の有る領域と無い領域とのバランスを取り、配線基板1の反りの発生を抑制するために設けられる。このようなダミーパターン32を有する配線基板1を本願発明の製造方法に適用する場合は次のような手法を採ることが好ましい。

【0083】

すなわち、本実施例においては、図9(a)に示すように、絶縁膜(ソルダーレジスト)10の開口部10aの内側領域の基板面を所定の単位エリア33、例えば1mm2毎に区切って、単位エリア33に対する配線の比率[%/mm2]がそれぞれ測定される。言い換えれば、1mm2当りのAu導体の割合が測定される。

【0084】

そして、それぞれの単位エリア33を測定した後、例えば、図9(b)に示すような配線の比率が、70%/mm2以上の単位エリア(図では、配線パターン及びダミーパターンがグレー色で塗り潰された単位エリア34)に対して、スプレーディスペンサによりソルダーレジストのコート材12を供給する。

【0085】

本実施例は、第一実施例と同様なコート材の効果が得られると共に、配線基板1における導体パターン密度の高い単位エリアに選択的にコート材12を供給することで、半導体チップ2と配線基板1とが接触するリスクを確実にかつ効率よく低減することができる。

【0086】

以上、本発明者によってなされた発明を実施例に基づき説明したが、本発明は前述した各実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。例えば、第二実施例では4つのメモリチップを積層したチップ積層体について説明したが、フリップチップ実装方式で半導体チップを配線基板に接続する態様の半導体装置であれば、本願発明はどのような構造体のチップに適用されても良い。また半導体チップの積層数も4段に限らず、3段以下又は6段以上でも良い。

【0087】

また各実施例では、半導体チップの中央領域にバンプ電極を形成した場合について説明したが、半導体チップのパンプ電極がどのような位置に形成されていても本発明を適用可能である。

【符号の説明】

【0088】

1 配線基板

1−1 配線母基板

2 半導体チップ

3 封止樹脂

4 半田ボール

5 電極パッド

6 スタッドバンプ

7 接続パッド

8 配線パターン

9 ランド

10 絶縁膜

10a 開口部

11 NCP(非導電ペースト)

12 コート材

13 製品形成部

14 ダイシングライン

15 貫通ビア

16 マスク

16a マスクの開口

17 噴射機構

18 ディスペンサ

19 ボンディングツール

20 マウントツール

21 ダイシングテープ

22 ダイシングブレード

24 半導体チップ

25 バンプ

26 貫通電極

27A 第1の封止樹脂

27B 第2の封止樹脂

28 吸着ステージ

28a 吸着穴

29 塗布ステージ

30 塗布用シート

31 チップ積層体

32 ダミーパターン

33 単位エリア

34 導体パターン密度の高い単位エリア

【技術分野】

【0001】

本発明は、配線が形成された配線基板の主面に非導電性接着材を介して半導体チップをフリップチップ実装方式で搭載してなる半導体装置の製造方法に関する。

【背景技術】

【0002】

主面に、半導体チップの電極パッドが接続される接続パッドを含む配線パターンが形成された配線基板を用意し、該配線基板の主面に半導体チップをフリップチップ実装方式で搭載する半導体装置の製造方法が知られている。この半導体装置の製造方法に関して、特許文献1には、半導体チップが搭載される側の面に該半導体チップが搭載される領域を取り囲むようにソルダーレジストが形成されている配線基板を用いて、フリップチップ実装を行う技術が開示されている。

【0003】

このような配線基板のチップ搭載領域には接続パッドの他に配線が露出されているため、配線基板のチップ搭載領域と半導体チップとの間にNCP(Non Conductive Paste)を配することがよくある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平09−82760号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

上記の配線基板に搭載される半導体チップが、メモリチップのように、該半導体チップの主面の中央領域に複数の電極パッドが配列されたものである場合には、該半導体チップの中央領域の電極パッドに対応して、配線基板上の接続パッドも中央領域に列状に配置される。このため、配線基板のチップ搭載領域の配線パターンは配線基板中央領域の接続パッドに向かって延びることとなり、チップ搭載領域内で配線が密集する領域が出来るという問題がある。

【0006】

また、配線パターンは一般に、Cu層にNi/Auのメッキ層が形成されている。このため、配線基板のチップ搭載領域と半導体チップとの間に配されたNCPに接触する面がAuとなる。NCPとAuの密着力はNCPと配線基板材料の密着力に比べて劣っている。なお、「密着力」とは、接着した2つの部材間の密着状態を維持するのに必要な力をいい、密着力が小さいほど2つの部材間が剥がれやすくなる。

【0007】

以上の事から、配線基板におけるNCPの塗布面積に対してAuメッキ配線の占有率が高くなればなるほど、半導体装置の信頼性試験などでの高温付加時に、配線が密集する領域のNCPとAuの界面で剥離が発生するおそれがある。

【0008】

このようなNCPの剥離は半導体装置の信頼性を低下させる。

【課題を解決するための手段】

【0009】

本発明による半導体装置の製造方法の一つの態様は、以下の工程を含む。

【0010】

まず、半導体チップを搭載するための配線基板であり、少なくとも片面に、該半導体チップを搭載する領域に対応させた開口部を有する絶縁膜が形成され、該開口部が、該半導体チップの主面の電極パッドが接続される接続パッドと該接続パッドに繋がる配線パターンとを露出させている、配線基板を用意する。

【0011】

続いて、上記の開口部内の接続パッドを除いた場所にある、配線パターンの表面にコート材層を形成する。このコート材は、非導電性ペースト(NCP)に対する密着力が該非導電性ペーストと前記配線パターンの表面との密着力よりも優れたものである。

【0012】

さらに、上記の開口部の、半導体チップを搭載する領域全体に、前記非導電性ペーストを塗布する。

【0013】

その後、フリップチップ実装方式で半導体チップの電極パッドと配線基板の接続パッドとを電気接続しながら、半導体チップを配線基板に非導電性ペーストを介して接合する。

【0014】

このような製造方法によれば、フリップチップ実装前に、配線基板におけるチップ搭載領域の配線パターンの表面に上記のコート材層(例えばソルダーレジスト)を設けたことにより、配線基板とNCPとの密着力が従来技術よりも向上する。結果、完成した半導体装置への加熱付加時において配線基板とNCPとの剥離を抑制することができる。

【0015】

さらに詳述すると、例えばガラスエポキシ配線基板におけるチップ搭載領域の配線パターンの表面が、Auのメッキ層で形成されている場合がある。この表面の材質は、NCPとガラスエポキシ配線基板との密着力に比べてNCPとの密着力が劣る。また、回路面の中央領域に電極パッドが列状に配設されているDRAMチップ等の半導体チップが搭載される配線基板では、該電極パッドに対応する接続パッドが列状に並び、これらの接続パッドに向かって配線パターンが延びるので、Auメッキ配線の密集箇所が出来やすい。このAu密集箇所はチップ搭載領域内でNCPとの密着性が相対的に低い所となる。以上の事を踏まえて、フリップチップ実装前に、チップ搭載領域の配線パターン上にソルダーレジストのコート材を付与しておくと、Au密集箇所とNCPとの密着力を増すことができる。

【発明の効果】

【0016】

したがって、本発明によれば、フリップチップ実装方式で配線基板上に電気接続された半導体チップとその配線基板との間に非導電性ペースト(NCP)を配した態様の半導体装置に関して、NCPと配線基板の密着力が従来よりも高いものを提供することができる。

【図面の簡単な説明】

【0017】

【図1】本発明の第一実施例による半導体装置の組立工程の様子を示した断面図。

【図2】図1の(a)の段階における半導体基板の製品形成部の平面図。

【図3】本発明の第一実施例による半導体装置の組立工程の様子を示した断面図。

【図4】本発明の第一実施例による半導体装置の組立工程の様子を示した断面図。

【図5】本発明の第二実施例による半導体装置の組立工程の様子を示した断面図。

【図6】本発明の第二実施例による半導体装置の組立工程の様子を示した断面図。

【図7】本発明の第二実施例による半導体装置の組立工程の様子を示した断面図。

【図8】本発明の第三実施例による半導体装置の製造方法を示す平面図。

【図9】本発明の第三実施例による半導体装置の製造方法を示す平面図。

【発明を実施するための形態】

【0018】

(実施例1)

図1、図3及び図4は、本発明の第一実施例による半導体装置の組立工程の様子を断面図で示している。図2は図1の(a)の段階における半導体基板の製品形成部の平面図を示している。

【0019】

まず、本実施例で製造される半導体装置について説明する。完成した半導体装置は、図4(c)に示されているとおり、配線基板1と、配線基板1の第一面に搭載された半導体チップ2と、配線基板1の第一面側において半導体チップ2を封止する封止樹脂3と、配線基板1の第一面とは反対側の第二面に搭載された外部端子である半田ボール4と、を有する。

【0020】

配線基板1は、基板面内にマトリックス状に区画された複数の製品形成部を有する略矩形の配線基板(以下、配線母基板と呼ぶ。)を製品形成部毎に分割して個片化したものである。

【0021】

半導体チップ2の主面には回路(不図示)が形成され、該回路は該主面の中央領域に複数の電極パッド5を配置している。配線基板1の第一面には、半導体チップ2の電極パッド5がスタッドバンプ6を介して電気接続される接続パッド7を含む配線パターン8が形成されている。一方、配線基板1の第二面には、半田ボール4を搭載するランド9が形成されている。接続パッド7とこれに対応するランド9とは、配線基板1の内部に形成された配線を介して電気的に接続されている。

【0022】

配線基板1の第一面は、半導体チップ2を搭載する領域を取り囲むようにソルダーレジストなどの絶縁膜10で被覆され、配線基板1の第二面のランド9を除いた領域も絶縁膜10で被覆されている。

【0023】

半導体チップ2は、いわゆるフリップチップ実装方式で配線基板1の第一面に電気接続されるとともに、接着部材11を介して配線基板1の第一面に接着されている。

【0024】

接着部材11としては、NCPが用いられる。NCPには通常、エポキシ樹脂が使用される。また、配線基板1の配線パターン8と接着部材11との界面には、ソルダーレジストからなるコート材12が存在する。このコート材12はNCPとの密着力がNCPと配線パターン8の表面との密着力よりも優れたものである。

【0025】

このような態様の半導体装置を製造するため、本願は、以下に説明する材料を用いた作り方を提案する。この方法によれば、従来技術よりも加熱付加に耐えられる製品が得られる。

【0026】

まず、図1(a)に示すような配線母基板1−1が準備される。

【0027】

配線母基板1−1は、基板面内にマトリックス状に区画された複数の製品形成部13(切断後に配線基板1となる部分)を有しており、それぞれの製品形成部13間の境界には、製品形成部13毎に分割する際のダイシングライン14が設けられている。配線母基板1−1は、例えば0.14mm厚のガラスエポキシ配線基板である。配線母基板1−1は、図1(a)に示すように、絶縁基材の上下面に所定の配線パターン8を形成し、配線パターン8を部分的に絶縁膜10、例えばソルダーレジストで被覆してなる。

【0028】

それぞれの製品形成部13について言うと、図2に示すように、配線基板1の第一面側の絶縁膜(ソルダーレジスト)10には、半導体チップが搭載される領域(以下、チップ搭載領域と称す)Xに対応して開口部10aが形成されている。開口部10aからは、複数の接続パッド7と、各接続パッド7に繋がった配線パターン8が露出されている。また、配線基板1の第二面側の絶縁膜(ソルダーレジスト)10から露出された部位にはランド9が配置されている。ランド9は配線基板1の第二面側に格子状に配置されている。

【0029】

接続パッド7とこれに対応するランド9とは、それぞれ配線パターン8および貫通ビア15により電気的に接続されている。配線パターン8は、例えばCuの導体層から構成されており、この導体層の表面にはNi/Auのメッキ層が形成されている。

【0030】

上記のような配線母基板1−1を用意した後、図3(a)に示すように、配線母基板1−1の、接続パッド7が形成されている側の面にマスク16を配置する。マスク16には、絶縁膜10の開口部10aに対応して開口16aが形成されている。開口16aは、絶縁膜10の開口部10a内の配線パターン6を露出するように形成されているが、接続パッド7はマスク16の一部によって覆われている。

【0031】

そして、図3(b)に示すように、マスク16の開口16aと絶縁膜10の開口部10aの両方から露出された領域に、例えばスプレーディスペンサのような噴射機構17によって、フィラーを含むソルダーレジストからなるコート材12をまばらに吹き付ける。いわゆるスプレーコート法が採用される。コート材12の層の厚さは絶縁膜(ソルダーレジスト)10の厚さより薄くされている。

【0032】

このコート材12としては、所定の大きさ、例えば10μm以上の粒径のフィラーが除去されたソルダーレジストが使用される。ソルダーレジストに含まれているフィラーの粒径が所定の大きさ以下になるように、例えばメッシュ材料で該ソルダーレジストを漉すことで、所定の大きさ以上のフィラーを除去する。

【0033】

これにより、所定の大きさ以上のフィラーはソルダーレジスト内に混在しなくなるとともに、ソルダーレジスト内のフィラー粒径のばらつきも低減できる。コート材12に含まれるフィラーの粒径を、フリップチップ実装時の配線基板と半導体チップとの間隔より小さいものに制限できるため、フリップチップ実装時にコート材12が半導体チップと接触するリスクを低減できる。なお、上記の「粒径」とは、ふるい分け法によって測定したふるいの目開きで表したものをいう。

【0034】

その後、図3(c)に示すように、マスク16を配線母基板1−1から除去し、コート材12が塗布された配線母基板1−1を所定温度、例えば120〜150℃程度でベークし、コート材12の層を硬化させる。このコート材12のベークは、フリップチップ実装前の配線母基板1−1のプリベークを兼ねるように実施されても良い。

【0035】

これにより、図1(b)に示すように、配線母基板1−1の接続パッド7が形成されている側の面において、接続パッド7を除いて配線パターン8の表面にコート材12が付与されたものが出来る。

【0036】

次に、図1(c)に示すように、ディスペンサ18で配線母基板1−1の各々の製品形成部13に、絶縁性の接着部材11、例えばエポキシ樹脂からなるNCPを供給する。これにより、各製品形成部13のチップ搭載領域XにNCPが塗布される。

【0037】

次に、図1(d)に示すように、第一面に所定の回路、例えばメモリ回路が形成されて、その第一面の電極パッド5にスタッドバンプ6が形成された半導体チップ2が準備される。そして、例えば300℃程度の高温に加熱されたボンディングツール19により、半導体チップ2の第一面とは反対側の第二面を保持し、半導体チップ2を配線母基板1−1に向けて押し付けることで、製品形成部13に半導体チップ2を搭載する。このようなフリップチップ実装により、半導体チップ2に配設された複数のスタッドバンプ(バンプ電極)6は、配線母基板1−1の複数の接続パッド7にそれぞれ接続される。

【0038】

ここで、コート材12の効果について説明しておく。

【0039】

上述したとおり、配線母基板1−1におけるチップ搭載領域Xの配線パターン8の表面が、例えばNi/Au、またはAuのメッキ層で形成されている場合がある。この表面の材質は、NCPとガラスエポキシ配線基板との密着力に比べてNCPとの密着力が劣る。そこで本発明では、フリップチップ実装前に、そのチップ搭載領域Xの配線パターン8上にコート材12が設けられた。コート材12にはソルダーレジストが使用された。これにより。配線基板1とNCPとの密着性が従来技術よりも向上した。結果、完成した半導体装置への加熱付加時において配線基板1とNCPとの剥離を抑制することができる。

【0040】

例えば、回路面の中央領域に電極パッドが列状に配設されているDRAMチップ等の半導体チップが搭載される配線基板では、該電極パッドに対応する接続パッドが列状に並び、これらの接続パッドに向かって配線パターンが延びるので、Auメッキ配線の密集箇所が出来やすい。このAu密集箇所はチップ搭載領域内でNCPとの密着性が相対的に低い所となる。しかし本願発明では、チップ搭載領域Xの配線パターン8上にソルダーレジストコートを行ったことで、Au密集箇所とNCPとの密着力を増すことができる。

【0041】

さらに本願では、コート材12をチップ搭載領域の配線パターン8上に設ける前に、コート材12に含まれるフィラーの粒径を、メッシュ材を用いて、フリップチップ実装時の配線基板と半導体チップとの間隔より小さいものに制限している。このため、フリップチップ実装の際に半導体チップ2とコート材12とが接触するおそれが無くなる。

【0042】

詳述すると、配線基板1とこの主面に搭載される半導体チップ2との距離は、配線基板主面の接続パッド7に接続する半導体チップ2の電極パッド5上のスタッドバンプ6の高さによって決まる。半導体装置の小型化に伴ってスタッドバンプ6の微細化が進むと、配線基板主面と半導体チップとの距離が狭くなる。こうした傾向では、チップ搭載領域Xの配線パターン8の表面へ塗布するソルダーレジストの厚みを管理しないと、該ソルダーレジストが、フリップチップ実装時に半導体チップ2の回路面と接触してしまう可能性がある。半導体チップの回路面へのソルダーレジストの接触は完成した半導体装置の電気特性に影響を及ぼすおそれがある。このため、コート材12に含まれるフィラー粒径が制限されている。

【0043】

再び、上記半導体装置の製造工程について説明する。

【0044】

前述のように半導体チップ2が実装された配線母基板1−1は、モールド工程に移行される。

【0045】

モールド工程では、図4(a)に示すように、半導体チップ2が搭載された第一面側の複数の製品形成部13を一括的に覆う封止樹脂3が形成される。具体的には、上型と下型からなる成形金型(不図示)を有するトランスファモールド装置などの成型装置を用いてモールド工程が実行される。上型には複数の製品形成部13を一括して覆う大きさのキャビティが形成されており、下型には配線母基板1−1を配置するための凹部が形成されている。半導体チップ2が実装された配線母基板1−1は、下型の凹部にセットされる。そして上型と下型で配線母基板2−1の周縁部をクランプすることで、配線母基板2−1の上方に、上記の大きさのキャビティが形成される。その後、熱硬化性の封止樹脂(例えばエポキシ樹脂)を該キャビティの中へ充填し、所定の温度(例えば180℃)でキュアすることで、封止樹脂が硬化する。その後、封止樹脂3が形成された配線母基板1−1は所定の温度でベークされることで、封止樹脂3が完全に硬化される。

【0046】

次に、封止樹脂3が形成された配線母基板1−1はボールマウント工程に移される。具体的には図4(b)に示すように、配線母基板1−1の第二面の製品形成部13毎に格子状に配置された複数のランド9の上に、導電性の半田ボール4が接合される。ボールマウント工程では、配線母基板1−1上のランド9の配置に合わせて複数の吸着孔が形成されたボールマウンターのマウントツール20が用いられる。具体的には、半田ボール4が前記吸着孔に保持され、フラックスを介して、複数のランド9に一括的に接合される。すべての製品形成部13に半田ボール4が搭載された後、配線母基板1−1のリフローが行われる。

【0047】

その後、配線母基板1−1はダイシング工程に移される。具体的には、図4(c)に示すように、配線母基板1−1の封止樹脂4側にダイシングテープ21が接着される。そして、ダイシング装置のダイシングブレード22により配線母基板1−1を縦横にダイシングライン14に沿って切断することで、各製品形成部13の間が分離される。その後、ダイシングテープ21から各製品形成部13をピックアップすることで、BGA型の半導体装置が得られる。

【0048】

(実施例2)

図5、図6及び図7は、本発明の第二実施例による半導体装置の組立工程の様子を断面図で示している。尚、これらの図において、第一実施例と同じ構成要素には同じ符号を用いている。

【0049】

まず、本実施例で製造される半導体装置について説明する。完成した半導体装置は、図7(c)に示されているとおり、貫通電極26を有する複数の半導体チップ24が積載されたチップ積層体31を有し、チップ積層体31が配線基板1に接続固定された構成である。チップ積層体31は、例えばメモリ回路が形成された4つの半導体チップ24を積載した構成である。

【0050】

半導体チップ24は、回路が形成された一方の面及び回路が形成されない他方の面にそれぞれ複数のバンプ電極25を備え、一方の面のバンプ電極25と他方の面のバンプ電極25とがそれぞれ貫通電極26によって接続されている。各半導体チップ24はバンプ電極25を介して各々の貫通電極26により互いに接続される。

【0051】

上記チップ積層体31は、各半導体チップ24間の隙間を埋めると共に、側面から見た断面が略台形状となる第一の封止樹脂27Aを備えている。第1の封止樹脂27Aは、例えば周知のアンダーフィル材を用いて形成される。

【0052】

上記チップ積層体31の最上段の半導体チップ24上には、第一実施例で説明した構成からなる配線基板1が接続されている。配線基板1は、基板面内にマトリックス状に区画された複数の製品形成部を有する略矩形の配線母基板を製品形成部毎に分割して個片化したものである。配線基板1の詳細な構成については第一実施例で述べたとおりなので割愛する。

【0053】

配線基板1の、チップ積層体31が搭載される面の接続パッド7には、例えばAuやCu等から成るスタッドバンプ6が形成されている。スタッドバンプ6は、最上段の半導体チップ24のバンプ電極25と接続されている。

【0054】

また、上記チップ積層体31と配線基板1とは、NCP等の接着部材11によって接着固定され、接着部材11により、スタッドバンプ6と配線基板1の接続パッド7とを接合した部位が保護されている。

【0055】

配線基板1上のチップ積層体31は第2の封止樹脂27Bによって封止されている。配線基板1の、該チップ積層体31が搭載されない側の面の複数のランド9には、半導体装置1の外部端子となる半田ボール4がそれぞれ接続されている。

【0056】

次に、第二実施例の半導体装置の製造方法について説明する。ここでは、上記チップ積層体の形成工程と、該チップ積層体の配線基板への実装工程およびそれ以降の工程を順番に述べる。

【0057】

図5は、上記チップ積層体の形成工程を示す断面図である。

【0058】

まず、貫通電極26を有する複数の半導体チップ24を準備する。半導体チップ24は、略四角形のSi等からなる板状の半導体基板の一方の面にメモリ回路等の所定の回路が形成された構成である。

【0059】

半導体チップ10は、図5(a)に示す吸着ステージ28上に、所定の回路が形成された一方の面を上方に向けて載置される。そして、半導体チップ10は、吸着ステージ28に設けられた吸着孔28aを介して不図示の真空装置により真空吸引されることで、吸着ステージ28上に固定される

吸着ステージ28上に保持された1段目の半導体チップ24上に、ボンディングツール19を用いて2段目の半導体チップ24を積層する。このとき、例えば300℃程度の高温に加熱されたボンディングツール19により、2段目の半導体チップ24を吸着孔19aを介して保持しながら、1段目の半導体チップ24に向けて押し付ける。このような熱圧着により、上記1段目の半導体チップ24の上面のバンプ電極25と、これに対応する上記2段目の半導体チップ24の下面のバンプ電極25とが電気的に接続される

2段目の半導体チップ10上には、上記と同様の手順で3段目の半導体チップ24を接続固定し、3段目の半導体チップ24上には、上記と同様の手順で4段目の半導体チップ10を接続固定する。このようにそれぞれの半導体チップ24をバンプ電極25で接続することで、半導体チップ24間に隙間が形成される。

【0060】

以上の手順で積層された複数の半導体チップ24は、図5(b)に示すように塗布ステージ29に貼付された塗布用シート30上に載置される。塗布用シート30には、フッ素系シートやシリコーン系接着材が塗布されたシート等のように、第1の封止樹脂27A(例えばアンダーフィル材)に対する濡れ性が悪い材料が用いられる。なお、塗布用シート30は、塗布ステージ29上に直接貼る必要はなく、平坦な面上であればどこでもよく、例えば塗布ステージ29上に載置した所定の治具等に貼ってもよい。

【0061】

塗布用シート30に載置された複数の半導体チップ24からなるチップ積層体31に対し、図5(b)に示すように、チップ積層体31の端部近傍からディスペンサ18により第1の封止樹脂27を供給する。供給されたアンダーフィル材27は、積載された複数の半導体チップ24の周囲にフィレットを形成しつつ、半導体チップ24どうしの隙間へ毛細管現象によって進入し、半導体チップ24間の隙間を埋める。

【0062】

そして、チップ積層体31への第1の封止樹脂27Aの充填が完了した後、塗布用シート30と共にチップ積層体31を所定の温度、例えば150℃程度でキュアすることで、第1の封止樹脂27Aが硬化される。この結果、図5(c)に示すように、チップ積層体31の周囲を覆うと共に半導体チップ24間の隙間を埋めるアンダーフィル材から成る第1の封止樹脂27Aが形成される。このとき、第1の封止樹脂27Aは、チップ積層体31の側面から見た断面が略台形状となる。また本実施例では、第1の封止樹脂27Aに対する濡れ性が悪い材料からなる塗布用シート30を用いるため、熱硬化時における塗布用シート30へのアンダーフィル材27の付着が防止される。

【0063】

第1の封止樹脂27Aの熱硬化後、該第1の封止樹脂27Aを含むチップ積層体31は、塗布用シート30からピックアップされる。本実施例では、第1の封止樹脂27Aに対する濡れ性が悪い材料からなる塗布用シート30を用いるため、チップ積層体31を塗布用シート30から容易にピックアップできる。

【0064】

さらに、上記チップ積層体31の配線基板1への実装工程、ならびに、それ以降の工程を説明していく。

【0065】

図6は上記チップ積層体31の配線基板1への実装工程を示す断面図であり、図7は、該実装工程以降の工程を示す断面図である。

【0066】

まず、図6(a)に示すような配線母基板1−1が準備される。この配線母基板1−1の構成は、上述した第一実施例において図1(a)に基づいて説明したとおりである。

【0067】

次いで、第一実施例と同様、図6(b)に示すように、配線母基板1−1の接続パッド7が形成されている側の面におけるチップ搭載領域であって、接続パッド7を除いた領域に、例えばスプレーディスペンサによりソルダーレジストからなるコート材12をまばらに噴射する(図3(a)〜(c)参照)。これにより、該チップ搭載領域に接続パッド7を除いてコート材12を吹き付けた配線母基板1−1が出来る。コート材12の態様および効果は第一実施例と同じである。

【0068】

次に、図6(c)に示すように、配線母基板1−1のそれぞれの製品形成部13の接続パッド7上に、スタッドバンプ6を形成する。

【0069】

スタッドバンプ6は、図示しないワイヤボンディング装置を用いて、溶融して先端がボール状となったAuやCu等のワイヤを配線母基板1−1の接続パッド7上に、例えば超音波熱圧着法で接続し、その後、該ワイヤの後端を引き切ることで形成される。

【0070】

尚、スタッドバンプ6は接続パッド7に凸状に形成されるため、該スタッドバンプを介して配線母基板1−1に接続されるチップ積層体31のバンプ電極25及び貫通電極16を小径化することができる。さらに、貫通電極16の小径化により、半導体チップ24に関する、貫通電極16を基点としたクラックの発生を抑制できる。

【0071】

次に、図6(d)に示すように、ディスペンサ18で配線母基板1−1の各々の製品形成部13に、絶縁性の接着部材11、例えばエポキシ樹脂のNCPを供給する。これにより、各製品形成部13のチップ搭載領域にNCPが塗布される。

【0072】

その後、接着部材11が塗布された配線母基板1−1のそれぞれの製品形成部13に、チップ積層体31が実装される。このとき、図6(e)に示すように、チップ積層体31はボンディングツール19によって吸着保持され、ボンディングツール19の加熱機構により、チップ積層体31が所定の温度(例えば300℃)まで加熱される。そして、ボンディングツール19が下降して、チップ積層体31の、ボンディングツール19とは反対側に位置する最下段の半導体チップ24が、配線母基板1−1に対して押し付けられることで、製品形成部13にチップ積層体31が実装される。この実装時に、配線母基板1の接続パッド7上に設けられたスタッドバンプ(バンプ電極)6が、チップ積層体31の最端の半導体チップ24上のバンプ電極25と接続される。

【0073】

このようなチップ積層体31と配線母基板1−1との接合により、接着部材11が広がり、チップ積層体31と配線母基板1−1との間に充填される。なお、前述したようにチップ積層体31は第一の封止樹脂27Aのために側面から見た断面が略台形状となっており、このチップ積層体31を配線母基板1−1に接合するとき、台形状の側断面を持ったチップ積層体31の側断面が狭くなっていく側の端部が、配線母基板1−1の絶縁膜10の開口部内に配置される。そのため、チップ積層体31の第一の封止樹脂27Aと配線母基板1−1の絶縁膜10とが干渉することなく、チップ積層体31と配線母基板1−1とを良好に接続することができる。

【0074】

また第一実施例と同様、チップ積層体31を配線母基板1−1に接合する前に、そのチップ積層体31が搭載される領域の配線パターン8上にコート材12が設けられた。これにより。配線基板1とNCPとの密着性が従来技術よりも向上した。結果、完成した半導体装置への加熱付加時において配線基板1とNCPとの剥離を抑制することができる。

【0075】

さらに第一実施例と同様、コート材12を配線パターン8上に設ける前に、コート材12に含まれるフィラーの粒径を、メッシュ材を用いて、接合後の配線基板1とチップ積層体31との間隔より小さいものに制限している。このため、チップ積層体31を配線基板1に接合した際に、チップ積層体31の最下段の半導体チップ24とコート材12とが接触するおそれが無くなる。

【0076】

次に、チップ積層体31が実装された配線母基板1−1は、モールド工程に移行される。

【0077】

モールド工程では、図7(a)に示すように、チップ積層体31が実装された第一面側の複数の製品形成部13を一括的に覆う第二の封止樹脂27Bが形成される。具体的には、第一実施例と同様、上型と下型からなる成形金型(不図示)を有するトランスファモールド装置などの成型装置を用いてモールド工程が実行される。上型には、チップ積層体31が実装された複数の製品形成部13を一括して覆う大きさのキャビティが形成されており、下型には配線母基板1−1を配置するための凹部が形成されている。チップ積層体31が実装された配線母基板1−1は、下型の凹部にセットされる。そして上型と下型で配線母基板2−1の周縁部をクランプすることで、配線母基板2−1の上方に、上記の大きさのキャビティが形成される。その後、熱硬化性の封止樹脂(例えばエポキシ樹脂)を該キャビティの中へ充填し、所定の温度(例えば180℃)でキュアすることで、封止樹脂が硬化する。その後、封止樹脂27Bが形成された配線母基板1−1は所定の温度でベークされることで、封止樹脂27Bが完全に硬化される。

【0078】

次に、第二の封止樹脂27Bが形成された配線母基板1−1はボールマウント工程に移される。具体的には図7(b)に示すように、配線母基板1−1の第二面の製品形成部13毎に格子状に配置された複数のランド9の上に、導電性の半田ボール4が接合される。ボールマウント工程では、第一実施例と同様、配線母基板1−1上のランド9の配置に合わせて複数の吸着孔が形成されたボールマウンターのマウントツール20が用いられる。

【0079】

その後、半田ボール4が搭載された配線母基板1−1はダイシング工程に移される。具体的には、図7(c)に示すように、配線母基板1−1の封止樹脂27B側にダイシングテープ21が接着される。そして、ダイシング装置のダイシングブレード22により配線母基板1−1を縦横にダイシングライン14に沿って切断することで、各製品形成部13の間が分離される。以上により、CoC(Chip on Chip)型の半導体装置が得られる。

【0080】

(実施例3)

図8及び図9は、第三実施例による半導体装置の製造方法を示す平面図である。これらの図では上述した実施例と同じ構成要素には同一の符号を用いている。

【0081】

上記第一及び第二実施例では、図2に示したように、半導体チップ2又はチップ積層体31が搭載される領域、すなわち絶縁膜10の開口部10aの内側領域に、貫通ビア15、接続パッド7および配線パターン8だけが設けられた配線基板が使用されていた。

【0082】

本実施例では、配線基板1の基板材料、配線材料、絶縁膜材料等は同じであるが、図8に示すように、絶縁膜10の開口部10aの内側領域の基板面に形成された配線パターン8の間の領域に、ダミーパターン32が形成されている。このダミーパターン32は、配線基板1の基材表面において配線パターン8の有る領域と無い領域とのバランスを取り、配線基板1の反りの発生を抑制するために設けられる。このようなダミーパターン32を有する配線基板1を本願発明の製造方法に適用する場合は次のような手法を採ることが好ましい。

【0083】

すなわち、本実施例においては、図9(a)に示すように、絶縁膜(ソルダーレジスト)10の開口部10aの内側領域の基板面を所定の単位エリア33、例えば1mm2毎に区切って、単位エリア33に対する配線の比率[%/mm2]がそれぞれ測定される。言い換えれば、1mm2当りのAu導体の割合が測定される。

【0084】

そして、それぞれの単位エリア33を測定した後、例えば、図9(b)に示すような配線の比率が、70%/mm2以上の単位エリア(図では、配線パターン及びダミーパターンがグレー色で塗り潰された単位エリア34)に対して、スプレーディスペンサによりソルダーレジストのコート材12を供給する。

【0085】

本実施例は、第一実施例と同様なコート材の効果が得られると共に、配線基板1における導体パターン密度の高い単位エリアに選択的にコート材12を供給することで、半導体チップ2と配線基板1とが接触するリスクを確実にかつ効率よく低減することができる。

【0086】

以上、本発明者によってなされた発明を実施例に基づき説明したが、本発明は前述した各実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。例えば、第二実施例では4つのメモリチップを積層したチップ積層体について説明したが、フリップチップ実装方式で半導体チップを配線基板に接続する態様の半導体装置であれば、本願発明はどのような構造体のチップに適用されても良い。また半導体チップの積層数も4段に限らず、3段以下又は6段以上でも良い。

【0087】

また各実施例では、半導体チップの中央領域にバンプ電極を形成した場合について説明したが、半導体チップのパンプ電極がどのような位置に形成されていても本発明を適用可能である。

【符号の説明】

【0088】

1 配線基板

1−1 配線母基板

2 半導体チップ

3 封止樹脂

4 半田ボール

5 電極パッド

6 スタッドバンプ

7 接続パッド

8 配線パターン

9 ランド

10 絶縁膜

10a 開口部

11 NCP(非導電ペースト)

12 コート材

13 製品形成部

14 ダイシングライン

15 貫通ビア

16 マスク

16a マスクの開口

17 噴射機構

18 ディスペンサ

19 ボンディングツール

20 マウントツール

21 ダイシングテープ

22 ダイシングブレード

24 半導体チップ

25 バンプ

26 貫通電極

27A 第1の封止樹脂

27B 第2の封止樹脂

28 吸着ステージ

28a 吸着穴

29 塗布ステージ

30 塗布用シート

31 チップ積層体

32 ダミーパターン

33 単位エリア

34 導体パターン密度の高い単位エリア

【特許請求の範囲】

【請求項1】

半導体装置の製造方法であって、

半導体チップを搭載するための配線基板であり、少なくとも片面に、該半導体チップを搭載する領域に対応させた開口部を有する絶縁膜が形成され、該開口部が、該半導体チップの主面の電極パッドが接続される接続パッドと該接続パッドに繋がる配線パターンとを露出させている、配線基板を用意し、

前記開口部内の前記接続パッドを除いた場所にある、前記配線パターンの表面に、非導電性ペーストに対する密着力が該非導電性ペーストと前記配線パターンの表面との密着力よりも優れたコート材層を形成し、

前記開口部の前記半導体チップを搭載する領域全体に前記非導電性ペーストを塗布し、

フリップチップ実装方式で前記半導体チップの前記電極パッドと前記配線基板の前記接続パッドとを電気接続しながら、前記半導体チップを前記配線基板に前記非導電性ペーストを介して接合する、半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法であって、

前記コート材層には、フィラーを含むソルダーレジストが用いられており、

該ソルダーレジストに含まれるフィラーの粒径は、前記フリップチップ実装方式で前記半導体チップの前記電極パッドと前記配線基板の前記接続パッドとを電気接続したときの前記半導体チップと前記配線基板の間の距離よりも小さく制限されている、半導体装置の製造方法。

【請求項3】

請求項2に記載の半導体装置の製造方法であって、

前記コート材層に用いる前記ソルダーレジストを前記コート材層の形成工程前にメッシュで漉して、前記ソルダーレジストに含まれるフィラーの粒径を制限する、半導体装置の製造方法。

【請求項4】

請求項1から3のいずれか1項に記載の半導体装置の製造方法であって、

前記コート材層の形成後であって前記非導電性ペーストの塗布前に、前記配線基板を所定の温度でベークして前記コート材層を硬化させる、半導体装置の製造方法。

【請求項5】

請求項1から4のいずれか1項に記載の半導体装置の製造方法であって、

前記コート材層の形成工程では、前記開口部内を所定の単位エリアに区切って、該単位エリアに対する配線の比率をそれぞれ測定した後、該配線の比率が所定の値以上の単位エリアに対し前記コート材層を形成する、半導体装置の製造方法。

【請求項6】

請求項1から5のいずれか1項に記載の半導体装置の製造方法であって、

前記配線基板に接合される前記半導体チップは、複数の半導体チップを積層し且つ互いに電気接続してなるチップ積層体の最も端に配置された半導体チップである、半導体装置の製造方法。

【請求項7】

請求項1から6のいずれか1項に記載の半導体装置の製造方法であって、

前記配線基板は、基板面内にマトリックス状に区画された複数の製品形成部にそれぞれ前記半導体チップを搭載するものであり、それぞれの前記製品形成部の間の境界には、各前記製品形成部を分割するための切断ラインが設けられている、半導体装置の製造方法。

【請求項8】

請求項1から7のいずれか1項に記載の半導体装置の製造方法であって、

前記配線基板はガラスエポキシ基板で構成され、前記配線パターンは表面がAuメッキされたものであり、前記非導電性ペーストはエポキシ樹脂からなる、半導体装置の製造方法。

【請求項9】

請求項1に記載の半導体装置の製造方法であって、

前記コート材層は、フィラーを含むソルダーレジストを吹き付けることで形成される、半導体装置の製造方法。

【請求項10】

請求項1に記載の半導体装置の製造方法であって、

前記コート材層の厚さは前記絶縁膜の厚さより薄い、半導体装置の製造方法。

【請求項1】

半導体装置の製造方法であって、

半導体チップを搭載するための配線基板であり、少なくとも片面に、該半導体チップを搭載する領域に対応させた開口部を有する絶縁膜が形成され、該開口部が、該半導体チップの主面の電極パッドが接続される接続パッドと該接続パッドに繋がる配線パターンとを露出させている、配線基板を用意し、

前記開口部内の前記接続パッドを除いた場所にある、前記配線パターンの表面に、非導電性ペーストに対する密着力が該非導電性ペーストと前記配線パターンの表面との密着力よりも優れたコート材層を形成し、

前記開口部の前記半導体チップを搭載する領域全体に前記非導電性ペーストを塗布し、

フリップチップ実装方式で前記半導体チップの前記電極パッドと前記配線基板の前記接続パッドとを電気接続しながら、前記半導体チップを前記配線基板に前記非導電性ペーストを介して接合する、半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法であって、

前記コート材層には、フィラーを含むソルダーレジストが用いられており、

該ソルダーレジストに含まれるフィラーの粒径は、前記フリップチップ実装方式で前記半導体チップの前記電極パッドと前記配線基板の前記接続パッドとを電気接続したときの前記半導体チップと前記配線基板の間の距離よりも小さく制限されている、半導体装置の製造方法。

【請求項3】

請求項2に記載の半導体装置の製造方法であって、

前記コート材層に用いる前記ソルダーレジストを前記コート材層の形成工程前にメッシュで漉して、前記ソルダーレジストに含まれるフィラーの粒径を制限する、半導体装置の製造方法。

【請求項4】

請求項1から3のいずれか1項に記載の半導体装置の製造方法であって、

前記コート材層の形成後であって前記非導電性ペーストの塗布前に、前記配線基板を所定の温度でベークして前記コート材層を硬化させる、半導体装置の製造方法。

【請求項5】

請求項1から4のいずれか1項に記載の半導体装置の製造方法であって、

前記コート材層の形成工程では、前記開口部内を所定の単位エリアに区切って、該単位エリアに対する配線の比率をそれぞれ測定した後、該配線の比率が所定の値以上の単位エリアに対し前記コート材層を形成する、半導体装置の製造方法。

【請求項6】

請求項1から5のいずれか1項に記載の半導体装置の製造方法であって、

前記配線基板に接合される前記半導体チップは、複数の半導体チップを積層し且つ互いに電気接続してなるチップ積層体の最も端に配置された半導体チップである、半導体装置の製造方法。

【請求項7】

請求項1から6のいずれか1項に記載の半導体装置の製造方法であって、

前記配線基板は、基板面内にマトリックス状に区画された複数の製品形成部にそれぞれ前記半導体チップを搭載するものであり、それぞれの前記製品形成部の間の境界には、各前記製品形成部を分割するための切断ラインが設けられている、半導体装置の製造方法。

【請求項8】

請求項1から7のいずれか1項に記載の半導体装置の製造方法であって、

前記配線基板はガラスエポキシ基板で構成され、前記配線パターンは表面がAuメッキされたものであり、前記非導電性ペーストはエポキシ樹脂からなる、半導体装置の製造方法。

【請求項9】

請求項1に記載の半導体装置の製造方法であって、

前記コート材層は、フィラーを含むソルダーレジストを吹き付けることで形成される、半導体装置の製造方法。

【請求項10】

請求項1に記載の半導体装置の製造方法であって、

前記コート材層の厚さは前記絶縁膜の厚さより薄い、半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−174900(P2012−174900A)

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願番号】特願2011−35830(P2011−35830)

【出願日】平成23年2月22日(2011.2.22)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願日】平成23年2月22日(2011.2.22)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]