半導体装置の製造方法

【課題】高歩留まりの薄型半導体装置の製造方法を提供する。

【解決手段】まず、半導体ウェハ10の第1の主面S1に、複数の素子領域3およびこの素子領域3にコンタクトする端子電極5を形成し、こののち半導体ウェハ10の第1の主面S1と対向する第2の主面S2を、半導体ウェハ10の外周縁部を残して、所望の厚さとなるまで、薄肉化する。そして、薄肉化された半導体ウェハ10の前記第2の主面S2に、金属層6を形成し、こののち、金属層6上に絶縁被膜7を形成し、最後に、半導体ウェハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得るものである。

【解決手段】まず、半導体ウェハ10の第1の主面S1に、複数の素子領域3およびこの素子領域3にコンタクトする端子電極5を形成し、こののち半導体ウェハ10の第1の主面S1と対向する第2の主面S2を、半導体ウェハ10の外周縁部を残して、所望の厚さとなるまで、薄肉化する。そして、薄肉化された半導体ウェハ10の前記第2の主面S2に、金属層6を形成し、こののち、金属層6上に絶縁被膜7を形成し、最後に、半導体ウェハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得るものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に係り、フリップチップ構造の半導体装置に関するものである。

【背景技術】

【0002】

近年、携帯電話をはじめとした電子機器における低消費電力化、高機能化および高速化に伴って、それに搭載される半導体装置も低消費電力化、高速化が要求されてきている。一般的に電子機器のロードスイッチおよびDC−DCコンバータ等に用いられているトランジスタも、それらに対応するためにオン抵抗の小さなものが要求されている。トランジスタのオン抵抗の低減をはかるためには、個々のデバイスを微細化して、単位面積あたりに配置するトランジスタの密度を大きくすることが、一つの方法としてあげられる。

【0003】

一例として、MOSFETの半導体チップに対し、フリップチップ実装を行い、半導体チップの外縁と半導体装置の外縁とが一致するようにしたチップサイズパッケージ(CSP)構造の半導体装置が提案されている(たとえば特許文献1)。

【0004】

このようなMOSFETにおいては図16に一例を示すように、第1の主面に動作領域が設けられる半導体基板の少なくとも動作領域と一部重畳する第2主面側の半導体基板に凹部を設けることで、半導体基板の反りを防止している。この構造では、動作領域の半導体基板が薄肉化されているため、動作速度の向上を図ることができる一方、外周部に肉厚部を有するため、第2の主面側に金属層を形成しても、半導体チップの反りを低減することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−205761号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら上記構造の半導体装置においては、特許文献1の段落0033の記載によれば半導体基板の周縁部の肉厚部の厚さ(t1)は200μm、中央部の肉薄部の厚さt2は20μm程度であるとされている。この形状は深い凹部を有するコの字の矩形状をなし、深さ(t2)が180μmと、非常に深く入りくぼんでいるため、加工の作業性が悪い。

また、拡散プロセス時のウェハキャリア冶具搭載時、あるいはプローブテスト時、さらには第2の主面側に品種や製造LOTなどの識別番号を示すマーキングを行う際、などにおいて非常に割れやすいという問題があった。

これはさらに、ダイシング時あるいは包装用のテーピング時、あるいはプリント基板実装時の真空吸着時などにおいて、非常に割れやすく、加工上および品質上の課題があった。

また、肉厚領域が存在するため、製品厚みの薄いものには搭載できず、結果として使用に一定の制限を免れ得ないという問題があった。

本発明は前記実情に鑑みてなされたもので、薄型の半導体装置を信頼性が高くかつ高歩留まりで提供することを目的とする。

【課題を解決するための手段】

【0007】

そこで本発明の半導体装置は、第1の主面と、前記第1の主面と対向する第2の主面を有し、所望の素子領域を形成した半導体基板と、前記第1の主面に形成された端子電極と、前記第2の主面全体を覆う金属層と、前記金属層全体を覆う絶縁被膜とを備え、前記絶縁被膜の外縁が前記半導体基板の外縁と一致している。

【0008】

また本発明は、前記半導体装置であって、前記絶縁被膜が、樹脂膜であるものを含む。

【0009】

また本発明は、前記半導体装置であって、前記樹脂膜が、シート状樹脂フィルムであるものを含む。

【0010】

また本発明は、前記半導体装置であって、前記樹脂膜は、塗布膜であるものを含む。

【0011】

また本発明は、前記半導体装置であって、前記半導体基板が、厚さが300μm以下であるものを含む。

【0012】

また本発明は、前記半導体装置であって、前記絶縁被膜の膜厚は50μm以下であるものを含む。

【0013】

また本発明は、前記半導体装置であって、前記金属層の膜厚は50μm以下であるものを含む。

【0014】

また本発明は、前記半導体装置であって、前記端子電極がバンプを備えたものを含む。

【0015】

また本発明は、前記半導体装置であって、前記素子領域は、第1の導電型のシリコン基板表面に形成された第1の導電型の半導体層内に形成された複数の第2導電型の半導体領域と、前記複数の第2導電型の半導体領域を貫通する複数のトレンチと、前記複数のトレンチの内壁にゲート絶縁膜を介して形成されたゲート電極と、前記第2導電型の半導体領域内に形成された第1導電型の半導体領域からなる複数のソース領域とを具備し、前記第1の主面に形成される前記端子電極が、前記ゲート電極のそれぞれに接続されるゲート端子と、前記ソース領域のそれぞれに接続されるソース端子とで構成され、前記第2の主面に形成される前記金属層は、前記シリコン基板の裏面全体を覆い、共通のドレイン電極を構成しており、前記絶縁被膜は前記金属層全体を覆うように形成されたものを含む。

【発明の効果】

【0016】

上記構成によれば、この半導体装置においては、金属層と前記絶縁被膜の外縁が半導体基板の外縁と一致しており、金属層を絶縁被膜で覆った状態でダイシングすることによって得られるため、薄型化に対しても破損は低減される。また、全体的に平坦な外径となるため、半導体装置の薄型化が可能となる。

【図面の簡単な説明】

【0017】

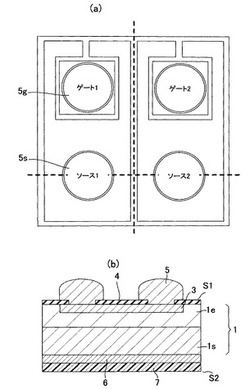

【図1】本発明の実施の形態1に係る半導体装置を示す図であり、(a)は上面図、(b)は断面図

【図2】(a)乃至(e)は同半導体装置の製造工程の全体を示す概要説明図

【図3】(a)乃至(d)はこの半導体装置の素子領域の製造工程を示す図

【図4】本発明の実施の形態1に係る半導体装置の要部説明図

【図5】本発明の実施の形態1に係る半導体装置の等価回路図

【図6】本発明の実施の形態1に係る半導体装置の動作説明図

【図7】本発明の実施の形態2に係る半導体装置を示す断面図

【図8】本発明の実施の形態3に係る半導体装置を示す断面図

【図9】(a)乃至(d)は本発明の実施の形態4に係る半導体装置の製造工程の一部を示す概要説明図

【図10】(a)乃至(d)は本発明の実施の形態5に係る半導体装置の製造工程を示す概要説明図

【図11】(a)乃至(d)は本発明の実施の形態6に係る半導体装置の製造工程の一部を示す概要説明図

【図12】本発明の実施の形態7に係る半導体装置の製造工程の一部を示す概要説明図

【図13】(a)乃至(d)は本発明の実施の形態7に係る半導体装置の製造工程における絶縁被膜の貼着工程を示す概要説明図

【図14】(a)乃至(c)は本発明の実施の形態7に係る半導体装置の製造工程における絶縁被膜の貼着工程を示す概要説明図

【図15】(a)乃至(c)は本発明の実施の形態7に係る半導体装置の製造工程における絶縁被膜の貼着工程を示す概要説明図

【図16】従来例の半導体装置を示す断面図

【0018】

以下本発明の実施の形態について、図面を参照しつつ詳細に説明する。

(実施の形態1)

図1(a)および(b)は本発明の実施の形態に係る半導体装置の上面図および断面図、図2(a)乃至(e)は同半導体装置の製造工程の全体を示す概要説明図である。図3(a)乃至(d)はこの半導体装置の素子領域の製造工程を示す図である。図4はこの半導体装置の要部説明図、図5はこの半導体装置の等価回路図、図6はこの半導体装置の動作説明図である。

本実施の形態の半導体装置は1対のMOSFETを集積化して形成されたもので、図1に示すように、第1の主面S1と、第1の主面S1と対向する第2の主面S2を有し、第1の主面S1側に素子領域3を形成した半導体基板1と、この第1の主面S1に形成された端子電極5と、第2の主面S2全体を覆う金属層6と、この金属層6全体を覆う遮光性のカーボンブラックを添加したソルダレジストからなる絶縁被膜7とを備えている。そして、この金属層6と絶縁被膜7の外縁が半導体基板1の外縁と一致したことを特徴とする。図5にこの半導体装置の等価回路を示すように、2つのMOSFETがドレイン電極を共通として並列接続されている。

【0019】

そしてこの半導体装置は、以下のようにして形成される。まず、半導体ウェハ10の第1の主面S1に、複数の素子領域3およびこの素子領域3にコンタクトする端子電極5を形成し、こののち半導体ウェハ10の第1の主面S1と対向する第2の主面S2を、半導体ウェハ10の外周縁部を残して、所望の厚さとなるまで、薄肉化する。そして、薄肉化された半導体ウェハ10の前記第2の主面S2に、金属層6を形成し、こののち、金属層6上に絶縁被膜7を形成し、最後に、半導体ウェハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得るものである。ここで各半導体装置は、それぞれドレインを金属層6として共通接続した1対のMOSFETを搭載したディスクリートMOSFETを構成するものである。

この半導体ウェハは、出発材料として8インチで厚さ700μmのものを用い、半導体ウェハ10の外周縁部約10mmを残して、最終的に厚さが200μmとなるように肉薄化した。そして、金属層の膜厚は20μmとし、絶縁被膜の膜厚は20μmとした。このようにしてチップサイズ1.2mm×1.2mmの半導体装置が得られる。

【0020】

次に、この半導体装置の製造方法の概要について図面を参照しつつ詳細に説明する。まず、図2(a)に示すように、8インチ、厚さ700μmの半導体ウェハを用い、この半導体ウェハ10の第1の主面S1に、複数の素子領域3を形成する。この図では詳細は省略するが、素子領域3の詳細については後述する。

次いで、図2(b)に示すように、素子領域3の形成された半導体ウェハ10の第1の主面S1に絶縁膜4を形成する。

次いで、図2(c)に示すように、半導体ウェハ10の第1の主面S1の素子領域に対向する領域を第2の主面S2側から研磨し、厚さ200μm程度になるまで肉薄化する。このとき半導体ウェハ10の外周縁から約10mmの肉厚部10Tを残している。 こののち、図2(d)に示すように、薄肉化された半導体ウェハ10の前記第2の主面S2に、スパッタリング法により、膜厚15μmのアルミニウム薄膜からなる金属層6を形成する。そして熱処理によりシリコン基板とアルミニウム薄膜とのオーミック接触をとる。

最後に、図2(e)に示すように、半導体ウェハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得る。

なお、前記実施の形態では、裏面の金属層6としてアルミニウム薄膜を用いたが、アルミニウム薄膜に限定されることなく、他の金属でも良い事はいうまでもない。例えばクロム+ニクロム+ニッケル+銀の4層構造とするなど、多層薄膜であってもよい。

【0021】

他の部分については通例の構成をとっている。

図4に要部拡大断面図を示すように、素子領域3は、エピタキシャル層1e内に形成されたP型ウェル31を貫通するように形成されたトレンチTにゲート酸化膜を介して形成された多結晶シリコン層からなるトレンチゲート33と、その両端に一定の深さを持つように形成されたN+領域からなるソース領域32sおよびドレイン領域とで構成される。そしてポリシリコンゲート33上を覆うように酸化シリコン膜からなる層間絶縁膜34が形成され、この層間絶縁膜34に開口するようにコンタクトホールが形成されている。そしてこのコンタクトホールを介して、アルミニウム電極が形成され、それぞれソース電極35s、ゲート電極35g、ドレイン電極(金属層6)が形成されている。そしてこの上層を覆う酸化シリコン膜からなる絶縁膜4に開口してソースバンプ5s、ゲートバンプ5gが形成されている。

そしてこのエピタキシャル層1eは、N型のシリコン基板1s表面に形成されており、ドレイン領域はN型のエピタキシャル層1eおよびN型基板1sで構成され、半導体チップの裏面全体が金属層6となっている。そしてこの金属層6全体を覆うように、ソルダレジストからなる絶縁被膜7が形成されている。

【0022】

すなわち、N型のシリコン基板1sの表面に形成されたN型のエピタキシャル層1e内に形成された複数のストライプ状のトレンチT内にゲート酸化膜を介して多結晶シリコン層(導電体層)を埋め込み形成したトレンチゲート33と、このシリコン基板表面を覆う酸化シリコン膜からなる層間絶縁膜34と、この層間絶縁膜34に形成された、ソースコンタクトを介してソース領域32sにコンタクトするように形成されたソース電極35sと、トレンチゲート33の周縁部でトレンチゲート33に接続されたゲート周辺配線と、ソース電極35sと同一表面上であって、前記ソース電極35sから離間した位置に形成され、前記ゲート周辺配線に接続されるゲート電極35gとを具備している(図4参照)。

【0023】

次に本発明の半導体装置の製造方法を、図3(a)乃至(d)を参照して詳細に説明する。

ストライプ状のトレンチゲート構造を有するN型MOSFETの製造方法は、図3(a)に示すように、半導体基板としてN+型のシリコンウェハを使用し、その表面にN-型のエピタキシャル層1eを形成する。このN-型のエピタキシャル層1e内にP型ウェル31を形成する。

【0024】

次に、図3(b)に示すようにフォトリソグラフィーおよびドライエッチングにより、P型ウェル31の形成されたN-型のエピタキシャル層1e表面にトレンチTを形成する。

【0025】

この後、図3(c)に示すようにトレンチ側壁に熱酸化により厚膜30nm程度のゲート酸化膜を形成したのち、トレンチT内にCVD法によって多結晶シリコン膜(トレンチゲート)を堆積し、多結晶シリコンに不純物ドーピングを行う。引き続き、化学機械研磨(CMP)あるいはエッチバックにより不要部を除去したのち、熱酸化により、この多結晶シリコン上に酸化シリコン膜からなる層間絶縁膜34を形成する。

【0026】

ソース領域32sとなるN型拡散層を形成するため、図3(d)に示すように、P型ウェル31中にイオン注入法を用いて、リン不純物を注入する。

その後、半導体チップ表面である第1の主面S1側に絶縁膜34および保護膜4を堆積しソース電極35sとソース領域32sを電気的に導通させるため、ソースコンタクト開口部を設けて、アルミニウム薄膜を形成し、ソース電極35sなどを構成する金属配線を形成する。このとき、ゲート電極35g、第2の主面S2側の金属電極6も同時に形成してもよい。そしてバンプ5s、5gを形成する。このようにして、図2(a)に示す半導体装置が形成される。図2(a)では素子領域3として詳細を省略している。

【0027】

このようにして形成された半導体装置は、図6に動作説明図を示すように、オン電流は矢印方向に流れる。ここでシリコン基板1s裏面の金属層6とでは金属層6の方が低抵抗であるため、オン電流の経路は矢印のように金属層6を経由して流れる。このように裏面に形成された金属層6は、オン抵抗の低減に大きく寄与し、動作速度の高速化をはかることができる。

【0028】

また、この金属層6を絶縁被膜で被覆しているため、ダイシング後に、真空チャックあるいはコレットで、分割された半導体装置すなわち半導体チップを搬送する際、キズがついたり、角部に割れやかけが生じ易たりすることはなく、金属層6は絶縁被膜7で確実に保護されている。これに対し、従来はこの金属層6は露出しており、ダイシング後に、真空チャックあるいはコレットで、分割された半導体装置すなわち半導体チップを搬送する際、キズがついたり、角部に割れやかけが生じ易いという問題があった。

【0029】

このように、本実施の形態の半導体装置では、剛性の高い金属層6を柔らかい絶縁被膜で覆うことで、2層構造の保護膜として作用し、保護膜自体の膜厚は薄くても強度の高い半導体チップを得ることが可能となる。この2層構造の保護膜は半導体チップの第2の主面全体を覆うように形成されているため、反りや歪み等の変形を生じにくく信頼性の高い半導体装置を提供することが可能となる。

このようにして極めて薄型で信頼性の高いチップサイズパッケージ(CSP)構造の半導体装置を得ることができる。

【0030】

また本実施の形態では、絶縁被膜7をカーボンブラックで着色されたソルダレジストで構成しているため、下地の金属層6のわずかな凹凸も吸収し、平坦な塗布膜を得ることができる。そしてこの平坦かつ平滑な塗布膜からなる絶縁被膜上に品種名や製造ロット名などを印刷し、識別表示を行う際に、金属層にキズがついたりすることもなく、また着色された絶縁被膜上に識別性に優れた識別表示を形成することが可能となる。

【0031】

また金属層6の表面を絶縁被膜で被覆することにより、外観性も良好となる。また着色剤を添加して着色された絶縁被膜とすることで、下地は見えず外観性の向上を図ることができる。

【0032】

この絶縁被膜7の膜厚は前記実施の形態に限定されるものではないが、50μm以下とするのが望ましい。50μm以下とすることにより、全体としての厚さが厚くなるのを防ぎ、さらには半導体チップの反りを低減することができる。

【0033】

なお、絶縁被膜としては、ソルダレジストに限定されることなく、ポリイミド膜、エポキシ樹脂、絶縁性シリコン樹脂、フェノール樹脂、アクリル樹脂などの有機系塗布膜、酸化アルミニウム膜、酸化シリコン膜などの酸化膜系絶縁塗布膜等が適用可能である。

また、前記絶縁被膜は、刷毛塗り法で形成したが、このほかトランスファーモールド法、印刷法、コーティング法、スクリーン印刷法など、適宜他の方法も適用可能である。

【0034】

なお、前記実施の形態では、この半導体ウェハは、出発材料として8インチで厚さ700μmのものを用い、半導体ウェハ10の外周縁部約10mmを残して、最終的に厚さが200μmとなるように肉薄化したが、最終的な厚さは、300μmよりも薄ければよく、望ましくは200μm以下である。下限はないが、製造可能要件を考慮すると1μm以上である。望ましくは特性を得る為のエピタキシャル層や基板の厚み、叉実用面として外部応力に対する強度や信頼性確保を考慮すると50μm程度であろう。

そして、金属層の膜厚は20μmとしたが、50μmより薄ければよい。50μmよりも厚いと半導体チップの全体厚が厚くなるだけでなく、金属層の熱膨張率が支配的となり反りが生じ易くなる。この金属層の膜厚は肉薄化後の半導体ウェハの膜厚の4分の1以下とするのが望ましい。

また絶縁被膜の膜厚は20μmとしたが、50μmより薄ければよい。50μmよりも厚いと半導体チップの全体厚が厚くなるだけでなく、絶縁被膜の剥離が生じ易くなる。この絶縁被膜の膜厚は金属層の膜厚よりも小さくするのが望ましい。

【0035】

さらにまた、前記実施の形態では、1対のMOSFETを搭載した半導体装置について説明したが、本発明は1個のMOSFETを用いた半導体装置、あるいは他の半導体装置にも適用可能であることはいうまでもない。

【0036】

(実施の形態2)

次に本発明の実施の形態2について説明する。

図7は本発明の実施の形態2にかかる半導体装置の断面図である。

前記実施の形態では絶縁被膜7としてソルダレジストからなる塗布膜を用いたが、本実施の形態では、図7に示すように、フィルムレジストからなる絶縁被膜7t、つまり貼着により装着するテープ材料を用いたものである。

【0037】

他の構成については前記実施の形態1と同様であり、ここでは説明を省略する。なお図7において、同一部材には図1において用いたものと同一符号を付した。

この構成によれば、金属層6の裏面にテープ材料等のシート状樹脂フィルムを貼着することで、膜厚のばらつきを低減し、ピンホールのない、絶縁被膜7tを形成することが可能となる。金属層6の裏面に貼着すればよいため、取扱がきわめて容易である。

なお、このテープ材料としては、エポキシ樹脂(Epoxy resin)、エポキシ樹脂に、シリカ(Silica)あるいはアクリル樹脂(Acrylic polymer)を混合した混合体、黒色の色を得る為に、0.1〜5%のカーボンブラックを混合したもの(Black film)、フィルムレジスト、あるいは樹脂テープに接着剤を塗布したものなどが適用可能である。

【0038】

(実施の形態3)

次に本発明の実施の形態3について説明する。

図8は本発明の実施の形態3にかかる半導体装置の断面図である。

前記実施の形態では絶縁被膜は単層膜で構成したが、本実施の形態では、図8に示すように、透光性の絶縁膜であるポリイミド膜7aと、カーボンブラックを添加した黒色のポリイミド膜7bとの2層膜を用いたものである。他は図1で示した半導体装置と同様であるためここでは説明を省略する。なお図8において、同一部材には図1において用いたものと同一符号を付した。

【0039】

この構成によれば、絶縁被膜を2層膜で構成しているため、キズを防ぐような硬い膜と密着性を向上するような展性の高い膜との2層膜とするなど、それぞれの膜に機能を持たせることもできる。また、最表層にのみ着色を行うようにしてもよい。

また、金属層に接する層は金属酸化膜、酸化シリコン膜あるいは窒化シリコン膜などの無機膜とし、表層側は有機系の塗布膜、あるいは樹脂シートなどで構成してもよい。

【0040】

以下は、この半導体装置の製造方法の変形例について説明する。

【0041】

(実施の形態4)

前記実施の形態1では図2(e)の工程において、外周縁に肉厚部10Tを残した半導体ウェハ10の、中央部の肉薄部をダイシングラインD.Lに沿って一挙に個片分割したが、本実施の形態では、図9(a)乃至(c)に示すように、一旦、外周ラインO.D.Lに沿って八角形に切断し、肉厚部10Tを切り落とした後、ダイシングラインD.Lに沿って個々の半導体チップに分断するものである。

図9(a)および(b)は断面図および上面説明図である。

図9(c)はこの八角形に切断された半導体ウェハから半導体チップ10cを切り出す工程を示す図である。

図9(d)はこの八角形に切断された半導体ウェハから切りだされた半導体チップ10cを示す図である。

なお、八角形に限定されず、多角形もしくは、略円形でもよい事は言うまでもない。

【0042】

他部については、前記実施の形態1と同様であり、ここでは説明を省略する。

この方法によれば、一旦肉厚部10Tを切り落とした後、ダイシングラインD.Lに沿って個々の半導体チップに分断するため、ダイシングが容易で、切断面の美しい切断が可能となる。

【0043】

他部については、前記実施の形態1と同様であり、ここでは説明を省略する。

この方法によれば、ダイシングが容易で、切断面の美しい切断が可能となる。

本実施の形態についても、詳細については省略するが、前記実施の形態1で説明したものと同様である。

【0044】

(実施の形態5)

前記実施の形態1では出発材料として700μmの半導体ウェハを用い、図2(c)の工程において、外周縁に肉厚部10Tを残すように、半導体ウェハ10の中央部を研磨し、一挙に肉薄部を形成したが、本実施の形態では、第2の主面S2側から研磨し、一旦、厚さ300μm程度になるまで肉薄化し、こののち外周縁に肉厚部10Tを残すように、半導体ウェハ10の中央部を研磨し、肉薄部を形成する。そしてこののちダイシングラインD.Lに沿って個片分割し、個々の半導体チップに分断するものである。

【0045】

まず、前記実施の形態1と同様、8インチ、厚さ700μmの半導体ウェハを用い、この半導体ウェハ10の第1の主面S1に、複数の素子領域3を形成し、さらに素子領域3の形成された半導体ウェハ10の第1の主面S1に絶縁膜4を形成する。

【0046】

図2(a)および(b)に示した工程までは前記実施の形態1と同様である。そしてこののち、図10(a)に示すように、半導体ウェーハ10の第2の主面S2側から全面研磨し、一旦、厚さ300μm程度になるまで肉薄化する。

【0047】

そして、図2(c)に示したのと同様、図10(b)に示すように、半導体ウェーハ10の第1の主面S1の素子領域に対向する領域を第2の主面S2側から研磨し、厚さ200μm程度になるまで肉薄化する。このとき半導体ウェーハ10の外周縁から約10mmの肉厚部10Tを残している。

【0048】

こののち、図10(c)に示すように、薄肉化された半導体ウェーハ10の前記第2の主面S2に、スパッタリング法により、膜厚15μmのアルミニウム薄膜からなる金属層6を形成する。そして熱処理によりシリコン基板とアルミニウム薄膜とのオーミック接触をとる。ここでも金属層としてはアルミニウム薄膜に限定されることなく、他の金属でも良く、またクロム+ニクロム+ニッケル+銀などの多層膜で構成してもよい。

【0049】

最後に、絶縁被膜7を形成し、図10(d)に示すように、半導体ウェーハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得る。

【0050】

この方法によれば、一旦肉薄化してから、素子領域に対向する面側を肉薄化しているため、半導体基板の受けるストレスは低減され、信頼性の高い半導体装置を提供することが可能となる。

【0051】

(実施の形態6)

前記実施の形態5では図10(d)の工程において、外周縁に肉厚部10Tを残した半導体ウェーハ10の、中央部の肉薄部をダイシングラインD.L.に沿って一挙に個片分割したが、本実施の形態では、図11(a)乃至(d)に示すように、一旦、外周ラインO.D.L.に沿って八角形に切断し、肉厚部10Tを切り落とした後、ダイシングラインD.L.に沿って個々の半導体チップに分断するものである。

図11(a)および(b)は断面図および上面説明図である。

図11(c)はこの八角形に切断された半導体ウェーハから半導体チップ10cを切り出す工程を示す図である。

図11(d)はこの八角形に切断された半導体ウェーハから切りだされた半導体チップ10cを示す図である。

なお、八角形に限定されず、多角形もしくは、略円形でもよい事は言うまでもない。

【0052】

他部については、前記実施の形態5と同様であり、ここでは説明を省略する。

この方法によれば、一旦肉厚部10Tを切り落とした後、ダイシングラインD.L.に沿って個々の半導体チップに分断するため、ダイシングが容易で、切断面の美しい切断が可能となる。

【0053】

(実施の形態7)

前記実施の形態5では図10(d)の工程において、半導体ウェーハ10の第2の面全体に絶縁被膜を形成したが、図12に示すように外周縁に肉厚部10Tを残した半導体ウェーハ10の、中央部の肉薄部の第2の主面S2側に選択的に樹脂膜からなる絶縁被膜7tを形成してもよい。以下にこの絶縁被膜7tの貼着方法について説明するが、他の工程については前記実施の形態6と同様であるためここでは説明を省略する。

【0054】

なお、このテープ材料としてエポキシ樹脂を主成分とする絶縁被膜7tを貼着する方法の一例を説明する。図13(a)乃至(d)、図14(a)乃至(c)、図15(a)乃至(c)は本発明の実施の形態7に係る半導体装置の製造工程における絶縁被膜の貼着工程を示す概要説明図である。樹脂材料としては前記実施の形態2で説明した材料と同様の樹脂が適用可能である。以下の図では半導体ウェーハ10のうち1ユニットの半導体基板1となる部分のみウェハとして示す。

ず、図13(a)に示すように、絶縁被膜7tとなる、エポキシ樹脂を主成分とする絶縁性樹脂を、PETフィルムからなる第1の剥離材17上に成膜し、第2の剥離材27を貼り合わせて、3層構造の絶縁テープを形成する。

そして、図13(b)に示すように、絶縁被膜7tと第2の剥離材27をウェーハ形状に符合したカッティングラインC.L.に沿ってほぼ円形あるいは多角形状にカットする。

こののち、図13(c)に示すように、第1の剥離材17に貼着された絶縁被膜7tを第2の剥離材27から剥離し、図13(d)に示すように、ウェーハ形状に符合したてほぼ円形あるいは多角形状にカットされた絶縁被膜7tを得る。

【0055】

そして、図14(a)に示すように、加熱ステージ400を80℃程度に加熱し、この加熱ステージ400上にウェハ(半導体基板1)を載置し、上記絶縁被膜7tの位置合わせを行う。

そして、図14(b)に示すように、絶縁被膜7tと第1の剥離材17を、60℃に加熱したローラ500を50mm/secで回転させ、ウェハ(半導体基板1)裏面に絶縁被膜7tを仮固着する。

こののち、図14(c)に示すように、第1の剥離材17上の絶縁被膜7tに貼着されたウェーハ1ごと加熱ステージ400から退避させる。

【0056】

そして、図15(a)に示すように、常温の冷却ステージ600にウェハ(半導体基板1)を載置する。

そして、図15(b)に示すように、絶縁被膜7tから第1の剥離材17を、剥離する。

こののち、図15(c)に示すように、ウェハ(半導体基板1)1上の絶縁被膜7tを冷却ステージ600から分離後、130℃で2時間硬化させて、一体化する。

【0057】

なお、前記半導体装置においてはバンプを形成した半導体装置について説明したが、必ずしもバンプは必要ではなく、別途スティフナーと呼ばれる支持基板を用いてソルダボールとの接続を行うなど適宜変更可能である。

【産業上の利用可能性】

【0058】

以上説明してきたように、本発明によれば、薄型で信頼性の高い半導体装置において高歩留まり化が可能であることから、リチウムイオン二次電池の制御回路などに有効である。

【符号の説明】

【0059】

S1 第1の主面

S2 第2の主面

1 半導体基板

1s シリコン基板

1e エピタキシャル層

3 素子領域

4 絶縁膜

6 金属層

7、7t 絶縁被膜

10 半導体ウェハ

17 第1の剥離材

T トレンチ

27 第2の剥離材

31 P型ウェル

32s ソース領域

34 層間絶縁膜

33 トレンチゲート

35s ソース電極

35g ゲート電極

【技術分野】

【0001】

本発明は、半導体装置の製造方法に係り、フリップチップ構造の半導体装置に関するものである。

【背景技術】

【0002】

近年、携帯電話をはじめとした電子機器における低消費電力化、高機能化および高速化に伴って、それに搭載される半導体装置も低消費電力化、高速化が要求されてきている。一般的に電子機器のロードスイッチおよびDC−DCコンバータ等に用いられているトランジスタも、それらに対応するためにオン抵抗の小さなものが要求されている。トランジスタのオン抵抗の低減をはかるためには、個々のデバイスを微細化して、単位面積あたりに配置するトランジスタの密度を大きくすることが、一つの方法としてあげられる。

【0003】

一例として、MOSFETの半導体チップに対し、フリップチップ実装を行い、半導体チップの外縁と半導体装置の外縁とが一致するようにしたチップサイズパッケージ(CSP)構造の半導体装置が提案されている(たとえば特許文献1)。

【0004】

このようなMOSFETにおいては図16に一例を示すように、第1の主面に動作領域が設けられる半導体基板の少なくとも動作領域と一部重畳する第2主面側の半導体基板に凹部を設けることで、半導体基板の反りを防止している。この構造では、動作領域の半導体基板が薄肉化されているため、動作速度の向上を図ることができる一方、外周部に肉厚部を有するため、第2の主面側に金属層を形成しても、半導体チップの反りを低減することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−205761号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら上記構造の半導体装置においては、特許文献1の段落0033の記載によれば半導体基板の周縁部の肉厚部の厚さ(t1)は200μm、中央部の肉薄部の厚さt2は20μm程度であるとされている。この形状は深い凹部を有するコの字の矩形状をなし、深さ(t2)が180μmと、非常に深く入りくぼんでいるため、加工の作業性が悪い。

また、拡散プロセス時のウェハキャリア冶具搭載時、あるいはプローブテスト時、さらには第2の主面側に品種や製造LOTなどの識別番号を示すマーキングを行う際、などにおいて非常に割れやすいという問題があった。

これはさらに、ダイシング時あるいは包装用のテーピング時、あるいはプリント基板実装時の真空吸着時などにおいて、非常に割れやすく、加工上および品質上の課題があった。

また、肉厚領域が存在するため、製品厚みの薄いものには搭載できず、結果として使用に一定の制限を免れ得ないという問題があった。

本発明は前記実情に鑑みてなされたもので、薄型の半導体装置を信頼性が高くかつ高歩留まりで提供することを目的とする。

【課題を解決するための手段】

【0007】

そこで本発明の半導体装置は、第1の主面と、前記第1の主面と対向する第2の主面を有し、所望の素子領域を形成した半導体基板と、前記第1の主面に形成された端子電極と、前記第2の主面全体を覆う金属層と、前記金属層全体を覆う絶縁被膜とを備え、前記絶縁被膜の外縁が前記半導体基板の外縁と一致している。

【0008】

また本発明は、前記半導体装置であって、前記絶縁被膜が、樹脂膜であるものを含む。

【0009】

また本発明は、前記半導体装置であって、前記樹脂膜が、シート状樹脂フィルムであるものを含む。

【0010】

また本発明は、前記半導体装置であって、前記樹脂膜は、塗布膜であるものを含む。

【0011】

また本発明は、前記半導体装置であって、前記半導体基板が、厚さが300μm以下であるものを含む。

【0012】

また本発明は、前記半導体装置であって、前記絶縁被膜の膜厚は50μm以下であるものを含む。

【0013】

また本発明は、前記半導体装置であって、前記金属層の膜厚は50μm以下であるものを含む。

【0014】

また本発明は、前記半導体装置であって、前記端子電極がバンプを備えたものを含む。

【0015】

また本発明は、前記半導体装置であって、前記素子領域は、第1の導電型のシリコン基板表面に形成された第1の導電型の半導体層内に形成された複数の第2導電型の半導体領域と、前記複数の第2導電型の半導体領域を貫通する複数のトレンチと、前記複数のトレンチの内壁にゲート絶縁膜を介して形成されたゲート電極と、前記第2導電型の半導体領域内に形成された第1導電型の半導体領域からなる複数のソース領域とを具備し、前記第1の主面に形成される前記端子電極が、前記ゲート電極のそれぞれに接続されるゲート端子と、前記ソース領域のそれぞれに接続されるソース端子とで構成され、前記第2の主面に形成される前記金属層は、前記シリコン基板の裏面全体を覆い、共通のドレイン電極を構成しており、前記絶縁被膜は前記金属層全体を覆うように形成されたものを含む。

【発明の効果】

【0016】

上記構成によれば、この半導体装置においては、金属層と前記絶縁被膜の外縁が半導体基板の外縁と一致しており、金属層を絶縁被膜で覆った状態でダイシングすることによって得られるため、薄型化に対しても破損は低減される。また、全体的に平坦な外径となるため、半導体装置の薄型化が可能となる。

【図面の簡単な説明】

【0017】

【図1】本発明の実施の形態1に係る半導体装置を示す図であり、(a)は上面図、(b)は断面図

【図2】(a)乃至(e)は同半導体装置の製造工程の全体を示す概要説明図

【図3】(a)乃至(d)はこの半導体装置の素子領域の製造工程を示す図

【図4】本発明の実施の形態1に係る半導体装置の要部説明図

【図5】本発明の実施の形態1に係る半導体装置の等価回路図

【図6】本発明の実施の形態1に係る半導体装置の動作説明図

【図7】本発明の実施の形態2に係る半導体装置を示す断面図

【図8】本発明の実施の形態3に係る半導体装置を示す断面図

【図9】(a)乃至(d)は本発明の実施の形態4に係る半導体装置の製造工程の一部を示す概要説明図

【図10】(a)乃至(d)は本発明の実施の形態5に係る半導体装置の製造工程を示す概要説明図

【図11】(a)乃至(d)は本発明の実施の形態6に係る半導体装置の製造工程の一部を示す概要説明図

【図12】本発明の実施の形態7に係る半導体装置の製造工程の一部を示す概要説明図

【図13】(a)乃至(d)は本発明の実施の形態7に係る半導体装置の製造工程における絶縁被膜の貼着工程を示す概要説明図

【図14】(a)乃至(c)は本発明の実施の形態7に係る半導体装置の製造工程における絶縁被膜の貼着工程を示す概要説明図

【図15】(a)乃至(c)は本発明の実施の形態7に係る半導体装置の製造工程における絶縁被膜の貼着工程を示す概要説明図

【図16】従来例の半導体装置を示す断面図

【0018】

以下本発明の実施の形態について、図面を参照しつつ詳細に説明する。

(実施の形態1)

図1(a)および(b)は本発明の実施の形態に係る半導体装置の上面図および断面図、図2(a)乃至(e)は同半導体装置の製造工程の全体を示す概要説明図である。図3(a)乃至(d)はこの半導体装置の素子領域の製造工程を示す図である。図4はこの半導体装置の要部説明図、図5はこの半導体装置の等価回路図、図6はこの半導体装置の動作説明図である。

本実施の形態の半導体装置は1対のMOSFETを集積化して形成されたもので、図1に示すように、第1の主面S1と、第1の主面S1と対向する第2の主面S2を有し、第1の主面S1側に素子領域3を形成した半導体基板1と、この第1の主面S1に形成された端子電極5と、第2の主面S2全体を覆う金属層6と、この金属層6全体を覆う遮光性のカーボンブラックを添加したソルダレジストからなる絶縁被膜7とを備えている。そして、この金属層6と絶縁被膜7の外縁が半導体基板1の外縁と一致したことを特徴とする。図5にこの半導体装置の等価回路を示すように、2つのMOSFETがドレイン電極を共通として並列接続されている。

【0019】

そしてこの半導体装置は、以下のようにして形成される。まず、半導体ウェハ10の第1の主面S1に、複数の素子領域3およびこの素子領域3にコンタクトする端子電極5を形成し、こののち半導体ウェハ10の第1の主面S1と対向する第2の主面S2を、半導体ウェハ10の外周縁部を残して、所望の厚さとなるまで、薄肉化する。そして、薄肉化された半導体ウェハ10の前記第2の主面S2に、金属層6を形成し、こののち、金属層6上に絶縁被膜7を形成し、最後に、半導体ウェハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得るものである。ここで各半導体装置は、それぞれドレインを金属層6として共通接続した1対のMOSFETを搭載したディスクリートMOSFETを構成するものである。

この半導体ウェハは、出発材料として8インチで厚さ700μmのものを用い、半導体ウェハ10の外周縁部約10mmを残して、最終的に厚さが200μmとなるように肉薄化した。そして、金属層の膜厚は20μmとし、絶縁被膜の膜厚は20μmとした。このようにしてチップサイズ1.2mm×1.2mmの半導体装置が得られる。

【0020】

次に、この半導体装置の製造方法の概要について図面を参照しつつ詳細に説明する。まず、図2(a)に示すように、8インチ、厚さ700μmの半導体ウェハを用い、この半導体ウェハ10の第1の主面S1に、複数の素子領域3を形成する。この図では詳細は省略するが、素子領域3の詳細については後述する。

次いで、図2(b)に示すように、素子領域3の形成された半導体ウェハ10の第1の主面S1に絶縁膜4を形成する。

次いで、図2(c)に示すように、半導体ウェハ10の第1の主面S1の素子領域に対向する領域を第2の主面S2側から研磨し、厚さ200μm程度になるまで肉薄化する。このとき半導体ウェハ10の外周縁から約10mmの肉厚部10Tを残している。 こののち、図2(d)に示すように、薄肉化された半導体ウェハ10の前記第2の主面S2に、スパッタリング法により、膜厚15μmのアルミニウム薄膜からなる金属層6を形成する。そして熱処理によりシリコン基板とアルミニウム薄膜とのオーミック接触をとる。

最後に、図2(e)に示すように、半導体ウェハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得る。

なお、前記実施の形態では、裏面の金属層6としてアルミニウム薄膜を用いたが、アルミニウム薄膜に限定されることなく、他の金属でも良い事はいうまでもない。例えばクロム+ニクロム+ニッケル+銀の4層構造とするなど、多層薄膜であってもよい。

【0021】

他の部分については通例の構成をとっている。

図4に要部拡大断面図を示すように、素子領域3は、エピタキシャル層1e内に形成されたP型ウェル31を貫通するように形成されたトレンチTにゲート酸化膜を介して形成された多結晶シリコン層からなるトレンチゲート33と、その両端に一定の深さを持つように形成されたN+領域からなるソース領域32sおよびドレイン領域とで構成される。そしてポリシリコンゲート33上を覆うように酸化シリコン膜からなる層間絶縁膜34が形成され、この層間絶縁膜34に開口するようにコンタクトホールが形成されている。そしてこのコンタクトホールを介して、アルミニウム電極が形成され、それぞれソース電極35s、ゲート電極35g、ドレイン電極(金属層6)が形成されている。そしてこの上層を覆う酸化シリコン膜からなる絶縁膜4に開口してソースバンプ5s、ゲートバンプ5gが形成されている。

そしてこのエピタキシャル層1eは、N型のシリコン基板1s表面に形成されており、ドレイン領域はN型のエピタキシャル層1eおよびN型基板1sで構成され、半導体チップの裏面全体が金属層6となっている。そしてこの金属層6全体を覆うように、ソルダレジストからなる絶縁被膜7が形成されている。

【0022】

すなわち、N型のシリコン基板1sの表面に形成されたN型のエピタキシャル層1e内に形成された複数のストライプ状のトレンチT内にゲート酸化膜を介して多結晶シリコン層(導電体層)を埋め込み形成したトレンチゲート33と、このシリコン基板表面を覆う酸化シリコン膜からなる層間絶縁膜34と、この層間絶縁膜34に形成された、ソースコンタクトを介してソース領域32sにコンタクトするように形成されたソース電極35sと、トレンチゲート33の周縁部でトレンチゲート33に接続されたゲート周辺配線と、ソース電極35sと同一表面上であって、前記ソース電極35sから離間した位置に形成され、前記ゲート周辺配線に接続されるゲート電極35gとを具備している(図4参照)。

【0023】

次に本発明の半導体装置の製造方法を、図3(a)乃至(d)を参照して詳細に説明する。

ストライプ状のトレンチゲート構造を有するN型MOSFETの製造方法は、図3(a)に示すように、半導体基板としてN+型のシリコンウェハを使用し、その表面にN-型のエピタキシャル層1eを形成する。このN-型のエピタキシャル層1e内にP型ウェル31を形成する。

【0024】

次に、図3(b)に示すようにフォトリソグラフィーおよびドライエッチングにより、P型ウェル31の形成されたN-型のエピタキシャル層1e表面にトレンチTを形成する。

【0025】

この後、図3(c)に示すようにトレンチ側壁に熱酸化により厚膜30nm程度のゲート酸化膜を形成したのち、トレンチT内にCVD法によって多結晶シリコン膜(トレンチゲート)を堆積し、多結晶シリコンに不純物ドーピングを行う。引き続き、化学機械研磨(CMP)あるいはエッチバックにより不要部を除去したのち、熱酸化により、この多結晶シリコン上に酸化シリコン膜からなる層間絶縁膜34を形成する。

【0026】

ソース領域32sとなるN型拡散層を形成するため、図3(d)に示すように、P型ウェル31中にイオン注入法を用いて、リン不純物を注入する。

その後、半導体チップ表面である第1の主面S1側に絶縁膜34および保護膜4を堆積しソース電極35sとソース領域32sを電気的に導通させるため、ソースコンタクト開口部を設けて、アルミニウム薄膜を形成し、ソース電極35sなどを構成する金属配線を形成する。このとき、ゲート電極35g、第2の主面S2側の金属電極6も同時に形成してもよい。そしてバンプ5s、5gを形成する。このようにして、図2(a)に示す半導体装置が形成される。図2(a)では素子領域3として詳細を省略している。

【0027】

このようにして形成された半導体装置は、図6に動作説明図を示すように、オン電流は矢印方向に流れる。ここでシリコン基板1s裏面の金属層6とでは金属層6の方が低抵抗であるため、オン電流の経路は矢印のように金属層6を経由して流れる。このように裏面に形成された金属層6は、オン抵抗の低減に大きく寄与し、動作速度の高速化をはかることができる。

【0028】

また、この金属層6を絶縁被膜で被覆しているため、ダイシング後に、真空チャックあるいはコレットで、分割された半導体装置すなわち半導体チップを搬送する際、キズがついたり、角部に割れやかけが生じ易たりすることはなく、金属層6は絶縁被膜7で確実に保護されている。これに対し、従来はこの金属層6は露出しており、ダイシング後に、真空チャックあるいはコレットで、分割された半導体装置すなわち半導体チップを搬送する際、キズがついたり、角部に割れやかけが生じ易いという問題があった。

【0029】

このように、本実施の形態の半導体装置では、剛性の高い金属層6を柔らかい絶縁被膜で覆うことで、2層構造の保護膜として作用し、保護膜自体の膜厚は薄くても強度の高い半導体チップを得ることが可能となる。この2層構造の保護膜は半導体チップの第2の主面全体を覆うように形成されているため、反りや歪み等の変形を生じにくく信頼性の高い半導体装置を提供することが可能となる。

このようにして極めて薄型で信頼性の高いチップサイズパッケージ(CSP)構造の半導体装置を得ることができる。

【0030】

また本実施の形態では、絶縁被膜7をカーボンブラックで着色されたソルダレジストで構成しているため、下地の金属層6のわずかな凹凸も吸収し、平坦な塗布膜を得ることができる。そしてこの平坦かつ平滑な塗布膜からなる絶縁被膜上に品種名や製造ロット名などを印刷し、識別表示を行う際に、金属層にキズがついたりすることもなく、また着色された絶縁被膜上に識別性に優れた識別表示を形成することが可能となる。

【0031】

また金属層6の表面を絶縁被膜で被覆することにより、外観性も良好となる。また着色剤を添加して着色された絶縁被膜とすることで、下地は見えず外観性の向上を図ることができる。

【0032】

この絶縁被膜7の膜厚は前記実施の形態に限定されるものではないが、50μm以下とするのが望ましい。50μm以下とすることにより、全体としての厚さが厚くなるのを防ぎ、さらには半導体チップの反りを低減することができる。

【0033】

なお、絶縁被膜としては、ソルダレジストに限定されることなく、ポリイミド膜、エポキシ樹脂、絶縁性シリコン樹脂、フェノール樹脂、アクリル樹脂などの有機系塗布膜、酸化アルミニウム膜、酸化シリコン膜などの酸化膜系絶縁塗布膜等が適用可能である。

また、前記絶縁被膜は、刷毛塗り法で形成したが、このほかトランスファーモールド法、印刷法、コーティング法、スクリーン印刷法など、適宜他の方法も適用可能である。

【0034】

なお、前記実施の形態では、この半導体ウェハは、出発材料として8インチで厚さ700μmのものを用い、半導体ウェハ10の外周縁部約10mmを残して、最終的に厚さが200μmとなるように肉薄化したが、最終的な厚さは、300μmよりも薄ければよく、望ましくは200μm以下である。下限はないが、製造可能要件を考慮すると1μm以上である。望ましくは特性を得る為のエピタキシャル層や基板の厚み、叉実用面として外部応力に対する強度や信頼性確保を考慮すると50μm程度であろう。

そして、金属層の膜厚は20μmとしたが、50μmより薄ければよい。50μmよりも厚いと半導体チップの全体厚が厚くなるだけでなく、金属層の熱膨張率が支配的となり反りが生じ易くなる。この金属層の膜厚は肉薄化後の半導体ウェハの膜厚の4分の1以下とするのが望ましい。

また絶縁被膜の膜厚は20μmとしたが、50μmより薄ければよい。50μmよりも厚いと半導体チップの全体厚が厚くなるだけでなく、絶縁被膜の剥離が生じ易くなる。この絶縁被膜の膜厚は金属層の膜厚よりも小さくするのが望ましい。

【0035】

さらにまた、前記実施の形態では、1対のMOSFETを搭載した半導体装置について説明したが、本発明は1個のMOSFETを用いた半導体装置、あるいは他の半導体装置にも適用可能であることはいうまでもない。

【0036】

(実施の形態2)

次に本発明の実施の形態2について説明する。

図7は本発明の実施の形態2にかかる半導体装置の断面図である。

前記実施の形態では絶縁被膜7としてソルダレジストからなる塗布膜を用いたが、本実施の形態では、図7に示すように、フィルムレジストからなる絶縁被膜7t、つまり貼着により装着するテープ材料を用いたものである。

【0037】

他の構成については前記実施の形態1と同様であり、ここでは説明を省略する。なお図7において、同一部材には図1において用いたものと同一符号を付した。

この構成によれば、金属層6の裏面にテープ材料等のシート状樹脂フィルムを貼着することで、膜厚のばらつきを低減し、ピンホールのない、絶縁被膜7tを形成することが可能となる。金属層6の裏面に貼着すればよいため、取扱がきわめて容易である。

なお、このテープ材料としては、エポキシ樹脂(Epoxy resin)、エポキシ樹脂に、シリカ(Silica)あるいはアクリル樹脂(Acrylic polymer)を混合した混合体、黒色の色を得る為に、0.1〜5%のカーボンブラックを混合したもの(Black film)、フィルムレジスト、あるいは樹脂テープに接着剤を塗布したものなどが適用可能である。

【0038】

(実施の形態3)

次に本発明の実施の形態3について説明する。

図8は本発明の実施の形態3にかかる半導体装置の断面図である。

前記実施の形態では絶縁被膜は単層膜で構成したが、本実施の形態では、図8に示すように、透光性の絶縁膜であるポリイミド膜7aと、カーボンブラックを添加した黒色のポリイミド膜7bとの2層膜を用いたものである。他は図1で示した半導体装置と同様であるためここでは説明を省略する。なお図8において、同一部材には図1において用いたものと同一符号を付した。

【0039】

この構成によれば、絶縁被膜を2層膜で構成しているため、キズを防ぐような硬い膜と密着性を向上するような展性の高い膜との2層膜とするなど、それぞれの膜に機能を持たせることもできる。また、最表層にのみ着色を行うようにしてもよい。

また、金属層に接する層は金属酸化膜、酸化シリコン膜あるいは窒化シリコン膜などの無機膜とし、表層側は有機系の塗布膜、あるいは樹脂シートなどで構成してもよい。

【0040】

以下は、この半導体装置の製造方法の変形例について説明する。

【0041】

(実施の形態4)

前記実施の形態1では図2(e)の工程において、外周縁に肉厚部10Tを残した半導体ウェハ10の、中央部の肉薄部をダイシングラインD.Lに沿って一挙に個片分割したが、本実施の形態では、図9(a)乃至(c)に示すように、一旦、外周ラインO.D.Lに沿って八角形に切断し、肉厚部10Tを切り落とした後、ダイシングラインD.Lに沿って個々の半導体チップに分断するものである。

図9(a)および(b)は断面図および上面説明図である。

図9(c)はこの八角形に切断された半導体ウェハから半導体チップ10cを切り出す工程を示す図である。

図9(d)はこの八角形に切断された半導体ウェハから切りだされた半導体チップ10cを示す図である。

なお、八角形に限定されず、多角形もしくは、略円形でもよい事は言うまでもない。

【0042】

他部については、前記実施の形態1と同様であり、ここでは説明を省略する。

この方法によれば、一旦肉厚部10Tを切り落とした後、ダイシングラインD.Lに沿って個々の半導体チップに分断するため、ダイシングが容易で、切断面の美しい切断が可能となる。

【0043】

他部については、前記実施の形態1と同様であり、ここでは説明を省略する。

この方法によれば、ダイシングが容易で、切断面の美しい切断が可能となる。

本実施の形態についても、詳細については省略するが、前記実施の形態1で説明したものと同様である。

【0044】

(実施の形態5)

前記実施の形態1では出発材料として700μmの半導体ウェハを用い、図2(c)の工程において、外周縁に肉厚部10Tを残すように、半導体ウェハ10の中央部を研磨し、一挙に肉薄部を形成したが、本実施の形態では、第2の主面S2側から研磨し、一旦、厚さ300μm程度になるまで肉薄化し、こののち外周縁に肉厚部10Tを残すように、半導体ウェハ10の中央部を研磨し、肉薄部を形成する。そしてこののちダイシングラインD.Lに沿って個片分割し、個々の半導体チップに分断するものである。

【0045】

まず、前記実施の形態1と同様、8インチ、厚さ700μmの半導体ウェハを用い、この半導体ウェハ10の第1の主面S1に、複数の素子領域3を形成し、さらに素子領域3の形成された半導体ウェハ10の第1の主面S1に絶縁膜4を形成する。

【0046】

図2(a)および(b)に示した工程までは前記実施の形態1と同様である。そしてこののち、図10(a)に示すように、半導体ウェーハ10の第2の主面S2側から全面研磨し、一旦、厚さ300μm程度になるまで肉薄化する。

【0047】

そして、図2(c)に示したのと同様、図10(b)に示すように、半導体ウェーハ10の第1の主面S1の素子領域に対向する領域を第2の主面S2側から研磨し、厚さ200μm程度になるまで肉薄化する。このとき半導体ウェーハ10の外周縁から約10mmの肉厚部10Tを残している。

【0048】

こののち、図10(c)に示すように、薄肉化された半導体ウェーハ10の前記第2の主面S2に、スパッタリング法により、膜厚15μmのアルミニウム薄膜からなる金属層6を形成する。そして熱処理によりシリコン基板とアルミニウム薄膜とのオーミック接触をとる。ここでも金属層としてはアルミニウム薄膜に限定されることなく、他の金属でも良く、またクロム+ニクロム+ニッケル+銀などの多層膜で構成してもよい。

【0049】

最後に、絶縁被膜7を形成し、図10(d)に示すように、半導体ウェーハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得る。

【0050】

この方法によれば、一旦肉薄化してから、素子領域に対向する面側を肉薄化しているため、半導体基板の受けるストレスは低減され、信頼性の高い半導体装置を提供することが可能となる。

【0051】

(実施の形態6)

前記実施の形態5では図10(d)の工程において、外周縁に肉厚部10Tを残した半導体ウェーハ10の、中央部の肉薄部をダイシングラインD.L.に沿って一挙に個片分割したが、本実施の形態では、図11(a)乃至(d)に示すように、一旦、外周ラインO.D.L.に沿って八角形に切断し、肉厚部10Tを切り落とした後、ダイシングラインD.L.に沿って個々の半導体チップに分断するものである。

図11(a)および(b)は断面図および上面説明図である。

図11(c)はこの八角形に切断された半導体ウェーハから半導体チップ10cを切り出す工程を示す図である。

図11(d)はこの八角形に切断された半導体ウェーハから切りだされた半導体チップ10cを示す図である。

なお、八角形に限定されず、多角形もしくは、略円形でもよい事は言うまでもない。

【0052】

他部については、前記実施の形態5と同様であり、ここでは説明を省略する。

この方法によれば、一旦肉厚部10Tを切り落とした後、ダイシングラインD.L.に沿って個々の半導体チップに分断するため、ダイシングが容易で、切断面の美しい切断が可能となる。

【0053】

(実施の形態7)

前記実施の形態5では図10(d)の工程において、半導体ウェーハ10の第2の面全体に絶縁被膜を形成したが、図12に示すように外周縁に肉厚部10Tを残した半導体ウェーハ10の、中央部の肉薄部の第2の主面S2側に選択的に樹脂膜からなる絶縁被膜7tを形成してもよい。以下にこの絶縁被膜7tの貼着方法について説明するが、他の工程については前記実施の形態6と同様であるためここでは説明を省略する。

【0054】

なお、このテープ材料としてエポキシ樹脂を主成分とする絶縁被膜7tを貼着する方法の一例を説明する。図13(a)乃至(d)、図14(a)乃至(c)、図15(a)乃至(c)は本発明の実施の形態7に係る半導体装置の製造工程における絶縁被膜の貼着工程を示す概要説明図である。樹脂材料としては前記実施の形態2で説明した材料と同様の樹脂が適用可能である。以下の図では半導体ウェーハ10のうち1ユニットの半導体基板1となる部分のみウェハとして示す。

ず、図13(a)に示すように、絶縁被膜7tとなる、エポキシ樹脂を主成分とする絶縁性樹脂を、PETフィルムからなる第1の剥離材17上に成膜し、第2の剥離材27を貼り合わせて、3層構造の絶縁テープを形成する。

そして、図13(b)に示すように、絶縁被膜7tと第2の剥離材27をウェーハ形状に符合したカッティングラインC.L.に沿ってほぼ円形あるいは多角形状にカットする。

こののち、図13(c)に示すように、第1の剥離材17に貼着された絶縁被膜7tを第2の剥離材27から剥離し、図13(d)に示すように、ウェーハ形状に符合したてほぼ円形あるいは多角形状にカットされた絶縁被膜7tを得る。

【0055】

そして、図14(a)に示すように、加熱ステージ400を80℃程度に加熱し、この加熱ステージ400上にウェハ(半導体基板1)を載置し、上記絶縁被膜7tの位置合わせを行う。

そして、図14(b)に示すように、絶縁被膜7tと第1の剥離材17を、60℃に加熱したローラ500を50mm/secで回転させ、ウェハ(半導体基板1)裏面に絶縁被膜7tを仮固着する。

こののち、図14(c)に示すように、第1の剥離材17上の絶縁被膜7tに貼着されたウェーハ1ごと加熱ステージ400から退避させる。

【0056】

そして、図15(a)に示すように、常温の冷却ステージ600にウェハ(半導体基板1)を載置する。

そして、図15(b)に示すように、絶縁被膜7tから第1の剥離材17を、剥離する。

こののち、図15(c)に示すように、ウェハ(半導体基板1)1上の絶縁被膜7tを冷却ステージ600から分離後、130℃で2時間硬化させて、一体化する。

【0057】

なお、前記半導体装置においてはバンプを形成した半導体装置について説明したが、必ずしもバンプは必要ではなく、別途スティフナーと呼ばれる支持基板を用いてソルダボールとの接続を行うなど適宜変更可能である。

【産業上の利用可能性】

【0058】

以上説明してきたように、本発明によれば、薄型で信頼性の高い半導体装置において高歩留まり化が可能であることから、リチウムイオン二次電池の制御回路などに有効である。

【符号の説明】

【0059】

S1 第1の主面

S2 第2の主面

1 半導体基板

1s シリコン基板

1e エピタキシャル層

3 素子領域

4 絶縁膜

6 金属層

7、7t 絶縁被膜

10 半導体ウェハ

17 第1の剥離材

T トレンチ

27 第2の剥離材

31 P型ウェル

32s ソース領域

34 層間絶縁膜

33 トレンチゲート

35s ソース電極

35g ゲート電極

【特許請求の範囲】

【請求項1】

半導体ウェーハの第1の主面に、複数の素子領域および前記素子領域にコンタクトする端子電極を形成する素子形成工程と、

前記半導体ウェーハの前記第1の主面と対向する第2の主面を、前記半導体ウェーハの外周縁部を残して、所望の厚さとなるまで、薄肉化する工程と、

薄肉化された前記半導体ウェーハの前記第2の主面に、金属層を形成する工程と、

前記金属層上に絶縁被膜を形成する工程と、

前記半導体ウェーハの前記素子領域を分割し、複数の半導体装置に分断する工程とを含む半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法であって、

前記分断する工程は、前記半導体ウェーハの外周縁部を切り取るように、第2主面側から多角形状にカットを行う工程である半導体装置の製造方法。

【請求項3】

請求項1に記載の半導体装置の製造方法であって、

前記薄肉化する工程に先立ち、前記第2の主面を全面研磨し、前記半導体ウェーハを中間的な厚さまで薄肉化する工程を含む半導体装置の製造方法。

【請求項4】

請求項1乃至3のいずれかに記載の半導体装置の製造方法であって、

前記絶縁被膜を形成する工程は、樹脂膜を形成する工程を含む半導体装置の製造方法。

【請求項5】

請求項4に記載の半導体装置の製造方法であって、

前記樹脂膜を形成する工程は、シート状樹脂フィルムを貼着する工程である半導体装置の製造方法。

【請求項6】

請求項4に記載の半導体装置の製造方法であって、

前記樹脂膜を形成する工程は、塗布膜を形成する工程である半導体装置の製造方法。

【請求項7】

請求項1に記載の半導体装置の製造方法であって、

前記肉薄化する工程は、少なくとも中央部の厚さが300μm以下となるように前記半導体ウェーハを研磨する工程である半導体装置の製造方法。

【請求項8】

請求項1に記載の半導体装置の製造方法であって、

前記肉薄化する工程は、半導体ウェーハの外周端面よりも1から20mm程度の外周端部を残すように前記半導体ウェーハを研磨する工程である半導体装置の製造方法。

【請求項9】

請求項8に記載の半導体装置の製造方法であって、

前記素子形成工程は、

前記素子領域は、第1の導電型のシリコン基板表面に形成された第1の導電型の半導体層内に形成された複数の第2導電型の半導体領域と、前記複数の第2導電型の半導体領域を貫通する複数のトレンチと、前記複数のトレンチの内壁にゲート絶縁膜を介して形成されたゲート電極と、前記第2導電型の半導体領域内に形成された第1導電型の半導体領域からなる複数のソース領域とを具備し、

前記第1の主面に形成される前記端子電極が、

前記ゲート電極のそれぞれに接続されるゲート端子と、

前記ソース領域のそれぞれに接続されるソース端子とで構成され、

前記第2の主面に形成される前記金属層は、前記シリコン基板の裏面全体を覆い、共通のドレイン電極を構成しており、

前記絶縁被膜は前記金属層全体を覆うように形成された半導体装置を前記半導体ウェーハ上に複数個形成する工程である半導体装置の製造方法。

【請求項1】

半導体ウェーハの第1の主面に、複数の素子領域および前記素子領域にコンタクトする端子電極を形成する素子形成工程と、

前記半導体ウェーハの前記第1の主面と対向する第2の主面を、前記半導体ウェーハの外周縁部を残して、所望の厚さとなるまで、薄肉化する工程と、

薄肉化された前記半導体ウェーハの前記第2の主面に、金属層を形成する工程と、

前記金属層上に絶縁被膜を形成する工程と、

前記半導体ウェーハの前記素子領域を分割し、複数の半導体装置に分断する工程とを含む半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法であって、

前記分断する工程は、前記半導体ウェーハの外周縁部を切り取るように、第2主面側から多角形状にカットを行う工程である半導体装置の製造方法。

【請求項3】

請求項1に記載の半導体装置の製造方法であって、

前記薄肉化する工程に先立ち、前記第2の主面を全面研磨し、前記半導体ウェーハを中間的な厚さまで薄肉化する工程を含む半導体装置の製造方法。

【請求項4】

請求項1乃至3のいずれかに記載の半導体装置の製造方法であって、

前記絶縁被膜を形成する工程は、樹脂膜を形成する工程を含む半導体装置の製造方法。

【請求項5】

請求項4に記載の半導体装置の製造方法であって、

前記樹脂膜を形成する工程は、シート状樹脂フィルムを貼着する工程である半導体装置の製造方法。

【請求項6】

請求項4に記載の半導体装置の製造方法であって、

前記樹脂膜を形成する工程は、塗布膜を形成する工程である半導体装置の製造方法。

【請求項7】

請求項1に記載の半導体装置の製造方法であって、

前記肉薄化する工程は、少なくとも中央部の厚さが300μm以下となるように前記半導体ウェーハを研磨する工程である半導体装置の製造方法。

【請求項8】

請求項1に記載の半導体装置の製造方法であって、

前記肉薄化する工程は、半導体ウェーハの外周端面よりも1から20mm程度の外周端部を残すように前記半導体ウェーハを研磨する工程である半導体装置の製造方法。

【請求項9】

請求項8に記載の半導体装置の製造方法であって、

前記素子形成工程は、

前記素子領域は、第1の導電型のシリコン基板表面に形成された第1の導電型の半導体層内に形成された複数の第2導電型の半導体領域と、前記複数の第2導電型の半導体領域を貫通する複数のトレンチと、前記複数のトレンチの内壁にゲート絶縁膜を介して形成されたゲート電極と、前記第2導電型の半導体領域内に形成された第1導電型の半導体領域からなる複数のソース領域とを具備し、

前記第1の主面に形成される前記端子電極が、

前記ゲート電極のそれぞれに接続されるゲート端子と、

前記ソース領域のそれぞれに接続されるソース端子とで構成され、

前記第2の主面に形成される前記金属層は、前記シリコン基板の裏面全体を覆い、共通のドレイン電極を構成しており、

前記絶縁被膜は前記金属層全体を覆うように形成された半導体装置を前記半導体ウェーハ上に複数個形成する工程である半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2012−182239(P2012−182239A)

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願番号】特願2011−42990(P2011−42990)

【出願日】平成23年2月28日(2011.2.28)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願日】平成23年2月28日(2011.2.28)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]