半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

LSI(large scale integrated circuit:大規模集積回路)の集積度が増して、トランジスタのゲート電極の幅が微細化すると、ゲート電極及びソース・ドレインが平面的に配置されたトランジスタにおいては、チャネル長が短くなって、ソース・ドレイン間のリーク電流を抑制することが困難になってくる。

そこで、チャネル構造を立体的にすることが試みられている。チャネル構造を立体的にしたトランジスタとして、リセス構造のトランジスタ(Recessed Channel Transistor:RCAT)が挙げられる。

【0003】

リセス構造のトランジスタにおいては、ゲート電極の一部が、半導体基板に形成された溝の内部に埋め込まれている。そして、溝の内壁に形成された絶縁膜がゲート絶縁膜となり、半導体基板の溝に沿った領域がチャネルを構成する。

このように、チャネル構造を立体的にすることによってチャネル長をリーク電流の抑制が可能な程度に長く確保しつつ、ゲート電極の幅を微細化することができる。

また、このような立体的な構造においては、ソース・ドレイン端が広がり、チャネルを流れる電流量を増加させることもできる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−081107号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の実施形態は、高集積化を図ることができる半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0006】

実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程と、前記柱状体をマスクとしてエッチングすることにより、前記露出した部分の下部を除去する工程とを備える。

【0007】

また、実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分を除去する工程と、前記電極加工側壁を除去する工程とを備える。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態に係る半導体装置を例示する斜視図である。

【図2】第1の実施形態に係る半導体装置を例示する断面図であり、図1に示すA−A’面による断面図である。

【図3】第2の実施形態に係る半導体装置を例示する断面図である。

【図4】第3の実施形態に係る半導体装置を例示する断面図である。

【図5】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図6】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図7】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図8】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図9】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図10】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図11】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図12】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図13】第4の実施形態に係る半導体装置の製造方法を例示する工程平面図である。

【図14】図13に示すA−A’線による工程断面図である。

【図15】図13に示すB−B’線による工程断面図である。

【図16】図13に示すC−C’線による工程断面図である。

【図17】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図18】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図19】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図20】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図21】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図22】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図23】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図24】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図25】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図26】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図27】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図28】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図29】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図30】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図31】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図32】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図33】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図34】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図35】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図36】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図37】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図38】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図39】第4の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図である。

【図40】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図41】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図42】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図43】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図44】第6の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図45】第6の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図46】第6の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【発明を実施するための形態】

【0009】

(第1の実施形態)

以下、図面を参照しつつ、本発明の実施形態について説明する。

先ず、第1の実施形態について説明する。

本実施形態は、半導体装置についてのものである。

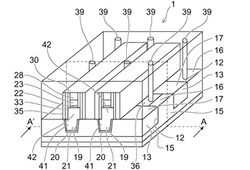

図1は、第1の実施形態に係る半導体装置を例示する斜視図である。

図2は、第1の実施形態に係る半導体装置を例示する断面図であり、図1に示すA−A’面による断面図である。

【0010】

先ず、第1の実施形態に係る半導体装置の構成について説明する。

図1及び図2に示すように、半導体装置1においては、半導体基板、例えばシリコン基板10が設けられている。シリコン基板10の上面には、1つの方向に延びる複数の溝12が平行に形成されている。溝12の内部には、絶縁材料、例えば酸化シリコン13が埋め込まれている。溝12の内部に酸化シリコン13が埋め込まれた領域をSTI領域(Shallow Trench Isolation)17とする。STI領域17に挟まれた領域を活性領域16とする。

シリコン基板10には、シリコン基板10の表面から、溝12の底面より深い領域まで、不純物、例えばボロンが導入されて、ウェル15が形成されている。

シリコン基板10には、STI領域17及び活性領域16が延びる方向に直交する方向に延びる溝19が設けられている。

【0011】

溝19の内面上には、ゲート絶縁膜、例えばシリコン酸化膜20が設けられている。また、溝19の内部には、導電材料、例えばポリシリコンが埋め込まれている。溝19の内部に埋め込まれたポリシリコンの部分を、下部導電部41という。ポリシリコンには、不純物、例えばリンが導入されている。

活性領域16の表層部分における溝19の外縁を含む領域には、不純物、例えばリンが導入された拡張領域34が形成されている。活性領域16の表層部分における溝を挟んで両側の拡張領域34の隣には、それぞれソース・ドレイン領域36が形成されている。ソース・ドレイン領域36には、不純物、例えばリンが、拡張領域34に導入された濃度より高濃度で導入されている。また、ソース・ドレイン領域36には、不純物が、拡張領域34より深く導入されている。

【0012】

また、溝19の直上域の一部を含む領域には、溝19に沿って、溝19の幅と略等しい幅で、導電材料からなる柱状体が設けられている。ここで、溝19の幅方向の長さを「幅」という。この溝19上に設けられた柱状体は、溝19の内部に埋設された導電材料と同じ材料のポリシリコンからなり、溝19の内部に埋め込まれた下部導電部41と一体化している。溝19上に設けられたポリシリコンの柱状体を、上部導電部42という。

上部導電部42と下部導電部41を合わせて導電部43という。

上部導電部42の位置と、下部導電部41及び溝19の位置とは、ズレが生じている。ズレは想定される範囲のものである。

【0013】

上部導電部42上には、バリアメタル層22が設けられている。バリアメタル層22としては、チタンと窒化チタンの積層膜が挙げられる。バリアメタル層22上には、低抵抗金属層23が設けられている。低抵抗金属層23の材料としては、タングステンがあげられる。低抵抗金属層23上には、ハードマスク28が設けられている。ハードマスク28の材料としては、窒化シリコンがあげられる。導電部43、バリアメタル層22及び低抵抗金属層23とから、ゲート電極が形成される。

【0014】

ハードマスク28、低抵抗金属層23及びバリアメタル層22は積層して、柱状体29を構成している。柱状体29におけるバリアメタル層22が、チタンと窒化チタンの積層膜である場合には、製造工程における酸化熱処理で、積層膜に含まれるチタンが酸化することがある。そこで、チタンの酸化を防ぐために、ハードマスク28、低抵抗金属層23及びバリアメタル層22の積層体の側面には、バリアメタル側壁30が設けられている。バリアメタル側壁30の材料としては、窒化シリコンがあげられる。バリアメタル側壁30が設けられている場合は、バリアメタル側壁30を含んだ積層構造を柱状体29という。

【0015】

上部導電部42及び柱状体29とで、柱状体32を構成する。

柱状体32の側面には、エクステンション側壁33とソース・ドレイン側壁35が設けられている。エクステンション側壁33の側面の端部を上から見た位置は、拡張領域34の溝19側の端部を上から見た位置と略同一である。ソース・ドレイン側壁35の側面の端部を上から見た位置は、ソース・ドレイン領域36の溝19側の端部を上から見た位置と略同一である。

【0016】

シリコン基板10上には層間絶縁膜37が設けられている。なお、図1においては、図を見やすくするために、層間絶縁膜37を省略してある。層間絶縁膜37におけるソース・ドレイン領域36上にはコンタクトホール38が形成されている。コンタクトホール38の内部には、コンタクト39が設けられている。

ソース・ドレイン領域36の表面は、シリサイド、例えばニッケルシリサイドが設けられている。コンタクトホール38内部に埋設されたコンタクト39はソース・ドレイン表面におけるシリサイドに接合されている。

【0017】

次に、第1の実施形態に係る半導体装置の動作について説明する。

先ず、半導体装置1のゲート電極に電圧を負荷する。そうすると、溝19の内面上に設けられたシリコン酸化膜20が、ゲート絶縁膜として働く。シリコン基板10の溝19に沿った領域がチャネルとして働き、反転層が形成される。そしてソース・ドレイン間に電圧を負荷すれば、反転層内をキャリアが移動し、電流が流れる。ゲート電極の電圧を変化させることによって、ソース・ドレイン間を流れる電流量を制御する。

【0018】

次に、第1の実施形態に係る半導体装置の効果について説明する。

リセス構造にするための溝19の内部にゲート電極の一部となるポリシリコンを完全に埋設することができる。よって、デザインルールが微細化して、リソグラフィーによる溝とゲート電極との間にズレが生じるようになっても、リセス構造のトランジスタを製造することができる。したがって、ゲート電極の幅を微細化しつつ、チャネル長を増加させ、高集積化した半導体装置を提供することができる。

【0019】

(第2の実施形態)

次に、第2の実施形態に係る半導体装置について説明する。

図3は、第2の実施形態に係る半導体装置を例示する断面図である。

図3に示すように、本実施形態においては、上部導電部42の側面には、段差が設けられている。

段差における上方を向いた面の幅は、溝19の位置と柱状体32の位置のズレの幅と略等しい。

【0020】

上部導電部42の上面の幅は、柱状体29の幅及び溝19の幅と略同一である。

一方、上部導電部42の下面の幅は、柱状体29の幅及び溝19の幅より大きい。

エクステンション側壁及びソース・ドレイン側壁は、柱状体32の側面形状に合わせて設けられている。

エクステンション側壁33の側面の最も外側の端部を上から見た位置は、拡張領域34の溝19側の端部を上から見た位置と略同一である。ソース・ドレイン側壁35の側面の最も外側の端部を上から見た位置は、ソース・ドレイン領域36の溝19側の端部を上から見た位置と略同一である。

その他の構成は、第1の実施形態と同様であるので省略する。また、動作も同様であるので省略する。

【0021】

次に、第2の実施形態に係る半導体装置の効果について説明する。

第2の実施形態においては、上部導電部42の下部の幅が広くなっている。したがって、下部導電部41を覆い、リセス構造にするための溝19の内部に電極の一部となるポリシリコンを完全に埋設することができる。よって、リセス構造を実現し、高集積化した半導体装置を提供することができる。

【0022】

(第3の実施形態)

次に、第3の実施形態について説明する。

図4は、第3の実施形態に係る半導体装置を例示する断面図である。

図4に示すように、本実施形態においては、上部導電部42の幅は、柱状体29の幅及び溝19の幅より大きい幅で設けられている。また、上部導電部42の側面には、第2の実施形態と異なり、段差が設けられていない。

エクステンション側壁及びソース・ドレイン側壁は、第2の柱状体の側面形状に合わせて設けられている。

その他の構成は、第1の実施形態と同様であるので省略する。また、動作及び効果も同様であるので省略する。

【0023】

(第4の実施形態)

次に、第4の実施形態について説明する。

本実施形態は、第1の実施形態に係る半導体装置の製造方法についてのものである。

図5〜12は、第4の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、

図13は、第4の実施形態に係る半導体装置の製造方法を例示する工程平面図であり、

図14は、図13に示すA−A’線による工程断面図であり、

図15は、図13に示すB−B’線による工程断面図であり、

図16は、図13に示すC−C’線による工程断面図であり、

図17〜図38は、第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【0024】

先ず、図5に示すように、例えば単結晶のシリコン(Si)からなるシリコン基板10を用意する。

そして、図6に示すように、シリコン基板10上にハードマスク11となる膜として、例えばSiN膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク11を形成する。ハードマスク11は、シリコン基板10上の1つの方向に平行に形成する。

【0025】

次に、図7に示すように、ハードマスク11をマスクとして反応性イオンエッチングを行い、シリコン基板10の上層部分にSTI領域17となる溝12を形成する。このとき、ハードマスク11に覆われて、エッチングされない領域が活性領域16となる。

その後、図8に示すように、溝12及びハードマスク11を含むシリコン基板10上をシリコン酸化膜13で覆う。

そして、図9に示すように、CMP(chemical mechanical polishing:化学的機械研磨)法によって、ハードマスクの表面が現れるまでシリコン酸化膜13を研磨し、シリコン酸化膜13の上面を平坦化する。

【0026】

次に、図10に示すように、ウェットエッチングによって、ハードマスク11の下面まで、すなわち、シリコン基板10におけるハードマスク11に覆われた部分の上面まで、シリコン酸化膜13を除去する。

その後、図11に示すように、ウェットエッチングにより、ハードマスク11(図10参照)を除去する。シリコン基板10の上面が現れている領域が活性領域16である。また、溝12の中にシリコン酸化膜13が埋め込まれた領域がSTI領域17である。STI領域17ではシリコン酸化膜13の上面が表面に現れている。

【0027】

そして、図12に示すように、活性領域16及びSTI領域17を含むシリコン基板10の上面上に、シリコン酸化膜14を形成する。その後、シリコン酸化膜14上から、イオン注入法によって、不純物として例えばボロンを導入する。導入する深さは、シリコン基板10の表面から溝12の底部より深い領域までとする。これによって、活性領域16においては、シリコン基板10の上面から、溝12の底部より深い領域に相当する深さまで、シリコン基板10中にボロンが導入される。STI領域17においては、溝12の底面から、溝12の底部より深い領域まで、シリコン基板10中にボロンが導入される。シリコン基板10におけるボロンが導入された部分がp形のウェル15となる。

【0028】

図13〜図16に示すように、上述の工程により、シリコン基板10上に、1つの方向に平行に延びるSTI領域17が形成される。そして、STI領域17の間に配置されるように活性領域16が形成される。シリコン基板10の表面にはシリコン酸化膜14が形成されているが、図13においては、図示を省略してある。

【0029】

次に、図17に示すように、図13のB−B’線における断面に相当する断面においては、シリコン基板10上にハードマスク18となる膜として、例えばSiN膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク18を形成する。ハードマスク18は、STI領域17を形成するための溝12と直交する方向に延びている。

【0030】

次に、図18に示すように、ハードマスク18をマスクとして、反応性イオンエッチングを行うことにより、シリコン酸化膜14及びシリコン基板10を選択的に除去する。これにより、溝19が形成される。

また、図19に示すように、図13のC−C’線における断面に相当する断面においては、STI領域17においても、シリコン基板10上にハードマスク18となる膜として、SiN膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク18を形成する。

次に、図20に示すように、ハードマスク18をマスクとして、反応性イオンエッチングにより、シリコン酸化膜13及びシリコン酸化膜14を選択的に除去する。これにより、溝19が形成される。

このように、図13に示すB−B’線による活性領域における溝19の内部と、図13に示すC−C’線によるSTI領域における溝19の内部は同じ構成となっている。そこで、以後は活性領域における工程断面図のみ示す。

【0031】

次に、図21に示すように、シリコン基板10上のハードマスク18及びシリコン酸化膜14を除去する。

その後、図22に示すように、溝19の内面上及びシリコン基板10の上面上にゲート絶縁膜となるシリコン酸化膜20を形成する。

【0032】

次に、図23に示すように、シリコン酸化膜20上からゲート電極の一部となるポリシリコン膜21を形成する。このポリシリコン膜にはリンが不純物として導入されている。ポリシリコン膜21は、溝19内を埋め込むように形成する。

その後、図24に示すように、ポリシリコン膜21上からバリアメタル層22として、例えばチタンと窒化チタンの積層膜を積層する。そして、その上から低抵抗金属層23として、例えばタングステン(W)膜を形成する。本実施形態において、ゲート電極は、ポリシリコン膜21、バリアメタル層22及び低抵抗金属層23を含んでいる。バリアメタル層22の材料としては、チタンと窒化チタンの積層膜の他、窒化チタンがあげられる。

【0033】

そして、図25に示すように、低抵抗金属層23上から、シリコン窒化膜24及び有機膜25を形成した後、その上に、シリコン酸化膜26を形成する。さらにシリコン酸化膜26上に、レジスト27を形成する。このとき、レジスト27の形成領域は、溝19の直上域と一致させることを目標とする。しかし、リソグラフィーの合わせズレにより、これらの位置にはズレが生じる場合がある。しかし、このズレの量はリソグラフィー法の精度から予測される範囲内にあり、溝19の幅よりも小さい。したがって、レジスト27は、溝19の直上域の一部を含む領域に形成される。

【0034】

次に、レジスト27をマスクとして、シリコン酸化膜26をパターニングする。

その後、図26に示すように、パターニングされたシリコン酸化膜26をマスクとして有機膜25及びシリコン窒化膜24を加工する。溝19とレジスト27との間のあわせズレと同じ幅のズレが、溝19とシリコン酸化膜26、有機膜25及びシリコン窒化膜24との間にも生じる。

【0035】

図27に示すように、本実施形態では、シリコン酸化膜26及び有機膜25を除去し、パターニングされたシリコン窒化膜24をハードマスク28とする。

次に、図28に示すように、ハードマスク28をマスクとして反応性イオンエッチングを行い、低抵抗金属層23及びバリアメタル層22を選択的に除去する。これによって、ハードマスク28で覆われている部分には、低抵抗金属層23及びバリアメタル層22からなるゲート電極の一部が形成される。

一方、ハードマスク28で覆われていない部分の表面には、ポリシリコン膜21が現れている。

【0036】

バリアメタル層22として窒化チタンとチタンの積層膜を用いた場合は、ゲート電極加工後の後酸化のときにチタンが酸化されて劣化する可能性がある。

そこで、図29に示すように、ハードマスク28、低抵抗金属層23及びバリアメタル層22を含む多層膜の側面上に、バリアメタル側壁30を形成する。バリアメタル側壁30の材料としては、例えば、シリコン窒化膜があげられる。バリアメタル側壁30は、CVD法(chemical vapor deposition:化学気相成長法)等により、シリコン窒化膜を形成した後、ハードマスク28、低抵抗金属層23及びバリアメタル層22を含む多層膜の側面上以外の部分を除去して形成する。

バリアメタル側壁30を形成した場合は、バリアメタル側壁30、ハードマスク28、低抵抗金属層23及びバリアメタル層22を含む多層膜を柱状体29という。バリアメタル側壁30を形成しない場合は、ハードマスク28、低抵抗金属層23及びバリアメタル層22を含む多層膜を柱状体29という。

【0037】

次に、図30に示すように、バリアメタル側壁30の側面上に電極加工側壁31を形成する。電極加工側壁31は、炭素を含む膜から形成される。炭素を含む膜の形成方法としては、CVD法等の成膜手法を用いて形成する方法と、エッチング時の反応生成物により形成する方法があげられる。CVD法等による方法では、先ず、シリコン基板10上に、炭素、水素及び窒素を含む膜を形成する。炭素の含有率が100%に近い膜も形成することができる。炭素、水素及び窒素を含む膜を形成した後に、柱状体29の側壁上以外の部分を除去して電極加工側壁31を形成する。エッチング時の反応生成物により形成する方法では、シリコン基板10上に、エッチング時の反応生成物により形成されたフルオロカーボン膜において、柱状体29の側壁上以外の部分を除去して形成する。バリアメタル側壁30の側面上における電極加工側壁31の厚さは、溝19の位置とハードマスク28の位置との間に想定される合わせズレ幅以上の膜厚とする。

【0038】

次に、ポリシリコン膜21の加工を行う。本実施形態においては、ゲート電極は、ポリシリコン膜21、バリアメタル層22及び低抵抗金属層23の三層構造とされている。したがって、ポリシリコン膜21は、ゲート電極の最下層膜となっている。

図31に示すように、電極加工側壁31及び柱状体29をマスクとしてポリシリコン膜21のエッチングを行う。これによって、ゲート電極間のポリシリコン膜21はエッチングされるが、電極加工側壁31で覆われたポリシリコン膜21はエッチングされない。

【0039】

そして、ゲート電極間のポリシリコン膜21を完全に除去せずに、エッチングを途中で一旦停止する。一旦停止することによって、電極加工側壁31で覆われたポリシリコン膜21の厚さを、ゲート電極間のポリシリコン膜21の厚さより厚く残しておく。ゲート電極間の絶縁を完全にするために行うオーバーエッチング時に、電極加工側壁31で覆われたポリシリコン膜21が除去されるようにする。そうすれば、溝19の位置とゲート電極の位置との間にズレが生じていても、下部導電部41がエッチングされずにすむ。

【0040】

次に、エッチングを途中で一旦停止するときのポリシリコン膜21の厚さについて説明する。

図31に示すように、ゲート電極間、すなわち、溝19が設けられていない部分のシリコン基板10上におけるポリシリコン膜21の厚さAが、次式(1)で表される厚さまで薄くなった時に、エッチングを途中で一旦停止する。

A=B−(B・X/100) (1)

ここで、Bは、電極加工側壁31の形成前における溝19が形成されていない部分のシリコン基板10上のポリシリコン膜21の厚さである。Xは、オーバーエッチング量を表し、単位は%である。オーバーエッチング量とは、シリコン基板10上の表面において、ポリシリコン膜を除去したとしても、ゲート電極間の絶縁を完全なものとするために余分に行うエッチング量である。

【0041】

Xが少ないほどコストが少なくてすむ。しかし、ポリシリコン膜21の厚さのばらつきを考慮し、ゲート電極間の絶縁を図るために、オーバーエッチング量は例えば30%以上とすることが好ましい。ゲート電極間の絶縁を向上させてトランジスタの歩留まりを上げつつ、生産コストを低下するためには、オーバーエッチング量は50%程度が好ましい。

【0042】

例えば、カーボン側壁31の形成前における溝19が形成されていないシリコン基板10上のポリシリコン膜21の厚さが100nmのとき、オーバーエッチング量を30%とすると、

100−(100・30/100)=70

となり、溝19が設けられていない部分のシリコン基板10上におけるポリシリコン膜21の厚さAが70nmまで薄くなった時に、ポリシリコン膜21のエッチングを一旦停止して、電極加工側壁31を除去することになる。

また、例えば、オーバーエッチング量を50%とすると、

100−(100・50/100)=50

となり、溝19が設けられていない部分のシリコン基板10上におけるポリシリコン膜21の厚さAが50nmまで薄くなった時に、ポリシリコン膜21のエッチングを一旦停止して、電極加工側壁31を除去することになる。

【0043】

そして、図32に示すように、再びエッチングを開始してポリシリコン膜21が上記(1)式で求めた厚さまで薄くなったときに、一旦エッチングを停止する。そして、酸素ガスを含むガスを用いたエッチングを行い、電極加工側壁31を除去する。この段階で、電極加工側壁31で覆われていた領域のポリシリコン膜21は厚く残っており、その外側のゲート電極間のポリシリコン膜21は薄く残っている。

【0044】

次に、図33に示すように、ポリシリコン膜21における電極加工側壁31で覆われていた部分と、ゲート電極の間に形成された部分を除去する。ゲート電極の間のポリシリコン膜21の部分が除去されて、シリコン酸化膜20が表面に現れるようになっても、設定したオーバーエッチング量のエッチングを続ける。そうすると、電極加工側壁31で覆われていた部分も除去されるが、ポリシリコン膜21における溝19内に埋め込まれた部分までエッチングされて、えぐれることはない。これは、電極加工側壁31で覆われていた部分のポリシリコン膜21をちょうどBの厚さだけエッチングできるように、あらかじめ、オーバーエッチング量Xを考慮して、(1)式によって、ゲート電極の間のポリシリコン膜21を残す厚さAを設定したからである。

その後、図34に示すように、ゲート電極間のシリコン基板10上のシリコン酸化膜20、すなわち、ゲート絶縁膜となる溝19の内壁のシリコン酸化膜20以外のシリコン酸化膜20を除去する。溝19内には、シリコン酸化膜20が残存している。

柱状体29及び上部導電部42を含む積層膜を柱状体32という。

【0045】

次に、図35に示すように、柱状体32の側面上にエクステンション側壁33を形成する。エクステンション側壁33は、シリコン基板10上にシリコン窒化膜を形成した後、柱状体32の側面上以外の部分を除去して形成する。

そして、図36に示すように、柱状体32及びエクステンション側壁33をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における柱状体32及びエクステンション側壁33に覆われていない領域に拡張領域34を形成する。

【0046】

さらに、図37に示すように、柱状体32の側面上にソース・ドレイン側壁35を形成する。

そして、図38に示すように、柱状体32、エクステンション側壁33及びソース・ドレイン側壁35をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における柱状体32、エクステンション側壁33及びソース・ドレイン側壁35に覆われていない領域にソース・ドレイン領域36を形成する。ソース・ドレイン領域36には、拡張領域34に注入された濃度より高濃度でリンを注入する。また、ソース・ドレイン領域36には、拡張領域34より深くリンを注入する。

【0047】

その後は、ニッケルを堆積した後、加熱することにより、ソース・ドレイン領域36の表面をシリサイド化する。次に、未反応のニッケルを除去する。そして、シリコン基板10上に層間絶縁膜37を堆積した後、層間絶縁膜37にソース・ドレイン領域に到達するコンタクトホール38を形成する。コンタクトホール内に導電部材を埋設してコンタクト39を形成する。

このようにして、図1及び図2に示すように、半導体装置1が完成する。

【0048】

次に、第4の実施形態に係る半導体装置の製造方法の効果について説明する。

リセス構造のトランジスタにおいては、溝19の内部及び直上域にゲート電極を形成する。そのため、ゲート電極の上部を加工するためのレジスト27を、溝19の位置に一致するように配置しようとする。しかし、実際はリソグラフィーの合わせズレにより、溝19の位置とレジスト27の位置との間にズレが生じることが多い。本実施形態に係る半導体装置の製造方法は、ゲート電極の側面上に、予測されるズレの長さのポリシリコン膜21のマージン部分を形成し、オーバーエッチングによって、マージン部分が除去されるようにしている。

したがって、ズレが生じている場合にも、リセス構造トランジスタの下部導電部41のエッチングを抑制することができる。よって、トランジスタの特性の劣化を抑制することができる。

【0049】

また、電極加工側壁31の材料として、炭素を含む材料とすると、ハードマスク、バリアメタル側壁、素子分離領域、ゲート絶縁膜の材料のエッチング速度との関係から、電極加工側壁31を形成しやすく、除去しやすい。したがって、本実施形態は、リセス構造のトランジスタを実現でき、高集積化を図ることができる半導体装置を提供することができる。

【0050】

(第4の実施形態の比較例)

次に、第4の実施形態の比較例について説明する。

本比較例においては、電極加工側壁31を形成しない場合における半導体装置の製造方法である。

第4の実施形態における図5〜図29に示す工程は、比較例においても同様なので説明を省略する。

図39は、第4の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図である。

図39に示すように、本比較例においては、電極加工側壁31を形成せずにポリシリコン膜21をエッチングする。ゲート電極間の絶縁を完全にするために、オーバーエッチングを実施すると、溝19とゲート電極との間にズレが生じているため、下部導電部41の一部も除去される。

【0051】

その後、ゲート電極間のシリコン酸化膜21、すなわち、ゲート絶縁膜となる溝19の内壁のシリコン酸化膜21以外のシリコン酸化膜21を除去する。そして、第4の実施形態における図35〜38に示すような工程を行って、半導体装置が製造される。

比較例に係る半導体装置においては、下部導電部41に欠損が生じる。そのため、リセス型のトランジスタの性能が十分に発揮されない。

【0052】

(第5の実施形態)

次に、第5の実施形態について説明する。

本実施形態は、第2の実施形態に係る半導体装置の製造方法の実施形態である。

本実施形態においては、第4の実施形態と異なり、(1)式で求めた厚さ以上のポリシリコン膜21を除去した後、電極加工側壁31を除去している。

以下、図面を参照しつつ、本実施形態について説明する。

図40〜図43は、第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

先ず、前述の第4の実施形態と同様に、図5〜図30に示す工程を実施する。これらの工程については、説明を省略する。

【0053】

図40に示すように、本実施形態においては、電極加工側壁31及び柱状体29をマスクとしてポリシリコン膜21を、ポリシリコン膜21の厚さが(1)式で求めた厚さより薄くなるまで除去した後に、一旦エッチングを停止する。

次に、図41に示すように、電極加工側壁31を、酸素を含むガスを用いたエッチングで除去する。この段階で、電極加工側壁31で覆われていた領域のポリシリコン膜21は厚く残っており、その外側のゲート電極の間の領域のポリシリコン膜21は、第4の実施形態の場合より薄くなっている。

【0054】

次に、図42に示すように、エッチングを再開して、電極加工側壁31で覆われていたポリシリコン膜21と、ゲート電極の間のポリシリコン膜21とを、柱状体29をマスクとして除去する。ゲート電極の間のポリシリコン膜21が除去されて、シリコン酸化膜20が表面に現れるようになっても、設定したオーバーエッチング量のエッチングを続ける。第5の実施形態においては、電極加工側壁31で覆われていたポリシリコン膜21は残っている。そして、上部導電部42の側面には段差が形成されている。

【0055】

その後、図43に示すように、ゲート電極間のシリコン酸化膜20、すなわち、ゲート絶縁膜となる溝19の内壁のシリコン酸化膜20以外の部分のシリコン酸化膜20を除去する。溝19内には、シリコン酸化膜20が残存している。

そして、第4の実施形態と同様に、図35〜図38に示すような工程を行う。

このようにして、図3に示すように、半導体装置2が製造される。

【0056】

次に、第5の実施形態に係る半導体装置の製造方法の効果について説明する。

本実施形態においては、電極加工側壁31で覆われていた部分のポリシリコン膜21が残っている。したがって、ゲート電極の幅が第4の実施形態の場合より大きくなっている。しかし、溝19とハードマスク28の位置にズレが生じ、かつオーバーエッチング量Xの設定値と実際のエッチング量にズレが生じていても、確実に、溝19の直上域をゲート電極のポリシリコン膜21で覆うことができる。よって、下部導電部41溝19のエッチングを抑制することができる。

本実施形態における上記以外の効果は、前述の第4の実施形態と同様である。

【0057】

(第6の実施形態)

次に、第6の実施形態について説明する。

本実施形態は、第3の実施形態に係る半導体装置の製造方法の実施形態である。

本実施形態においては、第4の実施形態と異なり、電極加工側壁31及び柱状体29をマスクとしてエッチングを行う際に、ポリシリコン膜21におけるマスクによって覆われていない部分を全て除去して、ゲート電極間のシリコン酸化膜20を表面に露出させた後に、電極加工側壁31を除去している。

以下、図面を参照しつつ、本実施形態について説明する。

図44〜図46は、第6の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

先ず、前述の第4の実施形態と同様に、図5〜図26に示す工程を実施する。これらの工程については説明を省略する。

【0058】

図44に示すように、本実施形態においては、電極加工側壁31及び柱状体29をマスクとしてポリシリコン膜21を、ゲート電極間のシリコン基板10表面にシリコン酸化膜20が現れるまで除去する。

その後、図45に示すように、電極加工側壁31を、酸素を含むガスを用いたエッチングで除去する。この段階で、電極加工側壁31で覆われていた領域のポリシリコン膜21は厚く残っており、その外側のゲート電極の間の領域のポリシリコン膜21は、除去されて、シリコン基板10上に形成されたシリコン酸化膜20が表面に現れている。

【0059】

次に、図46に示すように、表面に現れているシリコン酸化膜20を除去する。

そして、第4の実施形態と同様に、図35〜図38に示すような工程を行う。

このようにして、図4に示すように、半導体装置3が製造される。

【0060】

次に、第6の実施形態に係る半導体装置の効果について説明する。

本実施形態においては、図44に示す工程において、ポリシリコン膜21における柱状体29及び電極加工側壁31によって覆われていない部分の全体を除去した後、図45に示す工程において、電極加工側壁31を除去している。このため、ポリシリコン膜21のオーバーエッチング量に拘わらず、溝19の直上域にポリシリコン膜21を確実に残留させることができる。従って、前述の第4の実施形態のように、オーバーエッチング量Xを考慮する必要がない。また、ポリシリコン膜21の加工を1回のエッチング処理によって実施することができる。このため、工程が簡略である。一方、第4の実施形態は、本実施形態と比較して、ゲート電極の導電部43をより細く形成することができるため、半導体装置をより一層微細化することができる。

本実施形態における上記以外の効果は、前述の第4及び第5の実施形態の効果と同様である。

【0061】

以上説明した実施形態によれば、高集積化を図ることができる半導体装置の製造方法を提供することができる。

【0062】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。

【符号の説明】

【0063】

1、2、3:半導体装置、10:シリコン基板、11:ハードマスク、12:溝、13:シリコン酸化膜、14:シリコン酸化膜、15:ウェル、16:活性領域、17:STI領域、18:ハードマスク、19:溝、20:シリコン酸化膜、21:ポリシリコン膜、22:バリアメタル層、23:低抵抗金属層、24:窒化シリコン、25:有機膜、26シリコン酸化膜、27:レジスト、28:ハードマスク、29:第1の柱状体、30:バリアメタル側壁、31:電極加工側壁、32:第2の柱状体、33:エクステンション側壁、34:拡張領域、35:ソース・ドレイン側壁、36:ソースドレイン領域、37:層間絶縁膜、38:コンタクトホール、39:コンタクト、41:下部導電部、42:上部導電部、43:導電部

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

LSI(large scale integrated circuit:大規模集積回路)の集積度が増して、トランジスタのゲート電極の幅が微細化すると、ゲート電極及びソース・ドレインが平面的に配置されたトランジスタにおいては、チャネル長が短くなって、ソース・ドレイン間のリーク電流を抑制することが困難になってくる。

そこで、チャネル構造を立体的にすることが試みられている。チャネル構造を立体的にしたトランジスタとして、リセス構造のトランジスタ(Recessed Channel Transistor:RCAT)が挙げられる。

【0003】

リセス構造のトランジスタにおいては、ゲート電極の一部が、半導体基板に形成された溝の内部に埋め込まれている。そして、溝の内壁に形成された絶縁膜がゲート絶縁膜となり、半導体基板の溝に沿った領域がチャネルを構成する。

このように、チャネル構造を立体的にすることによってチャネル長をリーク電流の抑制が可能な程度に長く確保しつつ、ゲート電極の幅を微細化することができる。

また、このような立体的な構造においては、ソース・ドレイン端が広がり、チャネルを流れる電流量を増加させることもできる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−081107号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の実施形態は、高集積化を図ることができる半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0006】

実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程と、前記柱状体をマスクとしてエッチングすることにより、前記露出した部分の下部を除去する工程とを備える。

【0007】

また、実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分を除去する工程と、前記電極加工側壁を除去する工程とを備える。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態に係る半導体装置を例示する斜視図である。

【図2】第1の実施形態に係る半導体装置を例示する断面図であり、図1に示すA−A’面による断面図である。

【図3】第2の実施形態に係る半導体装置を例示する断面図である。

【図4】第3の実施形態に係る半導体装置を例示する断面図である。

【図5】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図6】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図7】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図8】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図9】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図10】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図11】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図12】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図13】第4の実施形態に係る半導体装置の製造方法を例示する工程平面図である。

【図14】図13に示すA−A’線による工程断面図である。

【図15】図13に示すB−B’線による工程断面図である。

【図16】図13に示すC−C’線による工程断面図である。

【図17】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図18】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図19】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図20】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図21】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図22】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図23】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図24】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図25】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図26】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図27】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図28】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図29】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図30】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図31】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図32】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図33】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図34】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図35】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図36】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図37】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図38】第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図39】第4の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図である。

【図40】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図41】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図42】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図43】第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図44】第6の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図45】第6の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【図46】第6の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【発明を実施するための形態】

【0009】

(第1の実施形態)

以下、図面を参照しつつ、本発明の実施形態について説明する。

先ず、第1の実施形態について説明する。

本実施形態は、半導体装置についてのものである。

図1は、第1の実施形態に係る半導体装置を例示する斜視図である。

図2は、第1の実施形態に係る半導体装置を例示する断面図であり、図1に示すA−A’面による断面図である。

【0010】

先ず、第1の実施形態に係る半導体装置の構成について説明する。

図1及び図2に示すように、半導体装置1においては、半導体基板、例えばシリコン基板10が設けられている。シリコン基板10の上面には、1つの方向に延びる複数の溝12が平行に形成されている。溝12の内部には、絶縁材料、例えば酸化シリコン13が埋め込まれている。溝12の内部に酸化シリコン13が埋め込まれた領域をSTI領域(Shallow Trench Isolation)17とする。STI領域17に挟まれた領域を活性領域16とする。

シリコン基板10には、シリコン基板10の表面から、溝12の底面より深い領域まで、不純物、例えばボロンが導入されて、ウェル15が形成されている。

シリコン基板10には、STI領域17及び活性領域16が延びる方向に直交する方向に延びる溝19が設けられている。

【0011】

溝19の内面上には、ゲート絶縁膜、例えばシリコン酸化膜20が設けられている。また、溝19の内部には、導電材料、例えばポリシリコンが埋め込まれている。溝19の内部に埋め込まれたポリシリコンの部分を、下部導電部41という。ポリシリコンには、不純物、例えばリンが導入されている。

活性領域16の表層部分における溝19の外縁を含む領域には、不純物、例えばリンが導入された拡張領域34が形成されている。活性領域16の表層部分における溝を挟んで両側の拡張領域34の隣には、それぞれソース・ドレイン領域36が形成されている。ソース・ドレイン領域36には、不純物、例えばリンが、拡張領域34に導入された濃度より高濃度で導入されている。また、ソース・ドレイン領域36には、不純物が、拡張領域34より深く導入されている。

【0012】

また、溝19の直上域の一部を含む領域には、溝19に沿って、溝19の幅と略等しい幅で、導電材料からなる柱状体が設けられている。ここで、溝19の幅方向の長さを「幅」という。この溝19上に設けられた柱状体は、溝19の内部に埋設された導電材料と同じ材料のポリシリコンからなり、溝19の内部に埋め込まれた下部導電部41と一体化している。溝19上に設けられたポリシリコンの柱状体を、上部導電部42という。

上部導電部42と下部導電部41を合わせて導電部43という。

上部導電部42の位置と、下部導電部41及び溝19の位置とは、ズレが生じている。ズレは想定される範囲のものである。

【0013】

上部導電部42上には、バリアメタル層22が設けられている。バリアメタル層22としては、チタンと窒化チタンの積層膜が挙げられる。バリアメタル層22上には、低抵抗金属層23が設けられている。低抵抗金属層23の材料としては、タングステンがあげられる。低抵抗金属層23上には、ハードマスク28が設けられている。ハードマスク28の材料としては、窒化シリコンがあげられる。導電部43、バリアメタル層22及び低抵抗金属層23とから、ゲート電極が形成される。

【0014】

ハードマスク28、低抵抗金属層23及びバリアメタル層22は積層して、柱状体29を構成している。柱状体29におけるバリアメタル層22が、チタンと窒化チタンの積層膜である場合には、製造工程における酸化熱処理で、積層膜に含まれるチタンが酸化することがある。そこで、チタンの酸化を防ぐために、ハードマスク28、低抵抗金属層23及びバリアメタル層22の積層体の側面には、バリアメタル側壁30が設けられている。バリアメタル側壁30の材料としては、窒化シリコンがあげられる。バリアメタル側壁30が設けられている場合は、バリアメタル側壁30を含んだ積層構造を柱状体29という。

【0015】

上部導電部42及び柱状体29とで、柱状体32を構成する。

柱状体32の側面には、エクステンション側壁33とソース・ドレイン側壁35が設けられている。エクステンション側壁33の側面の端部を上から見た位置は、拡張領域34の溝19側の端部を上から見た位置と略同一である。ソース・ドレイン側壁35の側面の端部を上から見た位置は、ソース・ドレイン領域36の溝19側の端部を上から見た位置と略同一である。

【0016】

シリコン基板10上には層間絶縁膜37が設けられている。なお、図1においては、図を見やすくするために、層間絶縁膜37を省略してある。層間絶縁膜37におけるソース・ドレイン領域36上にはコンタクトホール38が形成されている。コンタクトホール38の内部には、コンタクト39が設けられている。

ソース・ドレイン領域36の表面は、シリサイド、例えばニッケルシリサイドが設けられている。コンタクトホール38内部に埋設されたコンタクト39はソース・ドレイン表面におけるシリサイドに接合されている。

【0017】

次に、第1の実施形態に係る半導体装置の動作について説明する。

先ず、半導体装置1のゲート電極に電圧を負荷する。そうすると、溝19の内面上に設けられたシリコン酸化膜20が、ゲート絶縁膜として働く。シリコン基板10の溝19に沿った領域がチャネルとして働き、反転層が形成される。そしてソース・ドレイン間に電圧を負荷すれば、反転層内をキャリアが移動し、電流が流れる。ゲート電極の電圧を変化させることによって、ソース・ドレイン間を流れる電流量を制御する。

【0018】

次に、第1の実施形態に係る半導体装置の効果について説明する。

リセス構造にするための溝19の内部にゲート電極の一部となるポリシリコンを完全に埋設することができる。よって、デザインルールが微細化して、リソグラフィーによる溝とゲート電極との間にズレが生じるようになっても、リセス構造のトランジスタを製造することができる。したがって、ゲート電極の幅を微細化しつつ、チャネル長を増加させ、高集積化した半導体装置を提供することができる。

【0019】

(第2の実施形態)

次に、第2の実施形態に係る半導体装置について説明する。

図3は、第2の実施形態に係る半導体装置を例示する断面図である。

図3に示すように、本実施形態においては、上部導電部42の側面には、段差が設けられている。

段差における上方を向いた面の幅は、溝19の位置と柱状体32の位置のズレの幅と略等しい。

【0020】

上部導電部42の上面の幅は、柱状体29の幅及び溝19の幅と略同一である。

一方、上部導電部42の下面の幅は、柱状体29の幅及び溝19の幅より大きい。

エクステンション側壁及びソース・ドレイン側壁は、柱状体32の側面形状に合わせて設けられている。

エクステンション側壁33の側面の最も外側の端部を上から見た位置は、拡張領域34の溝19側の端部を上から見た位置と略同一である。ソース・ドレイン側壁35の側面の最も外側の端部を上から見た位置は、ソース・ドレイン領域36の溝19側の端部を上から見た位置と略同一である。

その他の構成は、第1の実施形態と同様であるので省略する。また、動作も同様であるので省略する。

【0021】

次に、第2の実施形態に係る半導体装置の効果について説明する。

第2の実施形態においては、上部導電部42の下部の幅が広くなっている。したがって、下部導電部41を覆い、リセス構造にするための溝19の内部に電極の一部となるポリシリコンを完全に埋設することができる。よって、リセス構造を実現し、高集積化した半導体装置を提供することができる。

【0022】

(第3の実施形態)

次に、第3の実施形態について説明する。

図4は、第3の実施形態に係る半導体装置を例示する断面図である。

図4に示すように、本実施形態においては、上部導電部42の幅は、柱状体29の幅及び溝19の幅より大きい幅で設けられている。また、上部導電部42の側面には、第2の実施形態と異なり、段差が設けられていない。

エクステンション側壁及びソース・ドレイン側壁は、第2の柱状体の側面形状に合わせて設けられている。

その他の構成は、第1の実施形態と同様であるので省略する。また、動作及び効果も同様であるので省略する。

【0023】

(第4の実施形態)

次に、第4の実施形態について説明する。

本実施形態は、第1の実施形態に係る半導体装置の製造方法についてのものである。

図5〜12は、第4の実施形態に係る半導体装置の製造方法を例示する工程断面図であり、

図13は、第4の実施形態に係る半導体装置の製造方法を例示する工程平面図であり、

図14は、図13に示すA−A’線による工程断面図であり、

図15は、図13に示すB−B’線による工程断面図であり、

図16は、図13に示すC−C’線による工程断面図であり、

図17〜図38は、第4の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

【0024】

先ず、図5に示すように、例えば単結晶のシリコン(Si)からなるシリコン基板10を用意する。

そして、図6に示すように、シリコン基板10上にハードマスク11となる膜として、例えばSiN膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク11を形成する。ハードマスク11は、シリコン基板10上の1つの方向に平行に形成する。

【0025】

次に、図7に示すように、ハードマスク11をマスクとして反応性イオンエッチングを行い、シリコン基板10の上層部分にSTI領域17となる溝12を形成する。このとき、ハードマスク11に覆われて、エッチングされない領域が活性領域16となる。

その後、図8に示すように、溝12及びハードマスク11を含むシリコン基板10上をシリコン酸化膜13で覆う。

そして、図9に示すように、CMP(chemical mechanical polishing:化学的機械研磨)法によって、ハードマスクの表面が現れるまでシリコン酸化膜13を研磨し、シリコン酸化膜13の上面を平坦化する。

【0026】

次に、図10に示すように、ウェットエッチングによって、ハードマスク11の下面まで、すなわち、シリコン基板10におけるハードマスク11に覆われた部分の上面まで、シリコン酸化膜13を除去する。

その後、図11に示すように、ウェットエッチングにより、ハードマスク11(図10参照)を除去する。シリコン基板10の上面が現れている領域が活性領域16である。また、溝12の中にシリコン酸化膜13が埋め込まれた領域がSTI領域17である。STI領域17ではシリコン酸化膜13の上面が表面に現れている。

【0027】

そして、図12に示すように、活性領域16及びSTI領域17を含むシリコン基板10の上面上に、シリコン酸化膜14を形成する。その後、シリコン酸化膜14上から、イオン注入法によって、不純物として例えばボロンを導入する。導入する深さは、シリコン基板10の表面から溝12の底部より深い領域までとする。これによって、活性領域16においては、シリコン基板10の上面から、溝12の底部より深い領域に相当する深さまで、シリコン基板10中にボロンが導入される。STI領域17においては、溝12の底面から、溝12の底部より深い領域まで、シリコン基板10中にボロンが導入される。シリコン基板10におけるボロンが導入された部分がp形のウェル15となる。

【0028】

図13〜図16に示すように、上述の工程により、シリコン基板10上に、1つの方向に平行に延びるSTI領域17が形成される。そして、STI領域17の間に配置されるように活性領域16が形成される。シリコン基板10の表面にはシリコン酸化膜14が形成されているが、図13においては、図示を省略してある。

【0029】

次に、図17に示すように、図13のB−B’線における断面に相当する断面においては、シリコン基板10上にハードマスク18となる膜として、例えばSiN膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク18を形成する。ハードマスク18は、STI領域17を形成するための溝12と直交する方向に延びている。

【0030】

次に、図18に示すように、ハードマスク18をマスクとして、反応性イオンエッチングを行うことにより、シリコン酸化膜14及びシリコン基板10を選択的に除去する。これにより、溝19が形成される。

また、図19に示すように、図13のC−C’線における断面に相当する断面においては、STI領域17においても、シリコン基板10上にハードマスク18となる膜として、SiN膜を形成した後、フォトリソグラフィー法等でパターニングしてハードマスク18を形成する。

次に、図20に示すように、ハードマスク18をマスクとして、反応性イオンエッチングにより、シリコン酸化膜13及びシリコン酸化膜14を選択的に除去する。これにより、溝19が形成される。

このように、図13に示すB−B’線による活性領域における溝19の内部と、図13に示すC−C’線によるSTI領域における溝19の内部は同じ構成となっている。そこで、以後は活性領域における工程断面図のみ示す。

【0031】

次に、図21に示すように、シリコン基板10上のハードマスク18及びシリコン酸化膜14を除去する。

その後、図22に示すように、溝19の内面上及びシリコン基板10の上面上にゲート絶縁膜となるシリコン酸化膜20を形成する。

【0032】

次に、図23に示すように、シリコン酸化膜20上からゲート電極の一部となるポリシリコン膜21を形成する。このポリシリコン膜にはリンが不純物として導入されている。ポリシリコン膜21は、溝19内を埋め込むように形成する。

その後、図24に示すように、ポリシリコン膜21上からバリアメタル層22として、例えばチタンと窒化チタンの積層膜を積層する。そして、その上から低抵抗金属層23として、例えばタングステン(W)膜を形成する。本実施形態において、ゲート電極は、ポリシリコン膜21、バリアメタル層22及び低抵抗金属層23を含んでいる。バリアメタル層22の材料としては、チタンと窒化チタンの積層膜の他、窒化チタンがあげられる。

【0033】

そして、図25に示すように、低抵抗金属層23上から、シリコン窒化膜24及び有機膜25を形成した後、その上に、シリコン酸化膜26を形成する。さらにシリコン酸化膜26上に、レジスト27を形成する。このとき、レジスト27の形成領域は、溝19の直上域と一致させることを目標とする。しかし、リソグラフィーの合わせズレにより、これらの位置にはズレが生じる場合がある。しかし、このズレの量はリソグラフィー法の精度から予測される範囲内にあり、溝19の幅よりも小さい。したがって、レジスト27は、溝19の直上域の一部を含む領域に形成される。

【0034】

次に、レジスト27をマスクとして、シリコン酸化膜26をパターニングする。

その後、図26に示すように、パターニングされたシリコン酸化膜26をマスクとして有機膜25及びシリコン窒化膜24を加工する。溝19とレジスト27との間のあわせズレと同じ幅のズレが、溝19とシリコン酸化膜26、有機膜25及びシリコン窒化膜24との間にも生じる。

【0035】

図27に示すように、本実施形態では、シリコン酸化膜26及び有機膜25を除去し、パターニングされたシリコン窒化膜24をハードマスク28とする。

次に、図28に示すように、ハードマスク28をマスクとして反応性イオンエッチングを行い、低抵抗金属層23及びバリアメタル層22を選択的に除去する。これによって、ハードマスク28で覆われている部分には、低抵抗金属層23及びバリアメタル層22からなるゲート電極の一部が形成される。

一方、ハードマスク28で覆われていない部分の表面には、ポリシリコン膜21が現れている。

【0036】

バリアメタル層22として窒化チタンとチタンの積層膜を用いた場合は、ゲート電極加工後の後酸化のときにチタンが酸化されて劣化する可能性がある。

そこで、図29に示すように、ハードマスク28、低抵抗金属層23及びバリアメタル層22を含む多層膜の側面上に、バリアメタル側壁30を形成する。バリアメタル側壁30の材料としては、例えば、シリコン窒化膜があげられる。バリアメタル側壁30は、CVD法(chemical vapor deposition:化学気相成長法)等により、シリコン窒化膜を形成した後、ハードマスク28、低抵抗金属層23及びバリアメタル層22を含む多層膜の側面上以外の部分を除去して形成する。

バリアメタル側壁30を形成した場合は、バリアメタル側壁30、ハードマスク28、低抵抗金属層23及びバリアメタル層22を含む多層膜を柱状体29という。バリアメタル側壁30を形成しない場合は、ハードマスク28、低抵抗金属層23及びバリアメタル層22を含む多層膜を柱状体29という。

【0037】

次に、図30に示すように、バリアメタル側壁30の側面上に電極加工側壁31を形成する。電極加工側壁31は、炭素を含む膜から形成される。炭素を含む膜の形成方法としては、CVD法等の成膜手法を用いて形成する方法と、エッチング時の反応生成物により形成する方法があげられる。CVD法等による方法では、先ず、シリコン基板10上に、炭素、水素及び窒素を含む膜を形成する。炭素の含有率が100%に近い膜も形成することができる。炭素、水素及び窒素を含む膜を形成した後に、柱状体29の側壁上以外の部分を除去して電極加工側壁31を形成する。エッチング時の反応生成物により形成する方法では、シリコン基板10上に、エッチング時の反応生成物により形成されたフルオロカーボン膜において、柱状体29の側壁上以外の部分を除去して形成する。バリアメタル側壁30の側面上における電極加工側壁31の厚さは、溝19の位置とハードマスク28の位置との間に想定される合わせズレ幅以上の膜厚とする。

【0038】

次に、ポリシリコン膜21の加工を行う。本実施形態においては、ゲート電極は、ポリシリコン膜21、バリアメタル層22及び低抵抗金属層23の三層構造とされている。したがって、ポリシリコン膜21は、ゲート電極の最下層膜となっている。

図31に示すように、電極加工側壁31及び柱状体29をマスクとしてポリシリコン膜21のエッチングを行う。これによって、ゲート電極間のポリシリコン膜21はエッチングされるが、電極加工側壁31で覆われたポリシリコン膜21はエッチングされない。

【0039】

そして、ゲート電極間のポリシリコン膜21を完全に除去せずに、エッチングを途中で一旦停止する。一旦停止することによって、電極加工側壁31で覆われたポリシリコン膜21の厚さを、ゲート電極間のポリシリコン膜21の厚さより厚く残しておく。ゲート電極間の絶縁を完全にするために行うオーバーエッチング時に、電極加工側壁31で覆われたポリシリコン膜21が除去されるようにする。そうすれば、溝19の位置とゲート電極の位置との間にズレが生じていても、下部導電部41がエッチングされずにすむ。

【0040】

次に、エッチングを途中で一旦停止するときのポリシリコン膜21の厚さについて説明する。

図31に示すように、ゲート電極間、すなわち、溝19が設けられていない部分のシリコン基板10上におけるポリシリコン膜21の厚さAが、次式(1)で表される厚さまで薄くなった時に、エッチングを途中で一旦停止する。

A=B−(B・X/100) (1)

ここで、Bは、電極加工側壁31の形成前における溝19が形成されていない部分のシリコン基板10上のポリシリコン膜21の厚さである。Xは、オーバーエッチング量を表し、単位は%である。オーバーエッチング量とは、シリコン基板10上の表面において、ポリシリコン膜を除去したとしても、ゲート電極間の絶縁を完全なものとするために余分に行うエッチング量である。

【0041】

Xが少ないほどコストが少なくてすむ。しかし、ポリシリコン膜21の厚さのばらつきを考慮し、ゲート電極間の絶縁を図るために、オーバーエッチング量は例えば30%以上とすることが好ましい。ゲート電極間の絶縁を向上させてトランジスタの歩留まりを上げつつ、生産コストを低下するためには、オーバーエッチング量は50%程度が好ましい。

【0042】

例えば、カーボン側壁31の形成前における溝19が形成されていないシリコン基板10上のポリシリコン膜21の厚さが100nmのとき、オーバーエッチング量を30%とすると、

100−(100・30/100)=70

となり、溝19が設けられていない部分のシリコン基板10上におけるポリシリコン膜21の厚さAが70nmまで薄くなった時に、ポリシリコン膜21のエッチングを一旦停止して、電極加工側壁31を除去することになる。

また、例えば、オーバーエッチング量を50%とすると、

100−(100・50/100)=50

となり、溝19が設けられていない部分のシリコン基板10上におけるポリシリコン膜21の厚さAが50nmまで薄くなった時に、ポリシリコン膜21のエッチングを一旦停止して、電極加工側壁31を除去することになる。

【0043】

そして、図32に示すように、再びエッチングを開始してポリシリコン膜21が上記(1)式で求めた厚さまで薄くなったときに、一旦エッチングを停止する。そして、酸素ガスを含むガスを用いたエッチングを行い、電極加工側壁31を除去する。この段階で、電極加工側壁31で覆われていた領域のポリシリコン膜21は厚く残っており、その外側のゲート電極間のポリシリコン膜21は薄く残っている。

【0044】

次に、図33に示すように、ポリシリコン膜21における電極加工側壁31で覆われていた部分と、ゲート電極の間に形成された部分を除去する。ゲート電極の間のポリシリコン膜21の部分が除去されて、シリコン酸化膜20が表面に現れるようになっても、設定したオーバーエッチング量のエッチングを続ける。そうすると、電極加工側壁31で覆われていた部分も除去されるが、ポリシリコン膜21における溝19内に埋め込まれた部分までエッチングされて、えぐれることはない。これは、電極加工側壁31で覆われていた部分のポリシリコン膜21をちょうどBの厚さだけエッチングできるように、あらかじめ、オーバーエッチング量Xを考慮して、(1)式によって、ゲート電極の間のポリシリコン膜21を残す厚さAを設定したからである。

その後、図34に示すように、ゲート電極間のシリコン基板10上のシリコン酸化膜20、すなわち、ゲート絶縁膜となる溝19の内壁のシリコン酸化膜20以外のシリコン酸化膜20を除去する。溝19内には、シリコン酸化膜20が残存している。

柱状体29及び上部導電部42を含む積層膜を柱状体32という。

【0045】

次に、図35に示すように、柱状体32の側面上にエクステンション側壁33を形成する。エクステンション側壁33は、シリコン基板10上にシリコン窒化膜を形成した後、柱状体32の側面上以外の部分を除去して形成する。

そして、図36に示すように、柱状体32及びエクステンション側壁33をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における柱状体32及びエクステンション側壁33に覆われていない領域に拡張領域34を形成する。

【0046】

さらに、図37に示すように、柱状体32の側面上にソース・ドレイン側壁35を形成する。

そして、図38に示すように、柱状体32、エクステンション側壁33及びソース・ドレイン側壁35をマスクとして、シリコン基板10にリンをイオン注入する。これにより、シリコン基板10における柱状体32、エクステンション側壁33及びソース・ドレイン側壁35に覆われていない領域にソース・ドレイン領域36を形成する。ソース・ドレイン領域36には、拡張領域34に注入された濃度より高濃度でリンを注入する。また、ソース・ドレイン領域36には、拡張領域34より深くリンを注入する。

【0047】

その後は、ニッケルを堆積した後、加熱することにより、ソース・ドレイン領域36の表面をシリサイド化する。次に、未反応のニッケルを除去する。そして、シリコン基板10上に層間絶縁膜37を堆積した後、層間絶縁膜37にソース・ドレイン領域に到達するコンタクトホール38を形成する。コンタクトホール内に導電部材を埋設してコンタクト39を形成する。

このようにして、図1及び図2に示すように、半導体装置1が完成する。

【0048】

次に、第4の実施形態に係る半導体装置の製造方法の効果について説明する。

リセス構造のトランジスタにおいては、溝19の内部及び直上域にゲート電極を形成する。そのため、ゲート電極の上部を加工するためのレジスト27を、溝19の位置に一致するように配置しようとする。しかし、実際はリソグラフィーの合わせズレにより、溝19の位置とレジスト27の位置との間にズレが生じることが多い。本実施形態に係る半導体装置の製造方法は、ゲート電極の側面上に、予測されるズレの長さのポリシリコン膜21のマージン部分を形成し、オーバーエッチングによって、マージン部分が除去されるようにしている。

したがって、ズレが生じている場合にも、リセス構造トランジスタの下部導電部41のエッチングを抑制することができる。よって、トランジスタの特性の劣化を抑制することができる。

【0049】

また、電極加工側壁31の材料として、炭素を含む材料とすると、ハードマスク、バリアメタル側壁、素子分離領域、ゲート絶縁膜の材料のエッチング速度との関係から、電極加工側壁31を形成しやすく、除去しやすい。したがって、本実施形態は、リセス構造のトランジスタを実現でき、高集積化を図ることができる半導体装置を提供することができる。

【0050】

(第4の実施形態の比較例)

次に、第4の実施形態の比較例について説明する。

本比較例においては、電極加工側壁31を形成しない場合における半導体装置の製造方法である。

第4の実施形態における図5〜図29に示す工程は、比較例においても同様なので説明を省略する。

図39は、第4の実施形態の比較例に係る半導体装置の製造方法を例示する工程断面図である。

図39に示すように、本比較例においては、電極加工側壁31を形成せずにポリシリコン膜21をエッチングする。ゲート電極間の絶縁を完全にするために、オーバーエッチングを実施すると、溝19とゲート電極との間にズレが生じているため、下部導電部41の一部も除去される。

【0051】

その後、ゲート電極間のシリコン酸化膜21、すなわち、ゲート絶縁膜となる溝19の内壁のシリコン酸化膜21以外のシリコン酸化膜21を除去する。そして、第4の実施形態における図35〜38に示すような工程を行って、半導体装置が製造される。

比較例に係る半導体装置においては、下部導電部41に欠損が生じる。そのため、リセス型のトランジスタの性能が十分に発揮されない。

【0052】

(第5の実施形態)

次に、第5の実施形態について説明する。

本実施形態は、第2の実施形態に係る半導体装置の製造方法の実施形態である。

本実施形態においては、第4の実施形態と異なり、(1)式で求めた厚さ以上のポリシリコン膜21を除去した後、電極加工側壁31を除去している。

以下、図面を参照しつつ、本実施形態について説明する。

図40〜図43は、第5の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

先ず、前述の第4の実施形態と同様に、図5〜図30に示す工程を実施する。これらの工程については、説明を省略する。

【0053】

図40に示すように、本実施形態においては、電極加工側壁31及び柱状体29をマスクとしてポリシリコン膜21を、ポリシリコン膜21の厚さが(1)式で求めた厚さより薄くなるまで除去した後に、一旦エッチングを停止する。

次に、図41に示すように、電極加工側壁31を、酸素を含むガスを用いたエッチングで除去する。この段階で、電極加工側壁31で覆われていた領域のポリシリコン膜21は厚く残っており、その外側のゲート電極の間の領域のポリシリコン膜21は、第4の実施形態の場合より薄くなっている。

【0054】

次に、図42に示すように、エッチングを再開して、電極加工側壁31で覆われていたポリシリコン膜21と、ゲート電極の間のポリシリコン膜21とを、柱状体29をマスクとして除去する。ゲート電極の間のポリシリコン膜21が除去されて、シリコン酸化膜20が表面に現れるようになっても、設定したオーバーエッチング量のエッチングを続ける。第5の実施形態においては、電極加工側壁31で覆われていたポリシリコン膜21は残っている。そして、上部導電部42の側面には段差が形成されている。

【0055】

その後、図43に示すように、ゲート電極間のシリコン酸化膜20、すなわち、ゲート絶縁膜となる溝19の内壁のシリコン酸化膜20以外の部分のシリコン酸化膜20を除去する。溝19内には、シリコン酸化膜20が残存している。

そして、第4の実施形態と同様に、図35〜図38に示すような工程を行う。

このようにして、図3に示すように、半導体装置2が製造される。

【0056】

次に、第5の実施形態に係る半導体装置の製造方法の効果について説明する。

本実施形態においては、電極加工側壁31で覆われていた部分のポリシリコン膜21が残っている。したがって、ゲート電極の幅が第4の実施形態の場合より大きくなっている。しかし、溝19とハードマスク28の位置にズレが生じ、かつオーバーエッチング量Xの設定値と実際のエッチング量にズレが生じていても、確実に、溝19の直上域をゲート電極のポリシリコン膜21で覆うことができる。よって、下部導電部41溝19のエッチングを抑制することができる。

本実施形態における上記以外の効果は、前述の第4の実施形態と同様である。

【0057】

(第6の実施形態)

次に、第6の実施形態について説明する。

本実施形態は、第3の実施形態に係る半導体装置の製造方法の実施形態である。

本実施形態においては、第4の実施形態と異なり、電極加工側壁31及び柱状体29をマスクとしてエッチングを行う際に、ポリシリコン膜21におけるマスクによって覆われていない部分を全て除去して、ゲート電極間のシリコン酸化膜20を表面に露出させた後に、電極加工側壁31を除去している。

以下、図面を参照しつつ、本実施形態について説明する。

図44〜図46は、第6の実施形態に係る半導体装置の製造方法を例示する工程断面図である。

先ず、前述の第4の実施形態と同様に、図5〜図26に示す工程を実施する。これらの工程については説明を省略する。

【0058】

図44に示すように、本実施形態においては、電極加工側壁31及び柱状体29をマスクとしてポリシリコン膜21を、ゲート電極間のシリコン基板10表面にシリコン酸化膜20が現れるまで除去する。

その後、図45に示すように、電極加工側壁31を、酸素を含むガスを用いたエッチングで除去する。この段階で、電極加工側壁31で覆われていた領域のポリシリコン膜21は厚く残っており、その外側のゲート電極の間の領域のポリシリコン膜21は、除去されて、シリコン基板10上に形成されたシリコン酸化膜20が表面に現れている。

【0059】

次に、図46に示すように、表面に現れているシリコン酸化膜20を除去する。

そして、第4の実施形態と同様に、図35〜図38に示すような工程を行う。

このようにして、図4に示すように、半導体装置3が製造される。

【0060】

次に、第6の実施形態に係る半導体装置の効果について説明する。

本実施形態においては、図44に示す工程において、ポリシリコン膜21における柱状体29及び電極加工側壁31によって覆われていない部分の全体を除去した後、図45に示す工程において、電極加工側壁31を除去している。このため、ポリシリコン膜21のオーバーエッチング量に拘わらず、溝19の直上域にポリシリコン膜21を確実に残留させることができる。従って、前述の第4の実施形態のように、オーバーエッチング量Xを考慮する必要がない。また、ポリシリコン膜21の加工を1回のエッチング処理によって実施することができる。このため、工程が簡略である。一方、第4の実施形態は、本実施形態と比較して、ゲート電極の導電部43をより細く形成することができるため、半導体装置をより一層微細化することができる。

本実施形態における上記以外の効果は、前述の第4及び第5の実施形態の効果と同様である。

【0061】

以上説明した実施形態によれば、高集積化を図ることができる半導体装置の製造方法を提供することができる。

【0062】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。

【符号の説明】

【0063】

1、2、3:半導体装置、10:シリコン基板、11:ハードマスク、12:溝、13:シリコン酸化膜、14:シリコン酸化膜、15:ウェル、16:活性領域、17:STI領域、18:ハードマスク、19:溝、20:シリコン酸化膜、21:ポリシリコン膜、22:バリアメタル層、23:低抵抗金属層、24:窒化シリコン、25:有機膜、26シリコン酸化膜、27:レジスト、28:ハードマスク、29:第1の柱状体、30:バリアメタル側壁、31:電極加工側壁、32:第2の柱状体、33:エクステンション側壁、34:拡張領域、35:ソース・ドレイン側壁、36:ソースドレイン領域、37:層間絶縁膜、38:コンタクトホール、39:コンタクト、41:下部導電部、42:上部導電部、43:導電部

【特許請求の範囲】

【請求項1】

半導体基板に第1の方向に延びる複数の溝を形成する工程と、

前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、

前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、

前記第1の導電層上に第2の導電層を堆積する工程と、

前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、

前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、

前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、

前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、

前記電極加工側壁を除去する工程と、

前記柱状体をマスクとしてエッチングすることにより、前記露出した部分の下部を除去する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項2】

半導体基板に第1の方向に延びる複数の溝を形成する工程と、

前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、

前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、

前記第1の導電層上に第2の導電層を堆積する工程と、

前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、

前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、

前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、

前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分を除去する工程と、

前記電極加工側壁を除去する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項3】

前記上部及び前記下部を合わせた厚さをt、前記第1の導電層のオーバーエッチング量をパーセント表示した量をAとした場合に、前記下部の厚さは、{t−(t・A/100)}であることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項4】

前記電極加工側壁の前記柱状体の前記側面上における厚さを、前記溝の位置と前記ハードマスクの位置との予測されるズレの長さ以上とすることを特徴とする請求項1〜3のいずれか1つに記載の半導体装置の製造方法。

【請求項5】

前記電極加工側壁の材料には、炭素が含まれることを特徴とする請求項1〜4のいずれか1つに記載の半導体装置の製造方法。

【請求項6】

前記電極加工側壁を形成する工程は、

炭素、窒素及び水素を含むガスを用いた化学気相成長法によって前記半導体基板上に炭素を含む膜を形成する工程と、

前記炭素を含む膜における前記2つの側面上以外に形成された部分を除去する工程と、

を有することを特徴とする請求項5記載の半導体装置の製造方法。

【請求項7】

前記柱状体を形成する工程は、前記第2の導電層をエッチングした後に、前記ハードマスク及び前記第2の導電層における前記溝の幅方向に面する2つの側面上にバリアメタル側壁を形成して、前記柱状体には前記バリアメタル側壁を含むようにする工程を有することを特徴とする請求項1〜6のいずれか1つに記載の半導体装置の製造方法。

【請求項8】

前記半導体基板に第1の方向に延びる溝を形成する工程の前に、前記半導体基板の上面に前記第1の方向と交差する方向に延びる複数本の素子分離領域を形成する工程をさらに備えたことを特徴とする請求項1〜7のいずれか1つに記載の半導体装置の製造方法。

【請求項9】

前記柱状体及び前記第1の導電層における前記溝の幅方向に面する2つの側面上にソース・ドレイン側壁を形成する工程と、

前記柱状体及び前記ソース・ドレイン側壁をマスクとして前記半導体基板に不純物を注入して、第1の不純物領域を形成する工程と、

前記半導体基板上に層間絶縁膜を形成する工程と、

前記層間絶縁膜に、前記第1の不純物領域に到達する貫通孔を形成する工程と、

前記貫通孔内に前記第1の不純物領域に接続する導電部材を埋設する工程と、

をさらに備えたことを特徴とする請求項1〜8のいずれか1つに記載の半導体装置の製造方法。

【請求項10】

前記ソース・ドレイン側壁を形成する工程の前に、

前記柱状体及び前記第1の導電層における前記溝の幅方向に面する2つの側面上にエクステンション側壁を形成する工程と、

前記柱状体及び前記エクステンション側壁をマスクとして前記半導体基板に不純物を注入して、第2の不純物領域を形成する工程と、

をさらに備えたことを特徴とする請求項9記載の半導体装置の製造方法。

【請求項1】

半導体基板に第1の方向に延びる複数の溝を形成する工程と、

前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、

前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、

前記第1の導電層上に第2の導電層を堆積する工程と、

前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、

前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、

前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、

前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、

前記電極加工側壁を除去する工程と、

前記柱状体をマスクとしてエッチングすることにより、前記露出した部分の下部を除去する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項2】

半導体基板に第1の方向に延びる複数の溝を形成する工程と、

前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、

前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、

前記第1の導電層上に第2の導電層を堆積する工程と、

前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、

前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、

前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、

前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分を除去する工程と、

前記電極加工側壁を除去する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項3】

前記上部及び前記下部を合わせた厚さをt、前記第1の導電層のオーバーエッチング量をパーセント表示した量をAとした場合に、前記下部の厚さは、{t−(t・A/100)}であることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項4】

前記電極加工側壁の前記柱状体の前記側面上における厚さを、前記溝の位置と前記ハードマスクの位置との予測されるズレの長さ以上とすることを特徴とする請求項1〜3のいずれか1つに記載の半導体装置の製造方法。

【請求項5】

前記電極加工側壁の材料には、炭素が含まれることを特徴とする請求項1〜4のいずれか1つに記載の半導体装置の製造方法。

【請求項6】

前記電極加工側壁を形成する工程は、

炭素、窒素及び水素を含むガスを用いた化学気相成長法によって前記半導体基板上に炭素を含む膜を形成する工程と、

前記炭素を含む膜における前記2つの側面上以外に形成された部分を除去する工程と、

を有することを特徴とする請求項5記載の半導体装置の製造方法。

【請求項7】

前記柱状体を形成する工程は、前記第2の導電層をエッチングした後に、前記ハードマスク及び前記第2の導電層における前記溝の幅方向に面する2つの側面上にバリアメタル側壁を形成して、前記柱状体には前記バリアメタル側壁を含むようにする工程を有することを特徴とする請求項1〜6のいずれか1つに記載の半導体装置の製造方法。

【請求項8】

前記半導体基板に第1の方向に延びる溝を形成する工程の前に、前記半導体基板の上面に前記第1の方向と交差する方向に延びる複数本の素子分離領域を形成する工程をさらに備えたことを特徴とする請求項1〜7のいずれか1つに記載の半導体装置の製造方法。

【請求項9】

前記柱状体及び前記第1の導電層における前記溝の幅方向に面する2つの側面上にソース・ドレイン側壁を形成する工程と、

前記柱状体及び前記ソース・ドレイン側壁をマスクとして前記半導体基板に不純物を注入して、第1の不純物領域を形成する工程と、

前記半導体基板上に層間絶縁膜を形成する工程と、

前記層間絶縁膜に、前記第1の不純物領域に到達する貫通孔を形成する工程と、

前記貫通孔内に前記第1の不純物領域に接続する導電部材を埋設する工程と、

をさらに備えたことを特徴とする請求項1〜8のいずれか1つに記載の半導体装置の製造方法。

【請求項10】

前記ソース・ドレイン側壁を形成する工程の前に、

前記柱状体及び前記第1の導電層における前記溝の幅方向に面する2つの側面上にエクステンション側壁を形成する工程と、

前記柱状体及び前記エクステンション側壁をマスクとして前記半導体基板に不純物を注入して、第2の不純物領域を形成する工程と、

をさらに備えたことを特徴とする請求項9記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【公開番号】特開2012−204530(P2012−204530A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2011−66545(P2011−66545)

【出願日】平成23年3月24日(2011.3.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成23年3月24日(2011.3.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]