半導体装置の製造方法

【課題】半導体基板に形成された開口部の側壁全体を均一に成膜することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一実施形態に係る半導体装置の製造方法は、底壁及び複数の凹部を有する側壁により構成された開口部を素子が形成された半導体基板に形成し、前記開口部側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記底壁側に成膜部材を堆積させ、前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより前記成膜部材を前記側壁の各凹部の前記開口部側に堆積させることを特徴とする。

【解決手段】本発明の一実施形態に係る半導体装置の製造方法は、底壁及び複数の凹部を有する側壁により構成された開口部を素子が形成された半導体基板に形成し、前記開口部側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記底壁側に成膜部材を堆積させ、前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより前記成膜部材を前記側壁の各凹部の前記開口部側に堆積させることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に半導体基板の一方の面から他方の面に貫通する貫通電極を備えた貫通電極基板を用いた半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、電子機器の高密度化、小型化が進み、LSIチップが半導体パッケージと同程度まで縮小化しており、パッケージ内におけるチップの2次元配置による高密度化は限界に達しつつある。そこで、パッケージ内におけるチップの実装密度を上げるため、LSIチップを3次元に積層する必要がある。また、LSIチップを積層した半導体パッケージ全体を高速動作させるために積層回路間の距離を近づける必要がある。

【0003】

そこで、上記のような要求に応えるため、LSIチップ間のインターポーザとして基板の表面と裏面とを導通する導通部を備えた貫通電極基板が提案されている。このような貫通電極基板では、孔内部に導電材を充填することで貫通電極が形成されている。

【0004】

貫通電極基板は、半導体基板にRIE(Reactive Ion Etching:反応性イオンエッチング)、Deep−RIE(以下、DRIE)、光エッチング、ウェットエッチング、レーザー加工、サンドブラスト、ドリル等の方法により開口部(貫通孔の場合もある)を形成し、開口部の側壁に絶縁層やバリア層を形成した後、絶縁層やバリア層を介して開口部内に導電材を充填し、半導体基板の表裏導通をとることにより得られる。

【0005】

上述したような方法により形成された開口部の側壁には、意図しない凹凸構造が形成されることがある。例えば、DRIEにより開口部を形成した場合、スキャロップがこの意図しない凹凸構造に相当する。このような開口部の側壁に対して、成膜する場合には成膜付き回り性の優れるCVD法を用いるのが一般的である。しかし、CVD法のように熱プロセスを伴う方法は、予め素子の形成された半導体基板では素子が成膜時の熱の影響を受けるために採用できない。このため、蒸着法やスパッタ法等を用いて絶縁層を形成することがある。また、絶縁層を形成した開口部内に、バリア層及びシード層のメタル層の形成を行う工程においても、スパッタ法等を用いることがある。

【0006】

しかしながら、高密度実装にあわせて開口径の更なる微細化、それによる高アスペクト化が進み、従来の蒸着法やスパッタ法等の成膜法で開口部の側壁全体に成膜することが困難になってきている。例えば、スパッタ法を用いて開口部の側壁に絶縁層やメタル層を成膜する場合、直進性の高いスパッタ粒子は、開口部の側壁に形成された凹凸構造の内部にまで十分に回り込むことができず、成膜されない箇所が生じることがある。このように開口部の内壁に絶縁層やバリア層が成膜されない箇所があると、絶縁性やバリア性の点で不良となる。また、開口部の内壁にシード層が成膜されない箇所があると、電解メッキ時にボイド発生や断線を招くこととなる。その結果、貫通電極の信頼性が低下するといった問題が生じてくる。

【0007】

開口部内のシード層の成膜不良によりボイド発生を抑制するものとして、例えば、特許文献1には、底部近傍にノッチが存在する貫通孔にCVD法で絶縁層を被覆した後、スパッタ法によりメタル層を形成し、メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、貫通孔底部に積層したメタル層をスパッタエッチングし、あるいは、貫通孔底部にメタル層を積層すると同時にそのメタル層をスパッタエッチングし、そのスパッタエッチングしたメタル材料を飛散させ、ノッチ部分にメタル層を充填することが提案されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2009−259876号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献1に開示された貫通電極の製造方法は、貫通孔底部にあるメタル層を用いて、貫通孔底部近傍の限られた範囲であるノッチに対してメタル層を付着させようとするものであるから、スパッタ粒子の指向性を高めて貫通孔底部へスパッタリングガスを引き込んだり、分子量が大きいガスを用いる。そのため、基板表面へダメージを与えてしまう虞がある。また、貫通孔側壁に凹凸構造が存在し、凹凸構造に成膜されてない部分があっても、当該部分にメタル層等を成膜することはできない。

【0010】

本発明はこのような課題に鑑み、予め素子の形成された半導体基板に貫通電極を形成する際に、貫通孔又は貫通孔となる開口部の側壁全体に複数の凹凸構造が存在する場合でも、貫通孔又は貫通孔となる開口部の側壁全体に均一に成膜することができる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明の一実施形態に係る半導体装置の製造方法は、底壁及び複数の凹部を有する側壁により構成された開口部を素子が形成された半導体基板に形成し、前記開口部側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記底壁側に成膜部材を堆積させ、前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより前記成膜部材を前記側壁の各凹部の前記開口部側に堆積させることを特徴とする。本発明の一実施形態に係る半導体装置の製造方法によれば、開口部の側壁全体に複数の凹凸形状が形成される場合にも、開口部の側壁全体に均一に成膜することができる。

【0012】

前記複数の凹部は、エッチングによる前記半導体基板への溝の形成と、前記溝の内部への保護膜形成とを繰り返し行うことにより形成されてもよい。

【0013】

前記開口部に対向して前記成膜部材を含むターゲットを配置し、前記ターゲットに所定の電圧を印加しつつスパッタリングを行うことにより、前記底壁及び前記側壁の各凹部の前記底壁側に前記成膜部材を堆積させてもよい。

【0014】

前記成膜部材は絶縁部材であり、前記成膜部材を介して前記開口部内に導電部材を形成し、前記開口部が形成されている側と反対側の前記半導体基板の面から前記半導体基板を薄化して、前記半導体基板の表裏を導通する貫通電極を形成してもよい。

【0015】

また、 本発明の一実施形態に係る半導体装置の製造方法は、半導体基板の第1面と第2面を貫通し、側壁に複数の凹部を有する貫通孔を素子が形成された半導体基板に形成し、前記第1面側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記第2面側に第1成膜部材を堆積させ、前記半導体基板の第2面に直接又は離間して第2成膜部材を配置し、前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより、前記第1成膜部材及び前記第2成膜部材を前記側壁の各凹部の前記第1面側に堆積させることを特徴とする。本発明の一実施形態に係る半導体装置の製造方法によれば、開口部の側壁全体に複数の凹凸形状が形成される場合にも、開口部の側壁全体に均一に成膜することができる。

【0016】

前記複数の凹部は、エッチングによる前記半導体基板への溝の形成と、前記溝の内部への保護膜形成とを繰り返し行うことにより形成されてもよい。

【0017】

前記貫通孔に対向して前記第1成膜部材を含むターゲットを配置し、前記ターゲットに所定の電圧を印加しつつスパッタリングを行うことにより、前記底壁及び前記側壁の各凹部の前記第2面側に前記第1成膜部材を堆積させてもよい。

【0018】

前記成膜部材は絶縁部材であり、前記成膜部材を介して前記貫通孔の内部に導電部材を形成して貫通電極を形成してもよい。

【発明の効果】

【0019】

本発明によれば、予め素子の形成された半導体基板に貫通電極を形成する際に、貫通孔又は貫通孔となる開口部の側壁全体に複数の凹凸形状が形成される場合にも、貫通孔又は貫通孔となる開口部の側壁全体に均一に成膜することができる半導体装置の製造方法を提供することができる。

【図面の簡単な説明】

【0020】

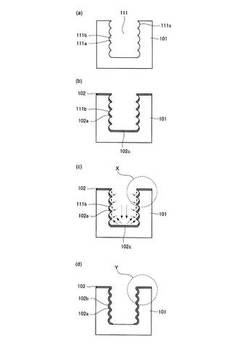

【図1】本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程を示す図であり、(a)は半導体基板に形成された開口部を示す断面図であり、(b)は第1の成膜工程を示す図であり、(c)は第2の成膜工程を示す図であり、(d)は開口部に形成された薄膜を示す断面図である。

【図2】図1に示した貫通電極基板を製造する工程を一部拡大して示す図であり、(a)は、図1(c)に示すX部分の拡大図であり、(b)は、図1(d)に示すY部分の拡大図である。

【図3】本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程に用いる装置を説明するための図である。

【図4】半導体基板に形成された開口部の断面の一例を示すSEM写真である。

【図5】図4に示すA領域の第1の成膜工程を行った後のSEM写真である。

【図6】図4に示すA領域の第2の成膜工程を行った後のSEM写真である。

【図7】図4に示すB領域の第1の成膜工程を行った後のSEM写真である。

【図8】図4に示すB領域の第2の成膜工程を行った後のSEM写真である。

【図9】図4に示すC領域の第1の成膜工程を行った後のSEM写真である。

【図10】図4に示すC領域の第2の成膜工程を行った後のSEM写真である。

【図11】図4に示すD領域の第1の成膜工程を行った後のSEM写真である。

【図12】図4に示すD領域の第2の成膜工程を行った後のSEM写真である。

【図13】図4に示すE領域の第1の成膜工程を行った後のSEM写真である。

【図14】図4に示すE領域の第2の成膜工程を行った後のSEM写真である。

【図15】図4に示すシリコン基板の表面、図4に示すA〜D領域におけるスキャロップの上部、及び図4に示すE領域において、第1の成膜工程後と第2の成膜工程後とで、絶縁膜の膜厚の比較を示す図である。

【図16】本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程を示す図であり、(a)はシード層の形成工程を示す図であり、(b)は導通部の形成工程を示す図であり、(c)は貫通電極基板を示す断面図である。

【図17】本発明の第2の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程を示す図であり、(a)は半導体基板に形成された貫通孔を示す断面図であり、(b)は第1の成膜工程により形成された絶縁膜を示す断面図であり、(c)は第2の成膜工程を示す図であり、(d)は貫通孔に形成された薄膜を示す断面図であり、(e)は(d)に示した半導体基板から不要な部分を取り除いた後の断面図である。

【図18】半導体基板に開口部を形成する工程の一例を示す図であり、(a)は半導体基板にエッチングマスクを配置した断面図であり、(b)はトレンチの形成工程を示す図であり、(c)は保護膜の形成工程を示す図であり、(d)はトレンチの形成工程を示す図であり、(e)は完成した開口部を示す断面図である。

【図19】半導体基板に形成された開口部の側壁に形成された凹部の例を示す図であり、(a)は、開口部の側壁に形成された凹部の一例を示す断面図であり、(b)は、開口部の側壁に形成された凹部の一例を示す断面図である。

【発明を実施するための形態】

【0021】

(第1の実施形態)

以下、図面を参照して、本発明の第1の実施形態に係る半導体装置の製造方法について詳細に説明する。

【0022】

第1の実施形態に係る半導体装置の製造方法は、貫通電極基板を用いた半導体装置の製造方法である。以下では、、図1、図2、図3、及び図18を参照し、本実施形態に係る半導体装置の製造方法について説明する。なお、半導体装置とは、半導体特性を利用して機能し得る装置全般を指し、半導体集積回路、電子機器は半導体装置の範囲に含むものとする。

【0023】

<貫通電極基板の製造方法>

図1は、本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程を示す図であり、(a)は半導体基板に形成された開口部を示す断面図であり、(b)は第1の成膜工程を示す図であり、(c)は第2の成膜工程を示す図であり、(d)は開口部に形成された薄膜を示す断面図である。図2は、図1に示した貫通電極基板を製造する工程を一部拡大して示す図であり、(a)は、図1(c)に示すX部分の拡大図であり、(b)は、図1(d)に示すY部分の拡大図である。図3は、本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する装置を説明するための図である。図18は、半導体基板に開口部を形成する工程の一例を示す図であり、(a)は半導体基板にエッチングマスクを配置した断面図であり、(b)はトレンチの形成工程を示す図であり、(c)は保護膜の形成工程を示す図であり、(d)はトレンチの形成工程を示す図であり、(e)は完成した開口部を示す断面図である。

【0024】

(1)半導体基板の準備

本実施形態においては、半導体基板としてシリコン基板101を準備する。シリコン基板101の厚さに制限はないが、取り扱い性を考慮すると50μm〜700μmの範囲のものを用いるのが好ましい。シリコン基板101には予め素子(図示せず)が形成されている。なお、シリコン基板101に形成される素子(図示せず)は公知の方法により配置される。形成される素子は抵抗、コイル、キャパシタ等の受動素子、メモリ、IC等の能動素子、発光素子、受光素子、センサ素子、スイッチング素子などが挙げられる。素子は、シリコン基板101の片側又は両側或いはシリコン基板101の内部に配置されている。

【0025】

(2)開口部111の形成

図18を参照して、図1(a)に図示した開口部111をシリコン基板101に形成する工程を説明する。開口部111は、シリコン基板101の一方の面と他方の面とを貫通しない溝として形成されている。開口部111の開口径に制限はないが、加工性、微細化への対応を考慮すると10μm〜200μmであることが好ましい。開口部111は、その内部に導電材を配置することによりシリコン基板101の一方の面と他方の面を導通する貫通電極が形成される部分である。図18は、DRIEにより、具体的にはボッシュプロセスにより開口部111を形成する工程を示している。

【0026】

図18(a)に図示したように、エッチングマスク106をシリコン基板101に配置する。エッチングマスク106をパターニングした後、図18(b)に図示したように、エッチングマスク106から露出したシリコン基板101に対して、エッチングガスとして例えば、SF6(六フッ化硫黄)を用いてシリコン基板101をエッチングしてトレンチ(溝)111tを形成する。SF6は等方性エッチングガスであるから、シリコン基板101の厚さ方向(縦方向ともよぶ)にエッチングが進むとともに、シリコン基板101の面方向(横方向ともよぶ)にもエッチングが進む。その後、図18(c)に図示したように、C4F8(パーフルオロシクロブタン)を用いてエッチング面に保護膜(フルオロカーボン膜)107を形成する。次いで、図18(d)に図示したように、保護膜107の形成されたエッチング底面を、SF6(六フッ化硫黄)を用いてエッチングすることにより、保護膜107を除去してさらにトレンチ111tを形成する。このように、ボッシュプロセスでは、図18(b)又は(d)に示したエッチングによりトレンチ111tを形成する工程と、図18(c)に示すエッチング面に保護膜107を形成する工程とを交互に繰り返す。これにより、図18(e)に図示したような開口部111を形成することができる。なお、エッチング工程と保護膜形成工程は各々重複しないよう設定されてもよいし、一部が重複するように設定されていてもよい。

【0027】

図18(e)に図示したように、ボッシュプロセスでは、開口部111の側壁に複数の凹部が生じ、エッチングマスク106の境界である開口部111の開口側の径よりも横方向に広がったスキャロップと呼ばれる凹凸構造(以下、スキャロップ111sという)が連続して形成される。スキャロップ111sは開口部111の深さ方向に連続して形成され、開口部111の側壁に複数の凹部が形成される。スキャロップ111sは、エッチングと保護膜形成の強度関係や時間比などによりその形状が変化するが、通常、横方向の深さP−V値が0.1μm〜0.5μm程度であり、縦方向のスキャロップ幅が0.1μm〜2.0μm程度の大きさを有する。以下では、図18(e)に一例として図示したスキャロップ111sの形成された開口部111に貫通電極を形成する方法について説明するが、開口部111の側壁に形成される複数の凹部は、ボッシュプロセスにより形成されるスキャロップ111sに限らず、他の方法により開口部111の側壁に連続的または局所的に形成される凹部であってもよい。複数の凹部の例を図19を用いて説明する。図19は、開口部111の側壁に形成される複数の凹部の一例を示す断面図である。図19(a)は、DRIEにより側壁にえぐれのような凹部111uが形成されている例を示す。図19(b)は、サンドブラスト、ドリル加工等により生じた側壁表面の荒れにより凹部111vが形成されている例を示す。このように、複数の凹部は、図18に図示したスキャロップ111sのような形状に限らず、図19に図示した凹部111u、111vのような形状であってもよい。

【0028】

また、図18(b)〜(e)ではスキャロップ111sのスキャロップ幅が全て一定として図示しているが、観察する側壁の位置により、その幅が異なる場合がある。例えば、エッチング条件を同一として実行した場合には、開口部側のスキャロップ幅及びP−V値の方が、底壁側のそれらよりも大きくなる傾向にある。このようなスキャロップ111sにより構成される側壁の凹凸構造は、開口部111内部に絶縁層やメタル層を形成する際に成膜できない部分を作り出し、後述する工程により形成される貫通電極の絶縁不良、バリア不良、導通不良などの諸々の原因となることがある。開口部側のスキャロップのP−V値が底壁側に比べて大きい場合、P−V値の高い箇所に均一に成膜することは困難となる。このため、スキャロップ111sを隙間なく覆い、開口部111の側壁面全体に均一に成膜する方法が求められる。

【0029】

以下、図1〜図3を参照し、図18(e)に図示したスキャロップ111sの形成された開口部111の側壁に絶縁膜102を成膜する方法について説明する。絶縁膜102は、単層として形成してもよく、2層以上の積層構造として形成してもよい。以下では、絶縁膜102を成膜する場合について説明するが、成膜するものがバリア膜、シード膜であってもよい。なお、図18(e)に示した保護膜107は、開口部111を完成させた後に除去してもよい。また、図示していないが、開口部111を完成させた後、開口部111を形成した面とは反対側の面から研磨、エッチング等の方法でシリコン基板101を後退(薄化)させて孔を貫通させ、貫通孔を形成してもよい。本実施形態では、保護膜107を除去した後の開口部111に貫通電極を形成する方法について以下に述べる。

【0030】

(3)絶縁膜102の形成

図1(a)に図示したように、開口部111の側壁には、上述した図18に示す工程により、複数の凹部からなるスキャロップ111sが形成される。以下、スキャロップ111sの各凹部のうち、開口部111の開口側(図1に示すシリコン基板101の上面側)の部分をスキャロップ111sの上部111bといい、開口部111の底壁側(図1に示すシリコン基板101の下面側)の部分をスキャロップ111sの下部111aという。図1(a)に示した開口部111の側壁及び底壁を含む内壁並びにシリコン基板101の上面に、絶縁膜102を形成する。絶縁膜102は、例えば、二酸化シリコン(SiO2)、窒化シリコン(SiN)、炭化シリコン(SiC)等の絶縁層から構成されるものであってもよい。このような絶縁膜102は、スパッタ法や真空蒸着法等を用いて形成される。スパッタ法等を用いることにより、予めシリコン基板101に素子等が形成されている場合にも、熱プロセスを伴わないため、熱による素子への影響を与えないようにすることができる。

【0031】

(3−1)第1の成膜工程

図1(b)は、第1の成膜工程を示す図であり、図1(b)に図示したように、開口部111の側壁、開口部111の底壁、及びシリコン基板101の上面に絶縁膜102を形成する。本実施形態として、以下では、図3に図示するスパッタ装置200を用いてスパッタリングを行う工程を説明する。

【0032】

図3に図示したように、スパッタ装置200は、チャンバー201、ターゲット202、試料台203、電源204、ガス導入装置205、排気装置206、及び制御装置207を含む。スパッタ装置200のチャンバー201内には、試料台203の上に、開口部111が上を向いて位置するようにシリコン基板101が配置され、シリコン基板101の開口部111と対向する位置に成膜材料であるターゲット202が配置される。本実施形態において、ターゲット202は絶縁部材からなる。チャンバー201内を真空にしてガス導入装置205から、例えばAr(アルゴン)ガスを導入し、電源204を制御装置207により制御し、チャンバー201とターゲット202に高周波(RF)電圧をかけると、ターゲット202に負のバイアス電圧が生じ、Arイオンがターゲット202に衝突し、ターゲット202に衝突したArイオンは、ターゲット202の粒子をはじき飛ばし、はじき飛ばされた絶縁部材の粒子がシリコン基板101の上面及び開口部111の内壁に衝突、付着し、絶縁膜102が形成される。

【0033】

ここで、第1の成膜工程におけるスパッタ装置200のスパッタリング条件としては、以下のような条件で行ってもよい。例えば、ターゲット202とシリコン基板101との距離を100mmとし、圧力を0.3Pa、RFパワーを2000W、基板バイアス負電圧を0V、Ar流量を20〜25sccmとしてスパッタを行う。

【0034】

第1の成膜工程によると、図1(b)に図示したように、スキャロップ111sの下部111a(各凹部の底壁側の部分)と開口部111の底壁には絶縁膜102(102a、102c)が堆積されることがわかる。しかしながら、図1(b)に図示したスキャロップ111sの上部111b(各凹部の開口部111側の部分)には、ほとんど絶縁膜102が堆積されないことがわかる。これは、開口部111の上部に配置されたターゲット202から飛散するスパッタ粒子が直進性を有していることや、スキャロップ111sの形状が庇のように働くため、スキャロップ111sの上部111bにまで到達しないと考えられる。

【0035】

なお、第1の成膜工程として、スパッタ法を用いることを説明したが、真空蒸着法を用いてもよい。真空蒸着法による場合も、スキャロップ111sの下部111aと開口部111の底壁には絶縁膜102(102a、102c)が堆積されるが、スキャロップ111sの上部111bには、絶縁膜102が堆積されず、図1(b)に図示したような絶縁膜102が形成される。

【0036】

次にスキャロップ111sの上部111bに絶縁膜102を成膜するための第2の成膜工程について以下に述べる。

【0037】

(3−2)第2の成膜工程

図1(c)は、第2の成膜工程を示す図であり、図1(d)は第2の成膜工程後の開口部111に形成された絶縁膜102を示す図である。また、図2(a)は、図1(c)に示すX部分の拡大図であり、図2(b)は、図1(d)に示すY部分の拡大図である。

【0038】

まず、図1(b)に図示した第1の成膜工程後のシリコン基板101を、図3に図示したチャンバー201内の試料台203の上に配置する。チャンバー201内を真空にしてガス導入装置205から、例えばAr(アルゴン)ガスを導入し、電源204を制御装置207により制御し、チャンバー201と試料台203に高周波電圧をかけると、シリコン基板101やスキャロップ111sの下部111a及び開口部111の底壁に堆積された絶縁膜102(102a、102c)に負のバイアス電圧が生じる。これにより、Arイオンはスキャロップ111sの下部111a及び開口部111の底壁に堆積された絶縁膜102(102a、102c)に引き寄せられて衝突し、絶縁膜102a、102cの粒子をはじき飛ばし、はじき飛ばされた絶縁膜102a、102cの粒子が、開口部111の内壁に衝突、付着し、スキャロップ111sの上部111bにおいても、図2(d)に図示したように絶縁膜102bが形成される。

【0039】

ここで、第2の成膜工程では、Arイオンの指向性を高めすぎないことにより、絶縁膜102aをスパッタエッチングしてスキャロップ111sの上部111bに効果的に成膜を施すことができる。第2の成膜工程におけるスパッタ装置200のスパッタリング条件として、例えば、圧力を0.16Pa、RFパワーを300W、Ar流量を10sccm、基板バイアス負電圧を0Vとして、スパッタを行ってもよい。なお、以下に表1として、本発明の第一の実施形態に係る第1の成膜工程及び第2の成膜工程のスパッタリング条件の一例についてまとめた表を示す。

【表1】

【0040】

上述した条件によれば、例えばロングスロー法を用いたスパッタ装置において圧力を0.1Pa程度としてスパッタリングを行うことと比較して、圧力を高めることにより指向性を低くすることができる。従って、第2の成膜工程によれば、指向性の高いロングスロー法やコリーメート法を用いたスパッタ装置よりも指向性を低くすることができ、スキャロップ111sの内部にまで十分にスパッタ粒子を飛散させることができる。

【0041】

なお、第1の成膜工程と第2の成膜工程とで、いずれもスパッタ法を用いる場合には、スパッタ装置200は、同じチャンバー201を用いるようにしてもよいが、異なるチャンバー201を用いるようにしてもよい。異なるチャンバー201を用いる場合には、連結された2つのチャンバー201を用いて、第1の成膜工程においては、チャンバー201とターゲット202に高周波電圧をかけ、第2の成膜工程においては、チャンバー201と試料台203に高周波電圧をかけるように、それぞれスパッタリング条件を異なるものに設定し、第1の成膜工程と第2の成膜工程とで、2つのチャンバー201間を、シリコン基板101を搬送できるようにスパッタ装置200を構成してもよい。

【0042】

このように、第2の成膜工程により、図1(d)及び図2(b)に図示したように、スキャロップ111sの上部111bにおいても絶縁膜102bを形成することができるため、開口部111の側壁面全体を隙間無く均一に覆う絶縁膜102bを形成することができる。また、図2(a)と図2(b)とを比較すると、スキャロップ111sの凹部の横方向の深さを小さくすることができるため、開口部111の側壁面を平滑化することができることもわかる。開口部111の側壁を平滑化することにより、後述する導電材を充填する際の充填性を向上させる効果が期待できる。なお、開口部111は、後の工程においてシリコン基板101の下面を研磨、エッチング等することにより貫通孔として形成されるため、図1(d)に図示したように、開口部111の底面に形成された絶縁膜102cが第2の成膜工程により削られ、除去されてもよい。

【0043】

以下、さらに詳細に、本実施形態に係る半導体装置の製造方法の第1の成膜工程及び第2の成膜工程により開口部111の内壁に形成された絶縁膜102の状態について、図4〜図15に示したSEM写真を参照して説明する。

【0044】

図4は、半導体基板に形成された開口部111の断面の一例を示すSEM写真である。図5は、図4に示すA領域の第1の成膜工程を行った後のSEM写真である。図6は、図4に示すA領域の第2の成膜工程を行った後のSEM写真である。図7は、図4に示すB領域の第1の成膜工程を行った後のSEM写真である。図8は、図4に示すB領域の第2の成膜工程を行った後のSEM写真である。図9は、図4に示すC領域の第1の成膜工程を行った後のSEM写真である。図10は、図4に示すC領域の第2の成膜工程を行った後のSEM写真である。図11は、図4に示すD領域の第1の成膜工程を行った後のSEM写真である。図12は、図4に示すD領域の第2の成膜工程を行った後のSEM写真である。図13は、図4に示すE領域の第1の成膜工程を行った後のSEM写真である。図14は、図4に示すE領域の第2の成膜工程を行った後のSEM写真である。図15は、シリコン基板101の表面、図4に示すA〜D領域のスキャロップ111sの上部111b、及び開口部111の底面である図4に示すE領域において、第1の成膜工程後と第2の成膜工程後とで、それぞれ絶縁膜102の膜厚の比較を示す図である。

【0045】

図4に示す開口部111は、上述した図18に示す形成工程によりシリコン基板101に形成された開口部111の一例を示したものである。開口部111の側壁面には、図4に示すように、スキャロップ111sが形成される。図4に示す開口部111の大きさは、開口径が180μm、深さが180μm、スキャロップ幅が1.5μm、P−V値が0.26μm〜0.35μmである。図4に示す開口部111の内壁に対し、成膜材料にSiO2を用いて、第1の成膜工程及び第2の成膜工程を行ったところ、図5〜図14のSEM写真に示すように絶縁膜102が形成された。

【0046】

図5及び図6は、図4に示すシリコン基板101の表面から深さ5μm程度の開口部111のA領域において、第1の成膜工程後又は第2の成膜工程後の内壁の断面をそれぞれ示したSEM写真である。図5と図6とを比較すると、第1の成膜工程後は、図5に示したように、スキャロップ111sの下部111aに集中して絶縁膜102aが形成されることがわかる。しかし、第2の成膜工程により、図6に示したように、スキャロップ111sの上部111bにおいても絶縁膜102bが形成され、絶縁膜102の膜厚が均一になることがわかる。

【0047】

また、図5に示されるように、第1の成膜工程後は、シリコン基板101の表面には絶縁膜102が厚く堆積し、開口部111の開口の縁部に、開口の内側に向かって庇のように突出した形状を有する絶縁膜102dが形成されることがわかる。このような形状を有する絶縁膜102dは、さらに他の膜等を開口部111内部に形成する場合に、均一に膜等を形成することの妨げとなり、不具合を生じさせる原因となることがある。しかし、本実施形態によれば、第2の成膜工程により、スパッタリングによって開口部111の内壁に付着した絶縁膜102の粒子を、下から上方向に飛散させるため、開口の縁部から突出した絶縁膜102dの突出部分を削り取ることができる。これにより、図6に示した絶縁膜102eのように、絶縁膜102eの角部が平坦化されたような形状を有するように形成することもできる。従って、本実施形態によれば、第1の成膜工程により、開口部111の開口付近に突出して形成された絶縁膜102dの突出部分を、第2の成膜工程により除去することもできるため、開口部111の内壁にさらに他の膜等を形成する場合にも、均一に形成することができる。

【0048】

図7及び図8は、図4に示すシリコン基板101の表面から深さ45μm程度の開口部111のB領域において、第1の成膜工程後又は第2の成膜工程後の内壁の断面をそれぞれ示したSEM写真である。また、図9及び図10は、図4に示すシリコン基板101の表面から深さ90μm程度の開口部111のC領域において、第1の成膜工程後又は第2の成膜工程後の内壁の断面をそれぞれ示したSEM写真である。図11及び図12は、図4に示すシリコン基板101の表面から深さ175μm程度の開口部111のD領域において、第1の成膜工程後又は第2の成膜工程後の内壁の断面をそれぞれ示したSEM写真である。図7と図8、図9と図10、図11と図12をそれぞれ比較すると、第1の成膜工程後は、スキャロップ111sの下部111aに集中して絶縁膜102aが形成されるが、第2の成膜工程により、スキャロップ111sの上部111bにも絶縁膜102bが形成され、開口部111の側壁面全体に成膜されることがわかる。従って、図5〜図12に示したように、A領域からD領域にわたって開口部111の側壁面全体にスキャロップ111のような凹凸構造を有する場合にも、絶縁膜102を均一に形成することができることがわかる。

【0049】

図13及び図14は、図4に示すシリコン基板101の表面から深さ185μm程度の開口部111の底部であるE領域において、第1の成膜工程後及び第2の成膜工程後の成膜状態をそれぞれ示した底部の断面のSEM写真である。図13と図14とを比較すると、第1の成膜工程後、開口部111の底面に堆積していた絶縁膜102cは、第2の成膜工程のスパッタリングにより、ほぼ除去されていることがわかる。

【0050】

図15は、開口部111の開口付近のシリコン基板101の表面、図4に示すA〜D領域におけるスキャロップ111sの上部111b、及び開口部111の底部である図4に示すE領域において、第1の成膜工程後と第2の成膜工程後とで、それぞれ絶縁膜102の膜厚の比較を示す図である。図15に示すように、シリコン基板101の表面及び開口部111の底部であるE領域は、第2の成膜工程後に、第1の成膜工程により形成された絶縁膜102がスパッタリングにより削られ、シリコン基板101の表面においては絶縁膜102の膜厚が減少し、底部のE領域においてはほぼ除去されることがわかる。また、開口部111の側壁に形成されたスキャロップ111sの上部111bは、C領域及びD領域において、第1の成膜工程後に絶縁膜102が形成されないことがわかる。しかし、第2の成膜工程後は、C領域及びD領域のスキャロップ111sの上部111bにも絶縁膜102が形成され、A〜D領域の内壁全体において、スキャロップ111sの上部111bの絶縁膜102の膜厚がそれぞれ増加していることがわかる。

【0051】

以上のように、本発明の第1の実施形態によれば、開口部111の側壁全体にスキャロップ111sのような複数の凹凸が形成されている場合にも、第1の成膜工程により、開口部111の底壁及びスキャロップ111sの下部111aに絶縁膜102を堆積した後、第2の成膜工程により、堆積された絶縁膜102を用いてシリコン基板101に所定の電圧を印加しつつスパッタリングを行うことによって、開口部111の側壁全体を均一に成膜することができる。従って、本発明の第1の実施形態によれば、側壁全体に隙間無く絶縁膜を形成することができるので、絶縁不良が防止され、貫通電極基板を製造する際の歩留まりを向上させ、その信頼性を向上させることができる。

【0052】

次に、図16を参照し、シード層113及び導通部114を形成する工程を説明する。図16は、本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板110を製造する工程を示す図であり、(a)はシード層113の形成工程を示す図であり、(b)は導通部114の形成工程を示す図であり、(c)は貫通電極基板110を示す断面図である。

【0053】

(4)シード層113の形成

図16(a)に示すように、シリコン基板101の絶縁膜102が形成された面及び開口部111の絶縁膜102が形成された内部に、シード層113を形成する。シード層113は、図示していないが、バリア膜とシード膜の積層構造により構成される。シード層113は、シリコン基板101側にバリア膜として例えばTiやTiN、その上にシード膜として例えばCuが積層された構造としてもよい。

【0054】

絶縁膜102の形成されたシリコン基板101の上に、バリア膜として、例えば窒化チタン(TiN)を成膜する。窒化チタンは絶縁膜102の成膜方法と同様に、予め素子が形成された基板に成膜することから、熱プロセスを伴わないスパッタ法等により成膜することが好ましい。上述した第1の成膜工程及び第2の成膜工程と同様の方法を用いることがより好ましい。これにより、開口部111の側壁に形成された絶縁膜102の表面を隙間無く覆うバリア膜を形成することができる。従って、後述する工程において充填される金属がシリコン基板101側に拡散することを防止することができる。

【0055】

次に、バリア膜の上にシード膜を成膜する。シード膜の成膜方法は、蒸着法、スパッタ法などから適宜選択できる。しかし、基板に予め素子が形成されていることから、熱プロセスを伴わないスパッタ法等によることが好ましい。上述した第1の成膜工程及び第2の成膜工程と同様の方法を用いることがより好ましい。これにより、バリア膜の表面を隙間無く覆うシード膜を形成することができる。なお、シード膜に用いる金属材料は、後述する図16(b)に示す導通部114の金属材料によって適宜選択することができる。シード膜は、電解メッキによって導通部114を形成するためのシード部及び給電部となる。なお、他の方法で導通部114を形成する場合には、シード層113は導通部114との密着性を高めるためのメタル層として機能する。

【0056】

このような工程によりバリア膜及びシード膜を形成することにより、図16(a)に示すシード層113が形成される。シード層113は、上述した第1の成膜工程及び第2の成膜工程と同様の方法を用いて形成することにより、開口部111の側壁に形成された絶縁膜102の表面を隙間無く均一に覆うように形成することができる。

【0057】

(5)導通部114の形成

次に、図16(b)に示すように、電解メッキによってシリコン基板101のシード層113を給電層として開口部111内部に導電材を充填して、導通部114を形成する。導電材の充填には、スパッタ法、電解メッキ法、溶融金属吸引法(圧力差を利用して溶融した金属を開口部へ引入れる方法)、印刷法等も使用することができる。開口部111が微細な場合には、電解メッキ法を用いることが好ましい。開口部111に充填する金属材料としては、銅(Cu)の他、金(Au)、ロジウム(Rh)、銀(Ag)、白金(Pt)、スズ(Sn)、アルミニウム(Al)、ニッケル(Ni)、クロム(Cr)等の金属及びこれらの合金などから選択され組み合わせた材料を用いてもよい。電解メッキ法により導電材を充填する場合、シード層113が均一に形成されているので充填される金属にボイド等の不良が発生することを防止できる。

【0058】

(6)不要な部分の除去

次に、シード層113及び導通部114の不要部をエッチングあるいはCMPにより除去する。また、開口部111が形成されている側と反対側のシリコン基板101面をバックグラインドによって導通部114の表面が露出するまで研磨することにより、導通部114を形成する。研磨により、シリコン基板101の厚さを薄くしてもよい。以上のプロセスによって、第1の実施形態に係る貫通電極基板110を得ることができる。

【0059】

このような製造工程により製造された貫通電極基板110を用いて、例えば、基板上に形成された素子の接続端子部と、貫通電極基板110の導通部114とを接続させることにより、半導体装置を形成することが可能となる。従って、本実施形態に係る半導体措置の製造方法によれば、貫通電極の絶縁不良、バリア不良、導通不良等を発生させないように貫通電極基板110を形成することができるため、信頼性を向上させた半導体装置を提供することが可能となる。

【0060】

以上、本発明の第1の実施形態によれば、上述した第1の成膜工程及び第2の成膜工程によって、開口部111の側壁全体にスキャロップ111sが形成されている場合にも、スキャロップ111sを隙間なく均一に覆う絶縁膜102及び絶縁膜102を隙間無く均一に覆うシード層113を形成することができるため、開口部111内部に貫通電極を形成する際に、ボイド等を生じさせずに貫通電極を形成することができる。これにより、本実施形態に係る半導体装置の製造方法によれば、貫通電極基板を製造する際の歩留まりを向上させ、その信頼性を向上させることができる。

【0061】

(第2の実施形態)

以下、図面を参照して、本発明の第2の実施形態に係る半導体装置の製造方法を詳細に説明する。第2の実施形態に係る半導体装置の製造方法は、第1の実施形態に係る半導体装置の製造方法と同様に、貫通電極基板を用いた半導体装置を製造するものである。なお、第1の実施形態に係る製造工程と同様の工程については、詳細な説明について省略する。

【0062】

<貫通電極基板の製造方法>

第2の実施形態に係る半導体装置の製造方法について、図17を参照して説明する。図17は、本発明の第2の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程を示す図であり、(a)はシリコン基板101に形成された貫通孔112を示す断面図であり、(b)は第1の成膜工程により形成された絶縁膜102を示す断面図であり、(c)は第2の成膜工程を示す図であり、(d)は貫通孔112に形成された絶縁膜102を示す断面図であり、(e)は(d)に示したシリコン基板101から不要な部分を取り除いた後の断面図である。

【0063】

(1)基板の準備

本実施形態においても、上述した第1の実施形態と同様に、基板としてシリコン基板101を準備する。シリコン基板101には予め素子(図示せず)が形成されている。形成される素子は抵抗、コイル、キャパシタ等の受動素子、メモリ、IC等の能動素子、発光素子、受光素子、センサ素子、スイッチング素子などが挙げられる。素子は、シリコン基板101の片側又は両側或いはシリコン基板101の内部に配置されている。

【0064】

(2)貫通孔112の形成

図17(a)に示す貫通孔112は、上述した第1の実施形態に係る開口部111の形成工程と同様に、DRIEにより、具体的にはボッシュプロセスにより形成されてもよい。シリコン基板111は第1の面(以下、上面ともよぶ)と第2の面(以下、下面ともよぶ)を連通する少なくとも1つの貫通孔を有している。図17(a)に図示していないが、シリコン基板101の下面にシリコン基板101を支持する基板を貼り付けてエッチングしてもよい。本実施形態においても、エッチングマスク(図示せず)をシリコン基板101の上面に配置し、ボッシュプロセスによりシリコン基板101を貫通する貫通孔112を形成する。これにより、図17(a)に示すように、貫通孔112の側壁面全体に、図1(a)に示す開口部111の側壁面と同様の複数の凹部からなるスキャロップ111sが形成される。

【0065】

(3)絶縁膜102の形成

(3−1)第1の成膜工程

図17(b)は、第1の成膜工程により形成された絶縁膜102を示す断面図であり、図17(a)に図示した貫通孔112の側壁及びシリコン基板101の上面に、上述した第1の実施形態に係る第1の成膜工程と同様に、スパッタ法又は真空蒸着法等を用いて絶縁膜102を形成する。

【0066】

スパッタ法を用いる場合には、上述した第1の実施形態に係る第1の成膜工程と同様に、貫通孔112が形成されたシリコン基板101を、図3に示すスパッタ装置200の試料台203上に第1の面が上側となるように配置し、チャンバー201内を真空にしてガス導入装置205から、例えばAr(アルゴン)ガスを導入し、電源204を制御装置207により制御し、チャンバー201とターゲット202に高周波(RF)電圧をかけると、ターゲット202に負のバイアス電圧が生じ、Arイオンがターゲット202に衝突し、ターゲット202に衝突したArイオンは、ターゲット202の粒子をはじき飛ばし、はじき飛ばされた成膜材料(絶縁部材)の粒子がシリコン基板101の上面及び貫通孔112の内壁に衝突、付着し、絶縁膜102が形成される。図17(b)に図示したように、第1の成膜工程によると、貫通孔112の側壁面において、スキャロップ111sの下部111a(各凹部の第2の面側)には絶縁膜102aが形成されるが、スキャロップ111sの上部111b(各凹部の第1の面側)には絶縁膜102が形成されない部分が生じる。

【0067】

(3−2)第2の成膜工程

図17(c)は、第2の成膜工程を示す図であり、図17(b)に示す第1の成膜工程後のシリコン基板101の下面に、絶縁膜102の成膜材料であるターゲット基板103を配置する。ターゲット基板103は、第1の成膜工程に用いたターゲット202と同様の成膜材料を用いることが望ましい。ここでは、ターゲット基板103は、絶縁膜102の成膜材料を含むものとする。なお、図17(c)に図示するように、ターゲット基板103の下面には、別途、ターゲット基板103を支持する基板104を配置してもよい。ターゲット基板103は、シリコン基板101の下面に直接接するように配置されていてもよいが、所定の間隙をもって配置されていてもよい。シリコン基板101の下面とターゲット基板103を離間して配置する場合には、シリコン基板101の下面に素子等が配置される際素子等の破損する可能性が排除できる。また、シリコン基板101の下面への取り付け、第2の成膜後の取り外しが容易となる。

【0068】

図17(c)に図示したターゲット基板103が下面に配置されたシリコン基板101を、図3に図示したスパッタ装置200の試料台203上に第1の面が上側となるように配置し、上述した第1の実施形態に係る第2の成膜工程と同様に、チャンバー201内を真空にしてガス導入装置205から、例えばAr(アルゴン)ガスを導入し、電源204を制御装置207により制御し、チャンバー201と試料台203に高周波電圧をかけると、シリコン基板101及びターゲット基板103に負のバイアス電圧が生じ、Arイオンがスキャロップ111sの下部111b及びターゲット基板103に引き寄せられ、Arイオンがスキャロップ111sの下部111aに形成された絶縁膜102a及びターゲット基板103に衝突して絶縁膜102の粒子をはじき飛ばし、はじき飛ばされた絶縁膜102の粒子が貫通孔112の側壁に衝突、付着し、スキャロップ111sの上部111bにも、図17(d)に図示したように絶縁膜102bが形成される。

【0069】

このように、本発明の第2の実施形態によれば、貫通孔112の側壁面全体にスキャロップ111sのような複数の凹凸が形成されている場合にも、第1の成膜工程により、貫通孔112のスキャロップ111sの下部111aに絶縁膜102を堆積した後、第2の成膜工程により、堆積された絶縁膜102を用いてシリコン基板101に所定の電圧を印加しつつスパッタリングを行うことによって、貫通孔112の側壁全体を均一に成膜することができる。従って、本発明の第2の実施形態によれば、後述する工程において貫通孔112に導電材を埋め込み貫通電極を形成した場合にも、ボイド等を生じさせずに形成することができるため、貫通電極基板を製造する際の歩留まりを向上させ、その信頼性を向上させることができる。

【0070】

(4)シード層113の形成

次に、図16を参照して、シード層113を形成する工程を説明する。上述した第1の実施形態と同様に、シリコン基板101の絶縁膜102が形成された面及び貫通孔112の内部に形成された絶縁膜102上に、シード層113を形成する。第1の実施形態と同様に、シード層113はバリア膜及びシード膜を含み、上述した第1の成膜工程及び第2の成膜工程を用いてバリア膜及びシード膜を成膜してもよい。これにより、貫通孔112の内部に形成された絶縁膜102の表面を隙間無く均一に覆うシード層113を形成することができる。従って、このような工程により形成されたシード層113によれば、第1の実施形態と同様に、後述する工程において充填される金属がシリコン基板101側に拡散することを防止し、且つボイド等の不良が発生することを防止することができる。

【0071】

(5)導通部114の形成

次に、上述した第1の実施形態と同様に、図16(b)に示すように、電解メッキによってシリコン基板101のシード層113を給電層として貫通孔112内部に導電材を充填して、導通部114を形成する。上述したように、予め素子が形成された基板に導通部114を形成することから、熱プロセスを伴わないスパッタ法を用いることが好ましい。導通部114は、絶縁膜102の表面を隙間無く覆うシード層113上に形成することができるため、ボイド等を生じさせることなく形成することができる。なお、貫通孔112に充填する金属材料としては、銅(Cu)の他、金(Au)、ロジウム(Rh)、銀(Ag)、白金(Pt)、スズ(Sn)、アルミニウム(Al)、ニッケル(Ni)、クロム(Cr)等の金属及びこれらの合金などから選択され組み合わせた材料を用いてもよい。

【0072】

(6)不要な部分の除去

次に、上述した第1の実施形態と同様に、シード層113及び導通部114の不要部をエッチングあるいはCMPにより除去する。研磨により、シリコン基板101の厚さを薄くしてもよい。以上のプロセスにより、図16(e)に示す貫通電極基板110と同様の、第2の実施形態に係る貫通電極基板110を得ることができる。

【0073】

このような製造工程により製造された貫通電極基板110を用いて、例えば、基板上に形成された素子の接続端子部と、貫通電極基板110の導通部114とを接続させることにより、半導体装置を形成することが可能となる。従って、本実施形態に係る半導体措置の製造方法によれば、貫通電極の絶縁不良、バリア不良、導通不良等を発生させないように貫通電極基板110を形成することができるため、信頼性を向上させた半導体装置を提供することができる。

【0074】

以上、本発明の第2の実施形態によれば、上述した第1の成膜工程及び第2の成膜工程によって、貫通孔112の側壁面全体にスキャロップ111sが形成されている場合にも、スキャロップ111sの形成された貫通孔112を隙間なく均一に覆う絶縁膜102及び絶縁膜102を隙間無く均一に覆うシード層113を形成することができるため、ボイド等を生じさせずに貫通電極を形成することができる。従って、本実施形態によれば、貫通電極基板を製造する際の歩留まりを向上させ、その信頼性を向上させることができる。

【符号の説明】

【0075】

101…シリコン基板、102…絶縁膜、110…貫通電極基板、111…開口部、111s…スキャロップ、112…貫通孔、200…スパッタ装置

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に半導体基板の一方の面から他方の面に貫通する貫通電極を備えた貫通電極基板を用いた半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、電子機器の高密度化、小型化が進み、LSIチップが半導体パッケージと同程度まで縮小化しており、パッケージ内におけるチップの2次元配置による高密度化は限界に達しつつある。そこで、パッケージ内におけるチップの実装密度を上げるため、LSIチップを3次元に積層する必要がある。また、LSIチップを積層した半導体パッケージ全体を高速動作させるために積層回路間の距離を近づける必要がある。

【0003】

そこで、上記のような要求に応えるため、LSIチップ間のインターポーザとして基板の表面と裏面とを導通する導通部を備えた貫通電極基板が提案されている。このような貫通電極基板では、孔内部に導電材を充填することで貫通電極が形成されている。

【0004】

貫通電極基板は、半導体基板にRIE(Reactive Ion Etching:反応性イオンエッチング)、Deep−RIE(以下、DRIE)、光エッチング、ウェットエッチング、レーザー加工、サンドブラスト、ドリル等の方法により開口部(貫通孔の場合もある)を形成し、開口部の側壁に絶縁層やバリア層を形成した後、絶縁層やバリア層を介して開口部内に導電材を充填し、半導体基板の表裏導通をとることにより得られる。

【0005】

上述したような方法により形成された開口部の側壁には、意図しない凹凸構造が形成されることがある。例えば、DRIEにより開口部を形成した場合、スキャロップがこの意図しない凹凸構造に相当する。このような開口部の側壁に対して、成膜する場合には成膜付き回り性の優れるCVD法を用いるのが一般的である。しかし、CVD法のように熱プロセスを伴う方法は、予め素子の形成された半導体基板では素子が成膜時の熱の影響を受けるために採用できない。このため、蒸着法やスパッタ法等を用いて絶縁層を形成することがある。また、絶縁層を形成した開口部内に、バリア層及びシード層のメタル層の形成を行う工程においても、スパッタ法等を用いることがある。

【0006】

しかしながら、高密度実装にあわせて開口径の更なる微細化、それによる高アスペクト化が進み、従来の蒸着法やスパッタ法等の成膜法で開口部の側壁全体に成膜することが困難になってきている。例えば、スパッタ法を用いて開口部の側壁に絶縁層やメタル層を成膜する場合、直進性の高いスパッタ粒子は、開口部の側壁に形成された凹凸構造の内部にまで十分に回り込むことができず、成膜されない箇所が生じることがある。このように開口部の内壁に絶縁層やバリア層が成膜されない箇所があると、絶縁性やバリア性の点で不良となる。また、開口部の内壁にシード層が成膜されない箇所があると、電解メッキ時にボイド発生や断線を招くこととなる。その結果、貫通電極の信頼性が低下するといった問題が生じてくる。

【0007】

開口部内のシード層の成膜不良によりボイド発生を抑制するものとして、例えば、特許文献1には、底部近傍にノッチが存在する貫通孔にCVD法で絶縁層を被覆した後、スパッタ法によりメタル層を形成し、メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、貫通孔底部に積層したメタル層をスパッタエッチングし、あるいは、貫通孔底部にメタル層を積層すると同時にそのメタル層をスパッタエッチングし、そのスパッタエッチングしたメタル材料を飛散させ、ノッチ部分にメタル層を充填することが提案されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2009−259876号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献1に開示された貫通電極の製造方法は、貫通孔底部にあるメタル層を用いて、貫通孔底部近傍の限られた範囲であるノッチに対してメタル層を付着させようとするものであるから、スパッタ粒子の指向性を高めて貫通孔底部へスパッタリングガスを引き込んだり、分子量が大きいガスを用いる。そのため、基板表面へダメージを与えてしまう虞がある。また、貫通孔側壁に凹凸構造が存在し、凹凸構造に成膜されてない部分があっても、当該部分にメタル層等を成膜することはできない。

【0010】

本発明はこのような課題に鑑み、予め素子の形成された半導体基板に貫通電極を形成する際に、貫通孔又は貫通孔となる開口部の側壁全体に複数の凹凸構造が存在する場合でも、貫通孔又は貫通孔となる開口部の側壁全体に均一に成膜することができる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明の一実施形態に係る半導体装置の製造方法は、底壁及び複数の凹部を有する側壁により構成された開口部を素子が形成された半導体基板に形成し、前記開口部側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記底壁側に成膜部材を堆積させ、前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより前記成膜部材を前記側壁の各凹部の前記開口部側に堆積させることを特徴とする。本発明の一実施形態に係る半導体装置の製造方法によれば、開口部の側壁全体に複数の凹凸形状が形成される場合にも、開口部の側壁全体に均一に成膜することができる。

【0012】

前記複数の凹部は、エッチングによる前記半導体基板への溝の形成と、前記溝の内部への保護膜形成とを繰り返し行うことにより形成されてもよい。

【0013】

前記開口部に対向して前記成膜部材を含むターゲットを配置し、前記ターゲットに所定の電圧を印加しつつスパッタリングを行うことにより、前記底壁及び前記側壁の各凹部の前記底壁側に前記成膜部材を堆積させてもよい。

【0014】

前記成膜部材は絶縁部材であり、前記成膜部材を介して前記開口部内に導電部材を形成し、前記開口部が形成されている側と反対側の前記半導体基板の面から前記半導体基板を薄化して、前記半導体基板の表裏を導通する貫通電極を形成してもよい。

【0015】

また、 本発明の一実施形態に係る半導体装置の製造方法は、半導体基板の第1面と第2面を貫通し、側壁に複数の凹部を有する貫通孔を素子が形成された半導体基板に形成し、前記第1面側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記第2面側に第1成膜部材を堆積させ、前記半導体基板の第2面に直接又は離間して第2成膜部材を配置し、前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより、前記第1成膜部材及び前記第2成膜部材を前記側壁の各凹部の前記第1面側に堆積させることを特徴とする。本発明の一実施形態に係る半導体装置の製造方法によれば、開口部の側壁全体に複数の凹凸形状が形成される場合にも、開口部の側壁全体に均一に成膜することができる。

【0016】

前記複数の凹部は、エッチングによる前記半導体基板への溝の形成と、前記溝の内部への保護膜形成とを繰り返し行うことにより形成されてもよい。

【0017】

前記貫通孔に対向して前記第1成膜部材を含むターゲットを配置し、前記ターゲットに所定の電圧を印加しつつスパッタリングを行うことにより、前記底壁及び前記側壁の各凹部の前記第2面側に前記第1成膜部材を堆積させてもよい。

【0018】

前記成膜部材は絶縁部材であり、前記成膜部材を介して前記貫通孔の内部に導電部材を形成して貫通電極を形成してもよい。

【発明の効果】

【0019】

本発明によれば、予め素子の形成された半導体基板に貫通電極を形成する際に、貫通孔又は貫通孔となる開口部の側壁全体に複数の凹凸形状が形成される場合にも、貫通孔又は貫通孔となる開口部の側壁全体に均一に成膜することができる半導体装置の製造方法を提供することができる。

【図面の簡単な説明】

【0020】

【図1】本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程を示す図であり、(a)は半導体基板に形成された開口部を示す断面図であり、(b)は第1の成膜工程を示す図であり、(c)は第2の成膜工程を示す図であり、(d)は開口部に形成された薄膜を示す断面図である。

【図2】図1に示した貫通電極基板を製造する工程を一部拡大して示す図であり、(a)は、図1(c)に示すX部分の拡大図であり、(b)は、図1(d)に示すY部分の拡大図である。

【図3】本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程に用いる装置を説明するための図である。

【図4】半導体基板に形成された開口部の断面の一例を示すSEM写真である。

【図5】図4に示すA領域の第1の成膜工程を行った後のSEM写真である。

【図6】図4に示すA領域の第2の成膜工程を行った後のSEM写真である。

【図7】図4に示すB領域の第1の成膜工程を行った後のSEM写真である。

【図8】図4に示すB領域の第2の成膜工程を行った後のSEM写真である。

【図9】図4に示すC領域の第1の成膜工程を行った後のSEM写真である。

【図10】図4に示すC領域の第2の成膜工程を行った後のSEM写真である。

【図11】図4に示すD領域の第1の成膜工程を行った後のSEM写真である。

【図12】図4に示すD領域の第2の成膜工程を行った後のSEM写真である。

【図13】図4に示すE領域の第1の成膜工程を行った後のSEM写真である。

【図14】図4に示すE領域の第2の成膜工程を行った後のSEM写真である。

【図15】図4に示すシリコン基板の表面、図4に示すA〜D領域におけるスキャロップの上部、及び図4に示すE領域において、第1の成膜工程後と第2の成膜工程後とで、絶縁膜の膜厚の比較を示す図である。

【図16】本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程を示す図であり、(a)はシード層の形成工程を示す図であり、(b)は導通部の形成工程を示す図であり、(c)は貫通電極基板を示す断面図である。

【図17】本発明の第2の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程を示す図であり、(a)は半導体基板に形成された貫通孔を示す断面図であり、(b)は第1の成膜工程により形成された絶縁膜を示す断面図であり、(c)は第2の成膜工程を示す図であり、(d)は貫通孔に形成された薄膜を示す断面図であり、(e)は(d)に示した半導体基板から不要な部分を取り除いた後の断面図である。

【図18】半導体基板に開口部を形成する工程の一例を示す図であり、(a)は半導体基板にエッチングマスクを配置した断面図であり、(b)はトレンチの形成工程を示す図であり、(c)は保護膜の形成工程を示す図であり、(d)はトレンチの形成工程を示す図であり、(e)は完成した開口部を示す断面図である。

【図19】半導体基板に形成された開口部の側壁に形成された凹部の例を示す図であり、(a)は、開口部の側壁に形成された凹部の一例を示す断面図であり、(b)は、開口部の側壁に形成された凹部の一例を示す断面図である。

【発明を実施するための形態】

【0021】

(第1の実施形態)

以下、図面を参照して、本発明の第1の実施形態に係る半導体装置の製造方法について詳細に説明する。

【0022】

第1の実施形態に係る半導体装置の製造方法は、貫通電極基板を用いた半導体装置の製造方法である。以下では、、図1、図2、図3、及び図18を参照し、本実施形態に係る半導体装置の製造方法について説明する。なお、半導体装置とは、半導体特性を利用して機能し得る装置全般を指し、半導体集積回路、電子機器は半導体装置の範囲に含むものとする。

【0023】

<貫通電極基板の製造方法>

図1は、本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程を示す図であり、(a)は半導体基板に形成された開口部を示す断面図であり、(b)は第1の成膜工程を示す図であり、(c)は第2の成膜工程を示す図であり、(d)は開口部に形成された薄膜を示す断面図である。図2は、図1に示した貫通電極基板を製造する工程を一部拡大して示す図であり、(a)は、図1(c)に示すX部分の拡大図であり、(b)は、図1(d)に示すY部分の拡大図である。図3は、本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する装置を説明するための図である。図18は、半導体基板に開口部を形成する工程の一例を示す図であり、(a)は半導体基板にエッチングマスクを配置した断面図であり、(b)はトレンチの形成工程を示す図であり、(c)は保護膜の形成工程を示す図であり、(d)はトレンチの形成工程を示す図であり、(e)は完成した開口部を示す断面図である。

【0024】

(1)半導体基板の準備

本実施形態においては、半導体基板としてシリコン基板101を準備する。シリコン基板101の厚さに制限はないが、取り扱い性を考慮すると50μm〜700μmの範囲のものを用いるのが好ましい。シリコン基板101には予め素子(図示せず)が形成されている。なお、シリコン基板101に形成される素子(図示せず)は公知の方法により配置される。形成される素子は抵抗、コイル、キャパシタ等の受動素子、メモリ、IC等の能動素子、発光素子、受光素子、センサ素子、スイッチング素子などが挙げられる。素子は、シリコン基板101の片側又は両側或いはシリコン基板101の内部に配置されている。

【0025】

(2)開口部111の形成

図18を参照して、図1(a)に図示した開口部111をシリコン基板101に形成する工程を説明する。開口部111は、シリコン基板101の一方の面と他方の面とを貫通しない溝として形成されている。開口部111の開口径に制限はないが、加工性、微細化への対応を考慮すると10μm〜200μmであることが好ましい。開口部111は、その内部に導電材を配置することによりシリコン基板101の一方の面と他方の面を導通する貫通電極が形成される部分である。図18は、DRIEにより、具体的にはボッシュプロセスにより開口部111を形成する工程を示している。

【0026】

図18(a)に図示したように、エッチングマスク106をシリコン基板101に配置する。エッチングマスク106をパターニングした後、図18(b)に図示したように、エッチングマスク106から露出したシリコン基板101に対して、エッチングガスとして例えば、SF6(六フッ化硫黄)を用いてシリコン基板101をエッチングしてトレンチ(溝)111tを形成する。SF6は等方性エッチングガスであるから、シリコン基板101の厚さ方向(縦方向ともよぶ)にエッチングが進むとともに、シリコン基板101の面方向(横方向ともよぶ)にもエッチングが進む。その後、図18(c)に図示したように、C4F8(パーフルオロシクロブタン)を用いてエッチング面に保護膜(フルオロカーボン膜)107を形成する。次いで、図18(d)に図示したように、保護膜107の形成されたエッチング底面を、SF6(六フッ化硫黄)を用いてエッチングすることにより、保護膜107を除去してさらにトレンチ111tを形成する。このように、ボッシュプロセスでは、図18(b)又は(d)に示したエッチングによりトレンチ111tを形成する工程と、図18(c)に示すエッチング面に保護膜107を形成する工程とを交互に繰り返す。これにより、図18(e)に図示したような開口部111を形成することができる。なお、エッチング工程と保護膜形成工程は各々重複しないよう設定されてもよいし、一部が重複するように設定されていてもよい。

【0027】

図18(e)に図示したように、ボッシュプロセスでは、開口部111の側壁に複数の凹部が生じ、エッチングマスク106の境界である開口部111の開口側の径よりも横方向に広がったスキャロップと呼ばれる凹凸構造(以下、スキャロップ111sという)が連続して形成される。スキャロップ111sは開口部111の深さ方向に連続して形成され、開口部111の側壁に複数の凹部が形成される。スキャロップ111sは、エッチングと保護膜形成の強度関係や時間比などによりその形状が変化するが、通常、横方向の深さP−V値が0.1μm〜0.5μm程度であり、縦方向のスキャロップ幅が0.1μm〜2.0μm程度の大きさを有する。以下では、図18(e)に一例として図示したスキャロップ111sの形成された開口部111に貫通電極を形成する方法について説明するが、開口部111の側壁に形成される複数の凹部は、ボッシュプロセスにより形成されるスキャロップ111sに限らず、他の方法により開口部111の側壁に連続的または局所的に形成される凹部であってもよい。複数の凹部の例を図19を用いて説明する。図19は、開口部111の側壁に形成される複数の凹部の一例を示す断面図である。図19(a)は、DRIEにより側壁にえぐれのような凹部111uが形成されている例を示す。図19(b)は、サンドブラスト、ドリル加工等により生じた側壁表面の荒れにより凹部111vが形成されている例を示す。このように、複数の凹部は、図18に図示したスキャロップ111sのような形状に限らず、図19に図示した凹部111u、111vのような形状であってもよい。

【0028】

また、図18(b)〜(e)ではスキャロップ111sのスキャロップ幅が全て一定として図示しているが、観察する側壁の位置により、その幅が異なる場合がある。例えば、エッチング条件を同一として実行した場合には、開口部側のスキャロップ幅及びP−V値の方が、底壁側のそれらよりも大きくなる傾向にある。このようなスキャロップ111sにより構成される側壁の凹凸構造は、開口部111内部に絶縁層やメタル層を形成する際に成膜できない部分を作り出し、後述する工程により形成される貫通電極の絶縁不良、バリア不良、導通不良などの諸々の原因となることがある。開口部側のスキャロップのP−V値が底壁側に比べて大きい場合、P−V値の高い箇所に均一に成膜することは困難となる。このため、スキャロップ111sを隙間なく覆い、開口部111の側壁面全体に均一に成膜する方法が求められる。

【0029】

以下、図1〜図3を参照し、図18(e)に図示したスキャロップ111sの形成された開口部111の側壁に絶縁膜102を成膜する方法について説明する。絶縁膜102は、単層として形成してもよく、2層以上の積層構造として形成してもよい。以下では、絶縁膜102を成膜する場合について説明するが、成膜するものがバリア膜、シード膜であってもよい。なお、図18(e)に示した保護膜107は、開口部111を完成させた後に除去してもよい。また、図示していないが、開口部111を完成させた後、開口部111を形成した面とは反対側の面から研磨、エッチング等の方法でシリコン基板101を後退(薄化)させて孔を貫通させ、貫通孔を形成してもよい。本実施形態では、保護膜107を除去した後の開口部111に貫通電極を形成する方法について以下に述べる。

【0030】

(3)絶縁膜102の形成

図1(a)に図示したように、開口部111の側壁には、上述した図18に示す工程により、複数の凹部からなるスキャロップ111sが形成される。以下、スキャロップ111sの各凹部のうち、開口部111の開口側(図1に示すシリコン基板101の上面側)の部分をスキャロップ111sの上部111bといい、開口部111の底壁側(図1に示すシリコン基板101の下面側)の部分をスキャロップ111sの下部111aという。図1(a)に示した開口部111の側壁及び底壁を含む内壁並びにシリコン基板101の上面に、絶縁膜102を形成する。絶縁膜102は、例えば、二酸化シリコン(SiO2)、窒化シリコン(SiN)、炭化シリコン(SiC)等の絶縁層から構成されるものであってもよい。このような絶縁膜102は、スパッタ法や真空蒸着法等を用いて形成される。スパッタ法等を用いることにより、予めシリコン基板101に素子等が形成されている場合にも、熱プロセスを伴わないため、熱による素子への影響を与えないようにすることができる。

【0031】

(3−1)第1の成膜工程

図1(b)は、第1の成膜工程を示す図であり、図1(b)に図示したように、開口部111の側壁、開口部111の底壁、及びシリコン基板101の上面に絶縁膜102を形成する。本実施形態として、以下では、図3に図示するスパッタ装置200を用いてスパッタリングを行う工程を説明する。

【0032】

図3に図示したように、スパッタ装置200は、チャンバー201、ターゲット202、試料台203、電源204、ガス導入装置205、排気装置206、及び制御装置207を含む。スパッタ装置200のチャンバー201内には、試料台203の上に、開口部111が上を向いて位置するようにシリコン基板101が配置され、シリコン基板101の開口部111と対向する位置に成膜材料であるターゲット202が配置される。本実施形態において、ターゲット202は絶縁部材からなる。チャンバー201内を真空にしてガス導入装置205から、例えばAr(アルゴン)ガスを導入し、電源204を制御装置207により制御し、チャンバー201とターゲット202に高周波(RF)電圧をかけると、ターゲット202に負のバイアス電圧が生じ、Arイオンがターゲット202に衝突し、ターゲット202に衝突したArイオンは、ターゲット202の粒子をはじき飛ばし、はじき飛ばされた絶縁部材の粒子がシリコン基板101の上面及び開口部111の内壁に衝突、付着し、絶縁膜102が形成される。

【0033】

ここで、第1の成膜工程におけるスパッタ装置200のスパッタリング条件としては、以下のような条件で行ってもよい。例えば、ターゲット202とシリコン基板101との距離を100mmとし、圧力を0.3Pa、RFパワーを2000W、基板バイアス負電圧を0V、Ar流量を20〜25sccmとしてスパッタを行う。

【0034】

第1の成膜工程によると、図1(b)に図示したように、スキャロップ111sの下部111a(各凹部の底壁側の部分)と開口部111の底壁には絶縁膜102(102a、102c)が堆積されることがわかる。しかしながら、図1(b)に図示したスキャロップ111sの上部111b(各凹部の開口部111側の部分)には、ほとんど絶縁膜102が堆積されないことがわかる。これは、開口部111の上部に配置されたターゲット202から飛散するスパッタ粒子が直進性を有していることや、スキャロップ111sの形状が庇のように働くため、スキャロップ111sの上部111bにまで到達しないと考えられる。

【0035】

なお、第1の成膜工程として、スパッタ法を用いることを説明したが、真空蒸着法を用いてもよい。真空蒸着法による場合も、スキャロップ111sの下部111aと開口部111の底壁には絶縁膜102(102a、102c)が堆積されるが、スキャロップ111sの上部111bには、絶縁膜102が堆積されず、図1(b)に図示したような絶縁膜102が形成される。

【0036】

次にスキャロップ111sの上部111bに絶縁膜102を成膜するための第2の成膜工程について以下に述べる。

【0037】

(3−2)第2の成膜工程

図1(c)は、第2の成膜工程を示す図であり、図1(d)は第2の成膜工程後の開口部111に形成された絶縁膜102を示す図である。また、図2(a)は、図1(c)に示すX部分の拡大図であり、図2(b)は、図1(d)に示すY部分の拡大図である。

【0038】

まず、図1(b)に図示した第1の成膜工程後のシリコン基板101を、図3に図示したチャンバー201内の試料台203の上に配置する。チャンバー201内を真空にしてガス導入装置205から、例えばAr(アルゴン)ガスを導入し、電源204を制御装置207により制御し、チャンバー201と試料台203に高周波電圧をかけると、シリコン基板101やスキャロップ111sの下部111a及び開口部111の底壁に堆積された絶縁膜102(102a、102c)に負のバイアス電圧が生じる。これにより、Arイオンはスキャロップ111sの下部111a及び開口部111の底壁に堆積された絶縁膜102(102a、102c)に引き寄せられて衝突し、絶縁膜102a、102cの粒子をはじき飛ばし、はじき飛ばされた絶縁膜102a、102cの粒子が、開口部111の内壁に衝突、付着し、スキャロップ111sの上部111bにおいても、図2(d)に図示したように絶縁膜102bが形成される。

【0039】

ここで、第2の成膜工程では、Arイオンの指向性を高めすぎないことにより、絶縁膜102aをスパッタエッチングしてスキャロップ111sの上部111bに効果的に成膜を施すことができる。第2の成膜工程におけるスパッタ装置200のスパッタリング条件として、例えば、圧力を0.16Pa、RFパワーを300W、Ar流量を10sccm、基板バイアス負電圧を0Vとして、スパッタを行ってもよい。なお、以下に表1として、本発明の第一の実施形態に係る第1の成膜工程及び第2の成膜工程のスパッタリング条件の一例についてまとめた表を示す。

【表1】

【0040】

上述した条件によれば、例えばロングスロー法を用いたスパッタ装置において圧力を0.1Pa程度としてスパッタリングを行うことと比較して、圧力を高めることにより指向性を低くすることができる。従って、第2の成膜工程によれば、指向性の高いロングスロー法やコリーメート法を用いたスパッタ装置よりも指向性を低くすることができ、スキャロップ111sの内部にまで十分にスパッタ粒子を飛散させることができる。

【0041】

なお、第1の成膜工程と第2の成膜工程とで、いずれもスパッタ法を用いる場合には、スパッタ装置200は、同じチャンバー201を用いるようにしてもよいが、異なるチャンバー201を用いるようにしてもよい。異なるチャンバー201を用いる場合には、連結された2つのチャンバー201を用いて、第1の成膜工程においては、チャンバー201とターゲット202に高周波電圧をかけ、第2の成膜工程においては、チャンバー201と試料台203に高周波電圧をかけるように、それぞれスパッタリング条件を異なるものに設定し、第1の成膜工程と第2の成膜工程とで、2つのチャンバー201間を、シリコン基板101を搬送できるようにスパッタ装置200を構成してもよい。

【0042】

このように、第2の成膜工程により、図1(d)及び図2(b)に図示したように、スキャロップ111sの上部111bにおいても絶縁膜102bを形成することができるため、開口部111の側壁面全体を隙間無く均一に覆う絶縁膜102bを形成することができる。また、図2(a)と図2(b)とを比較すると、スキャロップ111sの凹部の横方向の深さを小さくすることができるため、開口部111の側壁面を平滑化することができることもわかる。開口部111の側壁を平滑化することにより、後述する導電材を充填する際の充填性を向上させる効果が期待できる。なお、開口部111は、後の工程においてシリコン基板101の下面を研磨、エッチング等することにより貫通孔として形成されるため、図1(d)に図示したように、開口部111の底面に形成された絶縁膜102cが第2の成膜工程により削られ、除去されてもよい。

【0043】

以下、さらに詳細に、本実施形態に係る半導体装置の製造方法の第1の成膜工程及び第2の成膜工程により開口部111の内壁に形成された絶縁膜102の状態について、図4〜図15に示したSEM写真を参照して説明する。

【0044】

図4は、半導体基板に形成された開口部111の断面の一例を示すSEM写真である。図5は、図4に示すA領域の第1の成膜工程を行った後のSEM写真である。図6は、図4に示すA領域の第2の成膜工程を行った後のSEM写真である。図7は、図4に示すB領域の第1の成膜工程を行った後のSEM写真である。図8は、図4に示すB領域の第2の成膜工程を行った後のSEM写真である。図9は、図4に示すC領域の第1の成膜工程を行った後のSEM写真である。図10は、図4に示すC領域の第2の成膜工程を行った後のSEM写真である。図11は、図4に示すD領域の第1の成膜工程を行った後のSEM写真である。図12は、図4に示すD領域の第2の成膜工程を行った後のSEM写真である。図13は、図4に示すE領域の第1の成膜工程を行った後のSEM写真である。図14は、図4に示すE領域の第2の成膜工程を行った後のSEM写真である。図15は、シリコン基板101の表面、図4に示すA〜D領域のスキャロップ111sの上部111b、及び開口部111の底面である図4に示すE領域において、第1の成膜工程後と第2の成膜工程後とで、それぞれ絶縁膜102の膜厚の比較を示す図である。

【0045】

図4に示す開口部111は、上述した図18に示す形成工程によりシリコン基板101に形成された開口部111の一例を示したものである。開口部111の側壁面には、図4に示すように、スキャロップ111sが形成される。図4に示す開口部111の大きさは、開口径が180μm、深さが180μm、スキャロップ幅が1.5μm、P−V値が0.26μm〜0.35μmである。図4に示す開口部111の内壁に対し、成膜材料にSiO2を用いて、第1の成膜工程及び第2の成膜工程を行ったところ、図5〜図14のSEM写真に示すように絶縁膜102が形成された。

【0046】

図5及び図6は、図4に示すシリコン基板101の表面から深さ5μm程度の開口部111のA領域において、第1の成膜工程後又は第2の成膜工程後の内壁の断面をそれぞれ示したSEM写真である。図5と図6とを比較すると、第1の成膜工程後は、図5に示したように、スキャロップ111sの下部111aに集中して絶縁膜102aが形成されることがわかる。しかし、第2の成膜工程により、図6に示したように、スキャロップ111sの上部111bにおいても絶縁膜102bが形成され、絶縁膜102の膜厚が均一になることがわかる。

【0047】

また、図5に示されるように、第1の成膜工程後は、シリコン基板101の表面には絶縁膜102が厚く堆積し、開口部111の開口の縁部に、開口の内側に向かって庇のように突出した形状を有する絶縁膜102dが形成されることがわかる。このような形状を有する絶縁膜102dは、さらに他の膜等を開口部111内部に形成する場合に、均一に膜等を形成することの妨げとなり、不具合を生じさせる原因となることがある。しかし、本実施形態によれば、第2の成膜工程により、スパッタリングによって開口部111の内壁に付着した絶縁膜102の粒子を、下から上方向に飛散させるため、開口の縁部から突出した絶縁膜102dの突出部分を削り取ることができる。これにより、図6に示した絶縁膜102eのように、絶縁膜102eの角部が平坦化されたような形状を有するように形成することもできる。従って、本実施形態によれば、第1の成膜工程により、開口部111の開口付近に突出して形成された絶縁膜102dの突出部分を、第2の成膜工程により除去することもできるため、開口部111の内壁にさらに他の膜等を形成する場合にも、均一に形成することができる。

【0048】

図7及び図8は、図4に示すシリコン基板101の表面から深さ45μm程度の開口部111のB領域において、第1の成膜工程後又は第2の成膜工程後の内壁の断面をそれぞれ示したSEM写真である。また、図9及び図10は、図4に示すシリコン基板101の表面から深さ90μm程度の開口部111のC領域において、第1の成膜工程後又は第2の成膜工程後の内壁の断面をそれぞれ示したSEM写真である。図11及び図12は、図4に示すシリコン基板101の表面から深さ175μm程度の開口部111のD領域において、第1の成膜工程後又は第2の成膜工程後の内壁の断面をそれぞれ示したSEM写真である。図7と図8、図9と図10、図11と図12をそれぞれ比較すると、第1の成膜工程後は、スキャロップ111sの下部111aに集中して絶縁膜102aが形成されるが、第2の成膜工程により、スキャロップ111sの上部111bにも絶縁膜102bが形成され、開口部111の側壁面全体に成膜されることがわかる。従って、図5〜図12に示したように、A領域からD領域にわたって開口部111の側壁面全体にスキャロップ111のような凹凸構造を有する場合にも、絶縁膜102を均一に形成することができることがわかる。

【0049】

図13及び図14は、図4に示すシリコン基板101の表面から深さ185μm程度の開口部111の底部であるE領域において、第1の成膜工程後及び第2の成膜工程後の成膜状態をそれぞれ示した底部の断面のSEM写真である。図13と図14とを比較すると、第1の成膜工程後、開口部111の底面に堆積していた絶縁膜102cは、第2の成膜工程のスパッタリングにより、ほぼ除去されていることがわかる。

【0050】

図15は、開口部111の開口付近のシリコン基板101の表面、図4に示すA〜D領域におけるスキャロップ111sの上部111b、及び開口部111の底部である図4に示すE領域において、第1の成膜工程後と第2の成膜工程後とで、それぞれ絶縁膜102の膜厚の比較を示す図である。図15に示すように、シリコン基板101の表面及び開口部111の底部であるE領域は、第2の成膜工程後に、第1の成膜工程により形成された絶縁膜102がスパッタリングにより削られ、シリコン基板101の表面においては絶縁膜102の膜厚が減少し、底部のE領域においてはほぼ除去されることがわかる。また、開口部111の側壁に形成されたスキャロップ111sの上部111bは、C領域及びD領域において、第1の成膜工程後に絶縁膜102が形成されないことがわかる。しかし、第2の成膜工程後は、C領域及びD領域のスキャロップ111sの上部111bにも絶縁膜102が形成され、A〜D領域の内壁全体において、スキャロップ111sの上部111bの絶縁膜102の膜厚がそれぞれ増加していることがわかる。

【0051】

以上のように、本発明の第1の実施形態によれば、開口部111の側壁全体にスキャロップ111sのような複数の凹凸が形成されている場合にも、第1の成膜工程により、開口部111の底壁及びスキャロップ111sの下部111aに絶縁膜102を堆積した後、第2の成膜工程により、堆積された絶縁膜102を用いてシリコン基板101に所定の電圧を印加しつつスパッタリングを行うことによって、開口部111の側壁全体を均一に成膜することができる。従って、本発明の第1の実施形態によれば、側壁全体に隙間無く絶縁膜を形成することができるので、絶縁不良が防止され、貫通電極基板を製造する際の歩留まりを向上させ、その信頼性を向上させることができる。

【0052】

次に、図16を参照し、シード層113及び導通部114を形成する工程を説明する。図16は、本発明の第1の実施形態に係る半導体装置の製造方法において貫通電極基板110を製造する工程を示す図であり、(a)はシード層113の形成工程を示す図であり、(b)は導通部114の形成工程を示す図であり、(c)は貫通電極基板110を示す断面図である。

【0053】

(4)シード層113の形成

図16(a)に示すように、シリコン基板101の絶縁膜102が形成された面及び開口部111の絶縁膜102が形成された内部に、シード層113を形成する。シード層113は、図示していないが、バリア膜とシード膜の積層構造により構成される。シード層113は、シリコン基板101側にバリア膜として例えばTiやTiN、その上にシード膜として例えばCuが積層された構造としてもよい。

【0054】

絶縁膜102の形成されたシリコン基板101の上に、バリア膜として、例えば窒化チタン(TiN)を成膜する。窒化チタンは絶縁膜102の成膜方法と同様に、予め素子が形成された基板に成膜することから、熱プロセスを伴わないスパッタ法等により成膜することが好ましい。上述した第1の成膜工程及び第2の成膜工程と同様の方法を用いることがより好ましい。これにより、開口部111の側壁に形成された絶縁膜102の表面を隙間無く覆うバリア膜を形成することができる。従って、後述する工程において充填される金属がシリコン基板101側に拡散することを防止することができる。

【0055】

次に、バリア膜の上にシード膜を成膜する。シード膜の成膜方法は、蒸着法、スパッタ法などから適宜選択できる。しかし、基板に予め素子が形成されていることから、熱プロセスを伴わないスパッタ法等によることが好ましい。上述した第1の成膜工程及び第2の成膜工程と同様の方法を用いることがより好ましい。これにより、バリア膜の表面を隙間無く覆うシード膜を形成することができる。なお、シード膜に用いる金属材料は、後述する図16(b)に示す導通部114の金属材料によって適宜選択することができる。シード膜は、電解メッキによって導通部114を形成するためのシード部及び給電部となる。なお、他の方法で導通部114を形成する場合には、シード層113は導通部114との密着性を高めるためのメタル層として機能する。

【0056】

このような工程によりバリア膜及びシード膜を形成することにより、図16(a)に示すシード層113が形成される。シード層113は、上述した第1の成膜工程及び第2の成膜工程と同様の方法を用いて形成することにより、開口部111の側壁に形成された絶縁膜102の表面を隙間無く均一に覆うように形成することができる。

【0057】

(5)導通部114の形成

次に、図16(b)に示すように、電解メッキによってシリコン基板101のシード層113を給電層として開口部111内部に導電材を充填して、導通部114を形成する。導電材の充填には、スパッタ法、電解メッキ法、溶融金属吸引法(圧力差を利用して溶融した金属を開口部へ引入れる方法)、印刷法等も使用することができる。開口部111が微細な場合には、電解メッキ法を用いることが好ましい。開口部111に充填する金属材料としては、銅(Cu)の他、金(Au)、ロジウム(Rh)、銀(Ag)、白金(Pt)、スズ(Sn)、アルミニウム(Al)、ニッケル(Ni)、クロム(Cr)等の金属及びこれらの合金などから選択され組み合わせた材料を用いてもよい。電解メッキ法により導電材を充填する場合、シード層113が均一に形成されているので充填される金属にボイド等の不良が発生することを防止できる。

【0058】

(6)不要な部分の除去

次に、シード層113及び導通部114の不要部をエッチングあるいはCMPにより除去する。また、開口部111が形成されている側と反対側のシリコン基板101面をバックグラインドによって導通部114の表面が露出するまで研磨することにより、導通部114を形成する。研磨により、シリコン基板101の厚さを薄くしてもよい。以上のプロセスによって、第1の実施形態に係る貫通電極基板110を得ることができる。

【0059】

このような製造工程により製造された貫通電極基板110を用いて、例えば、基板上に形成された素子の接続端子部と、貫通電極基板110の導通部114とを接続させることにより、半導体装置を形成することが可能となる。従って、本実施形態に係る半導体措置の製造方法によれば、貫通電極の絶縁不良、バリア不良、導通不良等を発生させないように貫通電極基板110を形成することができるため、信頼性を向上させた半導体装置を提供することが可能となる。

【0060】

以上、本発明の第1の実施形態によれば、上述した第1の成膜工程及び第2の成膜工程によって、開口部111の側壁全体にスキャロップ111sが形成されている場合にも、スキャロップ111sを隙間なく均一に覆う絶縁膜102及び絶縁膜102を隙間無く均一に覆うシード層113を形成することができるため、開口部111内部に貫通電極を形成する際に、ボイド等を生じさせずに貫通電極を形成することができる。これにより、本実施形態に係る半導体装置の製造方法によれば、貫通電極基板を製造する際の歩留まりを向上させ、その信頼性を向上させることができる。

【0061】

(第2の実施形態)

以下、図面を参照して、本発明の第2の実施形態に係る半導体装置の製造方法を詳細に説明する。第2の実施形態に係る半導体装置の製造方法は、第1の実施形態に係る半導体装置の製造方法と同様に、貫通電極基板を用いた半導体装置を製造するものである。なお、第1の実施形態に係る製造工程と同様の工程については、詳細な説明について省略する。

【0062】

<貫通電極基板の製造方法>

第2の実施形態に係る半導体装置の製造方法について、図17を参照して説明する。図17は、本発明の第2の実施形態に係る半導体装置の製造方法において貫通電極基板を製造する工程を示す図であり、(a)はシリコン基板101に形成された貫通孔112を示す断面図であり、(b)は第1の成膜工程により形成された絶縁膜102を示す断面図であり、(c)は第2の成膜工程を示す図であり、(d)は貫通孔112に形成された絶縁膜102を示す断面図であり、(e)は(d)に示したシリコン基板101から不要な部分を取り除いた後の断面図である。

【0063】

(1)基板の準備

本実施形態においても、上述した第1の実施形態と同様に、基板としてシリコン基板101を準備する。シリコン基板101には予め素子(図示せず)が形成されている。形成される素子は抵抗、コイル、キャパシタ等の受動素子、メモリ、IC等の能動素子、発光素子、受光素子、センサ素子、スイッチング素子などが挙げられる。素子は、シリコン基板101の片側又は両側或いはシリコン基板101の内部に配置されている。

【0064】

(2)貫通孔112の形成

図17(a)に示す貫通孔112は、上述した第1の実施形態に係る開口部111の形成工程と同様に、DRIEにより、具体的にはボッシュプロセスにより形成されてもよい。シリコン基板111は第1の面(以下、上面ともよぶ)と第2の面(以下、下面ともよぶ)を連通する少なくとも1つの貫通孔を有している。図17(a)に図示していないが、シリコン基板101の下面にシリコン基板101を支持する基板を貼り付けてエッチングしてもよい。本実施形態においても、エッチングマスク(図示せず)をシリコン基板101の上面に配置し、ボッシュプロセスによりシリコン基板101を貫通する貫通孔112を形成する。これにより、図17(a)に示すように、貫通孔112の側壁面全体に、図1(a)に示す開口部111の側壁面と同様の複数の凹部からなるスキャロップ111sが形成される。

【0065】

(3)絶縁膜102の形成

(3−1)第1の成膜工程

図17(b)は、第1の成膜工程により形成された絶縁膜102を示す断面図であり、図17(a)に図示した貫通孔112の側壁及びシリコン基板101の上面に、上述した第1の実施形態に係る第1の成膜工程と同様に、スパッタ法又は真空蒸着法等を用いて絶縁膜102を形成する。

【0066】

スパッタ法を用いる場合には、上述した第1の実施形態に係る第1の成膜工程と同様に、貫通孔112が形成されたシリコン基板101を、図3に示すスパッタ装置200の試料台203上に第1の面が上側となるように配置し、チャンバー201内を真空にしてガス導入装置205から、例えばAr(アルゴン)ガスを導入し、電源204を制御装置207により制御し、チャンバー201とターゲット202に高周波(RF)電圧をかけると、ターゲット202に負のバイアス電圧が生じ、Arイオンがターゲット202に衝突し、ターゲット202に衝突したArイオンは、ターゲット202の粒子をはじき飛ばし、はじき飛ばされた成膜材料(絶縁部材)の粒子がシリコン基板101の上面及び貫通孔112の内壁に衝突、付着し、絶縁膜102が形成される。図17(b)に図示したように、第1の成膜工程によると、貫通孔112の側壁面において、スキャロップ111sの下部111a(各凹部の第2の面側)には絶縁膜102aが形成されるが、スキャロップ111sの上部111b(各凹部の第1の面側)には絶縁膜102が形成されない部分が生じる。

【0067】

(3−2)第2の成膜工程

図17(c)は、第2の成膜工程を示す図であり、図17(b)に示す第1の成膜工程後のシリコン基板101の下面に、絶縁膜102の成膜材料であるターゲット基板103を配置する。ターゲット基板103は、第1の成膜工程に用いたターゲット202と同様の成膜材料を用いることが望ましい。ここでは、ターゲット基板103は、絶縁膜102の成膜材料を含むものとする。なお、図17(c)に図示するように、ターゲット基板103の下面には、別途、ターゲット基板103を支持する基板104を配置してもよい。ターゲット基板103は、シリコン基板101の下面に直接接するように配置されていてもよいが、所定の間隙をもって配置されていてもよい。シリコン基板101の下面とターゲット基板103を離間して配置する場合には、シリコン基板101の下面に素子等が配置される際素子等の破損する可能性が排除できる。また、シリコン基板101の下面への取り付け、第2の成膜後の取り外しが容易となる。

【0068】

図17(c)に図示したターゲット基板103が下面に配置されたシリコン基板101を、図3に図示したスパッタ装置200の試料台203上に第1の面が上側となるように配置し、上述した第1の実施形態に係る第2の成膜工程と同様に、チャンバー201内を真空にしてガス導入装置205から、例えばAr(アルゴン)ガスを導入し、電源204を制御装置207により制御し、チャンバー201と試料台203に高周波電圧をかけると、シリコン基板101及びターゲット基板103に負のバイアス電圧が生じ、Arイオンがスキャロップ111sの下部111b及びターゲット基板103に引き寄せられ、Arイオンがスキャロップ111sの下部111aに形成された絶縁膜102a及びターゲット基板103に衝突して絶縁膜102の粒子をはじき飛ばし、はじき飛ばされた絶縁膜102の粒子が貫通孔112の側壁に衝突、付着し、スキャロップ111sの上部111bにも、図17(d)に図示したように絶縁膜102bが形成される。

【0069】

このように、本発明の第2の実施形態によれば、貫通孔112の側壁面全体にスキャロップ111sのような複数の凹凸が形成されている場合にも、第1の成膜工程により、貫通孔112のスキャロップ111sの下部111aに絶縁膜102を堆積した後、第2の成膜工程により、堆積された絶縁膜102を用いてシリコン基板101に所定の電圧を印加しつつスパッタリングを行うことによって、貫通孔112の側壁全体を均一に成膜することができる。従って、本発明の第2の実施形態によれば、後述する工程において貫通孔112に導電材を埋め込み貫通電極を形成した場合にも、ボイド等を生じさせずに形成することができるため、貫通電極基板を製造する際の歩留まりを向上させ、その信頼性を向上させることができる。

【0070】

(4)シード層113の形成

次に、図16を参照して、シード層113を形成する工程を説明する。上述した第1の実施形態と同様に、シリコン基板101の絶縁膜102が形成された面及び貫通孔112の内部に形成された絶縁膜102上に、シード層113を形成する。第1の実施形態と同様に、シード層113はバリア膜及びシード膜を含み、上述した第1の成膜工程及び第2の成膜工程を用いてバリア膜及びシード膜を成膜してもよい。これにより、貫通孔112の内部に形成された絶縁膜102の表面を隙間無く均一に覆うシード層113を形成することができる。従って、このような工程により形成されたシード層113によれば、第1の実施形態と同様に、後述する工程において充填される金属がシリコン基板101側に拡散することを防止し、且つボイド等の不良が発生することを防止することができる。

【0071】

(5)導通部114の形成

次に、上述した第1の実施形態と同様に、図16(b)に示すように、電解メッキによってシリコン基板101のシード層113を給電層として貫通孔112内部に導電材を充填して、導通部114を形成する。上述したように、予め素子が形成された基板に導通部114を形成することから、熱プロセスを伴わないスパッタ法を用いることが好ましい。導通部114は、絶縁膜102の表面を隙間無く覆うシード層113上に形成することができるため、ボイド等を生じさせることなく形成することができる。なお、貫通孔112に充填する金属材料としては、銅(Cu)の他、金(Au)、ロジウム(Rh)、銀(Ag)、白金(Pt)、スズ(Sn)、アルミニウム(Al)、ニッケル(Ni)、クロム(Cr)等の金属及びこれらの合金などから選択され組み合わせた材料を用いてもよい。

【0072】

(6)不要な部分の除去

次に、上述した第1の実施形態と同様に、シード層113及び導通部114の不要部をエッチングあるいはCMPにより除去する。研磨により、シリコン基板101の厚さを薄くしてもよい。以上のプロセスにより、図16(e)に示す貫通電極基板110と同様の、第2の実施形態に係る貫通電極基板110を得ることができる。

【0073】

このような製造工程により製造された貫通電極基板110を用いて、例えば、基板上に形成された素子の接続端子部と、貫通電極基板110の導通部114とを接続させることにより、半導体装置を形成することが可能となる。従って、本実施形態に係る半導体措置の製造方法によれば、貫通電極の絶縁不良、バリア不良、導通不良等を発生させないように貫通電極基板110を形成することができるため、信頼性を向上させた半導体装置を提供することができる。

【0074】

以上、本発明の第2の実施形態によれば、上述した第1の成膜工程及び第2の成膜工程によって、貫通孔112の側壁面全体にスキャロップ111sが形成されている場合にも、スキャロップ111sの形成された貫通孔112を隙間なく均一に覆う絶縁膜102及び絶縁膜102を隙間無く均一に覆うシード層113を形成することができるため、ボイド等を生じさせずに貫通電極を形成することができる。従って、本実施形態によれば、貫通電極基板を製造する際の歩留まりを向上させ、その信頼性を向上させることができる。

【符号の説明】

【0075】

101…シリコン基板、102…絶縁膜、110…貫通電極基板、111…開口部、111s…スキャロップ、112…貫通孔、200…スパッタ装置

【特許請求の範囲】

【請求項1】

底壁及び複数の凹部を有する側壁により構成された開口部を素子が形成された半導体基板に形成し、

前記開口部側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記底壁側に成膜部材を堆積させ、

前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより前記成膜部材を前記側壁の各凹部の前記開口部側に堆積させることを特徴とする半導体装置の製造方法。

【請求項2】

エッチングによる前記半導体基板への溝の形成と、前記溝の内部への保護膜形成とを繰り返し行うことにより、前記複数の凹部を形成することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記開口部に対向して前記成膜部材を含むターゲットを配置し、前記ターゲットに所定の電圧を印加しつつスパッタリングを行うことにより、前記底壁及び前記側壁の各凹部の前記底壁側に前記成膜部材を堆積させることを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記成膜部材は絶縁部材であり、前記成膜部材を介して前記開口部内に導電部材を形成し、前記開口部が形成されている側と反対側の前記半導体基板の面から前記半導体基板を薄化して、前記半導体基板の表裏を導通する貫通電極を形成することを特徴とする請求項1乃至3のいずれかに記載の半導体装置の製造方法。

【請求項5】

半導体基板の第1面と第2面を貫通し、側壁に複数の凹部を有する貫通孔を素子が形成された半導体基板に形成し、

前記第1面側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記第2面側に第1成膜部材を堆積させ、

前記半導体基板の第2面に直接又は離間して第2成膜部材を配置し、

前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより、前記第1成膜部材及び前記第2成膜部材を前記側壁の各凹部の前記第1面側に堆積させることを特徴とする半導体装置の製造方法。

【請求項6】

エッチングによる前記半導体基板への溝の形成と、前記溝の内部への保護膜形成とを繰り返し行うことにより、前記複数の凹部を形成することを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記貫通孔に対向して前記第1成膜部材を含むターゲットを配置し、前記ターゲットに所定の電圧を印加しつつスパッタリングを行うことにより、前記底壁及び前記側壁の各凹部の前記第2面側に前記第1成膜部材を堆積することを特徴とする請求項5または6に記載の半導体装置の製造方法。

【請求項8】

前記成膜部材は絶縁部材であり、前記成膜部材を介して前記貫通孔の内部に導電部材を形成して貫通電極を形成することを特徴とする請求項5乃至7のいずれかに記載の半導体装置の製造方法。

【請求項1】

底壁及び複数の凹部を有する側壁により構成された開口部を素子が形成された半導体基板に形成し、

前記開口部側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記底壁側に成膜部材を堆積させ、

前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより前記成膜部材を前記側壁の各凹部の前記開口部側に堆積させることを特徴とする半導体装置の製造方法。

【請求項2】

エッチングによる前記半導体基板への溝の形成と、前記溝の内部への保護膜形成とを繰り返し行うことにより、前記複数の凹部を形成することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記開口部に対向して前記成膜部材を含むターゲットを配置し、前記ターゲットに所定の電圧を印加しつつスパッタリングを行うことにより、前記底壁及び前記側壁の各凹部の前記底壁側に前記成膜部材を堆積させることを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記成膜部材は絶縁部材であり、前記成膜部材を介して前記開口部内に導電部材を形成し、前記開口部が形成されている側と反対側の前記半導体基板の面から前記半導体基板を薄化して、前記半導体基板の表裏を導通する貫通電極を形成することを特徴とする請求項1乃至3のいずれかに記載の半導体装置の製造方法。

【請求項5】

半導体基板の第1面と第2面を貫通し、側壁に複数の凹部を有する貫通孔を素子が形成された半導体基板に形成し、

前記第1面側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記第2面側に第1成膜部材を堆積させ、

前記半導体基板の第2面に直接又は離間して第2成膜部材を配置し、

前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより、前記第1成膜部材及び前記第2成膜部材を前記側壁の各凹部の前記第1面側に堆積させることを特徴とする半導体装置の製造方法。

【請求項6】

エッチングによる前記半導体基板への溝の形成と、前記溝の内部への保護膜形成とを繰り返し行うことにより、前記複数の凹部を形成することを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記貫通孔に対向して前記第1成膜部材を含むターゲットを配置し、前記ターゲットに所定の電圧を印加しつつスパッタリングを行うことにより、前記底壁及び前記側壁の各凹部の前記第2面側に前記第1成膜部材を堆積することを特徴とする請求項5または6に記載の半導体装置の製造方法。

【請求項8】

前記成膜部材は絶縁部材であり、前記成膜部材を介して前記貫通孔の内部に導電部材を形成して貫通電極を形成することを特徴とする請求項5乃至7のいずれかに記載の半導体装置の製造方法。

【図16】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図17】

【図18】

【図19】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図17】

【図18】

【図19】

【公開番号】特開2012−212797(P2012−212797A)

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願番号】特願2011−77874(P2011−77874)

【出願日】平成23年3月31日(2011.3.31)

【出願人】(000002897)大日本印刷株式会社 (14,506)

【Fターム(参考)】

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願日】平成23年3月31日(2011.3.31)

【出願人】(000002897)大日本印刷株式会社 (14,506)

【Fターム(参考)】

[ Back to top ]