半導体装置の製造方法

【課題】貫通電極の形成過程で、余分な酸化膜を確実に除去する。

【解決手段】貫通電極を形成するビアホール25の内面に酸化膜26を形成した後、Cu膜28を埋め込む。第1層間絶縁膜22の上に形成された余分なCu膜28をCMP法による研磨で除去するときに、酸化膜26も研磨されて膜厚が薄くなる。膜厚が薄くなった酸化膜26Bをハードマスクとして第1層間絶縁膜14に配線溝を形成する。このとき、酸化膜26Bの膜厚が薄くなる。配線溝に導電材を埋め込んだ後、余分な導電材を研磨によって除去する。このとき、残りの酸化膜26Bが全て研磨により除去される。

【解決手段】貫通電極を形成するビアホール25の内面に酸化膜26を形成した後、Cu膜28を埋め込む。第1層間絶縁膜22の上に形成された余分なCu膜28をCMP法による研磨で除去するときに、酸化膜26も研磨されて膜厚が薄くなる。膜厚が薄くなった酸化膜26Bをハードマスクとして第1層間絶縁膜14に配線溝を形成する。このとき、酸化膜26Bの膜厚が薄くなる。配線溝に導電材を埋め込んだ後、余分な導電材を研磨によって除去する。このとき、残りの酸化膜26Bが全て研磨により除去される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

電子部品には、半導体素子が形成された半導体装置を有するものがある。半導体装置は、例えば、シリコン基板上に半導体素子やその他の回路が形成される。複数の半導体装置を1つの電子部品の回路基板に実装すると電子部品が高性能化される。さらに、複数の半導体装置を積層して回路基板に実装すると、電子部品が小型化される。半導体装置を積層するときは、1つ目の半導体装置の上に2つ目の半導体装置を載置した後、それぞれの半導体装置の電極同士をワイヤボンディングによって電気的に接続する。

【0003】

このために、複数の半導体装置を積層して実装するためには、下側の半導体装置の電極は上側の半導体装置から露出する位置に形成される。従って、ワイヤボンディングを用いて半導体装置を積層するためには、上側の半導体装置の大きさを、下側の半導体装置の大きさより小さくする必要があった。その結果、下側の半導体装置の小型化が難しかった。

【0004】

そこで、近年では、半導体装置にシリコン基板を貫通する貫通電極(TSV,through-silicon via)が形成される。貫通電極は、シリコン基板を貫通するスルーホールの内部に銅などの導電材を埋め込んだ構成を有する。

【0005】

ここで、TSVの従来の形成方法について説明する。最初に、シリコン基板上に1層目の配線を形成する。続いて、1層目の配線の上に層間絶縁膜を形成する。この後、ドライエッチングによって、層間絶縁膜を貫通し、シリコン基板を所定の深さに達するビアホールを形成する。ビアホール内に絶縁膜を形成した後、密着層とシード層を形成する。この後、電解めっきによってビアホール内に金属を充填する。層間絶縁膜の上に残る金属や密着層を除去して、層間絶縁膜の表面と、ビアホール内に埋め込んだ金属の表面を露出させる。ビアホールの内壁に酸化膜を形成することで、ビアホールの絶縁性が確保され、ビアホール内の埋め込まれた金属の拡散が防止される。

【0006】

続いて、層間絶縁膜上に配線を形成する。この後、シリコン基板の裏面側をドライエッチング又はウエットエッチングして、貫通電極の裏面側を露出させる。露出した貫通電極の端面には、バンプを接合する。貫通電極は、バンプを介して、他の半導体装置の電極などに電気的に接続される。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】国際公開第WO2006/080337号

【発明の概要】

【発明が解決しようとする課題】

【0008】

ここで、貫通電極を電源供給用に用いる場合など、貫通電極に大電流を流すためには、酸化膜の膜厚を厚くする必要がある。しかしながら、酸化膜の膜厚が大きいと、シリコン基板表面の余分な酸化膜を確実に除去することが難しい。これは、酸化膜の研磨レートが遅く、研磨に時間を要するためである。さらに、研磨の均一性が悪いため、層間絶縁膜上の酸化膜を均一に除去することが困難である。このために、貫通電極を効率良く、形成することが望まれていた。

【課題を解決するための手段】

【0009】

本実施形態の一観点によれば、基板の一方の面上に半導体素子を形成する工程と、前記半導体素子の上方に第1の絶縁膜を形成する工程と、前記第1の絶縁膜を貫通し、前記基板にホールを形成する工程と、前記第1の絶縁膜上及び前記ホールの内壁に第2の絶縁膜を形成する工程と、前記ホール内に第1の導電材を埋める工程と、前記第1の絶縁膜上の前記第1の導電材と、前記第2の絶縁膜の一部を研磨によって除去する工程と、前記第2の絶縁膜と前記第1の絶縁膜をエッチングしてパターンを形成する工程と、前記パターンに第2の導電材を埋め込む工程と、前記第1の絶縁膜の上方の前記第2の導電材と、残りの前記第2の絶縁膜を研磨により除去し、前記第1の絶縁膜を露出させる工程と、前記基板の厚さを他方の面から減少させ、前記ホール内に埋めた前記第1の導電材を露出させる工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0010】

酸化膜を研磨する時間が短縮され、貫通電極を効率よく形成できる。

【図面の簡単な説明】

【0011】

【図1A】図1Aは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図1B】図1Bは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図1C】図1Cは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図1D】図1Dは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図1E】図1Eは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図1F】図1Fは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その6)である

【図1G】図1Gは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その7)である。

【図1H】図1Hは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その8)である。

【図1I】図1Iは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その9)である。

【図1J】図1Jは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その10)である。

【図1K】図1Kは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その11)である。

【図1L】図1Lは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その12)である。

【図1M】図1Mは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その13)である。

【図1N】図1Nは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その14)である。

【図1O】図1Oは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その15)である。

【図2】図2は、本発明の第1の実施の形態の変形例に係る半導体装置の製造工程を示す断面図である。

【図3】図3は、本発明の第1の実施の形態の他の変形例に係る半導体装置の製造工程を示す断面図である。

【図4A】図4Aは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図4B】図4Bは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図4C】図4Cは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図4D】図4Dは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図4E】図4Eは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図4F】図4Fは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その6)である。

【図4G】図4Gは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その7)である。

【図4H】図4Hは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その8)である。

【発明を実施するための最良の形態】

【0012】

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。

前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない。

【0013】

(第1の実施の形態)

実施の形態の半導体装置の製造方法について図面を参照して詳細に説明する。

最初に、図1Aに示す断面構造を得るまでの工程について説明する。

まず、n型又はp型のシリコン(半導体)基板1の一方の面である表面を熱酸化することにより素子分離絶縁膜2を例えば30nmの深さに形成し、この素子分離絶縁膜2でトランジスタの活性領域を画定する。このような素子分離構造は、LOCOS(Local Oxidation of Silicon)と呼ばれる。素子分離領域には、STI(Shallow Trench Isolation)を用いても良い。

【0014】

次いで、シリコン基板1の活性領域にイオン注入法により、ドーパント不純物を導入してウェルを形成する。ドーパント不純物としてp型不純物、例えばボロンを導入すると、シリコン基板1にpウェル3が形成される。pウェル3を形成した後、その活性領域の表面を熱酸化してゲート絶縁膜5を形成する。ゲート絶縁膜5は、例えば熱酸化膜を約6nm〜7nmの厚さに形成する。なお、以下においては、pウェル3を形成した場合について説明するが、シリコン基板1にnウェルを形成した場合も同様の工程が実施される。

【0015】

続いて、シリコン基板1の上側全面に、ポリシリコン膜を例えばCVD法を用いて200nmの膜厚に形成する。その後に、フォトリソグラフィ技術及びエッチング技術を用いてポリシリコン膜をパターニングして、シリコン基板1上にゲート電極6を形成する。ゲート電極6は、pウェル3上に互いに平行に複数形成され、その各々はワード線の一部を構成する。

【0016】

さらに、ゲート電極6をマスクにしてpウェル3にイオンを注入し、ゲート電極6の横のpウェル3にn型不純物としてリンを導入する。これにより、第1、第2ソース/ドレインエクステンション8が形成される。第1、第2ソース/ドレインエクステンション8は、エクステンションソース/ドレイン領域の浅い領域を構成する。その後に、シリコン基板1の上側全面に、絶縁膜としてシリコン酸化膜を例えばCVD法を用いて300nm

の厚さに形成する。その後、絶縁膜を異方性エッチングする。絶縁膜がエッチバックされ、ゲート電極6の側部に絶縁性サイドウォール10が形成される。

【0017】

続いて、絶縁性サイドウォール10とゲート電極6をマスクとして用い、シリコン基板1に砒素等のn型のドーパント不純物を再びイオン注入する。これにより、ゲート電極6の側方のpウェル3に、ソース/ドレイン拡散層11が形成される。ソース/ドレイン拡散層11は、エクステンションソース/ドレインの深い領域を構成する。

【0018】

さらに、シリコン基板1の全面に、例えば、スパッタリング法によりコバルト膜等の高融点金属膜を形成する。この後、高融点金属膜を加熱してシリコンと反応させる。これにより、ソース/ドレイン拡散層11におけるシリコン基板1上にコバルトシリサイド層等の高融点金属シリサイド層が形成され、各ソース/ドレイン拡散層11が低抵抗化する。この後、素子分離絶縁膜2の上などに未反応のまま残っている高融点金属膜を例えばウエットエッチングにより除去する。これにより、ソース/ドレイン拡散層11上に、例えばコバルトシリサイドで形成されるソース/ドレイン電極12Aが形成される。また、ゲート電極6の上部に、例えばコバルトシリサイドからなるシリサイド層12Bが形成される。

【0019】

ここまでの工程により、シリコン基板1の活性領域には、ゲート絶縁膜5、ゲート電極6、及びソース/ドレイン電極12A等から構成される半導体素子であるトランジスタT1,T2が形成される。

【0020】

さらに、シリコン基板1の上側の全面に、酸化防止絶縁膜13として酸窒化シリコン(SiON)膜をプラズマCVD法により形成する。

さらに、酸化防止絶縁膜13の上に、絶縁膜14として酸化シリコン(SiO2)膜をTEOS(tetra ethoxy silane)ガスを使用するプラズマCVD法により、約300nmの厚さに形成する。

【0021】

続いて、不図示のレジスト膜をマスクに用いて酸化防止絶縁膜13と絶縁膜14とをエッチングして、コンタクトホール15を形成する。コンタクトホール15の径は、例えば0.25μmとし、ソース/ドレイン拡散層11のソース/ドレイン電極12Aに到達するまでとする。

【0022】

そして、コンタクトホール15を用いてソース/ドレイン電極12Aに電気的に接続される導電性プラグ16を形成する。具体的には、コンタクトホール15の内面に厚さが30nmのTi膜と、厚さが20nmのTiN膜とを順番にスパッタリング法等により形成して2層の積層構造を有する密着膜(グルー膜)を作製する。さらに、密着膜上にW膜をCVD法により成長させる。この膜厚は、絶縁膜14上で例えば300nmに達する厚さとする。これにより、W膜でコンタクトホール15の空隙が埋まる。この後、絶縁膜14の上面上に成長した余分なW膜及び密着膜をCMP法で除去する。これにより、各コンタクトホール15に、導電性プラグ16が1つずつ形成される。

【0023】

次に、図1Bに示す断面構造を得るまでの工程について説明する。

絶縁膜14及び導電性プラグ16の全面に、酸化防止絶縁膜21膜として例えば、SICN膜をプラズマCVD法により30nmの厚さに形成する。酸化防止絶縁膜21の上には、第1の絶縁膜として第1層間絶縁膜22を形成する。第1層間絶縁膜22は、例えばSIOC膜をプラズマCVD法によって150nmの厚さに形成する。第1層間絶縁膜22は、SOG(Spin on Glass)法を用いて形成しても良い。

【0024】

さらに、第1層間絶縁膜22の全面にレジスト膜を例えばスピンコート法によって塗布

する。続いて、レジスト膜をパターニングしてマスク23を形成する。さらに、マスク23を用いて、第1層間絶縁膜22、酸化防止絶縁膜21、絶縁膜14、シリコン基板1を順番にエッチングして貫通電極用のビアホール25を形成する。ビアホール25の大きさは、コンタクトホール15に比べて十分に大きく、例えば幅が20μm、深さが数10μmとする。ビアホール25の形成後、マスク23は、例えばアッシングによって除去する。

【0025】

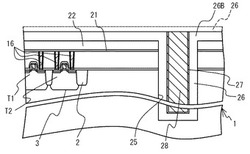

次に、図1Cに示す断面構造を得るまでの工程について説明する。

酸化防止絶縁膜21の全面及びビアホール25の内面にバリア(または拡散防止)膜となる第2の絶縁膜として例えば酸化膜26を200nmの厚さにプラズマCVD法によって形成する。このとき、ビアホール25の側壁には、酸化膜26が100nm程度の厚さに形成される。酸化膜26によって、ビアホール25に埋め込まれる導電材がシリコン基板1中に拡散することが防止される。ここで、酸化膜26は、プラズマCVD法によって形成したSiN膜でも良い。

【0026】

さらに、酸化膜26を覆うように、例えば、TaN膜27をスパッタ法によって150nmの厚さに形成する。この後、TaN膜27上に、第1の導電材としてCu膜28をメッキ法によって例えば10μmの厚さに形成する。これによって、ビアホール25にCu膜28が埋め込まれる。

【0027】

続いて、図1Dに示す断面構造を得るまでの工程について説明する。

Cu膜28の表面に硫酸過水溶液を滴下しながらシリコン基板1をスピンコーターで回転させて、Cu膜28を所定の厚さ、例えば1μm程度の厚さまでエッチングする。さらに、残りのCu膜28、TaN膜27、及び酸化膜26をCMP法によって研磨する。

【0028】

図1Eに破線で示すように、CMPを用いた研磨では、酸化膜26の上部を研磨して膜厚を薄くする。例えば、酸化膜26を50nm程度除去した段階で研磨を終了し、シリコン基板1の上方に例えば、第1の膜厚として150nm程度の酸化膜26Bを残す。酸化膜の研磨レートは50〜70nm/min程度であるため、このような研磨方法では、酸化膜26の研磨量が50nm程度なので、研磨時間が少なくて済む。また、研磨の均一性は5%程度であるが、研磨量が少ないので、研磨後の酸化膜26Bの表面の膜厚のばらつきが低く抑えられる。

【0029】

さらに、図1Fに示す断面構造を得るまでの工程について説明する。

酸化膜26B及びビアホール25内のCu膜28の上に、レジスト膜を塗布してマスクを形成する。さらに、マスクを用いて、酸化膜26B及び第1層間絶縁膜22をドライエッチングする。これによって、第1層間絶縁膜22に配線溝32,33,34からなるパターンが形成される。

【0030】

第1層間絶縁膜22をドライエッチングするときは、酸化膜26をハードマスクとして使用できる。図1Gに示すように、このドライエッチングでは、第1層間絶縁膜22から下方に30nm程度、オーバーエッチングする。これによって、配線溝32,33,34の底部の酸化防止絶縁膜21が完全に除去される。オーバーエッチングによって、絶縁膜14の一部が除去され、絶縁膜14に凹部が形成される。その結果、導電性プラグ16の上部が露出する。また、このエッチングでは、ビアホール25内のCu膜28及びTaN膜27が一部突出することがある。

【0031】

ここで、酸化膜26Bは、ドライエッチングのハードマスクとして使用したので、膜厚が減少して例えば第2の膜厚として20nm〜50nmの酸化膜26Cになる。酸化膜26Cをハードマスクとして使用するので、第1層間絶縁膜22のプラズマダメージが抑え

られる。

【0032】

続いて、図1Hに示す断面構造を得るまでの工程について説明する。

最初に、配線溝32,33,34の内面、コンタクトホール15の上端部分、酸化膜26Cの上に、TaN膜35を例えばスパッタ法にて約8nmの厚さに形成する。さらに、TaN膜35上に、第2の導電材としてCu膜36をメッキ法によって形成する。Cu膜36の厚さは、例えば800nmとする。酸化膜26Cの厚さは、薄くなっているので、配線溝32,33,34へのCu膜36の埋め込み不良は生じない。

【0033】

さらに、図1Iに示す断面構造を得るまでの工程について説明する。

表面のCu膜36と、TaN膜35と、酸化膜26CをCMP法による研磨で順番に除去する。このときに、残りの酸化膜26Cの全てと、酸化膜26Cの下の第1層間絶縁膜22を20nm程度研磨する。ここまでのプロセスで酸化膜26Cの膜厚は、20nm〜50nm程度まで減少させられているので、少ない研磨時間で酸化膜26Cを確実に除去できる。この研磨によって、1層目の配線36A,36B,36Cが形成される。配線36Aは、導電性プラグ16と電気的に接続される。これにより、配線36A,36B,36Cが低誘電体膜である第1層間絶縁膜22に埋め込まれた第1配線層40が形成される。

【0034】

次に、図1Jに示す断面構造を得るまでの工程について説明する。

第1配線層40の上には、酸化防止絶縁膜41として例えばSICN膜をスパッタ法によって約30nmの厚さに形成する。さらに、酸化防止絶縁膜41の上に、第2層間絶縁膜42として、例えば、SIOC膜をプラズマCVD法にて約250nmの厚さに形成する。第2層間絶縁膜42の上には、酸化膜43をプラズマCVD法によって約50nmの厚さに形成する。

【0035】

次に、酸化膜43の上にレジスト膜を形成する。レジスト膜をパターニングしてマスクを形成し、マスクを用いて酸化膜43及び第2層間絶縁膜42をエッチングして複数のビアホール45,46を形成する。ビアホール45は、第1配線層40の配線36A,36Cの形成位置の上方に形成される。ビアホール45の深さは、酸化防止絶縁膜41に到達するまでとする。さらに、ビアホール46は、ビアホール25に埋め込んだCu膜28の上方に形成される。ビアホール46の深さは、酸化防止絶縁膜41に到達するまでとする。ここで、図1Jではビアホール46が2つ形成されているが、ビアホール46の数は2つに限定されない。

【0036】

次に、図1Kに示す断面構造を得るまでの工程について説明する。

ビアホール45,46及び酸化膜43の全面にレジスト膜を塗布する。レジスト膜をパターニングして配線パターンに相当するマスクを形成する。マスクを用いて第2層間絶縁膜42をエッチングして2層目の配線溝47を形成する。エッチングには、レジスト膜から形成したマスクに加えて、酸化膜43がハードマスクとして使用される。この際に、ビアホール45の底部に露出する酸化防止絶縁膜41が除去され、第1層の配線36A,36Cの少なくとも一部、及びCu膜28の少なくとも一部が露出する。

【0037】

次に、図1Lに示す断面構造を得るまでの工程について説明する。

配線溝47及びビアホール45及び酸化膜43の全面に、バリアメタル膜であるTaN膜48を例えばスパッタ法にて約8nmの厚さに形成する。さらに、TaN膜48上にCu膜をメッキ法によって形成する。Cu膜の膜厚は、例えば800nmとする。この後、表面のCu膜と、TaN膜48と、酸化膜43をCMP法による研磨で順番に除去する。これによって、ビアホール45,46に導電性プラグ51A,51B,51Cが形成されると共に、配線溝47に配線52A,52Cが形成される。これによって、低誘電体膜で

ある第2層間絶縁膜42に配線52A,52Cが埋め込まれた第2配線層55が形成される。

【0038】

ここで、第1層45の配線36Aは、導電性プラグ51Aを介して第2配線層55の配線52Aに電気的に接続される。また、第1層45の配線36Cは、導電性プラグ51Bを介して第2配線層55の配線52Cに電気的に接続される。また、配線52Cは、複数の導電性プラグ51Cを介してビアホール25内に埋め込んだCu膜28にも電気的に接続される。例えば、ビアホール25内に埋め込んだCu膜28を用いて貫通電極を形成し、かつ貫通電極を電源供給用の電極として使用した場合には、第2配線層55の配線52Cから導電性プラグ51Bを経て、第1層45の配線36Cに電力が供給される。

【0039】

次に、図1Mに示す断面構造を得るまでの工程について説明する。

まず、第2配線層55の上に、第3配線層60を形成する。第3配線層60は、最初に酸化防止絶縁膜61を形成する。酸化防止絶縁膜61の上には、第3層間絶縁膜62を前記と同様に形成する。第3層間絶縁膜62には、下層の第2の配線52A,52Cに電気的に接続される導電性プラグ63A,63Cと、導電性プラグ63A,63Cに電気的に接続される第3の配線64A,64Cが形成される。第3配線層60の形成方法は、第2配線層55と同様である。

【0040】

さらに、第3配線層60の上に、第4配線層70を形成する。第4配線層70では、最初に酸化防止絶縁膜71を形成する。酸化防止絶縁膜71の上には、第4層間絶縁膜72を形成する。第4層間絶縁膜72には、下層の第3の配線64A,64Cに電気的に接続される導電性プラグ73A,73B,73Cと、導電性プラグ73A,73B,73Cによって第3の配線64A,64Cに接続される第4の配線74A,74Cが形成される。

【0041】

さらに、第4配線層70の上に、第5配線層80を形成する。第5配線層80では、最初に酸化防止絶縁膜81を形成する。酸化防止絶縁膜81の上には、第5層間絶縁膜82を形成する。第5層間絶縁膜82には、下層の第4の配線74A,74Bに電気的に接続される導電性プラグ83A,83Bと、導電性プラグ83A,83Cに電気的に接続される第5の配線84A,84Cが形成される。ここで、ビアホール25の上方に形成される導電性プラグ63C,73C,83Cの数は、2つずつに限定されない。

【0042】

続いて、図1Nに示す断面構造を得るまでの工程について説明する。

第5配線層80の上に、酸化膜91を例えばプラズマCVD法を用いて約1μmの厚さに形成する。さらに、酸化膜91の上にレジスト膜を塗布し、レジスト膜をパターニングしてマスクを形成する。マスクを用いて酸化膜91をエッチングし、ビアホール93を形成する。

【0043】

ビアホール93を含む酸化膜91の全面に、Ta膜、Ti膜、TiN膜の積層膜94を形成する。積層膜94は下から順番に、厚さ10nmのTa膜と、厚さ20nmのTi膜と、厚さ20nmのTiN膜からなる。Ta膜、Ti膜及びTiN膜は、例えばスパッタ法によって形成する。さらに、ビアホール93を埋めるように、Al膜95を例えばスパッタ法を用いて1.5μmの膜厚に形成する。

【0044】

Al膜95の上にレジスト膜を塗布した後に、レジスト膜をパターニングしてマスクを形成する。さらに、マスクを用いて、Al膜95をエッチングして、Alの配線96を形成する。Alの配線96及び酸化膜91の上には、SiN膜97を例えばプラズマCVD法にて約200nmの厚さに形成する。SiN膜97の上には、SIO膜98を例えばプラズマCVD法にて約1.5μmの厚さに形成する。SIO膜98の上にレジスト膜を塗布し後に、レジスト膜をパターニングしてマスクを形成する。さらに、マスクを用いて、

SIO膜98をエッチングして、ビアホール99を形成する。さらに、シリコン基板1をスピンコーターで回転させながら、SIO膜98及び配線96の上に、ポリイミド樹脂を塗布した後に硬化させてポリイミド膜100を形成した後、レジスト膜から形成したマスクを用いてポリイミド膜100をパターニングする。さらに、ビアホール99内にバンプ101を形成する。これによって、第5配線層80の一部の配線84A,84Cが、Alの配線96を介してバンプ101に電気的に接続される。

【0045】

この後、バックグラインダでシリコン基板1の他方の面である裏面を研磨する。研磨は、ビアホール25内のCu膜28がシリコン基板1の裏面に露出するまで行う。これにより、シリコン基板1を貫通する貫通電極110が形成される。

【0046】

次に、図1Oに示す断面構造を得るまでの工程について説明する。

シリコン基板1の裏面の全面にポリイミド樹脂を塗布し、硬化させることでポリイミド層111を形成する。さらに、ポリイミド層111をパターニングして貫通電極110を露出させた後、貫通電極110の裏面側の端面にバンプ112を電気的に接続する。これによって、半導体装置120が形成される。

【0047】

半導体装置120を積層するときは、下側のバンプ112を使って、他の半導体装置120や回路基板の電極に実装する。半導体装置120の上に他の半導体装置120を実装するときは、上側のバンプ101を使用する。

貫通電極110を電源供給に使用する場合には、複数の導電性プラグ51C,63C,73C,83Cを介して第2配線層55から第5配線層80の各層に直接に電力を供給できる。第1配線層40には、第2配線層55を経由して電力が供給される。

【0048】

以上、説明したように、この半導体装置の製造方法では、貫通電極110を形成する過程で第1層間絶縁膜22の上に形成される酸化膜26の膜厚を段階的に減少させ、最終的には研磨によって除去する。これによって、酸化膜26が第1層間絶縁膜22上に残留したり、第1層間絶縁膜22がオーバーエッチングされたりすることが防止される。例えば、酸化膜26が残留したままでシリコン基板1上に回路を形成すると、配線溝32〜34の深さが、本来の第1層間絶縁膜22の厚さと、残った酸化膜26の厚さを合計した深さなる。この場合には、配線溝32〜34にCu膜36が十分に埋め込まれない可能性が生じる。また、酸化膜26が残留することで配線溝32〜34が深くなると、配線溝32〜34に埋め込んだCu膜28の体積が大きくなるので、配線の容量が増大する可能性がある。この実施の形態では、配線溝32〜34が深くなり過ぎることがないので、配線を確実に埋め込める。さらに、配線の容量が増大することはない。

【0049】

ここで、この実施の形態の変形例について説明する。

図2に示すように、配線溝32〜34のドライエッチング時に酸化膜26Bを全て除去しても良い。即ち、酸化膜26B及び第1層間絶縁膜22をドライエッチングして配線溝32〜34を形成する。この際、第1層間絶縁膜22をオーバーエッチングして導電性プラグ16の上端部分を露出させると共に、酸化膜26を全て除去する。

【0050】

また、図1Gに示すような配線溝32〜34を形成するときに、酸化膜26Bの膜厚を減少させることなくエッチングを終了し、配線溝32〜34にCu膜36を埋め込んだ後の研磨にて酸化膜26Bを除去しても良い。例えば、配線溝32〜34の幅が深い場合や、配線溝32〜34の深さが浅い場合など、Cu膜36の埋め込み不良が生じない場合には、配線容量の増加を防止できる。

【0051】

さらに、図3に示すように、ビアホール25内のCu膜28は、第2配線層55Aに直接には接続されなくても良い。この場合は、シリコン基板1上に半導体素子であるトラン

ジスタT1,T2を形成した後、第1配線層40を形成する。さらに、シリコン基板1にビアホール25を形成し、ビアホール25の内壁に酸化膜26を形成した後、ビアホール25内にCu膜28を埋め込む。続いて、第1配線層40の上に、第2配線層55Aを形成する。第2配線層55Aは、配線52A、52Dを有する。また、ビアホール25内のCu膜28に電気的に接続される導電性プラグ51Dが複数形成される。この後、第2配線層55Aの上に、第3配線層60を形成する。第3配線層60は、配線64Cが導電性プラグ51Dを介して、ビアホール25内のCu膜28に電気的に接続される。この変形例では、ビアホール25にCu膜28を埋め込んだ貫通電極110は、第2配線層55Aの配線52A,52Dとは、直接には接続されない。これに対して、第3配線層60の配線64Cは、導電性プラグ51D,63Cを介して貫通電極110に電気的に接続される。

【0052】

また、第4配線層70Aの配線74A,74Dは、ビアホール25内のCu膜28には直接には接続されない。これに対して、第5配線層80の配線84Cは、導電性プラグ51D,63C,73D,83Cを介して貫通電極110に電気的に接続される。従って、図3に示す例では、第3配線層60の配線64Cと、第5配線層80の配線84Cのみがビアホール25内のCu膜28に直接に接続される。このように、貫通電極110は、シリコン基板1の上方に形成される多層配線構造の少なくとも1つの配線と接続される。このような変形例においても、前記と同様の効果が得られる。

【0053】

(第2の実施の形態)

第2の実施の形態について図面を参照して詳細に説明する。第1の実施の形態と同様の構成要素は同じ符号を付している。また、第1の実施の形態と重複する説明は、省略する。

【0054】

まず、図4Aに示す断面構造を得るまでの工程について説明する。

シリコン基板1上には、半導体素子であるトランジスタT1,T2を形成する。さらに、シリコン基板1及びトランジスタT1,T2を覆うように、第1の絶縁膜として絶縁膜14を形成する。この後、絶縁膜14の全面にレジスト膜を用いたマスク23Aを形成する。さらに、マスク23Aを用いて絶縁膜14及びシリコン基板1をドライエッチングして貫通電極用のビアホール25を形成する。ビアホール25の大きさは、例えば幅が20μm、深さが数10μmとする。ビアホール25の形成後には、マスク23Aを例えばアッシングによって除去する。

【0055】

図4Bに示すように、絶縁膜14の全面及びビアホール25の内面にバリアメタル膜として例えば酸化膜26をプラズマCVD法によって200nmの厚さに形成する。この場合、ビアホール25の側壁には、酸化膜26が100nm程度の膜厚に形成される。酸化膜26は、プラズマCVD法によって形成したSiN膜でも良い。

【0056】

さらに、酸化膜26を覆うように、例えば、TaN膜27をスパッタ法によって150nmの厚さに形成する。この後、TaN膜27上に、Cu膜28をメッキ法によって例えば10μmの厚さに形成する。これによって、ビアホール25にCu膜28が埋め込まれる。

【0057】

続いて、図4Cに示す断面構造を得るまでの工程について説明する。

最初に、Cu膜28の表面に硫酸過水溶液を滴下しながらシリコン基板1をスピンコーターで回転させて、Cu膜28を所定の厚さ、例えば1μm程度の厚さまでエッチングする。さらに、残りのCu膜28、TaN膜27、及び酸化膜26をCMP法によって研磨する。図4Cに破線で示すように、CMPを用いた研磨では、酸化膜26を上方から研磨して、膜厚を薄くする。たとえば、酸化膜26を50nm程度除去した段階で研磨を終了

し、シリコン基板1の上方に例えば、150nm程度の酸化膜26Bを残す。

【0058】

さらに、図4Dに示す断面構造を得るまでの工程について説明する。

まず、酸化膜26B及び絶縁膜14をドライエッチングしてコンタクトホール15からなるパターンを形成する。コンタクトホール15の径は、例えば0.25μmとする。ソース/ドレイン拡散層11のソース/ドレイン電極12Aに到達するまでとする。ドライエッチングは、酸化膜26B上に形成した不図示のマスクを用いる。さらに、酸化膜26Bをドライエッチングのハードマスクとして使用する。これによって、膜厚が例えば20nm〜50nmに減少した酸化膜26Cが形成される。酸化膜26Cをハードマスクとして使用するので、絶縁膜14のプラズマダメージが抑えられる。

【0059】

次に、図4Eに示すように、コンタクトホール15の内面及び酸化膜26C、Cu膜28の上に、例えば、密着膜16Aをスパッタ法によって150nmの厚さに形成する。この後、密着膜16A上に、第2の導電材としてW膜16Bをメッキ法によって例えば10μmの厚さに形成する。これによって、ビアホール25にW膜16Bが埋め込まれる。これにより、W膜16Bでコンタクトホール15の空隙が埋まる。

【0060】

この後、図4Fに示すように、絶縁膜14の上面上に成長した余分なW膜16B及び密着膜16AをCMP法で除去する。このときに、残りの酸化膜26Cの全てと、酸化膜26Cの下の絶縁膜14を20nm程度研磨する。ここまでのプロセスで酸化膜26Cの膜厚は、20nm〜50nm程度まで減少させられているので、少ない研磨時間で酸化膜26Cを確実に除去できる。ここまでの工程で、各コンタクトホール15に、導電性プラグ16が1つずつ形成される。

【0061】

次に、図4Gに示す断面構造を得るまでの工程について説明する。

絶縁膜14の上に、第1配線層40Aを形成する。第1配線層40Aは、最初に酸化防止絶縁膜141を形成する。酸化防止絶縁膜141の上には、第1層間絶縁膜142を形成する。第1層間絶縁膜142には、導電性プラグ16及びビアホール25のCu膜28に電気的に接続される導電性プラグ143A,143Cと、第1の配線144A,144Cが形成される。以降は、第2配線層55、第3配線層60、第4配線層70、第5配線層80を順番に形成する。

【0062】

さらに、第5配線層80の上に、酸化膜91を形成する。酸化膜91をエッチングしてビアホール93を形成する。

【0063】

ビアホール93を含む酸化膜91の全面に、積層膜として例えばTa膜、Ti膜、TiN膜を順番にスパッタ法にて形成する。さらに、ビアホール93を埋めるように、Al膜95を例えばスパッタ法を用いて形成する。Al膜95をエッチングして、Alの配線96を形成する。

【0064】

さらに、Alの配線96及び酸化膜91の上に、SiN膜97を例えばプラズマCVD法にて約200nmの厚さに形成する。SiN膜97の上には、SIO膜98を例えばプラズマCVD法にて約1.5μmの厚さに形成する。SIO膜98をエッチングして、ビアホール99を形成する。さらに、シリコン基板1をスピンコーターで回転させながら、SIO膜98及び配線96の上に、ポリイミド樹脂を塗布する。ポリイミド膜を硬化させてポリイミド層100を形成した後、レジスト膜から形成したマスクを用いてポリイミド膜をパターニングする。さらに、ビアホール99内にバンプ101を形成する。これによって、第5層の一部の配線83が、Alの配線96を介してバンプ101に電気的に接続される。

【0065】

この後、バックグラインダでシリコン基板1の裏面を研磨する。研磨は、スルービアホール25内のCu膜28がシリコン基板1の裏面に露出するまで行う。これにより、シリコン基板1を貫通する貫通電極110が形成される。

【0066】

次に、図4Hに示す断面構造を得るまでの工程について説明する。

シリコン基板1の裏面の全面にポリイミド樹脂を塗布し、硬化させることでポリイミド層111を形成する。さらに、ポリイミド層111をパターニングして貫通電極110を露出させた後、貫通電極110の裏面側の端面にバンプ112を電気的に接続する。これによって、半導体装置120Aが形成される。

【0067】

以上、説明したように、この半導体装置の製造方法では、貫通電極110を形成する過程で絶縁膜14の上に形成される酸化膜26を段階的に除去するので、酸化膜26が絶縁膜14上に残留したり、絶縁膜14がオーバーエッチングされたりすることが防止される。

【0068】

ここで、コンタクトホール15のドライエッチング時に酸化膜26Bを全て除去しても良い。例えば、配線溝32〜34が浅い場合など、Cu膜36の埋め込み不良が生じない場合には、酸化膜26Bの膜厚を減少させることなくコンタクトホール15を形成し、W膜16Aをコンタクトホール15に埋め込んだ後に研磨にて酸化膜26Bを除去しても良い。貫通電極110は、シリコン基板1の上方に形成される多層配線構造の少なくとも1つの配線と接続される。

【0069】

また、絶縁膜14にコンタクトホール15及び導電性プラグ16を形成した後に、ビアホール25の形成と、Cu膜28の埋め込みを行っても良い。この場合は、CMP法による研磨と、ドライエッチングと、CMP法による研磨とを順番に実行して酸化膜26を段階的に除去する。また、CMP法による研磨と、ドライエッチングを順番に実行して酸化膜26を段階的に除去しても良い。

【0070】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができる。

【0071】

以下に、前記の実施の形態の特徴を付記する。

(付記1) 基板の一方の面上に半導体素子を形成する工程と、前記半導体素子の上方に第1の絶縁膜を形成する工程と、前記第1の絶縁膜を貫通し、前記基板にホールを形成する工程と、前記第1の絶縁膜上及び前記ホールの内壁に第2の絶縁膜を形成する工程と、前記ホール内に第1の導電膜を埋める工程と、前記第1の絶縁膜上の前記第1の導電膜と、前記第2の絶縁膜の一部を研磨によって除去する工程と、前記第2の絶縁膜と前記第1の絶縁膜をエッチングしてパターンを形成する工程と、前記パターンに第2の導電膜を埋め込む工程と、前記第1の絶縁膜の上方の前記第2の導体膜と、残りの前記第2の絶縁膜を研磨により除去し、前記第1の絶縁膜を露出させる工程と、前記基板の厚さを他方の面から減少させ、前記ホール内に埋めた前記第1の導電膜を露出させる工程と、を含むことを特徴とする半導体装置の製造方法。

(付記2) 前記パターンを形成する工程は、前記第2の絶縁膜の膜厚をエッチングにより減少させる工程を含むことを特徴とする付記1に記載の半導体装置の製造方法。

(付記3) 前記第1の絶縁膜を形成する工程は、前記半導体素子に電気的に接続されるプラグを埋め込んだ膜上に前記第1の絶縁膜を形成する工程であり、前記パターンに第2

の導電膜を埋め込む工程は、前記第プラグと電気的に接続される配線溝を形成する工程を含むことを特徴とする付記1又は付記2に記載の半導体装置の製造方法。

(付記4) 前記ホールを形成する工程は、前記プラグを埋め込んだ前記膜を貫通して前記基板に前記ホールを形成する工程であることを特徴とする付記3に記載の半導体装置の製造方法。

(付記5) 前記第1の絶縁膜及び前記第2の導電膜の上に、前記第3の絶縁膜を形成する工程と、前記第3の絶縁膜に、前記第2の導電膜と電気的に接続する配線を形成する工程と、を含む付記3又は付記4に記載の半導体装置の製造方法。

(付記6) 前記第1の絶縁膜は、前記半導体素子の上に形成され、前記パターンに第2の導電膜を埋め込む工程は、前記半導体素子に電気的に接続されるプラグを形成する工程を含むことを特徴とする付記1又は付記2に記載の半導体装置の製造方法。

(付記7) 前記第1の絶縁膜を研磨によって露出させた後、前記第1の絶縁膜の上方に複数の配線層を形成する工程を含み、前記複数の配線層を形成した後に、前記基板の厚さを他方の面から減少させ、前記ホール内に埋めた前記第1の導電膜を露出させることを特徴とする付記1乃至6のいずれか一項に記載の半導体装置の製造方法。

(付記8) 前記第1の導電膜と前記第2の導電膜が前記複数の配線層の少なくとも一部でコンタクトしていることを特徴とする付記7に記載の半導体装置の製造方法。

(付記9) 基板の一方の面上に半導体素子を形成する工程と、前記半導体素子の上方に第1の絶縁膜を形成する工程と、前記第1の絶縁膜を貫通し、前記基板にホールを形成する工程と、前記第1の絶縁膜上、及び前記ホールの内壁に第2の絶縁膜を形成する工程と、前記ホールに導電材を埋め込む工程と、前記第1の絶縁膜上の前記導電材及び前記第2の絶縁膜を研磨し、前記第1の絶縁膜上の前記第2の絶縁膜を第1の膜厚に研磨する工程と、前記第1の絶縁膜上の第2の絶縁膜をエッチングよって第1の膜厚より薄い第2の膜厚にする工程と、第2の膜厚の第2の絶縁膜を研磨によって前記第1の絶縁膜上から除去する工程と、前記基板の上方に、前記導電材と電気的に接続される配線を形成した後、前記基板の厚さを他方の面側から減少させ、前記第1の導電膜を露出させる工程と、を含む半導体装置の製造方法。

(付記10) 前記第1の絶縁膜にパターンを形成する工程を有し、前記第1の絶縁膜をエッチングするときに、前記第2の絶縁膜を第2の膜厚にすることを特徴とする付記9に記載の半導体装置の製造方法。

(付記11) 前記第1の絶縁膜に配線材料を埋め込んで配線を形成する工程を有し、前記配線材料を研磨するときに、第2の膜厚の第2の絶縁膜を研磨によって前記第1の絶縁膜上から除去することを特徴とする付記9又は付記10に記載の半導体装置の製造方法。

【符号の説明】

【0072】

1 シリコン基板

14 絶縁膜(第1の絶縁膜)

15 コンタクトホール(パターン)

16 導電性プラグ

16B W膜(第2の導電材)

22 第1層間絶縁膜

25 ビアホール

26,26B,26C 酸化膜(第2の絶縁膜)

28 Cu膜(第1の導電膜)

32,33,34 配線溝(パターン)

36 Cu膜(第2の導電材)

40 第1配線層

55 第2配線層

60 第3配線層

70 第4配線層

80 第5配線層

T1,T2 半導体素子

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

電子部品には、半導体素子が形成された半導体装置を有するものがある。半導体装置は、例えば、シリコン基板上に半導体素子やその他の回路が形成される。複数の半導体装置を1つの電子部品の回路基板に実装すると電子部品が高性能化される。さらに、複数の半導体装置を積層して回路基板に実装すると、電子部品が小型化される。半導体装置を積層するときは、1つ目の半導体装置の上に2つ目の半導体装置を載置した後、それぞれの半導体装置の電極同士をワイヤボンディングによって電気的に接続する。

【0003】

このために、複数の半導体装置を積層して実装するためには、下側の半導体装置の電極は上側の半導体装置から露出する位置に形成される。従って、ワイヤボンディングを用いて半導体装置を積層するためには、上側の半導体装置の大きさを、下側の半導体装置の大きさより小さくする必要があった。その結果、下側の半導体装置の小型化が難しかった。

【0004】

そこで、近年では、半導体装置にシリコン基板を貫通する貫通電極(TSV,through-silicon via)が形成される。貫通電極は、シリコン基板を貫通するスルーホールの内部に銅などの導電材を埋め込んだ構成を有する。

【0005】

ここで、TSVの従来の形成方法について説明する。最初に、シリコン基板上に1層目の配線を形成する。続いて、1層目の配線の上に層間絶縁膜を形成する。この後、ドライエッチングによって、層間絶縁膜を貫通し、シリコン基板を所定の深さに達するビアホールを形成する。ビアホール内に絶縁膜を形成した後、密着層とシード層を形成する。この後、電解めっきによってビアホール内に金属を充填する。層間絶縁膜の上に残る金属や密着層を除去して、層間絶縁膜の表面と、ビアホール内に埋め込んだ金属の表面を露出させる。ビアホールの内壁に酸化膜を形成することで、ビアホールの絶縁性が確保され、ビアホール内の埋め込まれた金属の拡散が防止される。

【0006】

続いて、層間絶縁膜上に配線を形成する。この後、シリコン基板の裏面側をドライエッチング又はウエットエッチングして、貫通電極の裏面側を露出させる。露出した貫通電極の端面には、バンプを接合する。貫通電極は、バンプを介して、他の半導体装置の電極などに電気的に接続される。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】国際公開第WO2006/080337号

【発明の概要】

【発明が解決しようとする課題】

【0008】

ここで、貫通電極を電源供給用に用いる場合など、貫通電極に大電流を流すためには、酸化膜の膜厚を厚くする必要がある。しかしながら、酸化膜の膜厚が大きいと、シリコン基板表面の余分な酸化膜を確実に除去することが難しい。これは、酸化膜の研磨レートが遅く、研磨に時間を要するためである。さらに、研磨の均一性が悪いため、層間絶縁膜上の酸化膜を均一に除去することが困難である。このために、貫通電極を効率良く、形成することが望まれていた。

【課題を解決するための手段】

【0009】

本実施形態の一観点によれば、基板の一方の面上に半導体素子を形成する工程と、前記半導体素子の上方に第1の絶縁膜を形成する工程と、前記第1の絶縁膜を貫通し、前記基板にホールを形成する工程と、前記第1の絶縁膜上及び前記ホールの内壁に第2の絶縁膜を形成する工程と、前記ホール内に第1の導電材を埋める工程と、前記第1の絶縁膜上の前記第1の導電材と、前記第2の絶縁膜の一部を研磨によって除去する工程と、前記第2の絶縁膜と前記第1の絶縁膜をエッチングしてパターンを形成する工程と、前記パターンに第2の導電材を埋め込む工程と、前記第1の絶縁膜の上方の前記第2の導電材と、残りの前記第2の絶縁膜を研磨により除去し、前記第1の絶縁膜を露出させる工程と、前記基板の厚さを他方の面から減少させ、前記ホール内に埋めた前記第1の導電材を露出させる工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0010】

酸化膜を研磨する時間が短縮され、貫通電極を効率よく形成できる。

【図面の簡単な説明】

【0011】

【図1A】図1Aは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図1B】図1Bは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図1C】図1Cは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図1D】図1Dは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図1E】図1Eは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図1F】図1Fは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その6)である

【図1G】図1Gは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その7)である。

【図1H】図1Hは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その8)である。

【図1I】図1Iは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その9)である。

【図1J】図1Jは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その10)である。

【図1K】図1Kは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その11)である。

【図1L】図1Lは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その12)である。

【図1M】図1Mは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その13)である。

【図1N】図1Nは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その14)である。

【図1O】図1Oは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その15)である。

【図2】図2は、本発明の第1の実施の形態の変形例に係る半導体装置の製造工程を示す断面図である。

【図3】図3は、本発明の第1の実施の形態の他の変形例に係る半導体装置の製造工程を示す断面図である。

【図4A】図4Aは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図4B】図4Bは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図4C】図4Cは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図4D】図4Dは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図4E】図4Eは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図4F】図4Fは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その6)である。

【図4G】図4Gは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その7)である。

【図4H】図4Hは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その8)である。

【発明を実施するための最良の形態】

【0012】

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。

前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない。

【0013】

(第1の実施の形態)

実施の形態の半導体装置の製造方法について図面を参照して詳細に説明する。

最初に、図1Aに示す断面構造を得るまでの工程について説明する。

まず、n型又はp型のシリコン(半導体)基板1の一方の面である表面を熱酸化することにより素子分離絶縁膜2を例えば30nmの深さに形成し、この素子分離絶縁膜2でトランジスタの活性領域を画定する。このような素子分離構造は、LOCOS(Local Oxidation of Silicon)と呼ばれる。素子分離領域には、STI(Shallow Trench Isolation)を用いても良い。

【0014】

次いで、シリコン基板1の活性領域にイオン注入法により、ドーパント不純物を導入してウェルを形成する。ドーパント不純物としてp型不純物、例えばボロンを導入すると、シリコン基板1にpウェル3が形成される。pウェル3を形成した後、その活性領域の表面を熱酸化してゲート絶縁膜5を形成する。ゲート絶縁膜5は、例えば熱酸化膜を約6nm〜7nmの厚さに形成する。なお、以下においては、pウェル3を形成した場合について説明するが、シリコン基板1にnウェルを形成した場合も同様の工程が実施される。

【0015】

続いて、シリコン基板1の上側全面に、ポリシリコン膜を例えばCVD法を用いて200nmの膜厚に形成する。その後に、フォトリソグラフィ技術及びエッチング技術を用いてポリシリコン膜をパターニングして、シリコン基板1上にゲート電極6を形成する。ゲート電極6は、pウェル3上に互いに平行に複数形成され、その各々はワード線の一部を構成する。

【0016】

さらに、ゲート電極6をマスクにしてpウェル3にイオンを注入し、ゲート電極6の横のpウェル3にn型不純物としてリンを導入する。これにより、第1、第2ソース/ドレインエクステンション8が形成される。第1、第2ソース/ドレインエクステンション8は、エクステンションソース/ドレイン領域の浅い領域を構成する。その後に、シリコン基板1の上側全面に、絶縁膜としてシリコン酸化膜を例えばCVD法を用いて300nm

の厚さに形成する。その後、絶縁膜を異方性エッチングする。絶縁膜がエッチバックされ、ゲート電極6の側部に絶縁性サイドウォール10が形成される。

【0017】

続いて、絶縁性サイドウォール10とゲート電極6をマスクとして用い、シリコン基板1に砒素等のn型のドーパント不純物を再びイオン注入する。これにより、ゲート電極6の側方のpウェル3に、ソース/ドレイン拡散層11が形成される。ソース/ドレイン拡散層11は、エクステンションソース/ドレインの深い領域を構成する。

【0018】

さらに、シリコン基板1の全面に、例えば、スパッタリング法によりコバルト膜等の高融点金属膜を形成する。この後、高融点金属膜を加熱してシリコンと反応させる。これにより、ソース/ドレイン拡散層11におけるシリコン基板1上にコバルトシリサイド層等の高融点金属シリサイド層が形成され、各ソース/ドレイン拡散層11が低抵抗化する。この後、素子分離絶縁膜2の上などに未反応のまま残っている高融点金属膜を例えばウエットエッチングにより除去する。これにより、ソース/ドレイン拡散層11上に、例えばコバルトシリサイドで形成されるソース/ドレイン電極12Aが形成される。また、ゲート電極6の上部に、例えばコバルトシリサイドからなるシリサイド層12Bが形成される。

【0019】

ここまでの工程により、シリコン基板1の活性領域には、ゲート絶縁膜5、ゲート電極6、及びソース/ドレイン電極12A等から構成される半導体素子であるトランジスタT1,T2が形成される。

【0020】

さらに、シリコン基板1の上側の全面に、酸化防止絶縁膜13として酸窒化シリコン(SiON)膜をプラズマCVD法により形成する。

さらに、酸化防止絶縁膜13の上に、絶縁膜14として酸化シリコン(SiO2)膜をTEOS(tetra ethoxy silane)ガスを使用するプラズマCVD法により、約300nmの厚さに形成する。

【0021】

続いて、不図示のレジスト膜をマスクに用いて酸化防止絶縁膜13と絶縁膜14とをエッチングして、コンタクトホール15を形成する。コンタクトホール15の径は、例えば0.25μmとし、ソース/ドレイン拡散層11のソース/ドレイン電極12Aに到達するまでとする。

【0022】

そして、コンタクトホール15を用いてソース/ドレイン電極12Aに電気的に接続される導電性プラグ16を形成する。具体的には、コンタクトホール15の内面に厚さが30nmのTi膜と、厚さが20nmのTiN膜とを順番にスパッタリング法等により形成して2層の積層構造を有する密着膜(グルー膜)を作製する。さらに、密着膜上にW膜をCVD法により成長させる。この膜厚は、絶縁膜14上で例えば300nmに達する厚さとする。これにより、W膜でコンタクトホール15の空隙が埋まる。この後、絶縁膜14の上面上に成長した余分なW膜及び密着膜をCMP法で除去する。これにより、各コンタクトホール15に、導電性プラグ16が1つずつ形成される。

【0023】

次に、図1Bに示す断面構造を得るまでの工程について説明する。

絶縁膜14及び導電性プラグ16の全面に、酸化防止絶縁膜21膜として例えば、SICN膜をプラズマCVD法により30nmの厚さに形成する。酸化防止絶縁膜21の上には、第1の絶縁膜として第1層間絶縁膜22を形成する。第1層間絶縁膜22は、例えばSIOC膜をプラズマCVD法によって150nmの厚さに形成する。第1層間絶縁膜22は、SOG(Spin on Glass)法を用いて形成しても良い。

【0024】

さらに、第1層間絶縁膜22の全面にレジスト膜を例えばスピンコート法によって塗布

する。続いて、レジスト膜をパターニングしてマスク23を形成する。さらに、マスク23を用いて、第1層間絶縁膜22、酸化防止絶縁膜21、絶縁膜14、シリコン基板1を順番にエッチングして貫通電極用のビアホール25を形成する。ビアホール25の大きさは、コンタクトホール15に比べて十分に大きく、例えば幅が20μm、深さが数10μmとする。ビアホール25の形成後、マスク23は、例えばアッシングによって除去する。

【0025】

次に、図1Cに示す断面構造を得るまでの工程について説明する。

酸化防止絶縁膜21の全面及びビアホール25の内面にバリア(または拡散防止)膜となる第2の絶縁膜として例えば酸化膜26を200nmの厚さにプラズマCVD法によって形成する。このとき、ビアホール25の側壁には、酸化膜26が100nm程度の厚さに形成される。酸化膜26によって、ビアホール25に埋め込まれる導電材がシリコン基板1中に拡散することが防止される。ここで、酸化膜26は、プラズマCVD法によって形成したSiN膜でも良い。

【0026】

さらに、酸化膜26を覆うように、例えば、TaN膜27をスパッタ法によって150nmの厚さに形成する。この後、TaN膜27上に、第1の導電材としてCu膜28をメッキ法によって例えば10μmの厚さに形成する。これによって、ビアホール25にCu膜28が埋め込まれる。

【0027】

続いて、図1Dに示す断面構造を得るまでの工程について説明する。

Cu膜28の表面に硫酸過水溶液を滴下しながらシリコン基板1をスピンコーターで回転させて、Cu膜28を所定の厚さ、例えば1μm程度の厚さまでエッチングする。さらに、残りのCu膜28、TaN膜27、及び酸化膜26をCMP法によって研磨する。

【0028】

図1Eに破線で示すように、CMPを用いた研磨では、酸化膜26の上部を研磨して膜厚を薄くする。例えば、酸化膜26を50nm程度除去した段階で研磨を終了し、シリコン基板1の上方に例えば、第1の膜厚として150nm程度の酸化膜26Bを残す。酸化膜の研磨レートは50〜70nm/min程度であるため、このような研磨方法では、酸化膜26の研磨量が50nm程度なので、研磨時間が少なくて済む。また、研磨の均一性は5%程度であるが、研磨量が少ないので、研磨後の酸化膜26Bの表面の膜厚のばらつきが低く抑えられる。

【0029】

さらに、図1Fに示す断面構造を得るまでの工程について説明する。

酸化膜26B及びビアホール25内のCu膜28の上に、レジスト膜を塗布してマスクを形成する。さらに、マスクを用いて、酸化膜26B及び第1層間絶縁膜22をドライエッチングする。これによって、第1層間絶縁膜22に配線溝32,33,34からなるパターンが形成される。

【0030】

第1層間絶縁膜22をドライエッチングするときは、酸化膜26をハードマスクとして使用できる。図1Gに示すように、このドライエッチングでは、第1層間絶縁膜22から下方に30nm程度、オーバーエッチングする。これによって、配線溝32,33,34の底部の酸化防止絶縁膜21が完全に除去される。オーバーエッチングによって、絶縁膜14の一部が除去され、絶縁膜14に凹部が形成される。その結果、導電性プラグ16の上部が露出する。また、このエッチングでは、ビアホール25内のCu膜28及びTaN膜27が一部突出することがある。

【0031】

ここで、酸化膜26Bは、ドライエッチングのハードマスクとして使用したので、膜厚が減少して例えば第2の膜厚として20nm〜50nmの酸化膜26Cになる。酸化膜26Cをハードマスクとして使用するので、第1層間絶縁膜22のプラズマダメージが抑え

られる。

【0032】

続いて、図1Hに示す断面構造を得るまでの工程について説明する。

最初に、配線溝32,33,34の内面、コンタクトホール15の上端部分、酸化膜26Cの上に、TaN膜35を例えばスパッタ法にて約8nmの厚さに形成する。さらに、TaN膜35上に、第2の導電材としてCu膜36をメッキ法によって形成する。Cu膜36の厚さは、例えば800nmとする。酸化膜26Cの厚さは、薄くなっているので、配線溝32,33,34へのCu膜36の埋め込み不良は生じない。

【0033】

さらに、図1Iに示す断面構造を得るまでの工程について説明する。

表面のCu膜36と、TaN膜35と、酸化膜26CをCMP法による研磨で順番に除去する。このときに、残りの酸化膜26Cの全てと、酸化膜26Cの下の第1層間絶縁膜22を20nm程度研磨する。ここまでのプロセスで酸化膜26Cの膜厚は、20nm〜50nm程度まで減少させられているので、少ない研磨時間で酸化膜26Cを確実に除去できる。この研磨によって、1層目の配線36A,36B,36Cが形成される。配線36Aは、導電性プラグ16と電気的に接続される。これにより、配線36A,36B,36Cが低誘電体膜である第1層間絶縁膜22に埋め込まれた第1配線層40が形成される。

【0034】

次に、図1Jに示す断面構造を得るまでの工程について説明する。

第1配線層40の上には、酸化防止絶縁膜41として例えばSICN膜をスパッタ法によって約30nmの厚さに形成する。さらに、酸化防止絶縁膜41の上に、第2層間絶縁膜42として、例えば、SIOC膜をプラズマCVD法にて約250nmの厚さに形成する。第2層間絶縁膜42の上には、酸化膜43をプラズマCVD法によって約50nmの厚さに形成する。

【0035】

次に、酸化膜43の上にレジスト膜を形成する。レジスト膜をパターニングしてマスクを形成し、マスクを用いて酸化膜43及び第2層間絶縁膜42をエッチングして複数のビアホール45,46を形成する。ビアホール45は、第1配線層40の配線36A,36Cの形成位置の上方に形成される。ビアホール45の深さは、酸化防止絶縁膜41に到達するまでとする。さらに、ビアホール46は、ビアホール25に埋め込んだCu膜28の上方に形成される。ビアホール46の深さは、酸化防止絶縁膜41に到達するまでとする。ここで、図1Jではビアホール46が2つ形成されているが、ビアホール46の数は2つに限定されない。

【0036】

次に、図1Kに示す断面構造を得るまでの工程について説明する。

ビアホール45,46及び酸化膜43の全面にレジスト膜を塗布する。レジスト膜をパターニングして配線パターンに相当するマスクを形成する。マスクを用いて第2層間絶縁膜42をエッチングして2層目の配線溝47を形成する。エッチングには、レジスト膜から形成したマスクに加えて、酸化膜43がハードマスクとして使用される。この際に、ビアホール45の底部に露出する酸化防止絶縁膜41が除去され、第1層の配線36A,36Cの少なくとも一部、及びCu膜28の少なくとも一部が露出する。

【0037】

次に、図1Lに示す断面構造を得るまでの工程について説明する。

配線溝47及びビアホール45及び酸化膜43の全面に、バリアメタル膜であるTaN膜48を例えばスパッタ法にて約8nmの厚さに形成する。さらに、TaN膜48上にCu膜をメッキ法によって形成する。Cu膜の膜厚は、例えば800nmとする。この後、表面のCu膜と、TaN膜48と、酸化膜43をCMP法による研磨で順番に除去する。これによって、ビアホール45,46に導電性プラグ51A,51B,51Cが形成されると共に、配線溝47に配線52A,52Cが形成される。これによって、低誘電体膜で

ある第2層間絶縁膜42に配線52A,52Cが埋め込まれた第2配線層55が形成される。

【0038】

ここで、第1層45の配線36Aは、導電性プラグ51Aを介して第2配線層55の配線52Aに電気的に接続される。また、第1層45の配線36Cは、導電性プラグ51Bを介して第2配線層55の配線52Cに電気的に接続される。また、配線52Cは、複数の導電性プラグ51Cを介してビアホール25内に埋め込んだCu膜28にも電気的に接続される。例えば、ビアホール25内に埋め込んだCu膜28を用いて貫通電極を形成し、かつ貫通電極を電源供給用の電極として使用した場合には、第2配線層55の配線52Cから導電性プラグ51Bを経て、第1層45の配線36Cに電力が供給される。

【0039】

次に、図1Mに示す断面構造を得るまでの工程について説明する。

まず、第2配線層55の上に、第3配線層60を形成する。第3配線層60は、最初に酸化防止絶縁膜61を形成する。酸化防止絶縁膜61の上には、第3層間絶縁膜62を前記と同様に形成する。第3層間絶縁膜62には、下層の第2の配線52A,52Cに電気的に接続される導電性プラグ63A,63Cと、導電性プラグ63A,63Cに電気的に接続される第3の配線64A,64Cが形成される。第3配線層60の形成方法は、第2配線層55と同様である。

【0040】

さらに、第3配線層60の上に、第4配線層70を形成する。第4配線層70では、最初に酸化防止絶縁膜71を形成する。酸化防止絶縁膜71の上には、第4層間絶縁膜72を形成する。第4層間絶縁膜72には、下層の第3の配線64A,64Cに電気的に接続される導電性プラグ73A,73B,73Cと、導電性プラグ73A,73B,73Cによって第3の配線64A,64Cに接続される第4の配線74A,74Cが形成される。

【0041】

さらに、第4配線層70の上に、第5配線層80を形成する。第5配線層80では、最初に酸化防止絶縁膜81を形成する。酸化防止絶縁膜81の上には、第5層間絶縁膜82を形成する。第5層間絶縁膜82には、下層の第4の配線74A,74Bに電気的に接続される導電性プラグ83A,83Bと、導電性プラグ83A,83Cに電気的に接続される第5の配線84A,84Cが形成される。ここで、ビアホール25の上方に形成される導電性プラグ63C,73C,83Cの数は、2つずつに限定されない。

【0042】

続いて、図1Nに示す断面構造を得るまでの工程について説明する。

第5配線層80の上に、酸化膜91を例えばプラズマCVD法を用いて約1μmの厚さに形成する。さらに、酸化膜91の上にレジスト膜を塗布し、レジスト膜をパターニングしてマスクを形成する。マスクを用いて酸化膜91をエッチングし、ビアホール93を形成する。

【0043】

ビアホール93を含む酸化膜91の全面に、Ta膜、Ti膜、TiN膜の積層膜94を形成する。積層膜94は下から順番に、厚さ10nmのTa膜と、厚さ20nmのTi膜と、厚さ20nmのTiN膜からなる。Ta膜、Ti膜及びTiN膜は、例えばスパッタ法によって形成する。さらに、ビアホール93を埋めるように、Al膜95を例えばスパッタ法を用いて1.5μmの膜厚に形成する。

【0044】

Al膜95の上にレジスト膜を塗布した後に、レジスト膜をパターニングしてマスクを形成する。さらに、マスクを用いて、Al膜95をエッチングして、Alの配線96を形成する。Alの配線96及び酸化膜91の上には、SiN膜97を例えばプラズマCVD法にて約200nmの厚さに形成する。SiN膜97の上には、SIO膜98を例えばプラズマCVD法にて約1.5μmの厚さに形成する。SIO膜98の上にレジスト膜を塗布し後に、レジスト膜をパターニングしてマスクを形成する。さらに、マスクを用いて、

SIO膜98をエッチングして、ビアホール99を形成する。さらに、シリコン基板1をスピンコーターで回転させながら、SIO膜98及び配線96の上に、ポリイミド樹脂を塗布した後に硬化させてポリイミド膜100を形成した後、レジスト膜から形成したマスクを用いてポリイミド膜100をパターニングする。さらに、ビアホール99内にバンプ101を形成する。これによって、第5配線層80の一部の配線84A,84Cが、Alの配線96を介してバンプ101に電気的に接続される。

【0045】

この後、バックグラインダでシリコン基板1の他方の面である裏面を研磨する。研磨は、ビアホール25内のCu膜28がシリコン基板1の裏面に露出するまで行う。これにより、シリコン基板1を貫通する貫通電極110が形成される。

【0046】

次に、図1Oに示す断面構造を得るまでの工程について説明する。

シリコン基板1の裏面の全面にポリイミド樹脂を塗布し、硬化させることでポリイミド層111を形成する。さらに、ポリイミド層111をパターニングして貫通電極110を露出させた後、貫通電極110の裏面側の端面にバンプ112を電気的に接続する。これによって、半導体装置120が形成される。

【0047】

半導体装置120を積層するときは、下側のバンプ112を使って、他の半導体装置120や回路基板の電極に実装する。半導体装置120の上に他の半導体装置120を実装するときは、上側のバンプ101を使用する。

貫通電極110を電源供給に使用する場合には、複数の導電性プラグ51C,63C,73C,83Cを介して第2配線層55から第5配線層80の各層に直接に電力を供給できる。第1配線層40には、第2配線層55を経由して電力が供給される。

【0048】

以上、説明したように、この半導体装置の製造方法では、貫通電極110を形成する過程で第1層間絶縁膜22の上に形成される酸化膜26の膜厚を段階的に減少させ、最終的には研磨によって除去する。これによって、酸化膜26が第1層間絶縁膜22上に残留したり、第1層間絶縁膜22がオーバーエッチングされたりすることが防止される。例えば、酸化膜26が残留したままでシリコン基板1上に回路を形成すると、配線溝32〜34の深さが、本来の第1層間絶縁膜22の厚さと、残った酸化膜26の厚さを合計した深さなる。この場合には、配線溝32〜34にCu膜36が十分に埋め込まれない可能性が生じる。また、酸化膜26が残留することで配線溝32〜34が深くなると、配線溝32〜34に埋め込んだCu膜28の体積が大きくなるので、配線の容量が増大する可能性がある。この実施の形態では、配線溝32〜34が深くなり過ぎることがないので、配線を確実に埋め込める。さらに、配線の容量が増大することはない。

【0049】

ここで、この実施の形態の変形例について説明する。

図2に示すように、配線溝32〜34のドライエッチング時に酸化膜26Bを全て除去しても良い。即ち、酸化膜26B及び第1層間絶縁膜22をドライエッチングして配線溝32〜34を形成する。この際、第1層間絶縁膜22をオーバーエッチングして導電性プラグ16の上端部分を露出させると共に、酸化膜26を全て除去する。

【0050】

また、図1Gに示すような配線溝32〜34を形成するときに、酸化膜26Bの膜厚を減少させることなくエッチングを終了し、配線溝32〜34にCu膜36を埋め込んだ後の研磨にて酸化膜26Bを除去しても良い。例えば、配線溝32〜34の幅が深い場合や、配線溝32〜34の深さが浅い場合など、Cu膜36の埋め込み不良が生じない場合には、配線容量の増加を防止できる。

【0051】

さらに、図3に示すように、ビアホール25内のCu膜28は、第2配線層55Aに直接には接続されなくても良い。この場合は、シリコン基板1上に半導体素子であるトラン

ジスタT1,T2を形成した後、第1配線層40を形成する。さらに、シリコン基板1にビアホール25を形成し、ビアホール25の内壁に酸化膜26を形成した後、ビアホール25内にCu膜28を埋め込む。続いて、第1配線層40の上に、第2配線層55Aを形成する。第2配線層55Aは、配線52A、52Dを有する。また、ビアホール25内のCu膜28に電気的に接続される導電性プラグ51Dが複数形成される。この後、第2配線層55Aの上に、第3配線層60を形成する。第3配線層60は、配線64Cが導電性プラグ51Dを介して、ビアホール25内のCu膜28に電気的に接続される。この変形例では、ビアホール25にCu膜28を埋め込んだ貫通電極110は、第2配線層55Aの配線52A,52Dとは、直接には接続されない。これに対して、第3配線層60の配線64Cは、導電性プラグ51D,63Cを介して貫通電極110に電気的に接続される。

【0052】

また、第4配線層70Aの配線74A,74Dは、ビアホール25内のCu膜28には直接には接続されない。これに対して、第5配線層80の配線84Cは、導電性プラグ51D,63C,73D,83Cを介して貫通電極110に電気的に接続される。従って、図3に示す例では、第3配線層60の配線64Cと、第5配線層80の配線84Cのみがビアホール25内のCu膜28に直接に接続される。このように、貫通電極110は、シリコン基板1の上方に形成される多層配線構造の少なくとも1つの配線と接続される。このような変形例においても、前記と同様の効果が得られる。

【0053】

(第2の実施の形態)

第2の実施の形態について図面を参照して詳細に説明する。第1の実施の形態と同様の構成要素は同じ符号を付している。また、第1の実施の形態と重複する説明は、省略する。

【0054】

まず、図4Aに示す断面構造を得るまでの工程について説明する。

シリコン基板1上には、半導体素子であるトランジスタT1,T2を形成する。さらに、シリコン基板1及びトランジスタT1,T2を覆うように、第1の絶縁膜として絶縁膜14を形成する。この後、絶縁膜14の全面にレジスト膜を用いたマスク23Aを形成する。さらに、マスク23Aを用いて絶縁膜14及びシリコン基板1をドライエッチングして貫通電極用のビアホール25を形成する。ビアホール25の大きさは、例えば幅が20μm、深さが数10μmとする。ビアホール25の形成後には、マスク23Aを例えばアッシングによって除去する。

【0055】

図4Bに示すように、絶縁膜14の全面及びビアホール25の内面にバリアメタル膜として例えば酸化膜26をプラズマCVD法によって200nmの厚さに形成する。この場合、ビアホール25の側壁には、酸化膜26が100nm程度の膜厚に形成される。酸化膜26は、プラズマCVD法によって形成したSiN膜でも良い。

【0056】

さらに、酸化膜26を覆うように、例えば、TaN膜27をスパッタ法によって150nmの厚さに形成する。この後、TaN膜27上に、Cu膜28をメッキ法によって例えば10μmの厚さに形成する。これによって、ビアホール25にCu膜28が埋め込まれる。

【0057】

続いて、図4Cに示す断面構造を得るまでの工程について説明する。

最初に、Cu膜28の表面に硫酸過水溶液を滴下しながらシリコン基板1をスピンコーターで回転させて、Cu膜28を所定の厚さ、例えば1μm程度の厚さまでエッチングする。さらに、残りのCu膜28、TaN膜27、及び酸化膜26をCMP法によって研磨する。図4Cに破線で示すように、CMPを用いた研磨では、酸化膜26を上方から研磨して、膜厚を薄くする。たとえば、酸化膜26を50nm程度除去した段階で研磨を終了

し、シリコン基板1の上方に例えば、150nm程度の酸化膜26Bを残す。

【0058】

さらに、図4Dに示す断面構造を得るまでの工程について説明する。

まず、酸化膜26B及び絶縁膜14をドライエッチングしてコンタクトホール15からなるパターンを形成する。コンタクトホール15の径は、例えば0.25μmとする。ソース/ドレイン拡散層11のソース/ドレイン電極12Aに到達するまでとする。ドライエッチングは、酸化膜26B上に形成した不図示のマスクを用いる。さらに、酸化膜26Bをドライエッチングのハードマスクとして使用する。これによって、膜厚が例えば20nm〜50nmに減少した酸化膜26Cが形成される。酸化膜26Cをハードマスクとして使用するので、絶縁膜14のプラズマダメージが抑えられる。

【0059】

次に、図4Eに示すように、コンタクトホール15の内面及び酸化膜26C、Cu膜28の上に、例えば、密着膜16Aをスパッタ法によって150nmの厚さに形成する。この後、密着膜16A上に、第2の導電材としてW膜16Bをメッキ法によって例えば10μmの厚さに形成する。これによって、ビアホール25にW膜16Bが埋め込まれる。これにより、W膜16Bでコンタクトホール15の空隙が埋まる。

【0060】

この後、図4Fに示すように、絶縁膜14の上面上に成長した余分なW膜16B及び密着膜16AをCMP法で除去する。このときに、残りの酸化膜26Cの全てと、酸化膜26Cの下の絶縁膜14を20nm程度研磨する。ここまでのプロセスで酸化膜26Cの膜厚は、20nm〜50nm程度まで減少させられているので、少ない研磨時間で酸化膜26Cを確実に除去できる。ここまでの工程で、各コンタクトホール15に、導電性プラグ16が1つずつ形成される。

【0061】

次に、図4Gに示す断面構造を得るまでの工程について説明する。

絶縁膜14の上に、第1配線層40Aを形成する。第1配線層40Aは、最初に酸化防止絶縁膜141を形成する。酸化防止絶縁膜141の上には、第1層間絶縁膜142を形成する。第1層間絶縁膜142には、導電性プラグ16及びビアホール25のCu膜28に電気的に接続される導電性プラグ143A,143Cと、第1の配線144A,144Cが形成される。以降は、第2配線層55、第3配線層60、第4配線層70、第5配線層80を順番に形成する。

【0062】

さらに、第5配線層80の上に、酸化膜91を形成する。酸化膜91をエッチングしてビアホール93を形成する。

【0063】

ビアホール93を含む酸化膜91の全面に、積層膜として例えばTa膜、Ti膜、TiN膜を順番にスパッタ法にて形成する。さらに、ビアホール93を埋めるように、Al膜95を例えばスパッタ法を用いて形成する。Al膜95をエッチングして、Alの配線96を形成する。

【0064】

さらに、Alの配線96及び酸化膜91の上に、SiN膜97を例えばプラズマCVD法にて約200nmの厚さに形成する。SiN膜97の上には、SIO膜98を例えばプラズマCVD法にて約1.5μmの厚さに形成する。SIO膜98をエッチングして、ビアホール99を形成する。さらに、シリコン基板1をスピンコーターで回転させながら、SIO膜98及び配線96の上に、ポリイミド樹脂を塗布する。ポリイミド膜を硬化させてポリイミド層100を形成した後、レジスト膜から形成したマスクを用いてポリイミド膜をパターニングする。さらに、ビアホール99内にバンプ101を形成する。これによって、第5層の一部の配線83が、Alの配線96を介してバンプ101に電気的に接続される。

【0065】

この後、バックグラインダでシリコン基板1の裏面を研磨する。研磨は、スルービアホール25内のCu膜28がシリコン基板1の裏面に露出するまで行う。これにより、シリコン基板1を貫通する貫通電極110が形成される。

【0066】

次に、図4Hに示す断面構造を得るまでの工程について説明する。

シリコン基板1の裏面の全面にポリイミド樹脂を塗布し、硬化させることでポリイミド層111を形成する。さらに、ポリイミド層111をパターニングして貫通電極110を露出させた後、貫通電極110の裏面側の端面にバンプ112を電気的に接続する。これによって、半導体装置120Aが形成される。

【0067】

以上、説明したように、この半導体装置の製造方法では、貫通電極110を形成する過程で絶縁膜14の上に形成される酸化膜26を段階的に除去するので、酸化膜26が絶縁膜14上に残留したり、絶縁膜14がオーバーエッチングされたりすることが防止される。

【0068】

ここで、コンタクトホール15のドライエッチング時に酸化膜26Bを全て除去しても良い。例えば、配線溝32〜34が浅い場合など、Cu膜36の埋め込み不良が生じない場合には、酸化膜26Bの膜厚を減少させることなくコンタクトホール15を形成し、W膜16Aをコンタクトホール15に埋め込んだ後に研磨にて酸化膜26Bを除去しても良い。貫通電極110は、シリコン基板1の上方に形成される多層配線構造の少なくとも1つの配線と接続される。

【0069】

また、絶縁膜14にコンタクトホール15及び導電性プラグ16を形成した後に、ビアホール25の形成と、Cu膜28の埋め込みを行っても良い。この場合は、CMP法による研磨と、ドライエッチングと、CMP法による研磨とを順番に実行して酸化膜26を段階的に除去する。また、CMP法による研磨と、ドライエッチングを順番に実行して酸化膜26を段階的に除去しても良い。

【0070】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができる。

【0071】

以下に、前記の実施の形態の特徴を付記する。

(付記1) 基板の一方の面上に半導体素子を形成する工程と、前記半導体素子の上方に第1の絶縁膜を形成する工程と、前記第1の絶縁膜を貫通し、前記基板にホールを形成する工程と、前記第1の絶縁膜上及び前記ホールの内壁に第2の絶縁膜を形成する工程と、前記ホール内に第1の導電膜を埋める工程と、前記第1の絶縁膜上の前記第1の導電膜と、前記第2の絶縁膜の一部を研磨によって除去する工程と、前記第2の絶縁膜と前記第1の絶縁膜をエッチングしてパターンを形成する工程と、前記パターンに第2の導電膜を埋め込む工程と、前記第1の絶縁膜の上方の前記第2の導体膜と、残りの前記第2の絶縁膜を研磨により除去し、前記第1の絶縁膜を露出させる工程と、前記基板の厚さを他方の面から減少させ、前記ホール内に埋めた前記第1の導電膜を露出させる工程と、を含むことを特徴とする半導体装置の製造方法。

(付記2) 前記パターンを形成する工程は、前記第2の絶縁膜の膜厚をエッチングにより減少させる工程を含むことを特徴とする付記1に記載の半導体装置の製造方法。

(付記3) 前記第1の絶縁膜を形成する工程は、前記半導体素子に電気的に接続されるプラグを埋め込んだ膜上に前記第1の絶縁膜を形成する工程であり、前記パターンに第2

の導電膜を埋め込む工程は、前記第プラグと電気的に接続される配線溝を形成する工程を含むことを特徴とする付記1又は付記2に記載の半導体装置の製造方法。

(付記4) 前記ホールを形成する工程は、前記プラグを埋め込んだ前記膜を貫通して前記基板に前記ホールを形成する工程であることを特徴とする付記3に記載の半導体装置の製造方法。

(付記5) 前記第1の絶縁膜及び前記第2の導電膜の上に、前記第3の絶縁膜を形成する工程と、前記第3の絶縁膜に、前記第2の導電膜と電気的に接続する配線を形成する工程と、を含む付記3又は付記4に記載の半導体装置の製造方法。

(付記6) 前記第1の絶縁膜は、前記半導体素子の上に形成され、前記パターンに第2の導電膜を埋め込む工程は、前記半導体素子に電気的に接続されるプラグを形成する工程を含むことを特徴とする付記1又は付記2に記載の半導体装置の製造方法。

(付記7) 前記第1の絶縁膜を研磨によって露出させた後、前記第1の絶縁膜の上方に複数の配線層を形成する工程を含み、前記複数の配線層を形成した後に、前記基板の厚さを他方の面から減少させ、前記ホール内に埋めた前記第1の導電膜を露出させることを特徴とする付記1乃至6のいずれか一項に記載の半導体装置の製造方法。

(付記8) 前記第1の導電膜と前記第2の導電膜が前記複数の配線層の少なくとも一部でコンタクトしていることを特徴とする付記7に記載の半導体装置の製造方法。

(付記9) 基板の一方の面上に半導体素子を形成する工程と、前記半導体素子の上方に第1の絶縁膜を形成する工程と、前記第1の絶縁膜を貫通し、前記基板にホールを形成する工程と、前記第1の絶縁膜上、及び前記ホールの内壁に第2の絶縁膜を形成する工程と、前記ホールに導電材を埋め込む工程と、前記第1の絶縁膜上の前記導電材及び前記第2の絶縁膜を研磨し、前記第1の絶縁膜上の前記第2の絶縁膜を第1の膜厚に研磨する工程と、前記第1の絶縁膜上の第2の絶縁膜をエッチングよって第1の膜厚より薄い第2の膜厚にする工程と、第2の膜厚の第2の絶縁膜を研磨によって前記第1の絶縁膜上から除去する工程と、前記基板の上方に、前記導電材と電気的に接続される配線を形成した後、前記基板の厚さを他方の面側から減少させ、前記第1の導電膜を露出させる工程と、を含む半導体装置の製造方法。

(付記10) 前記第1の絶縁膜にパターンを形成する工程を有し、前記第1の絶縁膜をエッチングするときに、前記第2の絶縁膜を第2の膜厚にすることを特徴とする付記9に記載の半導体装置の製造方法。

(付記11) 前記第1の絶縁膜に配線材料を埋め込んで配線を形成する工程を有し、前記配線材料を研磨するときに、第2の膜厚の第2の絶縁膜を研磨によって前記第1の絶縁膜上から除去することを特徴とする付記9又は付記10に記載の半導体装置の製造方法。

【符号の説明】

【0072】

1 シリコン基板

14 絶縁膜(第1の絶縁膜)

15 コンタクトホール(パターン)

16 導電性プラグ

16B W膜(第2の導電材)

22 第1層間絶縁膜

25 ビアホール

26,26B,26C 酸化膜(第2の絶縁膜)

28 Cu膜(第1の導電膜)

32,33,34 配線溝(パターン)

36 Cu膜(第2の導電材)

40 第1配線層

55 第2配線層

60 第3配線層

70 第4配線層

80 第5配線層

T1,T2 半導体素子

【特許請求の範囲】

【請求項1】

基板の一方の面上に半導体素子を形成する工程と、

前記半導体素子の上方に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜を貫通し、前記基板にホールを形成する工程と、

前記第1の絶縁膜上及び前記ホールの内壁に第2の絶縁膜を形成する工程と、

前記ホール内に第1の導電材を埋める工程と、

前記第1の絶縁膜上の前記第1の導電材と、前記第2の絶縁膜の一部を研磨によって除去する工程と、

前記第2の絶縁膜と前記第1の絶縁膜をエッチングしてパターンを形成する工程と、

前記パターンに第2の導電材を埋め込む工程と、

前記第1の絶縁膜の上方の前記第2の導電材と、残りの前記第2の絶縁膜を研磨により除去し、前記第1の絶縁膜を露出させる工程と、

前記基板の厚さを他方の面から減少させ、前記ホール内に埋めた前記第1の導電材を露出させる工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記パターンを形成する工程は、前記第2の絶縁膜の膜厚をエッチングにより減少させる工程を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1の絶縁膜を形成する工程は、前記半導体素子に電気的に接続されるプラグを埋め込んだ膜上に前記第1の絶縁膜を形成する工程であり、

前記パターンに第2の導電材を埋め込む工程は、前記第プラグと電気的に接続される配線溝を形成する工程を含むことを特徴とする請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項4】

前記ホールを形成する工程は、前記プラグを埋め込んだ前記膜を貫通して前記基板に前記ホールを形成する工程であることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記第1の絶縁膜及び前記第2の導電材の上に、前記第3の絶縁膜を形成する工程と、

前記第3の絶縁膜に、前記第2の導電材と電気的に接続する配線を形成する工程と、

を含む請求項3又は請求項4に記載の半導体装置の製造方法。

【請求項6】

前記第1の絶縁膜は、前記半導体素子の上に形成され、前記パターンに第2の導電材を埋め込む工程は、前記半導体素子に電気的に接続されるプラグを形成する工程を含むことを特徴とする請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項7】

前記第1の絶縁膜を研磨によって露出させた後、前記第1の絶縁膜の上方に複数の配線層を形成する工程を含み、前記複数の配線層を形成した後に、前記基板の厚さを他方の面から減少させ、前記ホール内に埋めた前記第1の導電材を露出させることを特徴とする請求項1乃至6のいずれか一項に記載の半導体装置の製造方法。

【請求項8】

前記第1の導電材と前記第2の導電材が前記複数の配線層の少なくとも一部でコンタクトしていることを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項1】

基板の一方の面上に半導体素子を形成する工程と、

前記半導体素子の上方に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜を貫通し、前記基板にホールを形成する工程と、

前記第1の絶縁膜上及び前記ホールの内壁に第2の絶縁膜を形成する工程と、

前記ホール内に第1の導電材を埋める工程と、

前記第1の絶縁膜上の前記第1の導電材と、前記第2の絶縁膜の一部を研磨によって除去する工程と、

前記第2の絶縁膜と前記第1の絶縁膜をエッチングしてパターンを形成する工程と、

前記パターンに第2の導電材を埋め込む工程と、

前記第1の絶縁膜の上方の前記第2の導電材と、残りの前記第2の絶縁膜を研磨により除去し、前記第1の絶縁膜を露出させる工程と、

前記基板の厚さを他方の面から減少させ、前記ホール内に埋めた前記第1の導電材を露出させる工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

前記パターンを形成する工程は、前記第2の絶縁膜の膜厚をエッチングにより減少させる工程を含むことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1の絶縁膜を形成する工程は、前記半導体素子に電気的に接続されるプラグを埋め込んだ膜上に前記第1の絶縁膜を形成する工程であり、

前記パターンに第2の導電材を埋め込む工程は、前記第プラグと電気的に接続される配線溝を形成する工程を含むことを特徴とする請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項4】

前記ホールを形成する工程は、前記プラグを埋め込んだ前記膜を貫通して前記基板に前記ホールを形成する工程であることを特徴とする請求項3に記載の半導体装置の製造方法。

【請求項5】

前記第1の絶縁膜及び前記第2の導電材の上に、前記第3の絶縁膜を形成する工程と、

前記第3の絶縁膜に、前記第2の導電材と電気的に接続する配線を形成する工程と、

を含む請求項3又は請求項4に記載の半導体装置の製造方法。

【請求項6】

前記第1の絶縁膜は、前記半導体素子の上に形成され、前記パターンに第2の導電材を埋め込む工程は、前記半導体素子に電気的に接続されるプラグを形成する工程を含むことを特徴とする請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項7】

前記第1の絶縁膜を研磨によって露出させた後、前記第1の絶縁膜の上方に複数の配線層を形成する工程を含み、前記複数の配線層を形成した後に、前記基板の厚さを他方の面から減少させ、前記ホール内に埋めた前記第1の導電材を露出させることを特徴とする請求項1乃至6のいずれか一項に記載の半導体装置の製造方法。

【請求項8】

前記第1の導電材と前記第2の導電材が前記複数の配線層の少なくとも一部でコンタクトしていることを特徴とする請求項7に記載の半導体装置の製造方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図1J】

【図1K】

【図1L】

【図1M】

【図1N】

【図1O】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図4G】

【図4H】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図1J】

【図1K】

【図1L】

【図1M】

【図1N】

【図1O】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図4G】

【図4H】

【公開番号】特開2012−234887(P2012−234887A)

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願番号】特願2011−100820(P2011−100820)

【出願日】平成23年4月28日(2011.4.28)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願日】平成23年4月28日(2011.4.28)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]