半導体装置の製造方法

【課題】電極パターンが基板支持台に直接押し付けられることによって生じる電極パターンへのダメージの発生を防止することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板40の表面S1上に電極パターン41が形成される。半導体基板40の表面S1上において電極パターン41を覆う絶縁膜43が形成される。成膜装置の基板支持台100上に、絶縁膜43が基板支持台100に接するように半導体基板40が取り付けられる。基板支持台100に取り付けられた半導体基板40の裏面上に成膜装置によって電極層44が堆積される。電極層44が堆積された後に、電極パターン41の少なくとも一部が露出するように絶縁膜43がパターニングされる。

【解決手段】半導体基板40の表面S1上に電極パターン41が形成される。半導体基板40の表面S1上において電極パターン41を覆う絶縁膜43が形成される。成膜装置の基板支持台100上に、絶縁膜43が基板支持台100に接するように半導体基板40が取り付けられる。基板支持台100に取り付けられた半導体基板40の裏面上に成膜装置によって電極層44が堆積される。電極層44が堆積された後に、電極パターン41の少なくとも一部が露出するように絶縁膜43がパターニングされる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関するものであり、特に、半導体基板の表面および裏面の各々の上に設けられた電極を有する半導体装置の製造方法に関するものである。

【背景技術】

【0002】

特開2009−176882号公報によれば、MOS(Metal Oxide Semiconductor)セル領域およびガードリング領域を有するIGBT(Insulated Gate Bipolar Transistor)が開示されている。その製造方法において、半導体基板の表面上にアルミ電極が形成される。ガードリング領域においては、アルミ電極を保護するため、ガラスコート膜が形成される。次に半導体基板の裏面側に裏面電極が形成される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−176882号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記公報に記載の技術によれば、裏面電極が形成される際に、半導体基板の表面上のアルミ電極はMOSセル領域において露出している。よって裏面電極が形成される際にMOSセル領域においてアルミ電極にダメージが生じることがあった。具体的には、裏面電極の成膜のために半導体基板の表面が基板支持台によって支持される際に、成膜装置の基板支持台による圧迫によってMOSセル領域のアルミ電極に痕跡が残ることがあった。このような痕跡があると、外観検査において半導体装置が不良品と判断されたり、あるいは半導体装置の信頼性が低下したりすることがあった。

【0005】

本発明は、上記の課題に鑑みてなされたものであり、その目的は、電極パターンが基板支持台に直接押し付けられることによって生じる電極パターンへのダメージの発生を防止することができる半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0006】

本発明の半導体装置の製造方法は、以下の工程を有する。

半導体基板の表面上に電極パターンが形成される。半導体基板の表面上において電極パターンを覆う絶縁膜が形成される。成膜装置の基板支持台上に、絶縁膜が基板支持台に接するように半導体基板が取り付けられる。基板支持台に取り付けられた半導体基板の裏面上に成膜装置によって電極層が堆積される。電極層が堆積された後に、電極パターンの少なくとも一部が露出するように絶縁膜がパターニングされる。

【0007】

なお絶縁膜は半絶縁膜であってもよい。

【発明の効果】

【0008】

本発明によれば、電極パターンを覆う絶縁膜のパターニングは、電極層を堆積した後に行われる。これにより、絶縁膜のパターニングによって露出される電極パターンは、電極層が堆積される際にはまだ絶縁膜によって覆われており、よって基板支持台に直接押し付けられることがない。よって電極パターンが基板支持台に直接押し付けられることによって生じる電極パターンへのダメージの発生を防止することができる。

【図面の簡単な説明】

【0009】

【図1】本発明の実施の形態1における半導体装置の構成を概略的に示す部分平面図である。

【図2】図1の線II−IIに沿う概略的な部分断面図である。

【図3】本発明の実施の形態1における半導体装置の製造方法の第1工程を概略的に示す平面図である。

【図4】本発明の実施の形態1における半導体装置の製造方法の第2工程を概略的に示す部分断面図である。

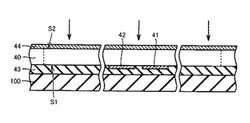

【図5】本発明の実施の形態1における半導体装置の製造方法の第3工程を概略的に示す部分断面図である。

【図6】本発明の実施の形態1における半導体装置の製造方法の第4工程を概略的に示す部分断面図である。

【図7】本発明の実施の形態1における半導体装置の製造方法の第5工程を概略的に示す部分断面図である。

【図8】本発明の実施の形態1における半導体装置の製造方法の第6工程を概略的に示す部分断面図である。

【図9】本発明の実施の形態1における半導体装置の製造方法の第7工程を概略的に示す部分断面図である。

【図10】本発明の実施の形態1における半導体装置の製造方法の第8工程を概略的に示す部分断面図である。

【図11】本発明の実施の形態1における半導体装置の製造方法の第9工程を概略的に示す部分断面図である。

【図12】本発明の実施の形態1における半導体装置の製造方法の第10工程を概略的に示す部分断面図である。

【図13】本発明の実施の形態1における半導体装置の製造方法の第11工程を概略的に示す部分断面図である。

【図14】本発明の実施の形態1における半導体装置の製造方法の第12工程を概略的に示す部分断面図である。

【図15】本発明の実施の形態1における半導体装置の製造方法の第15工程を概略的に示す平面図である。

【図16】本発明の実施の形態1における半導体装置の製造方法の第16工程を概略的に示す断面図である。

【図17】本発明の実施の形態2における半導体装置の製造方法の第1工程を概略的に示す断面図である。

【図18】本発明の実施の形態2における半導体装置の製造方法の第2工程を概略的に示す部分断面図である。

【図19】本発明の実施の形態2における半導体装置の製造方法の第3工程を概略的に示す部分断面図である。

【図20】本発明の実施の形態2における半導体装置の製造方法の第4工程を概略的に示す部分断面図である。

【図21】本発明の実施の形態2における半導体装置の製造方法の第5工程を概略的に示す部分断面図である。

【図22】本発明の実施の形態2における半導体装置の製造方法の第6工程を概略的に示す部分断面図である。

【図23】本発明の実施の形態2における半導体装置の製造方法の第7工程を概略的に示す部分断面図である。

【図24】本発明の実施の形態2における半導体装置の製造方法の第8工程を概略的に示す部分断面図である。

【図25】本発明の実施の形態3における半導体装置の製造方法の第1工程を概略的に示す部分断面図である。

【図26】本発明の実施の形態3における半導体装置の製造方法の第2工程を概略的に示す部分断面図である。

【図27】本発明の実施の形態4における半導体装置の構成を概略的に示す部分断面図である。

【図28】本発明の実施の形態4における半導体装置の製造方法の第1工程を概略的に示す部分断面図である。

【図29】本発明の実施の形態4における半導体装置の製造方法の第2工程を概略的に示す部分断面図である。

【図30】本発明の実施の形態4における半導体装置の製造方法の第3工程を概略的に示す部分断面図である。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態について図に基づいて説明する。

(実施の形態1)

図1および図2を参照して、本実施の形態の半導体装置91は、回路基板90と、半導体素子81と、ボンディングワイヤ61および62とを有する。半導体素子81は、たとえば、IGBT、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)、またはダイオードである。半導体素子81は、好ましくは電力用半導体素子である。また半導体素子81は、好ましくは、縦型素子である。

【0011】

半導体素子81は、半導体基板40と、裏面電極44(電極層)と、表面電極41および42(電極パターン)と、めっき膜51および52と、保護膜43(絶縁膜)とを有する。半導体基板40は、互いに対向する表面S1および裏面S2を有する。また半導体基板40は、平面視(図1)において、セル領域CLおよびガードリング領域GRを有する。ガードリング領域GRはセル領域CLを囲んでいる。セル領域CLは、半導体素子81の主要部であり、半導体素子81がスイッチング素子である場合、その主電流のスイッチングが行われる領域を含む。ガードリング領域GRは、半導体素子81の耐圧を向上させるためのものである。ガードリング領域GRにおける表面S1上には、ガードリング(図示せず)が形成されている。

【0012】

半導体基板40の裏面S2上には裏面電極44が形成されている。裏面電極44は、通常、積極的なパターニングがなされておらず、裏面S2のほぼ全体を覆っていてもよい。半導体素子81は、裏面電極44が回路基板90上に接合されることによって、回路基板90にダイボンディングされている。

【0013】

半導体基板40の表面S1上には表面電極41および42が形成されている。表面電極41および42の各々は、表面S1の一部の上に設けられている。表面電極41および42の材料は、たとえばアルミニウムである。

【0014】

表面電極41および42が形成された表面S1を覆うように保護膜43が形成されている。保護膜43は、表面電極41および42の各々の少なくとも一部を露出するように、開口部P1を有する。表面電極41を露出する開口部P1内において表面電極41上にめっき膜51が形成されており、また表面電極42を露出する開口部P1内において表面電極42上にめっき膜52が形成されている。開口部P1の内壁はオーバーハングした部分を有し、この部分の下方にできた空間の少なくとも一部がめっき膜51または52によって埋められている。

【0015】

保護膜43は絶縁膜である。絶縁膜は半絶縁膜であってもよく、具体的には半絶縁性シリコン窒化膜(sinSiN(Semi-Insulated Silicon Nitride))であってもよい。あるいは保護膜43は半絶縁膜でない通常の絶縁膜であってもよく、具体的にはポリイミド膜であってもよい。また絶縁膜はガラス膜であってもよい。

【0016】

ボンディングワイヤ61の一方端はめっき膜51を介して表面電極41に接続されており、またボンディングワイヤ62の一方端はめっき膜52を介して表面電極42に接続されている。ボンディングワイヤ61および62の各々の他方端は、半導体装置91が有する他の部材(図示せず)に接続されていてもよい。この他の部材は、たとえば、電極基板、または他の半導体素子である。他の半導体素子は、たとえば還流ダイオードである。

【0017】

次に半導体装置91の製造方法について説明する。

図3を参照して、半導体基板40としての半導体ウエハが準備される。次に半導体ウエハに複数のチップ領域CHが形成される。たとえば半導体素子81がIGBTまたはMOSFETの場合、チップ領域CHを形成する工程は、ゲート絶縁膜を形成する工程を含む。また複数のチップ領域CHを形成する工程は、各チップ領域CHにおいてセル領域CLおよびガードリング領域GRを形成する工程を含む。

【0018】

図4を参照して、半導体基板40の表面S1上に表面電極41および42が形成される。たとえば、半導体基板40上へのアルミニウム膜の成膜と、そのパターニングとが行われる。

【0019】

図5を参照して、半導体基板40の表面S1上において表面電極41および42を覆う保護膜43が形成される。

【0020】

図6を参照して、基板支持台100を有する成膜装置が準備される。成膜装置は、たとえばスパッタリング成膜装置である。この成膜装置の基板支持台100上に、保護膜43が基板支持台100に接するように、半導体基板40が取り付けられる。好ましくは基板支持台100は、半導体基板40と基板支持台100とが互いに押し付け合うように構成されており、たとえば、静電チャック、真空チャック、または機械的チャックを有する。

【0021】

図7を参照して、基板支持台100に取り付けられた半導体基板40の裏面S2上に、図中矢印で示すように、成膜装置によって裏面電極44が堆積される。

【0022】

さらに図8を参照して、裏面電極44が形成された半導体基板40が、基板支持台100から取り外される。

【0023】

図9を参照して、保護膜43上にエッチングマスク200が載置される。エッチングマスク200は、表面電極41および42の各々の上方において貫通孔THを有する。エッチングマスク200の材料は、たとえばステンレス鋼である。

【0024】

図10を参照して、エッチングマスク200の貫通孔TH内にエッチング液300が入れられる。エッチング液300は、たとえばフッ素系のものである。

【0025】

図11を参照して、エッチングマスク200の貫通孔TH内に入れられたエッチング液300が保護膜43をウエットエッチングすることによって、表面電極41および42の各々の一部が露出するように保護膜43がパターニングされる。これにより保護膜43に開口部P1が形成される。ウエットエッチングは一般に等方的であり、よってサイドエッチングが生じる。開口部P1の内壁は、サイドエッチングに起因して、オーバーハングした部分を有する。

【0026】

さらに図12を参照して、エッチング液300が除去される。

図13を参照して、保護膜43がパターニングされることによって露出された表面電極41および42のそれぞれの上に、めっき膜51および52が形成される。めっき膜51および52の材料は、たとえばアルミニウムまたは銅である。

【0027】

さらに図14を参照して、エッチングマスク200が取り外される。

図15を参照して、半導体基板40がダイシングラインDLに沿ってダイシングされる。これにより複数のチップ領域CHが互いに分離される。

【0028】

図16を参照して、上記ダイシングによって、半導体素子81が得られる。

再び図1および図2を参照して、半導体素子81の回路基板90へのダイボンディングが行われる。次に半導体素子81のワイヤボンディングが行われる。具体的には、めっき膜51および52のそれぞれにボンディングワイヤ61および62が接続される。言い換えると、表面電極41上へめっき膜51を介してボンディングワイヤ61が接続され、また表面電極42上へめっき膜52を介してボンディングワイヤ62が接続される。これにより半導体装置91が得られる。

【0029】

本実施の形態によれば、表面電極41および42を覆う保護膜43のパターニング(図11)は、裏面電極44(図7)を堆積した後に行われる。これにより、保護膜43のパターニングによって露出される表面電極41および42は、裏面電極44が堆積される際にはまだ保護膜43によって覆われており、よって基板支持台100(図7)に直接押し付けられることがない。よって表面電極41および42が基板支持台100に直接押し付けられることによって生じる表面電極41および42へのダメージの発生を防止することができる。

【0030】

また保護膜43のエッチングによって露出された表面電極41および42のそれぞれの上にめっき膜51および52が形成される。これにより、保護膜43の開口部P1の内壁がオーバーハングすることによって形成された隙間、言い換えると、保護膜43の表面と表面電極41および42のそれぞれとの間にサイドエッチングに起因して生じた隙間を、めっき膜51および52によって埋めることができる。ただしこの隙間が問題とならない場合は、めっき膜51および52の形成が省略されてもよい。なおこの隙間の大きさを抑制するには、保護膜43のエッチングに、より異方性の大きいエッチング法を用いればよい。

【0031】

なお本実施の形態においては、2つの表面電極41および42を有する半導体素子81について説明したが、表面電極41および42の数は任意である。半導体素子81がIGBTの場合、表面電極41および42のそれぞれがゲート電極およびエミッタ電極であってもよい。半導体素子81がMOSFETの場合、表面電極41および42のそれぞれが、ゲート電極およびソース電極であってもよい。半導体素子81がダイオードである場合、表面電極41および42の2つの電極の代わりに、1つのアノード電極またはカソード電極が設けられてもよい。

【0032】

また半導体素子81は終端構造としてガードリングを有するガードリング領域GRを含むが、ガードリングの代わりに他の終端構造が用いられてもよく、たとえばリサーフ(RESURF(Reduced Surface Field))構造を有するリサーフ領域が設けられてもよい。

【0033】

また保護膜43をエッチングするのに、ウエットエッチング法に代わってドライエッチング法が用いられてもよい。

【0034】

また保護膜43が半絶縁膜の場合、保護膜43中に微小な電流が流れ得るので、保護膜43が半絶縁膜でない絶縁膜の場合に比して、保護膜43内における電位差の発生を抑制することができる。これにより、ガードリング領域GRによる耐圧向上の効果をより高めることができる。

【0035】

(実施の形態2)

本実施の形態においては、まず図8に示す工程までが、実施の形態1と同様に行われる。

【0036】

図17を参照して、半導体基板40がダイシングされることで、複数のチップ領域CHが互いに分離される。

【0037】

図18を参照して、裏面電極44と回路基板90とが接合されることにより半導体基板40の裏面S2がダイボンディングされる。

【0038】

図19〜図24のそれぞれを参照して、図9〜図14とほぼ同様の工程が行われる。

図1および図2を参照して、実施の形態1と同様のワイヤボンディングが行われることで実施の形態1の半導体装置91とほぼ同様のものが得られる。

【0039】

本実施の形態によれば、裏面電極44が堆積された後、かつ保護膜43がパターニングされる前に、半導体基板40がダイシングされる。これにより、表面電極41および42を覆う保護膜43のパターニングは、ダイシング後に行われる。よって、保護膜43のパターニングによって露出される表面電極41および42は、ダイシングの際にはまだ保護膜43によって覆われている。よってダイシングの際に表面電極41および42に生じるダメージを防止することができる。

【0040】

また半導体基板40がダイシングされた後、かつ保護膜43がパターニングされる前に、半導体基板40の裏面がダイボンディングされる。これにより、表面電極41および42を覆う保護膜43のパターニングは、ダイボンディング後に行われる。よって、保護膜43のパターニングによって露出される表面電極41および42は、ダイボンディングの際にはまだ保護膜43によって覆われている。よってダイボンディングの際に表面電極41および42に生じるダメージを防止することができる。

【0041】

(実施の形態3)

本実施の形態においては、まず図8に示す工程までが、実施の形態1と同様に行われる。

【0042】

図25を参照して、表面電極41および42のそれぞれの上方において、保護膜43の上にエッチング液301が、図中矢印DRに示すように滴下される。エッチング液の滴下は、たとえば、エッチング液301の吐出装置201によって行われ得る。これにより保護膜43上の一部に選択的にエッチング液301が供給される。

【0043】

さらに図26を参照して、エッチング液301によるウエットエッチングにより保護膜43に、実施の形態1と同様、開口部P1が形成される。この後、めっき膜51および52の形成、ダイシング、ダイボンディング、およびワイヤボンディングが実施の形態1と同様に行われることで、実施の形態1の半導体装置91とほぼ同様のものが得られる。

【0044】

本実施の形態によれば、保護膜43の一部の上にエッチング液301(図25)を滴下することによって、部分的に保護膜43がエッチングされる。これにより、エッチングマスク200(図19)を用いることなく、保護膜43の一部をエッチングすることができる。

【0045】

なおはじめに実施の形態1の図8に示す工程までが行われる代わりに、実施の形態2の図18に示す工程までが行われてもよい。この場合、ダイシングされることによって互いに分離されたチップ領域CHの各々に形成された保護膜43上に、エッチング液301が滴下される。

【0046】

(実施の形態4)

図27を参照して、本実施の形態の半導体装置92は、半導体装置91(図2)の半導体素子81の代わりに、半導体素子82を有する。半導体素子82においては、保護膜43には、保護膜43の厚さ方向にほぼ平行な内壁を有する開口部P2が設けられている。なお半導体素子82にはめっき膜51および52(図2)が設けられていない。

【0047】

なお、上記以外の構成については、上述した実施の形態1の構成とほぼ同じであるため、同一または対応する要素について同一の符号を付し、その説明を繰り返さない。

【0048】

次に半導体装置92の製造方法について説明する。まず図8に示す工程までが実施の形態1と同様に行われる。

【0049】

図28を参照して、表面電極41および42のそれぞれの上方において保護膜43の上に粘着テープ401および402が貼り付けられる。

【0050】

図29を参照して、粘着テープ401および402のそれぞれを目標としてレーザ光403および404が照射される。

【0051】

さらに図30を参照して、レーザ光403および404によるレーザエッチングによって、粘着テープ401および402と、保護膜43のうち粘着テープ401および402が貼り付けられた部分とが除去される。これにより保護膜43に開口部P2が形成される。

【0052】

再び図27を参照して、ダイシング、ダイボンディング、およびワイヤボンディングが実施の形態1と同様に行われることで、半導体装置92が得られる。

【0053】

本実施の形態によれば保護膜43を非等方性エッチングによって加工することができる。これにより開口部P1(図2)におけるサイドエッチングを抑制することができる。よって実施の形態1において説明した隙間の形成を抑制することができる。

【0054】

なお本実施の形態においてはレーザ光403および404の照射の際に粘着テープ401および402が目標とされたが、粘着テープ401および402の代わりに他の目標物が設けられてもよく、たとえばエッチングマスク200(図9)を用いてその貫通孔THが目標とされてもよい。この場合、エッチングマスク200の貫通孔THによってレーザ光403および404の照射範囲が規制されてもよい。また保護膜43を介して表面電極41および42が十分に認識可能な場合は、目標物を別途設けることなく、レーザ光403および404が照射され得る。

【0055】

またはじめに実施の形態1の図8に示す工程までが行われる代わりに、実施の形態2の図18に示す工程までが行われてもよい。この場合、ダイシングされることによって互いに分離されたチップ領域CHの各々に形成された保護膜43上にレーザ光403および404が照射される。

【0056】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0057】

40 半導体基板、41,42 表面電極(電極パターン)、43 保護膜(絶縁膜)、44 裏面電極(電極層)、51,52 めっき膜、61,62 ボンディングワイヤ、81,82 半導体素子、90 回路基板、91,92 半導体装置、100 基板支持台、200 エッチングマスク、201 吐出装置、300,301 エッチング液、401,403 レーザ光、401,402 粘着テープ。

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関するものであり、特に、半導体基板の表面および裏面の各々の上に設けられた電極を有する半導体装置の製造方法に関するものである。

【背景技術】

【0002】

特開2009−176882号公報によれば、MOS(Metal Oxide Semiconductor)セル領域およびガードリング領域を有するIGBT(Insulated Gate Bipolar Transistor)が開示されている。その製造方法において、半導体基板の表面上にアルミ電極が形成される。ガードリング領域においては、アルミ電極を保護するため、ガラスコート膜が形成される。次に半導体基板の裏面側に裏面電極が形成される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−176882号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記公報に記載の技術によれば、裏面電極が形成される際に、半導体基板の表面上のアルミ電極はMOSセル領域において露出している。よって裏面電極が形成される際にMOSセル領域においてアルミ電極にダメージが生じることがあった。具体的には、裏面電極の成膜のために半導体基板の表面が基板支持台によって支持される際に、成膜装置の基板支持台による圧迫によってMOSセル領域のアルミ電極に痕跡が残ることがあった。このような痕跡があると、外観検査において半導体装置が不良品と判断されたり、あるいは半導体装置の信頼性が低下したりすることがあった。

【0005】

本発明は、上記の課題に鑑みてなされたものであり、その目的は、電極パターンが基板支持台に直接押し付けられることによって生じる電極パターンへのダメージの発生を防止することができる半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0006】

本発明の半導体装置の製造方法は、以下の工程を有する。

半導体基板の表面上に電極パターンが形成される。半導体基板の表面上において電極パターンを覆う絶縁膜が形成される。成膜装置の基板支持台上に、絶縁膜が基板支持台に接するように半導体基板が取り付けられる。基板支持台に取り付けられた半導体基板の裏面上に成膜装置によって電極層が堆積される。電極層が堆積された後に、電極パターンの少なくとも一部が露出するように絶縁膜がパターニングされる。

【0007】

なお絶縁膜は半絶縁膜であってもよい。

【発明の効果】

【0008】

本発明によれば、電極パターンを覆う絶縁膜のパターニングは、電極層を堆積した後に行われる。これにより、絶縁膜のパターニングによって露出される電極パターンは、電極層が堆積される際にはまだ絶縁膜によって覆われており、よって基板支持台に直接押し付けられることがない。よって電極パターンが基板支持台に直接押し付けられることによって生じる電極パターンへのダメージの発生を防止することができる。

【図面の簡単な説明】

【0009】

【図1】本発明の実施の形態1における半導体装置の構成を概略的に示す部分平面図である。

【図2】図1の線II−IIに沿う概略的な部分断面図である。

【図3】本発明の実施の形態1における半導体装置の製造方法の第1工程を概略的に示す平面図である。

【図4】本発明の実施の形態1における半導体装置の製造方法の第2工程を概略的に示す部分断面図である。

【図5】本発明の実施の形態1における半導体装置の製造方法の第3工程を概略的に示す部分断面図である。

【図6】本発明の実施の形態1における半導体装置の製造方法の第4工程を概略的に示す部分断面図である。

【図7】本発明の実施の形態1における半導体装置の製造方法の第5工程を概略的に示す部分断面図である。

【図8】本発明の実施の形態1における半導体装置の製造方法の第6工程を概略的に示す部分断面図である。

【図9】本発明の実施の形態1における半導体装置の製造方法の第7工程を概略的に示す部分断面図である。

【図10】本発明の実施の形態1における半導体装置の製造方法の第8工程を概略的に示す部分断面図である。

【図11】本発明の実施の形態1における半導体装置の製造方法の第9工程を概略的に示す部分断面図である。

【図12】本発明の実施の形態1における半導体装置の製造方法の第10工程を概略的に示す部分断面図である。

【図13】本発明の実施の形態1における半導体装置の製造方法の第11工程を概略的に示す部分断面図である。

【図14】本発明の実施の形態1における半導体装置の製造方法の第12工程を概略的に示す部分断面図である。

【図15】本発明の実施の形態1における半導体装置の製造方法の第15工程を概略的に示す平面図である。

【図16】本発明の実施の形態1における半導体装置の製造方法の第16工程を概略的に示す断面図である。

【図17】本発明の実施の形態2における半導体装置の製造方法の第1工程を概略的に示す断面図である。

【図18】本発明の実施の形態2における半導体装置の製造方法の第2工程を概略的に示す部分断面図である。

【図19】本発明の実施の形態2における半導体装置の製造方法の第3工程を概略的に示す部分断面図である。

【図20】本発明の実施の形態2における半導体装置の製造方法の第4工程を概略的に示す部分断面図である。

【図21】本発明の実施の形態2における半導体装置の製造方法の第5工程を概略的に示す部分断面図である。

【図22】本発明の実施の形態2における半導体装置の製造方法の第6工程を概略的に示す部分断面図である。

【図23】本発明の実施の形態2における半導体装置の製造方法の第7工程を概略的に示す部分断面図である。

【図24】本発明の実施の形態2における半導体装置の製造方法の第8工程を概略的に示す部分断面図である。

【図25】本発明の実施の形態3における半導体装置の製造方法の第1工程を概略的に示す部分断面図である。

【図26】本発明の実施の形態3における半導体装置の製造方法の第2工程を概略的に示す部分断面図である。

【図27】本発明の実施の形態4における半導体装置の構成を概略的に示す部分断面図である。

【図28】本発明の実施の形態4における半導体装置の製造方法の第1工程を概略的に示す部分断面図である。

【図29】本発明の実施の形態4における半導体装置の製造方法の第2工程を概略的に示す部分断面図である。

【図30】本発明の実施の形態4における半導体装置の製造方法の第3工程を概略的に示す部分断面図である。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態について図に基づいて説明する。

(実施の形態1)

図1および図2を参照して、本実施の形態の半導体装置91は、回路基板90と、半導体素子81と、ボンディングワイヤ61および62とを有する。半導体素子81は、たとえば、IGBT、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)、またはダイオードである。半導体素子81は、好ましくは電力用半導体素子である。また半導体素子81は、好ましくは、縦型素子である。

【0011】

半導体素子81は、半導体基板40と、裏面電極44(電極層)と、表面電極41および42(電極パターン)と、めっき膜51および52と、保護膜43(絶縁膜)とを有する。半導体基板40は、互いに対向する表面S1および裏面S2を有する。また半導体基板40は、平面視(図1)において、セル領域CLおよびガードリング領域GRを有する。ガードリング領域GRはセル領域CLを囲んでいる。セル領域CLは、半導体素子81の主要部であり、半導体素子81がスイッチング素子である場合、その主電流のスイッチングが行われる領域を含む。ガードリング領域GRは、半導体素子81の耐圧を向上させるためのものである。ガードリング領域GRにおける表面S1上には、ガードリング(図示せず)が形成されている。

【0012】

半導体基板40の裏面S2上には裏面電極44が形成されている。裏面電極44は、通常、積極的なパターニングがなされておらず、裏面S2のほぼ全体を覆っていてもよい。半導体素子81は、裏面電極44が回路基板90上に接合されることによって、回路基板90にダイボンディングされている。

【0013】

半導体基板40の表面S1上には表面電極41および42が形成されている。表面電極41および42の各々は、表面S1の一部の上に設けられている。表面電極41および42の材料は、たとえばアルミニウムである。

【0014】

表面電極41および42が形成された表面S1を覆うように保護膜43が形成されている。保護膜43は、表面電極41および42の各々の少なくとも一部を露出するように、開口部P1を有する。表面電極41を露出する開口部P1内において表面電極41上にめっき膜51が形成されており、また表面電極42を露出する開口部P1内において表面電極42上にめっき膜52が形成されている。開口部P1の内壁はオーバーハングした部分を有し、この部分の下方にできた空間の少なくとも一部がめっき膜51または52によって埋められている。

【0015】

保護膜43は絶縁膜である。絶縁膜は半絶縁膜であってもよく、具体的には半絶縁性シリコン窒化膜(sinSiN(Semi-Insulated Silicon Nitride))であってもよい。あるいは保護膜43は半絶縁膜でない通常の絶縁膜であってもよく、具体的にはポリイミド膜であってもよい。また絶縁膜はガラス膜であってもよい。

【0016】

ボンディングワイヤ61の一方端はめっき膜51を介して表面電極41に接続されており、またボンディングワイヤ62の一方端はめっき膜52を介して表面電極42に接続されている。ボンディングワイヤ61および62の各々の他方端は、半導体装置91が有する他の部材(図示せず)に接続されていてもよい。この他の部材は、たとえば、電極基板、または他の半導体素子である。他の半導体素子は、たとえば還流ダイオードである。

【0017】

次に半導体装置91の製造方法について説明する。

図3を参照して、半導体基板40としての半導体ウエハが準備される。次に半導体ウエハに複数のチップ領域CHが形成される。たとえば半導体素子81がIGBTまたはMOSFETの場合、チップ領域CHを形成する工程は、ゲート絶縁膜を形成する工程を含む。また複数のチップ領域CHを形成する工程は、各チップ領域CHにおいてセル領域CLおよびガードリング領域GRを形成する工程を含む。

【0018】

図4を参照して、半導体基板40の表面S1上に表面電極41および42が形成される。たとえば、半導体基板40上へのアルミニウム膜の成膜と、そのパターニングとが行われる。

【0019】

図5を参照して、半導体基板40の表面S1上において表面電極41および42を覆う保護膜43が形成される。

【0020】

図6を参照して、基板支持台100を有する成膜装置が準備される。成膜装置は、たとえばスパッタリング成膜装置である。この成膜装置の基板支持台100上に、保護膜43が基板支持台100に接するように、半導体基板40が取り付けられる。好ましくは基板支持台100は、半導体基板40と基板支持台100とが互いに押し付け合うように構成されており、たとえば、静電チャック、真空チャック、または機械的チャックを有する。

【0021】

図7を参照して、基板支持台100に取り付けられた半導体基板40の裏面S2上に、図中矢印で示すように、成膜装置によって裏面電極44が堆積される。

【0022】

さらに図8を参照して、裏面電極44が形成された半導体基板40が、基板支持台100から取り外される。

【0023】

図9を参照して、保護膜43上にエッチングマスク200が載置される。エッチングマスク200は、表面電極41および42の各々の上方において貫通孔THを有する。エッチングマスク200の材料は、たとえばステンレス鋼である。

【0024】

図10を参照して、エッチングマスク200の貫通孔TH内にエッチング液300が入れられる。エッチング液300は、たとえばフッ素系のものである。

【0025】

図11を参照して、エッチングマスク200の貫通孔TH内に入れられたエッチング液300が保護膜43をウエットエッチングすることによって、表面電極41および42の各々の一部が露出するように保護膜43がパターニングされる。これにより保護膜43に開口部P1が形成される。ウエットエッチングは一般に等方的であり、よってサイドエッチングが生じる。開口部P1の内壁は、サイドエッチングに起因して、オーバーハングした部分を有する。

【0026】

さらに図12を参照して、エッチング液300が除去される。

図13を参照して、保護膜43がパターニングされることによって露出された表面電極41および42のそれぞれの上に、めっき膜51および52が形成される。めっき膜51および52の材料は、たとえばアルミニウムまたは銅である。

【0027】

さらに図14を参照して、エッチングマスク200が取り外される。

図15を参照して、半導体基板40がダイシングラインDLに沿ってダイシングされる。これにより複数のチップ領域CHが互いに分離される。

【0028】

図16を参照して、上記ダイシングによって、半導体素子81が得られる。

再び図1および図2を参照して、半導体素子81の回路基板90へのダイボンディングが行われる。次に半導体素子81のワイヤボンディングが行われる。具体的には、めっき膜51および52のそれぞれにボンディングワイヤ61および62が接続される。言い換えると、表面電極41上へめっき膜51を介してボンディングワイヤ61が接続され、また表面電極42上へめっき膜52を介してボンディングワイヤ62が接続される。これにより半導体装置91が得られる。

【0029】

本実施の形態によれば、表面電極41および42を覆う保護膜43のパターニング(図11)は、裏面電極44(図7)を堆積した後に行われる。これにより、保護膜43のパターニングによって露出される表面電極41および42は、裏面電極44が堆積される際にはまだ保護膜43によって覆われており、よって基板支持台100(図7)に直接押し付けられることがない。よって表面電極41および42が基板支持台100に直接押し付けられることによって生じる表面電極41および42へのダメージの発生を防止することができる。

【0030】

また保護膜43のエッチングによって露出された表面電極41および42のそれぞれの上にめっき膜51および52が形成される。これにより、保護膜43の開口部P1の内壁がオーバーハングすることによって形成された隙間、言い換えると、保護膜43の表面と表面電極41および42のそれぞれとの間にサイドエッチングに起因して生じた隙間を、めっき膜51および52によって埋めることができる。ただしこの隙間が問題とならない場合は、めっき膜51および52の形成が省略されてもよい。なおこの隙間の大きさを抑制するには、保護膜43のエッチングに、より異方性の大きいエッチング法を用いればよい。

【0031】

なお本実施の形態においては、2つの表面電極41および42を有する半導体素子81について説明したが、表面電極41および42の数は任意である。半導体素子81がIGBTの場合、表面電極41および42のそれぞれがゲート電極およびエミッタ電極であってもよい。半導体素子81がMOSFETの場合、表面電極41および42のそれぞれが、ゲート電極およびソース電極であってもよい。半導体素子81がダイオードである場合、表面電極41および42の2つの電極の代わりに、1つのアノード電極またはカソード電極が設けられてもよい。

【0032】

また半導体素子81は終端構造としてガードリングを有するガードリング領域GRを含むが、ガードリングの代わりに他の終端構造が用いられてもよく、たとえばリサーフ(RESURF(Reduced Surface Field))構造を有するリサーフ領域が設けられてもよい。

【0033】

また保護膜43をエッチングするのに、ウエットエッチング法に代わってドライエッチング法が用いられてもよい。

【0034】

また保護膜43が半絶縁膜の場合、保護膜43中に微小な電流が流れ得るので、保護膜43が半絶縁膜でない絶縁膜の場合に比して、保護膜43内における電位差の発生を抑制することができる。これにより、ガードリング領域GRによる耐圧向上の効果をより高めることができる。

【0035】

(実施の形態2)

本実施の形態においては、まず図8に示す工程までが、実施の形態1と同様に行われる。

【0036】

図17を参照して、半導体基板40がダイシングされることで、複数のチップ領域CHが互いに分離される。

【0037】

図18を参照して、裏面電極44と回路基板90とが接合されることにより半導体基板40の裏面S2がダイボンディングされる。

【0038】

図19〜図24のそれぞれを参照して、図9〜図14とほぼ同様の工程が行われる。

図1および図2を参照して、実施の形態1と同様のワイヤボンディングが行われることで実施の形態1の半導体装置91とほぼ同様のものが得られる。

【0039】

本実施の形態によれば、裏面電極44が堆積された後、かつ保護膜43がパターニングされる前に、半導体基板40がダイシングされる。これにより、表面電極41および42を覆う保護膜43のパターニングは、ダイシング後に行われる。よって、保護膜43のパターニングによって露出される表面電極41および42は、ダイシングの際にはまだ保護膜43によって覆われている。よってダイシングの際に表面電極41および42に生じるダメージを防止することができる。

【0040】

また半導体基板40がダイシングされた後、かつ保護膜43がパターニングされる前に、半導体基板40の裏面がダイボンディングされる。これにより、表面電極41および42を覆う保護膜43のパターニングは、ダイボンディング後に行われる。よって、保護膜43のパターニングによって露出される表面電極41および42は、ダイボンディングの際にはまだ保護膜43によって覆われている。よってダイボンディングの際に表面電極41および42に生じるダメージを防止することができる。

【0041】

(実施の形態3)

本実施の形態においては、まず図8に示す工程までが、実施の形態1と同様に行われる。

【0042】

図25を参照して、表面電極41および42のそれぞれの上方において、保護膜43の上にエッチング液301が、図中矢印DRに示すように滴下される。エッチング液の滴下は、たとえば、エッチング液301の吐出装置201によって行われ得る。これにより保護膜43上の一部に選択的にエッチング液301が供給される。

【0043】

さらに図26を参照して、エッチング液301によるウエットエッチングにより保護膜43に、実施の形態1と同様、開口部P1が形成される。この後、めっき膜51および52の形成、ダイシング、ダイボンディング、およびワイヤボンディングが実施の形態1と同様に行われることで、実施の形態1の半導体装置91とほぼ同様のものが得られる。

【0044】

本実施の形態によれば、保護膜43の一部の上にエッチング液301(図25)を滴下することによって、部分的に保護膜43がエッチングされる。これにより、エッチングマスク200(図19)を用いることなく、保護膜43の一部をエッチングすることができる。

【0045】

なおはじめに実施の形態1の図8に示す工程までが行われる代わりに、実施の形態2の図18に示す工程までが行われてもよい。この場合、ダイシングされることによって互いに分離されたチップ領域CHの各々に形成された保護膜43上に、エッチング液301が滴下される。

【0046】

(実施の形態4)

図27を参照して、本実施の形態の半導体装置92は、半導体装置91(図2)の半導体素子81の代わりに、半導体素子82を有する。半導体素子82においては、保護膜43には、保護膜43の厚さ方向にほぼ平行な内壁を有する開口部P2が設けられている。なお半導体素子82にはめっき膜51および52(図2)が設けられていない。

【0047】

なお、上記以外の構成については、上述した実施の形態1の構成とほぼ同じであるため、同一または対応する要素について同一の符号を付し、その説明を繰り返さない。

【0048】

次に半導体装置92の製造方法について説明する。まず図8に示す工程までが実施の形態1と同様に行われる。

【0049】

図28を参照して、表面電極41および42のそれぞれの上方において保護膜43の上に粘着テープ401および402が貼り付けられる。

【0050】

図29を参照して、粘着テープ401および402のそれぞれを目標としてレーザ光403および404が照射される。

【0051】

さらに図30を参照して、レーザ光403および404によるレーザエッチングによって、粘着テープ401および402と、保護膜43のうち粘着テープ401および402が貼り付けられた部分とが除去される。これにより保護膜43に開口部P2が形成される。

【0052】

再び図27を参照して、ダイシング、ダイボンディング、およびワイヤボンディングが実施の形態1と同様に行われることで、半導体装置92が得られる。

【0053】

本実施の形態によれば保護膜43を非等方性エッチングによって加工することができる。これにより開口部P1(図2)におけるサイドエッチングを抑制することができる。よって実施の形態1において説明した隙間の形成を抑制することができる。

【0054】

なお本実施の形態においてはレーザ光403および404の照射の際に粘着テープ401および402が目標とされたが、粘着テープ401および402の代わりに他の目標物が設けられてもよく、たとえばエッチングマスク200(図9)を用いてその貫通孔THが目標とされてもよい。この場合、エッチングマスク200の貫通孔THによってレーザ光403および404の照射範囲が規制されてもよい。また保護膜43を介して表面電極41および42が十分に認識可能な場合は、目標物を別途設けることなく、レーザ光403および404が照射され得る。

【0055】

またはじめに実施の形態1の図8に示す工程までが行われる代わりに、実施の形態2の図18に示す工程までが行われてもよい。この場合、ダイシングされることによって互いに分離されたチップ領域CHの各々に形成された保護膜43上にレーザ光403および404が照射される。

【0056】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0057】

40 半導体基板、41,42 表面電極(電極パターン)、43 保護膜(絶縁膜)、44 裏面電極(電極層)、51,52 めっき膜、61,62 ボンディングワイヤ、81,82 半導体素子、90 回路基板、91,92 半導体装置、100 基板支持台、200 エッチングマスク、201 吐出装置、300,301 エッチング液、401,403 レーザ光、401,402 粘着テープ。

【特許請求の範囲】

【請求項1】

半導体基板の表面上に電極パターンを形成する工程と、

前記半導体基板の前記表面上において前記電極パターンを覆う絶縁膜を形成する工程と、

成膜装置の基板支持台上に、前記絶縁膜が前記基板支持台に接するように前記半導体基板を取り付ける工程と、

前記基板支持台に取り付けられた前記半導体基板の裏面上に前記成膜装置によって電極層を堆積する工程と、

前記電極層を堆積する工程の後に、前記電極パターンの少なくとも一部が露出するように前記絶縁膜をパターニングする工程とを備える、半導体装置の製造方法。

【請求項2】

前記電極層を堆積する工程の後、かつ前記絶縁膜をパターニングする工程の前に、前記半導体基板をダイシングする工程をさらに備える、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記半導体基板をダイシングする工程の後、かつ前記絶縁膜をパターニングする工程の前に、前記半導体基板の前記裏面をダイボンディングする工程をさらに備える、請求項2に記載の半導体装置の製造方法。

【請求項4】

前記絶縁膜をパターニングする工程によって露出された前記電極パターンの上へボンディングワイヤを接続する工程をさらに備える、請求項1〜3のいずれかに記載の半導体装置の製造方法。

【請求項5】

前記絶縁膜をパターニングする工程は、前記絶縁膜を等方的にエッチングする工程を含み、

前記絶縁膜をパターニングする工程の後に、前記絶縁膜をパターニングする工程によって露出された前記電極パターンの上にめっき膜を形成する工程をさらに備える、請求項1〜4のいずれかに記載の半導体装置の製造方法。

【請求項6】

前記絶縁膜をエッチングする工程は、前記絶縁膜上にエッチングマスクを設ける工程を含む、請求項5に記載の半導体装置の製造方法。

【請求項7】

前記絶縁膜をエッチングする工程は、前記絶縁膜の一部の上にエッチング液を滴下することによって部分的に前記絶縁膜をエッチングする工程を含む、請求項5に記載の半導体装置の製造方法。

【請求項8】

前記絶縁膜をパターニングする工程は、前記絶縁膜をレーザエッチングする工程を含む、請求項1〜4のいずれかに記載の半導体装置の製造方法。

【請求項9】

前記絶縁膜をレーザエッチングする工程は、

前記絶縁膜の一部に粘着テープを貼り付ける工程と、

レーザ光によって、前記粘着テープと、前記絶縁膜の前記粘着テープが貼り付けられた部分とを除去する工程とを含む、請求項8に記載の半導体装置の製造方法。

【請求項10】

前記絶縁膜は半絶縁性膜である、請求項1〜9のいずれかに記載の半導体装置の製造方法。

【請求項11】

前記絶縁膜はポリイミド膜である、請求項1〜9のいずれかに記載の半導体装置の製造方法。

【請求項1】

半導体基板の表面上に電極パターンを形成する工程と、

前記半導体基板の前記表面上において前記電極パターンを覆う絶縁膜を形成する工程と、

成膜装置の基板支持台上に、前記絶縁膜が前記基板支持台に接するように前記半導体基板を取り付ける工程と、

前記基板支持台に取り付けられた前記半導体基板の裏面上に前記成膜装置によって電極層を堆積する工程と、

前記電極層を堆積する工程の後に、前記電極パターンの少なくとも一部が露出するように前記絶縁膜をパターニングする工程とを備える、半導体装置の製造方法。

【請求項2】

前記電極層を堆積する工程の後、かつ前記絶縁膜をパターニングする工程の前に、前記半導体基板をダイシングする工程をさらに備える、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記半導体基板をダイシングする工程の後、かつ前記絶縁膜をパターニングする工程の前に、前記半導体基板の前記裏面をダイボンディングする工程をさらに備える、請求項2に記載の半導体装置の製造方法。

【請求項4】

前記絶縁膜をパターニングする工程によって露出された前記電極パターンの上へボンディングワイヤを接続する工程をさらに備える、請求項1〜3のいずれかに記載の半導体装置の製造方法。

【請求項5】

前記絶縁膜をパターニングする工程は、前記絶縁膜を等方的にエッチングする工程を含み、

前記絶縁膜をパターニングする工程の後に、前記絶縁膜をパターニングする工程によって露出された前記電極パターンの上にめっき膜を形成する工程をさらに備える、請求項1〜4のいずれかに記載の半導体装置の製造方法。

【請求項6】

前記絶縁膜をエッチングする工程は、前記絶縁膜上にエッチングマスクを設ける工程を含む、請求項5に記載の半導体装置の製造方法。

【請求項7】

前記絶縁膜をエッチングする工程は、前記絶縁膜の一部の上にエッチング液を滴下することによって部分的に前記絶縁膜をエッチングする工程を含む、請求項5に記載の半導体装置の製造方法。

【請求項8】

前記絶縁膜をパターニングする工程は、前記絶縁膜をレーザエッチングする工程を含む、請求項1〜4のいずれかに記載の半導体装置の製造方法。

【請求項9】

前記絶縁膜をレーザエッチングする工程は、

前記絶縁膜の一部に粘着テープを貼り付ける工程と、

レーザ光によって、前記粘着テープと、前記絶縁膜の前記粘着テープが貼り付けられた部分とを除去する工程とを含む、請求項8に記載の半導体装置の製造方法。

【請求項10】

前記絶縁膜は半絶縁性膜である、請求項1〜9のいずれかに記載の半導体装置の製造方法。

【請求項11】

前記絶縁膜はポリイミド膜である、請求項1〜9のいずれかに記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【公開番号】特開2012−235049(P2012−235049A)

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願番号】特願2011−104271(P2011−104271)

【出願日】平成23年5月9日(2011.5.9)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願日】平成23年5月9日(2011.5.9)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]