半導体装置の製造方法

【課題】基板のエッジ部分での膜剥がれを防止し、半導体装置を効率良く製造する。

【解決手段】基板1の上方に低誘電体膜31を形成する際に、基板1のエッジ部分1Aをエッジカット工程にて洗い流すことで段差部31Aが形成される。低誘電体膜31に配線溝41を形成した後、導電膜43を埋め込む。基板1のエッジ部分1Aの導電膜43を洗い流すと、導電膜43が埋め込まれていない配線溝41Aが形成される。配線溝41Aを保護フィルム51で覆ってから、CMP法にて余分な導電膜43を除去する。この後、保護フィルム51を基板1から取り外す。

【解決手段】基板1の上方に低誘電体膜31を形成する際に、基板1のエッジ部分1Aをエッジカット工程にて洗い流すことで段差部31Aが形成される。低誘電体膜31に配線溝41を形成した後、導電膜43を埋め込む。基板1のエッジ部分1Aの導電膜43を洗い流すと、導電膜43が埋め込まれていない配線溝41Aが形成される。配線溝41Aを保護フィルム51で覆ってから、CMP法にて余分な導電膜43を除去する。この後、保護フィルム51を基板1から取り外す。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の微細化及び動作の高速化を目的として、半導体回路の高集積化が進んでいる。これに伴って、半導体回路の配線幅や配線ピッチが縮小化している。配線幅や配線ピッチの縮小化は、半導体回路の配線抵抗の増加や、配線間容量の増加に原因になる。そこで、配線遅延の増大を防止する方法の一つとして、層間絶縁膜に低誘電率(Low−k)膜を用いた製造プロセスが開発されている。低誘電率の層間絶縁膜は、例えば、スピン塗布方式を用いて基板の表面に塗布した後に、加熱によって硬化させることで形成される。

【0003】

さらに、配線遅延の増大を防止する他の方法としては、低抵抗の配線金属材料を用いることがある。従来、配線材料はアルミニウム(Al)の利用が一般的であったが、半導体装置の微細化、動作の高速化に対してアルミニウムでは限界がある。そのため、エレクトロマイグレーションに強く、比抵抗の小さい銅(Cu)配線が必要になっている。ところが、銅膜は、ドライエッチングが困難である。このために、低誘電体膜に予め配線溝を形成し、硫酸銅めっき液を用いた電解めっき法で配線溝に銅膜を埋め込んだ後、低誘電体膜の表面の余分な銅膜をCMP(Chemical Mechanical Polishing)によって除去して配線の平坦化するダマシン工程(Cu−CMP工程)が採用される。

【0004】

ここで、スピン塗布方式を用いて低誘電体膜を形成すると、基板の周辺のエッジ部分に塗布材料が回り込むことがある。エッジ部分に形成された低誘電体膜は、後の工程などで、基板から剥がれることがあり、基板を搬送するカセットや、半導体製造装置を汚す原因になり易かった。そこで、塗布材料を基板に塗布した後に、エッジリンス工程を実施して基板のエッジ部分の塗布材料を洗い流す。これによって、塗布材料の回り込みが防止される。

【0005】

また、配線溝に銅膜を埋め込んだときは、他の半導体製造装置を金属汚染しないように、エッジリンス工程を実施する。エッジリンス工程では、基板のエッジ部分の銅膜が除去される。そのため、基板のエッジ部分に銅膜が埋め込まれていない配線溝が発生することがある。CMP法による銅膜の研磨では、基板のエッジ部分が研磨され易いので銅膜が埋め込まれていない配線溝が崩れ、低誘電体膜が剥がれることがある。基板から剥がれた低誘電体膜は、スクラッチ(研磨傷)や配線のショートの原因になり易い。

【0006】

そこで、従来の半導体装置の製造方法では、銅膜が埋め込まれていない配線溝の保護に剥離防止膜を用いることがある。具体的には、基板のエッジ部分の銅膜をエッジリンス工程によって除去した後、第1の研磨によって銅膜をバリア膜が露出するまで研磨する。次に、研磨面の全面に剥離防止膜を形成する。続いて、第2の研磨によって剥離防止膜とバリア膜を取り除く。これによって、基板のエッジ部分の配線溝のみの低誘電体膜の剥離が防止される。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2009−272560

【発明の概要】

【発明が解決しようとする課題】

【0008】

ここで、基板のエッジ部分の低誘電体膜を洗い流すと、基板上に低誘電体膜の端面による段差が形成される。段差には、銅膜のCMP時に他の領域よりも大きい研磨圧が作用し易い。このために、段差が大きくなると、段差部分の研磨圧の荷重が大きくなるので、膜が剥がれ易くなる。膜剥がれを防止するために研磨荷重を低下させると、研磨レートが低下するので、スループットが低下してしまう。

この発明は、このような事情に鑑みてなされたものであり、基板のエッジ部分での膜剥がれを防止し、半導体装置を効率良く製造できるようにすることを目的とする。

【課題を解決するための手段】

【0009】

実施形態の一観点によれば、基板の上方に塗布材料を塗布し、前記基板のエッジ部分の前記塗布材料を除去した後に、前記塗布材料を加熱して前記基板の上方に絶縁膜を形成すると共に、前記絶縁膜に溝を形成する工程と、前記溝に導電膜を埋め込む工程と、前記基板のエッジ部分の前記導電膜を除去する工程と、前記基板のエッジ部分を保護フィルムで覆う工程と、前記絶縁膜上の前記導電膜を研磨によって除去する工程と、研磨終了後に前記保護フィルムを前記基板から取り除く工程と、を含む半導体装置の製造方法が提供される。

【発明の効果】

【0010】

基板のエッジ部分において溝が形成された膜が保護フィルムによって保護されるので、研磨に起因する膜剥がれが防止される。

【図面の簡単な説明】

【0011】

【図1A】図1Aは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図1B】図1Bは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図1C】図1Cは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図1D】図1Dは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図1E】図1Eは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図1F】図1Fは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その6)である。

【図1G】図1Gは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その7)である。

【図1H】図1Hは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その8)である。

【図1I】図1Iは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その9)である。

【図1J】図1Jは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その10)である。

【図1K】図1Kは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その11)である。

【図1L】図1Lは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その12)である。

【図2】図2は、本発明の第1の実施の形態に係る半導体装置の製造工程に使用される保護フィルムの一例を示す平面図である。

【図3】図3は、本発明の第1の実施の形態に係る半導体装置の製造工程に使用される保護フィルムの変形例を示す平面図である。

【発明を実施するための最良の形態】

【0012】

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。

前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない。

【0013】

最初に、図1Aに示す断面構造を得るまでの工程について説明する。

まず、n型又はp型のシリコン(半導体)基板1の一方の面である表面を熱酸化することにより素子分離絶縁膜11を例えば300nmの深さに形成し、この素子分離絶縁膜11でトランジスタの活性領域を画定する。このような素子分離構造は、LOCOS(Local

Oxidation of Silicon)と呼ばれる。素子分離領域には、STI(Shallow Trench Isolation)を用いても良い。

【0014】

次いで、シリコン基板1の活性領域にイオン注入法により、ドーパント不純物を導入してウェルを形成する。ドーパント不純物としてp型不純物、例えばボロンを導入すると、シリコン基板1にpウェル12が形成される。pウェル12を形成した後、その活性領域の表面を熱酸化してゲート絶縁膜13を形成する。ゲート絶縁膜13は、例えば熱酸化膜を約6nm〜7nmの厚さに形成する。なお、以下においては、pウェル12を形成した場合について説明するが、シリコン基板1にnウェルを形成した場合も同様の工程が実施される。

【0015】

続いて、シリコン基板1の上側全面に、ポリシリコン膜を例えばCVD法を用いて200nmの膜厚に形成する。その後に、フォトリソグラフィ技術及びエッチング技術を用いてポリシリコン膜をパターニングして、シリコン基板1上にゲート電極14を形成する。ゲート電極14は、pウェル12上に互いに平行に複数形成され、その各々はワード線の一部を構成する。

【0016】

さらに、ゲート電極14をマスクにしてpウェル12にイオンを注入し、pウェル12のゲート電極14の両側の領域に、n型不純物としてリンを導入する。これにより、第1、第2ソース/ドレインエクステンション15が形成される。第1、第2ソース/ドレインエクステンション15は、エクステンションソース/ドレイン領域の浅い領域を構成する。その後に、シリコン基板1の上側全面に、絶縁膜としてシリコン酸化膜を例えばCVD法を用いて300nmの厚さに形成する。その後、絶縁膜を異方性エッチングする。絶縁膜がエッチバックされ、ゲート電極14の側部に絶縁性サイドウォール16が形成される。

【0017】

続いて、ゲート電極14及び絶縁性サイドウォール16をマスクとして用い、シリコン基板1に砒素等のn型のドーパント不純物を再びイオン注入する。これにより、ゲート電極14の側方のpウェル12に、ソース/ドレイン拡散層17が形成される。ソース/ドレイン拡散層17は、エクステンションソース/ドレインの深い領域を構成する。

【0018】

さらに、シリコン基板1の全面に、例えば、スパッタリング法によりコバルト膜等の高融点金属膜を形成する。この後、高融点金属膜を加熱してシリコンと反応させる。これにより、ソース/ドレイン拡散層17におけるシリコン基板1上にコバルトシリサイド層等の高融点金属シリサイド層が形成され、各ソース/ドレイン拡散層17が低抵抗化する。この後、素子分離絶縁領域11の上などに未反応のまま残っている高融点金属膜を例えばウエットエッチングにより除去する。これにより、ソース/ドレイン拡散層17上に、例えばコバルトシリサイドで形成されるソース/ドレイン電極18Aが形成される。また、

ゲート電極6の上部に、例えばコバルトシリサイドからなるシリサイド層18Bが形成される。

【0019】

ここまでの工程により、シリコン基板1の活性領域には、ゲート絶縁膜13、ゲート電極14、及びソース/ドレイン電極18A等から構成される半導体素子であるトランジスタT1,T2が形成される。

【0020】

次に、図1Bに示す断面構造を得るまでの工程について説明する。

シリコン基板1の上側の全面に、酸化防止膜20として酸窒化シリコン(SiON)膜をプラズマCVD法により形成する。さらに、酸化防止膜20の全面に、第1酸化膜21として、例えば酸化シリコン膜をプラズマCVD法によって300nmの厚さに形成する。

さらに、第1酸化膜21の上に、絶縁膜22として酸化シリコン(SiO2)膜をTEOS(tetra ethoxy silane)ガスを使用するプラズマCVD法により、約300nmの厚さに形成する。

【0021】

続いて、不図示のレジスト膜をマスクに用いて絶縁膜22と、第1酸化膜21と、酸化防止膜20とをエッチングして、コンタクトホール23を形成する。コンタクトホール23は、ソース/ドレイン拡散層17のソース/ドレイン電極18Aに達する深さまで形成し、その径は、例えば0.25μmとする。

【0022】

そして、コンタクトホール23を用いてソース/ドレイン電極18Aに電気的に接続される導電性プラグ24を形成する。具体的には、コンタクトホール15の内面に厚さが30nmのTi膜と、厚さが20nmのTiN膜とを順番にスパッタリング法等により形成して2層の積層構造を有する密着膜(グルー膜)を作製する。さらに、密着膜上にW膜をCVD法により成長させる。この膜厚は、絶縁膜22上で例えば300nmに達する厚さとする。これにより、W膜でコンタクトホール23の空隙が埋まる。この後、絶縁膜22の上面上に成長した余分なW膜及び密着膜をCMP法で除去する。これにより、各コンタクトホール23に、導電性プラグ24が1つずつ形成される。

【0023】

続いて、絶縁膜22の全面に、第1層間絶縁膜として、低誘電体(Low−k)膜31を形成する。低誘電体膜31の形成にあたっては、最初に、基板1の表面に塗布材料30を塗布する。塗布材料30は、スピン塗布方式によって20nm〜200nmの厚さに形成する。低誘電体膜31としては、SIOC膜やSION膜など、Si、N、O、Cを含む膜が形成される。

【0024】

図1Cに示す断面構造を得るまでの工程について説明する。

低誘電体膜31は、スピン塗布方式で形成されるので、基板1の周辺のエッジ部分1Aでは塗布材料30が回り込む。エッジ部分1Aに塗布材料30が残った状態で以降のプロセスを実施すると、基板1を収容する不図示のカセットや、他の製造装置内でエッジ部分1Aの低誘電体膜31が剥がれてダストになる。従って、塗布材料30を絶縁膜22上に塗布した後に、メチルアルコールなどを用いたエッジリンス工程によってエッジ部分1Aの塗布材料30を洗い落とす。

【0025】

エッジリンス工程は、例えば、最初に基板1を処理装置25の回転支持台26上に固定する。回転支持台36の上方には、エッジリンスノズル27が、回転支持台26上の基板1のエッジ部分1Aに向けて配置されている。回転支持台36を駆動させて基板1を回転させながら、エッジリンスノズル27から例えばシンナー等の薬液を基板1のエッジ部分1Aに供給する。エッジ部分1Aの塗布材料30が洗い流され、塗布材料30の回り込みが解消される。

【0026】

これによって、基板1の内周部分に残った低誘電体膜31の端部と、低誘電体膜31が除去された基板1のエッジ部分1A(絶縁膜22)とによって段差部31Aが形成される。段差部31Aの外周側では、下地の絶縁膜22が露出する。エッジリンスの幅W1は、例えば、基板1のエッジから0.5mm〜4.0mmとする。エッジリンス後は、基板1を不図示の焼成炉に入れて、300℃〜500℃で、3分間焼成する。これによって、低誘電体膜31として、厚さが100nm〜1000nmの多孔質の層間絶縁膜NCS(Nano Clustering Silicon;ポーラスシリカ系low-k材料)膜が形成される。低誘電体膜31は、MSQ(Methyl Silsesquioxane)、HSQ(Hydrogen Silsesquioxane)、又はこれらの積層膜でも良い。

【0027】

続いて、図1Dに示す断面構造を得るまでの工程について説明する。

段差部31Aを含む低誘電体膜31の全面と、露出した絶縁膜22の全面に、第2の絶縁膜35を例えばプラズマCVD方によって形成する。さらに、第2の絶縁膜35の上に、ハードマスク用のシリコン酸化膜36を例えばプラズマCVD法によって形成する。この後、シリコン酸化膜36の全面にポジ型のレジスト膜37をスピン塗布法を用いて塗布する。

【0028】

次に、図1Eに示す断面構造を得るまでの工程について説明する。

最初に、レジスト膜37を露光及び現像してマスクを形成する。このとき、基板1のエッジから1.5〜3.0mmの領域にパターンができないように周辺露光を行う。この後、マスクを用いてシリコン酸化膜36をエッチングしてハードマスク36Aを形成する。ハードマスク36Aの形成後には、レジスト膜37から形成したマスクを例えばアッシングによって除去する。さらに、ハードマスク36Aを用いて第2の絶縁膜35及び低誘電体膜31をエッチングして配線溝41を複数形成する。

【0029】

さらに、図1Fに示す断面構造を得るまでの工程について説明する。

配線溝41の内壁および基板1の表面を含む全面に、バリア膜42を例えばPVD法によって10nmの厚さに形成する。バリア膜42としては、Ta膜、Ti膜、TaN膜、TiN膜、WN膜、又はこれらの積層を用いることができる。

【0030】

続いて、バリア膜42上に、不図示のシード層を例えばPVD法により形成した後、電解メッキ法によって導電膜43を成長させる。導電膜43は、配線溝41に埋め込まれると共に、低誘電体膜31の上及び段差部31A、基板1のエッジ部分1Aにも形成される。配線用の導電膜43としては、銅(Cu)の他に、銀(Ag)、アルミニウム(Al)、タングステン(W)を含む膜でも良い。

【0031】

この後、エッジリンス工程を実施し、基板1のエッジ部分1Aの導電膜43を、エッジから1.5〜4.0mmの範囲(第2の範囲)の幅W2で除去する。これは、基板1のキャリアなどの金属汚染を防止するためである。エッジリンスによって、基板1のエッジ部分1Aには導電膜43が充填されない配線溝41Aが形成される。

【0032】

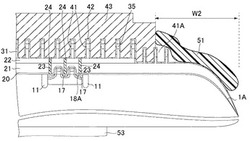

次に、図1Gに示すように、基板1のエッジ部分1Aを保護フィルム51で覆う。保護フィルム51は、例えば、ポリオレフィン系、アクリル系、PET(ポリエステル)系の材料から製造され、基板1に貼り付けるための粘着剤が塗布されている。粘着剤は、紫外線(UV)剥離型の材料であることが好ましい。保護フィルム51の厚さは、0.1μm〜10μmである。例えば、保護フィルム51の厚さは、配線溝41Aを覆う部分が段差部31Aを越える高さに達する大きさとする。保護フィルム51は、基板1のエッジから、例えば5mmの距離まで、少なくとも幅W2の領域を被覆する。これによって、導電膜43が埋め込まれていない配線溝41Aが保護フィルム51によって覆われる。

【0033】

ここで、保護フィルム51を基板1のエッジ部分1Aに取り付ける方法の一例について説明する。最初に、基板1を回転支持台53に載置し、低速で基板1を回転させる。図2に示すような帯状の保護フィルム51を基板1のエッジ部分1Aに貼り付ける。基板1が低速回転しているので、保護フィルム51は、基板1のエッジ部分1Aに略環状に貼り付けられる。また、図3に示すように、略リング状の保護フィルム51を基板1の周辺部1Aに貼り付けても良い。

【0034】

次に、図1Hに示すように、低誘電体膜31上の余分な導電膜43をCMP法による研磨で除去する。研磨によって導電膜43に加えて、バリア膜42及びハードマスク36Aを除去し、第2の絶縁膜35の上側の一部分が研磨される。この研磨では、基板1のエッジ部分1Aの保護フィルム51も同時に研磨される。保護フィルム51は、一部が第2の絶縁膜35の上端より上側にあるので、配線溝41Aの上方の保護フィルム51の一部が研磨される。保護フィルム51の全てが除去されることはないので、基板1のエッジ部分1Aの配線溝41Aは、保護フィルム51によって保護され、膜剥がれが防止される。

【0035】

導電膜43の研磨が終了したら、残った保護フィルム51を基板1から取り外す。保護フィルム51にUV剥離型の粘着剤を用いると、紫外線を保護フィルム51に照射することで、基板1のエッジ部分1Aから保護フィルム51を簡単に取り外せる。これによって、図1Iに示すように、低誘電体膜31に配線55が埋め込まれた第1の配線層60が形成される。

【0036】

次に、図1Jに示す断面構造を得るまでの工程について説明する。

第1の配線層60の上に、酸化防止絶縁膜61として例えばSIN膜をスパッタ法によって約30nmの厚さに形成する。さらに、酸化防止絶縁膜61の上に、第3の酸化膜62として例えばSIO膜をプラズマCVD法によって形成する。第3の酸化膜62の上には、第2層間絶縁膜となる低誘電体膜63を形成する。低誘電体膜63は、第1の配線層60の低誘電体膜31と同様の材料及び製造方法によって形成する。即ち、塗布材料30を第3の酸化膜62の全面にスピン型塗布装置を用いて塗布する。この後、エッジリンス工程によって、エッジ部分1Aで幅W1の領域の塗布材料を洗い流す。この後、塗布材料を焼成することで、低誘電体膜63が形成される。また、エッジリンス工程によって、基板1のエッジ部分1Aには、段差部63Aが形成される。段差部63Aは、低誘電体膜63の端部と、基板1(第3の酸化膜62)とによって形成される。

【0037】

さらに、低誘電体膜63の上に、ハードマスク用の第4のシリコン酸化膜65を例えばプラズマCVD法によって形成する。この後、第4のシリコン酸化膜65の全面にポジ型のレジスト膜66をスピン塗布法によって塗布する。

【0038】

次に、図1Kに示す断面構造を得るまでの工程について説明する。

最初に、レジスト膜66を露光及び現像してマスクを形成する。このとき、基板1のエッジから1.5〜3.0mmの領域にパターンができないように周辺露光を行う。この後、マスクを用いて第4のシリコン酸化膜65をエッチングしてハードマスク65Aを形成する。ハードマスク65Aの形成後には、レジスト膜66から形成したマスクを例えばアッシングによって除去する。さらに、ハードマスク65Aを用いて低誘電体膜63、第3の酸化膜62、酸化防止絶縁膜61をエッチングしてトレンチ溝81を複数形成する。

【0039】

さらに、トレンチ溝81を含む低誘電体膜63の上面にレジスト膜を塗布し、ハードマスク65Aを用いて低誘電体膜63及び第3の酸化膜62をエッチングして配線溝82を複数形成する。

トレンチ溝81及び配線溝82の内壁、基板1の表面を含む全面に、バリア膜83を例えばPVD法によって10nmの厚さに形成する。バリア膜83としては、Ta膜、Ti

膜、TaN膜、TiN膜、WN膜、又はこれらの積層を用いることができる。

【0040】

続いて、バリア膜83上に、不図示のシード層を例えばPVD法により形成した後、電解メッキ法によって導電膜84を成長させる。導電膜84は、トレンチ溝81及び配線溝82に埋め込まれると共に、基板1のエッジ部分1Aにも形成される。

【0041】

この後、エッジリンス工程を実施し、基板1のエッジ部分1Aの導電膜84を、エッジから1.5〜4.0mmの範囲(第2の範囲)の幅W2で除去する。エッジリンスによって、導電膜84が充填されない配線溝82Aが形成される。

【0042】

次に、基板1のエッジ部分1Aを保護フィルム91で覆う。保護フィルム91は、保護フィルム91と同様の材料から製造され、厚さは、0.1μm〜10μmである。例えば、保護フィルム91の厚さは、配線溝82Aを覆う部分が段差部63Aを越える高さに達する大きさとする。段差部63Aは、段差部31Aより大きいので、保護フィルム91の厚さは、保護フィルム51より厚くなる。ここで、導電膜84が充填されない配線溝82Aを覆う観点からは、保護フィルム91の厚さを保護フィルム51と同じにしても良い。

【0043】

保護フィルム91は、基板1のエッジから、例えば5mmの距離まで、少なくとも幅W2の領域を被覆する。これによって、導電膜84が埋め込まれていない低誘電体膜63が保護フィルム91によって覆われる。

【0044】

次に、図1Lに示すように、低誘電体膜71上の余分な導電膜84をCMP法による研磨で除去する。この研磨では、導電膜84に加えて、バリア膜83及びハードマスク65Aを除去する。さらに、基板1のエッジ部分1Aに貼り付けられた保護フィルム91も同時に研磨される。この研磨では、基板1のエッジ部分1Aの保護フィルム91も同時に研磨される。保護フィルム91は、一部が低誘電体膜63の上端より上側にあるので、配線溝82Aの上方の保護フィルム91の一部が研磨される。保護フィルム91の全てが除去されることはないので、基板1のエッジ部分1Aの配線溝82Aは、保護フィルム91によって保護され、膜剥がれが防止される。

【0045】

研磨が終了したら、紫外線(UV)を照射して残った保護フィルム91を基板1から取り外す。図1Iに示すように、低誘電体膜63に導電性プラグ93と配線94が埋め込まれた第2の配線層94が形成される。これによって、トランジスタT1,T2と2層の配線構造を有する半導体装置95が形成される。半導体装置95は、3層以上の配線構造を有しても良い。

【0046】

以上、説明したように、CMP法を用いて導電膜43,84を研磨する際に、基板1のエッジ部分1Aの配線溝41A,82Aを保護フィルム91で覆うようにしたので、エッジ部分1Aの膜剥がれを防止できる。保護フィルム91は、連続したシートとして予め用意できるので、基板1に簡単に取り付けたり、取り外したりできる。従って、効率良く半導体装置95を製造できる。保護フィルム91の膜厚を変化させることで、段差部31A,63Aが大きい場合でも、CMP法による研磨時の膜剥がれを防止できる。

【0047】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができる。

【符号の説明】

【0048】

1 基板

1A エッジ部分

30 塗布材料

31,63 低誘電体膜(絶縁膜)

31A,63A 段差部

41,82 配線溝

43,84 導体膜

51,91 保護フィルム

95 半導体装置

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の微細化及び動作の高速化を目的として、半導体回路の高集積化が進んでいる。これに伴って、半導体回路の配線幅や配線ピッチが縮小化している。配線幅や配線ピッチの縮小化は、半導体回路の配線抵抗の増加や、配線間容量の増加に原因になる。そこで、配線遅延の増大を防止する方法の一つとして、層間絶縁膜に低誘電率(Low−k)膜を用いた製造プロセスが開発されている。低誘電率の層間絶縁膜は、例えば、スピン塗布方式を用いて基板の表面に塗布した後に、加熱によって硬化させることで形成される。

【0003】

さらに、配線遅延の増大を防止する他の方法としては、低抵抗の配線金属材料を用いることがある。従来、配線材料はアルミニウム(Al)の利用が一般的であったが、半導体装置の微細化、動作の高速化に対してアルミニウムでは限界がある。そのため、エレクトロマイグレーションに強く、比抵抗の小さい銅(Cu)配線が必要になっている。ところが、銅膜は、ドライエッチングが困難である。このために、低誘電体膜に予め配線溝を形成し、硫酸銅めっき液を用いた電解めっき法で配線溝に銅膜を埋め込んだ後、低誘電体膜の表面の余分な銅膜をCMP(Chemical Mechanical Polishing)によって除去して配線の平坦化するダマシン工程(Cu−CMP工程)が採用される。

【0004】

ここで、スピン塗布方式を用いて低誘電体膜を形成すると、基板の周辺のエッジ部分に塗布材料が回り込むことがある。エッジ部分に形成された低誘電体膜は、後の工程などで、基板から剥がれることがあり、基板を搬送するカセットや、半導体製造装置を汚す原因になり易かった。そこで、塗布材料を基板に塗布した後に、エッジリンス工程を実施して基板のエッジ部分の塗布材料を洗い流す。これによって、塗布材料の回り込みが防止される。

【0005】

また、配線溝に銅膜を埋め込んだときは、他の半導体製造装置を金属汚染しないように、エッジリンス工程を実施する。エッジリンス工程では、基板のエッジ部分の銅膜が除去される。そのため、基板のエッジ部分に銅膜が埋め込まれていない配線溝が発生することがある。CMP法による銅膜の研磨では、基板のエッジ部分が研磨され易いので銅膜が埋め込まれていない配線溝が崩れ、低誘電体膜が剥がれることがある。基板から剥がれた低誘電体膜は、スクラッチ(研磨傷)や配線のショートの原因になり易い。

【0006】

そこで、従来の半導体装置の製造方法では、銅膜が埋め込まれていない配線溝の保護に剥離防止膜を用いることがある。具体的には、基板のエッジ部分の銅膜をエッジリンス工程によって除去した後、第1の研磨によって銅膜をバリア膜が露出するまで研磨する。次に、研磨面の全面に剥離防止膜を形成する。続いて、第2の研磨によって剥離防止膜とバリア膜を取り除く。これによって、基板のエッジ部分の配線溝のみの低誘電体膜の剥離が防止される。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2009−272560

【発明の概要】

【発明が解決しようとする課題】

【0008】

ここで、基板のエッジ部分の低誘電体膜を洗い流すと、基板上に低誘電体膜の端面による段差が形成される。段差には、銅膜のCMP時に他の領域よりも大きい研磨圧が作用し易い。このために、段差が大きくなると、段差部分の研磨圧の荷重が大きくなるので、膜が剥がれ易くなる。膜剥がれを防止するために研磨荷重を低下させると、研磨レートが低下するので、スループットが低下してしまう。

この発明は、このような事情に鑑みてなされたものであり、基板のエッジ部分での膜剥がれを防止し、半導体装置を効率良く製造できるようにすることを目的とする。

【課題を解決するための手段】

【0009】

実施形態の一観点によれば、基板の上方に塗布材料を塗布し、前記基板のエッジ部分の前記塗布材料を除去した後に、前記塗布材料を加熱して前記基板の上方に絶縁膜を形成すると共に、前記絶縁膜に溝を形成する工程と、前記溝に導電膜を埋め込む工程と、前記基板のエッジ部分の前記導電膜を除去する工程と、前記基板のエッジ部分を保護フィルムで覆う工程と、前記絶縁膜上の前記導電膜を研磨によって除去する工程と、研磨終了後に前記保護フィルムを前記基板から取り除く工程と、を含む半導体装置の製造方法が提供される。

【発明の効果】

【0010】

基板のエッジ部分において溝が形成された膜が保護フィルムによって保護されるので、研磨に起因する膜剥がれが防止される。

【図面の簡単な説明】

【0011】

【図1A】図1Aは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図1B】図1Bは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図1C】図1Cは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図1D】図1Dは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図1E】図1Eは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図1F】図1Fは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その6)である。

【図1G】図1Gは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その7)である。

【図1H】図1Hは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その8)である。

【図1I】図1Iは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その9)である。

【図1J】図1Jは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その10)である。

【図1K】図1Kは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その11)である。

【図1L】図1Lは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その12)である。

【図2】図2は、本発明の第1の実施の形態に係る半導体装置の製造工程に使用される保護フィルムの一例を示す平面図である。

【図3】図3は、本発明の第1の実施の形態に係る半導体装置の製造工程に使用される保護フィルムの変形例を示す平面図である。

【発明を実施するための最良の形態】

【0012】

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。

前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない。

【0013】

最初に、図1Aに示す断面構造を得るまでの工程について説明する。

まず、n型又はp型のシリコン(半導体)基板1の一方の面である表面を熱酸化することにより素子分離絶縁膜11を例えば300nmの深さに形成し、この素子分離絶縁膜11でトランジスタの活性領域を画定する。このような素子分離構造は、LOCOS(Local

Oxidation of Silicon)と呼ばれる。素子分離領域には、STI(Shallow Trench Isolation)を用いても良い。

【0014】

次いで、シリコン基板1の活性領域にイオン注入法により、ドーパント不純物を導入してウェルを形成する。ドーパント不純物としてp型不純物、例えばボロンを導入すると、シリコン基板1にpウェル12が形成される。pウェル12を形成した後、その活性領域の表面を熱酸化してゲート絶縁膜13を形成する。ゲート絶縁膜13は、例えば熱酸化膜を約6nm〜7nmの厚さに形成する。なお、以下においては、pウェル12を形成した場合について説明するが、シリコン基板1にnウェルを形成した場合も同様の工程が実施される。

【0015】

続いて、シリコン基板1の上側全面に、ポリシリコン膜を例えばCVD法を用いて200nmの膜厚に形成する。その後に、フォトリソグラフィ技術及びエッチング技術を用いてポリシリコン膜をパターニングして、シリコン基板1上にゲート電極14を形成する。ゲート電極14は、pウェル12上に互いに平行に複数形成され、その各々はワード線の一部を構成する。

【0016】

さらに、ゲート電極14をマスクにしてpウェル12にイオンを注入し、pウェル12のゲート電極14の両側の領域に、n型不純物としてリンを導入する。これにより、第1、第2ソース/ドレインエクステンション15が形成される。第1、第2ソース/ドレインエクステンション15は、エクステンションソース/ドレイン領域の浅い領域を構成する。その後に、シリコン基板1の上側全面に、絶縁膜としてシリコン酸化膜を例えばCVD法を用いて300nmの厚さに形成する。その後、絶縁膜を異方性エッチングする。絶縁膜がエッチバックされ、ゲート電極14の側部に絶縁性サイドウォール16が形成される。

【0017】

続いて、ゲート電極14及び絶縁性サイドウォール16をマスクとして用い、シリコン基板1に砒素等のn型のドーパント不純物を再びイオン注入する。これにより、ゲート電極14の側方のpウェル12に、ソース/ドレイン拡散層17が形成される。ソース/ドレイン拡散層17は、エクステンションソース/ドレインの深い領域を構成する。

【0018】

さらに、シリコン基板1の全面に、例えば、スパッタリング法によりコバルト膜等の高融点金属膜を形成する。この後、高融点金属膜を加熱してシリコンと反応させる。これにより、ソース/ドレイン拡散層17におけるシリコン基板1上にコバルトシリサイド層等の高融点金属シリサイド層が形成され、各ソース/ドレイン拡散層17が低抵抗化する。この後、素子分離絶縁領域11の上などに未反応のまま残っている高融点金属膜を例えばウエットエッチングにより除去する。これにより、ソース/ドレイン拡散層17上に、例えばコバルトシリサイドで形成されるソース/ドレイン電極18Aが形成される。また、

ゲート電極6の上部に、例えばコバルトシリサイドからなるシリサイド層18Bが形成される。

【0019】

ここまでの工程により、シリコン基板1の活性領域には、ゲート絶縁膜13、ゲート電極14、及びソース/ドレイン電極18A等から構成される半導体素子であるトランジスタT1,T2が形成される。

【0020】

次に、図1Bに示す断面構造を得るまでの工程について説明する。

シリコン基板1の上側の全面に、酸化防止膜20として酸窒化シリコン(SiON)膜をプラズマCVD法により形成する。さらに、酸化防止膜20の全面に、第1酸化膜21として、例えば酸化シリコン膜をプラズマCVD法によって300nmの厚さに形成する。

さらに、第1酸化膜21の上に、絶縁膜22として酸化シリコン(SiO2)膜をTEOS(tetra ethoxy silane)ガスを使用するプラズマCVD法により、約300nmの厚さに形成する。

【0021】

続いて、不図示のレジスト膜をマスクに用いて絶縁膜22と、第1酸化膜21と、酸化防止膜20とをエッチングして、コンタクトホール23を形成する。コンタクトホール23は、ソース/ドレイン拡散層17のソース/ドレイン電極18Aに達する深さまで形成し、その径は、例えば0.25μmとする。

【0022】

そして、コンタクトホール23を用いてソース/ドレイン電極18Aに電気的に接続される導電性プラグ24を形成する。具体的には、コンタクトホール15の内面に厚さが30nmのTi膜と、厚さが20nmのTiN膜とを順番にスパッタリング法等により形成して2層の積層構造を有する密着膜(グルー膜)を作製する。さらに、密着膜上にW膜をCVD法により成長させる。この膜厚は、絶縁膜22上で例えば300nmに達する厚さとする。これにより、W膜でコンタクトホール23の空隙が埋まる。この後、絶縁膜22の上面上に成長した余分なW膜及び密着膜をCMP法で除去する。これにより、各コンタクトホール23に、導電性プラグ24が1つずつ形成される。

【0023】

続いて、絶縁膜22の全面に、第1層間絶縁膜として、低誘電体(Low−k)膜31を形成する。低誘電体膜31の形成にあたっては、最初に、基板1の表面に塗布材料30を塗布する。塗布材料30は、スピン塗布方式によって20nm〜200nmの厚さに形成する。低誘電体膜31としては、SIOC膜やSION膜など、Si、N、O、Cを含む膜が形成される。

【0024】

図1Cに示す断面構造を得るまでの工程について説明する。

低誘電体膜31は、スピン塗布方式で形成されるので、基板1の周辺のエッジ部分1Aでは塗布材料30が回り込む。エッジ部分1Aに塗布材料30が残った状態で以降のプロセスを実施すると、基板1を収容する不図示のカセットや、他の製造装置内でエッジ部分1Aの低誘電体膜31が剥がれてダストになる。従って、塗布材料30を絶縁膜22上に塗布した後に、メチルアルコールなどを用いたエッジリンス工程によってエッジ部分1Aの塗布材料30を洗い落とす。

【0025】

エッジリンス工程は、例えば、最初に基板1を処理装置25の回転支持台26上に固定する。回転支持台36の上方には、エッジリンスノズル27が、回転支持台26上の基板1のエッジ部分1Aに向けて配置されている。回転支持台36を駆動させて基板1を回転させながら、エッジリンスノズル27から例えばシンナー等の薬液を基板1のエッジ部分1Aに供給する。エッジ部分1Aの塗布材料30が洗い流され、塗布材料30の回り込みが解消される。

【0026】

これによって、基板1の内周部分に残った低誘電体膜31の端部と、低誘電体膜31が除去された基板1のエッジ部分1A(絶縁膜22)とによって段差部31Aが形成される。段差部31Aの外周側では、下地の絶縁膜22が露出する。エッジリンスの幅W1は、例えば、基板1のエッジから0.5mm〜4.0mmとする。エッジリンス後は、基板1を不図示の焼成炉に入れて、300℃〜500℃で、3分間焼成する。これによって、低誘電体膜31として、厚さが100nm〜1000nmの多孔質の層間絶縁膜NCS(Nano Clustering Silicon;ポーラスシリカ系low-k材料)膜が形成される。低誘電体膜31は、MSQ(Methyl Silsesquioxane)、HSQ(Hydrogen Silsesquioxane)、又はこれらの積層膜でも良い。

【0027】

続いて、図1Dに示す断面構造を得るまでの工程について説明する。

段差部31Aを含む低誘電体膜31の全面と、露出した絶縁膜22の全面に、第2の絶縁膜35を例えばプラズマCVD方によって形成する。さらに、第2の絶縁膜35の上に、ハードマスク用のシリコン酸化膜36を例えばプラズマCVD法によって形成する。この後、シリコン酸化膜36の全面にポジ型のレジスト膜37をスピン塗布法を用いて塗布する。

【0028】

次に、図1Eに示す断面構造を得るまでの工程について説明する。

最初に、レジスト膜37を露光及び現像してマスクを形成する。このとき、基板1のエッジから1.5〜3.0mmの領域にパターンができないように周辺露光を行う。この後、マスクを用いてシリコン酸化膜36をエッチングしてハードマスク36Aを形成する。ハードマスク36Aの形成後には、レジスト膜37から形成したマスクを例えばアッシングによって除去する。さらに、ハードマスク36Aを用いて第2の絶縁膜35及び低誘電体膜31をエッチングして配線溝41を複数形成する。

【0029】

さらに、図1Fに示す断面構造を得るまでの工程について説明する。

配線溝41の内壁および基板1の表面を含む全面に、バリア膜42を例えばPVD法によって10nmの厚さに形成する。バリア膜42としては、Ta膜、Ti膜、TaN膜、TiN膜、WN膜、又はこれらの積層を用いることができる。

【0030】

続いて、バリア膜42上に、不図示のシード層を例えばPVD法により形成した後、電解メッキ法によって導電膜43を成長させる。導電膜43は、配線溝41に埋め込まれると共に、低誘電体膜31の上及び段差部31A、基板1のエッジ部分1Aにも形成される。配線用の導電膜43としては、銅(Cu)の他に、銀(Ag)、アルミニウム(Al)、タングステン(W)を含む膜でも良い。

【0031】

この後、エッジリンス工程を実施し、基板1のエッジ部分1Aの導電膜43を、エッジから1.5〜4.0mmの範囲(第2の範囲)の幅W2で除去する。これは、基板1のキャリアなどの金属汚染を防止するためである。エッジリンスによって、基板1のエッジ部分1Aには導電膜43が充填されない配線溝41Aが形成される。

【0032】

次に、図1Gに示すように、基板1のエッジ部分1Aを保護フィルム51で覆う。保護フィルム51は、例えば、ポリオレフィン系、アクリル系、PET(ポリエステル)系の材料から製造され、基板1に貼り付けるための粘着剤が塗布されている。粘着剤は、紫外線(UV)剥離型の材料であることが好ましい。保護フィルム51の厚さは、0.1μm〜10μmである。例えば、保護フィルム51の厚さは、配線溝41Aを覆う部分が段差部31Aを越える高さに達する大きさとする。保護フィルム51は、基板1のエッジから、例えば5mmの距離まで、少なくとも幅W2の領域を被覆する。これによって、導電膜43が埋め込まれていない配線溝41Aが保護フィルム51によって覆われる。

【0033】

ここで、保護フィルム51を基板1のエッジ部分1Aに取り付ける方法の一例について説明する。最初に、基板1を回転支持台53に載置し、低速で基板1を回転させる。図2に示すような帯状の保護フィルム51を基板1のエッジ部分1Aに貼り付ける。基板1が低速回転しているので、保護フィルム51は、基板1のエッジ部分1Aに略環状に貼り付けられる。また、図3に示すように、略リング状の保護フィルム51を基板1の周辺部1Aに貼り付けても良い。

【0034】

次に、図1Hに示すように、低誘電体膜31上の余分な導電膜43をCMP法による研磨で除去する。研磨によって導電膜43に加えて、バリア膜42及びハードマスク36Aを除去し、第2の絶縁膜35の上側の一部分が研磨される。この研磨では、基板1のエッジ部分1Aの保護フィルム51も同時に研磨される。保護フィルム51は、一部が第2の絶縁膜35の上端より上側にあるので、配線溝41Aの上方の保護フィルム51の一部が研磨される。保護フィルム51の全てが除去されることはないので、基板1のエッジ部分1Aの配線溝41Aは、保護フィルム51によって保護され、膜剥がれが防止される。

【0035】

導電膜43の研磨が終了したら、残った保護フィルム51を基板1から取り外す。保護フィルム51にUV剥離型の粘着剤を用いると、紫外線を保護フィルム51に照射することで、基板1のエッジ部分1Aから保護フィルム51を簡単に取り外せる。これによって、図1Iに示すように、低誘電体膜31に配線55が埋め込まれた第1の配線層60が形成される。

【0036】

次に、図1Jに示す断面構造を得るまでの工程について説明する。

第1の配線層60の上に、酸化防止絶縁膜61として例えばSIN膜をスパッタ法によって約30nmの厚さに形成する。さらに、酸化防止絶縁膜61の上に、第3の酸化膜62として例えばSIO膜をプラズマCVD法によって形成する。第3の酸化膜62の上には、第2層間絶縁膜となる低誘電体膜63を形成する。低誘電体膜63は、第1の配線層60の低誘電体膜31と同様の材料及び製造方法によって形成する。即ち、塗布材料30を第3の酸化膜62の全面にスピン型塗布装置を用いて塗布する。この後、エッジリンス工程によって、エッジ部分1Aで幅W1の領域の塗布材料を洗い流す。この後、塗布材料を焼成することで、低誘電体膜63が形成される。また、エッジリンス工程によって、基板1のエッジ部分1Aには、段差部63Aが形成される。段差部63Aは、低誘電体膜63の端部と、基板1(第3の酸化膜62)とによって形成される。

【0037】

さらに、低誘電体膜63の上に、ハードマスク用の第4のシリコン酸化膜65を例えばプラズマCVD法によって形成する。この後、第4のシリコン酸化膜65の全面にポジ型のレジスト膜66をスピン塗布法によって塗布する。

【0038】

次に、図1Kに示す断面構造を得るまでの工程について説明する。

最初に、レジスト膜66を露光及び現像してマスクを形成する。このとき、基板1のエッジから1.5〜3.0mmの領域にパターンができないように周辺露光を行う。この後、マスクを用いて第4のシリコン酸化膜65をエッチングしてハードマスク65Aを形成する。ハードマスク65Aの形成後には、レジスト膜66から形成したマスクを例えばアッシングによって除去する。さらに、ハードマスク65Aを用いて低誘電体膜63、第3の酸化膜62、酸化防止絶縁膜61をエッチングしてトレンチ溝81を複数形成する。

【0039】

さらに、トレンチ溝81を含む低誘電体膜63の上面にレジスト膜を塗布し、ハードマスク65Aを用いて低誘電体膜63及び第3の酸化膜62をエッチングして配線溝82を複数形成する。

トレンチ溝81及び配線溝82の内壁、基板1の表面を含む全面に、バリア膜83を例えばPVD法によって10nmの厚さに形成する。バリア膜83としては、Ta膜、Ti

膜、TaN膜、TiN膜、WN膜、又はこれらの積層を用いることができる。

【0040】

続いて、バリア膜83上に、不図示のシード層を例えばPVD法により形成した後、電解メッキ法によって導電膜84を成長させる。導電膜84は、トレンチ溝81及び配線溝82に埋め込まれると共に、基板1のエッジ部分1Aにも形成される。

【0041】

この後、エッジリンス工程を実施し、基板1のエッジ部分1Aの導電膜84を、エッジから1.5〜4.0mmの範囲(第2の範囲)の幅W2で除去する。エッジリンスによって、導電膜84が充填されない配線溝82Aが形成される。

【0042】

次に、基板1のエッジ部分1Aを保護フィルム91で覆う。保護フィルム91は、保護フィルム91と同様の材料から製造され、厚さは、0.1μm〜10μmである。例えば、保護フィルム91の厚さは、配線溝82Aを覆う部分が段差部63Aを越える高さに達する大きさとする。段差部63Aは、段差部31Aより大きいので、保護フィルム91の厚さは、保護フィルム51より厚くなる。ここで、導電膜84が充填されない配線溝82Aを覆う観点からは、保護フィルム91の厚さを保護フィルム51と同じにしても良い。

【0043】

保護フィルム91は、基板1のエッジから、例えば5mmの距離まで、少なくとも幅W2の領域を被覆する。これによって、導電膜84が埋め込まれていない低誘電体膜63が保護フィルム91によって覆われる。

【0044】

次に、図1Lに示すように、低誘電体膜71上の余分な導電膜84をCMP法による研磨で除去する。この研磨では、導電膜84に加えて、バリア膜83及びハードマスク65Aを除去する。さらに、基板1のエッジ部分1Aに貼り付けられた保護フィルム91も同時に研磨される。この研磨では、基板1のエッジ部分1Aの保護フィルム91も同時に研磨される。保護フィルム91は、一部が低誘電体膜63の上端より上側にあるので、配線溝82Aの上方の保護フィルム91の一部が研磨される。保護フィルム91の全てが除去されることはないので、基板1のエッジ部分1Aの配線溝82Aは、保護フィルム91によって保護され、膜剥がれが防止される。

【0045】

研磨が終了したら、紫外線(UV)を照射して残った保護フィルム91を基板1から取り外す。図1Iに示すように、低誘電体膜63に導電性プラグ93と配線94が埋め込まれた第2の配線層94が形成される。これによって、トランジスタT1,T2と2層の配線構造を有する半導体装置95が形成される。半導体装置95は、3層以上の配線構造を有しても良い。

【0046】

以上、説明したように、CMP法を用いて導電膜43,84を研磨する際に、基板1のエッジ部分1Aの配線溝41A,82Aを保護フィルム91で覆うようにしたので、エッジ部分1Aの膜剥がれを防止できる。保護フィルム91は、連続したシートとして予め用意できるので、基板1に簡単に取り付けたり、取り外したりできる。従って、効率良く半導体装置95を製造できる。保護フィルム91の膜厚を変化させることで、段差部31A,63Aが大きい場合でも、CMP法による研磨時の膜剥がれを防止できる。

【0047】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができる。

【符号の説明】

【0048】

1 基板

1A エッジ部分

30 塗布材料

31,63 低誘電体膜(絶縁膜)

31A,63A 段差部

41,82 配線溝

43,84 導体膜

51,91 保護フィルム

95 半導体装置

【特許請求の範囲】

【請求項1】

基板の上方に塗布材料を塗布し、前記基板のエッジ部分の前記塗布材料を除去した後に、加熱して前記基板の上方に絶縁膜を形成すると共に、

前記絶縁膜に溝を形成する工程と、

前記溝に導電膜を埋め込む工程と、

前記基板のエッジ部分の前記導電膜を除去する工程と、

前記基板のエッジ部分を保護フィルムで覆う工程と、

前記絶縁膜上の前記導電膜を研磨によって除去する工程と、

研磨終了後に前記保護フィルムを前記基板から取り除く工程と、

を含む半導体装置の製造方法。

【請求項2】

前記保護フィルムは、前記導電膜が埋め込まれていない前記絶縁膜の前記溝を覆うことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

研磨後の前記基板の上方に残った前記保護フィルムに紫外線を照射して除去することを特徴とする請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項4】

前記基板のエッジ部分の前記塗布材料を除去したときの形成される段差部の高さ以上の膜厚の前記保護フィルムを貼り付けることを特徴とする請求項1乃至請求項3のいずれか一項に記載の半導体装置の製造方法。

【請求項5】

前記基板を回転させながら、帯状の前記保護フィルムを前記基板のエッジ部分に貼り付けることを特徴とする請求項1乃至請求項4のいずれか一項に記載の半導体装置の製造方法。

【請求項1】

基板の上方に塗布材料を塗布し、前記基板のエッジ部分の前記塗布材料を除去した後に、加熱して前記基板の上方に絶縁膜を形成すると共に、

前記絶縁膜に溝を形成する工程と、

前記溝に導電膜を埋め込む工程と、

前記基板のエッジ部分の前記導電膜を除去する工程と、

前記基板のエッジ部分を保護フィルムで覆う工程と、

前記絶縁膜上の前記導電膜を研磨によって除去する工程と、

研磨終了後に前記保護フィルムを前記基板から取り除く工程と、

を含む半導体装置の製造方法。

【請求項2】

前記保護フィルムは、前記導電膜が埋め込まれていない前記絶縁膜の前記溝を覆うことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

研磨後の前記基板の上方に残った前記保護フィルムに紫外線を照射して除去することを特徴とする請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項4】

前記基板のエッジ部分の前記塗布材料を除去したときの形成される段差部の高さ以上の膜厚の前記保護フィルムを貼り付けることを特徴とする請求項1乃至請求項3のいずれか一項に記載の半導体装置の製造方法。

【請求項5】

前記基板を回転させながら、帯状の前記保護フィルムを前記基板のエッジ部分に貼り付けることを特徴とする請求項1乃至請求項4のいずれか一項に記載の半導体装置の製造方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図1J】

【図1K】

【図1L】

【図2】

【図3】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図1J】

【図1K】

【図1L】

【図2】

【図3】

【公開番号】特開2012−243793(P2012−243793A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−109235(P2011−109235)

【出願日】平成23年5月16日(2011.5.16)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月16日(2011.5.16)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]