半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

従来から、コンタクトホール等の微細な構造へ導電材料を埋設する際に、コンタクトホール内にボイドが発生するなどの問題点が指摘されていた。そこで、微細なコンタクトホールへの導電材料の埋設性を確保するために、Alリフロースパッタ法を用いた方法が提案されている。Alリフロースパッタ法は、Al膜を堆積させると共に高温加熱により堆積させたAl膜を流動化させることにより、埋設性・平坦性に優れたAl膜を形成できるという特徴を有する。

【0003】

例えば、特許文献1(特開平7−29853号公報)、および特許文献2(特開平11−243070号公報)には、窒化チタン膜を用いることにより、微細コンタクトホールへのAlリフロースパッタ法を用いたAlの埋設性を確保している。

【0004】

また、特許文献3(特開平7−176615号公報)では、高温スパッタTiを用いAl表面モホロジーを確保している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平7−29853号公報

【特許文献2】特開平11−243070号公報

【特許文献3】特開平7−176615号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

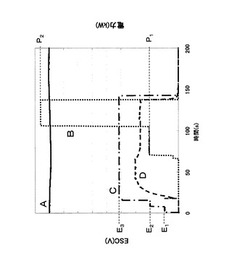

図1及び2はそれぞれ、上記特許文献1〜3のような従来のAlリフロースパッタ法を実施した状況を表す概略図、及びスパッタ条件を表す図である。図2中のAはチャンバー14内を流すArガスの温度、Bはターゲット11に印加するターゲット電力、Cは静電チャック(図1中には図示していない)を介して基板に印加するESC電圧、Dはステージ圧力を表す。

【0007】

図1及び2に示すように、従来のAlリフロースパッタ法では、スパッタ装置10のチャンバー14内のステージ12上に静電チャックにより、基板13を配置する。ステージ12と基板13間に高温のArガスを流すことにより、基板の温度を高温に保つ。この状態でESC電圧Cを一定値に設定した後、ステージ圧力(ウェハとステージの間に流すガスの圧力)Dを一定値まで上昇させる。次に、チャンバー内のターゲットに対して一定のターゲット電力Bを印加することで、Al膜の成膜を行う。

【0008】

上記のような従来のAlリフロースパッタ法では、ESC電圧Cを1段階で一定値に設定すると、ステージ12上で基板13が割れる、という現象が発生していた。この結果、Alリフロースパッタの生産性が低下することとなっていた。また、従来のAlリフロースパッタ法では、ターゲット電力を高く設定しAl成膜の温度を高温にすることでAl膜の埋設性を確保していたが、ウェハ割れにより生産性が低下する、という問題点があった。

【0009】

本発明は上記課題に鑑みてなされたものであり、ESC電圧を3段階にステップ状に増加させ、低レートと高レートの2種類のAlリフロースパッタ法を行うことで、微細なコンタクトホールへのAl材料の埋設性を高めるものである。

【課題を解決するための手段】

【0010】

一実施形態は、

基 基板の層間絶縁膜内にコンタクトホールを形成する工程と、

前記コンタクトホールの内壁上に順に、バリアメタル膜及びシードAl膜を形成する工程と、

前記基板を加熱した状態で、下記(1)〜(3)の工程を順に行うことにより、コンタクトプラグを形成する工程と、

(1)スパッタ装置のチャンバー内のステージ上に、チャックを介して前記基板を保持し、前記チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる工程、

(2)前記チャンバー内のターゲットに対して第一のターゲット電力を印加して前記コンタクトホール内を埋め込むように第一のAl膜を成膜する工程、

(3)前記チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して前記第一のAl膜上に第二のAl膜を成膜する工程、

を有する半導体装置の製造方法に関する。

【発明の効果】

【0011】

高い生産性で、コンタクトホール内にAl膜が良好に埋設されたコンタクトプラグを有する半導体装置を提供する。

【図面の簡単な説明】

【0012】

【図1】従来のAlリフロースパッタ法を使用する場合の問題点を表す図である。

【図2】従来のAlリフロースパッタ法によるスパッタ条件を表す図である。

【図3】本発明の半導体装置の製造方法の一例を表すフローチャートである。

【図4】図3の各工程を実施する装置を表す図である。

【図5】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図6】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図7】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図8】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図9】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図10】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図11】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図12】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図13】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図14】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図15】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図16】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図17】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図18】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【発明を実施するための形態】

【0013】

半導体装置の製造方法では、基板を加熱冷却後に、コンタクトホールの内壁上に順に、バリアメタル膜及びシードAl膜を形成する。バリアメタル膜としては、Ti膜、Ti膜/TiN膜、又は、Ti膜/TiN膜/Ti膜(何れの積層膜もコンタクトホールの内壁側から順に記載)を挙げることができる。シードAl膜等の埋設マージンを大幅に拡大することができるため、Ti膜/TiN膜/Ti膜の積層膜からなるバリアメタル膜が好ましい。バリアメタル膜の膜厚は5〜30nmであることが好ましく、シードAl膜の膜厚は150〜300nmであることが好ましい。コンタクトホールのアスペクト比は3以下であることが好ましい。バリアメタル膜とシードAl膜の膜厚、及びコンタクトホールのアスペクト比がこれらの範囲内にあることにより、後の工程(2)で、良好に第一のAl膜の成膜を行うことができる。

【0014】

この後、基板を加熱した状態で下記の3つの工程(1)〜(3)を順に行う。これにより、コンタクトプラグを形成する。なお、加熱により、下記工程(1)〜(3)の間、基板は一定温度に維持される。

【0015】

工程(1)

Al成膜の前処理工程であり、チャンバー内のステージ上に静電チャックを介して基板を保持し、静電チャックを介して基板に印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。このように、段階的にステージ電圧を変化させることにより、基板に印加される電圧は徐々に増加していくため、基板内には内部応力が生じにくくなる。この結果、ステージ上での基板の反りによる割れが発生しなくなる。

【0016】

第二の電圧は第一の電圧の1.5〜2.5倍であることが好ましく、第三の電圧は第一の電圧の3.5〜4.5倍であることが好ましい。また、第二の電圧は第一の電圧の2倍であり、第三の電圧は第一の電圧の4倍であることがより好ましい。第一、第二、及び第三の電圧をこれらの範囲内に設定することにより、ステージ上での基板の反りによる割れを効果的に防止することができる。

【0017】

工程(2)

第一のAlの成膜工程であり、チャンバー内のターゲットに対して第一のターゲット電力を印加して、コンタクトホール内に第一のAl膜を成膜する。第一のAlの成膜工程では、第一のターゲット電力を低めに制御することにより、低い成膜レートでAl膜を成膜する。これにより、コンタクトホール内にボイドを発生させることなく、良好な埋設性でコンタクトホール内にAl膜を埋設させることができる。第一のAl膜の成膜レートは、5nm/sであることが好ましい。5nm/sとすることにより、コンタクトホールへAl膜を良好な埋設性を確保することができる。

【0018】

工程(3)

第二のAlの成膜工程であり、チャンバー内のターゲットに対して、第一のターゲット電力よりも高い第二のターゲット電力を印加して、第一のAl膜上に第二のAl膜を成膜する。第二のAlの成膜工程では、チャンバー内に高めのターゲット電力を印加することにより、高い成膜レートでAlを成膜する。工程(2)において、コンタクトホール内は既に埋設性に優れた第一のAl膜で埋設されている。このため、工程(3)では、高い成膜レートにして短時間で効率よく第一のAl膜上に第二のAl膜を形成することができる。さらに、ESC電圧及びターゲット電力を制御することで、従来よりも工程(2)及び(3)の温度を低温で処理することができ、ウェハ割れの発生やパーツ寿命を改善することができる。この結果、半導体装置の生産性を高めることができます。

【0019】

第二のAl膜の成膜レートは、17nm/sであることが好ましい。17nm/sとすることにより、短時間でAl膜を成膜することができ、生産性を向上させることができる。

【0020】

第二のターゲット電力は、第一のターゲット電力の4〜5倍であることが好ましく、4.8倍であることがより好ましい。第一及び第二のターゲット電力がこれらの範囲内であることによって、コンタクトホール内の埋設性を確保しつつ、Alの成膜時間を短縮して生産性をより向上させることができる。

【0021】

工程(1)〜(3)における、チャンバー内のステージ温度は400〜450℃であることが好ましく、430℃であることがより好ましい。

【0022】

以下、図3〜18を参照して、半導体装置の製造方法の一例を説明する。図3は、半導体装置の製造方法の各工程を表すフローチャートである。図4は、半導体装置の製造装置を表す概略図である。図5〜18は、半導体装置の製造方法における各工程を表す図である。

【0023】

まず、シリコン基板20上に、Ti膜21、TiN膜22、Al膜23及びTiN膜24が積層された配線層を有する層間絶縁膜25を形成する。RIE工程を実施することにより、層間絶縁膜25内にコンタクトホール26を形成する(図5)。

【0024】

このシリコン基板を図4のロードポートA 50からロードロックチャンバー51に搬送する。シリコン基板を、第一の移動領域52を経由して、脱ガスチャンバー53に搬入する(図3のS1)。脱ガスチャンバー53内では、温度450℃、圧力8Torr、時間90sの条件で、シリコン基板に対して脱ガス処理を行う(図3のS2、図6)。脱ガス条件はこれに限定されるわけではなく、例えば、温度400〜500℃の範囲、圧力3〜10Torrの範囲、時間20〜120sの範囲とすることができる。

【0025】

シリコン基板を、図4の脱ガスチャンバー53から第一の移動領域52を経由して、RFエッチングチャンバー54内に搬入する。RFエッチングチャンバー54内では、Arスパッタエッチングを行う(図3のS3、図7)。これにより、コンタクトホールの底部に露出している配線層の表面酸化膜を除去すると共に、コンタクトホールの開口径を拡大させて、後の工程で良好なAl埋設性を確保することができる。この時のArスパッタエッチングのエッチング量を酸化膜換算で20nmとしたが、エッチング量はこれに限定されるわけではなく、5nmから40nmの範囲としても良い。

【0026】

シリコン基板を、図4のRFエッチングチャンバー54から第一の移動領域52を経由して、クールチャンバー55内に搬入する。クールチャンバー55内では、シリコン基板を100℃まで冷却する(図3のS4、図8)。

【0027】

シリコン基板を、図4のクールチャンバー55から第二の移動領域56を経由して、Ti成膜チャンバー57内の、静電チャック機能を有するステージに搬送し、静電チャックを介してステージ上にシリコン基板を保持する。Ti成膜チャンバー57のステージとシリコン基板間の隙間にArガスを流しながら、ガス伝導によりシリコン基板を23℃付近に維持する。このときのArガスの供給圧力は3〜10Torrの間で加圧調整することが好ましい。続いて、コンタクトホール内及び層間絶縁膜上の全面に、成膜条件を膜厚20nm、成膜温度23℃、ターゲット電力35kW(電力密度:29.6W/cm2)として、スパッタリングによりTi膜を成膜する(図3のS5、図9)。Tiの成膜条件はこれに限定されるわけではなく、膜厚5〜30nmの範囲、成膜温度0〜100℃の範囲、ターゲット電力5〜40kW(電力密度:4.2〜33.8W/cm2)の範囲とすることができる。

【0028】

シリコン基板を、図4のTi成膜チャンバー57から第二の移動領域56を経由して、シードAl膜成膜チャンバー58に搬送する(図3のS6、図10)。このときの成膜条件は、膜厚300nm、成膜温度23℃、ターゲット電力35kW(電力密度23.3W/cm2)とした。シードAl膜の成膜条件はこれに限定されるわけではなく、膜厚は150nmから400nmの範囲、成膜温度は0℃から100℃の範囲、ターゲット電力は30kWから40kW(電力密度:20W/cm2から33.8W/cm2)の範囲とすることができる。

【0029】

シリコン基板を、図4のシードAl膜成膜チャンバー58から第二の移動領域56を経由して、静電チャック機能と加熱機能を有するAlリフロースパッタ用チャンバー59のステージ上に搬送する。静電チャックにより、ステージ上にシリコン基板を保持する。

【0030】

次に、同一のチャンバー59内でシリコン基板の加熱、リフロースパッタ法による第一のAl膜と第二のAl膜の成膜を順に行う。以下、図11〜14を参照して、各工程を説明する。

【0031】

図11は、第一及び第二のAl膜の成膜のリフロースパッタ条件を表す図である。図11のAはステージの温度、Bはターゲットに対して印加するターゲット電力、Cは静電チャックを介してシリコン基板に印加するESC電圧、Dはステージ圧力(シリコン基板とステージの間に流すArガスの圧力)を表す。

【0032】

まず、加熱条件を加熱温度430℃で、ESC電圧を第一の電圧E1、第二の電圧E2、第三の電圧E3と、この順に3段階のステップ状に増加させる(工程(1))。ESC電圧が第三の電圧E3となった後に、ステージとシリコン基板間の隙間にArガスを流しガス伝導により、シリコン基板を加熱する(図3のS7、図11及び12)させる。加熱時間約60sで、チャンバー内のこの際、Al膜の一部と先に成膜したTi膜とが反応して、TiAl328が形成される。このシリコン基板の加熱中にシリコン基板の加熱条件はこれに限定されるわけではなく、温度は400〜450℃の範囲、加熱時間は30〜90sの範囲としても良い。

【0033】

加熱により430℃に維持した状態で、ターゲットに対して第一のターゲット電力を印加することにより、第一のAl膜の成膜として、低レートのAlリフロースパッタリングによるAl膜の成膜を行う(第一のAlリフロースパッタリング;工程(2);図3のS8、図11及び13)。これにより、コンタクトホール内は第一のAl膜で埋め込まれる。第一のAl膜の成膜条件は、膜厚200nm、温度430℃、ターゲット電力は5kWで成膜とする。第一のAl膜の成膜条件はこれに限定されるわけではなく、例えば、1回目の成膜条件は膜厚100〜300nm、温度400〜450℃の範囲、第一のターゲット電力2〜8kW(電力密度:1.33〜5.32W/cm2)の範囲とすることができる。

【0034】

続いて、加熱により430℃に維持した状態で、ターゲットに対して第一のターゲット電力よりも大きな第二のターゲット電力を印加することにより、第二のAl膜の成膜として、高レートのAlリフロースパッタリングによるAl膜の成膜を行う(第二のAlリフロースパッタリング;工程(3);図3のS9、図11及び14)。この成膜条件は、膜厚400nm、温度430℃、ターゲット電力20kW(電力密度13.3W/cm2)とする。第二のAl膜の成膜条件はこれに限定されるわけではなく、例えば、膜厚200〜600nmの範囲、温度400〜450℃の範囲、第二のターゲット電力15〜25kW(電力密度:9.98〜16.6W/cm2)の範囲とすることができる。

【0035】

シリコン基板を、図4のAlリフロースパッタ用チャンバー59から第二の移動領域56を経由して、クーリングチャンバー60に搬送する。冷却条件を温度23℃、ステージ圧力3Torr、時間30秒に設定して、シリコン基板を200℃以下まで冷却する(図3のS10、図15)。冷却条件はこれに限定されるわけではなく、ステージ圧力は1〜5Torrの間、時間5〜30秒とすることができる。

【0036】

シリコン基板を、図4のクーリングチャンバー60から第一の移動領域52を経由して、TiN成膜チャンバー61に搬送する。シリコン基板を、TiN成膜チャンバー61のステージに搬送し、静電チャックによりステージ上にシリコン基板を保持する。成膜条件を膜厚30nm、成膜温度23℃、ターゲット電力15kW(電力密度:11.6W/cm2)として、反射防止膜であるTiN膜を成膜する(図3のS11、図16)。成膜条件はこれに限定されるわけではなく、膜厚20〜70nmの範囲、成膜温度0〜200℃の範囲、ターゲット電力:10〜20kW(電力密度:7.70〜15.4W/cm2)の範囲とすることができる。

【0037】

シリコン基板を、図4のTiN成膜チャンバー61から第一の移動領域52を経由して、ロードロックチャンバー62に搬送する。冷却条件を温度23℃、ステージ圧力4Torr、時間10sとして、シリコン基板を冷却する(図3のS12、図17)。冷却条件はこれに限定されるわけではなく、ステージ圧力は2〜10Torrの範囲、時間は5〜30sの範囲とすることができる。

【0038】

冷却後のシリコン基板を、図4のロードロックチャンバー62からロードポートB 63に搬送した後、半導体製造装置から外部に搬送する(図3のS13)。

【0039】

図18に示すように、積層した各材料に対してリソグラフィー技術を用いたエッチングすることにより、コンタクトプラグを形成する。

【符号の説明】

【0040】

10 スパッタ装置

12 ステージ

13 基板

14 チャンバー

15 ポンプ

16 DC電源

17 マグネット

20 シリコン基板

21 Ti膜

22 TiN膜

23 Al膜

24 TiN膜

25 層間絶縁膜

26 コンタクトホール

50 ロードポートA

51 ロードロックチャンバー

52 第一の移動領域

53 脱ガスチャンバー

54 RF エッチングチャンバー

55 クールチャンバー

56 第二の移動領域

57 Ti成膜チャンバー

58 シードAl膜成膜チャンバー

59 Alリフロースパッタ用チャンバー

60 クーリングチャンバー

61 TiN成膜チャンバー

62 ロードロックチャンバー

63 ロードポートB

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

従来から、コンタクトホール等の微細な構造へ導電材料を埋設する際に、コンタクトホール内にボイドが発生するなどの問題点が指摘されていた。そこで、微細なコンタクトホールへの導電材料の埋設性を確保するために、Alリフロースパッタ法を用いた方法が提案されている。Alリフロースパッタ法は、Al膜を堆積させると共に高温加熱により堆積させたAl膜を流動化させることにより、埋設性・平坦性に優れたAl膜を形成できるという特徴を有する。

【0003】

例えば、特許文献1(特開平7−29853号公報)、および特許文献2(特開平11−243070号公報)には、窒化チタン膜を用いることにより、微細コンタクトホールへのAlリフロースパッタ法を用いたAlの埋設性を確保している。

【0004】

また、特許文献3(特開平7−176615号公報)では、高温スパッタTiを用いAl表面モホロジーを確保している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平7−29853号公報

【特許文献2】特開平11−243070号公報

【特許文献3】特開平7−176615号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

図1及び2はそれぞれ、上記特許文献1〜3のような従来のAlリフロースパッタ法を実施した状況を表す概略図、及びスパッタ条件を表す図である。図2中のAはチャンバー14内を流すArガスの温度、Bはターゲット11に印加するターゲット電力、Cは静電チャック(図1中には図示していない)を介して基板に印加するESC電圧、Dはステージ圧力を表す。

【0007】

図1及び2に示すように、従来のAlリフロースパッタ法では、スパッタ装置10のチャンバー14内のステージ12上に静電チャックにより、基板13を配置する。ステージ12と基板13間に高温のArガスを流すことにより、基板の温度を高温に保つ。この状態でESC電圧Cを一定値に設定した後、ステージ圧力(ウェハとステージの間に流すガスの圧力)Dを一定値まで上昇させる。次に、チャンバー内のターゲットに対して一定のターゲット電力Bを印加することで、Al膜の成膜を行う。

【0008】

上記のような従来のAlリフロースパッタ法では、ESC電圧Cを1段階で一定値に設定すると、ステージ12上で基板13が割れる、という現象が発生していた。この結果、Alリフロースパッタの生産性が低下することとなっていた。また、従来のAlリフロースパッタ法では、ターゲット電力を高く設定しAl成膜の温度を高温にすることでAl膜の埋設性を確保していたが、ウェハ割れにより生産性が低下する、という問題点があった。

【0009】

本発明は上記課題に鑑みてなされたものであり、ESC電圧を3段階にステップ状に増加させ、低レートと高レートの2種類のAlリフロースパッタ法を行うことで、微細なコンタクトホールへのAl材料の埋設性を高めるものである。

【課題を解決するための手段】

【0010】

一実施形態は、

基 基板の層間絶縁膜内にコンタクトホールを形成する工程と、

前記コンタクトホールの内壁上に順に、バリアメタル膜及びシードAl膜を形成する工程と、

前記基板を加熱した状態で、下記(1)〜(3)の工程を順に行うことにより、コンタクトプラグを形成する工程と、

(1)スパッタ装置のチャンバー内のステージ上に、チャックを介して前記基板を保持し、前記チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる工程、

(2)前記チャンバー内のターゲットに対して第一のターゲット電力を印加して前記コンタクトホール内を埋め込むように第一のAl膜を成膜する工程、

(3)前記チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して前記第一のAl膜上に第二のAl膜を成膜する工程、

を有する半導体装置の製造方法に関する。

【発明の効果】

【0011】

高い生産性で、コンタクトホール内にAl膜が良好に埋設されたコンタクトプラグを有する半導体装置を提供する。

【図面の簡単な説明】

【0012】

【図1】従来のAlリフロースパッタ法を使用する場合の問題点を表す図である。

【図2】従来のAlリフロースパッタ法によるスパッタ条件を表す図である。

【図3】本発明の半導体装置の製造方法の一例を表すフローチャートである。

【図4】図3の各工程を実施する装置を表す図である。

【図5】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図6】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図7】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図8】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図9】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図10】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図11】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図12】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図13】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図14】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図15】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図16】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図17】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【図18】本発明の半導体装置の製造方法の一例の一工程を表す図である。

【発明を実施するための形態】

【0013】

半導体装置の製造方法では、基板を加熱冷却後に、コンタクトホールの内壁上に順に、バリアメタル膜及びシードAl膜を形成する。バリアメタル膜としては、Ti膜、Ti膜/TiN膜、又は、Ti膜/TiN膜/Ti膜(何れの積層膜もコンタクトホールの内壁側から順に記載)を挙げることができる。シードAl膜等の埋設マージンを大幅に拡大することができるため、Ti膜/TiN膜/Ti膜の積層膜からなるバリアメタル膜が好ましい。バリアメタル膜の膜厚は5〜30nmであることが好ましく、シードAl膜の膜厚は150〜300nmであることが好ましい。コンタクトホールのアスペクト比は3以下であることが好ましい。バリアメタル膜とシードAl膜の膜厚、及びコンタクトホールのアスペクト比がこれらの範囲内にあることにより、後の工程(2)で、良好に第一のAl膜の成膜を行うことができる。

【0014】

この後、基板を加熱した状態で下記の3つの工程(1)〜(3)を順に行う。これにより、コンタクトプラグを形成する。なお、加熱により、下記工程(1)〜(3)の間、基板は一定温度に維持される。

【0015】

工程(1)

Al成膜の前処理工程であり、チャンバー内のステージ上に静電チャックを介して基板を保持し、静電チャックを介して基板に印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。このように、段階的にステージ電圧を変化させることにより、基板に印加される電圧は徐々に増加していくため、基板内には内部応力が生じにくくなる。この結果、ステージ上での基板の反りによる割れが発生しなくなる。

【0016】

第二の電圧は第一の電圧の1.5〜2.5倍であることが好ましく、第三の電圧は第一の電圧の3.5〜4.5倍であることが好ましい。また、第二の電圧は第一の電圧の2倍であり、第三の電圧は第一の電圧の4倍であることがより好ましい。第一、第二、及び第三の電圧をこれらの範囲内に設定することにより、ステージ上での基板の反りによる割れを効果的に防止することができる。

【0017】

工程(2)

第一のAlの成膜工程であり、チャンバー内のターゲットに対して第一のターゲット電力を印加して、コンタクトホール内に第一のAl膜を成膜する。第一のAlの成膜工程では、第一のターゲット電力を低めに制御することにより、低い成膜レートでAl膜を成膜する。これにより、コンタクトホール内にボイドを発生させることなく、良好な埋設性でコンタクトホール内にAl膜を埋設させることができる。第一のAl膜の成膜レートは、5nm/sであることが好ましい。5nm/sとすることにより、コンタクトホールへAl膜を良好な埋設性を確保することができる。

【0018】

工程(3)

第二のAlの成膜工程であり、チャンバー内のターゲットに対して、第一のターゲット電力よりも高い第二のターゲット電力を印加して、第一のAl膜上に第二のAl膜を成膜する。第二のAlの成膜工程では、チャンバー内に高めのターゲット電力を印加することにより、高い成膜レートでAlを成膜する。工程(2)において、コンタクトホール内は既に埋設性に優れた第一のAl膜で埋設されている。このため、工程(3)では、高い成膜レートにして短時間で効率よく第一のAl膜上に第二のAl膜を形成することができる。さらに、ESC電圧及びターゲット電力を制御することで、従来よりも工程(2)及び(3)の温度を低温で処理することができ、ウェハ割れの発生やパーツ寿命を改善することができる。この結果、半導体装置の生産性を高めることができます。

【0019】

第二のAl膜の成膜レートは、17nm/sであることが好ましい。17nm/sとすることにより、短時間でAl膜を成膜することができ、生産性を向上させることができる。

【0020】

第二のターゲット電力は、第一のターゲット電力の4〜5倍であることが好ましく、4.8倍であることがより好ましい。第一及び第二のターゲット電力がこれらの範囲内であることによって、コンタクトホール内の埋設性を確保しつつ、Alの成膜時間を短縮して生産性をより向上させることができる。

【0021】

工程(1)〜(3)における、チャンバー内のステージ温度は400〜450℃であることが好ましく、430℃であることがより好ましい。

【0022】

以下、図3〜18を参照して、半導体装置の製造方法の一例を説明する。図3は、半導体装置の製造方法の各工程を表すフローチャートである。図4は、半導体装置の製造装置を表す概略図である。図5〜18は、半導体装置の製造方法における各工程を表す図である。

【0023】

まず、シリコン基板20上に、Ti膜21、TiN膜22、Al膜23及びTiN膜24が積層された配線層を有する層間絶縁膜25を形成する。RIE工程を実施することにより、層間絶縁膜25内にコンタクトホール26を形成する(図5)。

【0024】

このシリコン基板を図4のロードポートA 50からロードロックチャンバー51に搬送する。シリコン基板を、第一の移動領域52を経由して、脱ガスチャンバー53に搬入する(図3のS1)。脱ガスチャンバー53内では、温度450℃、圧力8Torr、時間90sの条件で、シリコン基板に対して脱ガス処理を行う(図3のS2、図6)。脱ガス条件はこれに限定されるわけではなく、例えば、温度400〜500℃の範囲、圧力3〜10Torrの範囲、時間20〜120sの範囲とすることができる。

【0025】

シリコン基板を、図4の脱ガスチャンバー53から第一の移動領域52を経由して、RFエッチングチャンバー54内に搬入する。RFエッチングチャンバー54内では、Arスパッタエッチングを行う(図3のS3、図7)。これにより、コンタクトホールの底部に露出している配線層の表面酸化膜を除去すると共に、コンタクトホールの開口径を拡大させて、後の工程で良好なAl埋設性を確保することができる。この時のArスパッタエッチングのエッチング量を酸化膜換算で20nmとしたが、エッチング量はこれに限定されるわけではなく、5nmから40nmの範囲としても良い。

【0026】

シリコン基板を、図4のRFエッチングチャンバー54から第一の移動領域52を経由して、クールチャンバー55内に搬入する。クールチャンバー55内では、シリコン基板を100℃まで冷却する(図3のS4、図8)。

【0027】

シリコン基板を、図4のクールチャンバー55から第二の移動領域56を経由して、Ti成膜チャンバー57内の、静電チャック機能を有するステージに搬送し、静電チャックを介してステージ上にシリコン基板を保持する。Ti成膜チャンバー57のステージとシリコン基板間の隙間にArガスを流しながら、ガス伝導によりシリコン基板を23℃付近に維持する。このときのArガスの供給圧力は3〜10Torrの間で加圧調整することが好ましい。続いて、コンタクトホール内及び層間絶縁膜上の全面に、成膜条件を膜厚20nm、成膜温度23℃、ターゲット電力35kW(電力密度:29.6W/cm2)として、スパッタリングによりTi膜を成膜する(図3のS5、図9)。Tiの成膜条件はこれに限定されるわけではなく、膜厚5〜30nmの範囲、成膜温度0〜100℃の範囲、ターゲット電力5〜40kW(電力密度:4.2〜33.8W/cm2)の範囲とすることができる。

【0028】

シリコン基板を、図4のTi成膜チャンバー57から第二の移動領域56を経由して、シードAl膜成膜チャンバー58に搬送する(図3のS6、図10)。このときの成膜条件は、膜厚300nm、成膜温度23℃、ターゲット電力35kW(電力密度23.3W/cm2)とした。シードAl膜の成膜条件はこれに限定されるわけではなく、膜厚は150nmから400nmの範囲、成膜温度は0℃から100℃の範囲、ターゲット電力は30kWから40kW(電力密度:20W/cm2から33.8W/cm2)の範囲とすることができる。

【0029】

シリコン基板を、図4のシードAl膜成膜チャンバー58から第二の移動領域56を経由して、静電チャック機能と加熱機能を有するAlリフロースパッタ用チャンバー59のステージ上に搬送する。静電チャックにより、ステージ上にシリコン基板を保持する。

【0030】

次に、同一のチャンバー59内でシリコン基板の加熱、リフロースパッタ法による第一のAl膜と第二のAl膜の成膜を順に行う。以下、図11〜14を参照して、各工程を説明する。

【0031】

図11は、第一及び第二のAl膜の成膜のリフロースパッタ条件を表す図である。図11のAはステージの温度、Bはターゲットに対して印加するターゲット電力、Cは静電チャックを介してシリコン基板に印加するESC電圧、Dはステージ圧力(シリコン基板とステージの間に流すArガスの圧力)を表す。

【0032】

まず、加熱条件を加熱温度430℃で、ESC電圧を第一の電圧E1、第二の電圧E2、第三の電圧E3と、この順に3段階のステップ状に増加させる(工程(1))。ESC電圧が第三の電圧E3となった後に、ステージとシリコン基板間の隙間にArガスを流しガス伝導により、シリコン基板を加熱する(図3のS7、図11及び12)させる。加熱時間約60sで、チャンバー内のこの際、Al膜の一部と先に成膜したTi膜とが反応して、TiAl328が形成される。このシリコン基板の加熱中にシリコン基板の加熱条件はこれに限定されるわけではなく、温度は400〜450℃の範囲、加熱時間は30〜90sの範囲としても良い。

【0033】

加熱により430℃に維持した状態で、ターゲットに対して第一のターゲット電力を印加することにより、第一のAl膜の成膜として、低レートのAlリフロースパッタリングによるAl膜の成膜を行う(第一のAlリフロースパッタリング;工程(2);図3のS8、図11及び13)。これにより、コンタクトホール内は第一のAl膜で埋め込まれる。第一のAl膜の成膜条件は、膜厚200nm、温度430℃、ターゲット電力は5kWで成膜とする。第一のAl膜の成膜条件はこれに限定されるわけではなく、例えば、1回目の成膜条件は膜厚100〜300nm、温度400〜450℃の範囲、第一のターゲット電力2〜8kW(電力密度:1.33〜5.32W/cm2)の範囲とすることができる。

【0034】

続いて、加熱により430℃に維持した状態で、ターゲットに対して第一のターゲット電力よりも大きな第二のターゲット電力を印加することにより、第二のAl膜の成膜として、高レートのAlリフロースパッタリングによるAl膜の成膜を行う(第二のAlリフロースパッタリング;工程(3);図3のS9、図11及び14)。この成膜条件は、膜厚400nm、温度430℃、ターゲット電力20kW(電力密度13.3W/cm2)とする。第二のAl膜の成膜条件はこれに限定されるわけではなく、例えば、膜厚200〜600nmの範囲、温度400〜450℃の範囲、第二のターゲット電力15〜25kW(電力密度:9.98〜16.6W/cm2)の範囲とすることができる。

【0035】

シリコン基板を、図4のAlリフロースパッタ用チャンバー59から第二の移動領域56を経由して、クーリングチャンバー60に搬送する。冷却条件を温度23℃、ステージ圧力3Torr、時間30秒に設定して、シリコン基板を200℃以下まで冷却する(図3のS10、図15)。冷却条件はこれに限定されるわけではなく、ステージ圧力は1〜5Torrの間、時間5〜30秒とすることができる。

【0036】

シリコン基板を、図4のクーリングチャンバー60から第一の移動領域52を経由して、TiN成膜チャンバー61に搬送する。シリコン基板を、TiN成膜チャンバー61のステージに搬送し、静電チャックによりステージ上にシリコン基板を保持する。成膜条件を膜厚30nm、成膜温度23℃、ターゲット電力15kW(電力密度:11.6W/cm2)として、反射防止膜であるTiN膜を成膜する(図3のS11、図16)。成膜条件はこれに限定されるわけではなく、膜厚20〜70nmの範囲、成膜温度0〜200℃の範囲、ターゲット電力:10〜20kW(電力密度:7.70〜15.4W/cm2)の範囲とすることができる。

【0037】

シリコン基板を、図4のTiN成膜チャンバー61から第一の移動領域52を経由して、ロードロックチャンバー62に搬送する。冷却条件を温度23℃、ステージ圧力4Torr、時間10sとして、シリコン基板を冷却する(図3のS12、図17)。冷却条件はこれに限定されるわけではなく、ステージ圧力は2〜10Torrの範囲、時間は5〜30sの範囲とすることができる。

【0038】

冷却後のシリコン基板を、図4のロードロックチャンバー62からロードポートB 63に搬送した後、半導体製造装置から外部に搬送する(図3のS13)。

【0039】

図18に示すように、積層した各材料に対してリソグラフィー技術を用いたエッチングすることにより、コンタクトプラグを形成する。

【符号の説明】

【0040】

10 スパッタ装置

12 ステージ

13 基板

14 チャンバー

15 ポンプ

16 DC電源

17 マグネット

20 シリコン基板

21 Ti膜

22 TiN膜

23 Al膜

24 TiN膜

25 層間絶縁膜

26 コンタクトホール

50 ロードポートA

51 ロードロックチャンバー

52 第一の移動領域

53 脱ガスチャンバー

54 RF エッチングチャンバー

55 クールチャンバー

56 第二の移動領域

57 Ti成膜チャンバー

58 シードAl膜成膜チャンバー

59 Alリフロースパッタ用チャンバー

60 クーリングチャンバー

61 TiN成膜チャンバー

62 ロードロックチャンバー

63 ロードポートB

【特許請求の範囲】

【請求項1】

基板の層間絶縁膜内にコンタクトホールを形成する工程と、

前記コンタクトホールの内壁上に順に、バリアメタル膜及びシードAl膜を形成する工程と、

前記基板を加熱した状態で、下記(1)〜(3)の工程を順に行うことにより、コンタクトプラグを形成する工程と、

(1)スパッタ装置のチャンバー内のステージ上に、チャックを介して前記基板を保持し、前記チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる工程、

(2)前記チャンバー内のターゲットに対して第一のターゲット電力を印加して前記コンタクトホール内を埋め込むように第一のAl膜を成膜する工程、

(3)前記チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して前記第一のAl膜上に第二のAl膜を成膜する工程、

を有する半導体装置の製造方法。

【請求項2】

前記工程(1)において、

第二の電圧は、第一の電圧の1.5〜2.5倍である、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記工程(1)において、

第三の電圧は、第一の電圧の3.5〜4.5倍である、請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記工程(1)において、

第二の電圧は、第一の電圧の2倍であり、

第三の電圧は、第一の電圧の4倍である、請求項1〜3の何れか1項に記載の半導体装置の製造方法。

【請求項5】

前記工程(3)において、

第二のターゲット電力は、第一のターゲット電力の4〜5倍である、請求項1〜4の何れか1項に記載の半導体装置の製造方法。

【請求項6】

前記工程(3)において、

第二のターゲット電力は、第一のターゲット電力の4.8倍である、請求項5に記載の半導体装置の製造方法。

【請求項7】

前記工程(2)において、

前記第一のAl膜の成膜レートは、5nm/sである、請求項1〜6の何れか1項に記載の半導体装置の製造方法。

【請求項8】

前記工程(3)において、

前記第二のAl膜の成膜レートは、17nm/sである、請求項1〜7の何れか1項に記載の半導体装置の製造方法。

【請求項9】

前記工程(1)〜(3)において、前記チャンバー内のステージ温度は400〜450℃である、請求項1〜8の何れか1項に記載の半導体装置の製造方法。

【請求項10】

前記工程(1)〜(3)において、前記チャンバー内のステージ温度は430℃である、請求項9に記載の半導体装置の製造方法。

【請求項11】

前記コンタクトホールを形成する工程の前に、

配線層を形成する工程と、

前記配線層上に前記層間絶縁膜を形成する工程と、

を有し、

前記コンタクトホールを形成する工程において、

前記層間絶縁膜内に、前記配線層を露出させるように前記コンタクトホールを形成する、請求項1〜10の何れか1項に記載の半導体装置の製造方法。

【請求項12】

前記配線層は、前記コンタクトホール側から順に、TiN膜、第三のAl膜、及びTi膜を有する、請求項11に記載の半導体装置の製造方法。

【請求項13】

前記コンタクトプラグを形成する工程の後に、

前記第二のAl膜上に、スパッタ法により、TiN膜を形成する工程を有する、請求項1〜12の何れか1項に記載の半導体装置の製造方法。

【請求項14】

前記Ti膜の膜厚は5〜30nmである、請求項12に記載の半導体装置の製造方法。

【請求項15】

前記シードAl膜の膜厚は150〜300nmである、請求項1〜14の何れか1項に記載の半導体装置の製造方法。

【請求項16】

前記コンタクトホールのアスペクト比は3以下である、請求項1〜15の何れか1項に記載の半導体装置の製造方法。

【請求項1】

基板の層間絶縁膜内にコンタクトホールを形成する工程と、

前記コンタクトホールの内壁上に順に、バリアメタル膜及びシードAl膜を形成する工程と、

前記基板を加熱した状態で、下記(1)〜(3)の工程を順に行うことにより、コンタクトプラグを形成する工程と、

(1)スパッタ装置のチャンバー内のステージ上に、チャックを介して前記基板を保持し、前記チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる工程、

(2)前記チャンバー内のターゲットに対して第一のターゲット電力を印加して前記コンタクトホール内を埋め込むように第一のAl膜を成膜する工程、

(3)前記チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して前記第一のAl膜上に第二のAl膜を成膜する工程、

を有する半導体装置の製造方法。

【請求項2】

前記工程(1)において、

第二の電圧は、第一の電圧の1.5〜2.5倍である、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記工程(1)において、

第三の電圧は、第一の電圧の3.5〜4.5倍である、請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記工程(1)において、

第二の電圧は、第一の電圧の2倍であり、

第三の電圧は、第一の電圧の4倍である、請求項1〜3の何れか1項に記載の半導体装置の製造方法。

【請求項5】

前記工程(3)において、

第二のターゲット電力は、第一のターゲット電力の4〜5倍である、請求項1〜4の何れか1項に記載の半導体装置の製造方法。

【請求項6】

前記工程(3)において、

第二のターゲット電力は、第一のターゲット電力の4.8倍である、請求項5に記載の半導体装置の製造方法。

【請求項7】

前記工程(2)において、

前記第一のAl膜の成膜レートは、5nm/sである、請求項1〜6の何れか1項に記載の半導体装置の製造方法。

【請求項8】

前記工程(3)において、

前記第二のAl膜の成膜レートは、17nm/sである、請求項1〜7の何れか1項に記載の半導体装置の製造方法。

【請求項9】

前記工程(1)〜(3)において、前記チャンバー内のステージ温度は400〜450℃である、請求項1〜8の何れか1項に記載の半導体装置の製造方法。

【請求項10】

前記工程(1)〜(3)において、前記チャンバー内のステージ温度は430℃である、請求項9に記載の半導体装置の製造方法。

【請求項11】

前記コンタクトホールを形成する工程の前に、

配線層を形成する工程と、

前記配線層上に前記層間絶縁膜を形成する工程と、

を有し、

前記コンタクトホールを形成する工程において、

前記層間絶縁膜内に、前記配線層を露出させるように前記コンタクトホールを形成する、請求項1〜10の何れか1項に記載の半導体装置の製造方法。

【請求項12】

前記配線層は、前記コンタクトホール側から順に、TiN膜、第三のAl膜、及びTi膜を有する、請求項11に記載の半導体装置の製造方法。

【請求項13】

前記コンタクトプラグを形成する工程の後に、

前記第二のAl膜上に、スパッタ法により、TiN膜を形成する工程を有する、請求項1〜12の何れか1項に記載の半導体装置の製造方法。

【請求項14】

前記Ti膜の膜厚は5〜30nmである、請求項12に記載の半導体装置の製造方法。

【請求項15】

前記シードAl膜の膜厚は150〜300nmである、請求項1〜14の何れか1項に記載の半導体装置の製造方法。

【請求項16】

前記コンタクトホールのアスペクト比は3以下である、請求項1〜15の何れか1項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−248613(P2012−248613A)

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願番号】特願2011−118009(P2011−118009)

【出願日】平成23年5月26日(2011.5.26)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願日】平成23年5月26日(2011.5.26)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]