半導体装置の製造方法

【課題】CMP法により、金属膜を研磨して、層間絶縁膜に設けられた開口部内に導体パターンを形成する際、リセス、ディッシング、及びエロージョンを抑制可能な半導体装置の製造方法を提供する。

【解決手段】CMP法により、層間絶縁膜14の上面よりも上方に形成された金属膜19及びバリア膜18を除去することで、開口部内に、バリア膜18及び金属膜19よりなる導体パターンを形成する研磨工程と、を有し、該研磨工程では、層間絶縁膜14の上面が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことで、導体パターンを形成する。

【解決手段】CMP法により、層間絶縁膜14の上面よりも上方に形成された金属膜19及びバリア膜18を除去することで、開口部内に、バリア膜18及び金属膜19よりなる導体パターンを形成する研磨工程と、を有し、該研磨工程では、層間絶縁膜14の上面が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことで、導体パターンを形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、半導体基板上に設けられた層間絶縁膜に開口部(溝、或いはコンタクト孔)の内面を覆うバリア膜を成膜し、次いで、バリア膜を介して、開口部を埋め込む金属膜を形成し、その後、CMP(Chemical Mechanical Polishing)法により、開口部以外の部分に形成された余分なバリア膜及び金属膜を研磨除去することで、開口部を埋め込むバリア膜及び金属膜よりなる導体パターン(配線、或いはコンタクトプラグ)を形成することが行なわれている。

【0003】

また、従来、上記方法により導体パターンを形成する際、CMP処理を2段階以上に分けて行うことが行なわれている(例えば、特許文献1参照)。

例えば、2段階に分けてCMP処理を行なう場合、第1段階として、層間絶縁膜の研磨レートよりも金属膜の研磨レートが大きい条件を用いて研磨を行う。次いで、層間絶縁膜の上面、或いは層間絶縁膜の上面に形成されたバリア膜が露出した段階で、金属膜の研磨レートと層間絶縁膜の研磨レートとの差の小さい条件を用いて、第2段階の研磨を行なう。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−306869号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、層間絶縁膜の研磨レートよりも金属膜の研磨レートが大きい条件を用いて上記第1段階のCMP処理を行なった場合、層間絶縁膜の上面、或いは、層間絶縁膜の上面に形成されたバリア膜が露出した時点で、開口部に埋め込まれた金属膜が過剰に研磨されてしまうため、リセスが発生してしまうという問題があった。また、開口部のうち、幅或いは径が大きい部分では、ディッシングが発生しやすいという問題があった。

【0006】

さらに、開口部がコンタクト孔であって、該コンタクト孔に形成されたコンタクトプラグの密度が高い領域では、エロージョンが発生しやすいという問題があった。

また、今後、半導体装置を構成する素子(例えば、トランジスタ素子)の微細化がさらに進展した際、コンタクトプラグの面内密度が高い部分では、上記エロージョンの問題が顕著となる。

【課題を解決するための手段】

【0007】

本発明の一観点によれば、層間絶縁膜に開口部を形成する工程と、前記開口部を埋め込む厚さとされた金属膜を形成する工程と、CMP法により、前記層間絶縁膜の上面よりも上方に形成された前記金属膜を研磨除去することで、前記開口部内に導体パターンを形成する研磨工程と、を有し、前記研磨工程では、前記層間絶縁膜の上面が露出する前に、前記金属膜の研磨レートと前記層間絶縁膜の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0008】

本発明の半導体装置の製造方法によれば、CMP法により、層間絶縁膜の上面よりも上方に形成された金属膜を研磨除去することで、層間絶縁膜に形成された開口部内に導体パターンを形成する研磨工程において、層間絶縁膜の上面が露出する前に、金属膜の研磨レートと層間絶縁膜の研磨レートとの差が小さい条件を用いて研磨を行なうことで、層間絶縁膜の上面が露出された際、開口部内に形成された金属膜、及び金属膜が形成された開口部が密集した領域が過剰に研磨されることを抑制可能となる。これにより、リセス、ディッシング、及びエロージョンを抑制することができる。

【図面の簡単な説明】

【0009】

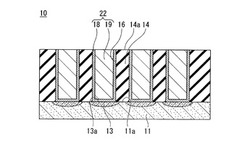

【図1】本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図(その1)である。

【図2】本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図(その2)である。

【図3】本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図(その3)である。

【図4】本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図(その4)であり、研磨工程の第1段階を説明するための図である。

【図5】本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図(その5)であり、研磨工程の第2段階を説明するための図である。

【図6】本実施の形態で使用する研磨布の構成を説明するための断面図である。

【図7】本発明の第1の実施の形態の変形例に係る半導体装置の製造工程を示す断面図であり、研磨工程の第1段階を説明するための図である。

【図8】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その1)である。

【図9】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その2)である。

【図10】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その3)である。

【図11】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その4)である。

【図12】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その5)であり、研磨工程の第1段階を説明するための図である。

【図13】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その6)であり、研磨工程の第2段階を説明するための図である。

【図14】本発明の第2の実施の形態の変形例に係る半導体装置の製造工程を示す断面図であり、研磨工程の第1段階を説明するための図である。

【発明を実施するための形態】

【0010】

以下、図面を参照して本発明を適用した実施の形態について詳細に説明する。なお、以下の説明で用いる図面は、本発明の実施の形態の構成を説明するためのものであり、図示される各部の大きさや厚さや寸法等は、実際の半導体装置の寸法関係とは異なる場合がある。

【0011】

(第1の実施の形態)

図1〜図5は、本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図である。また、図4は、研磨工程の第1段階を説明するための図であり、図5は、研磨工程の第2段階を説明するための図である。

【0012】

図1〜図5を参照して、第1の実施の形態の半導体装置10(図5参照)の製造方法について説明する。

始めに、図1に示す工程では、半導体基板11に、不純物拡散層13を構成要素として含むトランジスタ素子(図示せず)を形成する。半導体基板11としては、例えば、シリコン基板を用いる。また、不純物拡散層13は、半導体基板11とは異なる導電型の不純物を半導体基板11の表面11aにイオン注入することで形成する。

【0013】

次いで、半導体基板11の表面11a、及び不純物拡散層13の上面13aを覆うように、層間絶縁膜14を形成する。具体的には、層間絶縁膜14は、例えば、CVD(Chemical Vapor Deposition)法により形成する。また、層間絶縁膜14としては、例えば、シリコン酸化膜(SiO2膜)を用いることができる。

【0014】

次いで、図2に示す工程では、層間絶縁膜14に、不純物拡散層13の上面13aを露出する開口部としてコンタクト孔16を複数形成する。

具体的には、層間絶縁膜14の上面14aに、コンタクト孔16の形成領域に対応する層間絶縁膜14の上面14aを露出する複数の開口孔(図示せず)を有したフォトレジスト(図示せず)を形成する。次いで、該フォトレジストをマスクとする異方性エッチング(例えば、ドライエッチング)により、層間絶縁膜14をエッチングすることで、複数のコンタクト孔16を形成する。フォトレジスト(図示せず)は、複数のコンタクト孔16を形成後に除去する。

【0015】

次いで、図3に示す工程では、層間絶縁膜14の上面14a、及びコンタクト孔16の内面(コンタクト孔16から露出された不純物拡散層13の上面13aを含む)を覆うバリア膜18を形成する。

具体的には、例えば、CVD法により、バリア膜18を形成する。バリア膜18は、金属膜19がタングステン膜(W膜)の場合、例えば、Ti膜と、TiN膜と、を順次積層させたTi/TiN積層膜を用いることができる。

【0016】

次いで、バリア膜18の表面18aに、複数のコンタクト孔16を埋め込む厚さとされた金属膜19を形成する。具体的には、例えば、CVD法により、金属膜19としてタングステン膜を形成する。

【0017】

次いで、図4に示す工程では、研磨工程の第1段階として、層間絶縁膜14の研磨レートよりも金属膜19の研磨レートが大きい研磨条件を用いて、CMP法により、層間絶縁膜14の上面14aに形成されたバリア膜18の表面18aが露出されるまで、金属膜19の研磨を行なう。

層間絶縁膜14の研磨レートよりも金属膜19の研磨レートが大きい研磨条件は、例えば、研磨液(スラリー)に含まれる酸化剤の量を多くすることで実現できる。

【0018】

次いで、図5に示す工程では、研磨工程の第2段階として、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件(言い換えれば、金属膜19の研磨レートと層間絶縁膜14の研磨レートとが略等しくなる研磨条件)を用いて、CMP法により、層間絶縁膜14の上面14aに形成されたバリア膜18を研磨除去し、コンタクト孔16内にのみバリア膜18及び金属膜19を残存させることで、コンタクト孔16内にバリア膜18及び金属膜19よりなるコンタクトプラグ22(導体パターン)を形成する。

【0019】

このとき、半導体基板11の面内の全てにおいて、バリア膜18が除去されるように、ある程度のオーバー研磨を行なう。これにより、コンタクト孔16内に形成されたバリア膜18及び金属膜19と層間絶縁膜14とが略同じ速度で研磨されるため、リセス、ディッシング、エロージョン等を抑制できる。

【0020】

また、図5に示す工程では、金属膜19の研磨レートを1としたときに、層間絶縁膜14の研磨レートが1.1〜1.2程度(好ましくは、1.08)となる条件(具体的には、研磨圧や研磨液等で調整した条件)を用いるとよい。図5に示す工程では、図4に示す工程で使用する研磨液とは、異なる研磨液を使用する。

【0021】

図5に示す工程で使用する研磨液は、例えば、コロイダルシリカ粒子、金属膜19を酸化させる酸化剤、及び溶媒により構成できる。また、図5に示す工程で使用する研磨液に含まれる酸化剤としては、例えば、過ヨウ素酸塩の化合物を含むものを用いるとよい。

【0022】

また、図5に示す工程で使用する研磨液に含まれる溶媒としては、脱イオン水を用いるものを使用するとよい。さらに、図5に示す工程で使用する研磨液に含まれるコロイダルシリカ粒子は、研磨液に対して、8〜12wt%(好ましくは、10wt%)にするとよい。

【0023】

図6は、本実施の形態で使用する研磨布の構成を説明するための断面図である。

図6に示すように、図5に示す工程では、CMP装置の定盤(プラテン)に貼り付けられる第1の研磨布24(軟質パッド)と、第1の研磨布24上に積層され、かつ第1の研磨布の硬さよりも硬い第2の研磨布25(硬質パッド)と、を有した研磨布23(2層パッド)を用いて研磨を行うとよい。

【0024】

例えば、金属膜19としてタングステン膜を用い、第2の研磨布25単層で研磨を行った場合、コンタクト孔16の密度が70%程度の箇所でのエロージョンが40nm以下となる。

また、金属膜19としてタングステン膜を用い、第1の研磨布24単層で研磨を行った場合、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい条件を用いたとしても、研磨対象の表面形状に追従するため、エロージョンは100nmと大きくなる。

【0025】

また、金属膜19としてタングステン膜を用い、第2の研磨布25単層で研磨を行った場合、リセス及びディッシングは、4nm以下であり、第1の研磨布24単層で研磨を行った場合、リセス及びディッシングは、15nm以上でとなる。また、タングステン膜にシームが存在する場合、第1の研磨布24単層では、リセスが加速されてしまう。

そこで、上記説明したように、第1の研磨布24(軟質パッド)と、第1の研磨布24上に積層され、かつ第1の研磨布の硬さよりも硬い第2の研磨布25(硬質パッド)と、を有した研磨布23(2層パッド)を用いて研磨を行うとよい。

【0026】

なお、実際の半導体装置10は、図5に示す工程の後に、層間絶縁膜、ビア、及び配線等(全て図示せず)を必要に応じて形成することで製造される。

【0027】

第1の実施の形態の半導体装置の製造方法によれば、研磨工程の第1段階として、CMP法により、層間絶縁膜14の研磨レートよりも金属膜19の研磨レートが大きい研磨条件を用いて金属膜19の研磨を行ない、次いで、層間絶縁膜14の上面14a、または層間絶縁膜14の上面14aに形成されたバリア膜18が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いた研磨により、コンタクト孔16内に、バリア膜18及び金属膜19よりなるコンタクトプラグ22を形成することで、層間絶縁膜の14の上面14aが露出された際、コンタクト孔16内に形成された金属膜19、及び金属膜19が形成されたコンタクトホール16が密集した領域が過剰に研磨されることを抑制可能となるので、リセス、ディッシング、及びエロージョンを抑制することができる。

【0028】

また、層間絶縁膜14の研磨レートよりも金属膜19の研磨レートが大きい研磨条件を用いて、金属膜19の研磨を行なうことで、金属膜19の研磨時間を短くすることが可能となるので、研磨工程におけるスループットを向上できる。

【0029】

さらに、第1の実施の形態で説明したコンタクトプラグ22の形成方法(具体的には、研磨工程)を用いて、不純物拡散層13の上面13aと接触し、かつタングステン膜よりなるコンタクトプラグ22を形成することは、トランジスタ素子(図示せず)が微細化された半導体装置10に有効である。

【0030】

なお、第1の実施の形態では、コンタクトプラグ22の一例として、不純物拡散層13の上面13aと接触するコンタクトプラグを形成する場合について説明したが、第1の実施の形態で説明したコンタクトプラグ22の形成方法は、図5に示す構造体の上方に形成されるコンタクトプラグ(図示せず)にも適用可能である。

【0031】

また、第1の実施の形態では、金属膜19の一例として、タングステン膜を用いた場合を例に挙げて説明したが、本発明は、タングステン膜以外の金属膜19、具体的には、銅(Cu)膜やアルミニウム合金膜(例えば、Al−Si−Cu膜)等にも適用可能である。

【0032】

図7は、本発明の第1の実施の形態の変形例に係る半導体装置の製造工程を示す断面図であり、研磨工程の第1段階を説明するための図である。

【0033】

先に説明した図4に示す工程では、層間絶縁膜14の上面14aに形成されたバリア膜18の表面18aが露出されるまで、第1段階の研磨を行なう場合を例に挙げて説明したが、図7に示すように、第1段階の研磨は、バリア膜18の表面18aが露出される前の状態、つまり、第1段階の研磨終了後の研磨面全体が金属膜19の状態で終了させてもよい。

この場合、残存する金属膜19を研磨するところから、第2段階の研磨を開始し、該第2段階の研磨は、層間絶縁膜14の上面14aが露出されるまで行なう。

【0034】

次に、図3及び図5を参照して、本発明の第1の実施の形態の他の変形例に係る半導体装置10の製造方法について説明する。

第1の実施の形態の変形例に係る半導体装置の製造方法では、先に説明した図3に示す工程後に、図5で説明した金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件のみを用いて研磨を行なうことで、図5に示す複数のコンタクトプラグ22を形成する以外は、第1の実施の形態の半導体装置10の製造方法と同様な手法により行なわれる。

【0035】

つまり、第1の実施の形態の変形例に係る半導体装置10の製造方法では、1つの研磨条件のみを用いた研磨により、複数のコンタクトプラグ22を形成する。

このとき、層間絶縁膜の14の上面14aに形成されたバリア膜18及び金属膜19が除去されたかどうか判断するために、終点検出器(エンドポイント検知器)を用いるとよい。

【0036】

上記終点検出器としては、例えば、金属膜19及びバリア膜18から層間絶縁膜14が露出することで抵抗値が変化することを利用した渦電流方式の終点検出器、金属膜19及びバリア膜18から層間絶縁膜14が露出することで摩擦係数が変化することを利用したトルク式終点検出器、及び研磨時間の経過と共に波長が変わることを利用した光学式終点検出器等を用いることができる。

【0037】

また、第1の実施の形態の変形例に係る半導体装置10の製造方法の研磨工程では、層間絶縁膜14の上面14aが露出した後は、層間絶縁膜14と金属膜19とが同じ速度で研磨が進行するので、上記終点検出器により研磨の終点を検出した後の研磨(半導体基板11の面内ばらつきを考慮して行うオーバー研磨)は、コンタクトプラグ22の深さが所望の深さとなるように、時間管理で行なうとよい。

【0038】

第1の実施の形態の変形例の半導体装置10の製造方法によれば、コンタクト孔16内に、バリア膜18及び金属膜19よりなるコンタクトプラグ22を形成する研磨工程において、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件のみを用いて、金属膜19、バリア膜18、及び層間絶縁膜14を研磨して、コンタクト孔16内にバリア膜18及び金属膜19よりなるコンタクトプラグ22を形成することにより、研磨工程を2段階に分ける必要がなくなるので、半導体装置10の製造工程を簡略化することができる。

【0039】

(第2の実施の形態)

図8〜図13は、本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図である。また、図12は、研磨工程の第1段階を説明するための図であり、図13は、研磨工程の第2段階を説明するための図である。図8〜図13において、図5に示す構造体と同一構成部分には、同一符号を付す。

【0040】

主に、図8〜図13を参照して、第2の実施の形態の半導体装置25(図13参照)の製造方法について説明する。

始めに、第1の実施の形態で説明した図1〜図5に示す工程と同様な処理を行なうことで、図5に示す構造体を形成する。次いで、図8に示す工程では、図5に示す構造体の上面(具体的には、層間絶縁膜14の上面、及びコンタクトプラグ22の上面22a)を覆う第1のシリコン窒化膜27を形成する。第1のシリコン窒化膜27は、例えば、CVD法により形成することができる。

【0041】

次いで、第1のシリコン窒化膜27の上面27aに、第1の層間絶縁膜28を形成する。具体的には、CVD法により、第1のシリコン窒化膜27の上面27aにシリコン酸化膜を堆積させることで、該シリコン酸化膜よりなる第1の層間絶縁膜28を形成する。

次いで、第1の層間絶縁膜28の上面28aを覆う第2のシリコン窒化膜29を形成する。第2のシリコン窒化膜29は、例えば、CVD法により形成することができる。

【0042】

次いで、第2のシリコン窒化膜29の上面29aに、後述する図10に示すコンタクト孔34の形成領域に対応する部分に開口部を有したフォトレジスト(図示せず)を形成する。次いで、該フォトレジスト(図示せず)をマスクとする異方性エッチング(具体的にには、ドライエッチング)により、第2のシリコン窒化膜29を選択的にエッチングすることで、第1の層間絶縁膜28の上面28aを露出する複数の開口部30を形成する。

このとき、ドライエッチングの条件としては、シリコン窒化膜がエッチングされやすく、かつシリコン酸化膜がエッチングされにくい条件を用いる。なお、図示していないフォトレジスト(図示せず)は、複数の開口部30を形成後に除去する。

【0043】

次いで、図9に示す工程では、第2のシリコン窒化膜29の上面29aに、複数の開口部30を埋め込む第2の層間絶縁膜31を形成する。具体的には、CVD法により、第2のシリコン窒化膜29の上面29aにシリコン酸化膜を堆積させることで、該シリコン酸化膜よりなる第2の層間絶縁膜31を形成する。

【0044】

次いで、図10に示す工程では、図9に示す第2の層間絶縁膜31の上面31aに、開口部を有したフォトレジスト(図示せず)を形成し、該フォトレジストをマスクとする異方性エッチング(具体的には、ドライエッチング)により、該開口部の下方に位置する第2の層間絶縁膜31、及び図9に示す開口部30の下方に位置する第1の層間絶縁膜28を選択的にエッチングすることで、第2のシリコン窒化膜29の上面29aを露出する溝33を形成すると共に、第1のシリコン窒化膜27の上面27aを露出する孔(コンタクト孔34の一部となる図示していない孔)を形成する。

【0045】

このときのエッチング条件としては、第1及び第2のシリコン窒化膜27,29に対して十分な選択比を有し、かつ第1及び第2の層間絶縁膜28,31を選択的にエッチング可能な条件(言い換えれば、シリコン窒化膜がエッチングされにくく、かつシリコン酸化膜がエッチングされやすい条件)を用いるとよい。

【0046】

これにより、溝33を形成する際のエッチングストッパー膜として第2のシリコン窒化膜29を利用することが可能となるので、半導体基板11面内における溝33の深さばらつきを低減できる。

また、コンタクト孔34の一部となる孔を形成する際のエッチングストッパー膜として第1のシリコン窒化膜27を利用することが可能となるので、半導体基板11面内における該孔の深さばらつきを低減できる。

【0047】

次いで、シリコン酸化膜よりもシリコン窒化膜がエッチングされやすい条件を用いた異方性エッチング(具体的には、ドライエッチング)により、該孔の下方に残存する第1のシリコン窒化膜27を選択的にエッチングすることで、溝33と一体とされたコンタクト孔34を形成する。

その後、第2の層間絶縁膜31の上面31aに形成したフォトレジスト(図示せず)を除去する。

【0048】

次いで、図11に示す工程では、第2の層間絶縁膜31の上面31a、溝33の内面、及びコンタクト孔34の内面(コンタクト孔34から露出されたコンタクトプラグ22の上面22aを含む)を覆うバリア膜36を形成する。

【0049】

具体的には、例えば、CVD法により、バリア膜36を形成する。バリア膜36は、金属膜37がタングステン膜(W膜)の場合、例えば、Ti膜と、TiN膜と、を順次積層させたTi/TiN積層膜を用いることができる。

【0050】

次いで、バリア膜36の表面36aに、複数の溝33及びコンタクト孔34を埋め込む厚さとされた金属膜37を形成する。具体的には、例えば、CVD法により、金属膜37としてタングステン膜を形成する。

【0051】

次いで、図12に示す工程では、研磨工程の第1段階として、層間絶縁膜14の研磨レートよりも金属膜37の研磨レートが大きい研磨条件を用いて、CMP法により、第2の層間絶縁膜31の上面31aに形成されたバリア膜36の表面36aが露出されるまで、金属膜37の研磨を行なう。

【0052】

次いで、図13に示す工程では、研磨工程の第2段階として、金属膜37の研磨レートと第2の層間絶縁膜31の研磨レートとの差が小さい研磨条件(言い換えれば、金属膜37の研磨レートと第2の層間絶縁膜31の研磨レートとが略等しくなる研磨条件)を用いて、CMP法により、第2の層間絶縁膜31の上面31aに形成されたバリア膜36を研磨除去し、溝33及びコンタクト孔34内にのみバリア膜36及び金属膜37を残存させる。

【0053】

これにより、コンタクト孔34に、バリア膜36及び金属膜37よりなり、かつコンタクトプラグ22の上面22aと接続されたコンタクトプラグ39(第2の実施の形態の導体パターンのうちの1つ)と、溝33に、バリア膜36及び金属膜37よりなり、かつコンタクトプラグ39と一体とされた配線41(第2の実施の形態の導体パターンのうちの1つ)と、が一括形成される。これにより、第2の実施の形態の半導体装置25が製造される。

【0054】

このとき、半導体基板11の面内の全てにおいて、バリア膜36が除去されるように、ある程度のオーバー研磨を行なう。これにより、溝33内に形成されたバリア膜36及び金属膜37と第2の層間絶縁膜31とが略同じ速度で研磨されるため、リセス、ディッシング、エロージョン等を抑制できる。

【0055】

また、図13に示す工程では、金属膜37の研磨レートを1としたときに、第2の層間絶縁膜31の研磨レートが1.1〜1.2程度(好ましくは、1.08)となる条件(具体的には、研磨圧や研磨液等で調整した条件)を用いるとよい。図13に示す工程では、図12に示す工程で使用する研磨液とは、異なる研磨液を使用する。

【0056】

図13に示す工程で使用する研磨液は、例えば、コロイダルシリカ粒子、金属膜37を酸化させる酸化剤、及び溶媒により構成できる。また、図13に示す工程で使用する研磨液に含まれる酸化剤としては、例えば、過ヨウ素酸塩の化合物を含むものを用いるとよい。

【0057】

また、図13に示す工程で使用する研磨液に含まれる溶媒としては、脱イオン水を用いるものを使用するとよい。さらに、図13に示す工程で使用する研磨液に含まれるコロイダルシリカ粒子は、研磨液に対して、8〜12wt%(好ましくは、10wt%)にするとよい。

【0058】

なお、実際の半導体装置25は、図13に示す工程の後に、層間絶縁膜、ビア、及び配線等(全て図示せず)を必要に応じて形成することで製造される。

【0059】

第2の実施の形態の半導体装置の製造方法によれば、溝33及びコンタクト孔34の内面を覆うバリア膜36と、バリア膜36を介して、溝33及びコンタクト孔34を埋め込む金属膜37と、を形成後、研磨工程の第1段階として、CMP法により、第2の層間絶縁膜31の研磨レートよりも金属膜37の研磨レートが大きい研磨条件を用いて、バリア膜36が露出するまで金属膜37の研磨を行ない、次いで、第2の層間絶縁膜31の上面31aに形成された金属膜37の研磨レートと第2の層間絶縁膜31の研磨レートとの差が小さい研磨条件を用いて、第2の層間絶縁膜31の上面31aに形成されたバリア膜36を研磨除去することで、コンタクト孔34内に配置され、コンタクトプラグ22と接続されたコンタクトプラグ39と、溝33内に配置され、コンタクトプラグ39と一体とされた配線41と、を一括形成することにより、第2の層間絶縁膜31の上面31aが露出した際、溝33内に形成された金属膜37、及び金属膜37が形成された溝33が密集した領域が過剰に研磨されることを抑制可能となるので、リセス、ディッシング、及びエロージョンを抑制することができる。

【0060】

また、第2の層間絶縁膜31の研磨レートよりも金属膜37の研磨レートが大きい研磨条件を用いて、金属膜37の研磨を行なうことで、金属膜37の研磨時間を短くすることが可能となるので、研磨工程におけるスループットを向上できる。

【0061】

なお、第2の実施の形態では、デュアルダマシン構造を例に挙げて説明したが、第2の実施の形態の半導体装置25の製造方法は、シングルダマシン構造の配線を形成する場合にも適用可能である。

【0062】

また、第2の実施の形態では、金属膜37の一例として、タングステン膜を用いた場合を例に挙げて説明したが、本発明は、タングステン膜以外の金属膜37、具体的には、銅(Cu)膜やアルミニウム合金膜(例えば、Al−Si−Cu膜)等にも適用可能である。

【0063】

図14は、本発明の第2の実施の形態の変形例に係る半導体装置の製造工程を示す断面図であり、研磨工程の第1段階を説明するための図である。

【0064】

先に説明した図12に示す工程では、第2の層間絶縁膜31の上面31aに形成されたバリア膜36の表面36aが露出されるまで、第1段階の研磨を行なう場合を例に挙げて説明したが、図14に示すように、第1段階の研磨は、バリア膜36の表面36aが露出される前の状態、つまり、第1段階の研磨終了後の研磨面全体が金属膜37の状態で終了させてもよい。

この場合、残存する金属膜37を研磨するところから、第2段階の研磨を開始し、該第2段階の研磨は、第2の層間絶縁膜31の上面31aが露出されるまで行なう。

【0065】

次に、図11及び図13を参照して、本発明の第2の実施の形態の他の変形例に係る半導体装置25の製造方法について説明する。

第2の実施の形態の変形例に係る半導体装置25の製造方法は、先に説明した図11に示す工程後に、図13で説明した金属膜37の研磨レートと第2の層間絶縁膜31の研磨レートとの差が小さい研磨条件のみを用いて研磨を行なうことで、図13に示す複数のコンタクトプラグ39及び配線41を形成すること以外は、第2の実施の形態の半導体装置25の製造方法と同様な手法により行なう。

【0066】

つまり、第2の実施の形態の変形例に係る半導体装置25の製造方法では、1つの研磨条件のみを用いて、研磨を行うことで、複数のコンタクトプラグ39及び配線41を形成する。

【0067】

第2の実施の形態の変形例の半導体装置の製造方法によれば、コンタクト孔34及び溝33を埋め込むバリア膜36及び金属膜37を研磨する研磨工程において、金属膜33の研磨レートと第2の層間絶縁膜31の研磨レートとの差が小さい研磨条件のみを用いて、金属膜33、バリア膜34、及び第2の層間絶縁膜31の研磨を行なうことで、コンタクトプラグ39及び配線41を形成することにより、研磨工程を2段階に分ける必要がなくなるので、半導体装置25の製造工程を簡略化できる。

【0068】

なお、第2の実施の形態では、金属膜37の一例として、タングステン膜を用いた場合を例に挙げて説明したが、本発明は、タングステン膜以外の金属膜37、具体的には、銅(Cu)膜やアルミニウム合金膜(例えば、Al−Si−Cu膜)等にも適用可能である。

【0069】

以上、本発明の好ましい実施の形態について詳述したが、本発明はかかる特定の実施の形態に限定されるものではなく、特許請求の範囲内に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【産業上の利用可能性】

【0070】

本発明は、半導体装置の製造方法に適用可能である。

【符号の説明】

【0071】

10,25…半導体基板、11…半導体基板、11a,13a,14a,22a,27a,28a,29a,31a,41a…上面、13…不純物拡散層、14…層間絶縁膜、16,34…コンタクト孔、18,36…バリア膜、18a,33a,36a…表面、19,37…金属膜、22,39…コンタクトプラグ、23…研磨布、24…第1の研磨布、25…第2の研磨布、27…第1のシリコン窒化膜、28…第1の層間絶縁膜、29…第2のシリコン窒化膜、30…開口部、31…第1の層間絶縁膜、33…溝、41…配線

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、半導体基板上に設けられた層間絶縁膜に開口部(溝、或いはコンタクト孔)の内面を覆うバリア膜を成膜し、次いで、バリア膜を介して、開口部を埋め込む金属膜を形成し、その後、CMP(Chemical Mechanical Polishing)法により、開口部以外の部分に形成された余分なバリア膜及び金属膜を研磨除去することで、開口部を埋め込むバリア膜及び金属膜よりなる導体パターン(配線、或いはコンタクトプラグ)を形成することが行なわれている。

【0003】

また、従来、上記方法により導体パターンを形成する際、CMP処理を2段階以上に分けて行うことが行なわれている(例えば、特許文献1参照)。

例えば、2段階に分けてCMP処理を行なう場合、第1段階として、層間絶縁膜の研磨レートよりも金属膜の研磨レートが大きい条件を用いて研磨を行う。次いで、層間絶縁膜の上面、或いは層間絶縁膜の上面に形成されたバリア膜が露出した段階で、金属膜の研磨レートと層間絶縁膜の研磨レートとの差の小さい条件を用いて、第2段階の研磨を行なう。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−306869号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、層間絶縁膜の研磨レートよりも金属膜の研磨レートが大きい条件を用いて上記第1段階のCMP処理を行なった場合、層間絶縁膜の上面、或いは、層間絶縁膜の上面に形成されたバリア膜が露出した時点で、開口部に埋め込まれた金属膜が過剰に研磨されてしまうため、リセスが発生してしまうという問題があった。また、開口部のうち、幅或いは径が大きい部分では、ディッシングが発生しやすいという問題があった。

【0006】

さらに、開口部がコンタクト孔であって、該コンタクト孔に形成されたコンタクトプラグの密度が高い領域では、エロージョンが発生しやすいという問題があった。

また、今後、半導体装置を構成する素子(例えば、トランジスタ素子)の微細化がさらに進展した際、コンタクトプラグの面内密度が高い部分では、上記エロージョンの問題が顕著となる。

【課題を解決するための手段】

【0007】

本発明の一観点によれば、層間絶縁膜に開口部を形成する工程と、前記開口部を埋め込む厚さとされた金属膜を形成する工程と、CMP法により、前記層間絶縁膜の上面よりも上方に形成された前記金属膜を研磨除去することで、前記開口部内に導体パターンを形成する研磨工程と、を有し、前記研磨工程では、前記層間絶縁膜の上面が露出する前に、前記金属膜の研磨レートと前記層間絶縁膜の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0008】

本発明の半導体装置の製造方法によれば、CMP法により、層間絶縁膜の上面よりも上方に形成された金属膜を研磨除去することで、層間絶縁膜に形成された開口部内に導体パターンを形成する研磨工程において、層間絶縁膜の上面が露出する前に、金属膜の研磨レートと層間絶縁膜の研磨レートとの差が小さい条件を用いて研磨を行なうことで、層間絶縁膜の上面が露出された際、開口部内に形成された金属膜、及び金属膜が形成された開口部が密集した領域が過剰に研磨されることを抑制可能となる。これにより、リセス、ディッシング、及びエロージョンを抑制することができる。

【図面の簡単な説明】

【0009】

【図1】本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図(その1)である。

【図2】本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図(その2)である。

【図3】本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図(その3)である。

【図4】本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図(その4)であり、研磨工程の第1段階を説明するための図である。

【図5】本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図(その5)であり、研磨工程の第2段階を説明するための図である。

【図6】本実施の形態で使用する研磨布の構成を説明するための断面図である。

【図7】本発明の第1の実施の形態の変形例に係る半導体装置の製造工程を示す断面図であり、研磨工程の第1段階を説明するための図である。

【図8】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その1)である。

【図9】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その2)である。

【図10】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その3)である。

【図11】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その4)である。

【図12】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その5)であり、研磨工程の第1段階を説明するための図である。

【図13】本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図(その6)であり、研磨工程の第2段階を説明するための図である。

【図14】本発明の第2の実施の形態の変形例に係る半導体装置の製造工程を示す断面図であり、研磨工程の第1段階を説明するための図である。

【発明を実施するための形態】

【0010】

以下、図面を参照して本発明を適用した実施の形態について詳細に説明する。なお、以下の説明で用いる図面は、本発明の実施の形態の構成を説明するためのものであり、図示される各部の大きさや厚さや寸法等は、実際の半導体装置の寸法関係とは異なる場合がある。

【0011】

(第1の実施の形態)

図1〜図5は、本発明の第1の実施の形態に係る半導体装置の製造工程を示す断面図である。また、図4は、研磨工程の第1段階を説明するための図であり、図5は、研磨工程の第2段階を説明するための図である。

【0012】

図1〜図5を参照して、第1の実施の形態の半導体装置10(図5参照)の製造方法について説明する。

始めに、図1に示す工程では、半導体基板11に、不純物拡散層13を構成要素として含むトランジスタ素子(図示せず)を形成する。半導体基板11としては、例えば、シリコン基板を用いる。また、不純物拡散層13は、半導体基板11とは異なる導電型の不純物を半導体基板11の表面11aにイオン注入することで形成する。

【0013】

次いで、半導体基板11の表面11a、及び不純物拡散層13の上面13aを覆うように、層間絶縁膜14を形成する。具体的には、層間絶縁膜14は、例えば、CVD(Chemical Vapor Deposition)法により形成する。また、層間絶縁膜14としては、例えば、シリコン酸化膜(SiO2膜)を用いることができる。

【0014】

次いで、図2に示す工程では、層間絶縁膜14に、不純物拡散層13の上面13aを露出する開口部としてコンタクト孔16を複数形成する。

具体的には、層間絶縁膜14の上面14aに、コンタクト孔16の形成領域に対応する層間絶縁膜14の上面14aを露出する複数の開口孔(図示せず)を有したフォトレジスト(図示せず)を形成する。次いで、該フォトレジストをマスクとする異方性エッチング(例えば、ドライエッチング)により、層間絶縁膜14をエッチングすることで、複数のコンタクト孔16を形成する。フォトレジスト(図示せず)は、複数のコンタクト孔16を形成後に除去する。

【0015】

次いで、図3に示す工程では、層間絶縁膜14の上面14a、及びコンタクト孔16の内面(コンタクト孔16から露出された不純物拡散層13の上面13aを含む)を覆うバリア膜18を形成する。

具体的には、例えば、CVD法により、バリア膜18を形成する。バリア膜18は、金属膜19がタングステン膜(W膜)の場合、例えば、Ti膜と、TiN膜と、を順次積層させたTi/TiN積層膜を用いることができる。

【0016】

次いで、バリア膜18の表面18aに、複数のコンタクト孔16を埋め込む厚さとされた金属膜19を形成する。具体的には、例えば、CVD法により、金属膜19としてタングステン膜を形成する。

【0017】

次いで、図4に示す工程では、研磨工程の第1段階として、層間絶縁膜14の研磨レートよりも金属膜19の研磨レートが大きい研磨条件を用いて、CMP法により、層間絶縁膜14の上面14aに形成されたバリア膜18の表面18aが露出されるまで、金属膜19の研磨を行なう。

層間絶縁膜14の研磨レートよりも金属膜19の研磨レートが大きい研磨条件は、例えば、研磨液(スラリー)に含まれる酸化剤の量を多くすることで実現できる。

【0018】

次いで、図5に示す工程では、研磨工程の第2段階として、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件(言い換えれば、金属膜19の研磨レートと層間絶縁膜14の研磨レートとが略等しくなる研磨条件)を用いて、CMP法により、層間絶縁膜14の上面14aに形成されたバリア膜18を研磨除去し、コンタクト孔16内にのみバリア膜18及び金属膜19を残存させることで、コンタクト孔16内にバリア膜18及び金属膜19よりなるコンタクトプラグ22(導体パターン)を形成する。

【0019】

このとき、半導体基板11の面内の全てにおいて、バリア膜18が除去されるように、ある程度のオーバー研磨を行なう。これにより、コンタクト孔16内に形成されたバリア膜18及び金属膜19と層間絶縁膜14とが略同じ速度で研磨されるため、リセス、ディッシング、エロージョン等を抑制できる。

【0020】

また、図5に示す工程では、金属膜19の研磨レートを1としたときに、層間絶縁膜14の研磨レートが1.1〜1.2程度(好ましくは、1.08)となる条件(具体的には、研磨圧や研磨液等で調整した条件)を用いるとよい。図5に示す工程では、図4に示す工程で使用する研磨液とは、異なる研磨液を使用する。

【0021】

図5に示す工程で使用する研磨液は、例えば、コロイダルシリカ粒子、金属膜19を酸化させる酸化剤、及び溶媒により構成できる。また、図5に示す工程で使用する研磨液に含まれる酸化剤としては、例えば、過ヨウ素酸塩の化合物を含むものを用いるとよい。

【0022】

また、図5に示す工程で使用する研磨液に含まれる溶媒としては、脱イオン水を用いるものを使用するとよい。さらに、図5に示す工程で使用する研磨液に含まれるコロイダルシリカ粒子は、研磨液に対して、8〜12wt%(好ましくは、10wt%)にするとよい。

【0023】

図6は、本実施の形態で使用する研磨布の構成を説明するための断面図である。

図6に示すように、図5に示す工程では、CMP装置の定盤(プラテン)に貼り付けられる第1の研磨布24(軟質パッド)と、第1の研磨布24上に積層され、かつ第1の研磨布の硬さよりも硬い第2の研磨布25(硬質パッド)と、を有した研磨布23(2層パッド)を用いて研磨を行うとよい。

【0024】

例えば、金属膜19としてタングステン膜を用い、第2の研磨布25単層で研磨を行った場合、コンタクト孔16の密度が70%程度の箇所でのエロージョンが40nm以下となる。

また、金属膜19としてタングステン膜を用い、第1の研磨布24単層で研磨を行った場合、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい条件を用いたとしても、研磨対象の表面形状に追従するため、エロージョンは100nmと大きくなる。

【0025】

また、金属膜19としてタングステン膜を用い、第2の研磨布25単層で研磨を行った場合、リセス及びディッシングは、4nm以下であり、第1の研磨布24単層で研磨を行った場合、リセス及びディッシングは、15nm以上でとなる。また、タングステン膜にシームが存在する場合、第1の研磨布24単層では、リセスが加速されてしまう。

そこで、上記説明したように、第1の研磨布24(軟質パッド)と、第1の研磨布24上に積層され、かつ第1の研磨布の硬さよりも硬い第2の研磨布25(硬質パッド)と、を有した研磨布23(2層パッド)を用いて研磨を行うとよい。

【0026】

なお、実際の半導体装置10は、図5に示す工程の後に、層間絶縁膜、ビア、及び配線等(全て図示せず)を必要に応じて形成することで製造される。

【0027】

第1の実施の形態の半導体装置の製造方法によれば、研磨工程の第1段階として、CMP法により、層間絶縁膜14の研磨レートよりも金属膜19の研磨レートが大きい研磨条件を用いて金属膜19の研磨を行ない、次いで、層間絶縁膜14の上面14a、または層間絶縁膜14の上面14aに形成されたバリア膜18が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いた研磨により、コンタクト孔16内に、バリア膜18及び金属膜19よりなるコンタクトプラグ22を形成することで、層間絶縁膜の14の上面14aが露出された際、コンタクト孔16内に形成された金属膜19、及び金属膜19が形成されたコンタクトホール16が密集した領域が過剰に研磨されることを抑制可能となるので、リセス、ディッシング、及びエロージョンを抑制することができる。

【0028】

また、層間絶縁膜14の研磨レートよりも金属膜19の研磨レートが大きい研磨条件を用いて、金属膜19の研磨を行なうことで、金属膜19の研磨時間を短くすることが可能となるので、研磨工程におけるスループットを向上できる。

【0029】

さらに、第1の実施の形態で説明したコンタクトプラグ22の形成方法(具体的には、研磨工程)を用いて、不純物拡散層13の上面13aと接触し、かつタングステン膜よりなるコンタクトプラグ22を形成することは、トランジスタ素子(図示せず)が微細化された半導体装置10に有効である。

【0030】

なお、第1の実施の形態では、コンタクトプラグ22の一例として、不純物拡散層13の上面13aと接触するコンタクトプラグを形成する場合について説明したが、第1の実施の形態で説明したコンタクトプラグ22の形成方法は、図5に示す構造体の上方に形成されるコンタクトプラグ(図示せず)にも適用可能である。

【0031】

また、第1の実施の形態では、金属膜19の一例として、タングステン膜を用いた場合を例に挙げて説明したが、本発明は、タングステン膜以外の金属膜19、具体的には、銅(Cu)膜やアルミニウム合金膜(例えば、Al−Si−Cu膜)等にも適用可能である。

【0032】

図7は、本発明の第1の実施の形態の変形例に係る半導体装置の製造工程を示す断面図であり、研磨工程の第1段階を説明するための図である。

【0033】

先に説明した図4に示す工程では、層間絶縁膜14の上面14aに形成されたバリア膜18の表面18aが露出されるまで、第1段階の研磨を行なう場合を例に挙げて説明したが、図7に示すように、第1段階の研磨は、バリア膜18の表面18aが露出される前の状態、つまり、第1段階の研磨終了後の研磨面全体が金属膜19の状態で終了させてもよい。

この場合、残存する金属膜19を研磨するところから、第2段階の研磨を開始し、該第2段階の研磨は、層間絶縁膜14の上面14aが露出されるまで行なう。

【0034】

次に、図3及び図5を参照して、本発明の第1の実施の形態の他の変形例に係る半導体装置10の製造方法について説明する。

第1の実施の形態の変形例に係る半導体装置の製造方法では、先に説明した図3に示す工程後に、図5で説明した金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件のみを用いて研磨を行なうことで、図5に示す複数のコンタクトプラグ22を形成する以外は、第1の実施の形態の半導体装置10の製造方法と同様な手法により行なわれる。

【0035】

つまり、第1の実施の形態の変形例に係る半導体装置10の製造方法では、1つの研磨条件のみを用いた研磨により、複数のコンタクトプラグ22を形成する。

このとき、層間絶縁膜の14の上面14aに形成されたバリア膜18及び金属膜19が除去されたかどうか判断するために、終点検出器(エンドポイント検知器)を用いるとよい。

【0036】

上記終点検出器としては、例えば、金属膜19及びバリア膜18から層間絶縁膜14が露出することで抵抗値が変化することを利用した渦電流方式の終点検出器、金属膜19及びバリア膜18から層間絶縁膜14が露出することで摩擦係数が変化することを利用したトルク式終点検出器、及び研磨時間の経過と共に波長が変わることを利用した光学式終点検出器等を用いることができる。

【0037】

また、第1の実施の形態の変形例に係る半導体装置10の製造方法の研磨工程では、層間絶縁膜14の上面14aが露出した後は、層間絶縁膜14と金属膜19とが同じ速度で研磨が進行するので、上記終点検出器により研磨の終点を検出した後の研磨(半導体基板11の面内ばらつきを考慮して行うオーバー研磨)は、コンタクトプラグ22の深さが所望の深さとなるように、時間管理で行なうとよい。

【0038】

第1の実施の形態の変形例の半導体装置10の製造方法によれば、コンタクト孔16内に、バリア膜18及び金属膜19よりなるコンタクトプラグ22を形成する研磨工程において、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件のみを用いて、金属膜19、バリア膜18、及び層間絶縁膜14を研磨して、コンタクト孔16内にバリア膜18及び金属膜19よりなるコンタクトプラグ22を形成することにより、研磨工程を2段階に分ける必要がなくなるので、半導体装置10の製造工程を簡略化することができる。

【0039】

(第2の実施の形態)

図8〜図13は、本発明の第2の実施の形態に係る半導体装置の製造工程を示す断面図である。また、図12は、研磨工程の第1段階を説明するための図であり、図13は、研磨工程の第2段階を説明するための図である。図8〜図13において、図5に示す構造体と同一構成部分には、同一符号を付す。

【0040】

主に、図8〜図13を参照して、第2の実施の形態の半導体装置25(図13参照)の製造方法について説明する。

始めに、第1の実施の形態で説明した図1〜図5に示す工程と同様な処理を行なうことで、図5に示す構造体を形成する。次いで、図8に示す工程では、図5に示す構造体の上面(具体的には、層間絶縁膜14の上面、及びコンタクトプラグ22の上面22a)を覆う第1のシリコン窒化膜27を形成する。第1のシリコン窒化膜27は、例えば、CVD法により形成することができる。

【0041】

次いで、第1のシリコン窒化膜27の上面27aに、第1の層間絶縁膜28を形成する。具体的には、CVD法により、第1のシリコン窒化膜27の上面27aにシリコン酸化膜を堆積させることで、該シリコン酸化膜よりなる第1の層間絶縁膜28を形成する。

次いで、第1の層間絶縁膜28の上面28aを覆う第2のシリコン窒化膜29を形成する。第2のシリコン窒化膜29は、例えば、CVD法により形成することができる。

【0042】

次いで、第2のシリコン窒化膜29の上面29aに、後述する図10に示すコンタクト孔34の形成領域に対応する部分に開口部を有したフォトレジスト(図示せず)を形成する。次いで、該フォトレジスト(図示せず)をマスクとする異方性エッチング(具体的にには、ドライエッチング)により、第2のシリコン窒化膜29を選択的にエッチングすることで、第1の層間絶縁膜28の上面28aを露出する複数の開口部30を形成する。

このとき、ドライエッチングの条件としては、シリコン窒化膜がエッチングされやすく、かつシリコン酸化膜がエッチングされにくい条件を用いる。なお、図示していないフォトレジスト(図示せず)は、複数の開口部30を形成後に除去する。

【0043】

次いで、図9に示す工程では、第2のシリコン窒化膜29の上面29aに、複数の開口部30を埋め込む第2の層間絶縁膜31を形成する。具体的には、CVD法により、第2のシリコン窒化膜29の上面29aにシリコン酸化膜を堆積させることで、該シリコン酸化膜よりなる第2の層間絶縁膜31を形成する。

【0044】

次いで、図10に示す工程では、図9に示す第2の層間絶縁膜31の上面31aに、開口部を有したフォトレジスト(図示せず)を形成し、該フォトレジストをマスクとする異方性エッチング(具体的には、ドライエッチング)により、該開口部の下方に位置する第2の層間絶縁膜31、及び図9に示す開口部30の下方に位置する第1の層間絶縁膜28を選択的にエッチングすることで、第2のシリコン窒化膜29の上面29aを露出する溝33を形成すると共に、第1のシリコン窒化膜27の上面27aを露出する孔(コンタクト孔34の一部となる図示していない孔)を形成する。

【0045】

このときのエッチング条件としては、第1及び第2のシリコン窒化膜27,29に対して十分な選択比を有し、かつ第1及び第2の層間絶縁膜28,31を選択的にエッチング可能な条件(言い換えれば、シリコン窒化膜がエッチングされにくく、かつシリコン酸化膜がエッチングされやすい条件)を用いるとよい。

【0046】

これにより、溝33を形成する際のエッチングストッパー膜として第2のシリコン窒化膜29を利用することが可能となるので、半導体基板11面内における溝33の深さばらつきを低減できる。

また、コンタクト孔34の一部となる孔を形成する際のエッチングストッパー膜として第1のシリコン窒化膜27を利用することが可能となるので、半導体基板11面内における該孔の深さばらつきを低減できる。

【0047】

次いで、シリコン酸化膜よりもシリコン窒化膜がエッチングされやすい条件を用いた異方性エッチング(具体的には、ドライエッチング)により、該孔の下方に残存する第1のシリコン窒化膜27を選択的にエッチングすることで、溝33と一体とされたコンタクト孔34を形成する。

その後、第2の層間絶縁膜31の上面31aに形成したフォトレジスト(図示せず)を除去する。

【0048】

次いで、図11に示す工程では、第2の層間絶縁膜31の上面31a、溝33の内面、及びコンタクト孔34の内面(コンタクト孔34から露出されたコンタクトプラグ22の上面22aを含む)を覆うバリア膜36を形成する。

【0049】

具体的には、例えば、CVD法により、バリア膜36を形成する。バリア膜36は、金属膜37がタングステン膜(W膜)の場合、例えば、Ti膜と、TiN膜と、を順次積層させたTi/TiN積層膜を用いることができる。

【0050】

次いで、バリア膜36の表面36aに、複数の溝33及びコンタクト孔34を埋め込む厚さとされた金属膜37を形成する。具体的には、例えば、CVD法により、金属膜37としてタングステン膜を形成する。

【0051】

次いで、図12に示す工程では、研磨工程の第1段階として、層間絶縁膜14の研磨レートよりも金属膜37の研磨レートが大きい研磨条件を用いて、CMP法により、第2の層間絶縁膜31の上面31aに形成されたバリア膜36の表面36aが露出されるまで、金属膜37の研磨を行なう。

【0052】

次いで、図13に示す工程では、研磨工程の第2段階として、金属膜37の研磨レートと第2の層間絶縁膜31の研磨レートとの差が小さい研磨条件(言い換えれば、金属膜37の研磨レートと第2の層間絶縁膜31の研磨レートとが略等しくなる研磨条件)を用いて、CMP法により、第2の層間絶縁膜31の上面31aに形成されたバリア膜36を研磨除去し、溝33及びコンタクト孔34内にのみバリア膜36及び金属膜37を残存させる。

【0053】

これにより、コンタクト孔34に、バリア膜36及び金属膜37よりなり、かつコンタクトプラグ22の上面22aと接続されたコンタクトプラグ39(第2の実施の形態の導体パターンのうちの1つ)と、溝33に、バリア膜36及び金属膜37よりなり、かつコンタクトプラグ39と一体とされた配線41(第2の実施の形態の導体パターンのうちの1つ)と、が一括形成される。これにより、第2の実施の形態の半導体装置25が製造される。

【0054】

このとき、半導体基板11の面内の全てにおいて、バリア膜36が除去されるように、ある程度のオーバー研磨を行なう。これにより、溝33内に形成されたバリア膜36及び金属膜37と第2の層間絶縁膜31とが略同じ速度で研磨されるため、リセス、ディッシング、エロージョン等を抑制できる。

【0055】

また、図13に示す工程では、金属膜37の研磨レートを1としたときに、第2の層間絶縁膜31の研磨レートが1.1〜1.2程度(好ましくは、1.08)となる条件(具体的には、研磨圧や研磨液等で調整した条件)を用いるとよい。図13に示す工程では、図12に示す工程で使用する研磨液とは、異なる研磨液を使用する。

【0056】

図13に示す工程で使用する研磨液は、例えば、コロイダルシリカ粒子、金属膜37を酸化させる酸化剤、及び溶媒により構成できる。また、図13に示す工程で使用する研磨液に含まれる酸化剤としては、例えば、過ヨウ素酸塩の化合物を含むものを用いるとよい。

【0057】

また、図13に示す工程で使用する研磨液に含まれる溶媒としては、脱イオン水を用いるものを使用するとよい。さらに、図13に示す工程で使用する研磨液に含まれるコロイダルシリカ粒子は、研磨液に対して、8〜12wt%(好ましくは、10wt%)にするとよい。

【0058】

なお、実際の半導体装置25は、図13に示す工程の後に、層間絶縁膜、ビア、及び配線等(全て図示せず)を必要に応じて形成することで製造される。

【0059】

第2の実施の形態の半導体装置の製造方法によれば、溝33及びコンタクト孔34の内面を覆うバリア膜36と、バリア膜36を介して、溝33及びコンタクト孔34を埋め込む金属膜37と、を形成後、研磨工程の第1段階として、CMP法により、第2の層間絶縁膜31の研磨レートよりも金属膜37の研磨レートが大きい研磨条件を用いて、バリア膜36が露出するまで金属膜37の研磨を行ない、次いで、第2の層間絶縁膜31の上面31aに形成された金属膜37の研磨レートと第2の層間絶縁膜31の研磨レートとの差が小さい研磨条件を用いて、第2の層間絶縁膜31の上面31aに形成されたバリア膜36を研磨除去することで、コンタクト孔34内に配置され、コンタクトプラグ22と接続されたコンタクトプラグ39と、溝33内に配置され、コンタクトプラグ39と一体とされた配線41と、を一括形成することにより、第2の層間絶縁膜31の上面31aが露出した際、溝33内に形成された金属膜37、及び金属膜37が形成された溝33が密集した領域が過剰に研磨されることを抑制可能となるので、リセス、ディッシング、及びエロージョンを抑制することができる。

【0060】

また、第2の層間絶縁膜31の研磨レートよりも金属膜37の研磨レートが大きい研磨条件を用いて、金属膜37の研磨を行なうことで、金属膜37の研磨時間を短くすることが可能となるので、研磨工程におけるスループットを向上できる。

【0061】

なお、第2の実施の形態では、デュアルダマシン構造を例に挙げて説明したが、第2の実施の形態の半導体装置25の製造方法は、シングルダマシン構造の配線を形成する場合にも適用可能である。

【0062】

また、第2の実施の形態では、金属膜37の一例として、タングステン膜を用いた場合を例に挙げて説明したが、本発明は、タングステン膜以外の金属膜37、具体的には、銅(Cu)膜やアルミニウム合金膜(例えば、Al−Si−Cu膜)等にも適用可能である。

【0063】

図14は、本発明の第2の実施の形態の変形例に係る半導体装置の製造工程を示す断面図であり、研磨工程の第1段階を説明するための図である。

【0064】

先に説明した図12に示す工程では、第2の層間絶縁膜31の上面31aに形成されたバリア膜36の表面36aが露出されるまで、第1段階の研磨を行なう場合を例に挙げて説明したが、図14に示すように、第1段階の研磨は、バリア膜36の表面36aが露出される前の状態、つまり、第1段階の研磨終了後の研磨面全体が金属膜37の状態で終了させてもよい。

この場合、残存する金属膜37を研磨するところから、第2段階の研磨を開始し、該第2段階の研磨は、第2の層間絶縁膜31の上面31aが露出されるまで行なう。

【0065】

次に、図11及び図13を参照して、本発明の第2の実施の形態の他の変形例に係る半導体装置25の製造方法について説明する。

第2の実施の形態の変形例に係る半導体装置25の製造方法は、先に説明した図11に示す工程後に、図13で説明した金属膜37の研磨レートと第2の層間絶縁膜31の研磨レートとの差が小さい研磨条件のみを用いて研磨を行なうことで、図13に示す複数のコンタクトプラグ39及び配線41を形成すること以外は、第2の実施の形態の半導体装置25の製造方法と同様な手法により行なう。

【0066】

つまり、第2の実施の形態の変形例に係る半導体装置25の製造方法では、1つの研磨条件のみを用いて、研磨を行うことで、複数のコンタクトプラグ39及び配線41を形成する。

【0067】

第2の実施の形態の変形例の半導体装置の製造方法によれば、コンタクト孔34及び溝33を埋め込むバリア膜36及び金属膜37を研磨する研磨工程において、金属膜33の研磨レートと第2の層間絶縁膜31の研磨レートとの差が小さい研磨条件のみを用いて、金属膜33、バリア膜34、及び第2の層間絶縁膜31の研磨を行なうことで、コンタクトプラグ39及び配線41を形成することにより、研磨工程を2段階に分ける必要がなくなるので、半導体装置25の製造工程を簡略化できる。

【0068】

なお、第2の実施の形態では、金属膜37の一例として、タングステン膜を用いた場合を例に挙げて説明したが、本発明は、タングステン膜以外の金属膜37、具体的には、銅(Cu)膜やアルミニウム合金膜(例えば、Al−Si−Cu膜)等にも適用可能である。

【0069】

以上、本発明の好ましい実施の形態について詳述したが、本発明はかかる特定の実施の形態に限定されるものではなく、特許請求の範囲内に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【産業上の利用可能性】

【0070】

本発明は、半導体装置の製造方法に適用可能である。

【符号の説明】

【0071】

10,25…半導体基板、11…半導体基板、11a,13a,14a,22a,27a,28a,29a,31a,41a…上面、13…不純物拡散層、14…層間絶縁膜、16,34…コンタクト孔、18,36…バリア膜、18a,33a,36a…表面、19,37…金属膜、22,39…コンタクトプラグ、23…研磨布、24…第1の研磨布、25…第2の研磨布、27…第1のシリコン窒化膜、28…第1の層間絶縁膜、29…第2のシリコン窒化膜、30…開口部、31…第1の層間絶縁膜、33…溝、41…配線

【特許請求の範囲】

【請求項1】

層間絶縁膜に開口部を形成する工程と、

前記開口部を埋め込む厚さとされた金属膜を形成する工程と、

CMP法により、前記層間絶縁膜の上面よりも上方に形成された前記金属膜を研磨除去することで、前記開口部内に導体パターンを形成する研磨工程と、

を有し、

前記研磨工程では、前記層間絶縁膜の上面が露出する前に、前記金属膜の研磨レートと前記層間絶縁膜の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことを特徴とする半導体装置の製造方法。

【請求項2】

前記金属膜を形成する前に、前記層間絶縁膜の上面、及び前記開口部の内面を覆うバリア膜を形成する工程を設け、

前記研磨工程では、前記層間絶縁膜の上面に形成された前記バリア膜が露出する前に、前記金属膜の研磨レートと前記層間絶縁膜の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記研磨工程では、前記金属膜の研磨レートと前記層間絶縁膜の研磨レートとの差が小さい研磨条件を用いて研磨を行なう前に、前記層間絶縁膜の研磨レートよりも前記金属膜の研磨レートが大きい研磨条件を用いて研磨を行なうことを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項4】

前記研磨工程では、前記金属膜の研磨レートと前記層間絶縁膜の研磨レートとの差が小さい研磨条件のみを用いて研磨を行なうことを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項5】

前記研磨工程で使用する研磨布は、第1の研磨布と、該第1の研磨布上に積層された第2の研磨布と、を有し、

前記第2の研磨布は、前記第1の研磨布の硬さよりも硬いことを特徴とする請求項1ないし4のうち、いずれか1項記載の半導体装置の製造方法。

【請求項6】

前記開口部として、半導体基板の表面側に形成された不純物拡散層の上面を露出するコンタクト孔を形成し、

前記導体パターンとして、前記コンタクト孔を埋め込み、かつ前記不純物拡散層の上面と接触するコンタクトプラグを形成することを特徴とする請求項1ないし5のうち、いずれか1項記載の半導体装置の製造方法。

【請求項7】

前記半導体基板の表面に形成された素子層上に、前記層間絶縁膜を形成し、

前記開口部として、溝を形成し、

前記導体パターンとして、前記溝を埋め込む配線を形成することを特徴とする請求項1ないし6のうち、いずれか1項記載の半導体装置の製造方法。

【請求項1】

層間絶縁膜に開口部を形成する工程と、

前記開口部を埋め込む厚さとされた金属膜を形成する工程と、

CMP法により、前記層間絶縁膜の上面よりも上方に形成された前記金属膜を研磨除去することで、前記開口部内に導体パターンを形成する研磨工程と、

を有し、

前記研磨工程では、前記層間絶縁膜の上面が露出する前に、前記金属膜の研磨レートと前記層間絶縁膜の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことを特徴とする半導体装置の製造方法。

【請求項2】

前記金属膜を形成する前に、前記層間絶縁膜の上面、及び前記開口部の内面を覆うバリア膜を形成する工程を設け、

前記研磨工程では、前記層間絶縁膜の上面に形成された前記バリア膜が露出する前に、前記金属膜の研磨レートと前記層間絶縁膜の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記研磨工程では、前記金属膜の研磨レートと前記層間絶縁膜の研磨レートとの差が小さい研磨条件を用いて研磨を行なう前に、前記層間絶縁膜の研磨レートよりも前記金属膜の研磨レートが大きい研磨条件を用いて研磨を行なうことを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項4】

前記研磨工程では、前記金属膜の研磨レートと前記層間絶縁膜の研磨レートとの差が小さい研磨条件のみを用いて研磨を行なうことを特徴とする請求項1または2記載の半導体装置の製造方法。

【請求項5】

前記研磨工程で使用する研磨布は、第1の研磨布と、該第1の研磨布上に積層された第2の研磨布と、を有し、

前記第2の研磨布は、前記第1の研磨布の硬さよりも硬いことを特徴とする請求項1ないし4のうち、いずれか1項記載の半導体装置の製造方法。

【請求項6】

前記開口部として、半導体基板の表面側に形成された不純物拡散層の上面を露出するコンタクト孔を形成し、

前記導体パターンとして、前記コンタクト孔を埋め込み、かつ前記不純物拡散層の上面と接触するコンタクトプラグを形成することを特徴とする請求項1ないし5のうち、いずれか1項記載の半導体装置の製造方法。

【請求項7】

前記半導体基板の表面に形成された素子層上に、前記層間絶縁膜を形成し、

前記開口部として、溝を形成し、

前記導体パターンとして、前記溝を埋め込む配線を形成することを特徴とする請求項1ないし6のうち、いずれか1項記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−253121(P2012−253121A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2011−123231(P2011−123231)

【出願日】平成23年6月1日(2011.6.1)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成23年6月1日(2011.6.1)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]