半導体装置の製造方法

【課題】電解めっき法によるCu膜の確実に析出させる。

【解決手段】抑制剤と促進剤を添加しためっき液とシリコン基板の相対速度が100m/分以上になる速度でシリコン基板を回転させながら、シリコン基板をめっき槽に浸漬させる。抑制剤の分子がシード層の表面に吸着し、シード溶解が抑制される。導電膜を成長させるときは、シリコン基板とめっき液の相対速度が30m/分以下になる速度でシリコン基板を回転させながら、シリコン基板とアノード電極の間に通電する。ボトムアップ成長が促進され、配線溝内での空孔の形成が防止される。

【解決手段】抑制剤と促進剤を添加しためっき液とシリコン基板の相対速度が100m/分以上になる速度でシリコン基板を回転させながら、シリコン基板をめっき槽に浸漬させる。抑制剤の分子がシード層の表面に吸着し、シード溶解が抑制される。導電膜を成長させるときは、シリコン基板とめっき液の相対速度が30m/分以下になる速度でシリコン基板を回転させながら、シリコン基板とアノード電極の間に通電する。ボトムアップ成長が促進され、配線溝内での空孔の形成が防止される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、LSI(Large Scale Integration)などの半導体装置には、高速化や高集積化が要求されている。これに伴って、半導体回路の配線の微細化や、薄膜化、低抵抗化、高電流密度化が図られている。例えば、配線の微細化に用いられる配線材料は、抵抗が低く電気伝導率に優れたCu膜が用いられる。Cu膜を用いた配線の形成は、予め絶縁膜上に配線溝を形成した後に、例えば、電解めっき法にて配線溝内にCu膜を成長させる。

【0003】

電解めっき法では、最初に、Cuが絶縁膜中に拡散することを防止する拡散防止膜(Barrier Metal)を形成し、配線溝を覆う。さらに、拡散防止膜を覆うようにシード層を形成する。シード層は、例えば物理気相成長(Physical Vapor Deposition;PVD)法によって形成される。拡散防止膜とシード層は真空中で連続して形成される。この後、基板をカソード電極に接続し、めっき液中に浸漬させる。さらに、基板とアノード電極との間に通電して、めっき液中のCuイオンを還元させ、Cuを電解析出させる。

【0004】

微細配線に用いられる電解めっき法では、開口した配線溝の底部から上部へとCuの充填が進む、いわゆるボトムアップ成長が知られている。ボトムアップ成長は、めっき液に数種類の有機添加剤や無機添加剤を添加することで実施される。例えば、めっき液として硫酸銅水溶液を用いたCuの電解めっきでは、Cuの析出を抑制する効果をもつ抑制剤と、Cuの析出を促進する効果を持つ促進剤が添加される。この場合、配線溝の表面の各所において抑制剤と促進剤のそれぞれの吸着濃度差によって、配線溝の底部におけるCuの成長率が顕著になり、ボトムアップ成長が実現すると考えられる。

【0005】

Cu膜を形成した後は、絶縁膜の表面に形成された余分なCu膜を化学機械研磨(CMP)法によって取り除く。Cu膜の膜厚が不均一であった場合には、ディッシングのばらつきによって配線抵抗がばらつくことがある。このために、従来では、Cu膜を形成中に電解めっき槽内で基板を所定速度で回転させている。基板の回転速度としては、例えば、基板の直径D、回転数Nとした場合に、D×N×πで定義される基板周辺の速度が、めっき浸漬から10sec以内の第一工程では6000×πmm/分以下にし、続く第二工程では6000×πmm/分より大きくしている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−277772

【特許文献2】特開2009−228078

【発明の概要】

【発明が解決しようとする課題】

【0007】

ここで、Cuの電解めっきの際には、めっき液中にシード層が溶解することがある。一般にPVD法を用いた成膜では、シャドウ効果により配線溝の内壁に対するCuのカバレジが低下し易い。さらに、PVD法にて形成したCu膜は、めっき液である硫酸銅水溶液に若干溶解する性質を有する。このために、カバレジが低下した箇所がめっき液に触れることで、シード層が溶解して、欠損する可能性がある。シード層が欠損すると、その部分に局所的な導通不足が生じる。シード欠損による局所的な導通不足が生じると、Cuの電解めっき時に配線溝内に空孔が発生するなど、Cuの埋込み不良を誘発し易くなる。

【0008】

PVD法によるシード層でシャドウ効果を緩和する手段としては、シード層を厚くことがある。しかしながら、シード層を厚くすると、配線溝の上端の開口部分においてシード層がひさし形状(Overhang)に突出し易くなる。その結果、電解めっき時に配線溝の底部にCu膜が埋め込まれる前に、配線溝の開口部分がCu膜で先に塞がるPinch-off現象が誘発され、配線内に空孔を生じさせ易くなる。Pinch-off現象は、配線が微細になるほど発現し易い。Pinch-off現象を防止するためにシード層を薄くすると、シード溶解が生じ易くなる。

【0009】

また、PVD法よりも被覆性に優れた化学気相成長(Chemical Vapor Deposition;CVD)法を用いてシード層を形成すると、シャドウ効果は低減されるが、膜中不純物濃度が高くなり易いため、他の膜との密着性を確保し難い。

この発明は、このような事情に鑑みてなされたものであり、電解めっき法によるCu膜の析出を確実にすることを目的とする。

【課題を解決するための手段】

【0010】

実施の形態の一観点によれば、基板の上方に絶縁膜を形成する工程と、前記絶縁膜に溝を形成する工程と、前記溝の内壁に導電性のシード層を形成する工程と、金属塩を含む電解めっき液と前記基板の外周部分の相対速度が100m/分以上となる回転速度で回転させながら、前記基板を電解めっき液に浸漬させる工程と、電解めっき液中に浸漬した前記基板に通電して前記溝の内部に導電膜を成長させる工程と、を含む半導体装置の製造方法が提供される。

【0011】

また、実施の形態の別の観点によれば、基板の上方に絶縁膜を形成する工程と、前記絶縁膜に溝を形成する工程と、前記溝の内壁に導電性のシード層を形成する工程と、金属塩を含む電解めっき液と前記基板の外周部分の相対速度が第1の相対速度となる回転速度で回転させながら、前記基板を電解めっき液に浸漬させる工程と、電解めっき液と前記基板の外周部分の相対速度を、前記第1の相対速度より遅い第2の相対速度で回転させながら、電解めっき液に浸漬させた前記基板に通電して前記溝の内部に導電膜を成長させる工程と、を含む半導体装置の製造方法が提供される。

【発明の効果】

【0012】

基板をめっき槽に浸漬させる過程におけるシード溶解が抑制される。シード溶解に起因する導通不良が防止され、配線溝に導電膜を確実に形成できる。

【図面の簡単な説明】

【0013】

【図1A】図1Aは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図1B】図1Bは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図1C】図1Cは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図1D】図1Dは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図1E】図1Eは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図2】図2は、本発明の第1の実施の形態に係る半導体装置の製造工程で使用されるめっき装置の概略構成の一例を示す図である。

【図3】図3は、本発明の第1の実施の形態に係る半導体装置の電解めっき工程のシーケンス図である。

【図4A】図4Aは、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の一例を示す断面図(その1)である。

【図4B】図4Bは、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の一例を示す断面図(その2)である。

【図4C】図4Cは、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の一例を示す断面図(その3)である。

【図4D】図4Dは、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の一例を示す断面図(その4)である。

【図4E】図4Eは、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の一例を示す断面図(その5)である。

【図5】図5は、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の浸漬段階における側壁のシード溶解面積率と抑制剤濃度の関係を調べた図である。

【図6】図6は、本発明の第1の実施の形態に係る半導体装置の電解めっき工程において抑制剤が吸着する過程の概念図である。

【図7】図7は、本発明の第1の実施の形態に係る半導体装置の電解めっき工程のボトム成長段階における側壁のシード溶解面積率と相対速度の関係を調べた図である。

【図8】図8は、本発明の第1の実施の形態に係る半導体装置の電解めっき工程においてめっき液と基板の相対速度とめっき膜の成長速度の関係を示す図である。

【図9】図9は、本発明の第2の実施の形態に係る半導体装置の電解めっき工程のシーケンス図である。

【発明を実施するための最良の形態】

【0014】

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。

前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない。

【0015】

(第1の実施の形態)

第1の実施の形態について、図面を参照して実施の形態について詳細に説明する。

最初に、図1Aに示す断面構造を得るまでの工程について説明する。まず、n型又はp型のシリコン(半導体)基板1の一方の面である表面を熱酸化することにより素子分離絶縁膜2を例えば30nmの深さに形成し、この素子分離絶縁膜2でトランジスタの活性領域を画定する。このような素子分離構造は、LOCOS(Local Oxidation of Silicon)と呼ばれる。素子分離構造には、STI(Shallow Trench Isolation)を用いても良い。

【0016】

次いで、シリコン基板1の活性領域にイオン注入法により、ドーパント不純物を導入してウェルを形成する。ドーパント不純物としてp型不純物、例えばボロンを導入すると、シリコン基板1にpウェル3が形成される。pウェル3を形成した後、その活性領域の表面を熱酸化してゲート絶縁膜5を形成する。ゲート絶縁膜5は、例えば熱酸化膜を約6nm〜7nmの厚さに形成する。なお、以下においては、pウェル3を形成した場合について説明するが、シリコン基板1にnウェルを形成した場合も同様の工程が実施される。

【0017】

続いて、シリコン基板1の上側全面に、ポリシリコン膜を例えばCVD法を用いて200nmの膜厚に形成する。その後に、フォトリソグラフィ技術及びエッチング技術を用いてポリシリコン膜をパターニングして、シリコン基板1上にゲート電極6を形成する。ゲート電極6は、pウェル3上に互いに平行に複数形成される。

【0018】

さらに、ゲート電極6をマスクにしてpウェル3にイオンを注入し、pウェル3のゲート電極6の両側の領域に、n型不純物としてリンを導入する。これにより、第1、第2ソース/ドレインエクステンション8が形成される。第1、第2ソース/ドレインエクステ

ンション8は、エクステンションソース/ドレイン領域の浅い領域を構成する。その後に、シリコン基板1の上側全面に、絶縁膜としてシリコン酸化膜を例えばCVD法を用いて300nmの厚さに形成する。その後、絶縁膜を異方性エッチングする。絶縁膜がエッチバックされ、ゲート電極6の側部に絶縁性サイドウォール10が形成される。

【0019】

続いて、ゲート電極6及び絶縁性サイドウォール10をマスクとして用い、シリコン基板1に砒素等のn型のドーパント不純物を再びイオン注入する。これにより、ゲート電極6の側方のpウェル3に、ソース/ドレイン拡散層11が形成される。ソース/ドレイン拡散層11は、エクステンションソース/ドレインの深い領域を構成する。

【0020】

さらに、シリコン基板1の全面に、例えば、スパッタリング法によりコバルト膜等の高融点金属膜を10nmの厚さに形成する。この後、高融点金属膜を例えば、500℃で30秒加熱してシリコンと反応させる。これにより、ソース/ドレイン拡散層11におけるシリコン基板1上にコバルトシリサイド層等の高融点金属シリサイド層が形成され、各ソース/ドレイン拡散層11が低抵抗化する。この後、素子分離絶縁膜2の上などに未反応のまま残っている高融点金属膜を例えば硫酸と過酸化水素水の混合液によってウエットエッチングして除去する。この後、窒素雰囲気中、800℃で30秒のアニールを2回行う。これにより、ソース/ドレイン拡散層11上に、例えばコバルトシリサイドで形成されるソース/ドレイン電極12Aが形成される。また、ゲート電極6の上部に、例えばコバルトシリサイドからなるシリサイド層12Bが形成される。

【0021】

ここまでの工程により、シリコン基板1の活性領域には、ゲート絶縁膜5、ゲート電極6、及びソース/ドレイン電極12A等から構成される半導体素子であるトランジスタT1,T2が形成される。

【0022】

次に、シリコン基板1の上側の全面に、酸化膜14として、例えば酸化シリコン膜(SIO膜)をプラズマCVD法によって1000nmの厚さに形成する。この後、CMP法によって酸化膜14の表面を研磨して平坦化する。

【0023】

続いて、不図示のレジスト膜をマスクに用いて酸化膜14をエッチングして、コンタクトホール15を形成する。コンタクトホール15の径は、例えば0.25μmとし、ソース/ドレイン電極12Aに到達するまでとする。

【0024】

そして、コンタクトホール15を用いてソース/ドレイン電極12Aに電気的に接続される導電性プラグ16を形成する。具体的には、コンタクトホール15の内面に密着膜として、例えばTi/TiN膜をTiCl4ガスを用いたCVD法によって形成する。さらに、密着膜上にW膜を成長させる。W膜は、例えば、WF6ガスとSiH4ガス、又はWF6ガスとH2ガスを用いたCVD法によって形成する。W膜は、酸化膜14上で例えば300nmに達する厚さとする。これにより、W膜でコンタクトホール15の空隙が埋まる。この後、酸化膜14の上面上に成長した余分なW膜及び密着膜をCMP法で除去する。これにより、各コンタクトホール15に、導電性プラグ16が1つずつ形成される。

【0025】

次に、図1Bに示す断面構造を得るまでの工程について説明する。

酸化膜14の上に、ライナー膜21として、例えば、CやNを含む酸化膜をプラズマCVD法により数十nmの厚さに形成する。続いて、ライナー膜21の上に、絶縁層間膜22として、有機又は無機の低誘電率膜を100nm〜300nmの厚さに形成する。絶縁層間膜22は、例えば、スピン型塗布装置を用いてライナー膜21上に均一に塗布した後、熱処理によって硬化させる。ライナー膜21と絶縁層間膜22との積層膜によって1層目の層間絶縁膜20が形成される。

【0026】

この後、層間絶縁膜20上に、ハードマスクとなるシリコンカーバイト系の絶縁膜23を数十nmの厚さに形成する。さらに、絶縁膜23の上に、フォトレジスト膜をスピンコート法によって50nm〜500nmの厚さに形成する。続いて、レジスト膜をパターニングして配線溝に対応した開口を有するマスク24を形成する。

【0027】

次に、図1Cに示す断面構造を得るまでの工程について説明する。

さらに、マスク24を用いて、絶縁膜23をドライエッチングしてハードマスク23Aを形成する。さらに、層間絶縁膜20、ライナー膜21を順番にドライエッチングして配線溝26を形成する。ドライエッチングは、例えば、CF4などCF系のガス、NH3ガス、あるいはN2/H2ガスを添加した反応性プラズマエッチングが用いられる。配線溝26は、下層の導電性プラグ16が露出する深さまで形成される。配線溝26を形成した後は、マスク24を有機系の洗浄液で洗い流して除去しても良い。さらに、層間絶縁膜20に吸着した水分を除去するために、例えば150℃〜300℃で熱処理する。処理時間は、例えば、0.5分〜3分とする。その後、洗浄のために、Arプラズマを用いてハードマスク23A及び配線溝26を5nm〜15nmの範囲で物理的にエッチングする。又は、H2ガスを含む還元性ガスを導入しながら、150℃〜350℃で熱処理を0.5分〜3分実施しても良い。

【0028】

次に、図1Dに示す断面構造を得るまでの工程について説明する。

最初に、配線溝26の内面とハードマスク23Aを覆うようにバリアメタル膜27を形成する。さらに、バリアメタル膜27の上に不図示のシード層を形成する。バリアメタル膜27とシード層は、例えば、同一の成膜装置に付属されたそれぞれの専用チャンバにおいてPVD法によって形成される。即ち、バリアメタル膜27とシード層は、大気に暴露されることなく、真空下にて連続して形成される。バリアメタル膜27には、タンタル系化合物やチタン系化合物が用いられ、配線溝26及びハードマスク23A上に形成される。バリアメタル膜27の厚さは、平坦部で3nm〜30nmとする。シード層は、例えば、銅や銅合金が用いられる。シード層の厚さは、平坦部において10nm〜100nmとする。次に、電解めっき法によって配線溝26内にCuからなる導電膜28を充填する。導電膜28は、ハードマスク23Aの上方にも形成される。

【0029】

次に、図1Eに示すように、配線溝26上の余分なCuや、パターニングされていない平坦部のCu、バリアメタル膜27、ハードマスク23Aを除去するために、CMP(Chemical Mechanical Polishing)法により研磨する。CMP法には、有機酸スラリー液を用いる。研磨後は、基板表面の残留物を除去するため、有機酸洗浄液を用いた表面洗浄を行う場合もある。これによって、層間絶縁膜20に配線71が埋め込まれた配線層72が形成された半導体装置73が形成される。半導体装置73は、2層以上の配線層を有しても良い。この場合には、図1Bから図1Eに示す工程を繰り返す。

【0030】

ここで、図1Dを用いて説明した電解めっき工程の詳細について、以下に説明する。

図2に示すように、電解めっきに使用するめっき装置31は、上部に給電機構を備える回転ユニット32を有し、下部にめっき槽33が配置されている。回転ユニット32は、回転軸34の下端に基板ホルダ35が取り付けられている。基板ホルダ35の下面には、クランプ36が複数配置されており、シリコン基板1を下向き、即ち配線溝26の開口が下側に配置されるように、保持される。回転ユニット32は、回転コントローラ37によって制御される。

【0031】

めっき槽33内には、アノード電極38が、シリコン基板1と対向する位置に配置される。アノード電極38には、例えば、純銅又は含リン銅I(0at%〜数at%)が用いられる。アノード電極38とカソード電極(シリコン基板1)間には、シリコン基板1にめっき液が均一に接触するよう拡散板39が設置される。アノード電極38及び拡散板3

9は、めっき液内に浸漬されている。めっき槽33は、配管41を介してめっきタンク42が接続されており、めっき液はめっき槽33とめっきタンク42の間で、循環ポンプ43によって5l/分〜40l/分の速度で循環させられる。めっきタンク42には、めっき液中に添加剤を供給する添加剤供給機44が設けられており、めっき液中の添加剤濃度を調整可能になっている。めっき液には、抑制剤と促進剤が添加された硫酸銅水溶液を用いる。抑制剤には、比較的分子量の大きい(M.W.=1000〜5000)鎖状構造の有機高分子、例えば、ポリエチレングリコールやポリプロピレングリコールなどが用いられる。また、促進剤には、比較的分子量の小さく(M.W.=100〜500)、かつCuと親和力が高い元素(例えばS:硫黄)を含む有機あるいは無機化合物が用いられる。

【0032】

さらに、めっき装置31には、外部電源45が設けられており、めっき槽33内のアノード電極38と、回転ユニット32のクランプ36との間に電力を印加可能になっている。Cuの成長に必要な電流は、クランプ36を介してシリコン基板1に供給される。回転ユニット32に装着されたシリコン基板1はカソード電極に相当し、電解析出により表面がCuで被覆される。めっき槽33内へのめっき液及び添加剤の供給は、めっき槽33下部から行われ、めっき槽33上方へ流れた後、めっき槽33の側部のドレイン33Aを通って排出される。

【0033】

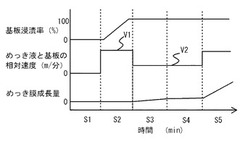

さらに、図3に電解めっき工程のシーケンスを示す。横軸は時間の経過を示す。縦軸は上から、基板浸漬率、めっき液とシリコン基板の相対速度、めっき膜成長量を示す。最初の第1のステップS1では、回転ユニット32にシリコン基板1を装着する。この段階では、基板浸漬率、相対速度、めっき膜成長量は、共にゼロである。

【0034】

続く第2のステップS2では、シリコン基板1をめっき液に浸漬させる。このとき、基板浸漬率は、徐々に増加する。シリコン基板1は、めっき面、即ち配線溝26が開口する面を下側にして回転ユニット32に装着される。回転ユニット32は、シリコン基板1を回転させながらめっき槽33に近接する方向へ移動し、シリコン基板1をめっき液へ浸漬させる。この回転によりシリコン基板1とめっき液の相対速度が生じる。相対速度は、100m/分以上の第1の速度V1に保持される。相対速度の詳細は、後に説明する。めっき膜成長量は、ゼロである。基板浸漬率が100%になった後も相対速度は、100m/分以上で保持され、この後、第3のステップS3であるボトムアップ成長段階に移行する。

【0035】

第3のステップS3以降では、基板浸漬率はめっき成長が終了するまで、100%に維持される。基板とめっき液の相対速度は、30m/分以下の第2の速度V2に維持される。相対速度の詳細は、後に説明する。シリコン基板1に対する通電によって、めっき膜の成長が開始される。続くステップS4で配線溝26に導電膜28が埋め込まれる。配線溝26への導電膜28の埋め込みが終了したら、第4のステップS5に移行する。

【0036】

第4のステップS5では、平坦部を含めたシリコン基板1の上方の全面に導電膜28を均一に成長させる。めっき液40を攪拌する観点から、相対速度を増加させる。しかしながら、相対速度は、第4のステップS4から変化させなくても良い。

【0037】

ここで、電解めっき工程におけるシリコン基板1とめっき液の相対速度(第1の速度V1)の詳細について説明する。

ステップS2でシリコン基板1をめっき液に浸漬させるときは、シリコン基板1とめっき液の相対速度が100m/分以上になるように制御する。シリコン基板1を回転運動させるので基板面内で相対速度に差が生じることになるが、シード溶解が起き易い箇所における相対速度が100m/分以上になるようにする。シード溶解が起き易い箇所とは、シリコン基板1の外周部付近であり、PVD法によるシード層の成膜時にシャドウ効果が発

生し易い場所である。

【0038】

図4Aにシャドウ効果が現われた箇所の一部拡大図を示す。図4Aでは、シリコン基板1が下向きにめっき装置31の回転ユニット32に保持されている状態における一部拡大図である。下向きに配置されたシリコン基板1には、配線溝26とハードマスク23Aを覆うようにバリアメタル膜27が形成されている。バリアメタル膜27の表面に形成されたシード層28Aは、配線溝26の奥部分がシャドウ効果によって相対的に薄くなっている。

【0039】

シード溶解の多くは、図4Bに示すようにシリコン基板1をめっき液へ浸漬するタイミングで起こると考えられる。めっき添加剤である抑制剤が、シード溶解を抑制する効果を有することを検証するために、配線溝26が形成されたシリコン基板1にバリアメタル膜27とシード層28AをPVD法にて形成し、抑制剤を0ml/l(無添加)しためっき液と、抑制剤を0.1ml/l添加しためっき液とに、それぞれ数秒間、シリコン基板1を浸漬させた。

【0040】

図5に示すように、抑制剤が無添加の場合の側壁のシード溶解の面積に比べて、抑制剤を0.1ml/l添加しためっき液では、配線溝26の側壁のシード溶解の面積が大幅に減少した。これは、抑制剤がシード層28Aの表面を被覆し、シード層28Aが保護されたためであると考えられる。

【0041】

図6に概念図を示すように、シリコン基板1の表面とめっき液40との界面には、拡散層51と呼ばれるミクロな領域が形成されると考えられる。シリコン基板1の表面から離れた領域は、流動層52になっている。めっき液40中の添加剤分子53は、液循環によりシリコン基板1の近傍に運ばれ、拡散層51を通って基板表面に到着(吸着)する。一般には、拡散層51内は限りなく静止系と見なされる。また、抑制剤分子53は分子量が比較的大きく、拡散層51中の移動速度は遅いと予想される。したがって、抑制剤分子53が基板表面に吸着する速度は、抑制剤分子53が拡散層51を通過する過程に律速されると考えられる。

【0042】

ここで、流動液体と固体界面に発生する拡散層51の厚さは、液体の流動速度に依存して変化し、流動速度が増すほど拡散層51の厚さは減少する。例として、溶液中に浸した回転電極の表面に発生する拡散層51の厚さは、Y. G. Levich(Physicochemical Hydrodynamics, Prentice-Hall, Englewood Cliffs, N.J., 1962)によると、拡散層厚さ: δ=1.61×D1/3ν1/6ω−1/2となる。ここで、D:拡散係数(dm2/s)、ν:動粘度 (dm2/s)、ω:角速度 (s−1)又は2πN/60(Nは回転数;rpm)であり、この式中の角速度が流動速度に相当する。

【0043】

この実施の形態では、流動速度はシリコン基板1とめっき液40の相対速度に相当する。つまり、シリコン基板1とめっき液40の相対速度を増大させて拡散層51の厚さを減らせば、シリコン基板1への抑制剤分子53の吸着速度が大きくなる。

【0044】

ここで、シリコン基板1とめっき液40の相対速度と、シード溶解の関係を調べた結果を図7に示す。めっき液40には、抑制剤が1ml/l添加し、相対速度は14m/分と、120m/分とした。図7からは、相対速度が14m/分に比べて、相対速度が120m/分ではシード溶解が軽減されていることがわかる。これは、相対速度が大きい方が、抑制剤の吸着速度が増加するためである。さらに、相対速度を変化させながら電解めっきをした結果、シリコン基板1とめっき液の相対速度が100m/分以上であれば、配線溝26に導電膜28を空隙なく形成できることがわかった。ここで、相対速度は、シード溶解が起き易い箇所、即ちシリコン基板1の外周部分におけるシリコン基板1とめっき液の

相対速度とする。

【0045】

シリコン基板1の回転速度は、めっき装置31の回転コントローラ37によって制御されている。また、めっき液の移動速度は、循環ポンプ43の性能などによって決まり、ほぼ一定の値にできる。したがって、シリコン基板1とめっき液の相対速度は、めっき装置31によって簡単に制御できる。

【0046】

次に、図3のステップS3におけるシリコン基板1とめっき液の相対速度(第2の速度V2)について説明する。

ステップS3では、図4Cに示すように、シリコン基板1をめっき液40に浸漬させた後、シリコン基板1に電流を流してめっき成膜を行う。この際、シリコン基板1とめっき液40の相対速度が30m/分以下になるように、回転速度を回転コントローラ37で制御する。ここでは、シード溶解が起き易い箇所、即ちシリコン基板1の外周部分におけるシリコン基板1とめっき液の相対速度が30m/分以下になるようにする。配線溝26に導電膜28が充填される過程では、添加剤の効果によりボトムアップ成長が支配的に進行する。

【0047】

ここで、ボトムアップ成長中にシード溶解が発生するケースもある。例えば、配線溝26の開口部分では、配線溝26の側壁に沿って空孔が発生することがある。これは、シード溶解に起因して発生すると考えられる。添加剤が比較的に吸着し易い配線溝26の開口付近に空孔が発生し易いことから、一度吸着した抑制剤が、電気分解などの作用によりシード層28Aの表面から脱離する機構が考えられる。したがって、ボトムアップ成長は、抑制剤が配線溝26の側壁のシード層28Aから脱離する前に完了させる必要がある。

【0048】

ボトムアップ成長速度を増加させるには、配線溝26の底部26Aにおける促進剤の吸着濃度(吸着速度)を増すか、あるいは抑制剤の吸着濃度を減少させれば良い。ここで、比較的分子量の小さい促進剤は、シリコン基板1への吸着速度が早く、拡散層51を通過する時間が短い。さらに、促進剤の吸着速度を増すのは困難である。一方、抑制剤の吸着速度は、拡散層51の厚さに依存するため、拡散層51を厚くすることで吸着速度を減少できる。

【0049】

抑制剤の吸着程度は、ボトムアップ成長速度と配線溝26以外の平坦領域におけるめっき成長速度の比較から把握可能であり、配線溝26の内外に抑制剤が十分吸着した状態では、ボトムアップ成長速度と平坦領域でのめっき成長速度は等しくなる。一方、抑制剤の供給が十分でなく、配線溝26の内部の抑制剤の吸着が乏しい場合は、ボトムアップ成長速度と平坦領域でのめっき成長速度の差は大きくなる。

【0050】

図8にめっき液40とシリコン基板1の相対速度とめっき成長速度の関係を示す。横軸は相対速度を示し、縦軸はめっき成長速度を示す。ラインL1はボトムアップ成長速度を示し、ラインL2は平坦部のめっき成長速度を示す。ボトムアップ成長速度は、幅70nmの配線溝26を用いて算出し、めっき液40中には1ml/lの抑制剤を添加した。相対速度が30m/分以下では、ボトムアップ成長速度と平坦領域でのめっき成長速度の差が大きい。この領域では、配線溝26の内部の抑制剤の吸着が少ないためである。一方、相対速度が100m/分以上ではボトムアップ成長速度と平坦部でのめっき成長速度がほぼ等しくなる。この領域では、配線溝26の内部の抑制剤吸着が十分進んでおり、吸着速度が速いことを示唆する。

【0051】

従って、図4Dに示すように、ボトムアップ成長によって配線溝26に導電膜28が充填されるまでは、ボトムアップ成長速度が平坦部に比べて顕著になる相対速度で導電膜28を成長させる。この後、図4Eに示すように、ハードマスク23Aの上に200nm〜

3000nmの厚さに導電膜28を成膜する。これは、後のCMP工程において研磨マージンを確保するためである。図4Cから図4Eにおける導電膜28の成長は、例えば、電流密度7〜30A/cm2にて行われる。めっき成膜後は、導電膜28の残留応力を緩和するため、100℃〜350℃で1分〜10分間熱処理を行っても良い。

【0052】

以上、説明したように、この実施の形態では、シリコン基板1をめっき液に浸漬させるときには、シリコン基板1とめっき液の相対速度を100m/分以上にした。これによって、シード層28Aの表面に対する抑制剤の吸着が促進され、シード溶解が低減される。これによって、配線溝26内の空隙発生を抑制できる。また、シリコン基板1をめっき液に浸漬させた後、導電膜28を成長させるときには、シリコン基板1とめっき液の相対速度を30m/分以下にしたので、配線溝26内の抑制剤の吸着が少なくなって、ボトムアップ成長が促進される。これによって、シード溶解が進行するよりも速やかに配線溝26内の導電膜28を埋め込むことができる。これによって、配線溝26の空隙発生を抑制できる。

【0053】

ここで、ステップS3のボトムアップ成長中にシード溶解が発生しない場合には、ステップS2のシリコン基板1の浸漬時のみ相対速度を制御しても良い。また、ステップS3のシリコン基板1の浸漬時のシード溶解を考慮する必要がない場合には、ステップS3のボトムアップ成長時のみ相対速度を制御しても良い。

【0054】

(第2の実施の形態)

第2の実施の形態について図面を参照して説明する。第1の実施の形態と同じ構成要素には同一の符号を付している。また、第1の実施の形態と重複する説明は省略する。

この実施の形態では、シード溶解を防止するために、バイアス電圧を印加しながらシリコン基板1をめっき液に浸漬することを特徴とする。

【0055】

図9に電解めっき工程のシーケンスを示す。横軸は時間の経過を示す。縦軸は上から、基板浸漬率、めっき液とシリコン基板の相対速度、バイアス電圧、めっき膜成長量を示す。第1のステップS1では、回転ユニット32にシリコン基板1を装着する。この段階では、基板浸漬率、相対速度、バイアス電圧、めっき膜成長量は、共にゼロである。

【0056】

続く第2のステップS2では、シリコン基板1をめっき液40に浸漬させる。このとき、基板浸漬率は、徐々に増加する。相対速度は、100m/分以上の第1の速度V1に保持される。バイアス電圧は、めっき成長の際の電圧以下の値であって、シリコン基板1とアノード電極38の間に導電膜28を析出させない程度に調整された電圧を印加する。バイアス電圧の大きさは、導電膜28の成長時より小さい値であって、シリコン基板1の大きさやパターン、めっき装置31によって異なる値が用いられる。この段階でのめっき膜成長量は、ゼロである。基板浸漬率が100%になった後も相対速度は、100m/分以上で保持され、この後、第3のステップS3であるボトムアップ成長段階に移行する。

【0057】

第3のステップS3以降では、基板浸漬率はめっき成長が終了するまで、100%に維持される。相対速度は、30m/分以下の第2の速度V2に維持される。バイアス電圧は、ゼロに設定され、代わりに所定の電流がシリコン基板1に供給される。これによって、めっき膜の成長が開始される。続くステップS4で配線溝26に導電膜28が埋め込まれる。

【0058】

第4のステップS5では、平坦部を含めたシリコン基板1の上方の全面に導電膜28を均一に成長させる。めっき液40を攪拌する観点から、相対速度を増加させる。しかしながら、相対速度は、第4のステップS4から変化させなくても良い。

【0059】

この後、余分な導電膜28をCMP法によって研磨すると、図1Eに示すような半導体装置73が形成される。この実施の形態では、シリコン基板1をめっき液に浸漬させるときにバイアス電圧を印加することで、シード溶解がさらに抑制される。これによって、配線溝26の空隙発生をさらに抑制できる。その他の効果は第1の実施の形態と同様である。

【0060】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができる。

【符号の説明】

【0061】

1 シリコン基板

20 層間絶縁膜

26 配線溝(パターン)

28 導電膜

28A シード層

40 めっき液

V1 第1の速度

V2 第2の速度

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、LSI(Large Scale Integration)などの半導体装置には、高速化や高集積化が要求されている。これに伴って、半導体回路の配線の微細化や、薄膜化、低抵抗化、高電流密度化が図られている。例えば、配線の微細化に用いられる配線材料は、抵抗が低く電気伝導率に優れたCu膜が用いられる。Cu膜を用いた配線の形成は、予め絶縁膜上に配線溝を形成した後に、例えば、電解めっき法にて配線溝内にCu膜を成長させる。

【0003】

電解めっき法では、最初に、Cuが絶縁膜中に拡散することを防止する拡散防止膜(Barrier Metal)を形成し、配線溝を覆う。さらに、拡散防止膜を覆うようにシード層を形成する。シード層は、例えば物理気相成長(Physical Vapor Deposition;PVD)法によって形成される。拡散防止膜とシード層は真空中で連続して形成される。この後、基板をカソード電極に接続し、めっき液中に浸漬させる。さらに、基板とアノード電極との間に通電して、めっき液中のCuイオンを還元させ、Cuを電解析出させる。

【0004】

微細配線に用いられる電解めっき法では、開口した配線溝の底部から上部へとCuの充填が進む、いわゆるボトムアップ成長が知られている。ボトムアップ成長は、めっき液に数種類の有機添加剤や無機添加剤を添加することで実施される。例えば、めっき液として硫酸銅水溶液を用いたCuの電解めっきでは、Cuの析出を抑制する効果をもつ抑制剤と、Cuの析出を促進する効果を持つ促進剤が添加される。この場合、配線溝の表面の各所において抑制剤と促進剤のそれぞれの吸着濃度差によって、配線溝の底部におけるCuの成長率が顕著になり、ボトムアップ成長が実現すると考えられる。

【0005】

Cu膜を形成した後は、絶縁膜の表面に形成された余分なCu膜を化学機械研磨(CMP)法によって取り除く。Cu膜の膜厚が不均一であった場合には、ディッシングのばらつきによって配線抵抗がばらつくことがある。このために、従来では、Cu膜を形成中に電解めっき槽内で基板を所定速度で回転させている。基板の回転速度としては、例えば、基板の直径D、回転数Nとした場合に、D×N×πで定義される基板周辺の速度が、めっき浸漬から10sec以内の第一工程では6000×πmm/分以下にし、続く第二工程では6000×πmm/分より大きくしている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−277772

【特許文献2】特開2009−228078

【発明の概要】

【発明が解決しようとする課題】

【0007】

ここで、Cuの電解めっきの際には、めっき液中にシード層が溶解することがある。一般にPVD法を用いた成膜では、シャドウ効果により配線溝の内壁に対するCuのカバレジが低下し易い。さらに、PVD法にて形成したCu膜は、めっき液である硫酸銅水溶液に若干溶解する性質を有する。このために、カバレジが低下した箇所がめっき液に触れることで、シード層が溶解して、欠損する可能性がある。シード層が欠損すると、その部分に局所的な導通不足が生じる。シード欠損による局所的な導通不足が生じると、Cuの電解めっき時に配線溝内に空孔が発生するなど、Cuの埋込み不良を誘発し易くなる。

【0008】

PVD法によるシード層でシャドウ効果を緩和する手段としては、シード層を厚くことがある。しかしながら、シード層を厚くすると、配線溝の上端の開口部分においてシード層がひさし形状(Overhang)に突出し易くなる。その結果、電解めっき時に配線溝の底部にCu膜が埋め込まれる前に、配線溝の開口部分がCu膜で先に塞がるPinch-off現象が誘発され、配線内に空孔を生じさせ易くなる。Pinch-off現象は、配線が微細になるほど発現し易い。Pinch-off現象を防止するためにシード層を薄くすると、シード溶解が生じ易くなる。

【0009】

また、PVD法よりも被覆性に優れた化学気相成長(Chemical Vapor Deposition;CVD)法を用いてシード層を形成すると、シャドウ効果は低減されるが、膜中不純物濃度が高くなり易いため、他の膜との密着性を確保し難い。

この発明は、このような事情に鑑みてなされたものであり、電解めっき法によるCu膜の析出を確実にすることを目的とする。

【課題を解決するための手段】

【0010】

実施の形態の一観点によれば、基板の上方に絶縁膜を形成する工程と、前記絶縁膜に溝を形成する工程と、前記溝の内壁に導電性のシード層を形成する工程と、金属塩を含む電解めっき液と前記基板の外周部分の相対速度が100m/分以上となる回転速度で回転させながら、前記基板を電解めっき液に浸漬させる工程と、電解めっき液中に浸漬した前記基板に通電して前記溝の内部に導電膜を成長させる工程と、を含む半導体装置の製造方法が提供される。

【0011】

また、実施の形態の別の観点によれば、基板の上方に絶縁膜を形成する工程と、前記絶縁膜に溝を形成する工程と、前記溝の内壁に導電性のシード層を形成する工程と、金属塩を含む電解めっき液と前記基板の外周部分の相対速度が第1の相対速度となる回転速度で回転させながら、前記基板を電解めっき液に浸漬させる工程と、電解めっき液と前記基板の外周部分の相対速度を、前記第1の相対速度より遅い第2の相対速度で回転させながら、電解めっき液に浸漬させた前記基板に通電して前記溝の内部に導電膜を成長させる工程と、を含む半導体装置の製造方法が提供される。

【発明の効果】

【0012】

基板をめっき槽に浸漬させる過程におけるシード溶解が抑制される。シード溶解に起因する導通不良が防止され、配線溝に導電膜を確実に形成できる。

【図面の簡単な説明】

【0013】

【図1A】図1Aは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図1B】図1Bは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図1C】図1Cは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図1D】図1Dは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図1E】図1Eは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図2】図2は、本発明の第1の実施の形態に係る半導体装置の製造工程で使用されるめっき装置の概略構成の一例を示す図である。

【図3】図3は、本発明の第1の実施の形態に係る半導体装置の電解めっき工程のシーケンス図である。

【図4A】図4Aは、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の一例を示す断面図(その1)である。

【図4B】図4Bは、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の一例を示す断面図(その2)である。

【図4C】図4Cは、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の一例を示す断面図(その3)である。

【図4D】図4Dは、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の一例を示す断面図(その4)である。

【図4E】図4Eは、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の一例を示す断面図(その5)である。

【図5】図5は、本発明の第1の実施の形態に係る半導体装置の電解めっき工程の浸漬段階における側壁のシード溶解面積率と抑制剤濃度の関係を調べた図である。

【図6】図6は、本発明の第1の実施の形態に係る半導体装置の電解めっき工程において抑制剤が吸着する過程の概念図である。

【図7】図7は、本発明の第1の実施の形態に係る半導体装置の電解めっき工程のボトム成長段階における側壁のシード溶解面積率と相対速度の関係を調べた図である。

【図8】図8は、本発明の第1の実施の形態に係る半導体装置の電解めっき工程においてめっき液と基板の相対速度とめっき膜の成長速度の関係を示す図である。

【図9】図9は、本発明の第2の実施の形態に係る半導体装置の電解めっき工程のシーケンス図である。

【発明を実施するための最良の形態】

【0014】

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。

前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない。

【0015】

(第1の実施の形態)

第1の実施の形態について、図面を参照して実施の形態について詳細に説明する。

最初に、図1Aに示す断面構造を得るまでの工程について説明する。まず、n型又はp型のシリコン(半導体)基板1の一方の面である表面を熱酸化することにより素子分離絶縁膜2を例えば30nmの深さに形成し、この素子分離絶縁膜2でトランジスタの活性領域を画定する。このような素子分離構造は、LOCOS(Local Oxidation of Silicon)と呼ばれる。素子分離構造には、STI(Shallow Trench Isolation)を用いても良い。

【0016】

次いで、シリコン基板1の活性領域にイオン注入法により、ドーパント不純物を導入してウェルを形成する。ドーパント不純物としてp型不純物、例えばボロンを導入すると、シリコン基板1にpウェル3が形成される。pウェル3を形成した後、その活性領域の表面を熱酸化してゲート絶縁膜5を形成する。ゲート絶縁膜5は、例えば熱酸化膜を約6nm〜7nmの厚さに形成する。なお、以下においては、pウェル3を形成した場合について説明するが、シリコン基板1にnウェルを形成した場合も同様の工程が実施される。

【0017】

続いて、シリコン基板1の上側全面に、ポリシリコン膜を例えばCVD法を用いて200nmの膜厚に形成する。その後に、フォトリソグラフィ技術及びエッチング技術を用いてポリシリコン膜をパターニングして、シリコン基板1上にゲート電極6を形成する。ゲート電極6は、pウェル3上に互いに平行に複数形成される。

【0018】

さらに、ゲート電極6をマスクにしてpウェル3にイオンを注入し、pウェル3のゲート電極6の両側の領域に、n型不純物としてリンを導入する。これにより、第1、第2ソース/ドレインエクステンション8が形成される。第1、第2ソース/ドレインエクステ

ンション8は、エクステンションソース/ドレイン領域の浅い領域を構成する。その後に、シリコン基板1の上側全面に、絶縁膜としてシリコン酸化膜を例えばCVD法を用いて300nmの厚さに形成する。その後、絶縁膜を異方性エッチングする。絶縁膜がエッチバックされ、ゲート電極6の側部に絶縁性サイドウォール10が形成される。

【0019】

続いて、ゲート電極6及び絶縁性サイドウォール10をマスクとして用い、シリコン基板1に砒素等のn型のドーパント不純物を再びイオン注入する。これにより、ゲート電極6の側方のpウェル3に、ソース/ドレイン拡散層11が形成される。ソース/ドレイン拡散層11は、エクステンションソース/ドレインの深い領域を構成する。

【0020】

さらに、シリコン基板1の全面に、例えば、スパッタリング法によりコバルト膜等の高融点金属膜を10nmの厚さに形成する。この後、高融点金属膜を例えば、500℃で30秒加熱してシリコンと反応させる。これにより、ソース/ドレイン拡散層11におけるシリコン基板1上にコバルトシリサイド層等の高融点金属シリサイド層が形成され、各ソース/ドレイン拡散層11が低抵抗化する。この後、素子分離絶縁膜2の上などに未反応のまま残っている高融点金属膜を例えば硫酸と過酸化水素水の混合液によってウエットエッチングして除去する。この後、窒素雰囲気中、800℃で30秒のアニールを2回行う。これにより、ソース/ドレイン拡散層11上に、例えばコバルトシリサイドで形成されるソース/ドレイン電極12Aが形成される。また、ゲート電極6の上部に、例えばコバルトシリサイドからなるシリサイド層12Bが形成される。

【0021】

ここまでの工程により、シリコン基板1の活性領域には、ゲート絶縁膜5、ゲート電極6、及びソース/ドレイン電極12A等から構成される半導体素子であるトランジスタT1,T2が形成される。

【0022】

次に、シリコン基板1の上側の全面に、酸化膜14として、例えば酸化シリコン膜(SIO膜)をプラズマCVD法によって1000nmの厚さに形成する。この後、CMP法によって酸化膜14の表面を研磨して平坦化する。

【0023】

続いて、不図示のレジスト膜をマスクに用いて酸化膜14をエッチングして、コンタクトホール15を形成する。コンタクトホール15の径は、例えば0.25μmとし、ソース/ドレイン電極12Aに到達するまでとする。

【0024】

そして、コンタクトホール15を用いてソース/ドレイン電極12Aに電気的に接続される導電性プラグ16を形成する。具体的には、コンタクトホール15の内面に密着膜として、例えばTi/TiN膜をTiCl4ガスを用いたCVD法によって形成する。さらに、密着膜上にW膜を成長させる。W膜は、例えば、WF6ガスとSiH4ガス、又はWF6ガスとH2ガスを用いたCVD法によって形成する。W膜は、酸化膜14上で例えば300nmに達する厚さとする。これにより、W膜でコンタクトホール15の空隙が埋まる。この後、酸化膜14の上面上に成長した余分なW膜及び密着膜をCMP法で除去する。これにより、各コンタクトホール15に、導電性プラグ16が1つずつ形成される。

【0025】

次に、図1Bに示す断面構造を得るまでの工程について説明する。

酸化膜14の上に、ライナー膜21として、例えば、CやNを含む酸化膜をプラズマCVD法により数十nmの厚さに形成する。続いて、ライナー膜21の上に、絶縁層間膜22として、有機又は無機の低誘電率膜を100nm〜300nmの厚さに形成する。絶縁層間膜22は、例えば、スピン型塗布装置を用いてライナー膜21上に均一に塗布した後、熱処理によって硬化させる。ライナー膜21と絶縁層間膜22との積層膜によって1層目の層間絶縁膜20が形成される。

【0026】

この後、層間絶縁膜20上に、ハードマスクとなるシリコンカーバイト系の絶縁膜23を数十nmの厚さに形成する。さらに、絶縁膜23の上に、フォトレジスト膜をスピンコート法によって50nm〜500nmの厚さに形成する。続いて、レジスト膜をパターニングして配線溝に対応した開口を有するマスク24を形成する。

【0027】

次に、図1Cに示す断面構造を得るまでの工程について説明する。

さらに、マスク24を用いて、絶縁膜23をドライエッチングしてハードマスク23Aを形成する。さらに、層間絶縁膜20、ライナー膜21を順番にドライエッチングして配線溝26を形成する。ドライエッチングは、例えば、CF4などCF系のガス、NH3ガス、あるいはN2/H2ガスを添加した反応性プラズマエッチングが用いられる。配線溝26は、下層の導電性プラグ16が露出する深さまで形成される。配線溝26を形成した後は、マスク24を有機系の洗浄液で洗い流して除去しても良い。さらに、層間絶縁膜20に吸着した水分を除去するために、例えば150℃〜300℃で熱処理する。処理時間は、例えば、0.5分〜3分とする。その後、洗浄のために、Arプラズマを用いてハードマスク23A及び配線溝26を5nm〜15nmの範囲で物理的にエッチングする。又は、H2ガスを含む還元性ガスを導入しながら、150℃〜350℃で熱処理を0.5分〜3分実施しても良い。

【0028】

次に、図1Dに示す断面構造を得るまでの工程について説明する。

最初に、配線溝26の内面とハードマスク23Aを覆うようにバリアメタル膜27を形成する。さらに、バリアメタル膜27の上に不図示のシード層を形成する。バリアメタル膜27とシード層は、例えば、同一の成膜装置に付属されたそれぞれの専用チャンバにおいてPVD法によって形成される。即ち、バリアメタル膜27とシード層は、大気に暴露されることなく、真空下にて連続して形成される。バリアメタル膜27には、タンタル系化合物やチタン系化合物が用いられ、配線溝26及びハードマスク23A上に形成される。バリアメタル膜27の厚さは、平坦部で3nm〜30nmとする。シード層は、例えば、銅や銅合金が用いられる。シード層の厚さは、平坦部において10nm〜100nmとする。次に、電解めっき法によって配線溝26内にCuからなる導電膜28を充填する。導電膜28は、ハードマスク23Aの上方にも形成される。

【0029】

次に、図1Eに示すように、配線溝26上の余分なCuや、パターニングされていない平坦部のCu、バリアメタル膜27、ハードマスク23Aを除去するために、CMP(Chemical Mechanical Polishing)法により研磨する。CMP法には、有機酸スラリー液を用いる。研磨後は、基板表面の残留物を除去するため、有機酸洗浄液を用いた表面洗浄を行う場合もある。これによって、層間絶縁膜20に配線71が埋め込まれた配線層72が形成された半導体装置73が形成される。半導体装置73は、2層以上の配線層を有しても良い。この場合には、図1Bから図1Eに示す工程を繰り返す。

【0030】

ここで、図1Dを用いて説明した電解めっき工程の詳細について、以下に説明する。

図2に示すように、電解めっきに使用するめっき装置31は、上部に給電機構を備える回転ユニット32を有し、下部にめっき槽33が配置されている。回転ユニット32は、回転軸34の下端に基板ホルダ35が取り付けられている。基板ホルダ35の下面には、クランプ36が複数配置されており、シリコン基板1を下向き、即ち配線溝26の開口が下側に配置されるように、保持される。回転ユニット32は、回転コントローラ37によって制御される。

【0031】

めっき槽33内には、アノード電極38が、シリコン基板1と対向する位置に配置される。アノード電極38には、例えば、純銅又は含リン銅I(0at%〜数at%)が用いられる。アノード電極38とカソード電極(シリコン基板1)間には、シリコン基板1にめっき液が均一に接触するよう拡散板39が設置される。アノード電極38及び拡散板3

9は、めっき液内に浸漬されている。めっき槽33は、配管41を介してめっきタンク42が接続されており、めっき液はめっき槽33とめっきタンク42の間で、循環ポンプ43によって5l/分〜40l/分の速度で循環させられる。めっきタンク42には、めっき液中に添加剤を供給する添加剤供給機44が設けられており、めっき液中の添加剤濃度を調整可能になっている。めっき液には、抑制剤と促進剤が添加された硫酸銅水溶液を用いる。抑制剤には、比較的分子量の大きい(M.W.=1000〜5000)鎖状構造の有機高分子、例えば、ポリエチレングリコールやポリプロピレングリコールなどが用いられる。また、促進剤には、比較的分子量の小さく(M.W.=100〜500)、かつCuと親和力が高い元素(例えばS:硫黄)を含む有機あるいは無機化合物が用いられる。

【0032】

さらに、めっき装置31には、外部電源45が設けられており、めっき槽33内のアノード電極38と、回転ユニット32のクランプ36との間に電力を印加可能になっている。Cuの成長に必要な電流は、クランプ36を介してシリコン基板1に供給される。回転ユニット32に装着されたシリコン基板1はカソード電極に相当し、電解析出により表面がCuで被覆される。めっき槽33内へのめっき液及び添加剤の供給は、めっき槽33下部から行われ、めっき槽33上方へ流れた後、めっき槽33の側部のドレイン33Aを通って排出される。

【0033】

さらに、図3に電解めっき工程のシーケンスを示す。横軸は時間の経過を示す。縦軸は上から、基板浸漬率、めっき液とシリコン基板の相対速度、めっき膜成長量を示す。最初の第1のステップS1では、回転ユニット32にシリコン基板1を装着する。この段階では、基板浸漬率、相対速度、めっき膜成長量は、共にゼロである。

【0034】

続く第2のステップS2では、シリコン基板1をめっき液に浸漬させる。このとき、基板浸漬率は、徐々に増加する。シリコン基板1は、めっき面、即ち配線溝26が開口する面を下側にして回転ユニット32に装着される。回転ユニット32は、シリコン基板1を回転させながらめっき槽33に近接する方向へ移動し、シリコン基板1をめっき液へ浸漬させる。この回転によりシリコン基板1とめっき液の相対速度が生じる。相対速度は、100m/分以上の第1の速度V1に保持される。相対速度の詳細は、後に説明する。めっき膜成長量は、ゼロである。基板浸漬率が100%になった後も相対速度は、100m/分以上で保持され、この後、第3のステップS3であるボトムアップ成長段階に移行する。

【0035】

第3のステップS3以降では、基板浸漬率はめっき成長が終了するまで、100%に維持される。基板とめっき液の相対速度は、30m/分以下の第2の速度V2に維持される。相対速度の詳細は、後に説明する。シリコン基板1に対する通電によって、めっき膜の成長が開始される。続くステップS4で配線溝26に導電膜28が埋め込まれる。配線溝26への導電膜28の埋め込みが終了したら、第4のステップS5に移行する。

【0036】

第4のステップS5では、平坦部を含めたシリコン基板1の上方の全面に導電膜28を均一に成長させる。めっき液40を攪拌する観点から、相対速度を増加させる。しかしながら、相対速度は、第4のステップS4から変化させなくても良い。

【0037】

ここで、電解めっき工程におけるシリコン基板1とめっき液の相対速度(第1の速度V1)の詳細について説明する。

ステップS2でシリコン基板1をめっき液に浸漬させるときは、シリコン基板1とめっき液の相対速度が100m/分以上になるように制御する。シリコン基板1を回転運動させるので基板面内で相対速度に差が生じることになるが、シード溶解が起き易い箇所における相対速度が100m/分以上になるようにする。シード溶解が起き易い箇所とは、シリコン基板1の外周部付近であり、PVD法によるシード層の成膜時にシャドウ効果が発

生し易い場所である。

【0038】

図4Aにシャドウ効果が現われた箇所の一部拡大図を示す。図4Aでは、シリコン基板1が下向きにめっき装置31の回転ユニット32に保持されている状態における一部拡大図である。下向きに配置されたシリコン基板1には、配線溝26とハードマスク23Aを覆うようにバリアメタル膜27が形成されている。バリアメタル膜27の表面に形成されたシード層28Aは、配線溝26の奥部分がシャドウ効果によって相対的に薄くなっている。

【0039】

シード溶解の多くは、図4Bに示すようにシリコン基板1をめっき液へ浸漬するタイミングで起こると考えられる。めっき添加剤である抑制剤が、シード溶解を抑制する効果を有することを検証するために、配線溝26が形成されたシリコン基板1にバリアメタル膜27とシード層28AをPVD法にて形成し、抑制剤を0ml/l(無添加)しためっき液と、抑制剤を0.1ml/l添加しためっき液とに、それぞれ数秒間、シリコン基板1を浸漬させた。

【0040】

図5に示すように、抑制剤が無添加の場合の側壁のシード溶解の面積に比べて、抑制剤を0.1ml/l添加しためっき液では、配線溝26の側壁のシード溶解の面積が大幅に減少した。これは、抑制剤がシード層28Aの表面を被覆し、シード層28Aが保護されたためであると考えられる。

【0041】

図6に概念図を示すように、シリコン基板1の表面とめっき液40との界面には、拡散層51と呼ばれるミクロな領域が形成されると考えられる。シリコン基板1の表面から離れた領域は、流動層52になっている。めっき液40中の添加剤分子53は、液循環によりシリコン基板1の近傍に運ばれ、拡散層51を通って基板表面に到着(吸着)する。一般には、拡散層51内は限りなく静止系と見なされる。また、抑制剤分子53は分子量が比較的大きく、拡散層51中の移動速度は遅いと予想される。したがって、抑制剤分子53が基板表面に吸着する速度は、抑制剤分子53が拡散層51を通過する過程に律速されると考えられる。

【0042】

ここで、流動液体と固体界面に発生する拡散層51の厚さは、液体の流動速度に依存して変化し、流動速度が増すほど拡散層51の厚さは減少する。例として、溶液中に浸した回転電極の表面に発生する拡散層51の厚さは、Y. G. Levich(Physicochemical Hydrodynamics, Prentice-Hall, Englewood Cliffs, N.J., 1962)によると、拡散層厚さ: δ=1.61×D1/3ν1/6ω−1/2となる。ここで、D:拡散係数(dm2/s)、ν:動粘度 (dm2/s)、ω:角速度 (s−1)又は2πN/60(Nは回転数;rpm)であり、この式中の角速度が流動速度に相当する。

【0043】

この実施の形態では、流動速度はシリコン基板1とめっき液40の相対速度に相当する。つまり、シリコン基板1とめっき液40の相対速度を増大させて拡散層51の厚さを減らせば、シリコン基板1への抑制剤分子53の吸着速度が大きくなる。

【0044】

ここで、シリコン基板1とめっき液40の相対速度と、シード溶解の関係を調べた結果を図7に示す。めっき液40には、抑制剤が1ml/l添加し、相対速度は14m/分と、120m/分とした。図7からは、相対速度が14m/分に比べて、相対速度が120m/分ではシード溶解が軽減されていることがわかる。これは、相対速度が大きい方が、抑制剤の吸着速度が増加するためである。さらに、相対速度を変化させながら電解めっきをした結果、シリコン基板1とめっき液の相対速度が100m/分以上であれば、配線溝26に導電膜28を空隙なく形成できることがわかった。ここで、相対速度は、シード溶解が起き易い箇所、即ちシリコン基板1の外周部分におけるシリコン基板1とめっき液の

相対速度とする。

【0045】

シリコン基板1の回転速度は、めっき装置31の回転コントローラ37によって制御されている。また、めっき液の移動速度は、循環ポンプ43の性能などによって決まり、ほぼ一定の値にできる。したがって、シリコン基板1とめっき液の相対速度は、めっき装置31によって簡単に制御できる。

【0046】

次に、図3のステップS3におけるシリコン基板1とめっき液の相対速度(第2の速度V2)について説明する。

ステップS3では、図4Cに示すように、シリコン基板1をめっき液40に浸漬させた後、シリコン基板1に電流を流してめっき成膜を行う。この際、シリコン基板1とめっき液40の相対速度が30m/分以下になるように、回転速度を回転コントローラ37で制御する。ここでは、シード溶解が起き易い箇所、即ちシリコン基板1の外周部分におけるシリコン基板1とめっき液の相対速度が30m/分以下になるようにする。配線溝26に導電膜28が充填される過程では、添加剤の効果によりボトムアップ成長が支配的に進行する。

【0047】

ここで、ボトムアップ成長中にシード溶解が発生するケースもある。例えば、配線溝26の開口部分では、配線溝26の側壁に沿って空孔が発生することがある。これは、シード溶解に起因して発生すると考えられる。添加剤が比較的に吸着し易い配線溝26の開口付近に空孔が発生し易いことから、一度吸着した抑制剤が、電気分解などの作用によりシード層28Aの表面から脱離する機構が考えられる。したがって、ボトムアップ成長は、抑制剤が配線溝26の側壁のシード層28Aから脱離する前に完了させる必要がある。

【0048】

ボトムアップ成長速度を増加させるには、配線溝26の底部26Aにおける促進剤の吸着濃度(吸着速度)を増すか、あるいは抑制剤の吸着濃度を減少させれば良い。ここで、比較的分子量の小さい促進剤は、シリコン基板1への吸着速度が早く、拡散層51を通過する時間が短い。さらに、促進剤の吸着速度を増すのは困難である。一方、抑制剤の吸着速度は、拡散層51の厚さに依存するため、拡散層51を厚くすることで吸着速度を減少できる。

【0049】

抑制剤の吸着程度は、ボトムアップ成長速度と配線溝26以外の平坦領域におけるめっき成長速度の比較から把握可能であり、配線溝26の内外に抑制剤が十分吸着した状態では、ボトムアップ成長速度と平坦領域でのめっき成長速度は等しくなる。一方、抑制剤の供給が十分でなく、配線溝26の内部の抑制剤の吸着が乏しい場合は、ボトムアップ成長速度と平坦領域でのめっき成長速度の差は大きくなる。

【0050】

図8にめっき液40とシリコン基板1の相対速度とめっき成長速度の関係を示す。横軸は相対速度を示し、縦軸はめっき成長速度を示す。ラインL1はボトムアップ成長速度を示し、ラインL2は平坦部のめっき成長速度を示す。ボトムアップ成長速度は、幅70nmの配線溝26を用いて算出し、めっき液40中には1ml/lの抑制剤を添加した。相対速度が30m/分以下では、ボトムアップ成長速度と平坦領域でのめっき成長速度の差が大きい。この領域では、配線溝26の内部の抑制剤の吸着が少ないためである。一方、相対速度が100m/分以上ではボトムアップ成長速度と平坦部でのめっき成長速度がほぼ等しくなる。この領域では、配線溝26の内部の抑制剤吸着が十分進んでおり、吸着速度が速いことを示唆する。

【0051】

従って、図4Dに示すように、ボトムアップ成長によって配線溝26に導電膜28が充填されるまでは、ボトムアップ成長速度が平坦部に比べて顕著になる相対速度で導電膜28を成長させる。この後、図4Eに示すように、ハードマスク23Aの上に200nm〜

3000nmの厚さに導電膜28を成膜する。これは、後のCMP工程において研磨マージンを確保するためである。図4Cから図4Eにおける導電膜28の成長は、例えば、電流密度7〜30A/cm2にて行われる。めっき成膜後は、導電膜28の残留応力を緩和するため、100℃〜350℃で1分〜10分間熱処理を行っても良い。

【0052】

以上、説明したように、この実施の形態では、シリコン基板1をめっき液に浸漬させるときには、シリコン基板1とめっき液の相対速度を100m/分以上にした。これによって、シード層28Aの表面に対する抑制剤の吸着が促進され、シード溶解が低減される。これによって、配線溝26内の空隙発生を抑制できる。また、シリコン基板1をめっき液に浸漬させた後、導電膜28を成長させるときには、シリコン基板1とめっき液の相対速度を30m/分以下にしたので、配線溝26内の抑制剤の吸着が少なくなって、ボトムアップ成長が促進される。これによって、シード溶解が進行するよりも速やかに配線溝26内の導電膜28を埋め込むことができる。これによって、配線溝26の空隙発生を抑制できる。

【0053】

ここで、ステップS3のボトムアップ成長中にシード溶解が発生しない場合には、ステップS2のシリコン基板1の浸漬時のみ相対速度を制御しても良い。また、ステップS3のシリコン基板1の浸漬時のシード溶解を考慮する必要がない場合には、ステップS3のボトムアップ成長時のみ相対速度を制御しても良い。

【0054】

(第2の実施の形態)

第2の実施の形態について図面を参照して説明する。第1の実施の形態と同じ構成要素には同一の符号を付している。また、第1の実施の形態と重複する説明は省略する。

この実施の形態では、シード溶解を防止するために、バイアス電圧を印加しながらシリコン基板1をめっき液に浸漬することを特徴とする。

【0055】

図9に電解めっき工程のシーケンスを示す。横軸は時間の経過を示す。縦軸は上から、基板浸漬率、めっき液とシリコン基板の相対速度、バイアス電圧、めっき膜成長量を示す。第1のステップS1では、回転ユニット32にシリコン基板1を装着する。この段階では、基板浸漬率、相対速度、バイアス電圧、めっき膜成長量は、共にゼロである。

【0056】

続く第2のステップS2では、シリコン基板1をめっき液40に浸漬させる。このとき、基板浸漬率は、徐々に増加する。相対速度は、100m/分以上の第1の速度V1に保持される。バイアス電圧は、めっき成長の際の電圧以下の値であって、シリコン基板1とアノード電極38の間に導電膜28を析出させない程度に調整された電圧を印加する。バイアス電圧の大きさは、導電膜28の成長時より小さい値であって、シリコン基板1の大きさやパターン、めっき装置31によって異なる値が用いられる。この段階でのめっき膜成長量は、ゼロである。基板浸漬率が100%になった後も相対速度は、100m/分以上で保持され、この後、第3のステップS3であるボトムアップ成長段階に移行する。

【0057】

第3のステップS3以降では、基板浸漬率はめっき成長が終了するまで、100%に維持される。相対速度は、30m/分以下の第2の速度V2に維持される。バイアス電圧は、ゼロに設定され、代わりに所定の電流がシリコン基板1に供給される。これによって、めっき膜の成長が開始される。続くステップS4で配線溝26に導電膜28が埋め込まれる。

【0058】

第4のステップS5では、平坦部を含めたシリコン基板1の上方の全面に導電膜28を均一に成長させる。めっき液40を攪拌する観点から、相対速度を増加させる。しかしながら、相対速度は、第4のステップS4から変化させなくても良い。

【0059】

この後、余分な導電膜28をCMP法によって研磨すると、図1Eに示すような半導体装置73が形成される。この実施の形態では、シリコン基板1をめっき液に浸漬させるときにバイアス電圧を印加することで、シード溶解がさらに抑制される。これによって、配線溝26の空隙発生をさらに抑制できる。その他の効果は第1の実施の形態と同様である。

【0060】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができる。

【符号の説明】

【0061】

1 シリコン基板

20 層間絶縁膜

26 配線溝(パターン)

28 導電膜

28A シード層

40 めっき液

V1 第1の速度

V2 第2の速度

【特許請求の範囲】

【請求項1】

基板の上方に絶縁膜を形成する工程と、

前記絶縁膜に溝を形成する工程と、

前記溝の内壁に導電性のシード層を形成する工程と、

金属塩を含む電解めっき液と前記基板の外周部分の相対速度が100m/分以上となる回転速度で回転させながら、前記基板を電解めっき液に浸漬させる工程と、

電解めっき液中に浸漬した前記基板に通電して前記溝の内部に導電膜を成長させる工程と、

を含む半導体装置の製造方法。

【請求項2】

電解めっき液と前記基板の外周部分の相対速度が30m/分以下となる回転速度で前記基板を回転させながら、電解めっき液中に浸漬した前記基板に通電して前記溝の内部に導電膜を成長させる請求項1に記載の半導体装置の製造方法。

【請求項3】

前記基板を電解めっき液に浸漬させる工程は、前記溝の内部に導電膜を成長させるときに前記基板に印加する電圧より低い電圧を前記基板に印加する請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項4】

基板の上方に絶縁膜を形成する工程と、

前記絶縁膜に溝を形成する工程と、

前記溝の内壁に導電性のシード層を形成する工程と、

金属塩を含む電解めっき液と前記基板の外周部分の相対速度が第1の相対速度となる回転速度で回転させながら、前記基板を電解めっき液に浸漬させる工程と、

電解めっき液と前記基板の外周部分の相対速度を、前記第1の相対速度より遅い第2の相対速度で回転させながら、電解めっき液に浸漬させた前記基板に通電して前記溝の内部に導電膜を成長させる工程と、

を含む半導体装置の製造方法。

【請求項1】

基板の上方に絶縁膜を形成する工程と、

前記絶縁膜に溝を形成する工程と、

前記溝の内壁に導電性のシード層を形成する工程と、

金属塩を含む電解めっき液と前記基板の外周部分の相対速度が100m/分以上となる回転速度で回転させながら、前記基板を電解めっき液に浸漬させる工程と、

電解めっき液中に浸漬した前記基板に通電して前記溝の内部に導電膜を成長させる工程と、

を含む半導体装置の製造方法。

【請求項2】

電解めっき液と前記基板の外周部分の相対速度が30m/分以下となる回転速度で前記基板を回転させながら、電解めっき液中に浸漬した前記基板に通電して前記溝の内部に導電膜を成長させる請求項1に記載の半導体装置の製造方法。

【請求項3】

前記基板を電解めっき液に浸漬させる工程は、前記溝の内部に導電膜を成長させるときに前記基板に印加する電圧より低い電圧を前記基板に印加する請求項1又は請求項2に記載の半導体装置の製造方法。

【請求項4】

基板の上方に絶縁膜を形成する工程と、

前記絶縁膜に溝を形成する工程と、

前記溝の内壁に導電性のシード層を形成する工程と、

金属塩を含む電解めっき液と前記基板の外周部分の相対速度が第1の相対速度となる回転速度で回転させながら、前記基板を電解めっき液に浸漬させる工程と、

電解めっき液と前記基板の外周部分の相対速度を、前記第1の相対速度より遅い第2の相対速度で回転させながら、電解めっき液に浸漬させた前記基板に通電して前記溝の内部に導電膜を成長させる工程と、

を含む半導体装置の製造方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図5】

【図6】

【図7】

【図8】

【図9】

【図1B】

【図1C】

【図1D】

【図1E】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−253258(P2012−253258A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2011−126072(P2011−126072)

【出願日】平成23年6月6日(2011.6.6)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成23年6月6日(2011.6.6)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]