半導体装置の製造方法

【課題】半導体装置の電気的な接続信頼性を向上させる。

【解決手段】(a)半導体基板の主面上に、主導体膜(下地膜)7Aおよび主導体膜7A上のストッパ絶縁膜(被測定膜)6sを積層する工程、(b)ストッパ絶縁膜6sに開口部8を形成する工程、を含んでいる。また、(c)開口部8に電子ビーム(励起線)EBを照射して、特性X線を放出させる工程、および(d)特性X線を検出し、特性X線の検出結果に基いて開口部8の底部8Bにおけるストッパ絶縁膜6sの有無または膜厚を判定する工程、を含んでいる。また、(d)工程では、特性X線に含まれる複数の元素成分の比率により、ストッパ絶縁膜6sの有無または膜厚を判定する。

【解決手段】(a)半導体基板の主面上に、主導体膜(下地膜)7Aおよび主導体膜7A上のストッパ絶縁膜(被測定膜)6sを積層する工程、(b)ストッパ絶縁膜6sに開口部8を形成する工程、を含んでいる。また、(c)開口部8に電子ビーム(励起線)EBを照射して、特性X線を放出させる工程、および(d)特性X線を検出し、特性X線の検出結果に基いて開口部8の底部8Bにおけるストッパ絶縁膜6sの有無または膜厚を判定する工程、を含んでいる。また、(d)工程では、特性X線に含まれる複数の元素成分の比率により、ストッパ絶縁膜6sの有無または膜厚を判定する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造技術に関し、特に半導体基板上に形成した積層膜に開口部を形成した後、残存膜の有無や膜厚を検査する工程に適用して有効な技術に関するものである。

【背景技術】

【0002】

特開2005−98923号公報(特許文献1)には、被測定膜に電子ビームを照射して、被測定膜から放出される二次電子の量を測定することにより、被測定膜の膜厚を測定する膜厚測定方法が記載されている。

【0003】

特開2008−34475号公報(特許文献2)には、コンタクトホールの底面に残る残存膜の厚さを測定する方法が記載されている。特許文献2では、コンタクトホールに電子線を照射して被検査対象の二次電子画像の電位コントラストを測定することで、残存膜の厚さや抵抗値が推定できるとしている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−98923号公報

【特許文献2】特開2008−34475号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

半導体装置の製造工程には、半導体基板の主面に半導体素子を形成した後、主面上に配線層を積層し、最上層の配線層に形成される複数の電極(パッド)と半導体素子を電気的に接続する工程(以下、配線層積層工程と呼ぶ)が含まれる。この配線層積層工程では、下地膜(半導体基板の主面または下層の配線層の上面)上に絶縁膜を形成し、該絶縁膜に溝(配線溝)や孔(コンタクトホール)などの開口部を形成する。そして、開口部に導体膜を埋め込むことにより上層と下層を電気的に接続する配線層を形成する。このため、半導体装置の電気的接続信頼性を確保する観点から、絶縁膜を確実に貫通する開口部を形成することが重要になる。開口部が絶縁膜を貫通しなければ、電気的接続不良(オープン不良)となるからである。

【0006】

また、開口部は、例えば、絶縁膜上にレジストパターンが形成されたレジスト膜を形成し、このレジスト膜をマスクとしたエッチング処理により形成する。この場合、レジスト膜を除去する工程(アッシング工程)や洗浄工程が必要となるが、これらアッシング工程や洗浄工程において、下層の配線層を保護する観点からは、以下の方法が有効である。すなわち、開口部の底部において、絶縁膜の一部を薄く残存させた状態でアッシング工程や洗浄工程を行い、その後、残存する薄膜(残存膜)を除去する方法が有効である。このような方法を用いるためには、エッチング工程で、残存膜が完全に除去されないように薄く残すことが重要となる。アッシング工程や洗浄工程の前に残存膜が除去されると下層の配線層を保護できなくなる不良(貫通不良)の原因となるからである。つまり、絶縁膜に開口部を形成する際には、その深さを制御する技術が必要となる。

【0007】

そこで、本願発明者は、絶縁膜に形成する開口部の深さを制御する技術の一環として、残存膜の有無、あるいは膜厚を検査する技術について検討を行い、以下の課題を見出した。

【0008】

すなわち、前記特許文献1や前記特許文献2に記載されるように、被測定膜に電子ビームを照射して、被測定膜から放出される二次電子の量、あるいは二次電子画像の電位コントラストを測定する方法の場合、残存膜の測定精度が低下する、あるいは測定不可能になることが判明した。

【0009】

例えば、開口部のアスペクト比が大きい場合、被測定膜や下地膜から放出される二次電子が、配線溝やコンタクトホールの側壁に吸収され易くなる。この結果、二次電子の検出量が低下して測定精度低下や測定不可能化の原因となる。また、二次電子の検出量は、開口部の周辺領域のパターンによるノイズの影響を受け易いため、測定精度低下の原因となる。また例えば、被測定膜とその下地膜が、二次電子放出特性の近い材料(例えば、金属膜同士)で構成されている場合、被測定膜とその下地膜の二次電子放出量の差が明確にならず、測定精度低下や測定不可能化の原因となる。

【0010】

また、残存膜の有無や膜厚の検査に時間を要すれば、製造工程へのフィードバック時間が増大するので、製造効率が低下する。このため、製造効率低下を抑制するためには、残存膜の有無や膜厚の検査時間を短縮する必要がある。

【0011】

本発明は、上記課題に鑑みてなされたものであり、その目的は、半導体装置の電気的な接続信頼性を向上させる技術を提供することにある。また、その他の目的としては、残存膜の有無や膜厚を効率的に検査する技術を提供することにある。

【0012】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0013】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0014】

すなわち、本願発明の一態様である半導体装置の製造方法は、(a)半導体基板の主面上に、下地膜および下地膜上の被測定膜を積層する工程、(b)前記被測定膜に開口部を形成する工程、を含んでいる。また、(c)前記開口部に励起線を照射して、特性X線を放出させる工程、および(d)前記特性X線を検出し、前記特性X線の検出結果に基いて前記開口部の底部における前記被測定膜の有無または膜厚を判定する工程、を含んでいる。また、前記(d)工程では、前記特性X線に含まれる複数の元素成分の比率により、前記被測定膜の有無または膜厚を判定するものである。

【発明の効果】

【0015】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下の通りである。

【0016】

すなわち、本願発明の一態様によれば、半導体装置の電気的な接続信頼性を向上させることができる。また、残存膜の有無や膜厚を効率的に検査することができる。

【図面の簡単な説明】

【0017】

【図1】本発明の一実施の形態である半導体装置の全体構造の一例を示す平面図である。

【図2】図1に示す半導体装置の断面構造の一例を示す拡大断面図である。

【図3】図1および図2に示す半導体装置の製造工程フローの概要を示す説明図である。

【図4】図3の半導体基板準備工程で準備する半導体基板の平面図である。

【図5】図3に示す配線層積層工程のプロセスフローを示す説明図である。

【図6】図2に示す第4層目の配線層の下地層が形成された状態を示す拡大断面図である。

【図7】図6に示す配線層の上面にエッチストッパ膜を成膜した状態を示す拡大断面図である。

【図8】図7に示すエッチストッパ膜上に主絶縁膜を成膜した状態を示す拡大断面図である。

【図9】図8に示す主絶縁膜上にコンタクトホールを形成するためのマスクを配置した状態を示す拡大断面図である。

【図10】図9に示す絶縁膜にコンタクトホールを形成した状態を示す拡大断面図である。

【図11】図10に示すマスクを除去した後、配線溝を形成するためのマスクを配置して配線溝を形成した状態を示す拡大断面図である。

【図12】図11に示すマスクを除去した後、コンタクトホール下層の残存膜を取り除いた状態を示す拡大断面図である。

【図13】図12に示す開口部の底部の残存膜を除去した後、開口部内にバリア導体膜を成膜した状態を示す拡大断面図である。

【図14】図13に示す開口部内に主導体膜を埋め込んだ状態を示す拡大断面図である。

【図15】図14に示す絶縁膜の上面に平坦化処理を施し、絶縁膜の上面上の導体膜を取り除いた状態を示す拡大断面図である。

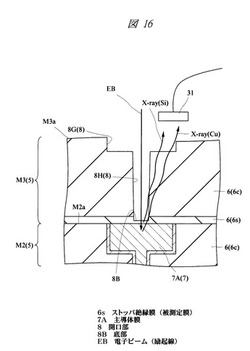

【図16】図5に示す残存膜検査工程を模式的に示す説明図である。

【図17】図16に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Cu/Si)の関係を示す説明図である。

【図18】図16に示す開口部に照射する電子ビームの強度(加速電圧)毎に、残存膜の膜厚と成分比率(Cu/Si)の関係を示す説明図である。

【図19】残存膜検査装置の概要構成を示す説明図である。

【図20】図5に示す残存膜検査工程において、残存膜を検査する開口部の位置の例を示す平面図である。

【図21】図20のA部の拡大平面図である。

【図22】図3に示す配線層積層工程のプロセスフローを示す説明図である。

【図23】図22に示すコンタクトホール貫通工程が完了した状態を示す拡大断面図である。

【図24】図23のB部において、残存膜検査工程を行った状態を模式的に示す説明図である。

【図25】図24に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Co/Si)の関係を示す説明図である。

【図26】図16に示す残存膜検査工程の変形例を模式的に示す説明図である。

【図27】図26に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Ti/Al)の関係を示す説明図である。

【図28】第1の比較例である残存膜検査工程を模式的に示す説明図である。

【図29】第2の比較例である残存膜検査工程を模式的に示す説明図である。

【発明を実施するための形態】

【0018】

(本願における記載形式の説明)

本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクション等に分けて記載するが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、記載の前後を問わず、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しの説明を省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。また、実施の形態の各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。また、添付図面においては、却って、煩雑になる場合または空隙との区別が明確である場合には、断面であってもハッチング等を省略する場合がある。これに関連して、説明等から明らかである場合等には、平面的に閉じた孔であっても、背景の輪郭線を省略する場合がある。更に、断面でなくとも、空隙でないことを明示するため、あるいは領域の境界を明示するために、ハッチングやドットパターンを付すことがある。

【0019】

<半導体装置の概要>

図1は、本実施の形態の半導体装置の全体構造の一例を示す平面図、図2は図1に示す半導体装置の断面構造の一例を示す拡大断面図である。図1に示すように、本実施の形態の半導体装置(半導体チップ)1は、四角形の平面形状を成す表面1aを有している。表面1aは、例えば、窒化シリコン膜、シリコン酸化膜、または窒化シリコン膜とシリコン酸化膜との積層膜で構成される、保護膜(保護絶縁膜)であるパッシベーション膜(保護膜、絶縁膜、保護絶縁膜)FPに覆われている。また、表面1a側には、表面1aの辺に沿って、例えば、アルミニウムで構成される複数のパッド(電極、電極パッド、ボンディングパッド)PDが形成されている。複数のパッドPDのそれぞれは、パッシベーション膜FPに形成された複数の開口部において、パッシベーション膜FPから露出している。この複数のパッドPDは、それぞれ半導体装置1の外部端子となっている。

【0020】

また、図2に示すように、半導体基板2の主面2aに複数の半導体素子Q1が形成されている。図2に示す半導体素子Q1は、例えば、MISFET(Metal Insulator Semiconductor Field Effect Transistor)である。半導体素子Q1のそれぞれは、主面2a上に形成されるゲート電極3、および主面2aにおいてゲート電極3の両隣に形成されるソース領域またはドレイン領域(以下、ソース、ドレイン領域4と記載する)を有している。また、半導体基板2の主面2a上には、複数の配線層5(図2に示す、配線層PM、M1、M2、M3、MX、MT)が積層されている。各配線層は、複数のコンタクトホール(孔、開口部)や配線溝(溝、開口部)が形成された絶縁膜(層間絶縁膜)6を有している。また、複数のコンタクトホールや配線溝には、導体膜(配線)7が埋め込まれ、この導体膜7を介して、下層の配線層5(または半導体素子Q1の電極)と上層の配線層5がそれぞれ電気的に接続されている。また、最上層の配線層MTには、配線(最上層配線)7tおよび複数のパッドPD(図1参照)が形成されている。複数のパッドPDは、配線層MTに形成される配線7tと接続され、下層に形成された複数の配線層5(詳しくは各配線層5の導体膜7)を介して半導体素子Q1と電気的に接続されている。

【0021】

本実施の形態では、各配線層5は、主成分にシリコンを含む絶縁膜6、金属膜からなる導体膜7を有しているが、絶縁膜6や導体膜7は、形成される配線層5毎に異なる成膜方法あるいは含有成分が異なる材料を用いることができる。例えば、本実施の形態では、最下層に配置され、各半導体素子Q1に当接させるコンタクト層となる配線層PMは、絶縁膜6aとしてCVD(Chemical Vapor Deposition)法により形成される酸化シリコン(SiO2)膜を形成している。詳しくは、オゾン(O3)およびTEOS(Tetra-Ethyl-Ortho-Silicate)を用いた熱CVDによる酸化シリコン膜であるオゾンTEOS膜と、TEOSを用いたプラズマCVDによる酸化シリコン膜であるプラズマTEOS膜の積層膜となっている。また、配線層PMのプラグ(コンタクトプラグ、導体膜)7aは、タングステン(W)を主体とする導体膜で構成される。詳しくは、例えば、チタン膜および窒化チタン膜を順次成膜したバリア導体膜と、タングステン膜の積層膜となっている。また、配線層PM上の配線層M1を構成する絶縁膜6bは、例えばプラズマCVDによる酸化シリコン膜で構成され、さらに上層の配線層M2、M3の絶縁膜6cは、炭素(C)がドープされた酸化シリコン膜(SiOC膜)となっている。また、さらに上層の配線層MXには、例えば、FSG(Fluorosilicate Glass)から成る絶縁膜6d、最上層の配線層MTには、USG(Undoped Silicate Glass)から成る絶縁膜6tが形成されている。また、配線層M2、M3、MXのプラグまたは配線である導体膜7としては、例えば、銅(Cu)を主体とする金属から成る導体膜7bが形成されている。詳しくは、導体膜7bは、例えば、タンタル(Ta)膜、窒化タンタル(TaN)膜あるいはこれらの積層膜などから成るバリア導体膜上に、銅または銅合金からなる主導体膜の積層膜で構成される。また、最上層の配線層MTとその下層の配線層MXを接続するプラグである導体膜7cは、例えば、タングステンから成り、最上層に形成される配線7tは例えばアルミニウムで構成される。また、各配線層5の界面には、開口部をエッチング法により形成する際のストッパ絶縁膜(エッチストッパ膜)として、例えば、炭素(C)がドープされた窒化シリコン膜(SiCN膜)が、主絶縁膜である絶縁膜6よりも薄く形成されている。

【0022】

<半導体装置の製造方法の概要>

次に、図1および図2に示す半導体装置の製造方法の概要について説明する。図3は、図1および図2に示す半導体装置の製造工程フローの概要を示す説明図である。また、図4は図3の半導体基板準備工程で準備する半導体基板の平面図である。図1および図2に示す半導体装置の製造方法の一例について図3を用いて簡単に説明すると、例えば、以下のように製造される。

【0023】

まず、半導体基板準備工程で、図4に示すウエハ(半導体基板)WHを準備する。ウエハWHは、図4に示すように、平面略円形の平板であって、例えば平面視において四角形を成す複数のチップ領域(デバイス領域)10aに区画されている。また複数のチップ領域10aの間には、スクライブ領域(ダイシング領域)10bが配置されている。

【0024】

半導体基板準備工程の後、半導体素子形成工程で、ウエハWHの主面2a(図2参照)にトランジスタやダイオードなどである複数の半導体素子Q1(図2参照)を形成する。本工程では、例えば、図2に示すように、ウエハWH(図4参照)の主面2aに素子分離領域11およびウェル領域12を形成する。素子分離領域11は、例えば、シリコン酸化膜などからなり、例えばSTI(Shallow Trench Isolation)法またはLOCOS(Local Oxidization of Silicon)法などにより形成される。また、ウェル領域12は、p型またはn型の導電型の不純物を含む半導体領域であって、半導体素子Q1を形成する領域に、不純物をイオン注入することにより形成される。例えば、nチャネル型の半導体素子Q1が形成される領域には、例えばホウ素(B)などのp型の不純物がイオン注入されることによりp型のウェル領域(p型ウェル領域)12が形成される。また、pチャネル型の半導体素子Q1が形成される領域には、リン(P)または砒素(As)などのn型の不純物がイオン注入されることにより、n型のウェル領域(n型ウェル領域)12が形成される。その後、主面2aのウェル領域12にゲート電極3およびソース、ドレイン領域4を形成し、半導体素子Q1を形成する。ゲート電極3は、例えば、2nm〜4nm程度の薄い酸化シリコン膜から成るゲート酸化膜上に、ポリシリコン膜(例えば、不純物を含む多結晶シリコン膜)を積層することで形成される。また、ゲート電極3の側面には、サイドウォール絶縁膜が形成される。また、ソース、ドレイン領域4は、ゲート電極3の両隣に不純物がイオン注入されることにより形成される。例えば、nチャネル型の半導体素子Q1が形成されるp型のウェル領域12には、リン(P)または砒素(As)などのn型の不純物がイオン注入され、n型半導体領域であるソース、ドレイン領域4が形成される。また、pチャネル型の半導体素子Q1が形成される領域には、ホウ素(B)などのp型の不純物がイオン注入され、p型半導体領域であるソース、ドレイン領域4が形成される。また、ゲート電極3およびソース、ドレイン領域4の表面には、金属シリサイド膜が積層される。この金属シリサイド膜は、ゲート電極3およびソース、ドレイン領域4の表面に、例えばコバルト(Co)膜やニッケル(Ni)膜などの金属膜を形成し、熱処理(アニール処理)を施すことで、金属膜とシリコンを反応させてシリサイド化することにより形成される。

【0025】

半導体素子形成工程の後、コンタクト層形成工程で、図2に示す各半導体素子Q1に当接させるコンタクト層となる配線層PMを形成する。その後、配線層積層工程として、主面2a上(配線層PM上)に複数の配線層5を積層する。このコンタクト層形成工程および配線層積層工程の詳細は後述するが、概要を説明すると以下である。下地層(半導体基板2または下層の配線層5)上に絶縁膜6を形成した後、絶縁膜6に開口部を形成する。その後、開口部内に導体膜7を埋め込んでプラグまたは配線を形成する。そして、配線層5の上面に例えばCMP(Chemical Mechanical Polishing)法による平坦化処理を施し、上面を平坦化する。これにより、導体膜7が絶縁膜6の下面および上面において露出した配線層5が形成される。この工程を繰り返し行うことで、複数の配線層5を積層することができる。なお、最上層の配線7tは、例えば、平坦化処理が施された最上層の絶縁膜6t上に、例えばスパッタ法によりアルミニウムから成る金属膜を成膜し、これをエッチングによりパターニングして形成される。この時、配線7tに接続される複数のパッドPD(図1参照)も形成される。

【0026】

配線層積層工程の後、保護膜形成工程で、最上層の配線7t上にパッシベーション膜(保護膜、絶縁膜、保護絶縁膜)FPを形成(成膜)する。本工程では、例えば、窒化シリコン膜、シリコン酸化膜、または窒化シリコン膜とシリコン酸化膜との積層膜をCVD法により成膜し、配線7tおよびこれに接続される複数のパッドPD(図1参照)を被覆する。その後、パッド開口部形成工程で、パッシベーション膜FPに複数の開口部を形成し、開口部において複数のパッドPD(図1参照)をパッシベーション膜FPから露出させる。その後、電気的検査工程などの処理を施した後、個片化工程として、ウエハWH(図4参照)をチップ領域10a(図4参照)毎に分割し、個片化する。本工程では、例えばダイシングブレードと呼ばれる切断刃を図4に示すウエハWHのスクライブ領域10bに沿って走らせて、ウエハWHを分割する。これにより、1枚のウエハWHから複数の半導体装置1(図1参照)を取得することができる。

【0027】

<配線層積層工程の詳細>

前記したコンタクト層形成工程および配線層積層工程では、絶縁膜6にコンタクトホールや配線溝などの開口部を形成し、該開口部に導体膜7を埋め込むことにより、プラグまたは配線を形成する。以下では、開口部を形成した後、開口部内に導体を埋め込む工程の説明として、図2に示す配線層M3を形成する工程を例に取り上げて詳細に説明する。図5は、図3に示す配線層積層工程のプロセスフローを示す説明図である。また、図6は、図2に示す第4層目の配線層の下地層が形成された状態を示す拡大断面図である。また、図7は図6に示す配線層の上面にエッチストッパ膜を成膜した状態を示す拡大断面図、図8は、図7に示すエッチストッパ膜上に主絶縁膜を成膜した状態を示す拡大断面図である。また、図9は、図8に示す主絶縁膜上にコンタクトホールを形成するためのマスクを配置した状態を示す拡大断面図、図10は、図9に示す絶縁膜にコンタクトホールを形成した状態を示す拡大断面図である。また、図11は、図10に示すマスクを除去した後、配線溝を形成するためのマスクを配置して配線溝を形成した状態を示す拡大断面図、図12は、図11に示すマスクを除去した後、コンタクトホール下層の残存膜を取り除いた状態を示す拡大断面図である。また、図13は、図12に示す開口部の底部の残存膜を除去した後、開口部内にバリア導体膜を成膜した状態を示す拡大断面図、図14は、図13に示す開口部内に主導体膜を埋め込んだ状態を示す拡大断面図である。図15は、図14に示す絶縁膜の上面に平坦化処理を施し、絶縁膜の上面上の導体膜を取り除いた状態を示す拡大断面図である。

【0028】

図3に示す配線層積層工程では、まず、下地層準備工程として、配線層の下地となる層を形成する。図6は、図2に示す配線層M3を形成する工程を説明する図なので、配線層M2がこの下地層に相当する。配線層M2には、絶縁膜6および絶縁膜6を貫通する開口部8が形成され、開口部8内に導体膜(下地膜)7が埋め込まれている。また、配線層M2の上面M2aは平坦化処理が施され、導体膜7が上面M2aの開口部8において、絶縁膜6から露出している。次に、ストッパ膜形成工程として、図7に示すように、ストッパ絶縁膜(被測定膜)6sを成膜(形成)する。ストッパ絶縁膜6sは、例えば炭素(C)がドープされた炭化窒化シリコン膜(SiCN膜)であって、例えば、CVD法により、例えば30nm〜50nm程度の厚さで形成される。本工程により、配線層M2の上面M2aにおいて、絶縁膜6cから露出する導体膜7(主導体膜(下地膜)7Aおよびバリア導体膜7B)は、ストッパ絶縁膜6sにより被覆される。

【0029】

次に主絶縁膜形成工程として、図8に示すようにストッパ絶縁膜6s上に、主層間絶縁膜である絶縁膜6cを成膜(形成、積層)する。絶縁膜6cは、例えば、炭素(C)がドープされた酸化炭化シリコン膜(SiOC膜)であって、例えばCVD法により、ストッパ絶縁膜6sよりも厚く、例えば300nm〜500nmの厚さで形成される。次に、第1マスク配置工程として、図9に示すように、絶縁膜6cの上面M3a上にレジスト膜21を配置する。レジスト膜21は、主絶縁膜である絶縁膜6cにコンタクトホール8H(図10参照)を形成するためのマスクであって、マスクパターンとして、コンタクトホール8Hを形成する位置にレジスト膜21を厚さ方向に貫通する貫通孔21aが形成される。

【0030】

次に、コンタクトホール形成工程として、図10に示すように、レジスト膜21をマスクとして絶縁膜6cの上面M3a側から下地層である配線層M2に向かって絶縁膜6cの一部を取り除き、コンタクトホール(開口部、孔)8Hを形成する。絶縁膜6cの一部を取り除く方法は、例えば、レジスト膜21をエッチングマスクとしてエッチング処理を行い、コンタクトホール8Hを形成する。エッチング方式は、ドライエッチング方式、ウェットエッチング方式、またはこれらを組み合わせて行う方式を用いることができる。配線層M3は、コンタクトホール8Hに接続される配線溝も形成するので、本工程の終了段階では、コンタクトホール8Hは図10に示すように絶縁膜6cを貫通せず、コンタクトホール8Hの底部8Bは絶縁膜6cの途中に配置されている。次に、第1マスク除去工程(アッシング工程)として、図10に示すレジスト膜21を取り除く。この時、下地層である配線層M2の導体膜7は、ストッパ絶縁膜6sおよびその上層の絶縁膜6cに覆われているので、アッシング処理中の導体膜7の汚染を抑制することができる。また、アッシング処理を行った後、レジスト膜21の残渣を取り除く洗浄工程を行う場合もあるが、この場合にも、配線層M2の導体膜7は、ストッパ絶縁膜6sおよびその上層の絶縁膜6cに覆われているので、洗浄処理中の導体膜7の汚染を抑制することができる。

【0031】

次に、第2マスク配置工程として、図11に示すように、絶縁膜6cの上面M3a上にレジスト膜22を配置する。レジスト膜22は、主絶縁膜である絶縁膜6cに配線溝(開口部)8Gを形成するためのマスクであって、マスクパターンとして、配線溝8Gを形成する位置にレジスト膜22を厚さ方向に貫通する開口部22aが形成される。レジスト膜22は配線溝8Gを形成するためのマスクであり、開口部22aは、図10に示すレジスト膜21の貫通孔21aよりも幅広に形成されている。次に、配線溝形成工程として、レジスト膜22をマスクとして絶縁膜6cの上面M3a側から下地層である配線層M2に向かって絶縁膜6cおよびストッパ絶縁膜6sの一部を取り除き、配線溝(開口部、溝)8Gを形成する。絶縁膜6cおよびストッパ絶縁膜6sの一部を取り除く方法は、コンタクトホール形成工程と同様に、例えば、レジスト膜22をエッチングマスクとしてエッチング処理を行い、配線溝8Gを形成する。この時、コンタクトホール8Hも、レジスト膜22の開口部22aにおいて、レジスト膜22から露出しているため、図10に示すコンタクトホール8Hの底部8Bの下層の絶縁膜6もさらに取り除かれる。このため、コンタクトホール8Hはさらに下方に向かって延び、絶縁膜6cを厚さ方向に貫通する。なお、本実施の形態では絶縁膜6cをシリコン酸化膜系の膜、ストッパ絶縁膜6sをシリコン窒化膜系の膜としている。このため、本工程で、シリコン酸化膜用のエッチング材(ドライエッチング方式の場合はエッチングガス、ウェットエッチング方式の場合はエッチング液)を用いることにより、ストッパ絶縁膜6sがエッチングにより貫通してしまうことを抑制できる。しかし、シリコン酸化膜用のエッチング材を用いた場合であっても、ストッパ絶縁膜6sの一部はエッチングにより取り除かれる。

【0032】

ここで、本工程では、図11に示すように、ストッパ絶縁膜6sを貫通させず、コンタクトホール8Hの底部8Bの下層において、ストッパ絶縁膜6sの一部を残存膜として残している。これにより、図5に示す第2マスク除去工程において、アッシング処理や洗浄処理を行う際に、下地層である配線層M2の導体膜7が汚染されることを抑制することができる。また、図5に示すコンタクトホール貫通工程で、確実にストッパ絶縁膜6sの残存膜を取り除く観点からは、残存膜の厚さは薄くすることが好ましい。例えば、本実施の形態では、ストッパ絶縁膜6sの残存膜が数nm〜20nm程度の範囲に収まるように制御している。残存膜の厚さの制御は、例えばエッチング処理の処理時間により制御することができる。しかし、本実施の形態のように、ストッパ絶縁膜6sの残存膜が数nm〜20nm程度の範囲に収まるように制御する場合には、エッチング処理の処理時間のみの制御では、ストッパ絶縁膜6sが貫通してしまうという問題が発生する。そこで、本実施の形態では、図5に示すように配線溝形成工程の後に残存膜検査工程を行い、残存膜の有無、あるいは残存膜の膜厚を検査している。この残存膜検査工程の結果を製造工程にフィードバックすることで、ストッパ絶縁膜6sの残存膜の厚さを高精度で制御することができる。例えば、ストッパ絶縁膜6sが貫通してしまう貫通不良や残存膜の膜厚が許容範囲を超えてしまう不良が発生した場合には、残存膜検査工程によって、不良の発生を検出することができる。このため、不良が検出された時点で製造を停止すれば、不良品が大量に生産されてしまうロスを防止することができる。また、製造工程の各条件をチェックして、不良の発生原因を特定すれば、これを反映した条件に修正することができる。ストッパ絶縁膜6sが貫通してしまう貫通不良のみを検出する場合には、残存膜検査工程では、残存膜の有無のみを検出することができれば良いが、残存膜の膜厚が許容範囲を超えてしまう不良までを検出する場合には、残存膜の膜厚を検出することが必要となる。この残存膜検査工程での具体的な検査方法は、後述する。

【0033】

次に、第2マスク除去工程(アッシング工程)として、図11に示すレジスト膜22を取り除く。この時、下地層である配線層M2の導体膜7は、コンタクトホール8Hの底部8Bの下層に配置されるストッパ絶縁膜6sの残存膜に覆われているので、アッシング処理中の導体膜7の汚染を抑制することができる。また、アッシング処理を行った後、レジスト膜22の残渣を取り除く洗浄工程を行う場合もあるが、この場合にも、配線層M2の導体膜7は、コンタクトホール8Hの底部8Bの下層に配置されるストッパ絶縁膜6sの残存膜に覆われているので、洗浄処理中の導体膜7の汚染を抑制することができる。

【0034】

次に、コンタクトホール貫通工程として、図12に示すように、コンタクトホール8Hの下層のストッパ絶縁膜6sの残存膜を取り除く。本工程では、ストッパ絶縁膜6sの残存膜を取り除くことで、コンタクトホール8Hがストッパ絶縁膜6sを厚さ方向に貫通する。このため、コンタクトホール8Hの底部8Bにおいて、下地層である配線層M2の導体膜7がストッパ絶縁膜6sから露出する。ストッパ絶縁膜6sの残存膜を取り除く方法としては、エッチング処理により取り除くことができる。本工程では、エッチングマスクは形成していないが、シリコン窒化膜用のエッチング材を用いることで、ストッパ絶縁膜6sを選択的(優先的)に取り除くことができる。また、前記した配線溝形成工程で、ストッパ絶縁膜6sの残存膜の厚さを、例えば数nm〜20nm程度とすることにより、エッチング処理の処理時間を短くすることができる。

【0035】

次に導体膜形成工程として、図12に示すコンタクトホール8Hおよび配線溝8G内に導体膜を形成する。まず、図13に示すように、主導体膜の成分が絶縁膜6c中に拡散することを防止ないしは抑制するバリア導体膜7Bをコンタクトホール8Hおよび配線溝8G内に成膜(形成)する。バリア導体膜7Bは、例えば、タンタル(Ta)膜、窒化タンタル(TaN)膜あるいはこれらの積層膜などから成り、例えば10nm程度の膜厚で成膜される。バリア導体膜7Bは、例えば、スパッタリング法やCVD法などによって形成する。本工程では、絶縁膜6cの上面M3a上にマスクを配置せずに行うので、バリア導体膜7Bは、コンタクトホール8Hおよび配線溝8Gの内壁面および絶縁膜6cの上面M3a上に成膜される。次に、図14に示すようにバリア導体膜7B上に、主導体膜7Aを成膜(形成)し、コンタクトホール8Hおよび配線溝8Gに埋め込む。主導体膜7Aは、例えば銅(Cu)から成り、例えばスパッタリング法または電解めっき法などを用いて形成される。また、主導体膜7Aは、銅を主成分とする導体膜、例えば銅または銅合金(Cuを主成分とし、例えばMg、Ag、Pd、Ti、Ta、Al、Nb、ZrまたはZnなどを含む)により形成することができる。また、バリア導体膜7B上に、主導体膜よりも薄い銅(または銅合金)などからなるシード膜をスパッタリング法などによって形成し、そのシード膜上にシード膜よりも厚い銅(または銅合金)などからなる主導体膜7Aをめっき法などによって形成することができる。

【0036】

次に、平坦化工程として、絶縁膜6cの上面M3a側に平坦化処理を施す。バリア導体膜7Bおよび主導体膜7Aはコンタクトホール8Hおよび配線溝8Gから成る開口部8の形状に倣って形成されるため、その表面は図14に示すように凹凸面となっている。このため、例えばCMP法(メタルCMP法)により平坦化し、余分なバリア導体膜7Bおよび主導体膜7Aを取り除く。また、この平坦化工程において絶縁膜6cの上面M3a上に形成されたバリア導体膜7Bおよび主導体膜7Aが取り除かれる。

【0037】

そして、平坦化工程が完了すると、図15に示す配線層M3が形成される。配線層M3には、絶縁膜6および絶縁膜6を貫通する開口部8が形成され、開口部8内に導体膜7が埋め込まれている。詳しくは、導体膜7は、コンタクトホール8Hに埋め込まれ、下層の配線層M2の主導体膜7Aと接触(接合)するプラグ7Pと、プラグ7P上に配置されプラグ7Pと一体に形成される配線(埋め込み配線)7Lから成る。また、配線層M3の上面M3aは平坦化処理が施され、導体膜7が上面M3aの開口部8において、絶縁膜6から露出している。これにより配線層M3は、さらに上層に積層される配線層5の下地層となる。つまり、図3に示す配線層積層工程では、図5に示すストッパ膜形成工程から平坦化工程までを繰り返し行うことで、複数の配線層5を積層する。

【0038】

なお、本実施の形態では、絶縁膜6にコンタクトホール8Hおよびこれに接続される配線溝8Gを形成し、この開口部8内に導体膜7を埋め込む、所謂、デュアルダマシン方式により形成する配線層5について説明した。しかし、配線層5の形成方法は上記に限定されない。例えば、配線溝8Gを形成せず、コンタクトホール8H内に導体膜7を埋め込み、平坦化処理を行った後で、プラグ7P上に配線7Lを形成する方式に適用することができる。また例えば、配線溝8Gを形成する前に、コンタクトホール8H内に導体膜7を埋め込み、平坦化処理を行った後で、さらに絶縁膜6を積層し、積層した絶縁膜6に配線溝8Gおよび配線溝8Gに埋め込まれる配線7Lを形成する方式に適用することができる。

【0039】

<残存膜検査工程の詳細>

次に、図5に示す残存膜検査工程の詳細について説明する。本セクションでは、まず、本願発明者が検討した比較例について説明した後、本実施の形態の残存膜検査工程の内容について説明する。図28は、本実施の形態に対する第1の比較例である残存膜検査工程を模式的に示す説明図、図29は、本実施の形態に対する第2の比較例である残存膜検査工程を模式的に示す説明図である。

【0040】

図5に示す残存膜検査工程では、図11に示すようにコンタクトホール8Hの底部8Bの下層における数nm〜20nm程度の薄膜の有無あるいは膜厚を測定する。このような残存膜検査を効率的に行う観点から、非接触方式の検査を行うことが好ましい。そこで、本願発明者は、非接触方式の検査方法として、図28に示すように光学干渉を利用した膜厚測定方法について検討した。光学干渉を利用した膜厚測定方法では、まず、図28に示すように下地膜100と下地膜100上に積層された被測定膜101を備える被検査対象物に対して照射光L1を照射する。照射光L1の一部は、被測定膜101の表面で反射され、反射光L2が発生する。また、照射光L1の別の一部は、被測定膜101を透過して下地膜100の表面(すなわち、被測定膜の裏面)で反射され、反射光L3が発生する。この反射光L2と反射光L3には、被測定膜の膜厚に対応して位相差が生じる。そこで、図28に示す膜厚測定方法は、被測定膜101上に位相検出器102を配置し、位相検出器102により反射光L2、L3の位相差を検出して、該位相差から被測定膜101の膜厚を算出するものである。ところが、このような光学干渉を利用した膜厚測定方法を適用する場合には、照射光L1を照射する領域が数十〜数百μm2程度の平坦面となっている必要がある。一方、図11に示すコンタクトホール8Hの底部8Bの平面寸法は、例えば、1μm2よりも小さい微細なパターンである。このため、図28に示す光学干渉を利用した膜厚測定方法は、図5に示す残存膜検査工程としては適用することができない。

【0041】

次に、本願発明者は、別の非接触方式の検査方法として、図29に示すように被検査対象物に電子ビームEBを照射して、被測定膜から放出される二次電子を検出することにより被測定膜101の有無や膜厚を測定する方法について検討した。図29に示す方法では、被検査対象物に対して被測定膜101側から電子ビームEBを照射する。すると、被測定膜101から電子ビームEBにより励起された二次電子SE1が放出される。また、電子ビームEBの加速電圧を高くして電子ビームEBの強度(エネルギー強度)を高くすると、被測定膜101の下層の下地膜100からも電子ビームEBにより励起された二次電子SE2が放出される。そして被測定膜の上面側に放出された二次電子SE1、SE2を二次電子検出部103で検出する。ここで、被測定膜101を絶縁膜、下地膜100を金属などの導電膜とした場合、二次電子SE2の量は二次電子SE1の量よりも多くなる。このため、電子ビームEBの加速電圧を徐々に上昇させて電子ビームEBの強度を上昇させると、二次電子発生量に変化点が生じる。そして膜厚が既知である評価用の被測定膜101を用いて、二次電子発生量の変化点と電子ビームEBの強度の相関関係を予め調査すれば、この調査結果と比較することで、被測定膜101の膜厚を測定できる。ところが、本願発明者が図29に示す膜厚測定方法についてさらに検討を行った結果、以下の課題を見出した。

【0042】

まず、図11に示すコンタクトホール8Hの底部8Bの下層におけるストッパ絶縁膜6sの残存膜の測定に適用した場合、残存膜の測定精度が低下する、あるいは測定不可能になる。開口部8のアスペクト比が大きい場合、被測定膜101(図29参照)や下地膜100(図29参照)から放出される二次電子SE1、SE2(図29参照)が、配線溝8Gやコンタクトホール8Hの側壁(絶縁膜6c)に吸収され易くなる。この結果、二次電子SE1、SE2の検出量の低下により測定精度低下や測定不可能化の原因となる。また、二次電子SE1、SE2の信号強度を評価する方式では、絶縁膜6によるノイズの影響を受け易い。したがって、このノイズの影響により測定精度が低下し易い。また、開口部8のパターン形状によって二次電子SE1、SE2の信号強度が変化するので、膜厚が既知である評価用の被測定膜101を用いた調査結果との比較が困難である。また、被測定膜101とその下地膜100が、二次電子放出特性の近い材料(例えば、金属膜同士)で構成されている場合、被測定膜101とその下地膜100の二次電子放出量の差が明確にならず、測定精度低下や測定不可能化の原因となる。

【0043】

上記検討結果を踏まえ、本実施の形態の残存膜検査工程について説明する。図16は、図5に示す残存膜検査工程を模式的に示す説明図である。本実施の形態の残存膜検査工程では、まず、開口部8(詳しくはコンタクトホール8Hの底部8B)に向かって電子ビーム(励起線)EBを照射する。開口部8に電子ビームEBを照射すると、被測定膜であるストッパ絶縁膜6sの残存膜からは、前記した第2の比較例で説明した二次電子の他、特性X線(例えば、図16でX−ray(Si)として模式的に示す特性X線)が放出される。また、電子ビームEBの強度を高くすると、下地膜である導体膜7も励起され、導体膜7から特性X線(例えば、図16でX−ray(Cu)として模式的に示す特性X線)が放出される。これらの特性X線は、励起された原子が電子を放出することにより生じた空孔に、電子が遷移する際に発生するX線である。このため、特性X線は、単一のエネルギー(線スペクトル)を有し、その値は電子を放出した元素毎に固有の値となっている(固有X線とも呼ばれる)。例えば、ストッパ絶縁膜6sからは、シリコン(Si)元素、酸素(O)元素、炭素(C)元素および窒素(N)元素の特性X線がそれぞれ放出される。また、例えば銅(Cu)からなる主導体膜7Aからは、銅(Cu)元素の特性X線が放出される。なお、主導体膜7Aからは、主導体膜7A中に拡散したシリコン成分からシリコン(Si)元素の特性X線も放出される場合もある。本実施の形態では、この特性X線を検出し、残存膜の有無あるいは残存膜の膜厚を判定(評価)する。詳しくは、配線層M3の上面M3a側に配置されるX線検出部31により、被測定膜および下地膜から放出される特性X線に含まれる複数の元素成分を検出する。例えば、ストッパ絶縁膜6sからは、主たる元素成分としてシリコン(Si)元素成分が検出され、主導体膜7Aからは、主たる元素成分として銅(Cu)元素成分が検出される。そして、これら複数種類の元素成分の比率により、被測定膜の有無または膜厚を判定(評価)する。例えば、銅(Cu)元素成分とシリコン(Si)元素成分を比較して、その成分比率(銅(Cu)元素成分/シリコン(Si)元素成分)により、ストッパ絶縁膜6sの残存膜の有無または膜厚を判定(評価)する。以下、評価方法について説明する。

【0044】

図17は、図16に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Cu/Si)の関係を示す説明図である。また、図18は、図16に示す開口部に照射する電子ビームの強度(加速電圧)毎に、残存膜の膜厚と成分比率(Cu/Si)の関係を示す説明図である。なお、図17および図18では、図16に示すストッパ絶縁膜6sの膜厚が既知の複数種類のサンプルを作成し、この複数種類のサンプルに対して電子ビームEB(図16参照)を照射して特性X線の成分比率と励起線の強度の相関を測定した結果を示している。分光分析の方式は、エネルギー分散型分光分析法と、波長分散型分光分析法に大別される。エネルギー分散型分光分析法では、EDS(Energy Dispersive X-ray Spectroscopy)と呼ばれるエネルギー分散型分光器を用いて分析を行う。また、波長分散型分光分析法では、WDS(Wavelength Dispersive X-ray Spectrometry)と呼ばれる波長分散型分光器を用いて分析を行う。波長分散型分光分析法は、エネルギー分散型分光分析法よりも分解能を高くし易いという利点があるが、検査装置の構造を単純化する観点からは、エネルギー分散型分光分析法の方が好ましい。

【0045】

まず、特性X線の放出量は、励起線である電子ビームEB(図16参照)の強度により変化するので、適正な電子ビームEB(図16参照)強度(電子の加速電圧)について検討した結果を図17に示す。成分比率により残存膜の有無を判定するためには、残存膜の有無によって、成分比率の測定結果が大きく異なるような励起線強度が好ましい。ここで、図17に示すように、電子ビームEB(図16参照)の加速電圧が2.5V以上4.0V以下の範囲では、残存膜が無い(膜厚=0.0nm)場合と残存膜が有る(膜厚=17.8nm)場合では、成分比率(Cu/Si)に10%以上の差がある。そして電子ビームEB(図16参照)の加速電圧を、さらに上昇させると、残存膜の有無による成分比率(Cu/Si)の差は小さくなる。一方、電子ビームEB(図16参照)の加速電圧が2.5Vよりも小さくなると、残存膜が有る(膜厚=17.8nm)場合において、下地層から放出される特性X線である銅(Cu)成分が小さくなる。これは、電子ビームEB(図16参照)の強度が小さくなることにより、下地層である導体膜7が励起され難くなるからである。したがって、図17に示す結果から、電子ビームEB(図16参照)の加速電圧が2.5V以上4.0V以下とすることが特に好ましい。

【0046】

次に、残存膜の膜厚と成分比率(Cu/Si)の関係について検討した結果を図18に示す。図18では、電子ビームEB(図16参照)の加速電圧がそれぞれ、2.5kVの場合、3.0kVの場合および4.0kVの場合について示している。図18に示すように、残存膜の膜厚が、0.0nm〜約18.0nmの範囲において、残存膜の膜厚と成分比率(Cu/Si)は、反比例の関係があることが判る。すなわち、残存膜の膜厚の上昇に伴って、成分比率(Cu/Si)は減少する。したがって、例えば2.5kV〜4.0kVのうちの任意の加速電圧で加速した電子ビームEB(図16参照)を図16に示す開口部8に照射し、検出された特性X線の成分比率と図18に示すように既知の膜厚の残存膜に励起線を照射して得られた相関関係データを比較することで、残存膜の膜厚を算出(判定)することができる。つまり、検出された特性X線に含まれる複数種類の元素成分の比率により、残存膜の有無または膜厚を判定(評価)することができる。

【0047】

次に、本実施の形態の残存膜検査工程に用いる残存膜検査装置の構成について説明する。図19は残存膜検査装置の概要構成を示す説明図である。図19に示す検査装置(残存膜検査装置)30は、励起線である電子ビームEBを照射する励起線照射部32、および被検査対象であるウエハWHを固定する基板固定部33を有している。また、検査装置30はウエハWHから放出された特性X線を検出する検出部31、および検出された信号データから残存膜の有無あるいは膜厚を判定する判定部34を有している。また、検査装置30は、励起線照射部32、基板固定部33、検出部31、および判定部34の動作(機械的動作または電気的動作)を制御する制御部35を有している。

【0048】

励起線照射部32は、例えば励起線である電子ビームEBを発生させる電子銃、およびウエハWHの検査対象となる開口部8(図16参照)の底部8B(図16参照)に向かって電子ビームEBを収束させて照射するレンズなどを備え、ウエハWHの主面上(検査対象である開口部上)に配置される。また、励起線照射部32は制御部35と電気的に接続され、電子銃から発射された電子ビームEBは、制御部35からの制御信号によって所定の加速電圧(例えば2.5V〜4.0Vのうちの任意の加速電圧)で加速され、ウエハWHの主面側の開口部8(図16参照)に照射される。また、検出部31は、判定部34および制御部35と電気的に接続される検出器を備え、ウエハWHの主面上(検査対象である開口部上)に配置される。検出部31で検出された複数種類の特性X線の検出信号は、判定部34が備える判定回路34aに伝送される。特性X線の検出信号は、特性X線の元素成分毎に分光され、判定回路34aに伝送される。例えば、エネルギー分散型の分光分析を行う検出部31では、特性X線のエネルギー毎に分光された検出信号が伝送される。また、波長分散型の分光分析を行う検出部31では、特性X線の波長毎に分光された検出信号が伝送される。

【0049】

判定部34の判定回路34aでは、元素成分毎の特性X線の検出信号について処理(統計処理)を行い、被測定膜に含まれる第1の元素成分の検出信号と、下地層に含まれる第2の元素成分の検出信号の比率(成分比率データ)を算出する。また、判定部34は、判定用データを保持するデータ保持部34bを備えている。この判定用データは、例えば、図18を用いて説明したように、既知の膜厚の残存膜に励起線を照射して得られた相関関係データ、あるいは、この相関関係データに基いて設定された閾値データである。この判定用データは、データ保持部34bから判定回路34aに伝送され、判定回路34aにおいて、成分比率の測定データと判定用データを比較することにより、残存膜の有無または膜厚を判定(評価)する。

【0050】

このように本実施の形態によれば、被測定膜および下地膜から照射される特性X線を検出することにより、残存膜の有無または膜厚を判定する。特性X線は二次電子よりも開口部8周囲の側壁に吸収され難い。このため、スルーホールなどのアスペクト比が高い開口部8の底部における残存膜を検査する場合であっても、特性X線を検出することができる。また、本実施の形態では、検出した特性X線の絶対値ではなく、特性X線に含まれる複数の元素成分の比率により残存膜の有無または膜厚を判定する。したがって、測定対象となる開口部8の周辺パターンの影響、あるいは、絶縁膜6cからのノイズの影響により、信号強度が変化した場合であっても、測定精度の低下を抑制することができる。また、本実施の形態では、被測定膜が絶縁膜(ストッパ絶縁膜6s)、下地膜が導体膜(主導体膜7A)である場合について説明したが、特性X線を検出する方式で検査可能な被測定膜と下地膜の構成はこれに限定されない。例えば、被測定膜および下地膜の双方が構成成分の異なる絶縁膜あるいは導体膜である場合にも適用することができる。各膜の構成成分が異なれば、絶縁膜同士あるいは導体膜同士であっても異なる成分の特性X線の比率を測定できるからである。

【0051】

なお、図17および図18において、残存膜の膜厚が0.0nmの時にもシリコン(Si)元素成分の特性X線が検出されているが、これは、主導体膜7A(図16参照)中に拡散したシリコン成分からシリコン(Si)元素の特性X線が放出されるためである。しかし、本実施の形態では、特性X線の成分比率により残存膜の有無、あるいは膜厚を判定するので、下地膜からシリコン(Si)元素の特性X線が放出されても、判定精度の低下を抑制することができる。例えば、図18において、残存膜の膜厚が0.0nmの時は、成分比率(Cu/Si)はいずれも80%以上(詳しくは83%以上)である。一方、残存膜の膜厚が12.1nmの時は、成分比率(Cu/Si)はいずれも80%未満である。したがって、例えば成分比率(Cu/Si)が83%未満であることを閾値として管理すれば、開口部8の底部における残存膜の有無を検査することができる。また例えば、開口部8の深度についてウエハ面内でのばらつきを考慮した場合、例えば、成分比率(Cu/Si)が80%未満であることを閾値として管理すれば、ウエハ面内の全ての開口部8において、残存膜が残っていると推定することができる。

【0052】

<残存膜検査工程の好ましい態様>

次に、上記で説明した残存膜検査工程の好ましい態様について説明する。図20は、図5に示す残存膜検査工程において、残存膜を検査する開口部の位置の例を示す平面図である。また、図21は、図20のA部の拡大平面図である。なお、図20に示すウエハWHには、多数の開口部8が形成されているが、検査位置を解り易くしめすため、多数の開口部8のうち、検査対象となる開口部8aを含む一部の開口部8のみ示している。ウエハWHには、各チップ領域10a(図4参照)に、それぞれ多数の開口部8が形成される。残存膜検査工程において、全ての開口部8について検査することもできるが、この場合、検査時間が増大し、製造効率低下の原因となる。そこで、本実施の形態では、複数の開口部8のうちの一部の開口部8aについて検査を行う。ウエハWHに一括して開口部8を形成する場合には、処理時間を管理することにより、複数の開口部8の深度は略同程度に揃えることができる。したがって、図20に示すように、互いに離間した任意の複数箇所(図20では3箇所)の開口部8aで残存膜の有無または膜厚を判定(評価)すれば、電子ビームEB(図16参照)を照射しないその他の開口部8bにおける残存膜の有無も推定することができる。例えば、ウエハWHの面内における開口部8の深度のばらつきを考慮して、例えば、全ての開口部8aにおいて残存膜の膜厚が10nm以上あれば他の開口部8bにおいても残存膜が残っていると推定することができる。この場合、開口部8bについて検査を行わないので、検査時間を大幅に短縮することができる。つまり、残存膜検査工程を効率化することができる。

【0053】

また、本実施の形態の残存膜検査工程は非破壊検査であるが、電子ビームEB(図16参照)を照射することにより、開口部8周辺の電気的特性が損なわれることを防止する観点からは、製品となるチップ領域10a(図4参照)に形成された開口部8b(図20参照)には電子ビームEB(図16参照)を照射しないことが好ましい。このため、本実施の形態では、図21に示すように、チップ領域10aの間に配置されるスクライブ領域10bに、チップ領域10a内と同様のプロセスで検査用の開口部8aを形成し、開口部8aに対して電子ビームEB(図16参照)を照射する。このような検査用のパターンは、TEG(Test Elementary Group)と呼ばれ、TEGに対して検査を行うことで、チップ領域10a内に形成されたパターンの状態を推定することができる。このスクライブ領域10bは、図3に示す個片化工程において切削加工する領域なので、製品である半導体装置1(図1参照)には、TEGのパターンは残らない。したがって、例えばスクライブ領域10bに形成された検査用の開口部8aの底部8Bに電子ビームEB(図16参照)を照射しても、これにより製品の電気的特性が損なわれることを防止できる。

【0054】

また、本実施の形態では、被測定膜および下地膜を励起する励起線として電子ビームEB(図16参照)を用いた例について説明したが、特性X線を発生させるために必要なエネルギーを有する励起源であれば電子ビームEB(図16参照)に代えてこれを用いることができる。例えば、励起線として、X線を用いることができる。この場合、開口部8の周辺に励起線が照射されてノイズが増大することを抑制する観点から、X線の照射口周辺に遮蔽板を設け、遮蔽板の開口部からX線を照射することが好ましい。ただし、励起線としては、電子ビームEB(図16参照)の方がX線よりも収束させ易いので、本実施の形態のように、スルーホールなどのアスペクト比の高い開口部8の底部8Bに照射する場合には、励起線として電子ビームEB(図16参照)を用いることが特に好ましい。

【0055】

<コンタクト層形成工程への適用>

次に、前記した残存膜検査工程の変形例として、図3に示すコンタクト層形成工程に適用した例について説明する。図22は、図3に示す配線層積層工程のプロセスフローを示す説明図である。また、図23は、図22に示すコンタクトホール貫通工程が完了した状態を示す拡大断面図である。また、図24は、図23のB部において、残存膜検査工程を行った状態を模式的に示す説明図である。また、図25は、図24に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Co/Si)の関係を示す説明図である。なお、図24および図25では、金属シリサイド膜として、コバルトシリサイド膜を形成した場合の例を示している。

【0056】

図3に示すコンタクト層形成工程では、まず、下地層準備工程として、配線層の下地となる層を形成する。コンタクト層形成工程に適用する場合には、ゲート電極3およびソース、ドレイン領域4の表面に形成された金属シリサイド膜9が、下地層となる。この金属シリサイド膜9は、ゲート電極3およびソース、ドレイン領域4の表面に、例えばコバルト(Co)膜やニッケル(Ni)膜などの金属膜を形成し、熱処理(アニール処理)を施すことで、金属膜とシリコンを反応させてシリサイド化することにより形成される。次に、ストッパ膜形成工程として、ストッパ絶縁膜(被測定膜)6sを成膜(形成)する。ストッパ絶縁膜6sは、例えば窒化シリコン膜(SiN膜)であって、例えば、CVD法により、例えば30nm〜50nm程度の厚さで形成される。本工程により、下地膜である金属シリサイド膜9は、ストッパ絶縁膜6sにより被覆される。

【0057】

次に主絶縁膜形成工程として、ストッパ絶縁膜6s上に、主層間絶縁膜である絶縁膜6aを成膜(形成)する。絶縁膜6aは、例えば、オゾン(O3)およびTEOS(Tetra-Ethyl-Ortho-Silicate)を用いた熱CVDによる酸化シリコン膜であるオゾンTEOS膜と、TEOSを用いたプラズマCVDによる酸化シリコン膜であるプラズマTEOS膜を積層して形成する。次に、マスク配置工程として、絶縁膜6aの上面PMa上にレジスト膜(図示は省略)を配置する。コンタクト層形成工程では、ゲート電極3表面の金属シリサイド膜9とゲート電極3およびソース、ドレイン領域4表面の金属シリサイド膜9の高さが異なるため、コンタクトホール8Hの高さが異なる。このため、コンタクトホール形成工程で、過剰にエッチングされることを抑制する観点から、ゲート電極3上のコンタクトホール8Hと、ソース、ドレイン領域4上のコンタクトホール8Hは、それぞれ別のレジスト膜(マスク)を用いて形成する。次に、コンタクトホール形成工程として、絶縁膜6aの上面PMa側から下地膜である金属シリサイド膜に向かって絶縁膜6aを取り除き、コンタクトホール(開口部、孔)8Hを形成する。絶縁膜6aを取り除く方法は、例えば、レジスト膜(図示は省略)をエッチングマスクとしてエッチング処理を行い、コンタクトホール8Hを形成する。エッチング方式は、ドライエッチング方式、ウェットエッチング方式、またはこれらを組み合わせて行う方式を用いることができる。この時、前記した配線層積層工程と同様に、シリコン酸化膜用のエッチング材を用いることにより、ストッパ絶縁膜6sがエッチングにより貫通してしまうことを抑制できる。しかし、シリコン酸化膜用のエッチング材を用いた場合であっても、ストッパ絶縁膜6sの一部はエッチングにより取り除かれる。また、ゲート電極3上のコンタクトホール8Hと、ソース、ドレイン領域4上のコンタクトホール8Hは、それぞれ別のレジスト膜(マスク)を用いて形成する。このため、一方のコンタクトホール8Hを形成した後でアッシング工程や洗浄工程を行い、レジスト膜を取り除いた後で、他方のコンタクトホール8Hを形成するためのレジスト膜を配置する。この時、ストッパ絶縁膜6sの一部は、コンタクトホール8Hの底部において残存膜として残っているので、アッシング処理中あるいは洗浄処理中の金属シリサイド膜9の汚染を抑制することができる。

【0058】

次に、コンタクトホール貫通工程として、図23に示すように、コンタクトホール8Hの下層のストッパ絶縁膜6sの残存膜を取り除く。本工程では、複数のコンタクトホール8H上にそれぞれ貫通孔23aが形成されたレジスト膜23をエッチングマスクとしたエッチング処理によりストッパ絶縁膜6sの残存膜を取り除く。これにより、コンタクトホール8Hがストッパ絶縁膜6sを厚さ方向に貫通する。そして、コンタクトホール8Hの底部において、下地膜である金属シリサイド膜9がストッパ絶縁膜6sから露出する。ここで、金属シリサイド膜9は、配線層積層工程で説明した導体膜7と比較して薄く、例えば、数nm〜数十nmであるため、エッチング時間を長くすると、金属シリサイド膜9をエッチングにより貫通してしまう。一方、エッチング時間が不足するとストッパ絶縁膜6sを貫通せず、導通不良(オープン不良)の原因となる。したがって、コンタクトホール8Hの深さを精密に制御する技術が必要となる。

【0059】

そこで、本実施の形態では、図22に示すように、コンタクトホール貫通工程の後で残存膜検査工程を行い、残存膜が取り除かれ、かつ金属シリサイド膜9が残っていることを検査する。図22に示すストッパ絶縁膜6sの残存膜の検査には、前記した配線層積層工程における残存膜検査工程を応用して適用することができる。すなわち、図24に示すように、コンタクトホール8Hの底部8Bに向かって、例えば電子ビーム(励起線)EBを照射することにより放出された特性X線を検出し、ストッパ絶縁膜6sの有無あるいは下地層である金属シリサイド膜9の有無を判定(評価)する。具体的には、複数成分の特性X線のうち、金属シリサイド膜に含まれる金属元素(例えばコバルト)成分と、ストッパ絶縁膜6sに主成分として含まれる半導体元素成分(例えばシリコン)の成分比率(Co/Si)により判定(評価)する。

【0060】

ここで、コンタクトホールに照射する電子ビームEB(図24参照)の強度(加速電圧)を変化させた場合の成分比率(Co/Si)の関係は図25に示すように変化する。まず、図23に示すように、コンタクトホール8Hがストッパ絶縁膜6sを貫通し、かつ、下地膜である金属シリサイド膜9を貫通していない場合には、図25に示すデータD1のように変化する。すなわち、電子ビームEB(図24参照)の加速電圧(励起線の強度)が低い領域では、金属シリサイド膜9が主に励起されるためコバルト元素に由来する特性X線成分の比率が高くなる。一方、電子ビームEB(図24参照)の加速電圧が上昇すると、金属シリサイド膜9よりもさらに下層の下地層(ウェル領域12)が励起されるので、シリコン元素に由来する特性X線成分の比率が上昇し、この結果、成分比率(Co/Si)は減少する。

【0061】

また、図23に示すコンタクトホール8Hがストッパ絶縁膜6sを貫通せず、ストッパ絶縁膜6sの残存膜が残っている場合には、図25に示すデータD2のように変化する。すなわち、電子ビームEB(図24参照)の加速電圧(励起線の強度)が低い領域では、ストッパ絶縁膜6sが主に励起されるため、コバルト元素に由来する特性X線成分の比率は低い。また、電子ビームEB(図24参照)の加速電圧が上昇すると、残存膜の下層の金属シリサイド膜9が励起されるため、コバルト元素に由来する特性X線成分の比率が上昇し、この結果、成分比率(Co/Si)は増加する。また、電子ビームEB(図24参照)の加速電圧がさらに上昇すると、金属シリサイド膜9よりもさらに下層のウェル領域12が励起されるので、シリコン元素に由来する特性X線成分の比率が上昇し、この結果、成分比率(Co/Si)は減少する。

【0062】

また、図23に示すコンタクトホール8Hが、下地膜である金属シリサイド膜9を貫通した場合には、図25に示すデータD3のように変化する。すなわち、電子ビームEB(図24参照)の加速電圧(励起線の強度)が低い領域では、ウェル領域12中に拡散した、僅かなコバルト成分を除き、コバルト元素に由来する特性X線は殆ど検出されない。また、電子ビームEB(図24参照)の加速電圧を上昇させてもコバルト成分は増加しないため、成分比率(Co/Si)は、電子ビームEB(図24参照)の加速電圧によらず低い。言い換えれば、金属シリサイド膜9を被測定膜とし、ウェル領域12を下地膜として測定していることになる。

【0063】

図25に示す成分比率(Co/Si)と電子ビームEB(図24参照)の加速電圧(励起線の強度)の相関関係から、ストッパ絶縁膜6sの有無あるいは下地層である金属シリサイド膜9の有無を容易に判定(評価)することができる。すなわち、例えば、1kV〜2kV程度の低い加速電圧の電子ビームEB(図24参照)(低強度の励起線)を照射すると、データD2、D3の場合には、データD1よりも成分比率(Co/Si)が極端に小さくなる。したがって、成分比率(Co/Si)が閾値よりも低ければ、ストッパ絶縁膜6sの除去不良、あるいは金属シリサイド膜9の貫通不良のいずれかが発生していることが判る。この時点で、製造工程にフィードバックすれば、不良品が大量に生産されてしまうロスを防止することができる。また、例えば、2kV〜4kV程度の加速電圧で電子ビームEB(図24参照)を照射すれば、データD2とデータD3の分類ができる。つまり、不良の内容を把握することができるので、不良の発生原因が特定し易くなる。なお、コンタクト層形成工程に残存膜検査工程を適用する場合にも、前記した図19に示す検査装置30を用いることができるので、重複する説明は省略する。

【0064】

このように、本実施の形態によれば、前記配線層積層工程で説明したように、残存膜が残っていることを確認するための検査の他、残存膜が残っていないことを確認するための検査、あるいは、下地膜を貫通していないことを確認するための検査として残存膜検査工程を適用することができる。なお、本実施の形態では、配線層積層工程において、残存膜が残っていることを確認するための検査に適用した例について説明した。また、コンタクト層形成工程において、残存膜が残っていないことを確認するための検査、あるいは、下地膜を貫通していないことを確認するための検査に適用した例について説明した。しかし、これらは互いに組み合わせて適用することができる。例えば、図5に示すコンタクトホール貫通工程の後で、残存膜が残っていないことを確認するための検査、あるいは、下地膜を貫通していないことを確認するための検査として残存膜検査工程を適用することができる。また、例えば、図22に示すコンタクトホール形成工程と、コンタクトホール貫通工程の間で、残存膜が残っていることを確認するための検査として残存膜検査工程を適用することができる。

【0065】

次に、図22に示す導体膜形成工程として、コンタクトホール8H内に導体膜を埋め込んで図2に示すプラグ7aを形成する。

【0066】

本工程では、まず、絶縁膜6aの上面PMa(図23参照)、およびコンタクトホール8Hの内面に、バリア導体膜として、例えば、チタン膜および窒化チタン膜を順次成膜する。バリア導体膜は、例えば、TiCl4をメタルソースガスとして用いたメタルCVD処理により、形成することができる。なお、バリア導体膜の形成方法については、被覆性等の問題がないのであれば、メタルCVD処理のほか、スパッタリング成膜、またはメタルCVD処理とスパッタリング成膜の組み合わせ等の方法が適用できる。次に、コンタクトホール8H内のバリア導体膜上に、主導体膜であるタングステン膜を形成する。タングステン膜は、例えば、WF6をメタルソースガスとして用いたメタルCVD処理により、コンタクトホール8Hを埋め込むように形成する。次に、平坦化工程として、メタルCMPにより、平坦化処理を施し、コンタクトホール8H外部のタングステン膜およびバリア導体膜を除去する。以上の工程により、図2に示すように、プリメタル層間絶縁膜の上面に、ゲート電極3あるいはソース、ドレイン領域4と電気的に接続されるプラグ7aが露出されたコンタクト層である配線層PMが形成される。この配線層PMは、配線層M1を形成する際の下地層となり、図3に示す配線層積層工程で配線層PM上に複数の配線層5が積層される。

【0067】

<変形例>

次に、本実施の形態の変形例について説明する。前記配線層形成工程および前記コンタクト層形成工程では、ストッパ絶縁膜6sを被測定膜とし、導体膜7または、金属シリサイド膜9を下地膜とする例について説明した。しかし、本実施の形態の残存膜検査工程における被測定膜と下地膜の組み合わせは上記に限定されない。例えば、被測定膜および下地膜が導体膜である場合、あるいは被測定膜および下地膜が絶縁膜である場合であっても、被測定膜と下地膜のそれぞれから異なる元素成分の特性X線が検出できれば適用することができる。一例として、本変形例では、被測定膜および下地膜が導体膜である場合について説明する。図26は、図16に示す残存膜検査工程の変形例を模式的に示す説明図である。また、図27は、図26に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Ti/Al)の関係を示す説明図である。

【0068】

図26に示す配線層5では、例えばアルミニウム(Al)から成る主導体膜7Cの上面および下面にそれぞれ、例えば窒化チタン(TiN)からなり、主導体膜7Cよりも薄いバリア導体膜7Dが成膜され、導体膜7を構成する。導体膜7上には、絶縁膜6が積層され、絶縁膜6の上面側から導体膜7に向かってコンタクトホール8Hが形成されている。このコンタクトホール8H内にプラグとなる導体膜(図示は省略)を埋め込むことで、配線層5と、配線層5の上層に積層される配線層を電気的に接続する層間導電路が形成される。このため、コンタクトホール8Hを形成する工程では、コンタクトホール8Hの底部8Bにおいて、導体膜7を確実に露出させる必要がある。一方、コンタクトホール8Hがバリア導体膜7Dを貫通すると、主導体膜7Cが露出してしまうため、コンタクトホール8Hの底部8Bに、バリア導体膜7Dの一部を残存させる必要がある。

【0069】

このように導体膜7を確実に露出させ、かつ、薄いバリア導体膜7Dの一部を残存させるため、前記した残存膜検査工程を応用して適用することができる。すなわち、コンタクトホール8Hを形成した後で、バリア導体膜7Dを被測定膜、主導体膜7Cを下地膜として残存膜検査工程を適用する。例えば、複数成分の特性X線のうち、バリア導体膜7Dに主成分として含まれる金属元素(例えばチタン)成分と、主導体膜7Cに主成分として含まれる金属元素成分(例えばアルミニウム)の成分比率(Ti/Al)により判定(評価)する。

【0070】

ここで、コンタクトホールに照射する電子ビームEB(図26参照)の強度(加速電圧)を変化させた場合の成分比率(Ti/Al)の関係は図27に示すように変化する。まず、図26に示すように、コンタクトホール8Hが絶縁膜6を貫通し、かつ、バリア導体膜7Dを貫通していない場合には、図27に示すデータD4のように変化する。すなわち、電子ビームEB(図26参照)の加速電圧(励起線の強度)が低い領域では、バリア導体膜7Dが主に励起されるためチタン元素に由来する特性X線成分の比率が高くなる。一方、電子ビームEB(図26参照)の加速電圧が上昇すると、バリア導体膜7Dの下地層である主導体膜7Cが励起されるので、アルミニウム元素に由来する特性X線成分の比率が上昇し、この結果、成分比率(Ti/Al)は減少する。

【0071】

また、図26に示すコンタクトホール8Hが絶縁膜6を貫通せず、バリア導体膜7Dが露出していない場合には、図27に示すデータD5のように変化する。すなわち、電子ビームEB(図26参照)の加速電圧(励起線の強度)が低い領域では、絶縁膜6が主に励起されるため、チタン元素やアルミニウム元素に由来する特性X線成分は殆ど検出されない。また、電子ビームEB(図26参照)の加速電圧が上昇すると、チタン元素に由来する特性X線成分の比率が上昇し、成分比率(Ti/Al)は増加する。また、電子ビームEB(図26参照)の加速電圧がさらに上昇すると、バリア導体膜7Dの下地層である主導体膜7Cが励起されるので、アルミニウム元素に由来する特性X線成分の比率が上昇し、この結果、成分比率(Ti/Al)は減少する。

【0072】

また、図26に示すコンタクトホール8Hが、バリア導体膜7Dを貫通した場合には、図27に示すデータD6のように変化する。すなわち、チタン元素に由来する特性X線は、電子ビームEB(図26参照)の加速電圧によらず、殆ど検出されない。このため、成分比率(Ti/Al)は、電子ビームEB(図26参照)の加速電圧によらず低い。

【0073】

つまり、図27に示す成分比率(Ti/Al)と電子ビームEB(図26参照)の加速電圧(励起線の強度)の相関関係から、絶縁膜6の残存膜の有無あるいはバリア導体膜7Dの有無を容易に判定(評価)することができる。すなわち、例えば、1kV〜2kV程度の低い加速電圧の電子ビームEB(図26参照)(低強度の励起線)を照射すると、データD5、D6の場合には、データD4よりも成分比率(Ti/Al)が極端に小さくなる。したがって、成分比率(Ti/Al)が閾値よりも低ければ、絶縁膜6の除去不良、あるいはバリア導体膜7Dの貫通不良のいずれかが発生していることが判る。この時点で、製造工程にフィードバックすれば、不良品が大量に生産されてしまうロスを防止することができる。また、例えば、2kV〜4kV程度の加速電圧で電子ビームEB(図26参照)を照射すれば、データD5とデータD6の分類ができる。つまり、不良の内容を把握することができるので、不良の発生原因が特定し易くなる。なお、コンタクト層形成工程に残存膜検査工程を適用する場合にも、前記した図19に示す検査装置30を用いることができるので、重複する説明は省略する。

【0074】

このように、本変形例によれば、特性X線を検出する方式を採用することで、被測定膜および下地膜がそれぞれ導体膜であっても、残存膜の有無、あるいは膜厚を容易に測定することができる。

【0075】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0076】

例えば、前記実施の形態では、予め判定用データを取得して、成分比率の測定データと判定用データを比較することにより、残存膜の有無あるいは膜厚を測定する方法について説明した。しかし、判定用データを予め準備しなくても残存膜の有無を判定することができる。例えば、図17、図25あるいは図27に示すように、残存膜の有無によって、特性X線の成分比率データが大きく変化する強度の励起線(例えば加速電圧が1kV〜2kV程度の電子線)を照射すれば、判定用データと比較しなくても、残存膜の有無を判定することができる。

【0077】

また、例えば、前記変形例では、被測定膜であるバリア導体膜7Dの有無を判定する例について説明したが、配線層積層工程で説明したように、バリア導体膜7Dの膜厚を判定することもできる。

【産業上の利用可能性】

【0078】

本発明は、半導体基板上に配線層を積層する半導体装置に利用可能である。

【符号の説明】

【0079】

1 半導体装置(半導体チップ)

1a 表面

2 半導体基板

2a 主面

3 ゲート電極

4 ソース、ドレイン領域(半導体領域)

5 配線層

6、6a、6b、6c、6d、6t 絶縁膜

6s ストッパ絶縁膜

7、7b、7c 導体膜

7A、7C 主導体膜

7B、7D バリア導体膜

7L 配線

7P、7a プラグ(コンタクトプラグ)

7t 配線

8 開口部

8B 底部

8G 配線溝

8H コンタクトホール

8a 開口部

8b 開口部

9 金属シリサイド膜

10a チップ領域

10b スクライブ領域

11 素子分離領域

12 ウェル領域

21、22、23 レジスト膜

21a、23a 貫通孔

22a 開口部

30 検査装置(残存膜検査装置)

31 検出部

32 励起線照射部

33 基板固定部

34 判定部

34a 判定回路

34b データ保持部

35 制御部

100 下地膜

101 被測定膜

102 位相検出器

103 二次電子検出部

D1、D2、D3、D4、D5、D6 データ

EB 電子ビーム(励起線)

FP パッシベーション膜

L1 照射光

L2、L3 反射光

PM、M1、M2、MX、MT 配線層

PMa、M2a、M3a 上面

PD パッド(電極)

Q1 半導体素子

SE1、SE2 二次電子

WH ウエハ(半導体基板)

【技術分野】

【0001】

本発明は、半導体装置の製造技術に関し、特に半導体基板上に形成した積層膜に開口部を形成した後、残存膜の有無や膜厚を検査する工程に適用して有効な技術に関するものである。

【背景技術】

【0002】

特開2005−98923号公報(特許文献1)には、被測定膜に電子ビームを照射して、被測定膜から放出される二次電子の量を測定することにより、被測定膜の膜厚を測定する膜厚測定方法が記載されている。

【0003】

特開2008−34475号公報(特許文献2)には、コンタクトホールの底面に残る残存膜の厚さを測定する方法が記載されている。特許文献2では、コンタクトホールに電子線を照射して被検査対象の二次電子画像の電位コントラストを測定することで、残存膜の厚さや抵抗値が推定できるとしている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−98923号公報

【特許文献2】特開2008−34475号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

半導体装置の製造工程には、半導体基板の主面に半導体素子を形成した後、主面上に配線層を積層し、最上層の配線層に形成される複数の電極(パッド)と半導体素子を電気的に接続する工程(以下、配線層積層工程と呼ぶ)が含まれる。この配線層積層工程では、下地膜(半導体基板の主面または下層の配線層の上面)上に絶縁膜を形成し、該絶縁膜に溝(配線溝)や孔(コンタクトホール)などの開口部を形成する。そして、開口部に導体膜を埋め込むことにより上層と下層を電気的に接続する配線層を形成する。このため、半導体装置の電気的接続信頼性を確保する観点から、絶縁膜を確実に貫通する開口部を形成することが重要になる。開口部が絶縁膜を貫通しなければ、電気的接続不良(オープン不良)となるからである。

【0006】

また、開口部は、例えば、絶縁膜上にレジストパターンが形成されたレジスト膜を形成し、このレジスト膜をマスクとしたエッチング処理により形成する。この場合、レジスト膜を除去する工程(アッシング工程)や洗浄工程が必要となるが、これらアッシング工程や洗浄工程において、下層の配線層を保護する観点からは、以下の方法が有効である。すなわち、開口部の底部において、絶縁膜の一部を薄く残存させた状態でアッシング工程や洗浄工程を行い、その後、残存する薄膜(残存膜)を除去する方法が有効である。このような方法を用いるためには、エッチング工程で、残存膜が完全に除去されないように薄く残すことが重要となる。アッシング工程や洗浄工程の前に残存膜が除去されると下層の配線層を保護できなくなる不良(貫通不良)の原因となるからである。つまり、絶縁膜に開口部を形成する際には、その深さを制御する技術が必要となる。

【0007】

そこで、本願発明者は、絶縁膜に形成する開口部の深さを制御する技術の一環として、残存膜の有無、あるいは膜厚を検査する技術について検討を行い、以下の課題を見出した。

【0008】

すなわち、前記特許文献1や前記特許文献2に記載されるように、被測定膜に電子ビームを照射して、被測定膜から放出される二次電子の量、あるいは二次電子画像の電位コントラストを測定する方法の場合、残存膜の測定精度が低下する、あるいは測定不可能になることが判明した。

【0009】

例えば、開口部のアスペクト比が大きい場合、被測定膜や下地膜から放出される二次電子が、配線溝やコンタクトホールの側壁に吸収され易くなる。この結果、二次電子の検出量が低下して測定精度低下や測定不可能化の原因となる。また、二次電子の検出量は、開口部の周辺領域のパターンによるノイズの影響を受け易いため、測定精度低下の原因となる。また例えば、被測定膜とその下地膜が、二次電子放出特性の近い材料(例えば、金属膜同士)で構成されている場合、被測定膜とその下地膜の二次電子放出量の差が明確にならず、測定精度低下や測定不可能化の原因となる。

【0010】

また、残存膜の有無や膜厚の検査に時間を要すれば、製造工程へのフィードバック時間が増大するので、製造効率が低下する。このため、製造効率低下を抑制するためには、残存膜の有無や膜厚の検査時間を短縮する必要がある。

【0011】

本発明は、上記課題に鑑みてなされたものであり、その目的は、半導体装置の電気的な接続信頼性を向上させる技術を提供することにある。また、その他の目的としては、残存膜の有無や膜厚を効率的に検査する技術を提供することにある。

【0012】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0013】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0014】

すなわち、本願発明の一態様である半導体装置の製造方法は、(a)半導体基板の主面上に、下地膜および下地膜上の被測定膜を積層する工程、(b)前記被測定膜に開口部を形成する工程、を含んでいる。また、(c)前記開口部に励起線を照射して、特性X線を放出させる工程、および(d)前記特性X線を検出し、前記特性X線の検出結果に基いて前記開口部の底部における前記被測定膜の有無または膜厚を判定する工程、を含んでいる。また、前記(d)工程では、前記特性X線に含まれる複数の元素成分の比率により、前記被測定膜の有無または膜厚を判定するものである。

【発明の効果】

【0015】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下の通りである。

【0016】

すなわち、本願発明の一態様によれば、半導体装置の電気的な接続信頼性を向上させることができる。また、残存膜の有無や膜厚を効率的に検査することができる。

【図面の簡単な説明】

【0017】

【図1】本発明の一実施の形態である半導体装置の全体構造の一例を示す平面図である。

【図2】図1に示す半導体装置の断面構造の一例を示す拡大断面図である。

【図3】図1および図2に示す半導体装置の製造工程フローの概要を示す説明図である。

【図4】図3の半導体基板準備工程で準備する半導体基板の平面図である。

【図5】図3に示す配線層積層工程のプロセスフローを示す説明図である。

【図6】図2に示す第4層目の配線層の下地層が形成された状態を示す拡大断面図である。

【図7】図6に示す配線層の上面にエッチストッパ膜を成膜した状態を示す拡大断面図である。

【図8】図7に示すエッチストッパ膜上に主絶縁膜を成膜した状態を示す拡大断面図である。

【図9】図8に示す主絶縁膜上にコンタクトホールを形成するためのマスクを配置した状態を示す拡大断面図である。

【図10】図9に示す絶縁膜にコンタクトホールを形成した状態を示す拡大断面図である。

【図11】図10に示すマスクを除去した後、配線溝を形成するためのマスクを配置して配線溝を形成した状態を示す拡大断面図である。

【図12】図11に示すマスクを除去した後、コンタクトホール下層の残存膜を取り除いた状態を示す拡大断面図である。

【図13】図12に示す開口部の底部の残存膜を除去した後、開口部内にバリア導体膜を成膜した状態を示す拡大断面図である。

【図14】図13に示す開口部内に主導体膜を埋め込んだ状態を示す拡大断面図である。

【図15】図14に示す絶縁膜の上面に平坦化処理を施し、絶縁膜の上面上の導体膜を取り除いた状態を示す拡大断面図である。

【図16】図5に示す残存膜検査工程を模式的に示す説明図である。

【図17】図16に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Cu/Si)の関係を示す説明図である。

【図18】図16に示す開口部に照射する電子ビームの強度(加速電圧)毎に、残存膜の膜厚と成分比率(Cu/Si)の関係を示す説明図である。

【図19】残存膜検査装置の概要構成を示す説明図である。

【図20】図5に示す残存膜検査工程において、残存膜を検査する開口部の位置の例を示す平面図である。

【図21】図20のA部の拡大平面図である。

【図22】図3に示す配線層積層工程のプロセスフローを示す説明図である。

【図23】図22に示すコンタクトホール貫通工程が完了した状態を示す拡大断面図である。

【図24】図23のB部において、残存膜検査工程を行った状態を模式的に示す説明図である。

【図25】図24に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Co/Si)の関係を示す説明図である。

【図26】図16に示す残存膜検査工程の変形例を模式的に示す説明図である。

【図27】図26に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Ti/Al)の関係を示す説明図である。

【図28】第1の比較例である残存膜検査工程を模式的に示す説明図である。

【図29】第2の比較例である残存膜検査工程を模式的に示す説明図である。

【発明を実施するための形態】

【0018】

(本願における記載形式の説明)

本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクション等に分けて記載するが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、記載の前後を問わず、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しの説明を省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。また、実施の形態の各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。また、添付図面においては、却って、煩雑になる場合または空隙との区別が明確である場合には、断面であってもハッチング等を省略する場合がある。これに関連して、説明等から明らかである場合等には、平面的に閉じた孔であっても、背景の輪郭線を省略する場合がある。更に、断面でなくとも、空隙でないことを明示するため、あるいは領域の境界を明示するために、ハッチングやドットパターンを付すことがある。

【0019】

<半導体装置の概要>

図1は、本実施の形態の半導体装置の全体構造の一例を示す平面図、図2は図1に示す半導体装置の断面構造の一例を示す拡大断面図である。図1に示すように、本実施の形態の半導体装置(半導体チップ)1は、四角形の平面形状を成す表面1aを有している。表面1aは、例えば、窒化シリコン膜、シリコン酸化膜、または窒化シリコン膜とシリコン酸化膜との積層膜で構成される、保護膜(保護絶縁膜)であるパッシベーション膜(保護膜、絶縁膜、保護絶縁膜)FPに覆われている。また、表面1a側には、表面1aの辺に沿って、例えば、アルミニウムで構成される複数のパッド(電極、電極パッド、ボンディングパッド)PDが形成されている。複数のパッドPDのそれぞれは、パッシベーション膜FPに形成された複数の開口部において、パッシベーション膜FPから露出している。この複数のパッドPDは、それぞれ半導体装置1の外部端子となっている。

【0020】

また、図2に示すように、半導体基板2の主面2aに複数の半導体素子Q1が形成されている。図2に示す半導体素子Q1は、例えば、MISFET(Metal Insulator Semiconductor Field Effect Transistor)である。半導体素子Q1のそれぞれは、主面2a上に形成されるゲート電極3、および主面2aにおいてゲート電極3の両隣に形成されるソース領域またはドレイン領域(以下、ソース、ドレイン領域4と記載する)を有している。また、半導体基板2の主面2a上には、複数の配線層5(図2に示す、配線層PM、M1、M2、M3、MX、MT)が積層されている。各配線層は、複数のコンタクトホール(孔、開口部)や配線溝(溝、開口部)が形成された絶縁膜(層間絶縁膜)6を有している。また、複数のコンタクトホールや配線溝には、導体膜(配線)7が埋め込まれ、この導体膜7を介して、下層の配線層5(または半導体素子Q1の電極)と上層の配線層5がそれぞれ電気的に接続されている。また、最上層の配線層MTには、配線(最上層配線)7tおよび複数のパッドPD(図1参照)が形成されている。複数のパッドPDは、配線層MTに形成される配線7tと接続され、下層に形成された複数の配線層5(詳しくは各配線層5の導体膜7)を介して半導体素子Q1と電気的に接続されている。

【0021】

本実施の形態では、各配線層5は、主成分にシリコンを含む絶縁膜6、金属膜からなる導体膜7を有しているが、絶縁膜6や導体膜7は、形成される配線層5毎に異なる成膜方法あるいは含有成分が異なる材料を用いることができる。例えば、本実施の形態では、最下層に配置され、各半導体素子Q1に当接させるコンタクト層となる配線層PMは、絶縁膜6aとしてCVD(Chemical Vapor Deposition)法により形成される酸化シリコン(SiO2)膜を形成している。詳しくは、オゾン(O3)およびTEOS(Tetra-Ethyl-Ortho-Silicate)を用いた熱CVDによる酸化シリコン膜であるオゾンTEOS膜と、TEOSを用いたプラズマCVDによる酸化シリコン膜であるプラズマTEOS膜の積層膜となっている。また、配線層PMのプラグ(コンタクトプラグ、導体膜)7aは、タングステン(W)を主体とする導体膜で構成される。詳しくは、例えば、チタン膜および窒化チタン膜を順次成膜したバリア導体膜と、タングステン膜の積層膜となっている。また、配線層PM上の配線層M1を構成する絶縁膜6bは、例えばプラズマCVDによる酸化シリコン膜で構成され、さらに上層の配線層M2、M3の絶縁膜6cは、炭素(C)がドープされた酸化シリコン膜(SiOC膜)となっている。また、さらに上層の配線層MXには、例えば、FSG(Fluorosilicate Glass)から成る絶縁膜6d、最上層の配線層MTには、USG(Undoped Silicate Glass)から成る絶縁膜6tが形成されている。また、配線層M2、M3、MXのプラグまたは配線である導体膜7としては、例えば、銅(Cu)を主体とする金属から成る導体膜7bが形成されている。詳しくは、導体膜7bは、例えば、タンタル(Ta)膜、窒化タンタル(TaN)膜あるいはこれらの積層膜などから成るバリア導体膜上に、銅または銅合金からなる主導体膜の積層膜で構成される。また、最上層の配線層MTとその下層の配線層MXを接続するプラグである導体膜7cは、例えば、タングステンから成り、最上層に形成される配線7tは例えばアルミニウムで構成される。また、各配線層5の界面には、開口部をエッチング法により形成する際のストッパ絶縁膜(エッチストッパ膜)として、例えば、炭素(C)がドープされた窒化シリコン膜(SiCN膜)が、主絶縁膜である絶縁膜6よりも薄く形成されている。

【0022】

<半導体装置の製造方法の概要>

次に、図1および図2に示す半導体装置の製造方法の概要について説明する。図3は、図1および図2に示す半導体装置の製造工程フローの概要を示す説明図である。また、図4は図3の半導体基板準備工程で準備する半導体基板の平面図である。図1および図2に示す半導体装置の製造方法の一例について図3を用いて簡単に説明すると、例えば、以下のように製造される。

【0023】

まず、半導体基板準備工程で、図4に示すウエハ(半導体基板)WHを準備する。ウエハWHは、図4に示すように、平面略円形の平板であって、例えば平面視において四角形を成す複数のチップ領域(デバイス領域)10aに区画されている。また複数のチップ領域10aの間には、スクライブ領域(ダイシング領域)10bが配置されている。

【0024】

半導体基板準備工程の後、半導体素子形成工程で、ウエハWHの主面2a(図2参照)にトランジスタやダイオードなどである複数の半導体素子Q1(図2参照)を形成する。本工程では、例えば、図2に示すように、ウエハWH(図4参照)の主面2aに素子分離領域11およびウェル領域12を形成する。素子分離領域11は、例えば、シリコン酸化膜などからなり、例えばSTI(Shallow Trench Isolation)法またはLOCOS(Local Oxidization of Silicon)法などにより形成される。また、ウェル領域12は、p型またはn型の導電型の不純物を含む半導体領域であって、半導体素子Q1を形成する領域に、不純物をイオン注入することにより形成される。例えば、nチャネル型の半導体素子Q1が形成される領域には、例えばホウ素(B)などのp型の不純物がイオン注入されることによりp型のウェル領域(p型ウェル領域)12が形成される。また、pチャネル型の半導体素子Q1が形成される領域には、リン(P)または砒素(As)などのn型の不純物がイオン注入されることにより、n型のウェル領域(n型ウェル領域)12が形成される。その後、主面2aのウェル領域12にゲート電極3およびソース、ドレイン領域4を形成し、半導体素子Q1を形成する。ゲート電極3は、例えば、2nm〜4nm程度の薄い酸化シリコン膜から成るゲート酸化膜上に、ポリシリコン膜(例えば、不純物を含む多結晶シリコン膜)を積層することで形成される。また、ゲート電極3の側面には、サイドウォール絶縁膜が形成される。また、ソース、ドレイン領域4は、ゲート電極3の両隣に不純物がイオン注入されることにより形成される。例えば、nチャネル型の半導体素子Q1が形成されるp型のウェル領域12には、リン(P)または砒素(As)などのn型の不純物がイオン注入され、n型半導体領域であるソース、ドレイン領域4が形成される。また、pチャネル型の半導体素子Q1が形成される領域には、ホウ素(B)などのp型の不純物がイオン注入され、p型半導体領域であるソース、ドレイン領域4が形成される。また、ゲート電極3およびソース、ドレイン領域4の表面には、金属シリサイド膜が積層される。この金属シリサイド膜は、ゲート電極3およびソース、ドレイン領域4の表面に、例えばコバルト(Co)膜やニッケル(Ni)膜などの金属膜を形成し、熱処理(アニール処理)を施すことで、金属膜とシリコンを反応させてシリサイド化することにより形成される。

【0025】

半導体素子形成工程の後、コンタクト層形成工程で、図2に示す各半導体素子Q1に当接させるコンタクト層となる配線層PMを形成する。その後、配線層積層工程として、主面2a上(配線層PM上)に複数の配線層5を積層する。このコンタクト層形成工程および配線層積層工程の詳細は後述するが、概要を説明すると以下である。下地層(半導体基板2または下層の配線層5)上に絶縁膜6を形成した後、絶縁膜6に開口部を形成する。その後、開口部内に導体膜7を埋め込んでプラグまたは配線を形成する。そして、配線層5の上面に例えばCMP(Chemical Mechanical Polishing)法による平坦化処理を施し、上面を平坦化する。これにより、導体膜7が絶縁膜6の下面および上面において露出した配線層5が形成される。この工程を繰り返し行うことで、複数の配線層5を積層することができる。なお、最上層の配線7tは、例えば、平坦化処理が施された最上層の絶縁膜6t上に、例えばスパッタ法によりアルミニウムから成る金属膜を成膜し、これをエッチングによりパターニングして形成される。この時、配線7tに接続される複数のパッドPD(図1参照)も形成される。

【0026】

配線層積層工程の後、保護膜形成工程で、最上層の配線7t上にパッシベーション膜(保護膜、絶縁膜、保護絶縁膜)FPを形成(成膜)する。本工程では、例えば、窒化シリコン膜、シリコン酸化膜、または窒化シリコン膜とシリコン酸化膜との積層膜をCVD法により成膜し、配線7tおよびこれに接続される複数のパッドPD(図1参照)を被覆する。その後、パッド開口部形成工程で、パッシベーション膜FPに複数の開口部を形成し、開口部において複数のパッドPD(図1参照)をパッシベーション膜FPから露出させる。その後、電気的検査工程などの処理を施した後、個片化工程として、ウエハWH(図4参照)をチップ領域10a(図4参照)毎に分割し、個片化する。本工程では、例えばダイシングブレードと呼ばれる切断刃を図4に示すウエハWHのスクライブ領域10bに沿って走らせて、ウエハWHを分割する。これにより、1枚のウエハWHから複数の半導体装置1(図1参照)を取得することができる。

【0027】

<配線層積層工程の詳細>

前記したコンタクト層形成工程および配線層積層工程では、絶縁膜6にコンタクトホールや配線溝などの開口部を形成し、該開口部に導体膜7を埋め込むことにより、プラグまたは配線を形成する。以下では、開口部を形成した後、開口部内に導体を埋め込む工程の説明として、図2に示す配線層M3を形成する工程を例に取り上げて詳細に説明する。図5は、図3に示す配線層積層工程のプロセスフローを示す説明図である。また、図6は、図2に示す第4層目の配線層の下地層が形成された状態を示す拡大断面図である。また、図7は図6に示す配線層の上面にエッチストッパ膜を成膜した状態を示す拡大断面図、図8は、図7に示すエッチストッパ膜上に主絶縁膜を成膜した状態を示す拡大断面図である。また、図9は、図8に示す主絶縁膜上にコンタクトホールを形成するためのマスクを配置した状態を示す拡大断面図、図10は、図9に示す絶縁膜にコンタクトホールを形成した状態を示す拡大断面図である。また、図11は、図10に示すマスクを除去した後、配線溝を形成するためのマスクを配置して配線溝を形成した状態を示す拡大断面図、図12は、図11に示すマスクを除去した後、コンタクトホール下層の残存膜を取り除いた状態を示す拡大断面図である。また、図13は、図12に示す開口部の底部の残存膜を除去した後、開口部内にバリア導体膜を成膜した状態を示す拡大断面図、図14は、図13に示す開口部内に主導体膜を埋め込んだ状態を示す拡大断面図である。図15は、図14に示す絶縁膜の上面に平坦化処理を施し、絶縁膜の上面上の導体膜を取り除いた状態を示す拡大断面図である。

【0028】

図3に示す配線層積層工程では、まず、下地層準備工程として、配線層の下地となる層を形成する。図6は、図2に示す配線層M3を形成する工程を説明する図なので、配線層M2がこの下地層に相当する。配線層M2には、絶縁膜6および絶縁膜6を貫通する開口部8が形成され、開口部8内に導体膜(下地膜)7が埋め込まれている。また、配線層M2の上面M2aは平坦化処理が施され、導体膜7が上面M2aの開口部8において、絶縁膜6から露出している。次に、ストッパ膜形成工程として、図7に示すように、ストッパ絶縁膜(被測定膜)6sを成膜(形成)する。ストッパ絶縁膜6sは、例えば炭素(C)がドープされた炭化窒化シリコン膜(SiCN膜)であって、例えば、CVD法により、例えば30nm〜50nm程度の厚さで形成される。本工程により、配線層M2の上面M2aにおいて、絶縁膜6cから露出する導体膜7(主導体膜(下地膜)7Aおよびバリア導体膜7B)は、ストッパ絶縁膜6sにより被覆される。

【0029】

次に主絶縁膜形成工程として、図8に示すようにストッパ絶縁膜6s上に、主層間絶縁膜である絶縁膜6cを成膜(形成、積層)する。絶縁膜6cは、例えば、炭素(C)がドープされた酸化炭化シリコン膜(SiOC膜)であって、例えばCVD法により、ストッパ絶縁膜6sよりも厚く、例えば300nm〜500nmの厚さで形成される。次に、第1マスク配置工程として、図9に示すように、絶縁膜6cの上面M3a上にレジスト膜21を配置する。レジスト膜21は、主絶縁膜である絶縁膜6cにコンタクトホール8H(図10参照)を形成するためのマスクであって、マスクパターンとして、コンタクトホール8Hを形成する位置にレジスト膜21を厚さ方向に貫通する貫通孔21aが形成される。

【0030】

次に、コンタクトホール形成工程として、図10に示すように、レジスト膜21をマスクとして絶縁膜6cの上面M3a側から下地層である配線層M2に向かって絶縁膜6cの一部を取り除き、コンタクトホール(開口部、孔)8Hを形成する。絶縁膜6cの一部を取り除く方法は、例えば、レジスト膜21をエッチングマスクとしてエッチング処理を行い、コンタクトホール8Hを形成する。エッチング方式は、ドライエッチング方式、ウェットエッチング方式、またはこれらを組み合わせて行う方式を用いることができる。配線層M3は、コンタクトホール8Hに接続される配線溝も形成するので、本工程の終了段階では、コンタクトホール8Hは図10に示すように絶縁膜6cを貫通せず、コンタクトホール8Hの底部8Bは絶縁膜6cの途中に配置されている。次に、第1マスク除去工程(アッシング工程)として、図10に示すレジスト膜21を取り除く。この時、下地層である配線層M2の導体膜7は、ストッパ絶縁膜6sおよびその上層の絶縁膜6cに覆われているので、アッシング処理中の導体膜7の汚染を抑制することができる。また、アッシング処理を行った後、レジスト膜21の残渣を取り除く洗浄工程を行う場合もあるが、この場合にも、配線層M2の導体膜7は、ストッパ絶縁膜6sおよびその上層の絶縁膜6cに覆われているので、洗浄処理中の導体膜7の汚染を抑制することができる。

【0031】

次に、第2マスク配置工程として、図11に示すように、絶縁膜6cの上面M3a上にレジスト膜22を配置する。レジスト膜22は、主絶縁膜である絶縁膜6cに配線溝(開口部)8Gを形成するためのマスクであって、マスクパターンとして、配線溝8Gを形成する位置にレジスト膜22を厚さ方向に貫通する開口部22aが形成される。レジスト膜22は配線溝8Gを形成するためのマスクであり、開口部22aは、図10に示すレジスト膜21の貫通孔21aよりも幅広に形成されている。次に、配線溝形成工程として、レジスト膜22をマスクとして絶縁膜6cの上面M3a側から下地層である配線層M2に向かって絶縁膜6cおよびストッパ絶縁膜6sの一部を取り除き、配線溝(開口部、溝)8Gを形成する。絶縁膜6cおよびストッパ絶縁膜6sの一部を取り除く方法は、コンタクトホール形成工程と同様に、例えば、レジスト膜22をエッチングマスクとしてエッチング処理を行い、配線溝8Gを形成する。この時、コンタクトホール8Hも、レジスト膜22の開口部22aにおいて、レジスト膜22から露出しているため、図10に示すコンタクトホール8Hの底部8Bの下層の絶縁膜6もさらに取り除かれる。このため、コンタクトホール8Hはさらに下方に向かって延び、絶縁膜6cを厚さ方向に貫通する。なお、本実施の形態では絶縁膜6cをシリコン酸化膜系の膜、ストッパ絶縁膜6sをシリコン窒化膜系の膜としている。このため、本工程で、シリコン酸化膜用のエッチング材(ドライエッチング方式の場合はエッチングガス、ウェットエッチング方式の場合はエッチング液)を用いることにより、ストッパ絶縁膜6sがエッチングにより貫通してしまうことを抑制できる。しかし、シリコン酸化膜用のエッチング材を用いた場合であっても、ストッパ絶縁膜6sの一部はエッチングにより取り除かれる。

【0032】

ここで、本工程では、図11に示すように、ストッパ絶縁膜6sを貫通させず、コンタクトホール8Hの底部8Bの下層において、ストッパ絶縁膜6sの一部を残存膜として残している。これにより、図5に示す第2マスク除去工程において、アッシング処理や洗浄処理を行う際に、下地層である配線層M2の導体膜7が汚染されることを抑制することができる。また、図5に示すコンタクトホール貫通工程で、確実にストッパ絶縁膜6sの残存膜を取り除く観点からは、残存膜の厚さは薄くすることが好ましい。例えば、本実施の形態では、ストッパ絶縁膜6sの残存膜が数nm〜20nm程度の範囲に収まるように制御している。残存膜の厚さの制御は、例えばエッチング処理の処理時間により制御することができる。しかし、本実施の形態のように、ストッパ絶縁膜6sの残存膜が数nm〜20nm程度の範囲に収まるように制御する場合には、エッチング処理の処理時間のみの制御では、ストッパ絶縁膜6sが貫通してしまうという問題が発生する。そこで、本実施の形態では、図5に示すように配線溝形成工程の後に残存膜検査工程を行い、残存膜の有無、あるいは残存膜の膜厚を検査している。この残存膜検査工程の結果を製造工程にフィードバックすることで、ストッパ絶縁膜6sの残存膜の厚さを高精度で制御することができる。例えば、ストッパ絶縁膜6sが貫通してしまう貫通不良や残存膜の膜厚が許容範囲を超えてしまう不良が発生した場合には、残存膜検査工程によって、不良の発生を検出することができる。このため、不良が検出された時点で製造を停止すれば、不良品が大量に生産されてしまうロスを防止することができる。また、製造工程の各条件をチェックして、不良の発生原因を特定すれば、これを反映した条件に修正することができる。ストッパ絶縁膜6sが貫通してしまう貫通不良のみを検出する場合には、残存膜検査工程では、残存膜の有無のみを検出することができれば良いが、残存膜の膜厚が許容範囲を超えてしまう不良までを検出する場合には、残存膜の膜厚を検出することが必要となる。この残存膜検査工程での具体的な検査方法は、後述する。

【0033】

次に、第2マスク除去工程(アッシング工程)として、図11に示すレジスト膜22を取り除く。この時、下地層である配線層M2の導体膜7は、コンタクトホール8Hの底部8Bの下層に配置されるストッパ絶縁膜6sの残存膜に覆われているので、アッシング処理中の導体膜7の汚染を抑制することができる。また、アッシング処理を行った後、レジスト膜22の残渣を取り除く洗浄工程を行う場合もあるが、この場合にも、配線層M2の導体膜7は、コンタクトホール8Hの底部8Bの下層に配置されるストッパ絶縁膜6sの残存膜に覆われているので、洗浄処理中の導体膜7の汚染を抑制することができる。

【0034】

次に、コンタクトホール貫通工程として、図12に示すように、コンタクトホール8Hの下層のストッパ絶縁膜6sの残存膜を取り除く。本工程では、ストッパ絶縁膜6sの残存膜を取り除くことで、コンタクトホール8Hがストッパ絶縁膜6sを厚さ方向に貫通する。このため、コンタクトホール8Hの底部8Bにおいて、下地層である配線層M2の導体膜7がストッパ絶縁膜6sから露出する。ストッパ絶縁膜6sの残存膜を取り除く方法としては、エッチング処理により取り除くことができる。本工程では、エッチングマスクは形成していないが、シリコン窒化膜用のエッチング材を用いることで、ストッパ絶縁膜6sを選択的(優先的)に取り除くことができる。また、前記した配線溝形成工程で、ストッパ絶縁膜6sの残存膜の厚さを、例えば数nm〜20nm程度とすることにより、エッチング処理の処理時間を短くすることができる。

【0035】

次に導体膜形成工程として、図12に示すコンタクトホール8Hおよび配線溝8G内に導体膜を形成する。まず、図13に示すように、主導体膜の成分が絶縁膜6c中に拡散することを防止ないしは抑制するバリア導体膜7Bをコンタクトホール8Hおよび配線溝8G内に成膜(形成)する。バリア導体膜7Bは、例えば、タンタル(Ta)膜、窒化タンタル(TaN)膜あるいはこれらの積層膜などから成り、例えば10nm程度の膜厚で成膜される。バリア導体膜7Bは、例えば、スパッタリング法やCVD法などによって形成する。本工程では、絶縁膜6cの上面M3a上にマスクを配置せずに行うので、バリア導体膜7Bは、コンタクトホール8Hおよび配線溝8Gの内壁面および絶縁膜6cの上面M3a上に成膜される。次に、図14に示すようにバリア導体膜7B上に、主導体膜7Aを成膜(形成)し、コンタクトホール8Hおよび配線溝8Gに埋め込む。主導体膜7Aは、例えば銅(Cu)から成り、例えばスパッタリング法または電解めっき法などを用いて形成される。また、主導体膜7Aは、銅を主成分とする導体膜、例えば銅または銅合金(Cuを主成分とし、例えばMg、Ag、Pd、Ti、Ta、Al、Nb、ZrまたはZnなどを含む)により形成することができる。また、バリア導体膜7B上に、主導体膜よりも薄い銅(または銅合金)などからなるシード膜をスパッタリング法などによって形成し、そのシード膜上にシード膜よりも厚い銅(または銅合金)などからなる主導体膜7Aをめっき法などによって形成することができる。

【0036】

次に、平坦化工程として、絶縁膜6cの上面M3a側に平坦化処理を施す。バリア導体膜7Bおよび主導体膜7Aはコンタクトホール8Hおよび配線溝8Gから成る開口部8の形状に倣って形成されるため、その表面は図14に示すように凹凸面となっている。このため、例えばCMP法(メタルCMP法)により平坦化し、余分なバリア導体膜7Bおよび主導体膜7Aを取り除く。また、この平坦化工程において絶縁膜6cの上面M3a上に形成されたバリア導体膜7Bおよび主導体膜7Aが取り除かれる。

【0037】

そして、平坦化工程が完了すると、図15に示す配線層M3が形成される。配線層M3には、絶縁膜6および絶縁膜6を貫通する開口部8が形成され、開口部8内に導体膜7が埋め込まれている。詳しくは、導体膜7は、コンタクトホール8Hに埋め込まれ、下層の配線層M2の主導体膜7Aと接触(接合)するプラグ7Pと、プラグ7P上に配置されプラグ7Pと一体に形成される配線(埋め込み配線)7Lから成る。また、配線層M3の上面M3aは平坦化処理が施され、導体膜7が上面M3aの開口部8において、絶縁膜6から露出している。これにより配線層M3は、さらに上層に積層される配線層5の下地層となる。つまり、図3に示す配線層積層工程では、図5に示すストッパ膜形成工程から平坦化工程までを繰り返し行うことで、複数の配線層5を積層する。

【0038】

なお、本実施の形態では、絶縁膜6にコンタクトホール8Hおよびこれに接続される配線溝8Gを形成し、この開口部8内に導体膜7を埋め込む、所謂、デュアルダマシン方式により形成する配線層5について説明した。しかし、配線層5の形成方法は上記に限定されない。例えば、配線溝8Gを形成せず、コンタクトホール8H内に導体膜7を埋め込み、平坦化処理を行った後で、プラグ7P上に配線7Lを形成する方式に適用することができる。また例えば、配線溝8Gを形成する前に、コンタクトホール8H内に導体膜7を埋め込み、平坦化処理を行った後で、さらに絶縁膜6を積層し、積層した絶縁膜6に配線溝8Gおよび配線溝8Gに埋め込まれる配線7Lを形成する方式に適用することができる。

【0039】

<残存膜検査工程の詳細>

次に、図5に示す残存膜検査工程の詳細について説明する。本セクションでは、まず、本願発明者が検討した比較例について説明した後、本実施の形態の残存膜検査工程の内容について説明する。図28は、本実施の形態に対する第1の比較例である残存膜検査工程を模式的に示す説明図、図29は、本実施の形態に対する第2の比較例である残存膜検査工程を模式的に示す説明図である。

【0040】

図5に示す残存膜検査工程では、図11に示すようにコンタクトホール8Hの底部8Bの下層における数nm〜20nm程度の薄膜の有無あるいは膜厚を測定する。このような残存膜検査を効率的に行う観点から、非接触方式の検査を行うことが好ましい。そこで、本願発明者は、非接触方式の検査方法として、図28に示すように光学干渉を利用した膜厚測定方法について検討した。光学干渉を利用した膜厚測定方法では、まず、図28に示すように下地膜100と下地膜100上に積層された被測定膜101を備える被検査対象物に対して照射光L1を照射する。照射光L1の一部は、被測定膜101の表面で反射され、反射光L2が発生する。また、照射光L1の別の一部は、被測定膜101を透過して下地膜100の表面(すなわち、被測定膜の裏面)で反射され、反射光L3が発生する。この反射光L2と反射光L3には、被測定膜の膜厚に対応して位相差が生じる。そこで、図28に示す膜厚測定方法は、被測定膜101上に位相検出器102を配置し、位相検出器102により反射光L2、L3の位相差を検出して、該位相差から被測定膜101の膜厚を算出するものである。ところが、このような光学干渉を利用した膜厚測定方法を適用する場合には、照射光L1を照射する領域が数十〜数百μm2程度の平坦面となっている必要がある。一方、図11に示すコンタクトホール8Hの底部8Bの平面寸法は、例えば、1μm2よりも小さい微細なパターンである。このため、図28に示す光学干渉を利用した膜厚測定方法は、図5に示す残存膜検査工程としては適用することができない。

【0041】

次に、本願発明者は、別の非接触方式の検査方法として、図29に示すように被検査対象物に電子ビームEBを照射して、被測定膜から放出される二次電子を検出することにより被測定膜101の有無や膜厚を測定する方法について検討した。図29に示す方法では、被検査対象物に対して被測定膜101側から電子ビームEBを照射する。すると、被測定膜101から電子ビームEBにより励起された二次電子SE1が放出される。また、電子ビームEBの加速電圧を高くして電子ビームEBの強度(エネルギー強度)を高くすると、被測定膜101の下層の下地膜100からも電子ビームEBにより励起された二次電子SE2が放出される。そして被測定膜の上面側に放出された二次電子SE1、SE2を二次電子検出部103で検出する。ここで、被測定膜101を絶縁膜、下地膜100を金属などの導電膜とした場合、二次電子SE2の量は二次電子SE1の量よりも多くなる。このため、電子ビームEBの加速電圧を徐々に上昇させて電子ビームEBの強度を上昇させると、二次電子発生量に変化点が生じる。そして膜厚が既知である評価用の被測定膜101を用いて、二次電子発生量の変化点と電子ビームEBの強度の相関関係を予め調査すれば、この調査結果と比較することで、被測定膜101の膜厚を測定できる。ところが、本願発明者が図29に示す膜厚測定方法についてさらに検討を行った結果、以下の課題を見出した。

【0042】

まず、図11に示すコンタクトホール8Hの底部8Bの下層におけるストッパ絶縁膜6sの残存膜の測定に適用した場合、残存膜の測定精度が低下する、あるいは測定不可能になる。開口部8のアスペクト比が大きい場合、被測定膜101(図29参照)や下地膜100(図29参照)から放出される二次電子SE1、SE2(図29参照)が、配線溝8Gやコンタクトホール8Hの側壁(絶縁膜6c)に吸収され易くなる。この結果、二次電子SE1、SE2の検出量の低下により測定精度低下や測定不可能化の原因となる。また、二次電子SE1、SE2の信号強度を評価する方式では、絶縁膜6によるノイズの影響を受け易い。したがって、このノイズの影響により測定精度が低下し易い。また、開口部8のパターン形状によって二次電子SE1、SE2の信号強度が変化するので、膜厚が既知である評価用の被測定膜101を用いた調査結果との比較が困難である。また、被測定膜101とその下地膜100が、二次電子放出特性の近い材料(例えば、金属膜同士)で構成されている場合、被測定膜101とその下地膜100の二次電子放出量の差が明確にならず、測定精度低下や測定不可能化の原因となる。

【0043】

上記検討結果を踏まえ、本実施の形態の残存膜検査工程について説明する。図16は、図5に示す残存膜検査工程を模式的に示す説明図である。本実施の形態の残存膜検査工程では、まず、開口部8(詳しくはコンタクトホール8Hの底部8B)に向かって電子ビーム(励起線)EBを照射する。開口部8に電子ビームEBを照射すると、被測定膜であるストッパ絶縁膜6sの残存膜からは、前記した第2の比較例で説明した二次電子の他、特性X線(例えば、図16でX−ray(Si)として模式的に示す特性X線)が放出される。また、電子ビームEBの強度を高くすると、下地膜である導体膜7も励起され、導体膜7から特性X線(例えば、図16でX−ray(Cu)として模式的に示す特性X線)が放出される。これらの特性X線は、励起された原子が電子を放出することにより生じた空孔に、電子が遷移する際に発生するX線である。このため、特性X線は、単一のエネルギー(線スペクトル)を有し、その値は電子を放出した元素毎に固有の値となっている(固有X線とも呼ばれる)。例えば、ストッパ絶縁膜6sからは、シリコン(Si)元素、酸素(O)元素、炭素(C)元素および窒素(N)元素の特性X線がそれぞれ放出される。また、例えば銅(Cu)からなる主導体膜7Aからは、銅(Cu)元素の特性X線が放出される。なお、主導体膜7Aからは、主導体膜7A中に拡散したシリコン成分からシリコン(Si)元素の特性X線も放出される場合もある。本実施の形態では、この特性X線を検出し、残存膜の有無あるいは残存膜の膜厚を判定(評価)する。詳しくは、配線層M3の上面M3a側に配置されるX線検出部31により、被測定膜および下地膜から放出される特性X線に含まれる複数の元素成分を検出する。例えば、ストッパ絶縁膜6sからは、主たる元素成分としてシリコン(Si)元素成分が検出され、主導体膜7Aからは、主たる元素成分として銅(Cu)元素成分が検出される。そして、これら複数種類の元素成分の比率により、被測定膜の有無または膜厚を判定(評価)する。例えば、銅(Cu)元素成分とシリコン(Si)元素成分を比較して、その成分比率(銅(Cu)元素成分/シリコン(Si)元素成分)により、ストッパ絶縁膜6sの残存膜の有無または膜厚を判定(評価)する。以下、評価方法について説明する。

【0044】

図17は、図16に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Cu/Si)の関係を示す説明図である。また、図18は、図16に示す開口部に照射する電子ビームの強度(加速電圧)毎に、残存膜の膜厚と成分比率(Cu/Si)の関係を示す説明図である。なお、図17および図18では、図16に示すストッパ絶縁膜6sの膜厚が既知の複数種類のサンプルを作成し、この複数種類のサンプルに対して電子ビームEB(図16参照)を照射して特性X線の成分比率と励起線の強度の相関を測定した結果を示している。分光分析の方式は、エネルギー分散型分光分析法と、波長分散型分光分析法に大別される。エネルギー分散型分光分析法では、EDS(Energy Dispersive X-ray Spectroscopy)と呼ばれるエネルギー分散型分光器を用いて分析を行う。また、波長分散型分光分析法では、WDS(Wavelength Dispersive X-ray Spectrometry)と呼ばれる波長分散型分光器を用いて分析を行う。波長分散型分光分析法は、エネルギー分散型分光分析法よりも分解能を高くし易いという利点があるが、検査装置の構造を単純化する観点からは、エネルギー分散型分光分析法の方が好ましい。

【0045】

まず、特性X線の放出量は、励起線である電子ビームEB(図16参照)の強度により変化するので、適正な電子ビームEB(図16参照)強度(電子の加速電圧)について検討した結果を図17に示す。成分比率により残存膜の有無を判定するためには、残存膜の有無によって、成分比率の測定結果が大きく異なるような励起線強度が好ましい。ここで、図17に示すように、電子ビームEB(図16参照)の加速電圧が2.5V以上4.0V以下の範囲では、残存膜が無い(膜厚=0.0nm)場合と残存膜が有る(膜厚=17.8nm)場合では、成分比率(Cu/Si)に10%以上の差がある。そして電子ビームEB(図16参照)の加速電圧を、さらに上昇させると、残存膜の有無による成分比率(Cu/Si)の差は小さくなる。一方、電子ビームEB(図16参照)の加速電圧が2.5Vよりも小さくなると、残存膜が有る(膜厚=17.8nm)場合において、下地層から放出される特性X線である銅(Cu)成分が小さくなる。これは、電子ビームEB(図16参照)の強度が小さくなることにより、下地層である導体膜7が励起され難くなるからである。したがって、図17に示す結果から、電子ビームEB(図16参照)の加速電圧が2.5V以上4.0V以下とすることが特に好ましい。

【0046】

次に、残存膜の膜厚と成分比率(Cu/Si)の関係について検討した結果を図18に示す。図18では、電子ビームEB(図16参照)の加速電圧がそれぞれ、2.5kVの場合、3.0kVの場合および4.0kVの場合について示している。図18に示すように、残存膜の膜厚が、0.0nm〜約18.0nmの範囲において、残存膜の膜厚と成分比率(Cu/Si)は、反比例の関係があることが判る。すなわち、残存膜の膜厚の上昇に伴って、成分比率(Cu/Si)は減少する。したがって、例えば2.5kV〜4.0kVのうちの任意の加速電圧で加速した電子ビームEB(図16参照)を図16に示す開口部8に照射し、検出された特性X線の成分比率と図18に示すように既知の膜厚の残存膜に励起線を照射して得られた相関関係データを比較することで、残存膜の膜厚を算出(判定)することができる。つまり、検出された特性X線に含まれる複数種類の元素成分の比率により、残存膜の有無または膜厚を判定(評価)することができる。

【0047】

次に、本実施の形態の残存膜検査工程に用いる残存膜検査装置の構成について説明する。図19は残存膜検査装置の概要構成を示す説明図である。図19に示す検査装置(残存膜検査装置)30は、励起線である電子ビームEBを照射する励起線照射部32、および被検査対象であるウエハWHを固定する基板固定部33を有している。また、検査装置30はウエハWHから放出された特性X線を検出する検出部31、および検出された信号データから残存膜の有無あるいは膜厚を判定する判定部34を有している。また、検査装置30は、励起線照射部32、基板固定部33、検出部31、および判定部34の動作(機械的動作または電気的動作)を制御する制御部35を有している。

【0048】

励起線照射部32は、例えば励起線である電子ビームEBを発生させる電子銃、およびウエハWHの検査対象となる開口部8(図16参照)の底部8B(図16参照)に向かって電子ビームEBを収束させて照射するレンズなどを備え、ウエハWHの主面上(検査対象である開口部上)に配置される。また、励起線照射部32は制御部35と電気的に接続され、電子銃から発射された電子ビームEBは、制御部35からの制御信号によって所定の加速電圧(例えば2.5V〜4.0Vのうちの任意の加速電圧)で加速され、ウエハWHの主面側の開口部8(図16参照)に照射される。また、検出部31は、判定部34および制御部35と電気的に接続される検出器を備え、ウエハWHの主面上(検査対象である開口部上)に配置される。検出部31で検出された複数種類の特性X線の検出信号は、判定部34が備える判定回路34aに伝送される。特性X線の検出信号は、特性X線の元素成分毎に分光され、判定回路34aに伝送される。例えば、エネルギー分散型の分光分析を行う検出部31では、特性X線のエネルギー毎に分光された検出信号が伝送される。また、波長分散型の分光分析を行う検出部31では、特性X線の波長毎に分光された検出信号が伝送される。

【0049】

判定部34の判定回路34aでは、元素成分毎の特性X線の検出信号について処理(統計処理)を行い、被測定膜に含まれる第1の元素成分の検出信号と、下地層に含まれる第2の元素成分の検出信号の比率(成分比率データ)を算出する。また、判定部34は、判定用データを保持するデータ保持部34bを備えている。この判定用データは、例えば、図18を用いて説明したように、既知の膜厚の残存膜に励起線を照射して得られた相関関係データ、あるいは、この相関関係データに基いて設定された閾値データである。この判定用データは、データ保持部34bから判定回路34aに伝送され、判定回路34aにおいて、成分比率の測定データと判定用データを比較することにより、残存膜の有無または膜厚を判定(評価)する。

【0050】

このように本実施の形態によれば、被測定膜および下地膜から照射される特性X線を検出することにより、残存膜の有無または膜厚を判定する。特性X線は二次電子よりも開口部8周囲の側壁に吸収され難い。このため、スルーホールなどのアスペクト比が高い開口部8の底部における残存膜を検査する場合であっても、特性X線を検出することができる。また、本実施の形態では、検出した特性X線の絶対値ではなく、特性X線に含まれる複数の元素成分の比率により残存膜の有無または膜厚を判定する。したがって、測定対象となる開口部8の周辺パターンの影響、あるいは、絶縁膜6cからのノイズの影響により、信号強度が変化した場合であっても、測定精度の低下を抑制することができる。また、本実施の形態では、被測定膜が絶縁膜(ストッパ絶縁膜6s)、下地膜が導体膜(主導体膜7A)である場合について説明したが、特性X線を検出する方式で検査可能な被測定膜と下地膜の構成はこれに限定されない。例えば、被測定膜および下地膜の双方が構成成分の異なる絶縁膜あるいは導体膜である場合にも適用することができる。各膜の構成成分が異なれば、絶縁膜同士あるいは導体膜同士であっても異なる成分の特性X線の比率を測定できるからである。

【0051】

なお、図17および図18において、残存膜の膜厚が0.0nmの時にもシリコン(Si)元素成分の特性X線が検出されているが、これは、主導体膜7A(図16参照)中に拡散したシリコン成分からシリコン(Si)元素の特性X線が放出されるためである。しかし、本実施の形態では、特性X線の成分比率により残存膜の有無、あるいは膜厚を判定するので、下地膜からシリコン(Si)元素の特性X線が放出されても、判定精度の低下を抑制することができる。例えば、図18において、残存膜の膜厚が0.0nmの時は、成分比率(Cu/Si)はいずれも80%以上(詳しくは83%以上)である。一方、残存膜の膜厚が12.1nmの時は、成分比率(Cu/Si)はいずれも80%未満である。したがって、例えば成分比率(Cu/Si)が83%未満であることを閾値として管理すれば、開口部8の底部における残存膜の有無を検査することができる。また例えば、開口部8の深度についてウエハ面内でのばらつきを考慮した場合、例えば、成分比率(Cu/Si)が80%未満であることを閾値として管理すれば、ウエハ面内の全ての開口部8において、残存膜が残っていると推定することができる。

【0052】

<残存膜検査工程の好ましい態様>

次に、上記で説明した残存膜検査工程の好ましい態様について説明する。図20は、図5に示す残存膜検査工程において、残存膜を検査する開口部の位置の例を示す平面図である。また、図21は、図20のA部の拡大平面図である。なお、図20に示すウエハWHには、多数の開口部8が形成されているが、検査位置を解り易くしめすため、多数の開口部8のうち、検査対象となる開口部8aを含む一部の開口部8のみ示している。ウエハWHには、各チップ領域10a(図4参照)に、それぞれ多数の開口部8が形成される。残存膜検査工程において、全ての開口部8について検査することもできるが、この場合、検査時間が増大し、製造効率低下の原因となる。そこで、本実施の形態では、複数の開口部8のうちの一部の開口部8aについて検査を行う。ウエハWHに一括して開口部8を形成する場合には、処理時間を管理することにより、複数の開口部8の深度は略同程度に揃えることができる。したがって、図20に示すように、互いに離間した任意の複数箇所(図20では3箇所)の開口部8aで残存膜の有無または膜厚を判定(評価)すれば、電子ビームEB(図16参照)を照射しないその他の開口部8bにおける残存膜の有無も推定することができる。例えば、ウエハWHの面内における開口部8の深度のばらつきを考慮して、例えば、全ての開口部8aにおいて残存膜の膜厚が10nm以上あれば他の開口部8bにおいても残存膜が残っていると推定することができる。この場合、開口部8bについて検査を行わないので、検査時間を大幅に短縮することができる。つまり、残存膜検査工程を効率化することができる。

【0053】

また、本実施の形態の残存膜検査工程は非破壊検査であるが、電子ビームEB(図16参照)を照射することにより、開口部8周辺の電気的特性が損なわれることを防止する観点からは、製品となるチップ領域10a(図4参照)に形成された開口部8b(図20参照)には電子ビームEB(図16参照)を照射しないことが好ましい。このため、本実施の形態では、図21に示すように、チップ領域10aの間に配置されるスクライブ領域10bに、チップ領域10a内と同様のプロセスで検査用の開口部8aを形成し、開口部8aに対して電子ビームEB(図16参照)を照射する。このような検査用のパターンは、TEG(Test Elementary Group)と呼ばれ、TEGに対して検査を行うことで、チップ領域10a内に形成されたパターンの状態を推定することができる。このスクライブ領域10bは、図3に示す個片化工程において切削加工する領域なので、製品である半導体装置1(図1参照)には、TEGのパターンは残らない。したがって、例えばスクライブ領域10bに形成された検査用の開口部8aの底部8Bに電子ビームEB(図16参照)を照射しても、これにより製品の電気的特性が損なわれることを防止できる。

【0054】

また、本実施の形態では、被測定膜および下地膜を励起する励起線として電子ビームEB(図16参照)を用いた例について説明したが、特性X線を発生させるために必要なエネルギーを有する励起源であれば電子ビームEB(図16参照)に代えてこれを用いることができる。例えば、励起線として、X線を用いることができる。この場合、開口部8の周辺に励起線が照射されてノイズが増大することを抑制する観点から、X線の照射口周辺に遮蔽板を設け、遮蔽板の開口部からX線を照射することが好ましい。ただし、励起線としては、電子ビームEB(図16参照)の方がX線よりも収束させ易いので、本実施の形態のように、スルーホールなどのアスペクト比の高い開口部8の底部8Bに照射する場合には、励起線として電子ビームEB(図16参照)を用いることが特に好ましい。

【0055】

<コンタクト層形成工程への適用>

次に、前記した残存膜検査工程の変形例として、図3に示すコンタクト層形成工程に適用した例について説明する。図22は、図3に示す配線層積層工程のプロセスフローを示す説明図である。また、図23は、図22に示すコンタクトホール貫通工程が完了した状態を示す拡大断面図である。また、図24は、図23のB部において、残存膜検査工程を行った状態を模式的に示す説明図である。また、図25は、図24に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Co/Si)の関係を示す説明図である。なお、図24および図25では、金属シリサイド膜として、コバルトシリサイド膜を形成した場合の例を示している。

【0056】

図3に示すコンタクト層形成工程では、まず、下地層準備工程として、配線層の下地となる層を形成する。コンタクト層形成工程に適用する場合には、ゲート電極3およびソース、ドレイン領域4の表面に形成された金属シリサイド膜9が、下地層となる。この金属シリサイド膜9は、ゲート電極3およびソース、ドレイン領域4の表面に、例えばコバルト(Co)膜やニッケル(Ni)膜などの金属膜を形成し、熱処理(アニール処理)を施すことで、金属膜とシリコンを反応させてシリサイド化することにより形成される。次に、ストッパ膜形成工程として、ストッパ絶縁膜(被測定膜)6sを成膜(形成)する。ストッパ絶縁膜6sは、例えば窒化シリコン膜(SiN膜)であって、例えば、CVD法により、例えば30nm〜50nm程度の厚さで形成される。本工程により、下地膜である金属シリサイド膜9は、ストッパ絶縁膜6sにより被覆される。

【0057】

次に主絶縁膜形成工程として、ストッパ絶縁膜6s上に、主層間絶縁膜である絶縁膜6aを成膜(形成)する。絶縁膜6aは、例えば、オゾン(O3)およびTEOS(Tetra-Ethyl-Ortho-Silicate)を用いた熱CVDによる酸化シリコン膜であるオゾンTEOS膜と、TEOSを用いたプラズマCVDによる酸化シリコン膜であるプラズマTEOS膜を積層して形成する。次に、マスク配置工程として、絶縁膜6aの上面PMa上にレジスト膜(図示は省略)を配置する。コンタクト層形成工程では、ゲート電極3表面の金属シリサイド膜9とゲート電極3およびソース、ドレイン領域4表面の金属シリサイド膜9の高さが異なるため、コンタクトホール8Hの高さが異なる。このため、コンタクトホール形成工程で、過剰にエッチングされることを抑制する観点から、ゲート電極3上のコンタクトホール8Hと、ソース、ドレイン領域4上のコンタクトホール8Hは、それぞれ別のレジスト膜(マスク)を用いて形成する。次に、コンタクトホール形成工程として、絶縁膜6aの上面PMa側から下地膜である金属シリサイド膜に向かって絶縁膜6aを取り除き、コンタクトホール(開口部、孔)8Hを形成する。絶縁膜6aを取り除く方法は、例えば、レジスト膜(図示は省略)をエッチングマスクとしてエッチング処理を行い、コンタクトホール8Hを形成する。エッチング方式は、ドライエッチング方式、ウェットエッチング方式、またはこれらを組み合わせて行う方式を用いることができる。この時、前記した配線層積層工程と同様に、シリコン酸化膜用のエッチング材を用いることにより、ストッパ絶縁膜6sがエッチングにより貫通してしまうことを抑制できる。しかし、シリコン酸化膜用のエッチング材を用いた場合であっても、ストッパ絶縁膜6sの一部はエッチングにより取り除かれる。また、ゲート電極3上のコンタクトホール8Hと、ソース、ドレイン領域4上のコンタクトホール8Hは、それぞれ別のレジスト膜(マスク)を用いて形成する。このため、一方のコンタクトホール8Hを形成した後でアッシング工程や洗浄工程を行い、レジスト膜を取り除いた後で、他方のコンタクトホール8Hを形成するためのレジスト膜を配置する。この時、ストッパ絶縁膜6sの一部は、コンタクトホール8Hの底部において残存膜として残っているので、アッシング処理中あるいは洗浄処理中の金属シリサイド膜9の汚染を抑制することができる。

【0058】

次に、コンタクトホール貫通工程として、図23に示すように、コンタクトホール8Hの下層のストッパ絶縁膜6sの残存膜を取り除く。本工程では、複数のコンタクトホール8H上にそれぞれ貫通孔23aが形成されたレジスト膜23をエッチングマスクとしたエッチング処理によりストッパ絶縁膜6sの残存膜を取り除く。これにより、コンタクトホール8Hがストッパ絶縁膜6sを厚さ方向に貫通する。そして、コンタクトホール8Hの底部において、下地膜である金属シリサイド膜9がストッパ絶縁膜6sから露出する。ここで、金属シリサイド膜9は、配線層積層工程で説明した導体膜7と比較して薄く、例えば、数nm〜数十nmであるため、エッチング時間を長くすると、金属シリサイド膜9をエッチングにより貫通してしまう。一方、エッチング時間が不足するとストッパ絶縁膜6sを貫通せず、導通不良(オープン不良)の原因となる。したがって、コンタクトホール8Hの深さを精密に制御する技術が必要となる。

【0059】

そこで、本実施の形態では、図22に示すように、コンタクトホール貫通工程の後で残存膜検査工程を行い、残存膜が取り除かれ、かつ金属シリサイド膜9が残っていることを検査する。図22に示すストッパ絶縁膜6sの残存膜の検査には、前記した配線層積層工程における残存膜検査工程を応用して適用することができる。すなわち、図24に示すように、コンタクトホール8Hの底部8Bに向かって、例えば電子ビーム(励起線)EBを照射することにより放出された特性X線を検出し、ストッパ絶縁膜6sの有無あるいは下地層である金属シリサイド膜9の有無を判定(評価)する。具体的には、複数成分の特性X線のうち、金属シリサイド膜に含まれる金属元素(例えばコバルト)成分と、ストッパ絶縁膜6sに主成分として含まれる半導体元素成分(例えばシリコン)の成分比率(Co/Si)により判定(評価)する。

【0060】

ここで、コンタクトホールに照射する電子ビームEB(図24参照)の強度(加速電圧)を変化させた場合の成分比率(Co/Si)の関係は図25に示すように変化する。まず、図23に示すように、コンタクトホール8Hがストッパ絶縁膜6sを貫通し、かつ、下地膜である金属シリサイド膜9を貫通していない場合には、図25に示すデータD1のように変化する。すなわち、電子ビームEB(図24参照)の加速電圧(励起線の強度)が低い領域では、金属シリサイド膜9が主に励起されるためコバルト元素に由来する特性X線成分の比率が高くなる。一方、電子ビームEB(図24参照)の加速電圧が上昇すると、金属シリサイド膜9よりもさらに下層の下地層(ウェル領域12)が励起されるので、シリコン元素に由来する特性X線成分の比率が上昇し、この結果、成分比率(Co/Si)は減少する。

【0061】

また、図23に示すコンタクトホール8Hがストッパ絶縁膜6sを貫通せず、ストッパ絶縁膜6sの残存膜が残っている場合には、図25に示すデータD2のように変化する。すなわち、電子ビームEB(図24参照)の加速電圧(励起線の強度)が低い領域では、ストッパ絶縁膜6sが主に励起されるため、コバルト元素に由来する特性X線成分の比率は低い。また、電子ビームEB(図24参照)の加速電圧が上昇すると、残存膜の下層の金属シリサイド膜9が励起されるため、コバルト元素に由来する特性X線成分の比率が上昇し、この結果、成分比率(Co/Si)は増加する。また、電子ビームEB(図24参照)の加速電圧がさらに上昇すると、金属シリサイド膜9よりもさらに下層のウェル領域12が励起されるので、シリコン元素に由来する特性X線成分の比率が上昇し、この結果、成分比率(Co/Si)は減少する。

【0062】

また、図23に示すコンタクトホール8Hが、下地膜である金属シリサイド膜9を貫通した場合には、図25に示すデータD3のように変化する。すなわち、電子ビームEB(図24参照)の加速電圧(励起線の強度)が低い領域では、ウェル領域12中に拡散した、僅かなコバルト成分を除き、コバルト元素に由来する特性X線は殆ど検出されない。また、電子ビームEB(図24参照)の加速電圧を上昇させてもコバルト成分は増加しないため、成分比率(Co/Si)は、電子ビームEB(図24参照)の加速電圧によらず低い。言い換えれば、金属シリサイド膜9を被測定膜とし、ウェル領域12を下地膜として測定していることになる。

【0063】

図25に示す成分比率(Co/Si)と電子ビームEB(図24参照)の加速電圧(励起線の強度)の相関関係から、ストッパ絶縁膜6sの有無あるいは下地層である金属シリサイド膜9の有無を容易に判定(評価)することができる。すなわち、例えば、1kV〜2kV程度の低い加速電圧の電子ビームEB(図24参照)(低強度の励起線)を照射すると、データD2、D3の場合には、データD1よりも成分比率(Co/Si)が極端に小さくなる。したがって、成分比率(Co/Si)が閾値よりも低ければ、ストッパ絶縁膜6sの除去不良、あるいは金属シリサイド膜9の貫通不良のいずれかが発生していることが判る。この時点で、製造工程にフィードバックすれば、不良品が大量に生産されてしまうロスを防止することができる。また、例えば、2kV〜4kV程度の加速電圧で電子ビームEB(図24参照)を照射すれば、データD2とデータD3の分類ができる。つまり、不良の内容を把握することができるので、不良の発生原因が特定し易くなる。なお、コンタクト層形成工程に残存膜検査工程を適用する場合にも、前記した図19に示す検査装置30を用いることができるので、重複する説明は省略する。

【0064】

このように、本実施の形態によれば、前記配線層積層工程で説明したように、残存膜が残っていることを確認するための検査の他、残存膜が残っていないことを確認するための検査、あるいは、下地膜を貫通していないことを確認するための検査として残存膜検査工程を適用することができる。なお、本実施の形態では、配線層積層工程において、残存膜が残っていることを確認するための検査に適用した例について説明した。また、コンタクト層形成工程において、残存膜が残っていないことを確認するための検査、あるいは、下地膜を貫通していないことを確認するための検査に適用した例について説明した。しかし、これらは互いに組み合わせて適用することができる。例えば、図5に示すコンタクトホール貫通工程の後で、残存膜が残っていないことを確認するための検査、あるいは、下地膜を貫通していないことを確認するための検査として残存膜検査工程を適用することができる。また、例えば、図22に示すコンタクトホール形成工程と、コンタクトホール貫通工程の間で、残存膜が残っていることを確認するための検査として残存膜検査工程を適用することができる。

【0065】

次に、図22に示す導体膜形成工程として、コンタクトホール8H内に導体膜を埋め込んで図2に示すプラグ7aを形成する。

【0066】

本工程では、まず、絶縁膜6aの上面PMa(図23参照)、およびコンタクトホール8Hの内面に、バリア導体膜として、例えば、チタン膜および窒化チタン膜を順次成膜する。バリア導体膜は、例えば、TiCl4をメタルソースガスとして用いたメタルCVD処理により、形成することができる。なお、バリア導体膜の形成方法については、被覆性等の問題がないのであれば、メタルCVD処理のほか、スパッタリング成膜、またはメタルCVD処理とスパッタリング成膜の組み合わせ等の方法が適用できる。次に、コンタクトホール8H内のバリア導体膜上に、主導体膜であるタングステン膜を形成する。タングステン膜は、例えば、WF6をメタルソースガスとして用いたメタルCVD処理により、コンタクトホール8Hを埋め込むように形成する。次に、平坦化工程として、メタルCMPにより、平坦化処理を施し、コンタクトホール8H外部のタングステン膜およびバリア導体膜を除去する。以上の工程により、図2に示すように、プリメタル層間絶縁膜の上面に、ゲート電極3あるいはソース、ドレイン領域4と電気的に接続されるプラグ7aが露出されたコンタクト層である配線層PMが形成される。この配線層PMは、配線層M1を形成する際の下地層となり、図3に示す配線層積層工程で配線層PM上に複数の配線層5が積層される。

【0067】

<変形例>

次に、本実施の形態の変形例について説明する。前記配線層形成工程および前記コンタクト層形成工程では、ストッパ絶縁膜6sを被測定膜とし、導体膜7または、金属シリサイド膜9を下地膜とする例について説明した。しかし、本実施の形態の残存膜検査工程における被測定膜と下地膜の組み合わせは上記に限定されない。例えば、被測定膜および下地膜が導体膜である場合、あるいは被測定膜および下地膜が絶縁膜である場合であっても、被測定膜と下地膜のそれぞれから異なる元素成分の特性X線が検出できれば適用することができる。一例として、本変形例では、被測定膜および下地膜が導体膜である場合について説明する。図26は、図16に示す残存膜検査工程の変形例を模式的に示す説明図である。また、図27は、図26に示す開口部に照射する電子ビームの強度(加速電圧)を変化させた場合の残存膜の有無と成分比率(Ti/Al)の関係を示す説明図である。

【0068】

図26に示す配線層5では、例えばアルミニウム(Al)から成る主導体膜7Cの上面および下面にそれぞれ、例えば窒化チタン(TiN)からなり、主導体膜7Cよりも薄いバリア導体膜7Dが成膜され、導体膜7を構成する。導体膜7上には、絶縁膜6が積層され、絶縁膜6の上面側から導体膜7に向かってコンタクトホール8Hが形成されている。このコンタクトホール8H内にプラグとなる導体膜(図示は省略)を埋め込むことで、配線層5と、配線層5の上層に積層される配線層を電気的に接続する層間導電路が形成される。このため、コンタクトホール8Hを形成する工程では、コンタクトホール8Hの底部8Bにおいて、導体膜7を確実に露出させる必要がある。一方、コンタクトホール8Hがバリア導体膜7Dを貫通すると、主導体膜7Cが露出してしまうため、コンタクトホール8Hの底部8Bに、バリア導体膜7Dの一部を残存させる必要がある。

【0069】

このように導体膜7を確実に露出させ、かつ、薄いバリア導体膜7Dの一部を残存させるため、前記した残存膜検査工程を応用して適用することができる。すなわち、コンタクトホール8Hを形成した後で、バリア導体膜7Dを被測定膜、主導体膜7Cを下地膜として残存膜検査工程を適用する。例えば、複数成分の特性X線のうち、バリア導体膜7Dに主成分として含まれる金属元素(例えばチタン)成分と、主導体膜7Cに主成分として含まれる金属元素成分(例えばアルミニウム)の成分比率(Ti/Al)により判定(評価)する。

【0070】

ここで、コンタクトホールに照射する電子ビームEB(図26参照)の強度(加速電圧)を変化させた場合の成分比率(Ti/Al)の関係は図27に示すように変化する。まず、図26に示すように、コンタクトホール8Hが絶縁膜6を貫通し、かつ、バリア導体膜7Dを貫通していない場合には、図27に示すデータD4のように変化する。すなわち、電子ビームEB(図26参照)の加速電圧(励起線の強度)が低い領域では、バリア導体膜7Dが主に励起されるためチタン元素に由来する特性X線成分の比率が高くなる。一方、電子ビームEB(図26参照)の加速電圧が上昇すると、バリア導体膜7Dの下地層である主導体膜7Cが励起されるので、アルミニウム元素に由来する特性X線成分の比率が上昇し、この結果、成分比率(Ti/Al)は減少する。

【0071】

また、図26に示すコンタクトホール8Hが絶縁膜6を貫通せず、バリア導体膜7Dが露出していない場合には、図27に示すデータD5のように変化する。すなわち、電子ビームEB(図26参照)の加速電圧(励起線の強度)が低い領域では、絶縁膜6が主に励起されるため、チタン元素やアルミニウム元素に由来する特性X線成分は殆ど検出されない。また、電子ビームEB(図26参照)の加速電圧が上昇すると、チタン元素に由来する特性X線成分の比率が上昇し、成分比率(Ti/Al)は増加する。また、電子ビームEB(図26参照)の加速電圧がさらに上昇すると、バリア導体膜7Dの下地層である主導体膜7Cが励起されるので、アルミニウム元素に由来する特性X線成分の比率が上昇し、この結果、成分比率(Ti/Al)は減少する。

【0072】

また、図26に示すコンタクトホール8Hが、バリア導体膜7Dを貫通した場合には、図27に示すデータD6のように変化する。すなわち、チタン元素に由来する特性X線は、電子ビームEB(図26参照)の加速電圧によらず、殆ど検出されない。このため、成分比率(Ti/Al)は、電子ビームEB(図26参照)の加速電圧によらず低い。

【0073】

つまり、図27に示す成分比率(Ti/Al)と電子ビームEB(図26参照)の加速電圧(励起線の強度)の相関関係から、絶縁膜6の残存膜の有無あるいはバリア導体膜7Dの有無を容易に判定(評価)することができる。すなわち、例えば、1kV〜2kV程度の低い加速電圧の電子ビームEB(図26参照)(低強度の励起線)を照射すると、データD5、D6の場合には、データD4よりも成分比率(Ti/Al)が極端に小さくなる。したがって、成分比率(Ti/Al)が閾値よりも低ければ、絶縁膜6の除去不良、あるいはバリア導体膜7Dの貫通不良のいずれかが発生していることが判る。この時点で、製造工程にフィードバックすれば、不良品が大量に生産されてしまうロスを防止することができる。また、例えば、2kV〜4kV程度の加速電圧で電子ビームEB(図26参照)を照射すれば、データD5とデータD6の分類ができる。つまり、不良の内容を把握することができるので、不良の発生原因が特定し易くなる。なお、コンタクト層形成工程に残存膜検査工程を適用する場合にも、前記した図19に示す検査装置30を用いることができるので、重複する説明は省略する。

【0074】

このように、本変形例によれば、特性X線を検出する方式を採用することで、被測定膜および下地膜がそれぞれ導体膜であっても、残存膜の有無、あるいは膜厚を容易に測定することができる。

【0075】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0076】

例えば、前記実施の形態では、予め判定用データを取得して、成分比率の測定データと判定用データを比較することにより、残存膜の有無あるいは膜厚を測定する方法について説明した。しかし、判定用データを予め準備しなくても残存膜の有無を判定することができる。例えば、図17、図25あるいは図27に示すように、残存膜の有無によって、特性X線の成分比率データが大きく変化する強度の励起線(例えば加速電圧が1kV〜2kV程度の電子線)を照射すれば、判定用データと比較しなくても、残存膜の有無を判定することができる。

【0077】

また、例えば、前記変形例では、被測定膜であるバリア導体膜7Dの有無を判定する例について説明したが、配線層積層工程で説明したように、バリア導体膜7Dの膜厚を判定することもできる。

【産業上の利用可能性】

【0078】

本発明は、半導体基板上に配線層を積層する半導体装置に利用可能である。

【符号の説明】

【0079】

1 半導体装置(半導体チップ)

1a 表面

2 半導体基板

2a 主面

3 ゲート電極

4 ソース、ドレイン領域(半導体領域)

5 配線層

6、6a、6b、6c、6d、6t 絶縁膜

6s ストッパ絶縁膜

7、7b、7c 導体膜

7A、7C 主導体膜

7B、7D バリア導体膜

7L 配線

7P、7a プラグ(コンタクトプラグ)

7t 配線

8 開口部

8B 底部

8G 配線溝

8H コンタクトホール

8a 開口部

8b 開口部

9 金属シリサイド膜

10a チップ領域

10b スクライブ領域

11 素子分離領域

12 ウェル領域

21、22、23 レジスト膜

21a、23a 貫通孔

22a 開口部

30 検査装置(残存膜検査装置)

31 検出部

32 励起線照射部

33 基板固定部

34 判定部

34a 判定回路

34b データ保持部

35 制御部

100 下地膜

101 被測定膜

102 位相検出器

103 二次電子検出部

D1、D2、D3、D4、D5、D6 データ

EB 電子ビーム(励起線)

FP パッシベーション膜

L1 照射光

L2、L3 反射光

PM、M1、M2、MX、MT 配線層

PMa、M2a、M3a 上面

PD パッド(電極)

Q1 半導体素子

SE1、SE2 二次電子

WH ウエハ(半導体基板)

【特許請求の範囲】

【請求項1】

(a)半導体基板の主面上に、下地膜および前記下地膜上の被測定膜を積層する工程、

(b)前記被測定膜に開口部を形成する工程、

(c)前記開口部の底部に励起線を照射して、特性X線を放出させる工程、

(d)前記特性X線を検出し、前記特性X線の検出結果に基いて前記開口部の底部における前記被測定膜の有無を判定する工程、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

請求項1において、

前記(c)工程で放出させる特性X線は、前記被測定膜を構成する第1の元素に由来する第1元素成分と、前記下地膜を構成する第2の元素に由来する第2元素成分を含み、

前記(d)工程では、前記特性X線のうち、前記第1元素成分と前記第2元素成分の成分比率により、前記被測定膜の有無を判定することを特徴とする半導体装置の製造方法。

【請求項3】

請求項2において、

前記(c)工程の前に、前記励起線の強度と前記成分比率の相関関係を測定し、判定用データを取得する工程をさらに有し、

前記(d)工程では、前記第1元素成分と前記第2元素成分の成分比率の測定データと、前記判定用データを比較することにより、前記被測定膜の有無を判定することを特徴とする半導体装置の製造方法。

【請求項4】

請求項3において、

前記(b)工程では、前記半導体基板の前記主面上に、複数の前記開口部を形成し、

前記(c)工程では、前記複数の開口部のうち、一または複数の第1開口部に前記励起線を照射し、前記複数の開口部のうち、前記第1開口部とは異なる第2開口部には前記励起線を照射しないことを特徴とする半導体装置の製造方法。

【請求項5】

請求項4において、

前記半導体基板は、前記主面上において、複数のチップ領域と、前記複数のチップ領域の間に配置されるスクライブ領域を有し、

前記一または複数の第1開口部は、前記スクライブ領域に形成され、複数の前記第2開口部は前記複数のチップ領域にそれぞれ形成されていることを特徴とする半導体装置の製造方法。

【請求項6】

請求項1において、

前記励起線は電子ビームであることを特徴とする半導体装置の製造方法。

【請求項7】

請求項1において、

前記開口部は、下層の配線と上層の配線を電気的に接続する導電経路となるコンタクトホールであることを特徴とする半導体装置の製造方法。

【請求項8】

請求項1において、

前記被測定膜は、第1の元素を含む導電膜であって、前記下地膜は、前記第1の元素とは異なる第2の元素を含む導電膜であることを特徴とする半導体装置の製造方法。

【請求項9】

請求項1において、

前記被測定膜は、第1の元素を含む絶縁膜であって、前記下地膜は、前記第1の元素とは異なる第2の元素を含む導電膜であることを特徴とする半導体装置の製造方法。

【請求項10】

請求項1において、

前記(b)工程では、前記被測定膜上に配置したレジスト膜をマスクとしたエッチング処理により、前記開口部を形成し、

前記(d)工程で、前記被測定膜が残存していることを確認した後、さらに、

(e)前記レジスト膜を除去する工程、を含んでいることを特徴とする半導体装置の製造方法。

【請求項11】

請求項1において、

前記(d)工程で、前記被測定膜が取り除かれ、前記下地膜が前記開口部の底部において露出していることを検査した後、さらに、

(e)前記開口部内に導体膜を形成する工程、を含んでいることを特徴とする半導体装置の製造方法。

【請求項12】

請求項11において、

前記(d)工程で、前記開口部が前記下地膜を貫通していないことをさらに検査することを特徴とする半導体装置の製造方法。

【請求項13】

(a)半導体基板の主面上に、下地膜および前記下地膜上の被測定膜を積層する工程、

(b)前記被測定膜に開口部を形成する工程、

(c)前記開口部の底部に励起線を照射して、特性X線を放出させる工程、

(d)前記特性X線を検出し、前記特性X線の検出結果に基いて前記開口部の底部における前記被測定膜の膜厚を判定する工程、

を含み、

前記(c)工程で放出させる特性X線は、前記被測定膜を構成する第1の元素に由来する第1元素成分と、前記下地膜を構成する第2の元素に由来する第2元素成分を含み、

前記(c)工程の前に、前記励起線の強度と前記第1元素成分と前記第2元素成分の成分比率の相関関係を測定し、判定用データを取得する工程をさらに有し、

前記(d)工程では、前記第1元素成分と前記第2元素成分の成分比率の測定データと、前記判定用データを比較することにより、前記被測定膜の膜厚を判定することを特徴とする半導体装置の製造方法。

【請求項14】

請求項13において、

前記(b)工程では、前記半導体基板の前記主面上に、複数の前記開口部を形成し、

前記(c)工程では、前記複数の開口部のうち、一または複数の第1開口部に前記励起線を照射し、前記複数の開口部のうち、前記第1開口部とは異なる第2開口部には前記励起線を照射しないことを特徴とする半導体装置の製造方法。

【請求項15】

請求項14において、

前記半導体基板は、前記主面上において、複数のチップ領域と、前記複数のチップ領域の間に配置されるスクライブ領域を有し、

前記一または複数の第1開口部は、前記スクライブ領域に形成され、複数の前記第2開口部は前記複数のチップ領域にそれぞれ形成されていることを特徴とする半導体装置の製造方法。

【請求項16】

請求項13において、

前記被測定膜は、前記第1の元素を含む導電膜であって、前記下地膜は、前記第1の元素とは異なる前記第2の元素を含む導電膜であることを特徴とする半導体装置の製造方法。

【請求項17】

請求項13において、

前記被測定膜は、第1の元素を含む絶縁膜であって、前記下地膜は、前記第1の元素とは異なる前記第2の元素を含む導電膜であることを特徴とする半導体装置の製造方法。

【請求項18】

請求項13において、

前記(b)工程では、前記被測定膜上に配置したレジスト膜をマスクとしたエッチング処理により、前記開口部を形成し、

前記(d)工程で、前記被測定膜が残存していることを確認した後、さらに、

(e)前記レジスト膜を除去する工程、を含んでいることを特徴とする半導体装置の製造方法。

【請求項19】

請求項13において、

前記(d)工程で、前記被測定膜が取り除かれ、前記下地膜が前記開口部の底部において露出していることを検査した後、さらに、

(e)前記開口部内に導体膜を形成する工程、を含んでいることを特徴とする半導体装置の製造方法。

【請求項20】

請求項13において、

前記(d)工程で、前記開口部が前記下地膜を貫通していないことをさらに検査することを特徴とする半導体装置の製造方法。

【請求項1】

(a)半導体基板の主面上に、下地膜および前記下地膜上の被測定膜を積層する工程、

(b)前記被測定膜に開口部を形成する工程、

(c)前記開口部の底部に励起線を照射して、特性X線を放出させる工程、

(d)前記特性X線を検出し、前記特性X線の検出結果に基いて前記開口部の底部における前記被測定膜の有無を判定する工程、

を含むことを特徴とする半導体装置の製造方法。

【請求項2】

請求項1において、

前記(c)工程で放出させる特性X線は、前記被測定膜を構成する第1の元素に由来する第1元素成分と、前記下地膜を構成する第2の元素に由来する第2元素成分を含み、

前記(d)工程では、前記特性X線のうち、前記第1元素成分と前記第2元素成分の成分比率により、前記被測定膜の有無を判定することを特徴とする半導体装置の製造方法。

【請求項3】

請求項2において、

前記(c)工程の前に、前記励起線の強度と前記成分比率の相関関係を測定し、判定用データを取得する工程をさらに有し、

前記(d)工程では、前記第1元素成分と前記第2元素成分の成分比率の測定データと、前記判定用データを比較することにより、前記被測定膜の有無を判定することを特徴とする半導体装置の製造方法。

【請求項4】

請求項3において、

前記(b)工程では、前記半導体基板の前記主面上に、複数の前記開口部を形成し、

前記(c)工程では、前記複数の開口部のうち、一または複数の第1開口部に前記励起線を照射し、前記複数の開口部のうち、前記第1開口部とは異なる第2開口部には前記励起線を照射しないことを特徴とする半導体装置の製造方法。

【請求項5】

請求項4において、

前記半導体基板は、前記主面上において、複数のチップ領域と、前記複数のチップ領域の間に配置されるスクライブ領域を有し、

前記一または複数の第1開口部は、前記スクライブ領域に形成され、複数の前記第2開口部は前記複数のチップ領域にそれぞれ形成されていることを特徴とする半導体装置の製造方法。

【請求項6】

請求項1において、

前記励起線は電子ビームであることを特徴とする半導体装置の製造方法。

【請求項7】

請求項1において、

前記開口部は、下層の配線と上層の配線を電気的に接続する導電経路となるコンタクトホールであることを特徴とする半導体装置の製造方法。

【請求項8】

請求項1において、

前記被測定膜は、第1の元素を含む導電膜であって、前記下地膜は、前記第1の元素とは異なる第2の元素を含む導電膜であることを特徴とする半導体装置の製造方法。

【請求項9】

請求項1において、

前記被測定膜は、第1の元素を含む絶縁膜であって、前記下地膜は、前記第1の元素とは異なる第2の元素を含む導電膜であることを特徴とする半導体装置の製造方法。

【請求項10】

請求項1において、

前記(b)工程では、前記被測定膜上に配置したレジスト膜をマスクとしたエッチング処理により、前記開口部を形成し、

前記(d)工程で、前記被測定膜が残存していることを確認した後、さらに、

(e)前記レジスト膜を除去する工程、を含んでいることを特徴とする半導体装置の製造方法。

【請求項11】

請求項1において、

前記(d)工程で、前記被測定膜が取り除かれ、前記下地膜が前記開口部の底部において露出していることを検査した後、さらに、

(e)前記開口部内に導体膜を形成する工程、を含んでいることを特徴とする半導体装置の製造方法。

【請求項12】

請求項11において、

前記(d)工程で、前記開口部が前記下地膜を貫通していないことをさらに検査することを特徴とする半導体装置の製造方法。

【請求項13】

(a)半導体基板の主面上に、下地膜および前記下地膜上の被測定膜を積層する工程、

(b)前記被測定膜に開口部を形成する工程、

(c)前記開口部の底部に励起線を照射して、特性X線を放出させる工程、

(d)前記特性X線を検出し、前記特性X線の検出結果に基いて前記開口部の底部における前記被測定膜の膜厚を判定する工程、

を含み、

前記(c)工程で放出させる特性X線は、前記被測定膜を構成する第1の元素に由来する第1元素成分と、前記下地膜を構成する第2の元素に由来する第2元素成分を含み、

前記(c)工程の前に、前記励起線の強度と前記第1元素成分と前記第2元素成分の成分比率の相関関係を測定し、判定用データを取得する工程をさらに有し、

前記(d)工程では、前記第1元素成分と前記第2元素成分の成分比率の測定データと、前記判定用データを比較することにより、前記被測定膜の膜厚を判定することを特徴とする半導体装置の製造方法。

【請求項14】

請求項13において、

前記(b)工程では、前記半導体基板の前記主面上に、複数の前記開口部を形成し、

前記(c)工程では、前記複数の開口部のうち、一または複数の第1開口部に前記励起線を照射し、前記複数の開口部のうち、前記第1開口部とは異なる第2開口部には前記励起線を照射しないことを特徴とする半導体装置の製造方法。

【請求項15】

請求項14において、

前記半導体基板は、前記主面上において、複数のチップ領域と、前記複数のチップ領域の間に配置されるスクライブ領域を有し、

前記一または複数の第1開口部は、前記スクライブ領域に形成され、複数の前記第2開口部は前記複数のチップ領域にそれぞれ形成されていることを特徴とする半導体装置の製造方法。

【請求項16】

請求項13において、

前記被測定膜は、前記第1の元素を含む導電膜であって、前記下地膜は、前記第1の元素とは異なる前記第2の元素を含む導電膜であることを特徴とする半導体装置の製造方法。

【請求項17】

請求項13において、

前記被測定膜は、第1の元素を含む絶縁膜であって、前記下地膜は、前記第1の元素とは異なる前記第2の元素を含む導電膜であることを特徴とする半導体装置の製造方法。

【請求項18】

請求項13において、

前記(b)工程では、前記被測定膜上に配置したレジスト膜をマスクとしたエッチング処理により、前記開口部を形成し、

前記(d)工程で、前記被測定膜が残存していることを確認した後、さらに、

(e)前記レジスト膜を除去する工程、を含んでいることを特徴とする半導体装置の製造方法。

【請求項19】

請求項13において、

前記(d)工程で、前記被測定膜が取り除かれ、前記下地膜が前記開口部の底部において露出していることを検査した後、さらに、

(e)前記開口部内に導体膜を形成する工程、を含んでいることを特徴とする半導体装置の製造方法。

【請求項20】

請求項13において、

前記(d)工程で、前記開口部が前記下地膜を貫通していないことをさらに検査することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【公開番号】特開2012−98113(P2012−98113A)

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願番号】特願2010−245160(P2010−245160)

【出願日】平成22年11月1日(2010.11.1)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願日】平成22年11月1日(2010.11.1)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]