半導体装置の製造方法

【課題】半導体チップの組立工程におけるハンドリング性を向上し、しかも、半導体チップの損傷を回避する半導体装置の製造方法を提供すること。

【解決手段】ダイシングライン16によって区画された複数の半導体チップ4を含む半導体ウエハ2を準備する第1の工程と、半導体ウエハ2に支持板13を付着する第2の工程と、半導体ウエハ2および支持板13をダイシングライン16に沿って切断し、半導体チップ4および分割された支持板13からなる積層体3を形成する第3の工程と、積層体3を配線基板18に搭載し、積層体3の半導体チップ4および配線基板18を電気的に接続する第4の工程とを有する半導体装置1の製造方法。

【解決手段】ダイシングライン16によって区画された複数の半導体チップ4を含む半導体ウエハ2を準備する第1の工程と、半導体ウエハ2に支持板13を付着する第2の工程と、半導体ウエハ2および支持板13をダイシングライン16に沿って切断し、半導体チップ4および分割された支持板13からなる積層体3を形成する第3の工程と、積層体3を配線基板18に搭載し、積層体3の半導体チップ4および配線基板18を電気的に接続する第4の工程とを有する半導体装置1の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、表裏に貫通した貫通電極を有する半導体チップを回路基板上に積層配置してなる半導体装置が知られている(例えば、特許文献1参照。)。

【0003】

この特許文献1に記載されるような貫通電極が形成された半導体チップでは、ビア加工のアスペクト比に限界があり、シリコン基板の厚みを、要求された貫通電極の配置ピッチ以下に設定する必要がある。そのため、貫通電極の配置ピッチが微細になるにつれて、シリコン基板の厚みを薄くする必要が生じていた。そして、シリコン基板の厚みが70μm以下になると、半導体チップのハンドリング性に難が生じるという問題があった。

【0004】

そこで、半導体ウエハのハンドリング性を向上する従来技術として、支持基板で被処理基板(半導体ウエハ)を支持した状態で被処理基板を処理する工程を有する基板処理方法が知られている(例えば、特許文献2参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007−36184号公報

【特許文献2】特開2007−324406号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところが、特許文献2に記載の従来の基板処理方法では、限定された工程における半導体ウエハのハンドリング性については考慮されているものの、半導体ウエハのダイシング工程等を含む半導体チップの組立工程におけるハンドリング性については一切考慮されていなかった。

【0007】

そこで、本発明は、従来の問題を解決するものであって、すなわち、本発明の目的は、半導体チップの組立工程におけるハンドリング性を向上し、しかも、半導体チップの損傷を回避する半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0008】

本発明の半導体装置の製造方法は、ダイシングラインによって区画された複数の半導体チップを含む半導体ウエハを準備する第1の工程と、前記半導体ウエハに支持板を付着する第2の工程と、前記半導体ウエハおよび前記支持板をダイシングラインに沿って切断し、前記半導体チップおよび分割された前記支持板からなる積層体を形成する第3の工程と、前記積層体を配線基板に搭載し、前記積層体の半導体チップおよび前記配線基板を電気的に接続する第4の工程とを有することにより、前述した課題を解決したものである。

【発明の効果】

【0009】

本発明では、半導体ウエハのダイシング工程等を含む半導体チップの組立工程における半導体チップのハンドリング性の向上および半導体チップの損傷の回避を実現できる。

【図面の簡単な説明】

【0010】

【図1A】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体ウエハの製造フローを模式的に示す工程図である。

【図1B】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体ウエハの製造フローを模式的に示す工程図である。

【図1C】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体ウエハの製造フローを模式的に示す工程図である。

【図1D】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体ウエハの製造フローを模式的に示す工程図である。

【図2A】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図2B】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図2C】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

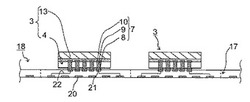

【図3A】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図3B】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図3C】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図3D】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図3E】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図4A】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図4B】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図4C】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図4D】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図4E】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図5A】本発明の第2実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図5B】本発明の第2実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図5C】本発明の第2実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図5D】本発明の第2実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図5E】本発明の第2実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図6A】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図6B】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図6C】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図7A】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図7B】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図7C】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図7D】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図7E】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【発明を実施するための形態】

【0011】

以下に、具体例に沿って、本発明に係る半導体装置の製造方法を説明する。なお、本発明で用いる「表面」は、半導体ウエハの回路形成面のことを意味し、また、「裏面」は、前記表面の反対側の面のことを意味しており、配線基板や半導体装置の現実の姿勢を限定するものではない。また、以下の説明に用いる各図面は、各部を認識可能な大きさとするため、各部材の縮尺を適宜変更している。

【実施例1】

【0012】

以下に、本発明の第1実施例である半導体装置の製造方法を図1A乃至図4Eを用いて説明する。

【0013】

初めに、第1実施例における半導体ウエハ2の製造フローを図1A乃至図1Dに基づいて説明する。

【0014】

まず、図1Aに示すように、シリコン基板6の回路形成面(以下、表面と称する)26には、半導体ウエハ2の個々のチップ領域毎に、所定の回路(例えばメモリ回路と電極パッド)上に、表面側バンプ電極8が形成される。表面側バンプ電極8は、例えばCu等からなり、表面側バンプ電極8の外面(表面)には、Ni/Auメッキ層が形成されている。また、表面側バンプ電極8の下方には、絶縁層に囲まれた導体層9が所定の深さで形成されている。この導体層9は、例えばCuから成る。なお、図1A乃至図1Dの符号16は、ダイシングラインを示している。

【0015】

次に、図1Bに示すように、半導体ウエハ2は、第1接着層12を介して、ウエハサポート部材(支持板)11により、その表面側を保持される。このウエハサポート部材11としては、例えばガラス基板が用いられる。また、第1接着層12としては、例えばUV硬化型アクリル系の接着材が使用される。また、第1接着層12は、例えば20μm程度の高さの表面側バンプ電極8を覆う場合には、50μm程度の厚さで形成される。

このように、表面側バンプ電極8を突出形成した半導体ウエハ2の表面側と、ウエハサポート部材11との間に、第1接着層12を介在させることにより、表面側バンプ電極8を損傷することなく、ウエハサポート部材11により半導体ウエハ2を良好に保持することができる。

【0016】

次に、図1Cに示すように、ウエハサポート部材11により表面側を保持された半導体ウエハ2は、バックグラインド工程に移行され、ウエハサポート部材11に保持された状態で半導体ウエハ2の裏面を所定の厚さ、例えば50μm厚まで研削し、半導体ウエハ2の裏面から導体層9を露出させると共に、半導体ウエハ2を薄型化する。

このように、ウエハサポート部材11により、薄型化された半導体ウエハ2を保持しているため、薄型化された半導体ウエハ2の搬送等、取り扱いが容易になる。

【0017】

次に、図1Dに示すように、半導体ウエハ2の裏面側(すなわち、後述する支持基板13を搭載する半導体ウエハ2の搭載面側)から露出した導体層9上に、裏面側バンプ電極10を形成する。この裏面側バンプ電極10は、シリコン基板6の厚み方向において表面側バンプ電極8に対応する位置に形成される。この裏面側バンプ電極10は、例えばCuからなり、裏面側バンプ電極10の外面(表面)には、SnAgメッキ層が形成されている。

【0018】

以上のように、一面に複数のチップ領域と、貫通電極7を有し、第1接着層12を介してウエハサポート部材11により表面側を保持された半導体ウエハ2が準備される。

【0019】

次に、第1実施例における支持基板付半導体チップ3の製造フローを図2A乃至図2Cに基づいて説明する。

【0020】

まず、図2Aに示すように、ウエハサポート部材11により表面側を保持された半導体ウエハ2は、第2接着層14を介して、支持基板(支持板)13により裏面側を保持される。この支持基板13としては、例えば、シリコン基板、ガラスエポキシ基板、エポキシ樹脂基板、SUS基板、Al基板が用いられる。また、第2接着層14としては、例えばウエハサポート部材11と同様に、UV硬化型アクリル系の接着材が使用される。また、第2接着層14は、例えば20μm程度の高さの裏面側バンプ電極10を覆う場合には、50μm程度の厚さで構成される。

【0021】

次に、図2Bに示すように、半導体ウエハ2は、ウエハサポート部材11のデマウント工程に移行される。このデマウント工程では、例えば、ウエハサポート部材11の第1接着層12に紫外線を照射し、接着力を低下させ、ウエハサポート部材11を除去する。これにより、半導体ウエハ2の表面側を露出させる。この際、支持基板13の第2接着層14が、ウエハサポート部材11の第1接着層12への紫外線照射時に影響を受け可能性もあるため、支持基板13の第2接着層14として、ウエハサポート部材11の第1接着層12とは異なるUV硬化特性を有する接着材を用いる方が好ましい。例えば、有る一定の温度以上で剥離性を発現する接着材が挙げられる。

【0022】

次に、図2Cに示すように、ダイシング工程に移行され、半導体ウエハ2の裏面側に配置された支持基板13にダイシングテープ15を貼り付ける。このダイシング工程では、ダイシング装置(図示しない)により、半導体ウエハ2の表面側のチップ領域間のダイシングライン16を認識し、認識されたダイシングライン16に基づき、半導体ウエハ2の裏面側から、高速回転するダイシングブレード(図示しない)によりダイシングライン16を切断する。このダイシングでは、支持基板13の第2接着層14の一部まで切断されるように調整されており、半導体ウエハ2と支持基板13は、完全にチップ領域(半導体チップ4)毎に切断される。そして、半導体ウエハ2を表面側からダイシングライン16を切断し、半導体ウエハ2は、個々の半導体チップ4毎に切断分離され、支持基板付半導体チップ(積層体)3が得られる。

【0023】

このように支持基板付半導体チップ3を構成したことにより、ダイシングテープ15からピックアップ装置(図示しない)により各半導体チップ4(支持基板付半導体チップ3)を突き上げてピックアップする際に、貫通電極7を有する半導体チップ4が支持基板13により補強されているため、チップクラックの発生等を抑制し、良好にダイシングテープ15から半導体チップ4(支持基板付半導体チップ3)をピックアップすることができる。また、ダイシングテープ15に貼り付けられる面側に支持基板13を配置していることにより、半導体チップ4(支持基板付半導体チップ3)が直接的に突き上げられることを回避するため、突き上げ時におけるチップクラックの発生をより一層低減できる。

【0024】

次に、第1実施例における支持基板付半導体チップ3を用いたボンディング工程を図3A乃至図3Eに基づいて説明する。

【0025】

まず、図3Aに示すように、支持基板付半導体チップ3が搭載される配線基板18が準備される。この配線基板18は、例えば0.14mm厚のガラスエポキシ配線基板であり、マトリックス状に配置された複数の製品形成部19を有している。配線基板18の複数の製品形成部19には、それぞれ所定の配線パターンが形成され、配線22は、部分的に絶縁膜、例えばソルダーレジストで覆われている。また、製品形成部19間は、ダイシングライン17となる。製品形成部19の一面側の配線22のソルダーレジストから露出された部位には、複数の接続パッド21が形成されている。また、製品形成部19の他面の配線22のソルダーレジストから露出された部位には、複数のランド20が形成されている。そして、接続パッド21と、接続パッド21に対応するランド20とは、配線基板18の配線22によりそれぞれ電気的に接続されている。

【0026】

次に、図3Bに示すように、配線基板18は、ボンディング工程に移行される。このボンディング工程では、例えばボンディング装置(図示しない)のボンディングツール(図示しない)により、支持基板付半導体チップ3の支持基板13を配置した裏面側を吸着保持する。そして、配線基板18の各製品形成部19に、支持基板付半導体チップ3を、ボンディングツールにより高温、例えば300℃程度で荷重を印加し、フリップチップボンディングする。これにより、図3Bに示すように、配線基板18の各製品形成部19に、支持基板付半導体チップ3が搭載され、支持基板付半導体チップ3の表面側バンプ電極8と配線基板18の接続パッド21とが電気的に接続される。なお、支持基板付半導体チップ3の接合は、荷重だけでなく、超音波も印加するように構成してもよい。

【0027】

ここで、本実施例では、支持基板付半導体チップ3の裏面側バンプ電極10にはSnAgメッキ層が形成されているが、支持基板13を介して、ボンディングツールに保持されることで、SnAgメッキ層の溶融温度までボンディングツールが加熱されても、裏面側バンプ電極10のSnAgメッキがボンディングツールに付着することなく、支持基板付半導体チップ3の表面側を配線基板18に対して良好にフリップチップボンディングすることができる。

【0028】

次に、図3Cに示すように、配線基板18に搭載された支持基板付半導体チップ3の第2接着層14に紫外線を照射し、第2接着層14の接着力を低下させ、個片化された支持基板13を除去する。これにより、配線基板18に搭載された半導体チップ4の裏面側は露出される。なお、支持基板13の除去は、他の支持基板13に各支持基板13を貼り付け、一括で除去、或いは、支持基板13を研削することで、除去するように構成してもよい。

【0029】

次に、図3Dに示すように、配線基板18上に搭載された半導体チップ4の裏面側に、2段目の支持基板付半導体チップ3をフリップチップボンディングにより搭載する。これにより、配線基板18上に搭載された1段目の半導体チップ4の裏面上に、2段目の支持基板付半導体チップ3が搭載され、1段目の半導体チップ4の裏面側バンプ電極10のSnAgメッキ層と2段目の支持基板付半導体チップ3の表面側バンプ電極8のNi/Auメッキ層とが電気的に接続される。

【0030】

次に、図3Eに示すように、1段目の支持基板付半導体チップ3と同様に、2段目の支持基板付半導体チップ3の支持基板13が除去され、配線基板18の各製品形成部19に、2段の半導体チップ4により構成されたチップ積層体5が形成される。

【0031】

このように、半導体チップ4に支持基板13を固着し、50μm程度の厚さで貫通電極7を有する半導体チップ4を支持基板13により保持するように構成したことにより、既存のボンディング装置で、50μm程度の薄い半導体チップ4を、チップクラックを発生させることなく良好にハンドリングすることができ、半導体装置1の組立工程での歩留を向上させることができる。また、支持基板付半導体チップ3を配線基板18に実装した後、支持基板13を除去するように構成することで、貫通電極7を有する半導体チップ4を多段に積層できる。

また、半導体チップ4の裏面側に支持基板13を設けることで、半導体チップ4の裏面側バンプ電極10にSnAgメッキ層が形成されていても、支持基板13を介してボンディングツール(図示しない)により保持されるため、SnAgメッキ層の溶融温度までボンディングツールが加熱されても、裏面側バンプ電極10のSnAgメッキがボンディングツールに付着することなく、半導体チップ4のSnAgメッキ層側を保持することができる。

【0032】

次に、第1実施例における半導体装置1の組立フローを図4A乃至図4Eに基づいて説明する。

【0033】

まず、図4Aに示すように、チップ積層体5が形成された配線基板18は、アンダーフィル封止工程に移行される。このアンダーフィル封止工程では、ポッティング装置(図示しない)により、各チップ積層体5の端部の近傍位置にアンダーフィル材23を供給する。供給されたアンダーフィル材23は、毛細管現象により、積層された半導体チップ4間の隙間に充填される。そして、チップ積層体5へのアンダーフィル材23の充填完了後、所定温度、例えば150℃程度でキュアすることで、アンダーフィル材23が硬化され、図4Aに示すように、配線基板18上のチップ積層体5の周囲及び半導体チップ4間にアンダーフィル材23の層が形成される。

【0034】

次に、図4Bに示すように、チップ積層体5が搭載された配線基板18は、モールド工程に移行される。このモールド工程では、配線基板18は、トランスファモールド装置(図示しない)の上型と下型からなる成型金型(図示しない)にセットされる。成型金型の上型には複数のチップ搭載部を一括的に覆うようにキャビティが形成されており、このキャビティ内に配線基板18上のチップ積層体5が配置される。そして、ゲート部からキャビティ内に加熱溶融された封止樹脂24を注入し、配線基板18のチップ積層体5の搭載面側を封止する。この封止樹脂24としては、例えばエポキシ樹脂等の熱硬化性樹脂が用いられる。そして、配線基板18の一面側のキャビティが封止樹脂24で充填された状態で、所定の温度、例えば180℃程度でキュアすることで、封止樹脂24が熱硬化され、図4Bに示すように、配線基板18の複数の製品形成部19を一括的に覆う封止樹脂24の層が形成される。その後、封止樹脂24の層が形成された配線基板18を、所定の温度でベークすることで、封止樹脂24が完全に硬化される。

【0035】

このように、配線基板18とチップ積層体5間と、チップ積層体5の半導体チップ4間とに接着部材(アンダーフィル材23)が充填された状態で、配線基板18上を一括的に覆う封止樹脂24層を形成したことで、モールド時における半導体チップ4間へのボイドの発生を抑制できる。

【0036】

次に、図4Cに示すように、封止樹脂24の層が形成された配線基板18は、ボールマウント工程に移行され、配線基板18の他面に形成されたランド20に、導電性の金属ボール25、例えば半田ボールを搭載し、外部端子を形成する。このボールマウント工程では、配線基板18上に配置された複数のランド20に合せて、複数の吸着孔が形成されたボールマウンター(図示しない)のマウントツール(図示しない)を用いて、半田等からなる金属ボール25をマウントツールで吸着保持し、吸着保持された金属ボール25にフラックスを転写形成し、配線基板18上の複数のランド20に一括搭載する。そして、全ての製品形成部19への金属ボール25搭載後、配線基板18をリフローすることで外部端子が形成される。

【0037】

次に、図4Dに示すように、金属ボール25が搭載された配線基板18は、基板ダイシング工程に移行され、配線基板18を切断し、個々の製品形成部19毎に分離する。この基板ダイシング工程では、配線基板18の封止樹脂24の層側にダイシングテープ15を貼着し、ダイシングテープ15によって配線基板18を支持する。その後、ダイシング装置(図示しない)のダイシングブレード(図示しない)により縦横に切断して、製品形成部19毎に分離する。そして配線基板18の切断分離後、ダイシングテープ15からピックアップすることで、図4Eに示すような複数のCoC型の半導体装置1が得られる。

【実施例2】

【0038】

次に、本発明の第2実施例である半導体装置の製造方法を図5A乃至図5Eに基づいて説明する。

ここで、第1実施例においては、配線基板18のアンダーフィル封止工程へ移行する際に、最上段に位置する支持基板付半導体チップ3から支持基板13を除去したが、第2実施例においては、後述するように、最上段に位置する支持基板付半導体チップ3に支持基板13を残存させている。そして、この事以外の構成については、前述した第1実施例の内容と全く同じであるため、その説明を省略する。

【0039】

第2実施例である半導体装置の製造方法では、配線基板18のアンダーフィル封止工程へ移行する際に、最上段の支持基板13をチップ積層体5に残存させている。詳述すると、支持基板13が絶縁部材、或いは、支持基板13が導電材料であっても絶縁性の接着材で絶縁分離されている場合には、図5Aに示すように、最上段に積層される支持基板付半導体チップ3に支持基板13を残存させても何ら構わない。これにより、第1実施例における効果に加えて、配線基板18上のチップ積層体5を補強することができ、チップ積層体5にかかる熱膨張率の差異による応力を緩和できる。また、最上段の支持基板13の除去工程も不要となり、製造負担を低減できる。また、支持基板13が導電材である場合、すなわち、放熱特性の高い材料から成る場合には、半導体装置1の放熱性を向上できる。

【実施例3】

【0040】

次に、本発明の第3実施例である半導体装置の製造方法を図6A乃至図7Eに基づいて説明する。

ここで、第1実施例においては、第2接着層14を介して支持基板13を半導体ウエハ2上に設けたが、第3実施例においては、後述するように、第2接着層14を介することなく支持基板13を半導体ウエハ2上に設けている。そして、この事に関する事以外の構成については、前述した第1実施例の内容と全く同じであるため、その説明を省略する。

【0041】

第3実施例である半導体装置の製造方法では、図6Aに示すように、ウエハサポート部材11に支持された半導体ウエハ2の裏面上に、絶縁性の樹脂をスピンナー塗布により均一で所定の厚さの支持基板13の層が形成される。次に、図6Bに示すように、実施例1と同様に、ウエハサポート部材11が除去され、図6Cに示すように、ダイシングされて、図6Cに示すような支持基板付半導体チップ3が形成できる。次に、図7Bに示すように、実施例1と同様に、支持基板付半導体チップ3が配線基板18に搭載される。次に、図7Cに示すように、バックグラインドにより支持基板13を研削し、裏面側バンプ電極10が露出されるまで支持基板13を除去する。

【0042】

このように、第3実施例においては、半導体ウエハ2に、スピンナー塗布により、絶縁樹脂からなる支持基板13の層を形成し、支持基板付半導体チップ3を配線基板18に実装した後、支持基板13の層を研削して除去することで、実施例1と同様に、半導体チップ3のハンドリング性を向上できると共に、支持基板13の層形成の際、薄化された半導体ウエハ2に面方向荷重がかからないためダメージのより少ない形成が可能である。

【0043】

以上、本発明者によってなされた発明を上記の実施例に基づき具体的に説明したが、本発明は上記の実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0044】

例えば、上記の実施例では、半導体チップを2段に積層する場合について説明したが、3段以上に積層するように構成しても何ら構わない。

【0045】

また、上記の実施例では、同一サイズのメモリチップを積層した場合について説明したが、異なるサイズの半導体チップを積層する場合に適用しても何ら構わない。

【0046】

さらに、上記の実施例では、SnAgメッキが形成された裏面側に支持基板を搭載し、ウエハサポート部材から支持基板に半導体ウエハを移し替えるように構成したが、SnAgメッキがなく、ボンディングツールへのSnAgメッキの付着の恐れがない半導体ウエハの場合には、ウエハサポート部材を支持基板として、半導体ウエハと共に切断し、積層体を形成するように構成しても何ら構わない。

【符号の説明】

【0047】

1 ・・・ 半導体装置

2 ・・・ 半導体ウエハ

3 ・・・ 支持基板付半導体チップ(積層体)

4 ・・・ 半導体チップ

5 ・・・ チップ積層体

6 ・・・ シリコン基板

7 ・・・ 貫通電極

8 ・・・ 表面側バンプ電極

9 ・・・ 導体層

10 ・・・ 裏面側バンプ電極

11 ・・・ ウエハサポート部材(支持板)

12 ・・・ 第1接着層

13 ・・・ 支持基板(支持板)

14 ・・・ 第2接着層

15 ・・・ ダイシングテープ

16 ・・・ ダイシングライン

17 ・・・ ダイシングライン

18 ・・・ 配線基板

19 ・・・ 製品形成部

20 ・・・ ランド

21 ・・・ 接続パッド

22 ・・・ 配線

23 ・・・ アンダーフィル材

24 ・・・ 封止樹脂

25 ・・・ 金属ボール

26 ・・・ 回路形成面(表面)

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、表裏に貫通した貫通電極を有する半導体チップを回路基板上に積層配置してなる半導体装置が知られている(例えば、特許文献1参照。)。

【0003】

この特許文献1に記載されるような貫通電極が形成された半導体チップでは、ビア加工のアスペクト比に限界があり、シリコン基板の厚みを、要求された貫通電極の配置ピッチ以下に設定する必要がある。そのため、貫通電極の配置ピッチが微細になるにつれて、シリコン基板の厚みを薄くする必要が生じていた。そして、シリコン基板の厚みが70μm以下になると、半導体チップのハンドリング性に難が生じるという問題があった。

【0004】

そこで、半導体ウエハのハンドリング性を向上する従来技術として、支持基板で被処理基板(半導体ウエハ)を支持した状態で被処理基板を処理する工程を有する基板処理方法が知られている(例えば、特許文献2参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007−36184号公報

【特許文献2】特開2007−324406号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところが、特許文献2に記載の従来の基板処理方法では、限定された工程における半導体ウエハのハンドリング性については考慮されているものの、半導体ウエハのダイシング工程等を含む半導体チップの組立工程におけるハンドリング性については一切考慮されていなかった。

【0007】

そこで、本発明は、従来の問題を解決するものであって、すなわち、本発明の目的は、半導体チップの組立工程におけるハンドリング性を向上し、しかも、半導体チップの損傷を回避する半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0008】

本発明の半導体装置の製造方法は、ダイシングラインによって区画された複数の半導体チップを含む半導体ウエハを準備する第1の工程と、前記半導体ウエハに支持板を付着する第2の工程と、前記半導体ウエハおよび前記支持板をダイシングラインに沿って切断し、前記半導体チップおよび分割された前記支持板からなる積層体を形成する第3の工程と、前記積層体を配線基板に搭載し、前記積層体の半導体チップおよび前記配線基板を電気的に接続する第4の工程とを有することにより、前述した課題を解決したものである。

【発明の効果】

【0009】

本発明では、半導体ウエハのダイシング工程等を含む半導体チップの組立工程における半導体チップのハンドリング性の向上および半導体チップの損傷の回避を実現できる。

【図面の簡単な説明】

【0010】

【図1A】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体ウエハの製造フローを模式的に示す工程図である。

【図1B】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体ウエハの製造フローを模式的に示す工程図である。

【図1C】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体ウエハの製造フローを模式的に示す工程図である。

【図1D】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体ウエハの製造フローを模式的に示す工程図である。

【図2A】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図2B】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図2C】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図3A】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図3B】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図3C】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図3D】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図3E】本発明の第1実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図4A】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図4B】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図4C】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図4D】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図4E】本発明の第1実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図5A】本発明の第2実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図5B】本発明の第2実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図5C】本発明の第2実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図5D】本発明の第2実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図5E】本発明の第2実施例である半導体装置の製造方法を説明する図であり、半導体装置の組立フローを模式的に示す工程図である。

【図6A】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図6B】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図6C】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップの製造フローを模式的に示す工程図である。

【図7A】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図7B】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図7C】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図7D】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【図7E】本発明の第3実施例である半導体装置の製造方法を説明する図であり、支持基板付半導体チップのボンディング工程を模式的に示す工程図である。

【発明を実施するための形態】

【0011】

以下に、具体例に沿って、本発明に係る半導体装置の製造方法を説明する。なお、本発明で用いる「表面」は、半導体ウエハの回路形成面のことを意味し、また、「裏面」は、前記表面の反対側の面のことを意味しており、配線基板や半導体装置の現実の姿勢を限定するものではない。また、以下の説明に用いる各図面は、各部を認識可能な大きさとするため、各部材の縮尺を適宜変更している。

【実施例1】

【0012】

以下に、本発明の第1実施例である半導体装置の製造方法を図1A乃至図4Eを用いて説明する。

【0013】

初めに、第1実施例における半導体ウエハ2の製造フローを図1A乃至図1Dに基づいて説明する。

【0014】

まず、図1Aに示すように、シリコン基板6の回路形成面(以下、表面と称する)26には、半導体ウエハ2の個々のチップ領域毎に、所定の回路(例えばメモリ回路と電極パッド)上に、表面側バンプ電極8が形成される。表面側バンプ電極8は、例えばCu等からなり、表面側バンプ電極8の外面(表面)には、Ni/Auメッキ層が形成されている。また、表面側バンプ電極8の下方には、絶縁層に囲まれた導体層9が所定の深さで形成されている。この導体層9は、例えばCuから成る。なお、図1A乃至図1Dの符号16は、ダイシングラインを示している。

【0015】

次に、図1Bに示すように、半導体ウエハ2は、第1接着層12を介して、ウエハサポート部材(支持板)11により、その表面側を保持される。このウエハサポート部材11としては、例えばガラス基板が用いられる。また、第1接着層12としては、例えばUV硬化型アクリル系の接着材が使用される。また、第1接着層12は、例えば20μm程度の高さの表面側バンプ電極8を覆う場合には、50μm程度の厚さで形成される。

このように、表面側バンプ電極8を突出形成した半導体ウエハ2の表面側と、ウエハサポート部材11との間に、第1接着層12を介在させることにより、表面側バンプ電極8を損傷することなく、ウエハサポート部材11により半導体ウエハ2を良好に保持することができる。

【0016】

次に、図1Cに示すように、ウエハサポート部材11により表面側を保持された半導体ウエハ2は、バックグラインド工程に移行され、ウエハサポート部材11に保持された状態で半導体ウエハ2の裏面を所定の厚さ、例えば50μm厚まで研削し、半導体ウエハ2の裏面から導体層9を露出させると共に、半導体ウエハ2を薄型化する。

このように、ウエハサポート部材11により、薄型化された半導体ウエハ2を保持しているため、薄型化された半導体ウエハ2の搬送等、取り扱いが容易になる。

【0017】

次に、図1Dに示すように、半導体ウエハ2の裏面側(すなわち、後述する支持基板13を搭載する半導体ウエハ2の搭載面側)から露出した導体層9上に、裏面側バンプ電極10を形成する。この裏面側バンプ電極10は、シリコン基板6の厚み方向において表面側バンプ電極8に対応する位置に形成される。この裏面側バンプ電極10は、例えばCuからなり、裏面側バンプ電極10の外面(表面)には、SnAgメッキ層が形成されている。

【0018】

以上のように、一面に複数のチップ領域と、貫通電極7を有し、第1接着層12を介してウエハサポート部材11により表面側を保持された半導体ウエハ2が準備される。

【0019】

次に、第1実施例における支持基板付半導体チップ3の製造フローを図2A乃至図2Cに基づいて説明する。

【0020】

まず、図2Aに示すように、ウエハサポート部材11により表面側を保持された半導体ウエハ2は、第2接着層14を介して、支持基板(支持板)13により裏面側を保持される。この支持基板13としては、例えば、シリコン基板、ガラスエポキシ基板、エポキシ樹脂基板、SUS基板、Al基板が用いられる。また、第2接着層14としては、例えばウエハサポート部材11と同様に、UV硬化型アクリル系の接着材が使用される。また、第2接着層14は、例えば20μm程度の高さの裏面側バンプ電極10を覆う場合には、50μm程度の厚さで構成される。

【0021】

次に、図2Bに示すように、半導体ウエハ2は、ウエハサポート部材11のデマウント工程に移行される。このデマウント工程では、例えば、ウエハサポート部材11の第1接着層12に紫外線を照射し、接着力を低下させ、ウエハサポート部材11を除去する。これにより、半導体ウエハ2の表面側を露出させる。この際、支持基板13の第2接着層14が、ウエハサポート部材11の第1接着層12への紫外線照射時に影響を受け可能性もあるため、支持基板13の第2接着層14として、ウエハサポート部材11の第1接着層12とは異なるUV硬化特性を有する接着材を用いる方が好ましい。例えば、有る一定の温度以上で剥離性を発現する接着材が挙げられる。

【0022】

次に、図2Cに示すように、ダイシング工程に移行され、半導体ウエハ2の裏面側に配置された支持基板13にダイシングテープ15を貼り付ける。このダイシング工程では、ダイシング装置(図示しない)により、半導体ウエハ2の表面側のチップ領域間のダイシングライン16を認識し、認識されたダイシングライン16に基づき、半導体ウエハ2の裏面側から、高速回転するダイシングブレード(図示しない)によりダイシングライン16を切断する。このダイシングでは、支持基板13の第2接着層14の一部まで切断されるように調整されており、半導体ウエハ2と支持基板13は、完全にチップ領域(半導体チップ4)毎に切断される。そして、半導体ウエハ2を表面側からダイシングライン16を切断し、半導体ウエハ2は、個々の半導体チップ4毎に切断分離され、支持基板付半導体チップ(積層体)3が得られる。

【0023】

このように支持基板付半導体チップ3を構成したことにより、ダイシングテープ15からピックアップ装置(図示しない)により各半導体チップ4(支持基板付半導体チップ3)を突き上げてピックアップする際に、貫通電極7を有する半導体チップ4が支持基板13により補強されているため、チップクラックの発生等を抑制し、良好にダイシングテープ15から半導体チップ4(支持基板付半導体チップ3)をピックアップすることができる。また、ダイシングテープ15に貼り付けられる面側に支持基板13を配置していることにより、半導体チップ4(支持基板付半導体チップ3)が直接的に突き上げられることを回避するため、突き上げ時におけるチップクラックの発生をより一層低減できる。

【0024】

次に、第1実施例における支持基板付半導体チップ3を用いたボンディング工程を図3A乃至図3Eに基づいて説明する。

【0025】

まず、図3Aに示すように、支持基板付半導体チップ3が搭載される配線基板18が準備される。この配線基板18は、例えば0.14mm厚のガラスエポキシ配線基板であり、マトリックス状に配置された複数の製品形成部19を有している。配線基板18の複数の製品形成部19には、それぞれ所定の配線パターンが形成され、配線22は、部分的に絶縁膜、例えばソルダーレジストで覆われている。また、製品形成部19間は、ダイシングライン17となる。製品形成部19の一面側の配線22のソルダーレジストから露出された部位には、複数の接続パッド21が形成されている。また、製品形成部19の他面の配線22のソルダーレジストから露出された部位には、複数のランド20が形成されている。そして、接続パッド21と、接続パッド21に対応するランド20とは、配線基板18の配線22によりそれぞれ電気的に接続されている。

【0026】

次に、図3Bに示すように、配線基板18は、ボンディング工程に移行される。このボンディング工程では、例えばボンディング装置(図示しない)のボンディングツール(図示しない)により、支持基板付半導体チップ3の支持基板13を配置した裏面側を吸着保持する。そして、配線基板18の各製品形成部19に、支持基板付半導体チップ3を、ボンディングツールにより高温、例えば300℃程度で荷重を印加し、フリップチップボンディングする。これにより、図3Bに示すように、配線基板18の各製品形成部19に、支持基板付半導体チップ3が搭載され、支持基板付半導体チップ3の表面側バンプ電極8と配線基板18の接続パッド21とが電気的に接続される。なお、支持基板付半導体チップ3の接合は、荷重だけでなく、超音波も印加するように構成してもよい。

【0027】

ここで、本実施例では、支持基板付半導体チップ3の裏面側バンプ電極10にはSnAgメッキ層が形成されているが、支持基板13を介して、ボンディングツールに保持されることで、SnAgメッキ層の溶融温度までボンディングツールが加熱されても、裏面側バンプ電極10のSnAgメッキがボンディングツールに付着することなく、支持基板付半導体チップ3の表面側を配線基板18に対して良好にフリップチップボンディングすることができる。

【0028】

次に、図3Cに示すように、配線基板18に搭載された支持基板付半導体チップ3の第2接着層14に紫外線を照射し、第2接着層14の接着力を低下させ、個片化された支持基板13を除去する。これにより、配線基板18に搭載された半導体チップ4の裏面側は露出される。なお、支持基板13の除去は、他の支持基板13に各支持基板13を貼り付け、一括で除去、或いは、支持基板13を研削することで、除去するように構成してもよい。

【0029】

次に、図3Dに示すように、配線基板18上に搭載された半導体チップ4の裏面側に、2段目の支持基板付半導体チップ3をフリップチップボンディングにより搭載する。これにより、配線基板18上に搭載された1段目の半導体チップ4の裏面上に、2段目の支持基板付半導体チップ3が搭載され、1段目の半導体チップ4の裏面側バンプ電極10のSnAgメッキ層と2段目の支持基板付半導体チップ3の表面側バンプ電極8のNi/Auメッキ層とが電気的に接続される。

【0030】

次に、図3Eに示すように、1段目の支持基板付半導体チップ3と同様に、2段目の支持基板付半導体チップ3の支持基板13が除去され、配線基板18の各製品形成部19に、2段の半導体チップ4により構成されたチップ積層体5が形成される。

【0031】

このように、半導体チップ4に支持基板13を固着し、50μm程度の厚さで貫通電極7を有する半導体チップ4を支持基板13により保持するように構成したことにより、既存のボンディング装置で、50μm程度の薄い半導体チップ4を、チップクラックを発生させることなく良好にハンドリングすることができ、半導体装置1の組立工程での歩留を向上させることができる。また、支持基板付半導体チップ3を配線基板18に実装した後、支持基板13を除去するように構成することで、貫通電極7を有する半導体チップ4を多段に積層できる。

また、半導体チップ4の裏面側に支持基板13を設けることで、半導体チップ4の裏面側バンプ電極10にSnAgメッキ層が形成されていても、支持基板13を介してボンディングツール(図示しない)により保持されるため、SnAgメッキ層の溶融温度までボンディングツールが加熱されても、裏面側バンプ電極10のSnAgメッキがボンディングツールに付着することなく、半導体チップ4のSnAgメッキ層側を保持することができる。

【0032】

次に、第1実施例における半導体装置1の組立フローを図4A乃至図4Eに基づいて説明する。

【0033】

まず、図4Aに示すように、チップ積層体5が形成された配線基板18は、アンダーフィル封止工程に移行される。このアンダーフィル封止工程では、ポッティング装置(図示しない)により、各チップ積層体5の端部の近傍位置にアンダーフィル材23を供給する。供給されたアンダーフィル材23は、毛細管現象により、積層された半導体チップ4間の隙間に充填される。そして、チップ積層体5へのアンダーフィル材23の充填完了後、所定温度、例えば150℃程度でキュアすることで、アンダーフィル材23が硬化され、図4Aに示すように、配線基板18上のチップ積層体5の周囲及び半導体チップ4間にアンダーフィル材23の層が形成される。

【0034】

次に、図4Bに示すように、チップ積層体5が搭載された配線基板18は、モールド工程に移行される。このモールド工程では、配線基板18は、トランスファモールド装置(図示しない)の上型と下型からなる成型金型(図示しない)にセットされる。成型金型の上型には複数のチップ搭載部を一括的に覆うようにキャビティが形成されており、このキャビティ内に配線基板18上のチップ積層体5が配置される。そして、ゲート部からキャビティ内に加熱溶融された封止樹脂24を注入し、配線基板18のチップ積層体5の搭載面側を封止する。この封止樹脂24としては、例えばエポキシ樹脂等の熱硬化性樹脂が用いられる。そして、配線基板18の一面側のキャビティが封止樹脂24で充填された状態で、所定の温度、例えば180℃程度でキュアすることで、封止樹脂24が熱硬化され、図4Bに示すように、配線基板18の複数の製品形成部19を一括的に覆う封止樹脂24の層が形成される。その後、封止樹脂24の層が形成された配線基板18を、所定の温度でベークすることで、封止樹脂24が完全に硬化される。

【0035】

このように、配線基板18とチップ積層体5間と、チップ積層体5の半導体チップ4間とに接着部材(アンダーフィル材23)が充填された状態で、配線基板18上を一括的に覆う封止樹脂24層を形成したことで、モールド時における半導体チップ4間へのボイドの発生を抑制できる。

【0036】

次に、図4Cに示すように、封止樹脂24の層が形成された配線基板18は、ボールマウント工程に移行され、配線基板18の他面に形成されたランド20に、導電性の金属ボール25、例えば半田ボールを搭載し、外部端子を形成する。このボールマウント工程では、配線基板18上に配置された複数のランド20に合せて、複数の吸着孔が形成されたボールマウンター(図示しない)のマウントツール(図示しない)を用いて、半田等からなる金属ボール25をマウントツールで吸着保持し、吸着保持された金属ボール25にフラックスを転写形成し、配線基板18上の複数のランド20に一括搭載する。そして、全ての製品形成部19への金属ボール25搭載後、配線基板18をリフローすることで外部端子が形成される。

【0037】

次に、図4Dに示すように、金属ボール25が搭載された配線基板18は、基板ダイシング工程に移行され、配線基板18を切断し、個々の製品形成部19毎に分離する。この基板ダイシング工程では、配線基板18の封止樹脂24の層側にダイシングテープ15を貼着し、ダイシングテープ15によって配線基板18を支持する。その後、ダイシング装置(図示しない)のダイシングブレード(図示しない)により縦横に切断して、製品形成部19毎に分離する。そして配線基板18の切断分離後、ダイシングテープ15からピックアップすることで、図4Eに示すような複数のCoC型の半導体装置1が得られる。

【実施例2】

【0038】

次に、本発明の第2実施例である半導体装置の製造方法を図5A乃至図5Eに基づいて説明する。

ここで、第1実施例においては、配線基板18のアンダーフィル封止工程へ移行する際に、最上段に位置する支持基板付半導体チップ3から支持基板13を除去したが、第2実施例においては、後述するように、最上段に位置する支持基板付半導体チップ3に支持基板13を残存させている。そして、この事以外の構成については、前述した第1実施例の内容と全く同じであるため、その説明を省略する。

【0039】

第2実施例である半導体装置の製造方法では、配線基板18のアンダーフィル封止工程へ移行する際に、最上段の支持基板13をチップ積層体5に残存させている。詳述すると、支持基板13が絶縁部材、或いは、支持基板13が導電材料であっても絶縁性の接着材で絶縁分離されている場合には、図5Aに示すように、最上段に積層される支持基板付半導体チップ3に支持基板13を残存させても何ら構わない。これにより、第1実施例における効果に加えて、配線基板18上のチップ積層体5を補強することができ、チップ積層体5にかかる熱膨張率の差異による応力を緩和できる。また、最上段の支持基板13の除去工程も不要となり、製造負担を低減できる。また、支持基板13が導電材である場合、すなわち、放熱特性の高い材料から成る場合には、半導体装置1の放熱性を向上できる。

【実施例3】

【0040】

次に、本発明の第3実施例である半導体装置の製造方法を図6A乃至図7Eに基づいて説明する。

ここで、第1実施例においては、第2接着層14を介して支持基板13を半導体ウエハ2上に設けたが、第3実施例においては、後述するように、第2接着層14を介することなく支持基板13を半導体ウエハ2上に設けている。そして、この事に関する事以外の構成については、前述した第1実施例の内容と全く同じであるため、その説明を省略する。

【0041】

第3実施例である半導体装置の製造方法では、図6Aに示すように、ウエハサポート部材11に支持された半導体ウエハ2の裏面上に、絶縁性の樹脂をスピンナー塗布により均一で所定の厚さの支持基板13の層が形成される。次に、図6Bに示すように、実施例1と同様に、ウエハサポート部材11が除去され、図6Cに示すように、ダイシングされて、図6Cに示すような支持基板付半導体チップ3が形成できる。次に、図7Bに示すように、実施例1と同様に、支持基板付半導体チップ3が配線基板18に搭載される。次に、図7Cに示すように、バックグラインドにより支持基板13を研削し、裏面側バンプ電極10が露出されるまで支持基板13を除去する。

【0042】

このように、第3実施例においては、半導体ウエハ2に、スピンナー塗布により、絶縁樹脂からなる支持基板13の層を形成し、支持基板付半導体チップ3を配線基板18に実装した後、支持基板13の層を研削して除去することで、実施例1と同様に、半導体チップ3のハンドリング性を向上できると共に、支持基板13の層形成の際、薄化された半導体ウエハ2に面方向荷重がかからないためダメージのより少ない形成が可能である。

【0043】

以上、本発明者によってなされた発明を上記の実施例に基づき具体的に説明したが、本発明は上記の実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0044】

例えば、上記の実施例では、半導体チップを2段に積層する場合について説明したが、3段以上に積層するように構成しても何ら構わない。

【0045】

また、上記の実施例では、同一サイズのメモリチップを積層した場合について説明したが、異なるサイズの半導体チップを積層する場合に適用しても何ら構わない。

【0046】

さらに、上記の実施例では、SnAgメッキが形成された裏面側に支持基板を搭載し、ウエハサポート部材から支持基板に半導体ウエハを移し替えるように構成したが、SnAgメッキがなく、ボンディングツールへのSnAgメッキの付着の恐れがない半導体ウエハの場合には、ウエハサポート部材を支持基板として、半導体ウエハと共に切断し、積層体を形成するように構成しても何ら構わない。

【符号の説明】

【0047】

1 ・・・ 半導体装置

2 ・・・ 半導体ウエハ

3 ・・・ 支持基板付半導体チップ(積層体)

4 ・・・ 半導体チップ

5 ・・・ チップ積層体

6 ・・・ シリコン基板

7 ・・・ 貫通電極

8 ・・・ 表面側バンプ電極

9 ・・・ 導体層

10 ・・・ 裏面側バンプ電極

11 ・・・ ウエハサポート部材(支持板)

12 ・・・ 第1接着層

13 ・・・ 支持基板(支持板)

14 ・・・ 第2接着層

15 ・・・ ダイシングテープ

16 ・・・ ダイシングライン

17 ・・・ ダイシングライン

18 ・・・ 配線基板

19 ・・・ 製品形成部

20 ・・・ ランド

21 ・・・ 接続パッド

22 ・・・ 配線

23 ・・・ アンダーフィル材

24 ・・・ 封止樹脂

25 ・・・ 金属ボール

26 ・・・ 回路形成面(表面)

【特許請求の範囲】

【請求項1】

ダイシングラインによって区画された複数の半導体チップを含む半導体ウエハを準備する第1の工程と、

前記半導体ウエハに支持板を付着する第2の工程と、

前記半導体ウエハおよび前記支持板をダイシングラインに沿って切断し、前記半導体チップおよび分割された前記支持板からなる積層体を形成する第3の工程と、

前記積層体を配線基板に搭載し、前記積層体の半導体チップおよび前記配線基板を電気的に接続する第4の工程とを有することを特徴とする半導体装置の製造方法。

【請求項2】

前記第1の工程において準備される前記半導体ウエハの前記支持板を付着した側の一方面には、前記半導体ウエハの外部に露出するバンプ電極が設けられており、

前記バンプ電極の外面には、SnAgメッキ層が形成されていることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1の工程において準備される前記半導体ウエハには、前記半導体ウエハの他方面側に配置されたバンプ電極と、前記半導体ウエハを貫通し前記一方面側のバンプ電極および前記他方面側のバンプ電極の間を接続する導体層とが設けられていることを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第4の工程は、前記積層体を前記配線基板に搭載する工程と、前記積層体の半導体チップおよび前記配線基板を電気的に接続する工程と、前記積層体から支持板を除去する工程と、前記支持板を除去された半導体チップ上に他の積層体を搭載する工程とを含むことを特徴とする請求項1乃至請求項3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記第1の工程において準備される前記半導体ウエハには、前記支持板を付着した一方面とは反対側の他方面に、他の支持板が付着されていることを特徴とする請求項1乃至請求項4のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記他方面側の支持板は、第1接着層を介して前記半導体ウエハに付着され、

前記一方面側の支持板は、第2接着層を介して前記半導体ウエハに付着されることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記第1接着層および第2接着層は、UV硬化型の接着材からそれぞれ成り、

前記第1接着層の接着材と前記第2接着層の接着材とは、互いに異なるUV硬化特性を有することを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記第3の工程において、前記支持板にダイシングテープを貼り付けた状態で、前記半導体ウエハおよび前記支持板をダイシングラインに沿って切断することを特徴とする請求項1乃至請求項7のいずれか1項に記載の半導体装置の製造方法。

【請求項9】

前記配線基板および前記配線基板に搭載された半導体チップをモールドする第5の工程を更に有し、

前記第5の工程において、前記配線基板に搭載された半導体チップのうち最上段に位置する半導体チップには、前記支持板が付着された状態で残されていることを特徴とする請求項1乃至請求項8のいずれか1項に記載の半導体装置の製造方法。

【請求項10】

前記支持板は、放熱特性の高い材料から成ることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項1】

ダイシングラインによって区画された複数の半導体チップを含む半導体ウエハを準備する第1の工程と、

前記半導体ウエハに支持板を付着する第2の工程と、

前記半導体ウエハおよび前記支持板をダイシングラインに沿って切断し、前記半導体チップおよび分割された前記支持板からなる積層体を形成する第3の工程と、

前記積層体を配線基板に搭載し、前記積層体の半導体チップおよび前記配線基板を電気的に接続する第4の工程とを有することを特徴とする半導体装置の製造方法。

【請求項2】

前記第1の工程において準備される前記半導体ウエハの前記支持板を付着した側の一方面には、前記半導体ウエハの外部に露出するバンプ電極が設けられており、

前記バンプ電極の外面には、SnAgメッキ層が形成されていることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記第1の工程において準備される前記半導体ウエハには、前記半導体ウエハの他方面側に配置されたバンプ電極と、前記半導体ウエハを貫通し前記一方面側のバンプ電極および前記他方面側のバンプ電極の間を接続する導体層とが設けられていることを特徴とする請求項2に記載の半導体装置の製造方法。

【請求項4】

前記第4の工程は、前記積層体を前記配線基板に搭載する工程と、前記積層体の半導体チップおよび前記配線基板を電気的に接続する工程と、前記積層体から支持板を除去する工程と、前記支持板を除去された半導体チップ上に他の積層体を搭載する工程とを含むことを特徴とする請求項1乃至請求項3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記第1の工程において準備される前記半導体ウエハには、前記支持板を付着した一方面とは反対側の他方面に、他の支持板が付着されていることを特徴とする請求項1乃至請求項4のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記他方面側の支持板は、第1接着層を介して前記半導体ウエハに付着され、

前記一方面側の支持板は、第2接着層を介して前記半導体ウエハに付着されることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記第1接着層および第2接着層は、UV硬化型の接着材からそれぞれ成り、

前記第1接着層の接着材と前記第2接着層の接着材とは、互いに異なるUV硬化特性を有することを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記第3の工程において、前記支持板にダイシングテープを貼り付けた状態で、前記半導体ウエハおよび前記支持板をダイシングラインに沿って切断することを特徴とする請求項1乃至請求項7のいずれか1項に記載の半導体装置の製造方法。

【請求項9】

前記配線基板および前記配線基板に搭載された半導体チップをモールドする第5の工程を更に有し、

前記第5の工程において、前記配線基板に搭載された半導体チップのうち最上段に位置する半導体チップには、前記支持板が付着された状態で残されていることを特徴とする請求項1乃至請求項8のいずれか1項に記載の半導体装置の製造方法。

【請求項10】

前記支持板は、放熱特性の高い材料から成ることを特徴とする請求項9に記載の半導体装置の製造方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図2A】

【図2B】

【図2C】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図6A】

【図6B】

【図6C】

【図7A】

【図7B】

【図7C】

【図7D】

【図7E】

【図1B】

【図1C】

【図1D】

【図2A】

【図2B】

【図2C】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図6A】

【図6B】

【図6C】

【図7A】

【図7B】

【図7C】

【図7D】

【図7E】

【公開番号】特開2012−99693(P2012−99693A)

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願番号】特願2010−247125(P2010−247125)

【出願日】平成22年11月4日(2010.11.4)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願日】平成22年11月4日(2010.11.4)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]