半導体装置の製造方法

【課題】高い歩留まりを実現できる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、基板11上の絶縁層13に形成された第1の凹部14および第1の凹部14よりも幅が狭い第2の凹部15に、基板11を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜21を形成する工程を備えている。また、前記半導体装置の製造方法は、第1の銅膜21上に、不純物濃度が第1の銅膜21よりも高い第2の銅膜22を、第1の銅膜21の形成時よりも流動性が小さい状態で形成する工程を備えている。

【解決手段】実施形態によれば、半導体装置の製造方法は、基板11上の絶縁層13に形成された第1の凹部14および第1の凹部14よりも幅が狭い第2の凹部15に、基板11を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜21を形成する工程を備えている。また、前記半導体装置の製造方法は、第1の銅膜21上に、不純物濃度が第1の銅膜21よりも高い第2の銅膜22を、第1の銅膜21の形成時よりも流動性が小さい状態で形成する工程を備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

銅配線の形成方法として、絶縁層に形成した配線溝に銅を埋め込むダマシン(damascene)法が知られている。配線の微細化が進むと、幅が狭くアスペクト比の高い溝や孔に銅を埋め込むことが求められる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−7049号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

高い歩留まりを実現できる半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0005】

実施形態によれば、半導体装置の製造方法は、基板上の絶縁層に形成された第1の凹部および前記第1の凹部よりも幅が狭い第2の凹部に、前記基板を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜を形成する工程を備えている。また、前記半導体装置の製造方法は、前記第1の銅膜上に、不純物濃度が前記第1の銅膜よりも高い第2の銅膜を、前記第1の銅膜の形成時よりも流動性が小さい状態で形成する工程を備えている。

【図面の簡単な説明】

【0006】

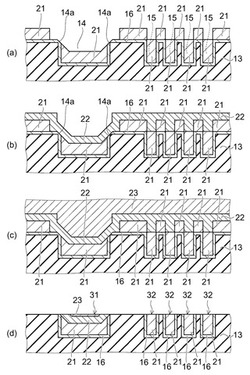

【図1】第1実施形態の半導体装置の製造方法を示す模式断面図。

【図2】第1実施形態の半導体装置の製造方法を示す模式断面図。

【図3】第2実施形態の半導体装置の製造方法を示す模式断面図。

【図4】スパッタ装置の模式図。

【発明を実施するための形態】

【0007】

以下、図面を参照し、実施形態について説明する。なお、各図面中、同じ要素には同じ符号を付している。

【0008】

実施形態の半導体装置の製造方法は、絶縁層に形成された溝または孔などの凹部に銅を埋め込む工程、いわゆるダマシン法による銅配線の形成工程を有する。

【0009】

凹部内に銅を埋め込むにあたって、電解めっき法は埋め込み性に優れる。電解めっき法は、核付層(シード層)と呼ばれる銅膜を形成した基板を陰極に用いて、めっき液中に含まれる銅イオンをシード層上に析出させる。この電解めっき法による銅の埋め込み性は、凹部に形成するシード層の被覆性に大きく依存し、シード層の被覆不良が生じると、銅の埋め込み不良(ボイド)の原因になり得る。

【0010】

そこで、以下に説明する実施形態によれば、電解めっきにおけるシード層として機能する銅膜を、相対的に幅が異なる複数の凹部に同時に被覆性良く形成できる方法が提供される。

【0011】

(第1実施形態)

図1(a)〜図2(d)は、第1実施形態の半導体装置の製造方法における銅配線の形成方法を示す模式断面図である。

【0012】

図1(a)に示すように、基板11上に絶縁膜12が形成され、さらにその絶縁膜12上に絶縁層13が形成される。基板11は、例えばシリコン基板であり、図示しないトランジスタなどが形成されている。

【0013】

絶縁膜12は、例えば、シリコン基板表面に熱酸化法により形成されたシリコン酸化膜であり、膜厚は20nmほどである。絶縁層13は、例えば、シリコン酸化膜よりも低誘電率のSiOC系材料からなり、膜厚は300nmほどである。絶縁層13は、例えば、CVD(chemical vapor deposition)法で形成される。

【0014】

絶縁層13上には図示しないレジストマスクが形成され、そのレジストマスクを用いたRIE(Reactive Ion Etching)により、図1(b)に示すように、絶縁層13に第1の凹部14と第2の凹部15が形成される。

【0015】

第1の凹部14及び第2の凹部15は、溝または孔であり、ともに深さは例えば250nmである。第1の凹部14の幅は例えば500nmであり、第2の凹部15の幅は、第1の凹部14の幅よりも狭く、例えば50nmである。

【0016】

レジストマスクは例えばウェットプロセスで除去され、その後、図1(c)に示すように、第1の凹部14の内壁、第2の凹部15の内壁、および絶縁層13の上面に沿って、コンフォーマルにバリアメタル16が形成される。バリアメタル16は、例えば、スパッタ法により形成されたタンタル膜であり、膜厚は15nmほどである。

【0017】

バリアメタル16は、第1の凹部14内及び第2の凹部15内に埋め込まれる銅との密着性に優れ、また銅の基板11側への拡散を防止する。なお、バリアメタル16としては、タンタル以外にも、窒化チタン、窒化タンタル、窒化タングステンなどを用いることもできる。

【0018】

バリアメタル16上には、図2(b)に示す、第1の銅膜21及び第2の銅膜22が形成される。これら第1の銅膜21及び第2の銅膜22は、スパッタ法により形成される。

【0019】

図4は、第1の銅膜21及び第2の銅膜22を形成するスパッタ装置の一例を表す模式図である。

【0020】

処理室51内に、銅ターゲット54とウェーハ10とが対向配置される。ウェーハ10は、第1の銅膜21及び第2の銅膜22の成膜対象であり、前述した図1(c)に示す構造を有し、基板11側がウェーハ支持部52上に支持される。ウェーハ支持部52には、基板11を加熱可能な加熱装置53が設けられている。あるいは、加熱装置53は、ウェーハ支持部52とは別に設けてもよい。

【0021】

また、処理室51内には、銅ターゲット54とは別に、チタンターゲット55が設けられている。チタンターゲット55は、処理室51の側壁側で、ウェーハ10の外周方向に沿って設けられている。チタンターゲット55は、少なくとも2つに(電気的に)分割されている。そして、ウェーハ10の中心軸を挟んで対向するチタンターゲット55間に放電を生起可能となっている。

【0022】

処理室51内には、ガス導入路56を通じて所望のガスが導入される。また、排気路57を通じた排気により、処理室51内は大気から遮断された減圧雰囲気にされる。

【0023】

上記スパッタ装置を用いて、まず図2(a)に示すように、第1の銅膜21がスパッタ成膜される。このとき、銅ターゲット54とウェーハ支持部52間に放電を生じさせ、チタンターゲット55間には放電を生じさせない。したがって、銅ターゲット54からスパッタされた銅によって、放電ガスに起因する元素以外にほとんど不純物を含まない第1の銅膜21が形成される。第1の銅膜21におけるチタン組成比は、0.01(atomic percent)よりも低い。

【0024】

また、第1の銅膜21のスパッタ成膜時、加熱装置53によって基板11を、銅が流動可能なリフロー温度に加熱している。このリフロー温度は、40℃以上であり、本実施形態では約50℃に加熱している。

【0025】

特に、相対的に幅が狭いあるいはアスペクト比が高い第2の凹部15の底部側に到達した銅粒子が流動して凝集することで、その底部側の銅膜被覆性が向上する。第1の銅膜21のスパッタ成膜は、その膜厚が例えば50nmになるまで続けられる。この結果、第2の凹部15は、ボイド(空孔)を形成することなく第1の銅膜21で完全に埋め込まれる。

【0026】

相対的に幅の大きな第1の凹部14内は、第1の銅膜21で完全に埋め込まれるに至っていない。また、幅の広い第1の凹部14では、スパッタ時のダメージや、銅の凝集により、開口側のコーナー部14aで、第1の銅膜21の被覆不良が発生しやすい傾向がある。

【0027】

コーナー部14aに飛来した銅粒子は、体積のより大きな部分(絶縁層13上面の銅および第1の凹部14内の銅)に引っ張られて流動しやすく、コーナー部14aにおける銅の量が不足しやすい。コーナー部14aの銅が不足し、そのコーナー部14aでバリアメタル16もしくは絶縁層13が露出すると、その後の電解めっき時にコーナー部14aで銅が析出せず、あるいは銅膜の密着力が低下し、ボイドの原因になり得る。

【0028】

銅膜をリフローさせずに形成するとコーナー部14aでの銅の流動は起きないが、微細幅の第2の凹部15内への銅膜の埋め込み性が低下する。

【0029】

そこで、第1実施形態では、第1の銅膜21の形成後、図2(b)に示すように、第1の銅膜21上に、不純物濃度が第1の銅膜21よりも高い第2の銅膜22を形成する。

【0030】

第2の銅膜22は、銅とチタンとの合金膜であり、銅の凝集を抑制する不純物としてチタンを例えば0.01(atomic percent)以上含む。

【0031】

第2の銅膜22の成膜時、図4に示すスパッタ装置におけるチタンターゲット55間にも放電を起こす。これにより、銅ターゲット54からスパッタされた銅と、チタンターゲット55からスパッタされたチタンとの合金膜が第1の銅膜21上に形成される。

【0032】

第2の銅膜22は、第1の銅膜21のスパッタ成膜時と同じ処理室51内で、大気開放されることなく続けてスパッタ成膜される。また、基板11の温度は上記リフロー温度に保持されている。

【0033】

第2の銅膜22の膜厚は、例えば30nmにされる。前工程で第1の銅膜21の被覆不良が生じていたコーナー部14aに、高い密着力で第2の銅膜22が形成される。第2の銅膜22の成膜時、基板温度はリフロー温度に保持されているが、第2の銅膜22における不純物であるチタンの濃度(組成比)は第1の銅膜21よりも高い。

【0034】

そのため、第2の銅膜22では銅の流動化による銅の凝集が抑えられ、第1の銅膜21成膜時よりも流動性が小さい状態で第2の銅膜22を形成できるので、コーナー部14aを確実に被覆することができる。

【0035】

第2の銅膜22成膜時の基板温度を第1の銅膜21成膜時の基板温度から下げることなく、第1の銅膜21及び第2の銅膜22を同じ処理室51内で続けてスパッタ成膜することができるため、高い生産性を実現できる。すなわち、第1の銅膜21の形成後、基板温度をリフロー温度よりも低くする過程が不要であり、別の処理室にウェーハ10を入れ替えることも不要である。

【0036】

第2の銅膜22の形成後、第1の銅膜21及び第2の銅膜22をシード層として用いた電解めっき法により、そのシード層上に図2(c)に示すように第3の銅膜(銅めっき膜)23を形成する。例えば、第3の銅膜23は800nmの膜厚にされる。

【0037】

第3の銅膜23の形成後、例えばCMP(Chemical Mechanical Polishing)法により、第3の銅膜23の上面側から少なくとも絶縁層13に達するまで研磨して平坦化する。

【0038】

これにより、図2(d)に示すように、絶縁層13に埋め込まれた相対的に幅の異なる第1の銅配線31と第2の銅配線32が形成される。

【0039】

ここで、第1実施形態、第1比較例および第2比較例について、ボイド発生率を比較評価した。その結果を、表1に表す。

【0040】

【表1】

【0041】

第1実施形態では、前述したように、基板温度を銅のリフロー温度よりも高い50℃に保持した状態で、幅が500nmの配線溝及び幅が50nmの配線溝に、50nmの膜厚で第1の銅膜21をスパッタ成膜した後、30nmの膜厚で第2の銅膜22をスパッタ成膜した。第1の銅膜21におけるチタン組成比は0.01(atomic percent)より低く、第2の銅膜22におけるチタン組成比は0.01(atomic percent)以上である。その後、第1の銅膜21及び第2の銅膜22をシード層とした電解めっき法により、第3の銅膜(銅めっき膜)23を800nmの膜厚で形成した。

【0042】

第1比較例では、基板温度を銅のリフロー温度よりも低い20℃に保持した状態で、幅が500nmの配線溝及び幅が50nmの配線溝に、チタン組成比が0.01(atomic percent)より低い銅膜を80nmの膜厚でスパッタ成膜した。その後、その銅膜をシード層とした電解めっき法により、銅めっき膜を800nmの膜厚で形成した。

【0043】

第2比較例では、基板温度を銅のリフロー温度よりも高い50℃に保持した状態で、幅が500nmの配線溝及び幅が50nmの配線溝に、チタン組成比が0.01(atomic percent)より低い銅膜を80nmの膜厚でスパッタ成膜した。その後、その銅膜をシード層とした電解めっき法により、銅めっき膜を800nmの膜厚で形成した。

【0044】

第1実施形態、第1比較例および第2比較例ともに、FIB(Focused Ion Beam)によるエッチングで配線溝断面を切り出した後に、SEM(Scanning Electron Microscope)で観察するFIB−SEM解析でボイド(空孔)の有無を確認した。

【0045】

幅が500nmの配線100本と、幅が50nmの配線100本をそれぞれ観察した。表1におけるボイド発生率は、それぞれの100本の配線のうちボイドが確認された本数に対応する。

【0046】

幅が50nmの配線についてのボイド発生率は、第1比較例で100%、第2比較例及び第1実施形態で0%だった。第1比較例では、基板温度が銅のリフロー温度よりも低いため、銅の流動化が起きず、幅が50nmの配線溝が銅で完全に埋め込まれることなくその配線溝の間口が閉塞してしまった。

【0047】

幅が500nmの配線についてのボイド発生率は、第1比較例及び第1実施形態で0%、第2比較例で74%だった。第2比較例では、幅が500nmの配線溝の開口側のコーナー部で銅の流動化によってシード層の被覆不良が生じ、これがボイドの原因になった。

【0048】

第1実施形態によれば、相対的に幅の異なる第1の凹部14と第2の凹部15とに同時に銅を埋め込むにあたって、第1の銅膜21をリフロー温度下のスパッタ法によって形成した後、基板温度の低下ではなく、不純物添加によって流動化を抑制された第2の銅膜22を形成する。これにより、生産性を低下させることなく、第1の凹部14及び第2の凹部15への銅の埋め込み性を向上させて、高い歩留まりが得られる。

【0049】

なお、第2の銅膜22におけるチタン濃度(組成比)を、0.01(atomic percent)より低くした場合には銅の凝集が生じたが、0.01(atomic percent)以上にした場合には銅の凝集が生じなかったことを実験により確認できた。したがって、第2の銅膜22におけるチタン濃度(組成比)は、0.01(atomic percent)以上が望ましい。

【0050】

第1実施形態によれば、相対的にチタン濃度が低く抵抗が低い第1の銅膜21の膜厚を、第2の銅膜22の膜厚よりも厚くすることで、埋込銅配線全体の抵抗上昇を抑えることができる。第2の銅膜22の膜厚は、相対的に幅が広い第1の凹部14のコーナー部14aを確実に被覆できる膜厚で十分である。

【0051】

(第2実施形態)

図3は、第2実施形態の半導体装置の製造方法における銅配線の形成方法を示す模式断面図である。図3は、第1実施形態における図2(b)に示す工程に対応する。

【0052】

第2実施形態では、第2の銅膜の形成工程以外は、第1の実施形態と同じである。すなわち、第2実施形態では、第1の銅膜21の形成後、炭素を含有するガス雰囲気中でのスパッタ法により、炭素を不純物として含む第2の銅膜42を形成する。

【0053】

例えば、処理室内にメタンガスを10sccmの流量で導入して、銅ターゲットを用いたスパッタ成膜を行う。これにより、第2の銅膜42に炭素が含有される。

【0054】

なお、炭素を含有するガスは、メタン以外に、例えば、エタン、エチレン、アセチレン、プロパン、メチルアセチレン、メチルアミン、ジメチルアミンなども用いることができる。

【0055】

第2実施形態においても第2の銅膜42の成膜時、基板温度はリフロー温度に保持されている。第2の銅膜42における不純物である炭素の濃度(組成比)は第1の銅膜21よりも高い。そのため、第2の銅膜42では銅の流動化による銅の凝集が抑えられ、幅が広い第1の凹部14のコーナー部14aを第2の銅膜42で確実に被覆することができる。

【0056】

第2実施形態においても、第2の銅膜42成膜時の基板温度を第1の銅膜21成膜時の基板温度から下げることなく、第1の銅膜21及び第2の銅膜42を同じ処理室内で続けてスパッタ成膜することができるため、高い生産性を実現できる。

【0057】

第2の銅膜42の形成後、第1実施形態と同様に、第1の銅膜21及び第2の銅膜42をシード層として用いた電解めっき法により、そのシード層上に第3の銅膜(銅めっき膜)を例えば800nmの膜厚で形成する。

【0058】

そして、第3の銅膜形成後、例えばCMP法により、第3の銅膜の上面側から少なくとも絶縁層13に達するまで研磨して平坦化する。これにより、第2実施形態においても、絶縁層13に埋め込まれた相対的に幅の異なる第1の銅配線と第2の銅配線が形成される。

【0059】

また、第2実施形態についても、前述した第1実施形態、第1比較例および第2比較例と同様のボイド発生率を評価した。その結果を前述した表1に表す。

【0060】

第2実施形態では、前述したように、基板温度を銅のリフロー温度よりも高い50℃に保持した状態で、幅が500nmの配線溝及び幅が50nmの配線溝に、50nmの膜厚で第1の銅膜21をスパッタ成膜した後、30nmの膜厚で第2の銅膜42をスパッタ成膜した。第1の銅膜21における炭素組成比は0.01(atomic percent)より低く、第2の銅膜42における炭素組成比は0.01(atomic percent)以上である。その後、第1の銅膜21及び第2の銅膜42をシード層とした電解めっき法により、第3の銅膜(銅めっき膜)を800nmの膜厚で形成した。

【0061】

第2実施形態では、幅が50nmの配線についてのボイド発生率および幅が500nmの配線についてのボイド発生率はともに0%だった。

【0062】

第2実施形態においても、相対的に幅の異なる第1の凹部14と第2の凹部15とに同時に銅を埋め込むにあたって、第1の銅膜21をリフロー温度下のスパッタ法によって形成した後、基板温度の低下ではなく、不純物添加によって流動化を抑制された第2の銅膜42を形成する。これにより、生産性を低下させることなく、第1の凹部14及び第2の凹部15への銅の埋め込み性を向上させて、高い歩留まりが得られる。

【0063】

なお、第2の銅膜42における炭素濃度(組成比)を、0.01(atomic percent)より低くした場合には銅の凝集が生じたが、0.01(atomic percent)以上にした場合には銅の凝集が生じなかったことを実験により確認できた。したがって、第2の銅膜42における炭素濃度(組成比)は、0.01(atomic percent)以上が望ましい。

【0064】

相対的に炭素濃度が低く抵抗が低い第1の銅膜21の膜厚を、第2の銅膜42の膜厚よりも厚くすることで、埋込銅配線全体の抵抗上昇を抑えることができる。

【0065】

前述した各実施形態において、スパッタ法でシード層を形成し、そのシード層を使って電解めっき法により銅めっき膜を形成することで、低コストで銅の埋込配線を形成できる。なお、第1実施形態における第2の銅膜22の形成にあたって、銅とチタンの合金ターゲットを使ってスパッタ成膜を行ってもよい。また、不純物としてチタン以外にアルミニウムを用いてもよく、チタン及びアルミニウムの少なくとも1種を含む第2の銅膜22を成膜することで、被覆性良くシード層を形成することができる。

【0066】

あるいは、CVD(chemical vapor deposition)法によってシード層を形成してもよい。例えば、銅の有機金属錯体あるいは銅のハロゲン化物を原料に用いたCVD法によって、銅膜を形成することができる。

【0067】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0068】

10…ウェーハ、11…基板、13…絶縁層、14…第1の凹部、15…第2の凹部、16…バリアメタル、21…第1の銅膜、22,42…第2の銅膜、23…第3の銅膜、31…第1の銅配線、32…第2の銅配線、51…処理室、54…銅ターゲット、55…チタンターゲット

【技術分野】

【0001】

本発明の実施形態は、半導体装置の製造方法に関する。

【背景技術】

【0002】

銅配線の形成方法として、絶縁層に形成した配線溝に銅を埋め込むダマシン(damascene)法が知られている。配線の微細化が進むと、幅が狭くアスペクト比の高い溝や孔に銅を埋め込むことが求められる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−7049号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

高い歩留まりを実現できる半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0005】

実施形態によれば、半導体装置の製造方法は、基板上の絶縁層に形成された第1の凹部および前記第1の凹部よりも幅が狭い第2の凹部に、前記基板を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜を形成する工程を備えている。また、前記半導体装置の製造方法は、前記第1の銅膜上に、不純物濃度が前記第1の銅膜よりも高い第2の銅膜を、前記第1の銅膜の形成時よりも流動性が小さい状態で形成する工程を備えている。

【図面の簡単な説明】

【0006】

【図1】第1実施形態の半導体装置の製造方法を示す模式断面図。

【図2】第1実施形態の半導体装置の製造方法を示す模式断面図。

【図3】第2実施形態の半導体装置の製造方法を示す模式断面図。

【図4】スパッタ装置の模式図。

【発明を実施するための形態】

【0007】

以下、図面を参照し、実施形態について説明する。なお、各図面中、同じ要素には同じ符号を付している。

【0008】

実施形態の半導体装置の製造方法は、絶縁層に形成された溝または孔などの凹部に銅を埋め込む工程、いわゆるダマシン法による銅配線の形成工程を有する。

【0009】

凹部内に銅を埋め込むにあたって、電解めっき法は埋め込み性に優れる。電解めっき法は、核付層(シード層)と呼ばれる銅膜を形成した基板を陰極に用いて、めっき液中に含まれる銅イオンをシード層上に析出させる。この電解めっき法による銅の埋め込み性は、凹部に形成するシード層の被覆性に大きく依存し、シード層の被覆不良が生じると、銅の埋め込み不良(ボイド)の原因になり得る。

【0010】

そこで、以下に説明する実施形態によれば、電解めっきにおけるシード層として機能する銅膜を、相対的に幅が異なる複数の凹部に同時に被覆性良く形成できる方法が提供される。

【0011】

(第1実施形態)

図1(a)〜図2(d)は、第1実施形態の半導体装置の製造方法における銅配線の形成方法を示す模式断面図である。

【0012】

図1(a)に示すように、基板11上に絶縁膜12が形成され、さらにその絶縁膜12上に絶縁層13が形成される。基板11は、例えばシリコン基板であり、図示しないトランジスタなどが形成されている。

【0013】

絶縁膜12は、例えば、シリコン基板表面に熱酸化法により形成されたシリコン酸化膜であり、膜厚は20nmほどである。絶縁層13は、例えば、シリコン酸化膜よりも低誘電率のSiOC系材料からなり、膜厚は300nmほどである。絶縁層13は、例えば、CVD(chemical vapor deposition)法で形成される。

【0014】

絶縁層13上には図示しないレジストマスクが形成され、そのレジストマスクを用いたRIE(Reactive Ion Etching)により、図1(b)に示すように、絶縁層13に第1の凹部14と第2の凹部15が形成される。

【0015】

第1の凹部14及び第2の凹部15は、溝または孔であり、ともに深さは例えば250nmである。第1の凹部14の幅は例えば500nmであり、第2の凹部15の幅は、第1の凹部14の幅よりも狭く、例えば50nmである。

【0016】

レジストマスクは例えばウェットプロセスで除去され、その後、図1(c)に示すように、第1の凹部14の内壁、第2の凹部15の内壁、および絶縁層13の上面に沿って、コンフォーマルにバリアメタル16が形成される。バリアメタル16は、例えば、スパッタ法により形成されたタンタル膜であり、膜厚は15nmほどである。

【0017】

バリアメタル16は、第1の凹部14内及び第2の凹部15内に埋め込まれる銅との密着性に優れ、また銅の基板11側への拡散を防止する。なお、バリアメタル16としては、タンタル以外にも、窒化チタン、窒化タンタル、窒化タングステンなどを用いることもできる。

【0018】

バリアメタル16上には、図2(b)に示す、第1の銅膜21及び第2の銅膜22が形成される。これら第1の銅膜21及び第2の銅膜22は、スパッタ法により形成される。

【0019】

図4は、第1の銅膜21及び第2の銅膜22を形成するスパッタ装置の一例を表す模式図である。

【0020】

処理室51内に、銅ターゲット54とウェーハ10とが対向配置される。ウェーハ10は、第1の銅膜21及び第2の銅膜22の成膜対象であり、前述した図1(c)に示す構造を有し、基板11側がウェーハ支持部52上に支持される。ウェーハ支持部52には、基板11を加熱可能な加熱装置53が設けられている。あるいは、加熱装置53は、ウェーハ支持部52とは別に設けてもよい。

【0021】

また、処理室51内には、銅ターゲット54とは別に、チタンターゲット55が設けられている。チタンターゲット55は、処理室51の側壁側で、ウェーハ10の外周方向に沿って設けられている。チタンターゲット55は、少なくとも2つに(電気的に)分割されている。そして、ウェーハ10の中心軸を挟んで対向するチタンターゲット55間に放電を生起可能となっている。

【0022】

処理室51内には、ガス導入路56を通じて所望のガスが導入される。また、排気路57を通じた排気により、処理室51内は大気から遮断された減圧雰囲気にされる。

【0023】

上記スパッタ装置を用いて、まず図2(a)に示すように、第1の銅膜21がスパッタ成膜される。このとき、銅ターゲット54とウェーハ支持部52間に放電を生じさせ、チタンターゲット55間には放電を生じさせない。したがって、銅ターゲット54からスパッタされた銅によって、放電ガスに起因する元素以外にほとんど不純物を含まない第1の銅膜21が形成される。第1の銅膜21におけるチタン組成比は、0.01(atomic percent)よりも低い。

【0024】

また、第1の銅膜21のスパッタ成膜時、加熱装置53によって基板11を、銅が流動可能なリフロー温度に加熱している。このリフロー温度は、40℃以上であり、本実施形態では約50℃に加熱している。

【0025】

特に、相対的に幅が狭いあるいはアスペクト比が高い第2の凹部15の底部側に到達した銅粒子が流動して凝集することで、その底部側の銅膜被覆性が向上する。第1の銅膜21のスパッタ成膜は、その膜厚が例えば50nmになるまで続けられる。この結果、第2の凹部15は、ボイド(空孔)を形成することなく第1の銅膜21で完全に埋め込まれる。

【0026】

相対的に幅の大きな第1の凹部14内は、第1の銅膜21で完全に埋め込まれるに至っていない。また、幅の広い第1の凹部14では、スパッタ時のダメージや、銅の凝集により、開口側のコーナー部14aで、第1の銅膜21の被覆不良が発生しやすい傾向がある。

【0027】

コーナー部14aに飛来した銅粒子は、体積のより大きな部分(絶縁層13上面の銅および第1の凹部14内の銅)に引っ張られて流動しやすく、コーナー部14aにおける銅の量が不足しやすい。コーナー部14aの銅が不足し、そのコーナー部14aでバリアメタル16もしくは絶縁層13が露出すると、その後の電解めっき時にコーナー部14aで銅が析出せず、あるいは銅膜の密着力が低下し、ボイドの原因になり得る。

【0028】

銅膜をリフローさせずに形成するとコーナー部14aでの銅の流動は起きないが、微細幅の第2の凹部15内への銅膜の埋め込み性が低下する。

【0029】

そこで、第1実施形態では、第1の銅膜21の形成後、図2(b)に示すように、第1の銅膜21上に、不純物濃度が第1の銅膜21よりも高い第2の銅膜22を形成する。

【0030】

第2の銅膜22は、銅とチタンとの合金膜であり、銅の凝集を抑制する不純物としてチタンを例えば0.01(atomic percent)以上含む。

【0031】

第2の銅膜22の成膜時、図4に示すスパッタ装置におけるチタンターゲット55間にも放電を起こす。これにより、銅ターゲット54からスパッタされた銅と、チタンターゲット55からスパッタされたチタンとの合金膜が第1の銅膜21上に形成される。

【0032】

第2の銅膜22は、第1の銅膜21のスパッタ成膜時と同じ処理室51内で、大気開放されることなく続けてスパッタ成膜される。また、基板11の温度は上記リフロー温度に保持されている。

【0033】

第2の銅膜22の膜厚は、例えば30nmにされる。前工程で第1の銅膜21の被覆不良が生じていたコーナー部14aに、高い密着力で第2の銅膜22が形成される。第2の銅膜22の成膜時、基板温度はリフロー温度に保持されているが、第2の銅膜22における不純物であるチタンの濃度(組成比)は第1の銅膜21よりも高い。

【0034】

そのため、第2の銅膜22では銅の流動化による銅の凝集が抑えられ、第1の銅膜21成膜時よりも流動性が小さい状態で第2の銅膜22を形成できるので、コーナー部14aを確実に被覆することができる。

【0035】

第2の銅膜22成膜時の基板温度を第1の銅膜21成膜時の基板温度から下げることなく、第1の銅膜21及び第2の銅膜22を同じ処理室51内で続けてスパッタ成膜することができるため、高い生産性を実現できる。すなわち、第1の銅膜21の形成後、基板温度をリフロー温度よりも低くする過程が不要であり、別の処理室にウェーハ10を入れ替えることも不要である。

【0036】

第2の銅膜22の形成後、第1の銅膜21及び第2の銅膜22をシード層として用いた電解めっき法により、そのシード層上に図2(c)に示すように第3の銅膜(銅めっき膜)23を形成する。例えば、第3の銅膜23は800nmの膜厚にされる。

【0037】

第3の銅膜23の形成後、例えばCMP(Chemical Mechanical Polishing)法により、第3の銅膜23の上面側から少なくとも絶縁層13に達するまで研磨して平坦化する。

【0038】

これにより、図2(d)に示すように、絶縁層13に埋め込まれた相対的に幅の異なる第1の銅配線31と第2の銅配線32が形成される。

【0039】

ここで、第1実施形態、第1比較例および第2比較例について、ボイド発生率を比較評価した。その結果を、表1に表す。

【0040】

【表1】

【0041】

第1実施形態では、前述したように、基板温度を銅のリフロー温度よりも高い50℃に保持した状態で、幅が500nmの配線溝及び幅が50nmの配線溝に、50nmの膜厚で第1の銅膜21をスパッタ成膜した後、30nmの膜厚で第2の銅膜22をスパッタ成膜した。第1の銅膜21におけるチタン組成比は0.01(atomic percent)より低く、第2の銅膜22におけるチタン組成比は0.01(atomic percent)以上である。その後、第1の銅膜21及び第2の銅膜22をシード層とした電解めっき法により、第3の銅膜(銅めっき膜)23を800nmの膜厚で形成した。

【0042】

第1比較例では、基板温度を銅のリフロー温度よりも低い20℃に保持した状態で、幅が500nmの配線溝及び幅が50nmの配線溝に、チタン組成比が0.01(atomic percent)より低い銅膜を80nmの膜厚でスパッタ成膜した。その後、その銅膜をシード層とした電解めっき法により、銅めっき膜を800nmの膜厚で形成した。

【0043】

第2比較例では、基板温度を銅のリフロー温度よりも高い50℃に保持した状態で、幅が500nmの配線溝及び幅が50nmの配線溝に、チタン組成比が0.01(atomic percent)より低い銅膜を80nmの膜厚でスパッタ成膜した。その後、その銅膜をシード層とした電解めっき法により、銅めっき膜を800nmの膜厚で形成した。

【0044】

第1実施形態、第1比較例および第2比較例ともに、FIB(Focused Ion Beam)によるエッチングで配線溝断面を切り出した後に、SEM(Scanning Electron Microscope)で観察するFIB−SEM解析でボイド(空孔)の有無を確認した。

【0045】

幅が500nmの配線100本と、幅が50nmの配線100本をそれぞれ観察した。表1におけるボイド発生率は、それぞれの100本の配線のうちボイドが確認された本数に対応する。

【0046】

幅が50nmの配線についてのボイド発生率は、第1比較例で100%、第2比較例及び第1実施形態で0%だった。第1比較例では、基板温度が銅のリフロー温度よりも低いため、銅の流動化が起きず、幅が50nmの配線溝が銅で完全に埋め込まれることなくその配線溝の間口が閉塞してしまった。

【0047】

幅が500nmの配線についてのボイド発生率は、第1比較例及び第1実施形態で0%、第2比較例で74%だった。第2比較例では、幅が500nmの配線溝の開口側のコーナー部で銅の流動化によってシード層の被覆不良が生じ、これがボイドの原因になった。

【0048】

第1実施形態によれば、相対的に幅の異なる第1の凹部14と第2の凹部15とに同時に銅を埋め込むにあたって、第1の銅膜21をリフロー温度下のスパッタ法によって形成した後、基板温度の低下ではなく、不純物添加によって流動化を抑制された第2の銅膜22を形成する。これにより、生産性を低下させることなく、第1の凹部14及び第2の凹部15への銅の埋め込み性を向上させて、高い歩留まりが得られる。

【0049】

なお、第2の銅膜22におけるチタン濃度(組成比)を、0.01(atomic percent)より低くした場合には銅の凝集が生じたが、0.01(atomic percent)以上にした場合には銅の凝集が生じなかったことを実験により確認できた。したがって、第2の銅膜22におけるチタン濃度(組成比)は、0.01(atomic percent)以上が望ましい。

【0050】

第1実施形態によれば、相対的にチタン濃度が低く抵抗が低い第1の銅膜21の膜厚を、第2の銅膜22の膜厚よりも厚くすることで、埋込銅配線全体の抵抗上昇を抑えることができる。第2の銅膜22の膜厚は、相対的に幅が広い第1の凹部14のコーナー部14aを確実に被覆できる膜厚で十分である。

【0051】

(第2実施形態)

図3は、第2実施形態の半導体装置の製造方法における銅配線の形成方法を示す模式断面図である。図3は、第1実施形態における図2(b)に示す工程に対応する。

【0052】

第2実施形態では、第2の銅膜の形成工程以外は、第1の実施形態と同じである。すなわち、第2実施形態では、第1の銅膜21の形成後、炭素を含有するガス雰囲気中でのスパッタ法により、炭素を不純物として含む第2の銅膜42を形成する。

【0053】

例えば、処理室内にメタンガスを10sccmの流量で導入して、銅ターゲットを用いたスパッタ成膜を行う。これにより、第2の銅膜42に炭素が含有される。

【0054】

なお、炭素を含有するガスは、メタン以外に、例えば、エタン、エチレン、アセチレン、プロパン、メチルアセチレン、メチルアミン、ジメチルアミンなども用いることができる。

【0055】

第2実施形態においても第2の銅膜42の成膜時、基板温度はリフロー温度に保持されている。第2の銅膜42における不純物である炭素の濃度(組成比)は第1の銅膜21よりも高い。そのため、第2の銅膜42では銅の流動化による銅の凝集が抑えられ、幅が広い第1の凹部14のコーナー部14aを第2の銅膜42で確実に被覆することができる。

【0056】

第2実施形態においても、第2の銅膜42成膜時の基板温度を第1の銅膜21成膜時の基板温度から下げることなく、第1の銅膜21及び第2の銅膜42を同じ処理室内で続けてスパッタ成膜することができるため、高い生産性を実現できる。

【0057】

第2の銅膜42の形成後、第1実施形態と同様に、第1の銅膜21及び第2の銅膜42をシード層として用いた電解めっき法により、そのシード層上に第3の銅膜(銅めっき膜)を例えば800nmの膜厚で形成する。

【0058】

そして、第3の銅膜形成後、例えばCMP法により、第3の銅膜の上面側から少なくとも絶縁層13に達するまで研磨して平坦化する。これにより、第2実施形態においても、絶縁層13に埋め込まれた相対的に幅の異なる第1の銅配線と第2の銅配線が形成される。

【0059】

また、第2実施形態についても、前述した第1実施形態、第1比較例および第2比較例と同様のボイド発生率を評価した。その結果を前述した表1に表す。

【0060】

第2実施形態では、前述したように、基板温度を銅のリフロー温度よりも高い50℃に保持した状態で、幅が500nmの配線溝及び幅が50nmの配線溝に、50nmの膜厚で第1の銅膜21をスパッタ成膜した後、30nmの膜厚で第2の銅膜42をスパッタ成膜した。第1の銅膜21における炭素組成比は0.01(atomic percent)より低く、第2の銅膜42における炭素組成比は0.01(atomic percent)以上である。その後、第1の銅膜21及び第2の銅膜42をシード層とした電解めっき法により、第3の銅膜(銅めっき膜)を800nmの膜厚で形成した。

【0061】

第2実施形態では、幅が50nmの配線についてのボイド発生率および幅が500nmの配線についてのボイド発生率はともに0%だった。

【0062】

第2実施形態においても、相対的に幅の異なる第1の凹部14と第2の凹部15とに同時に銅を埋め込むにあたって、第1の銅膜21をリフロー温度下のスパッタ法によって形成した後、基板温度の低下ではなく、不純物添加によって流動化を抑制された第2の銅膜42を形成する。これにより、生産性を低下させることなく、第1の凹部14及び第2の凹部15への銅の埋め込み性を向上させて、高い歩留まりが得られる。

【0063】

なお、第2の銅膜42における炭素濃度(組成比)を、0.01(atomic percent)より低くした場合には銅の凝集が生じたが、0.01(atomic percent)以上にした場合には銅の凝集が生じなかったことを実験により確認できた。したがって、第2の銅膜42における炭素濃度(組成比)は、0.01(atomic percent)以上が望ましい。

【0064】

相対的に炭素濃度が低く抵抗が低い第1の銅膜21の膜厚を、第2の銅膜42の膜厚よりも厚くすることで、埋込銅配線全体の抵抗上昇を抑えることができる。

【0065】

前述した各実施形態において、スパッタ法でシード層を形成し、そのシード層を使って電解めっき法により銅めっき膜を形成することで、低コストで銅の埋込配線を形成できる。なお、第1実施形態における第2の銅膜22の形成にあたって、銅とチタンの合金ターゲットを使ってスパッタ成膜を行ってもよい。また、不純物としてチタン以外にアルミニウムを用いてもよく、チタン及びアルミニウムの少なくとも1種を含む第2の銅膜22を成膜することで、被覆性良くシード層を形成することができる。

【0066】

あるいは、CVD(chemical vapor deposition)法によってシード層を形成してもよい。例えば、銅の有機金属錯体あるいは銅のハロゲン化物を原料に用いたCVD法によって、銅膜を形成することができる。

【0067】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0068】

10…ウェーハ、11…基板、13…絶縁層、14…第1の凹部、15…第2の凹部、16…バリアメタル、21…第1の銅膜、22,42…第2の銅膜、23…第3の銅膜、31…第1の銅配線、32…第2の銅配線、51…処理室、54…銅ターゲット、55…チタンターゲット

【特許請求の範囲】

【請求項1】

基板上の絶縁層に形成された第1の凹部および前記第1の凹部よりも幅が狭い第2の凹部に、前記基板を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜を形成する工程と、

前記第1の銅膜上に、不純物濃度が前記第1の銅膜よりも高い第2の銅膜を形成する工程と、

前記第1の銅膜及び前記第2の銅膜をシード層として用いた電解めっき法により、前記シード層上に第3の銅膜を形成する工程と、

を備え、

前記第1の銅膜及び前記第2の銅膜を、スパッタ法により同じ処理室内で続けて形成する半導体装置の製造方法。

【請求項2】

基板上の絶縁層に形成された第1の凹部および前記第1の凹部よりも幅が狭い第2の凹部に、前記基板を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜を形成する工程と、

前記第1の銅膜上に、不純物濃度が前記第1の銅膜よりも高い第2の銅膜を、前記第1の銅膜の形成時よりも流動性が小さい状態で形成する工程と、

を備えた半導体装置の製造方法。

【請求項3】

スパッタ法により、銅とチタン及びアルミニウムの少なくとも1種とを含む合金膜を前記第2の銅膜として形成する請求項2記載の半導体装置の製造方法。

【請求項4】

炭素を含有するガス雰囲気中でのスパッタ法により、前記炭素を不純物として含む前記第2の銅膜を形成する請求項2記載の半導体装置の製造方法。

【請求項5】

前記第1の銅膜及び前記第2の銅膜を、スパッタ法により同じ処理室内で続けて形成する請求項2〜4のいずれか1つに記載の半導体装置の製造方法。

【請求項1】

基板上の絶縁層に形成された第1の凹部および前記第1の凹部よりも幅が狭い第2の凹部に、前記基板を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜を形成する工程と、

前記第1の銅膜上に、不純物濃度が前記第1の銅膜よりも高い第2の銅膜を形成する工程と、

前記第1の銅膜及び前記第2の銅膜をシード層として用いた電解めっき法により、前記シード層上に第3の銅膜を形成する工程と、

を備え、

前記第1の銅膜及び前記第2の銅膜を、スパッタ法により同じ処理室内で続けて形成する半導体装置の製造方法。

【請求項2】

基板上の絶縁層に形成された第1の凹部および前記第1の凹部よりも幅が狭い第2の凹部に、前記基板を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜を形成する工程と、

前記第1の銅膜上に、不純物濃度が前記第1の銅膜よりも高い第2の銅膜を、前記第1の銅膜の形成時よりも流動性が小さい状態で形成する工程と、

を備えた半導体装置の製造方法。

【請求項3】

スパッタ法により、銅とチタン及びアルミニウムの少なくとも1種とを含む合金膜を前記第2の銅膜として形成する請求項2記載の半導体装置の製造方法。

【請求項4】

炭素を含有するガス雰囲気中でのスパッタ法により、前記炭素を不純物として含む前記第2の銅膜を形成する請求項2記載の半導体装置の製造方法。

【請求項5】

前記第1の銅膜及び前記第2の銅膜を、スパッタ法により同じ処理室内で続けて形成する請求項2〜4のいずれか1つに記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−105753(P2013−105753A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−246153(P2011−246153)

【出願日】平成23年11月10日(2011.11.10)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月10日(2011.11.10)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]