半導体装置の製造方法

【課題】接続孔部分における電気的特性のばらつきを低減することにより、半導体装置の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバ57において150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバ57において150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造技術に関し、特に、絶縁膜に開口された接続孔の内部に金属膜を埋め込む半導体装置の製造工程に適用して有効な技術に関するものである。

【背景技術】

【0002】

日本特許公開2003−324108号公報(対応米国はUSP6864183)には、三フッ化窒素ガス、フッ化水素ガス、六フッ化二炭素ガス、四フッ化炭素ガスおよび六フッ化硫黄ガスよりなる群から選ばれる少なくとも1種以上のフッ化系ガスとアルゴンガスとの混合ガスを用いてプラズマエッチングを行うことにより、シリコン基板およびゲート電極の表面に存在する自然酸化膜を除去する方法が開示されている(特許文献1参照)。

【0003】

また、日本特許公開平2−256235号公報(対応米国はUSP5030319)には、ハロゲン元素を含むガスと塩基性ガスとによりハロゲン塩を生成し、これを被処置体の酸化膜と反応させる、あるいはハロゲン塩ガスを直接酸化膜と反応させて、下地にダメージを与えることなく酸化膜を選択的にエッチング、除去する方法が開示されている(特許文献2参照)。

【0004】

また、日本特許公開平3−116727号公報には、表面に酸化膜の形成された半導体基板をフッ素原子を含むガス中に曝したのち、還元性ガス中あるいは不活性ガス中あるいは真空中でアニールすることにより、該酸化膜を除去するクリーニング方法が開示されている(特許文献3参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−324108号公報

【特許文献2】特開平2−256235号公報

【特許文献3】特開平3−116727号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

半導体装置の高集積化が進むにつれて、電界効果トランジスタはスケーリング則に従い微細化され、ゲートやソース・ドレインと配線とを繋ぐため、層間絶縁膜に形成される接続孔においては0.1μm以下の口径が要求されている。しかし、接続孔の底部に露出する導電材料の表面(例えばゲートを構成する導電膜、ソース・ドレインを構成する半導体領域、あるいは上記導電膜や半導体領域上に形成されるシリサイド層などの表面)には自然酸化膜が形成されやすく、上記接続孔の内部に金属膜を埋め込む際は、良好な導通をとるために自然酸化膜を除去する必要がある。特に、口径が0.1μm以下の微細な接続孔では、接続孔の底部の自然酸化膜の除去は難しく、従来から様々なクリーニング方法や処理装置等が提案されている。

【0007】

ところで、接続孔の底部に形成される自然酸化膜の厚さにはばらつきがある。このため、本発明者らは、オーバーエッチングすることなく接続孔の底部の自然酸化膜や不純物を完全に除去する方法として、接続孔を形成した後に、例えばHFガスとNH3ガスまたはNF3ガスとNH3ガス等の還元ガスを用いたドライクリーニング処理、あるいはNF3ガスとNH3ガスまたはNF3ガスとH2ガス等の還元ガスを含むArガスの反応性プラズマを用いたドライクリーニング処理を行っている。

【0008】

しかしながら、上記ドライクリーニング処理については、以下に説明する種々の技術的課題が存在する。

【0009】

ドライクリーニング処置を行った接続孔の底部および側面にはケイフッ化アンモニウム((NH4)2SiF6)が生成される。接続孔の内部には、一般にバリアメタル膜(例えばチタン膜上に窒化チタン膜を積み重ねた積層膜)を介して主導電材料となる金属膜が埋め込まれるが、上記生成物が残留していると、接続孔の底面においては、バリアメタル膜とその下の導電材料との接触抵抗がばらつき、接続孔の側面においては、バリアメタル膜が剥がれるなどの問題が生ずる。

【0010】

そこで、ドライクリーニング処理を行った接続孔部分を上記生成物の昇華温度である100℃程度で暖めることによって接続孔の底面および側面から生成物を除去する検討を行った。ところが、100℃程度の温度で接続孔部分を暖めても生成物を完全に昇華させることができず、上記問題を回避することはできないことが明らかとなった。これは、接続孔の底面および側面に生成する生成物の組成が全て(NH4)2SiF6ではなく、(NH4)2SiF6から僅かにずれた組成(非化学量論的組成の化合物、これらも混乱のないときは便宜的にケイフッ化アンモニウムまたは((NH4)2SiF6)で表示する)も含まれており、その組成が僅かにずれた生成物が100℃程度の温度では昇華せずに接続孔の底面および側面に残留したためと考えられる。

【0011】

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

一実施の形態によれば、絶縁膜に開口した接続孔の内部にバリアメタル膜を形成する前に、第1のチャンバに備わるウエハステージ上に半導体ウエハを置く工程と、ウエハステージの上方に設置されたシャワーヘッドを介して還元ガスを供給し、接続孔の内部をドライクリーニング処理する工程と、シャワーヘッドの加熱温度を利用した100から150℃の第1の温度で半導体ウエハを熱処理する工程と、半導体ウエハを第1のチャンバから第2のチャンバへ搬送する工程と、第2のチャンバにおいて150から400℃の第2の温度で半導体ウエハを熱処理する工程とを含むものである。

【発明の効果】

【0013】

一実施の形態によれば、接続孔部分における電気的特性のばらつきを低減することができるので、半導体装置の信頼性および製造歩留まりを向上させることができる。

【図面の簡単な説明】

【0014】

【図1】実施の形態1であるCMOSデバイスの製造工程を示す半導体基板の要部断面図である。

【図2】図1に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図3】図2に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図4】図3に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図5】(a)は図4に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図であり、(b)は同図(a)に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図6】実施の形態1によるバリアメタル膜の成膜装置の概略平面図である。

【図7】実施の形態1によるバリアメタル膜の成膜工程図である。

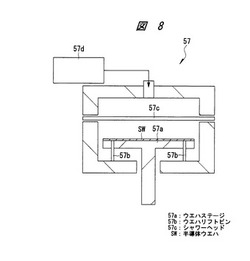

【図8】実施の形態1によるバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバの概略断面図である。

【図9】(a)、(b)および(c)は、それぞれ実施の形態1によるバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバにおける半導体ウエハの処理工程を説明するためのチャンバの概略断面図である。

【図10】nMISを形成した後に、ドライクリーニング処理および熱処理を半導体基板に施した場合のゲート電極と半導体基板との間に流れる電流と熱処理温度との関係を示すグラフ図である。

【図11】図5に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図12】図11に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図13】図12に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図14】図13に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図15】実施の形態2によるバリアメタル膜の成膜工程図である。

【図16】(a)、(b)および(c)は、それぞれ実施の形態2によるバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバにおける半導体ウエハの処理工程を説明するためのチャンバの概略断面図である。

【図17】(a)、(b)および(c)は、それぞれ実施の形態3によるバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバの概略断面図である。

【発明を実施するための形態】

【0015】

本実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、本実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。さらに、本実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、本実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0016】

また、本実施の形態においては、電界効果トランジスタを代表するMIS・FET(Metal Insulator Semiconductor Field Effect Transistor)をMISと略し、pチャネル型のMIS・FETをpMISと略し、nチャネル型のMIS・FETをnMISと略す。また、便宜的にMOSと記載しても非酸化膜を除外するものではない。また、本実施の形態において、ウエハと言うときは、Si(Silicon)単結晶ウエハを主とするが、それのみではなく、SOI(Silicon On Insulator)ウエハ、集積回路をその上に形成するための絶縁膜基板等を広く指すものとする。その形も円形またはほぼ円形のみでなく、正方形、長方形等も含むものとする。また、シリコン膜、シリコン部、シリコン部材等というときは、明らかにそうでないときまたはそうでない旨明示されているときを除き、純粋なシリコンばかりでなく、不純物を含むもの、SiGeまたはSiGeC等のシリコンを主要な成分の一つとする合金等(歪シリコンを含む)、添加物を含むものを含むことはいうまでもない。また、多結晶シリコン等というときも、明らかにそうでないときまたはそうでない旨明示されているときを除き、典型的なものばかりでなく、アモルファスシリコン等も含むことはいうまでもない。

【0017】

また、本実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本実施の形態を図面に基づいて詳細に説明する。

【0018】

また、ドライクリーニング技術に関しては、一之瀬らの日本国特許出願第2006−3704号(2006.1.11出願)、日本国特許出願第2006−12355号(2006.1.20出願)、日本国特許出願第2006−107780号(2006.4.10出願)に開示されているので、それと重複する部分については、原則として繰り返さないこことする。

【0019】

(実施の形態1)

実施の形態1によるCMOS(Complementary Metal Oxide Semiconductor)デバイスの製造方法を図1から図14を用いて説明する。図1から図5および図11から図14はCMOSデバイスの要部断面図、図6はバリアメタル成膜装置の概略平面図、図7はバリアメタル膜の成膜工程図、図8はバリアメタル成膜装置に備わるドライクリーニング処理用チャンバの概略断面図、図9(a)、(b)および(c)はそれぞれバリアメタル成膜装置に備わるドライクリーニング処理用チャンバにおける半導体ウエハの処理工程を説明するためのチャンバの概略断面図、図10はnMISを形成した後に、ドライクリーニング処理および熱処理を半導体基板に施した場合のゲート電極と半導体基板との間に流れる電流と熱処理温度との関係を示すグラフ図である。

【0020】

まず、図1に示すように、例えばp型の単結晶シリコンからなる半導体基板(半導体ウエハと称する平面略円形状の半導体の薄板)1を用意する。次に、半導体基板1の主面に素子分離領域4を形成する。素子分離領域4は、半導体基板1をエッチングして深さ0.35μmの溝を形成し、続いて半導体基板1の主面上にCVD(Chemical Vapor Deposition)法により絶縁膜、例えば酸化シリコン膜を堆積した後、溝の外部の酸化シリコン膜をCMP(Chemical Mechanical Polishing)法により除去することによって形成する。

【0021】

次に、半導体基板1のnMIS形成領域にp型不純物、例えばボロン(B)をイオン注入してp型ウェル6を形成し、半導体基板1のpMIS形成領域にn型不純物、例えばリン(P)をイオン注入してn型ウェル8を形成する。この後、p型ウェル6またはn型ウェル8にnMISまたはpMISのしきい値を制御するための不純物をイオン注入してもよい。

【0022】

次に、例えばフッ酸水溶液を用いたウェットエッチングにより半導体基板1の表面を洗浄した後、半導体基板1を熱酸化して、例えば厚さ5nmのゲート絶縁膜9を半導体基板1の表面(p型ウェル6およびn型ウェル8のそれぞれの表面)に形成する。

【0023】

次に、図2に示すように、ゲート絶縁膜9上に、例えば厚さ0.2μmのゲート電極用の導体膜を形成した後、レジストパターンをマスクとしたドライエッチングによりゲート電極用の導体膜を加工して導体膜からなるゲート電極10n,10pを形成する。ゲート電極用の導体膜は、例えばCVD法により形成された多結晶シリコン膜からなり、nMIS形成領域にはn型不純物が導入された多結晶シリコン膜からなるゲート電極10n、pMIS形成領域にはp型不純物が導入された多結晶シリコン膜からなるゲート電極10pが形成される。

【0024】

次に、p型ウェル6にn型不純物、例えばヒ素(As)をイオン注入し、nMISのゲート電極10nに対して自己整合的に相対的に低濃度なソース・ドレイン拡張領域11を形成する。同様に、n型ウェル8にp型不純物、例えばフッ化ボロン(BF2)をイオン注入し、pMISのゲート電極10pに対して自己整合的に相対的に低濃度なソース・ドレイン拡張領域12を形成する。上記ソース・ドレイン拡張領域11,12の深さは、例えば30nmである。

【0025】

次に、図3に示すように、半導体基板1の主面上に、例えば厚さ10nmの酸化シリコン膜13をCVD法により堆積した後、さらに酸化シリコン膜13上に窒化シリコン膜をCVD法により堆積する。続いて窒化シリコン膜をRIE(Reactive Ion Etching)法により異方性エッチングして、nMISのゲート電極10nおよびpMISのゲート電極10pのそれぞれの側壁にサイドウォール15を形成する。その後、p型ウェル6にn型不純物、例えばヒ素をイオン注入し、nMISのゲート電極10nおよびサイドウォール15に対して自己整合的に相対的に高濃度なソース・ドレイン拡散領域16を形成する。同様に、n型ウェル8にp型不純物、例えばフッ化ボロンをイオン注入し、pMISのゲート電極10pおよびサイドウォール15に対して自己整合的に相対的に高濃度なソース・ドレイン拡散領域17を形成する。上記ソース・ドレイン拡散領域16,17の深さは、例えば50nmである。

【0026】

次に、サリサイド技術によりnMISのゲート電極10nおよびソース・ドレイン拡散領域16の表面およびpMISのゲート電極10pおよびソース・ドレイン拡散領域17の表面に低抵抗のニッケルシリサイド(NiSi)層18を形成する。なお、ここではニッケルシリサイド層を例示したが、他のシリサイド層、例えばチタンシリサイド層またはコバルトシリサイド層等を形成してもよい。ニッケルシリサイド層18は、例えば以下に説明する方法により形成される。

【0027】

まず、半導体基板1の主面上にスパッタリング法によりニッケル膜および窒化チタン膜を順次堆積する。ニッケル膜の厚さは、例えば10nm、窒化チタン膜の厚さは、例えば15nmである。窒化チタン膜はニッケル膜の酸化を防止するためにニッケル膜上に設けられ、窒化チタン膜に代えてチタン膜を用いてもよい。続いて半導体基板1にRTA(Rapid Thermal Anneal)法を用いて、例えば温度320℃の熱処理を30秒施すことにより、ニッケル膜とnMISのゲート電極10nを構成するn型多結晶シリコン膜およびニッケル膜とnMISのソース・ドレイン拡散領域16が形成された半導体基板1を構成する単結晶シリコンとを選択的に反応させてニッケルシリサイド層18を形成する。同様に、ニッケル膜とpMISのゲート電極10pを構成するp型多結晶シリコン膜およびニッケル膜とpMISのソース・ドレイン拡散領域17が形成された半導体基板1を構成する単結晶シリコンとを選択的に反応させてニッケルシリサイド層18を形成する。続いて硫酸を用いたウエット洗浄、または硫酸と過酸化水素水とを用いたウエット洗浄等により、未反応のニッケル膜および窒化チタン膜を除去した後、半導体基板1にRTA法を用いて、例えば温度550℃の熱処置を30秒施すことにより、ニッケルシリサイド層18の低抵抗化を行う。

【0028】

次に、図4に示すように、半導体基板1の主面上にCVD法により窒化シリコン膜を堆積して第1絶縁膜19aを形成する。続いて第1絶縁膜19a上にプラズマCVD法によりTEOS(Tetra Ethyl Ortho Silicate)膜を堆積して第2絶縁膜19bを形成し、第1および第2絶縁膜19a,19bからなる層間絶縁膜を形成する。その後、第2絶縁膜19bの表面をCMP法により研磨する。下地段差に起因して第1絶縁膜19aの表面に凹凸形状が形成されていても、第2絶縁膜19bの表面をCMP法により研磨することにより、その表面が平坦化された層間絶縁膜が得られる。

【0029】

次に、レジストパターンをマスクとして第1および第2絶縁膜19a,19bをエッチングし、接続孔20を所定の箇所、例えばnMISのゲート電極10nおよびソース・ドレイン拡散領域16、ならびにpMISのゲート電極10pおよびソース・ドレイン拡散領域17の上方に位置する第1および第2絶縁膜19a,19bに形成する。接続孔20の口径は0.1μm以下、例えば0.08μmである。

【0030】

次に、図5(a)に示すように、接続孔20の内部を含む半導体基板1の主面上にチタン膜21を堆積し、さらに図5(b)に示すように、チタン膜21上に窒化チタン膜22を堆積する。チタン膜21は酸素原子を25at%まで固溶できることからニッケルシリサイド層18表面の還元材として用いられて、ニッケルシリサイド層18との接触抵抗を低減する機能を有する。また、窒化チタン膜22は後の工程で接続孔20の内部に埋め込まれる金属膜の構成原子が拡散するのを抑制または防止する機能を有する。なお、以下の説明においては、チタン膜21上に窒化チタン膜22を積み重ねた積層膜をバリアメタル膜と言い、接続孔20の内部に埋め込まれて主導電材料となる金属膜とは区別する。

【0031】

チタン膜21および窒化チタン膜22の成膜には、図6に示す成膜装置50が用いられる。以下に、チタン膜21および窒化チタン膜22の形成方法について図6から図9を用いて詳細に説明する。

【0032】

成膜装置50は、第1搬送室51aと第2搬送室51bの2つの搬送室が配置され、第1搬送室51aの周囲に開閉手段であるゲートバルブ52を介してローダ53、アンローダ54および3つのチャンバ55,56,57が備わり、第2搬送室51bの周囲に開閉手段であるゲートバルブ52を介して2つのチャンバ58,59が備わったマルチチャンバタイプである。さらに、第1搬送室51aと第2搬送室51bとの間には2つの搬送用のチャンバ60,61が備わっている。第1搬送室51aは排気機構等により所定の真空度に保持され、その中央部には半導体ウエハSWを搬送するための多関節アーム構造の搬送用ロボット62aが設けられている。同様に、第2搬送室51bは排気機構等により所定の真空度に保持され、その中央部には半導体ウエハSWを搬送するための多関節アーム構造の搬送用ロボット62bが設けられている。

【0033】

第1搬送室51aに備わるチャンバ55,56は、例えば150℃以上の高温の加熱処理を行う加熱処理用チャンバ、チャンバ57はドライクリーニング処置用チャンバである。第2搬送室51bに備わるチャンバ58は高指向性スパッタリング法またはプラズマCVD法によりチタン膜21を堆積するチタン成膜用チャンバ、チャンバ59はMOCVD(Metal Organic Chemical Vapor Deposition)法またはプラズマCVD法により窒化チタン膜22を堆積する窒化チタン成膜用チャンバである。第1搬送室51aと第2搬送室51bとの間に備わるチャンバ60,61は第1搬送室51aと第2搬送室51bとの間での半導体ウエハSWの受け渡しを行う受渡用チャンバであり、また半導体ウエハSWの冷却にも用いられる冷却用チャンバである。なお、成膜装置50では、第1搬送室51aのみに備わるチャンバを3つとし、第2搬送室51bのみに備わるチャンバを2つとしたが、これに限定されるものではなく、同じ用途のチャンバまたは他の用途のチャンバを追加することも可能である。

【0034】

まず、ローダ53に複数の半導体ウエハSWを搭載したフープ(Front Open Unified Pod)を載せた後(図7の工程P1)、搬送用ロボット62aによってフープから1枚の半導体ウエハSWを取り出し、第1搬送室51aへ真空搬入する。フープは半導体ウエハSWのバッチ搬送用の密閉収納容器であり、通常25枚、12枚、6枚等のバッチ単位で半導体ウエハSWを収納する。フープの容器外壁は微細な通気フィルタ部を除いて機密構造になっており、塵埃はほぼ完全に排除される。従って、クラス1000の雰囲気で搬送しても、内部はクラス1の清浄度が保てるようになっている。成膜装置50とのドッキングは、フープの扉を成膜装置50の内部に引き込むことによって清浄さを保持した状態で行われる。

【0035】

次に、搬送用ロボット62aによって半導体ウエハSWを第1搬送室51aからドライクリーニング処理用のチャンバ57へ真空搬送する(図7の工程P2)。図8にチャンバ57の概略断面図を示す。チャンバ57は主としてウエハステージ57a、ウエハリフトピン57b、シャワーヘッド57cおよびリモートプラズマ発生装置57dによって構成される。ウエハステージ57aおよびウエハリフトピン57bは独立した昇降機構を持ち、シャワーヘッド57cと半導体ウエハSWとの距離および半導体ウエハSWとウエハステージ57aとの距離を任意に制御することができる。また、ウエハステージ57aの上方に設置されたシャワーヘッド57cは常に一定温度に維持されており、その温度は例えば180℃である。

【0036】

チャンバ57へ半導体ウエハSWを搬入する時は、図9(a)に示すように、ウエハステージ57aを下降させ、ウエハリフトピン57bを上昇させて、ウエハリフトピン57b上に半導体ウエハSWを載せる。シャワーヘッド57cと半導体ウエハSWとの距離は、例えば16.5±12.7mm、半導体ウエハSWとウエハステージ57aとの距離は、例えば25.4±17.8mmに設定される。

【0037】

続いて半導体ウエハSWの主面上をドライクリーニング処理する時は、図9(b)に示すように、ウエハステージ57aを上昇させ、ウエハリフトピン57bを下降させて、ウエハステージ57a上に半導体ウエハSWを載せる。シャワーヘッド57cと半導体ウエハSWとの距離は、例えば17.8±5.1mmに設定される。

【0038】

ドライクリーニング処理時には、リモートプラズマ発生装置57dにおいて還元ガス、例えばNF3ガスおよびNH3ガスを添加したArガスまたはNF3ガスおよびH2ガスを添加したArガスを励起させてプラズマを生成し、このプラズマをチャンバ57内へ導入する。チャンバ57内に導入されたプラズマをシャワーヘッド57cを介して半導体ウエハSWの主面上に供給することにより、プラズマとニッケルシリサイド層18の表面に形成された自然酸化膜との間で起きる、例えば式(1)に示す還元反応によって自然酸化膜が除去される。ドライクリーニング処理時におけるプロセス条件は、例えばシャワーヘッド温度180℃、NF3ガス流量14sccm、NH3ガス流量70sccm、圧力400Pa、プラズマパワー30Wである。

【0039】

SiO2+NF3+NH3→ (NH4)2SiF6+O2 式(1)

この時、還元反応により生成された生成物((NH4)2SiF6)が接続孔20の内部を含む半導体ウエハSWの主面上に残留する。さらに、半導体ウエハSWはウエハステージ57a上に載せてあるだけであり、上記生成物は半導体ウエハSWの側面および裏面の一部にも残留する。半導体ウエハSWの側面および裏面の一部に残留する生成物は、半導体ウエハSWを他のチャンバへ搬送する場合などにおいて剥がれ、汚染や発塵の原因となる。そこで、ドライクリーニング処置に続いて、チャンバ57内において半導体ウエハSWに熱処理を施すことにより、半導体ウエハSWの主面上に残留する生成物を除去すると同時に、半導体ウエハSWの側面および裏面の一部に残留する生成物を除去する。

【0040】

続いて半導体ウエハSWを熱処理する時は、図9(c)に示すように、ウエハステージ57aを下降させ、ウエハリフトピン57bを上昇させて、半導体ウエハSWを温度180℃に設定されたシャワーヘッド57cへ近づける。シャワーヘッド57cと半導体ウエハSWとの距離は、例えば3.8±2.6mm、半導体ウエハSWとウエハステージ57aとの距離は、例えば5.9mm以上に設定される。

【0041】

熱処理時には、シャワーヘッド57cの加熱温度(180℃)を利用して半導体ウエハSWが加熱される。半導体ウエハSWの温度は100から150℃となり、上記ドライクリーニング処置時に半導体ウエハSWの主面上に形成された生成物((NH4)2SiF6)が、例えば式(2)に示す反応によって昇華し除去される。さらに、この熱処理によって半導体ウエハSWの側面および裏面も加熱されて、側面および裏面の一部に残留した生成物も除去される。

【0042】

(NH4)2SiF6→ SiF4+2NH3+2HF 式(2)

しかしながら、上記ドライクリーニング処理時に半導体ウエハSWに形成された生成物の組成が(NH4)2SiF6から僅かでもずれていると、温度100から150℃の熱処理では式(2)の反応が起こり難く、完全に生成物を除去することができなくなり、極微少の生成物が半導体ウエハSWの主面上に残留する。前述したように、接続孔20の内部に微少でも生成物が残留していると、その後接続孔20に内部に形成されるチタン膜21とニッケルシリサイド層18との接触抵抗のばらつきなどの問題が生じる。そこで、次工程において、半導体ウエハSWに150℃よりも高い温度の熱処理を施して、半導体ウエハSWの主面上に残留した微少の生成物を除去する。

【0043】

次に、搬送用ロボット62aによって半導体ウエハSWをドライクリーニング処理用のチャンバ57から加熱処理用のチャンバ55(またはチャンバ56)へ第1搬送室51aを介して真空搬送し、チャンバ55(またはチャンバ56)に備わるステージ上に載せる(図7の工程P3)。チャンバ55(またはチャンバ56)のステージ上に半導体ウエハSWを載せることにより、半導体ウエハSWを所定の温度で加熱し、100から150℃の温度では昇華せずに半導体ウエハSWの主面上に残留した生成物を昇華させて除去する。半導体ウエハSWの主面上での温度は、例えば150から400℃が適切な範囲と考えられる(他の条件によってはこの範囲に限定されないことはもとよりである)。また、量産に適した範囲としては165から350℃が考えられるが、さらに180から220℃等の200℃を中心値とする範囲が最も好適と考えられる。

【0044】

図10は、nMIS(図10の挿入図)を形成した後に、ドライクリーニング処理および熱処理を半導体基板に施した場合のゲート電極と半導体基板との間に流れる電流(リーク電流)と熱処理温度との関係を示すグラフ図である。

【0045】

正常なnMISのゲート電流は1×10−13A/μm2程度であるが、nMISの表面にドライクリーニング処理により生成した生成物が残留すると、その生成物を通して5×10−11A/μm2以上の表面リーク電流が流れる。しかし、150℃よりも高い温度で熱処理を行うと、温度の増加に従って表面リーク電流が減少し、例えば160℃程度の温度で熱処理をすると、リーク電流は1×10−12A/μm2程度に減少し、さらに180℃程度の温度で熱処理をすると、リーク電流は1×10−13A/μm2程度に減少する。このことから、180℃よりも高い温度で熱処理をすることにより、nMISの表面にリーク電流が流れない状態まで生成物を除去することができると考えられる。

【0046】

次に、搬送用ロボット62aによって半導体ウエハSWを加熱処理用のチャンバ55(またはチャンバ56)から冷却・受渡用のチャンバ60(またはチャンバ61)へ第1搬送室51aを介して真空搬送し、チャンバ60(またはチャンバ61)に備わるステージ上に載せる(図7の工程P4)。チャンバ60(またはチャンバ61)のステージ上に半導体ウエハSWを載せることにより、半導体ウエハSWは冷却される。

【0047】

次に、搬送用ロボット62bによって半導体ウエハSWを冷却・受渡用のチャンバ60(またはチャンバ61)からチタン成膜用のチャンバ58へ第2搬送室51bを介して真空搬送する(図7の工程P5)。チャンバ58内を排気機構により所定の真空度、例えば1.33×10−6Paとした後、半導体ウエハSWを所定の温度に加熱し、チャンバ58内へArガスを所定の流量により導入して高指向性スパッタリング法により半導体ウエハSWの主面上へチタン膜21を堆積する。チタン膜21の厚さは、例えば20nmである。なお、チタン膜21は高指向性スパッタリング法の他に、プラズマCVD法により堆積することができる。

【0048】

次に、搬送用ロボット62bによって半導体ウエハSWをチタン成膜用のチャンバ58から窒化チタン成膜用のチャンバ59へ第2搬送室51bを介して真空搬送する(図7の工程P6)。チャンバ59内を排気機構により所定の真空度とした後、半導体ウエハSWを所定の温度に加熱し、チャンバ59内へ所定のガスを所定の流量により導入してMOCVD法またはプラズマCVD法により半導体ウエハSWの主面上へ窒化チタン膜22を堆積する。窒化チタン膜22の厚さは、例えば5nmである。

【0049】

次に、搬送用ロボット62bによって半導体ウエハSWを窒化チタン成膜用のチャンバ59から冷却・受渡用のチャンバ60(またはチャンバ61)へ第2搬送室51bを介して真空搬送する(図7の工程P7)。

【0050】

次に、搬送用ロボット62aによって半導体ウエハSWを冷却・受渡用のチャンバ60(またはチャンバ61)からアンローダ54へ真空搬出し(図7の工程P8)、アンローダ54に置かれたフープへ載せる。

【0051】

このように、ドライクリーニング処理の工程(図7の工程P2)とチタン膜21を堆積する工程(図7の工程P5)との間に150から400℃の熱処理を半導体基板1に施すことによって(図7の工程P3)、接続孔20の底面および側面にドライクリーニング処置時に生成された生成物が除去されるので、接続孔20の底面におけるチタン膜21とニッケルシリサイド層18との接触抵抗のばらつきを低減することができる。さらに、接続孔20の側面におけるチタン膜21の剥がれを防止することができる。

【0052】

その後、図11に示すように、接続孔20の内部を含む半導体基板1の主面上にタングステン膜23をCVD法により堆積し、例えばCMP法によりタングステン膜23の表面を平坦化することによって接続孔20の内部にタングステン膜23を埋め込み、タングステン膜23を主導電材料とするプラグを形成する。

【0053】

なお、前述した接続孔20の内部にプラグを形成する工程では、プラグの主導電材料をタングステン膜23とし、バリアメタル膜をチタン膜21上に窒化チタン膜22を積み重ねた積層膜としたが、これに限定されるものではなく、種々変更することは可能である。例えば(1)プラグの主導電材料をタングステン膜とし、バリアメタル膜を窒化タングステン膜とする。1台のタングステン成膜装置を用いて窒化タングステン膜およびタングステン膜を順次成膜することができるので、スループットが向上し、コストを低減することができる。(2)プラグの主導電材料を銅膜とし、バリアメタル膜を窒化チタン膜とする。(3)プラグの主導電材料を銅膜とし、バリアメタル膜を窒化タンタル膜とする。窒化タンタル膜を用いることにより、バリアメタル膜に窒化チタン膜を用いた場合よりも銅原子が拡散するのを抑制または防止することができる。(4)プラグの主導電材料を銅膜とし、バリアメタル膜を窒化タンタル膜上にタンタル膜を積み重ねた積層膜とする。銅膜と窒化タンタル膜との間にタンタル膜を挿入することにより、銅膜と窒化タンタル膜との密着性を向上させることができる。(5)プラグの主導電材料を銅膜とし、バリアメタル膜を窒化タンタル膜上にルテニウム膜を積み重ねた積層膜とする。銅膜と窒化タンタル膜との間にルテニウム膜を挿入することにより、銅膜と窒化タンタル膜との密着性を向上させることができる。(6)プラグの主導電材料をアルミニウム膜とし、バリアメタル膜をチタン膜上に窒化チタン膜を積み重ねた積層膜、または窒化タングステン膜とする。

【0054】

次に、図12に示すように、半導体基板1の主面上にストッパ絶縁膜24および配線形成用の絶縁膜25を順次形成する。ストッパ絶縁膜24は絶縁膜25への溝加工の際にエッチングストッパとなる膜であり、絶縁膜25に対してエッチング選択比を有する材料を用いる。ストッパ絶縁膜24は、例えばプラズマCVD法により形成される窒化シリコン膜とし、絶縁膜25は、例えばプラズマCVD法により形成される酸化シリコン膜とすることができる。なお、ストッパ絶縁膜24と絶縁膜25には次に説明する第1層目の配線が形成される。

【0055】

次に、シングルダマシン法により第1層目の配線を形成する。まず、レジストパターンをマスクとしたドライエッチングによってストッパ絶縁膜24および絶縁膜25の所定の領域に配線溝26を形成した後、半導体基板1の主面上にバリアメタル膜27を形成する。バリアメタル膜27は、例えば窒化チタン膜、窒化タンタル膜、窒化タンタル膜上にタンタル膜を積み重ねた積層膜、または窒化タンタル膜上にルテニウム膜を積み重ねた積層膜である。続いてCVD法またはスパッタリング法によりバリアメタル膜27上に銅のシード層を形成し、さらに電解めっき法を用いてシード層上に銅めっき膜を形成する。銅めっき膜により配線溝26の内部を埋め込む。続いて配線溝26以外の領域の銅めっき膜、シード層およびバリアメタル膜27をCMP法により除去して、銅膜を主導電材料とする第1層目の配線M1を形成する。

【0056】

次に、デュアルダマシン法により第2層目の配線を形成する。まず、図13に示すように、半導体基板1の主面上にキャップ絶縁膜28、層間絶縁膜29および配線形成用のストッパ絶縁膜30を順次形成する。キャップ絶縁膜28および層間絶縁膜29には、後に説明するように接続孔が形成される。キャップ絶縁膜28は、層間絶縁膜29に対してエッチング選択比を有する材料で構成され、例えばプラズマCVD法により形成される窒化シリコン膜とすることができる。さらにキャップ絶縁膜28は第1層目の配線M1を構成する銅の拡散を防止する保護膜としての機能を有している。層間絶縁膜29は、例えばプラズマCVD法により形成されるTEOS膜とすることができる。ストッパ絶縁膜30は、層間絶縁膜29および後にストッパ絶縁膜30の上層に堆積される配線形成用の絶縁膜に対してエッチング選択比を有する絶縁材料で構成され、例えばプラズマCVD法により形成される窒化シリコン膜とすることができる。

【0057】

次に、孔形成用のレジストパターンをマスクとしたドライエッチングによりストッパ絶縁膜30を加工した後、ストッパ絶縁膜30上に配線形成用の絶縁膜31を形成する。絶縁膜31は、例えばTEOS膜とすることができる。

【0058】

次に、配線溝形成用のレジストパターンをマスクとしたドライエッチングにより絶縁膜31を加工する。この際、ストッパ絶縁膜30がエッチングストッパとして機能する。続いてストッパ絶縁膜30および配線溝形成用のレジストパターンをマスクとしたドライエッチングにより層間絶縁膜29を加工する。この際、キャップ絶縁膜28がエッチングストッパとして機能する。続いて露出したキャップ絶縁膜28をドライエッチングにより除去することにより、キャップ絶縁膜28および層間絶縁膜29に接続孔32が形成され、ストッパ絶縁膜30および絶縁膜31に配線溝33が形成される。

【0059】

次に、接続孔32および配線溝33の内部に第2層目の配線を形成する。第2層目の配線は、バリアメタル層および主導電材料である銅膜からなり、この配線と下層配線である第1層目の配線M1とを接続する接続部材は第2層目の配線と一体に形成される。まず、接続孔32および配線溝33の内部を含む半導体基板1の主面上にバリアメタル膜34を形成する。バリアメタル膜34は、例えば窒化チタン膜、窒化タンタル膜、窒化タンタル膜上にタンタル膜を積み重ねた積層膜、または窒化タンタル膜上にルテニウム膜を積み重ねた積層膜である。バリアメタル膜34を形成する前には前述したドライクリーニング処理が行われるが、このドライクリーニング処理においてもその後、前述した100から150℃の温度での加熱と150℃よりも高い温度での加熱とを半導体ウエハに対して行い、接続孔32の底面ならびに接続孔32および配線溝33の側壁に生成した生成物の除去を行ってもよい。これにより、バリアメタル膜34と第1層目の配線M1との接触抵抗のばらつきを低減することができ、また、キャップ絶縁膜28、層間絶縁膜29、ストッパ絶縁膜30および絶縁膜31からのバリアメタル膜34の剥がれを防止することができる。続いてCVD法またはスパッタリング法によりバリアメタル膜34上に銅のシード層を形成し、さらに電解めっき法を用いてシード層上に銅めっき膜を形成する。銅めっき膜により接続孔32および配線溝33の内部を埋め込む。続いて接続孔32および配線溝33以外の領域の銅めっき膜、シード層およびバリアメタル膜34をCMP法により除去して、銅膜を主導電材料とする第2層目の配線M2を形成する。

【0060】

その後、図14に示すように、例えば前述した第2層目の配線M2と同様な方法によりさらに上層の配線を形成する。図14では、第3層目から第6層目の配線M3,M4,M5,M6を形成したCMOSデバイスを例示している。続いて第6層目の配線M6上に窒化シリコン膜35を形成し、窒化シリコン膜35上に酸化シリコン膜36を形成する。これら窒化シリコン膜35および酸化シリコン膜36は、外部からの水分や不純物の侵入防止およびα線の透過の抑制を行うパッシベーション膜として機能する。

【0061】

次に、窒化シリコン膜35および酸化シリコン膜36をレジストパターンをマスクとしたエッチングにより加工して、第6層目の配線M6の一部(ボンディングパッド部)を露出させる。続いて露出した第6層目の配線M6上に金膜およびニッケル膜等の積層膜からなるバンプ下地電極37を形成し、バンプ下地電極37上に金または半田等からなるバンプ電極38を形成することにより、実施の形態1であるCMOSデバイスが略完成する。なお、このバンプ電極38は外部接続用電極となる。この後、半導体ウエハSWから半導体チップに個々に切り分けられ、パッケージ基板等に実装されて半導体装置が完成するが、それらの説明は省略する。

【0062】

なお、実施の形態1のドライクリーニング処理では、リモートプラズマ発生装置57dにおいて還元ガス、例えばNF3ガスおよびNH3ガスを添加したArガス(プラズマ励起用のガスとしてはArガスが多用されるが、その他の希ガスまたはそれらの混合ガスでもよい)を励起させてプラズマを生成し、このプラズマをチャンバ57内へ導入して自然酸化膜を還元反応により除去したが、プラズマを用いずに、HFガスとNH3ガスまたはNF3ガスとNH3ガス等の還元ガスをチャンバ57内へ導入して自然酸化膜を還元反応により除去してもよい。

【0063】

また、リモートプラズマ装置に限定されるものではなく、その他の特性に問題がなければ、通常のプラズマ装置を用いても問題はない。リモートプラズマは基板に損傷を与えない利点がある。

【0064】

また、プラズマを用いて処理する場合は、上記ガスの組み合わせに限らず、窒素、水素、フッ素(これらの複合ラジカルを含む)のそれぞれのラジカルまたは反応種を生成するものであれば、特にこのプロセスに対して有害なものでなければ、その他のガスの組み合わせでもよい。すなわち、窒素、水素およびフッ素ラジカル生成ガス(混合ガス含む)とプラズマ励起ガスとその他の添加ガス等との混合ガス雰囲気を適宜用いればよい。

【0065】

また、還元ガス等の反応ガスは上記ガスに限らず、酸化膜と比較的低温で反応して気化する反応種を生成するものであればよい。

【0066】

このように、実施の形態1によれば、接続孔20の内部にバリアメタル膜(チタン膜21上に窒化チタン膜22を積み重ねた積層膜)を形成する前に行うドライクリーニング処置により、接続孔20の底面および側面に化学量論的組成から僅かにずれた生成物が残留するが、この生成物はドライクリーニング処理の後に行う150℃よりも高い温度の熱処理により除去されるので、接続孔20の底面におけるバリアメタル膜とニッケルシリサイド層18との接触抵抗のばらつきを低減することができ、また接続孔20の側面におけるバリアメタル膜の剥がれを防ぐことができるので、接続孔20部分における電気的特性のばらつきを低減することができる。また、実施の形態1は上下層の配線を接続する接続孔部分にも適用することができ、同様の効果を得ることができる。例えば実施の形態1に例示したデュアルダマシン配線の形成工程において、接続孔32および配線溝33の内部にバリアメタル膜34を形成する前に行うドライクリーニング処理の後に実施の形態1を実施することにより、接続孔32部分における電気的特性のばらつきを低減することができる。

【0067】

(実施の形態2)

前述した実施の形態1で説明したように、バリアメタル膜の形成工程において行われるドライクリーニング処理では、半導体ウエハSWの主面上、側面および裏面の一部に生成物が残留する。このため、ドライクリーニング処理用のチャンバ57に備わる180℃に設定されたシャワーヘッド57cによって半導体ウエハSWを100から150℃の温度で加熱して(NH4)2SiF6の組成の生成物を除去し、さらに、加熱処理用のチャンバ55,56により半導体ウエハを150℃よりも高い温度で加熱して(NH4)2SiF6から僅かに組成のずれた生成物の除去を行っている。

【0068】

実施の形態2では、ドライクリーニング処理用のチャンバ57に備わるシャワーヘッド57CHの温度を180℃よりも高い温度、例えば250℃に設定し、ドライクリーニング処理の直後に、シャワーヘッド57CHにより半導体ウエハSWを180から220℃の温度で加熱して(NH4)2SiF6の組成の生成物および(NH4)2SiF6から僅かに組成のずれた生成物の除去を行う。

【0069】

実施の形態2によるバリアメタル膜の形成方法を図15および図16を用いて説明する。図15はバリアメタル膜の成膜工程図、図16(a)、(b)および(c)はそれぞれバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバにおける半導体ウエハの処理工程を説明するためのチャンバの概略断面図である。なお、バリアメタル膜の成膜装置は、前述した実施の形態1の成膜装置50を用いる。

【0070】

まず、前述した実施の形態1と同様にして、半導体ウエハSWをローダ53からドライクリーニング処理用のチャンバ57へ真空搬送する(図15の工程P1,P2)。チャンバ57に備わるシャワーヘッド57CHは常に一定温度に維持されており、その温度は例えば250℃である。

【0071】

チャンバ57へ半導体ウエハSWを搬入する時は、図16(a)に示すように、ウエハステージ57aを下降させ、ウエハリフトピン57bを上昇させて、ウエハリフトピン57b上に半導体ウエハSWを載せる。シャワーヘッド57CHと半導体ウエハSWとの距離は、例えば16.5±12.7mm、半導体ウエハSWとウエハステージ57aとの距離は、例えば25.4±17.8mmに設定される。

【0072】

続いて半導体ウエハSWの主面上をドライクリーニング処理する時は、図16(b)に示すように、ウエハステージ57aを上昇させ、ウエハリフトピン57bを下降させて、ウエハステージ57a上に半導体ウエハSWを載せる。シャワーヘッド57CHと半導体ウエハSWとの距離は、例えば17.8±5.1mmに設定される。ドライクリーニング処理が行われた半導体ウエハSWの主面上、側面および裏面の一部には、還元反応により生成された生成物((NH4)2SiF6)が残留する。

【0073】

続いて半導体ウエハSWを熱処理する時は、図16(c)に示すように、ウエハステージ57aを下降させ、ウエハリフトピン57bを上昇させて、半導体ウエハSWを温度250℃に設定されたシャワーヘッド57CHへ近づける。シャワーヘッド57CHと半導体ウエハSWとの距離は、例えば3.8±2.6mm、半導体ウエハSWとウエハステージ57aとの距離は、例えば5.9mm以上に設定される。

【0074】

熱処理時には、シャワーヘッド57CHの加熱温度(250℃)を利用して半導体ウエハSWが加熱されるので、半導体ウエハSWの温度は150℃よりも高くなり、上記ドライクリーニング処置時に半導体ウエハSWの主面上、側面および裏面の一部に残留した(NH4)2SiF6の組成の生成物が除去され、さらに(NH4)2SiF6から僅かに組成のずれた生成物も除去される。

【0075】

次に、搬送用ロボット62aによって半導体ウエハSWをドライクリーニング処理用のチャンバ57から冷却・受渡用のチャンバ60(またはチャンバ61)へ第1搬送室51aを介して真空搬送し、チャンバ60(またはチャンバ61)に備わるステージ上に載せる(図15の工程P3)。チャンバ60(またはチャンバ61)のステージ上に半導体ウエハSWを載せることにより、半導体ウエハSWは冷却される。

【0076】

その後は前述した実施の形態1と同様に、搬送用ロボット62bによってチタン成膜用のチャンバ58においてチタン膜を堆積し(図15の工程P4)、窒化チタン成膜用のチャンバ59においてチタン膜上に窒化チタン膜を堆積した後(図15の工程P5)、半導体ウエハSWを冷却・受渡用のチャンバ60(またはチャンバ61)へ真空搬送する(図15の工程P6)。さらに、搬送用ロボット62aによって半導体ウエハSWをアンローダ54へ真空搬出し(図15の工程P7)、アンローダ54に置かれたフープへ載せる。

【0077】

このように、実施の形態2によれば、ドライクリーニング処理において半導体ウエハSWの側面および裏面の一部に生成した不要な生成物は、ドライクリーニング処理に続くシャワーヘッド57CHによる180から220℃の熱処理によって除去されるので、前述した実施の形態1で行う熱処理用のチャンバ55,56における熱処理工程が不要となり、前述した実施の形態1よりも製造工程数を削減することができる。

【0078】

(実施の形態3)

前述した実施の形態1で説明したように、バリアメタル膜の形成工程において行われるドライクリーニング処理では、一般に半導体ウエハSWをウエハステージ57aに単に置くだけであり、このため、半導体ウエハSWの主面上のみならず、半導体ウエハSWの側面および裏面の一部にも(NH4)2SiF6の組成の生成物が残留する。半導体ウエハSWの側面および裏面の一部に残留した生成物は、半導体ウエハSWを他のチャンバへ搬送する場合などにおいて剥がれて、汚染や発塵の原因となる。そこで、前述した実施の形態1および2では、ドライクリーニング処置に続いて、同じチャンバ57内で半導体ウエハSWに熱処理を施すことにより、半導体ウエハSWの主面上に残留する生成物を除去すると同時に、半導体ウエハSWの側面および裏面の一部に残留する生成物を除去している。

【0079】

実施の形態3では、ドライクリーニング処理時において半導体ウエハSWの裏面へのドライクリーニングガスの回り込みを防ぐことにより、半導体ウエハSWの側面および裏面の一部への生成物の生成を防止する。従って、前述した実施の形態1においてドライクリーニング処理後に続いて行われるシャワーヘッド57cによる半導体ウエハSWの熱処理、すなわちチャンバ57に備わるウエハステージ57aを下降させ、ウエハリフトピン57bを上昇させて、半導体ウエハSWを温度180℃に設定されたシャワーヘッド57cへ近づけることによる熱処理(図9(c))は不要となる。なお、ドライクリーニング処理により半導体ウエハSWの主面上に残留する生成物は、熱処理用のチャンバ55,56における150℃よりも高い温度の熱処理により除去することができる。

【0080】

実施の形態3によるドライクリーニング処理の方法を図17を用いて説明する。図17(a)、(b)および(c)はそれぞれバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバの概略断面図である。

【0081】

図17(a)は、半導体ウエハSWの側面および裏面の一部への生成物の生成を防止する第1のドライクリーニング処理方法を説明する図である。半導体ウエハSWはウエハステージ57a上に置かれており、昇降機構を有するシーリング57eを半導体ウエハSWの主面上の周囲に接触させて押さえることにより、半導体ウエハSWの周囲および裏面へのドライクリーニングガスの回り込みを防いでいる。

【0082】

図17(b)は、半導体ウエハSWの側面および裏面の一部への生成物の生成を防止する第2のドライクリーニング処理方法を説明する図である。半導体ウエハSWは静電チャック機能を有するウエハステージ57a上に置かれており、半導体ウエハSWの裏面とウエハステージ57aとの間に隙間を形成することなく、ドライクリーニング処理を行うことができる。静電チャックは、ウエハステージ57aの上に誘電層を設けてウエハステージ57aと半導体ウエハSWとの間に電圧を印加し、両者間に発生した力によって半導体ウエハSWを吸着する機構である。吸着方式の違いによって誘電体として絶縁材料を使用するクーロン力型とジョンソン・ラベック力型とに分類されるが、低電圧で強い吸着力を有するジョンソン・ラベック力型はアルミナなどのセラミック製の静電チャックに多く、耐熱性と耐プラズマ性の面で有利であることから普及している。静電チャックは機械的な保持具を使用しないことから半導体ウエハSWの全面を均一に処理することができる。

【0083】

さらに、昇降機構を有するシャドウリング57fを半導体ウエハSWの主面上の周囲に備えており、半導体ウエハSWに接触させずに半導体ウエハSWの周囲をシャドウリング57fによって覆い、ウエハステージ57aの周囲から上方に向けてHeガス等の不活性ガスを流す。これにより、半導体ウエハSWの周囲および裏面へのドライクリーニングガスの回り込みを防いでいる。

【0084】

図17(c)は、半導体ウエハSWの側面および裏面の一部への生成物の生成を防止する第3のドライクリーニング処理方法を説明する図である。半導体ウエハSWはウエハステージ57a上に置かれており、昇降機構を有するシーリング57eを半導体ウエハSWの主面上の周囲に接触させて押さえることにより、半導体ウエハSWの周囲および裏面へのドライクリーニングガスの回り込みを防いでいる。

【0085】

さらに、シーリング57eの下部にはシーリング57eにつながる排気室57gが備わっており、ウエハステージ57aは排気室57g内に置かれている。排気室57gにはHeガス等の不活性ガスを排気室57gへ導入する配管と排気室57gから排気する配管とが設けられており、半導体ウエハSWの周囲および裏面へ不活性ガスを流入できる構造となっている。

【0086】

このように、実施の形態3によれば、ドライクリーニング処理において半導体ウエハSWの側面および裏面の一部に不要な生成物が生成せず、ドライクリーニング処理に続くシャワーヘッド57cによる半導体ウエハSWの熱処理が不要となるので、前述した実施の形態1よりも製造工程数を削減することができる。

【0087】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0088】

以下に、本願に開示された発明の概要を項に分けて簡潔に示す。

1.絶縁膜に開口した接続孔の内部にバリアメタル膜を介して金属膜を埋め込む半導体装置の製造方法であって、前記絶縁膜に前記接続孔を形成した後、前記接続孔の内部に前記バリアメタル膜を堆積する前に以下の工程を含む半導体装置の製造方法:

(a)第1のチャンバに備わるウエハステージ上に半導体ウエハを置く工程;

(b)前記ウエハステージの上方に設置されたシャワーヘッドを介して還元ガスを供給し、前記接続孔の内部をドライクリーニング処理する工程;

(c)前記シャワーヘッドの加熱温度を利用(シャワーヘッドの輻射等)した第1の温度で前記半導体ウエハに対して第1の熱処理する工程;

(d)前記半導体ウエハを前記第1のチャンバから第2のチャンバへ搬送する工程;

(e)前記第2のチャンバにおいて、前記第1の温度よりも高い第2の温度で前記半導体ウエハに対して第2の熱処理する工程。

【0089】

なお、本願では、主にバリアメタル形成前の接続孔内洗浄プロセスについて説明したが、本項1、8、または11の各サブパラグラフのプロセスは、その他のウエハ処理の前処理(ドライ洗浄)として適用できることは言うまでもない。

【0090】

すなわち、熱処理または各種の膜形成等のウエハ処理前の洗浄(例えばシリコン表面の自然酸化膜を比較的低温(例えば摂氏400度以下)で昇華、蒸発または気化する物質に変換する処理)としてドライ洗浄を実行する際に、ドライ洗浄の結果生成し、ウエハ表面(上面、側面、裏面を含む)に堆積、結露または凝結した洗浄残渣(洗浄処理生成物を含む)をドライ洗浄室と同室で、洗浄機構の一部または全部を利用して、第1の温度(ウエハ上面温度)で熱処理することによって前記洗浄残渣の一部を気化させて除去した後、ウエハを別の処理室に移動させ、そこで第1の温度よりも高い第2の温度(ウエハ上面温度)で熱処理することによって残留する残渣を気化させるものである。

【0091】

第1の熱処理は比較的低温で出来るため、装置構造を比較的簡単に出来ること、またはスループットを確保できる利点がある。また、この処理によって、ハンドリングに必要な裏面、側面の残渣は比較的完全に(ハンドリングによる汚染の伝播を回避する限度で)除去できる利点がある。第2の熱処理が必要なのは、生成物が非化学量論的な組成を含むと気化温度が上昇する場合があるほか、複雑な構造を有する実際のウエハ上面では、地形学的特徴に依存して、実効的気化温度が上昇する場合があるからである。

2.前記項1記載の半導体装置の製造方法おいて、前記第1の温度は100以上150℃未満である。

3.前記項1記載の半導体装置の製造方法において、前記第2の温度は150から400℃である。

4.前記項1記載の半導体装置の製造方法において、前記第2の温度は165から350℃である。

5.前記項1記載の半導体装置の製造方法において、前記第2の温度は180から220℃である。

6.前記項1記載の半導体装置の製造方法において、前記第2の温度は200℃である。

7.前記項1記載の半導体装置の製造方法において、前記第1のチャンバと前記第2のチャンバとの間の前記半導体ウエハの搬送は、真空搬送される。

8.絶縁膜に開口した接続孔の内部にバリアメタル膜を介して金属膜を埋め込む半導体装置の製造方法であって、前記絶縁膜に前記接続孔を形成した後、前記接続孔の内部に前記バリアメタル膜を堆積する前に以下の工程を含む半導体装置の製造方法:

(a)第1のチャンバに備わるウエハステージ上に半導体ウエハを置く工程;

(b)前記ウエハステージの上方に設置されたシャワーヘッドを介して還元ガスを供給し、前記半導体ウエハの主面上のシリコンの表面をドライクリーニング処理する工程;

(c)前記シャワーヘッドの加熱温度を利用した第1の温度で前記半導体ウエハに対して第1の熱処理する工程、

ここで、前記シャワーヘッドは180℃よりも高い温度に維持される。

【0092】

すなわち、熱処理または各種の膜形成等のウエハ処理前の洗浄(例えばシリコン表面の自然酸化膜を比較的低温(例えば摂氏400度以下)で昇華、蒸発または気化する物質に変換する処理)としてドライ洗浄を実行する際に、ドライ洗浄の結果生成し、ウエハ表面(上面、側面、裏面を含む)に堆積、結露または凝結した洗浄残渣(洗浄処理生成物を含む)をドライ洗浄室と同室で、洗浄機構の一部または全部を利用して、十分に高い温度(ウエハ上面温度)で熱処理することによって前記洗浄残渣のほぼ全部を気化させて除去するものである。

【0093】

この場合は一回の熱処理でしかも同室で出来るため、装置の処理室を有効に利用できる利点がある。

9.前記項8記載の半導体装置の製造方法において、前記第1の温度は180から220℃である。

10.前記項8記載の半導体装置の製造方法において、前記第1の温度は200℃である。

11.絶縁膜に開口した接続孔の内部にバリアメタル膜を介して金属膜を埋め込む半導体装置の製造方法であって、前記絶縁膜に前記接続孔を形成した後、前記接続孔の内部に前記バリアメタル膜を堆積する前に以下の工程を含む半導体装置の製造方法:

(a)第1のチャンバに備わるウエハステージ上に半導体ウエハを置く工程;

(b)前記ウエハステージの上方に設置されたシャワーヘッドを介して還元ガスを供給し、前記接続孔の内部をドライクリーニング処理する工程;

(c)前記半導体ウエハを前記第1のチャンバから第2のチャンバへ搬送する工程;

(d)前記第2のチャンバにおいて、第2の温度で前記半導体ウエハを熱処理(前記項1の第2の熱処理に対応)する工程、

ここで、前記工程(b)では、前記半導体ウエハの側面および裏面に前記還元ガスが供給されない。

【0094】

すなわち、熱処理または各種の膜形成等のウエハ処理前の洗浄(例えばシリコン表面の自然酸化膜を比較的低温(例えば摂氏400度以下)で昇華、蒸発または気化する物質に変換する処理)としてドライ洗浄を実行する際に、ドライ洗浄の結果生成し、ウエハ表面(このとき上面の周辺部、側面、裏面に堆積物が付着しないようにしてドライ洗浄を実行することが必要である)に堆積、結露または凝結した洗浄残渣(洗浄処理生成物を含む)をドライ洗浄室と別室で、十分に高い温度(ウエハ上面温度)で熱処理することによって前記洗浄残渣のほぼ全部を気化させて除去するものである。

12.前記項11記載の半導体装置の製造方法において、前記第2の温度は150から400℃である。

13.前記項11記載の半導体装置の製造方法において、前記第2の温度は165から350℃である。

14.前記項11記載の半導体装置の製造方法において、前記第2の温度は180から220℃である。

15.前記項11記載の半導体装置の製造方法において、前記第2の温度は200℃である。

16.前記項11記載の半導体装置の製造方法において、前記工程(b)は以下の工程を含む:

(b1)前記ウエハステージ上に置かれた前記半導体ウエハの周辺部をシーリングにより押さえる工程。

17.前記項11記載の半導体装置の製造方法において、前記工程(b)は以下の工程を含む:

(b1)前記半導体ウエハを静電チャックにより前記ウエハステージ上に吸着する工程;

(b2)前記半導体ウエハの周辺部を前記半導体ウエハと接触させずにシャドウリングにより覆い、前記ウエハステージの周辺部から不活性ガスを流入させる工程。

18.前記項11記載の半導体装置の製造方法において、前記工程(b)は以下の工程を含む:

(b1)前記ウエハステージ上に置かれた前記半導体ウエハの周辺部をシーリングにより押さえる工程;

(b2)前記ウエハステージの裏面側から不活性ガスを流入させる工程。

19.前記項11記載の半導体装置の製造方法において、前記第1のチャンバと前記第2のチャンバとの間の前記半導体ウエハの搬送は、真空搬送される。

20.前記項1、8または11記載の半導体装置の製造方法において、前記金属膜はタングステン膜であり、前記バリアメタル膜はチタン膜上に窒化チタン膜を積み重ねた積層膜、または窒化タングステン膜である。

21.前記項1、8または11記載の半導体装置の製造方法において、前記金属膜は銅膜であり、前記バリアメタル膜は窒化チタン膜、窒化タンタル膜、窒化タンタル膜上にタンタル膜を積み重ねた積層膜、または窒化タンタル膜上にルテニウム膜を積み重ねた積層膜である。

22.前記項1、8または11記載の半導体装置の製造方法において、前記金属膜はアルミニウム膜であり、前記バリアメタル膜はチタン膜上に窒化チタン膜を積み重ねた積層膜、または窒化タングステン膜である。

【符号の説明】

【0095】

1 半導体基板

4 素子分離領域

6 p型ウェル

8 n型ウェル

9 ゲート絶縁膜

10n ゲート電極

10p ゲート電極

11 ソース・ドレイン拡張領域

12 ソース・ドレイン拡張領域

13 酸化シリコン膜

15 サイドウォール

16 ソース・ドレイン拡散領域

17 ソース・ドレイン拡散領域

18 ニッケルシリサイド層

19a 第1絶縁膜

19b 第2絶縁膜

20 接続孔

21 チタン膜

22 窒化チタン膜

23 タングステン膜

24 ストッパ絶縁膜

25 絶縁膜

26 配線溝

27 バリアメタル膜

28 キャップ絶縁膜

29 層間絶縁膜

30 ストッパ絶縁膜

31 絶縁膜

32 接続孔

33 配線溝

34 バリアメタル膜

35 窒化シリコン膜

36 酸化シリコン膜

37 バンプ下地電極

38 バンプ電極

50 成膜装置

51a 第1搬送室

51b 第2搬送室

52 ゲートバルブ

53 ローダ

54 アンローダ

55,56,57 チャンバ

57a ウエハステージ

57b ウエハリフトピン

57c,57CH シャワーヘッド

57d リモートプラズマ発生装置

57e シーリング

57f シャドウリング

57g 排気室

58,59,60,61 チャンバ

62a,62b 搬送用ロボット

M1,M2,M3,M4,M5,M6 配線

SW 半導体ウエハ

【技術分野】

【0001】

本発明は、半導体装置の製造技術に関し、特に、絶縁膜に開口された接続孔の内部に金属膜を埋め込む半導体装置の製造工程に適用して有効な技術に関するものである。

【背景技術】

【0002】

日本特許公開2003−324108号公報(対応米国はUSP6864183)には、三フッ化窒素ガス、フッ化水素ガス、六フッ化二炭素ガス、四フッ化炭素ガスおよび六フッ化硫黄ガスよりなる群から選ばれる少なくとも1種以上のフッ化系ガスとアルゴンガスとの混合ガスを用いてプラズマエッチングを行うことにより、シリコン基板およびゲート電極の表面に存在する自然酸化膜を除去する方法が開示されている(特許文献1参照)。

【0003】

また、日本特許公開平2−256235号公報(対応米国はUSP5030319)には、ハロゲン元素を含むガスと塩基性ガスとによりハロゲン塩を生成し、これを被処置体の酸化膜と反応させる、あるいはハロゲン塩ガスを直接酸化膜と反応させて、下地にダメージを与えることなく酸化膜を選択的にエッチング、除去する方法が開示されている(特許文献2参照)。

【0004】

また、日本特許公開平3−116727号公報には、表面に酸化膜の形成された半導体基板をフッ素原子を含むガス中に曝したのち、還元性ガス中あるいは不活性ガス中あるいは真空中でアニールすることにより、該酸化膜を除去するクリーニング方法が開示されている(特許文献3参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−324108号公報

【特許文献2】特開平2−256235号公報

【特許文献3】特開平3−116727号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

半導体装置の高集積化が進むにつれて、電界効果トランジスタはスケーリング則に従い微細化され、ゲートやソース・ドレインと配線とを繋ぐため、層間絶縁膜に形成される接続孔においては0.1μm以下の口径が要求されている。しかし、接続孔の底部に露出する導電材料の表面(例えばゲートを構成する導電膜、ソース・ドレインを構成する半導体領域、あるいは上記導電膜や半導体領域上に形成されるシリサイド層などの表面)には自然酸化膜が形成されやすく、上記接続孔の内部に金属膜を埋め込む際は、良好な導通をとるために自然酸化膜を除去する必要がある。特に、口径が0.1μm以下の微細な接続孔では、接続孔の底部の自然酸化膜の除去は難しく、従来から様々なクリーニング方法や処理装置等が提案されている。

【0007】

ところで、接続孔の底部に形成される自然酸化膜の厚さにはばらつきがある。このため、本発明者らは、オーバーエッチングすることなく接続孔の底部の自然酸化膜や不純物を完全に除去する方法として、接続孔を形成した後に、例えばHFガスとNH3ガスまたはNF3ガスとNH3ガス等の還元ガスを用いたドライクリーニング処理、あるいはNF3ガスとNH3ガスまたはNF3ガスとH2ガス等の還元ガスを含むArガスの反応性プラズマを用いたドライクリーニング処理を行っている。

【0008】

しかしながら、上記ドライクリーニング処理については、以下に説明する種々の技術的課題が存在する。

【0009】

ドライクリーニング処置を行った接続孔の底部および側面にはケイフッ化アンモニウム((NH4)2SiF6)が生成される。接続孔の内部には、一般にバリアメタル膜(例えばチタン膜上に窒化チタン膜を積み重ねた積層膜)を介して主導電材料となる金属膜が埋め込まれるが、上記生成物が残留していると、接続孔の底面においては、バリアメタル膜とその下の導電材料との接触抵抗がばらつき、接続孔の側面においては、バリアメタル膜が剥がれるなどの問題が生ずる。

【0010】

そこで、ドライクリーニング処理を行った接続孔部分を上記生成物の昇華温度である100℃程度で暖めることによって接続孔の底面および側面から生成物を除去する検討を行った。ところが、100℃程度の温度で接続孔部分を暖めても生成物を完全に昇華させることができず、上記問題を回避することはできないことが明らかとなった。これは、接続孔の底面および側面に生成する生成物の組成が全て(NH4)2SiF6ではなく、(NH4)2SiF6から僅かにずれた組成(非化学量論的組成の化合物、これらも混乱のないときは便宜的にケイフッ化アンモニウムまたは((NH4)2SiF6)で表示する)も含まれており、その組成が僅かにずれた生成物が100℃程度の温度では昇華せずに接続孔の底面および側面に残留したためと考えられる。

【0011】

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

一実施の形態によれば、絶縁膜に開口した接続孔の内部にバリアメタル膜を形成する前に、第1のチャンバに備わるウエハステージ上に半導体ウエハを置く工程と、ウエハステージの上方に設置されたシャワーヘッドを介して還元ガスを供給し、接続孔の内部をドライクリーニング処理する工程と、シャワーヘッドの加熱温度を利用した100から150℃の第1の温度で半導体ウエハを熱処理する工程と、半導体ウエハを第1のチャンバから第2のチャンバへ搬送する工程と、第2のチャンバにおいて150から400℃の第2の温度で半導体ウエハを熱処理する工程とを含むものである。

【発明の効果】

【0013】

一実施の形態によれば、接続孔部分における電気的特性のばらつきを低減することができるので、半導体装置の信頼性および製造歩留まりを向上させることができる。

【図面の簡単な説明】

【0014】

【図1】実施の形態1であるCMOSデバイスの製造工程を示す半導体基板の要部断面図である。

【図2】図1に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図3】図2に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図4】図3に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図5】(a)は図4に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図であり、(b)は同図(a)に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図6】実施の形態1によるバリアメタル膜の成膜装置の概略平面図である。

【図7】実施の形態1によるバリアメタル膜の成膜工程図である。

【図8】実施の形態1によるバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバの概略断面図である。

【図9】(a)、(b)および(c)は、それぞれ実施の形態1によるバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバにおける半導体ウエハの処理工程を説明するためのチャンバの概略断面図である。

【図10】nMISを形成した後に、ドライクリーニング処理および熱処理を半導体基板に施した場合のゲート電極と半導体基板との間に流れる電流と熱処理温度との関係を示すグラフ図である。

【図11】図5に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図12】図11に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図13】図12に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図14】図13に続くCMOSデバイスの製造工程中の図1と同じ箇所の要部断面図である。

【図15】実施の形態2によるバリアメタル膜の成膜工程図である。

【図16】(a)、(b)および(c)は、それぞれ実施の形態2によるバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバにおける半導体ウエハの処理工程を説明するためのチャンバの概略断面図である。

【図17】(a)、(b)および(c)は、それぞれ実施の形態3によるバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバの概略断面図である。

【発明を実施するための形態】

【0015】

本実施の形態において、便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、本実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。さらに、本実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、本実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0016】

また、本実施の形態においては、電界効果トランジスタを代表するMIS・FET(Metal Insulator Semiconductor Field Effect Transistor)をMISと略し、pチャネル型のMIS・FETをpMISと略し、nチャネル型のMIS・FETをnMISと略す。また、便宜的にMOSと記載しても非酸化膜を除外するものではない。また、本実施の形態において、ウエハと言うときは、Si(Silicon)単結晶ウエハを主とするが、それのみではなく、SOI(Silicon On Insulator)ウエハ、集積回路をその上に形成するための絶縁膜基板等を広く指すものとする。その形も円形またはほぼ円形のみでなく、正方形、長方形等も含むものとする。また、シリコン膜、シリコン部、シリコン部材等というときは、明らかにそうでないときまたはそうでない旨明示されているときを除き、純粋なシリコンばかりでなく、不純物を含むもの、SiGeまたはSiGeC等のシリコンを主要な成分の一つとする合金等(歪シリコンを含む)、添加物を含むものを含むことはいうまでもない。また、多結晶シリコン等というときも、明らかにそうでないときまたはそうでない旨明示されているときを除き、典型的なものばかりでなく、アモルファスシリコン等も含むことはいうまでもない。

【0017】

また、本実施の形態を説明するための全図において、同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。以下、本実施の形態を図面に基づいて詳細に説明する。

【0018】

また、ドライクリーニング技術に関しては、一之瀬らの日本国特許出願第2006−3704号(2006.1.11出願)、日本国特許出願第2006−12355号(2006.1.20出願)、日本国特許出願第2006−107780号(2006.4.10出願)に開示されているので、それと重複する部分については、原則として繰り返さないこことする。

【0019】

(実施の形態1)

実施の形態1によるCMOS(Complementary Metal Oxide Semiconductor)デバイスの製造方法を図1から図14を用いて説明する。図1から図5および図11から図14はCMOSデバイスの要部断面図、図6はバリアメタル成膜装置の概略平面図、図7はバリアメタル膜の成膜工程図、図8はバリアメタル成膜装置に備わるドライクリーニング処理用チャンバの概略断面図、図9(a)、(b)および(c)はそれぞれバリアメタル成膜装置に備わるドライクリーニング処理用チャンバにおける半導体ウエハの処理工程を説明するためのチャンバの概略断面図、図10はnMISを形成した後に、ドライクリーニング処理および熱処理を半導体基板に施した場合のゲート電極と半導体基板との間に流れる電流と熱処理温度との関係を示すグラフ図である。

【0020】

まず、図1に示すように、例えばp型の単結晶シリコンからなる半導体基板(半導体ウエハと称する平面略円形状の半導体の薄板)1を用意する。次に、半導体基板1の主面に素子分離領域4を形成する。素子分離領域4は、半導体基板1をエッチングして深さ0.35μmの溝を形成し、続いて半導体基板1の主面上にCVD(Chemical Vapor Deposition)法により絶縁膜、例えば酸化シリコン膜を堆積した後、溝の外部の酸化シリコン膜をCMP(Chemical Mechanical Polishing)法により除去することによって形成する。

【0021】

次に、半導体基板1のnMIS形成領域にp型不純物、例えばボロン(B)をイオン注入してp型ウェル6を形成し、半導体基板1のpMIS形成領域にn型不純物、例えばリン(P)をイオン注入してn型ウェル8を形成する。この後、p型ウェル6またはn型ウェル8にnMISまたはpMISのしきい値を制御するための不純物をイオン注入してもよい。

【0022】

次に、例えばフッ酸水溶液を用いたウェットエッチングにより半導体基板1の表面を洗浄した後、半導体基板1を熱酸化して、例えば厚さ5nmのゲート絶縁膜9を半導体基板1の表面(p型ウェル6およびn型ウェル8のそれぞれの表面)に形成する。

【0023】

次に、図2に示すように、ゲート絶縁膜9上に、例えば厚さ0.2μmのゲート電極用の導体膜を形成した後、レジストパターンをマスクとしたドライエッチングによりゲート電極用の導体膜を加工して導体膜からなるゲート電極10n,10pを形成する。ゲート電極用の導体膜は、例えばCVD法により形成された多結晶シリコン膜からなり、nMIS形成領域にはn型不純物が導入された多結晶シリコン膜からなるゲート電極10n、pMIS形成領域にはp型不純物が導入された多結晶シリコン膜からなるゲート電極10pが形成される。

【0024】

次に、p型ウェル6にn型不純物、例えばヒ素(As)をイオン注入し、nMISのゲート電極10nに対して自己整合的に相対的に低濃度なソース・ドレイン拡張領域11を形成する。同様に、n型ウェル8にp型不純物、例えばフッ化ボロン(BF2)をイオン注入し、pMISのゲート電極10pに対して自己整合的に相対的に低濃度なソース・ドレイン拡張領域12を形成する。上記ソース・ドレイン拡張領域11,12の深さは、例えば30nmである。

【0025】

次に、図3に示すように、半導体基板1の主面上に、例えば厚さ10nmの酸化シリコン膜13をCVD法により堆積した後、さらに酸化シリコン膜13上に窒化シリコン膜をCVD法により堆積する。続いて窒化シリコン膜をRIE(Reactive Ion Etching)法により異方性エッチングして、nMISのゲート電極10nおよびpMISのゲート電極10pのそれぞれの側壁にサイドウォール15を形成する。その後、p型ウェル6にn型不純物、例えばヒ素をイオン注入し、nMISのゲート電極10nおよびサイドウォール15に対して自己整合的に相対的に高濃度なソース・ドレイン拡散領域16を形成する。同様に、n型ウェル8にp型不純物、例えばフッ化ボロンをイオン注入し、pMISのゲート電極10pおよびサイドウォール15に対して自己整合的に相対的に高濃度なソース・ドレイン拡散領域17を形成する。上記ソース・ドレイン拡散領域16,17の深さは、例えば50nmである。

【0026】

次に、サリサイド技術によりnMISのゲート電極10nおよびソース・ドレイン拡散領域16の表面およびpMISのゲート電極10pおよびソース・ドレイン拡散領域17の表面に低抵抗のニッケルシリサイド(NiSi)層18を形成する。なお、ここではニッケルシリサイド層を例示したが、他のシリサイド層、例えばチタンシリサイド層またはコバルトシリサイド層等を形成してもよい。ニッケルシリサイド層18は、例えば以下に説明する方法により形成される。

【0027】

まず、半導体基板1の主面上にスパッタリング法によりニッケル膜および窒化チタン膜を順次堆積する。ニッケル膜の厚さは、例えば10nm、窒化チタン膜の厚さは、例えば15nmである。窒化チタン膜はニッケル膜の酸化を防止するためにニッケル膜上に設けられ、窒化チタン膜に代えてチタン膜を用いてもよい。続いて半導体基板1にRTA(Rapid Thermal Anneal)法を用いて、例えば温度320℃の熱処理を30秒施すことにより、ニッケル膜とnMISのゲート電極10nを構成するn型多結晶シリコン膜およびニッケル膜とnMISのソース・ドレイン拡散領域16が形成された半導体基板1を構成する単結晶シリコンとを選択的に反応させてニッケルシリサイド層18を形成する。同様に、ニッケル膜とpMISのゲート電極10pを構成するp型多結晶シリコン膜およびニッケル膜とpMISのソース・ドレイン拡散領域17が形成された半導体基板1を構成する単結晶シリコンとを選択的に反応させてニッケルシリサイド層18を形成する。続いて硫酸を用いたウエット洗浄、または硫酸と過酸化水素水とを用いたウエット洗浄等により、未反応のニッケル膜および窒化チタン膜を除去した後、半導体基板1にRTA法を用いて、例えば温度550℃の熱処置を30秒施すことにより、ニッケルシリサイド層18の低抵抗化を行う。

【0028】

次に、図4に示すように、半導体基板1の主面上にCVD法により窒化シリコン膜を堆積して第1絶縁膜19aを形成する。続いて第1絶縁膜19a上にプラズマCVD法によりTEOS(Tetra Ethyl Ortho Silicate)膜を堆積して第2絶縁膜19bを形成し、第1および第2絶縁膜19a,19bからなる層間絶縁膜を形成する。その後、第2絶縁膜19bの表面をCMP法により研磨する。下地段差に起因して第1絶縁膜19aの表面に凹凸形状が形成されていても、第2絶縁膜19bの表面をCMP法により研磨することにより、その表面が平坦化された層間絶縁膜が得られる。

【0029】

次に、レジストパターンをマスクとして第1および第2絶縁膜19a,19bをエッチングし、接続孔20を所定の箇所、例えばnMISのゲート電極10nおよびソース・ドレイン拡散領域16、ならびにpMISのゲート電極10pおよびソース・ドレイン拡散領域17の上方に位置する第1および第2絶縁膜19a,19bに形成する。接続孔20の口径は0.1μm以下、例えば0.08μmである。

【0030】

次に、図5(a)に示すように、接続孔20の内部を含む半導体基板1の主面上にチタン膜21を堆積し、さらに図5(b)に示すように、チタン膜21上に窒化チタン膜22を堆積する。チタン膜21は酸素原子を25at%まで固溶できることからニッケルシリサイド層18表面の還元材として用いられて、ニッケルシリサイド層18との接触抵抗を低減する機能を有する。また、窒化チタン膜22は後の工程で接続孔20の内部に埋め込まれる金属膜の構成原子が拡散するのを抑制または防止する機能を有する。なお、以下の説明においては、チタン膜21上に窒化チタン膜22を積み重ねた積層膜をバリアメタル膜と言い、接続孔20の内部に埋め込まれて主導電材料となる金属膜とは区別する。

【0031】

チタン膜21および窒化チタン膜22の成膜には、図6に示す成膜装置50が用いられる。以下に、チタン膜21および窒化チタン膜22の形成方法について図6から図9を用いて詳細に説明する。

【0032】

成膜装置50は、第1搬送室51aと第2搬送室51bの2つの搬送室が配置され、第1搬送室51aの周囲に開閉手段であるゲートバルブ52を介してローダ53、アンローダ54および3つのチャンバ55,56,57が備わり、第2搬送室51bの周囲に開閉手段であるゲートバルブ52を介して2つのチャンバ58,59が備わったマルチチャンバタイプである。さらに、第1搬送室51aと第2搬送室51bとの間には2つの搬送用のチャンバ60,61が備わっている。第1搬送室51aは排気機構等により所定の真空度に保持され、その中央部には半導体ウエハSWを搬送するための多関節アーム構造の搬送用ロボット62aが設けられている。同様に、第2搬送室51bは排気機構等により所定の真空度に保持され、その中央部には半導体ウエハSWを搬送するための多関節アーム構造の搬送用ロボット62bが設けられている。

【0033】

第1搬送室51aに備わるチャンバ55,56は、例えば150℃以上の高温の加熱処理を行う加熱処理用チャンバ、チャンバ57はドライクリーニング処置用チャンバである。第2搬送室51bに備わるチャンバ58は高指向性スパッタリング法またはプラズマCVD法によりチタン膜21を堆積するチタン成膜用チャンバ、チャンバ59はMOCVD(Metal Organic Chemical Vapor Deposition)法またはプラズマCVD法により窒化チタン膜22を堆積する窒化チタン成膜用チャンバである。第1搬送室51aと第2搬送室51bとの間に備わるチャンバ60,61は第1搬送室51aと第2搬送室51bとの間での半導体ウエハSWの受け渡しを行う受渡用チャンバであり、また半導体ウエハSWの冷却にも用いられる冷却用チャンバである。なお、成膜装置50では、第1搬送室51aのみに備わるチャンバを3つとし、第2搬送室51bのみに備わるチャンバを2つとしたが、これに限定されるものではなく、同じ用途のチャンバまたは他の用途のチャンバを追加することも可能である。

【0034】

まず、ローダ53に複数の半導体ウエハSWを搭載したフープ(Front Open Unified Pod)を載せた後(図7の工程P1)、搬送用ロボット62aによってフープから1枚の半導体ウエハSWを取り出し、第1搬送室51aへ真空搬入する。フープは半導体ウエハSWのバッチ搬送用の密閉収納容器であり、通常25枚、12枚、6枚等のバッチ単位で半導体ウエハSWを収納する。フープの容器外壁は微細な通気フィルタ部を除いて機密構造になっており、塵埃はほぼ完全に排除される。従って、クラス1000の雰囲気で搬送しても、内部はクラス1の清浄度が保てるようになっている。成膜装置50とのドッキングは、フープの扉を成膜装置50の内部に引き込むことによって清浄さを保持した状態で行われる。

【0035】

次に、搬送用ロボット62aによって半導体ウエハSWを第1搬送室51aからドライクリーニング処理用のチャンバ57へ真空搬送する(図7の工程P2)。図8にチャンバ57の概略断面図を示す。チャンバ57は主としてウエハステージ57a、ウエハリフトピン57b、シャワーヘッド57cおよびリモートプラズマ発生装置57dによって構成される。ウエハステージ57aおよびウエハリフトピン57bは独立した昇降機構を持ち、シャワーヘッド57cと半導体ウエハSWとの距離および半導体ウエハSWとウエハステージ57aとの距離を任意に制御することができる。また、ウエハステージ57aの上方に設置されたシャワーヘッド57cは常に一定温度に維持されており、その温度は例えば180℃である。

【0036】

チャンバ57へ半導体ウエハSWを搬入する時は、図9(a)に示すように、ウエハステージ57aを下降させ、ウエハリフトピン57bを上昇させて、ウエハリフトピン57b上に半導体ウエハSWを載せる。シャワーヘッド57cと半導体ウエハSWとの距離は、例えば16.5±12.7mm、半導体ウエハSWとウエハステージ57aとの距離は、例えば25.4±17.8mmに設定される。

【0037】

続いて半導体ウエハSWの主面上をドライクリーニング処理する時は、図9(b)に示すように、ウエハステージ57aを上昇させ、ウエハリフトピン57bを下降させて、ウエハステージ57a上に半導体ウエハSWを載せる。シャワーヘッド57cと半導体ウエハSWとの距離は、例えば17.8±5.1mmに設定される。

【0038】

ドライクリーニング処理時には、リモートプラズマ発生装置57dにおいて還元ガス、例えばNF3ガスおよびNH3ガスを添加したArガスまたはNF3ガスおよびH2ガスを添加したArガスを励起させてプラズマを生成し、このプラズマをチャンバ57内へ導入する。チャンバ57内に導入されたプラズマをシャワーヘッド57cを介して半導体ウエハSWの主面上に供給することにより、プラズマとニッケルシリサイド層18の表面に形成された自然酸化膜との間で起きる、例えば式(1)に示す還元反応によって自然酸化膜が除去される。ドライクリーニング処理時におけるプロセス条件は、例えばシャワーヘッド温度180℃、NF3ガス流量14sccm、NH3ガス流量70sccm、圧力400Pa、プラズマパワー30Wである。

【0039】

SiO2+NF3+NH3→ (NH4)2SiF6+O2 式(1)

この時、還元反応により生成された生成物((NH4)2SiF6)が接続孔20の内部を含む半導体ウエハSWの主面上に残留する。さらに、半導体ウエハSWはウエハステージ57a上に載せてあるだけであり、上記生成物は半導体ウエハSWの側面および裏面の一部にも残留する。半導体ウエハSWの側面および裏面の一部に残留する生成物は、半導体ウエハSWを他のチャンバへ搬送する場合などにおいて剥がれ、汚染や発塵の原因となる。そこで、ドライクリーニング処置に続いて、チャンバ57内において半導体ウエハSWに熱処理を施すことにより、半導体ウエハSWの主面上に残留する生成物を除去すると同時に、半導体ウエハSWの側面および裏面の一部に残留する生成物を除去する。

【0040】

続いて半導体ウエハSWを熱処理する時は、図9(c)に示すように、ウエハステージ57aを下降させ、ウエハリフトピン57bを上昇させて、半導体ウエハSWを温度180℃に設定されたシャワーヘッド57cへ近づける。シャワーヘッド57cと半導体ウエハSWとの距離は、例えば3.8±2.6mm、半導体ウエハSWとウエハステージ57aとの距離は、例えば5.9mm以上に設定される。

【0041】

熱処理時には、シャワーヘッド57cの加熱温度(180℃)を利用して半導体ウエハSWが加熱される。半導体ウエハSWの温度は100から150℃となり、上記ドライクリーニング処置時に半導体ウエハSWの主面上に形成された生成物((NH4)2SiF6)が、例えば式(2)に示す反応によって昇華し除去される。さらに、この熱処理によって半導体ウエハSWの側面および裏面も加熱されて、側面および裏面の一部に残留した生成物も除去される。

【0042】

(NH4)2SiF6→ SiF4+2NH3+2HF 式(2)

しかしながら、上記ドライクリーニング処理時に半導体ウエハSWに形成された生成物の組成が(NH4)2SiF6から僅かでもずれていると、温度100から150℃の熱処理では式(2)の反応が起こり難く、完全に生成物を除去することができなくなり、極微少の生成物が半導体ウエハSWの主面上に残留する。前述したように、接続孔20の内部に微少でも生成物が残留していると、その後接続孔20に内部に形成されるチタン膜21とニッケルシリサイド層18との接触抵抗のばらつきなどの問題が生じる。そこで、次工程において、半導体ウエハSWに150℃よりも高い温度の熱処理を施して、半導体ウエハSWの主面上に残留した微少の生成物を除去する。

【0043】

次に、搬送用ロボット62aによって半導体ウエハSWをドライクリーニング処理用のチャンバ57から加熱処理用のチャンバ55(またはチャンバ56)へ第1搬送室51aを介して真空搬送し、チャンバ55(またはチャンバ56)に備わるステージ上に載せる(図7の工程P3)。チャンバ55(またはチャンバ56)のステージ上に半導体ウエハSWを載せることにより、半導体ウエハSWを所定の温度で加熱し、100から150℃の温度では昇華せずに半導体ウエハSWの主面上に残留した生成物を昇華させて除去する。半導体ウエハSWの主面上での温度は、例えば150から400℃が適切な範囲と考えられる(他の条件によってはこの範囲に限定されないことはもとよりである)。また、量産に適した範囲としては165から350℃が考えられるが、さらに180から220℃等の200℃を中心値とする範囲が最も好適と考えられる。

【0044】

図10は、nMIS(図10の挿入図)を形成した後に、ドライクリーニング処理および熱処理を半導体基板に施した場合のゲート電極と半導体基板との間に流れる電流(リーク電流)と熱処理温度との関係を示すグラフ図である。

【0045】

正常なnMISのゲート電流は1×10−13A/μm2程度であるが、nMISの表面にドライクリーニング処理により生成した生成物が残留すると、その生成物を通して5×10−11A/μm2以上の表面リーク電流が流れる。しかし、150℃よりも高い温度で熱処理を行うと、温度の増加に従って表面リーク電流が減少し、例えば160℃程度の温度で熱処理をすると、リーク電流は1×10−12A/μm2程度に減少し、さらに180℃程度の温度で熱処理をすると、リーク電流は1×10−13A/μm2程度に減少する。このことから、180℃よりも高い温度で熱処理をすることにより、nMISの表面にリーク電流が流れない状態まで生成物を除去することができると考えられる。

【0046】

次に、搬送用ロボット62aによって半導体ウエハSWを加熱処理用のチャンバ55(またはチャンバ56)から冷却・受渡用のチャンバ60(またはチャンバ61)へ第1搬送室51aを介して真空搬送し、チャンバ60(またはチャンバ61)に備わるステージ上に載せる(図7の工程P4)。チャンバ60(またはチャンバ61)のステージ上に半導体ウエハSWを載せることにより、半導体ウエハSWは冷却される。

【0047】

次に、搬送用ロボット62bによって半導体ウエハSWを冷却・受渡用のチャンバ60(またはチャンバ61)からチタン成膜用のチャンバ58へ第2搬送室51bを介して真空搬送する(図7の工程P5)。チャンバ58内を排気機構により所定の真空度、例えば1.33×10−6Paとした後、半導体ウエハSWを所定の温度に加熱し、チャンバ58内へArガスを所定の流量により導入して高指向性スパッタリング法により半導体ウエハSWの主面上へチタン膜21を堆積する。チタン膜21の厚さは、例えば20nmである。なお、チタン膜21は高指向性スパッタリング法の他に、プラズマCVD法により堆積することができる。

【0048】

次に、搬送用ロボット62bによって半導体ウエハSWをチタン成膜用のチャンバ58から窒化チタン成膜用のチャンバ59へ第2搬送室51bを介して真空搬送する(図7の工程P6)。チャンバ59内を排気機構により所定の真空度とした後、半導体ウエハSWを所定の温度に加熱し、チャンバ59内へ所定のガスを所定の流量により導入してMOCVD法またはプラズマCVD法により半導体ウエハSWの主面上へ窒化チタン膜22を堆積する。窒化チタン膜22の厚さは、例えば5nmである。

【0049】

次に、搬送用ロボット62bによって半導体ウエハSWを窒化チタン成膜用のチャンバ59から冷却・受渡用のチャンバ60(またはチャンバ61)へ第2搬送室51bを介して真空搬送する(図7の工程P7)。

【0050】

次に、搬送用ロボット62aによって半導体ウエハSWを冷却・受渡用のチャンバ60(またはチャンバ61)からアンローダ54へ真空搬出し(図7の工程P8)、アンローダ54に置かれたフープへ載せる。

【0051】

このように、ドライクリーニング処理の工程(図7の工程P2)とチタン膜21を堆積する工程(図7の工程P5)との間に150から400℃の熱処理を半導体基板1に施すことによって(図7の工程P3)、接続孔20の底面および側面にドライクリーニング処置時に生成された生成物が除去されるので、接続孔20の底面におけるチタン膜21とニッケルシリサイド層18との接触抵抗のばらつきを低減することができる。さらに、接続孔20の側面におけるチタン膜21の剥がれを防止することができる。

【0052】

その後、図11に示すように、接続孔20の内部を含む半導体基板1の主面上にタングステン膜23をCVD法により堆積し、例えばCMP法によりタングステン膜23の表面を平坦化することによって接続孔20の内部にタングステン膜23を埋め込み、タングステン膜23を主導電材料とするプラグを形成する。

【0053】

なお、前述した接続孔20の内部にプラグを形成する工程では、プラグの主導電材料をタングステン膜23とし、バリアメタル膜をチタン膜21上に窒化チタン膜22を積み重ねた積層膜としたが、これに限定されるものではなく、種々変更することは可能である。例えば(1)プラグの主導電材料をタングステン膜とし、バリアメタル膜を窒化タングステン膜とする。1台のタングステン成膜装置を用いて窒化タングステン膜およびタングステン膜を順次成膜することができるので、スループットが向上し、コストを低減することができる。(2)プラグの主導電材料を銅膜とし、バリアメタル膜を窒化チタン膜とする。(3)プラグの主導電材料を銅膜とし、バリアメタル膜を窒化タンタル膜とする。窒化タンタル膜を用いることにより、バリアメタル膜に窒化チタン膜を用いた場合よりも銅原子が拡散するのを抑制または防止することができる。(4)プラグの主導電材料を銅膜とし、バリアメタル膜を窒化タンタル膜上にタンタル膜を積み重ねた積層膜とする。銅膜と窒化タンタル膜との間にタンタル膜を挿入することにより、銅膜と窒化タンタル膜との密着性を向上させることができる。(5)プラグの主導電材料を銅膜とし、バリアメタル膜を窒化タンタル膜上にルテニウム膜を積み重ねた積層膜とする。銅膜と窒化タンタル膜との間にルテニウム膜を挿入することにより、銅膜と窒化タンタル膜との密着性を向上させることができる。(6)プラグの主導電材料をアルミニウム膜とし、バリアメタル膜をチタン膜上に窒化チタン膜を積み重ねた積層膜、または窒化タングステン膜とする。

【0054】

次に、図12に示すように、半導体基板1の主面上にストッパ絶縁膜24および配線形成用の絶縁膜25を順次形成する。ストッパ絶縁膜24は絶縁膜25への溝加工の際にエッチングストッパとなる膜であり、絶縁膜25に対してエッチング選択比を有する材料を用いる。ストッパ絶縁膜24は、例えばプラズマCVD法により形成される窒化シリコン膜とし、絶縁膜25は、例えばプラズマCVD法により形成される酸化シリコン膜とすることができる。なお、ストッパ絶縁膜24と絶縁膜25には次に説明する第1層目の配線が形成される。

【0055】

次に、シングルダマシン法により第1層目の配線を形成する。まず、レジストパターンをマスクとしたドライエッチングによってストッパ絶縁膜24および絶縁膜25の所定の領域に配線溝26を形成した後、半導体基板1の主面上にバリアメタル膜27を形成する。バリアメタル膜27は、例えば窒化チタン膜、窒化タンタル膜、窒化タンタル膜上にタンタル膜を積み重ねた積層膜、または窒化タンタル膜上にルテニウム膜を積み重ねた積層膜である。続いてCVD法またはスパッタリング法によりバリアメタル膜27上に銅のシード層を形成し、さらに電解めっき法を用いてシード層上に銅めっき膜を形成する。銅めっき膜により配線溝26の内部を埋め込む。続いて配線溝26以外の領域の銅めっき膜、シード層およびバリアメタル膜27をCMP法により除去して、銅膜を主導電材料とする第1層目の配線M1を形成する。

【0056】

次に、デュアルダマシン法により第2層目の配線を形成する。まず、図13に示すように、半導体基板1の主面上にキャップ絶縁膜28、層間絶縁膜29および配線形成用のストッパ絶縁膜30を順次形成する。キャップ絶縁膜28および層間絶縁膜29には、後に説明するように接続孔が形成される。キャップ絶縁膜28は、層間絶縁膜29に対してエッチング選択比を有する材料で構成され、例えばプラズマCVD法により形成される窒化シリコン膜とすることができる。さらにキャップ絶縁膜28は第1層目の配線M1を構成する銅の拡散を防止する保護膜としての機能を有している。層間絶縁膜29は、例えばプラズマCVD法により形成されるTEOS膜とすることができる。ストッパ絶縁膜30は、層間絶縁膜29および後にストッパ絶縁膜30の上層に堆積される配線形成用の絶縁膜に対してエッチング選択比を有する絶縁材料で構成され、例えばプラズマCVD法により形成される窒化シリコン膜とすることができる。

【0057】

次に、孔形成用のレジストパターンをマスクとしたドライエッチングによりストッパ絶縁膜30を加工した後、ストッパ絶縁膜30上に配線形成用の絶縁膜31を形成する。絶縁膜31は、例えばTEOS膜とすることができる。

【0058】

次に、配線溝形成用のレジストパターンをマスクとしたドライエッチングにより絶縁膜31を加工する。この際、ストッパ絶縁膜30がエッチングストッパとして機能する。続いてストッパ絶縁膜30および配線溝形成用のレジストパターンをマスクとしたドライエッチングにより層間絶縁膜29を加工する。この際、キャップ絶縁膜28がエッチングストッパとして機能する。続いて露出したキャップ絶縁膜28をドライエッチングにより除去することにより、キャップ絶縁膜28および層間絶縁膜29に接続孔32が形成され、ストッパ絶縁膜30および絶縁膜31に配線溝33が形成される。

【0059】

次に、接続孔32および配線溝33の内部に第2層目の配線を形成する。第2層目の配線は、バリアメタル層および主導電材料である銅膜からなり、この配線と下層配線である第1層目の配線M1とを接続する接続部材は第2層目の配線と一体に形成される。まず、接続孔32および配線溝33の内部を含む半導体基板1の主面上にバリアメタル膜34を形成する。バリアメタル膜34は、例えば窒化チタン膜、窒化タンタル膜、窒化タンタル膜上にタンタル膜を積み重ねた積層膜、または窒化タンタル膜上にルテニウム膜を積み重ねた積層膜である。バリアメタル膜34を形成する前には前述したドライクリーニング処理が行われるが、このドライクリーニング処理においてもその後、前述した100から150℃の温度での加熱と150℃よりも高い温度での加熱とを半導体ウエハに対して行い、接続孔32の底面ならびに接続孔32および配線溝33の側壁に生成した生成物の除去を行ってもよい。これにより、バリアメタル膜34と第1層目の配線M1との接触抵抗のばらつきを低減することができ、また、キャップ絶縁膜28、層間絶縁膜29、ストッパ絶縁膜30および絶縁膜31からのバリアメタル膜34の剥がれを防止することができる。続いてCVD法またはスパッタリング法によりバリアメタル膜34上に銅のシード層を形成し、さらに電解めっき法を用いてシード層上に銅めっき膜を形成する。銅めっき膜により接続孔32および配線溝33の内部を埋め込む。続いて接続孔32および配線溝33以外の領域の銅めっき膜、シード層およびバリアメタル膜34をCMP法により除去して、銅膜を主導電材料とする第2層目の配線M2を形成する。

【0060】

その後、図14に示すように、例えば前述した第2層目の配線M2と同様な方法によりさらに上層の配線を形成する。図14では、第3層目から第6層目の配線M3,M4,M5,M6を形成したCMOSデバイスを例示している。続いて第6層目の配線M6上に窒化シリコン膜35を形成し、窒化シリコン膜35上に酸化シリコン膜36を形成する。これら窒化シリコン膜35および酸化シリコン膜36は、外部からの水分や不純物の侵入防止およびα線の透過の抑制を行うパッシベーション膜として機能する。

【0061】

次に、窒化シリコン膜35および酸化シリコン膜36をレジストパターンをマスクとしたエッチングにより加工して、第6層目の配線M6の一部(ボンディングパッド部)を露出させる。続いて露出した第6層目の配線M6上に金膜およびニッケル膜等の積層膜からなるバンプ下地電極37を形成し、バンプ下地電極37上に金または半田等からなるバンプ電極38を形成することにより、実施の形態1であるCMOSデバイスが略完成する。なお、このバンプ電極38は外部接続用電極となる。この後、半導体ウエハSWから半導体チップに個々に切り分けられ、パッケージ基板等に実装されて半導体装置が完成するが、それらの説明は省略する。

【0062】

なお、実施の形態1のドライクリーニング処理では、リモートプラズマ発生装置57dにおいて還元ガス、例えばNF3ガスおよびNH3ガスを添加したArガス(プラズマ励起用のガスとしてはArガスが多用されるが、その他の希ガスまたはそれらの混合ガスでもよい)を励起させてプラズマを生成し、このプラズマをチャンバ57内へ導入して自然酸化膜を還元反応により除去したが、プラズマを用いずに、HFガスとNH3ガスまたはNF3ガスとNH3ガス等の還元ガスをチャンバ57内へ導入して自然酸化膜を還元反応により除去してもよい。

【0063】

また、リモートプラズマ装置に限定されるものではなく、その他の特性に問題がなければ、通常のプラズマ装置を用いても問題はない。リモートプラズマは基板に損傷を与えない利点がある。

【0064】

また、プラズマを用いて処理する場合は、上記ガスの組み合わせに限らず、窒素、水素、フッ素(これらの複合ラジカルを含む)のそれぞれのラジカルまたは反応種を生成するものであれば、特にこのプロセスに対して有害なものでなければ、その他のガスの組み合わせでもよい。すなわち、窒素、水素およびフッ素ラジカル生成ガス(混合ガス含む)とプラズマ励起ガスとその他の添加ガス等との混合ガス雰囲気を適宜用いればよい。

【0065】

また、還元ガス等の反応ガスは上記ガスに限らず、酸化膜と比較的低温で反応して気化する反応種を生成するものであればよい。

【0066】

このように、実施の形態1によれば、接続孔20の内部にバリアメタル膜(チタン膜21上に窒化チタン膜22を積み重ねた積層膜)を形成する前に行うドライクリーニング処置により、接続孔20の底面および側面に化学量論的組成から僅かにずれた生成物が残留するが、この生成物はドライクリーニング処理の後に行う150℃よりも高い温度の熱処理により除去されるので、接続孔20の底面におけるバリアメタル膜とニッケルシリサイド層18との接触抵抗のばらつきを低減することができ、また接続孔20の側面におけるバリアメタル膜の剥がれを防ぐことができるので、接続孔20部分における電気的特性のばらつきを低減することができる。また、実施の形態1は上下層の配線を接続する接続孔部分にも適用することができ、同様の効果を得ることができる。例えば実施の形態1に例示したデュアルダマシン配線の形成工程において、接続孔32および配線溝33の内部にバリアメタル膜34を形成する前に行うドライクリーニング処理の後に実施の形態1を実施することにより、接続孔32部分における電気的特性のばらつきを低減することができる。

【0067】

(実施の形態2)

前述した実施の形態1で説明したように、バリアメタル膜の形成工程において行われるドライクリーニング処理では、半導体ウエハSWの主面上、側面および裏面の一部に生成物が残留する。このため、ドライクリーニング処理用のチャンバ57に備わる180℃に設定されたシャワーヘッド57cによって半導体ウエハSWを100から150℃の温度で加熱して(NH4)2SiF6の組成の生成物を除去し、さらに、加熱処理用のチャンバ55,56により半導体ウエハを150℃よりも高い温度で加熱して(NH4)2SiF6から僅かに組成のずれた生成物の除去を行っている。

【0068】

実施の形態2では、ドライクリーニング処理用のチャンバ57に備わるシャワーヘッド57CHの温度を180℃よりも高い温度、例えば250℃に設定し、ドライクリーニング処理の直後に、シャワーヘッド57CHにより半導体ウエハSWを180から220℃の温度で加熱して(NH4)2SiF6の組成の生成物および(NH4)2SiF6から僅かに組成のずれた生成物の除去を行う。

【0069】

実施の形態2によるバリアメタル膜の形成方法を図15および図16を用いて説明する。図15はバリアメタル膜の成膜工程図、図16(a)、(b)および(c)はそれぞれバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバにおける半導体ウエハの処理工程を説明するためのチャンバの概略断面図である。なお、バリアメタル膜の成膜装置は、前述した実施の形態1の成膜装置50を用いる。

【0070】

まず、前述した実施の形態1と同様にして、半導体ウエハSWをローダ53からドライクリーニング処理用のチャンバ57へ真空搬送する(図15の工程P1,P2)。チャンバ57に備わるシャワーヘッド57CHは常に一定温度に維持されており、その温度は例えば250℃である。

【0071】

チャンバ57へ半導体ウエハSWを搬入する時は、図16(a)に示すように、ウエハステージ57aを下降させ、ウエハリフトピン57bを上昇させて、ウエハリフトピン57b上に半導体ウエハSWを載せる。シャワーヘッド57CHと半導体ウエハSWとの距離は、例えば16.5±12.7mm、半導体ウエハSWとウエハステージ57aとの距離は、例えば25.4±17.8mmに設定される。

【0072】

続いて半導体ウエハSWの主面上をドライクリーニング処理する時は、図16(b)に示すように、ウエハステージ57aを上昇させ、ウエハリフトピン57bを下降させて、ウエハステージ57a上に半導体ウエハSWを載せる。シャワーヘッド57CHと半導体ウエハSWとの距離は、例えば17.8±5.1mmに設定される。ドライクリーニング処理が行われた半導体ウエハSWの主面上、側面および裏面の一部には、還元反応により生成された生成物((NH4)2SiF6)が残留する。

【0073】

続いて半導体ウエハSWを熱処理する時は、図16(c)に示すように、ウエハステージ57aを下降させ、ウエハリフトピン57bを上昇させて、半導体ウエハSWを温度250℃に設定されたシャワーヘッド57CHへ近づける。シャワーヘッド57CHと半導体ウエハSWとの距離は、例えば3.8±2.6mm、半導体ウエハSWとウエハステージ57aとの距離は、例えば5.9mm以上に設定される。

【0074】

熱処理時には、シャワーヘッド57CHの加熱温度(250℃)を利用して半導体ウエハSWが加熱されるので、半導体ウエハSWの温度は150℃よりも高くなり、上記ドライクリーニング処置時に半導体ウエハSWの主面上、側面および裏面の一部に残留した(NH4)2SiF6の組成の生成物が除去され、さらに(NH4)2SiF6から僅かに組成のずれた生成物も除去される。

【0075】

次に、搬送用ロボット62aによって半導体ウエハSWをドライクリーニング処理用のチャンバ57から冷却・受渡用のチャンバ60(またはチャンバ61)へ第1搬送室51aを介して真空搬送し、チャンバ60(またはチャンバ61)に備わるステージ上に載せる(図15の工程P3)。チャンバ60(またはチャンバ61)のステージ上に半導体ウエハSWを載せることにより、半導体ウエハSWは冷却される。

【0076】

その後は前述した実施の形態1と同様に、搬送用ロボット62bによってチタン成膜用のチャンバ58においてチタン膜を堆積し(図15の工程P4)、窒化チタン成膜用のチャンバ59においてチタン膜上に窒化チタン膜を堆積した後(図15の工程P5)、半導体ウエハSWを冷却・受渡用のチャンバ60(またはチャンバ61)へ真空搬送する(図15の工程P6)。さらに、搬送用ロボット62aによって半導体ウエハSWをアンローダ54へ真空搬出し(図15の工程P7)、アンローダ54に置かれたフープへ載せる。

【0077】

このように、実施の形態2によれば、ドライクリーニング処理において半導体ウエハSWの側面および裏面の一部に生成した不要な生成物は、ドライクリーニング処理に続くシャワーヘッド57CHによる180から220℃の熱処理によって除去されるので、前述した実施の形態1で行う熱処理用のチャンバ55,56における熱処理工程が不要となり、前述した実施の形態1よりも製造工程数を削減することができる。

【0078】

(実施の形態3)

前述した実施の形態1で説明したように、バリアメタル膜の形成工程において行われるドライクリーニング処理では、一般に半導体ウエハSWをウエハステージ57aに単に置くだけであり、このため、半導体ウエハSWの主面上のみならず、半導体ウエハSWの側面および裏面の一部にも(NH4)2SiF6の組成の生成物が残留する。半導体ウエハSWの側面および裏面の一部に残留した生成物は、半導体ウエハSWを他のチャンバへ搬送する場合などにおいて剥がれて、汚染や発塵の原因となる。そこで、前述した実施の形態1および2では、ドライクリーニング処置に続いて、同じチャンバ57内で半導体ウエハSWに熱処理を施すことにより、半導体ウエハSWの主面上に残留する生成物を除去すると同時に、半導体ウエハSWの側面および裏面の一部に残留する生成物を除去している。

【0079】

実施の形態3では、ドライクリーニング処理時において半導体ウエハSWの裏面へのドライクリーニングガスの回り込みを防ぐことにより、半導体ウエハSWの側面および裏面の一部への生成物の生成を防止する。従って、前述した実施の形態1においてドライクリーニング処理後に続いて行われるシャワーヘッド57cによる半導体ウエハSWの熱処理、すなわちチャンバ57に備わるウエハステージ57aを下降させ、ウエハリフトピン57bを上昇させて、半導体ウエハSWを温度180℃に設定されたシャワーヘッド57cへ近づけることによる熱処理(図9(c))は不要となる。なお、ドライクリーニング処理により半導体ウエハSWの主面上に残留する生成物は、熱処理用のチャンバ55,56における150℃よりも高い温度の熱処理により除去することができる。

【0080】

実施の形態3によるドライクリーニング処理の方法を図17を用いて説明する。図17(a)、(b)および(c)はそれぞれバリアメタル膜の成膜装置に備わるドライクリーニング処理用チャンバの概略断面図である。

【0081】

図17(a)は、半導体ウエハSWの側面および裏面の一部への生成物の生成を防止する第1のドライクリーニング処理方法を説明する図である。半導体ウエハSWはウエハステージ57a上に置かれており、昇降機構を有するシーリング57eを半導体ウエハSWの主面上の周囲に接触させて押さえることにより、半導体ウエハSWの周囲および裏面へのドライクリーニングガスの回り込みを防いでいる。

【0082】

図17(b)は、半導体ウエハSWの側面および裏面の一部への生成物の生成を防止する第2のドライクリーニング処理方法を説明する図である。半導体ウエハSWは静電チャック機能を有するウエハステージ57a上に置かれており、半導体ウエハSWの裏面とウエハステージ57aとの間に隙間を形成することなく、ドライクリーニング処理を行うことができる。静電チャックは、ウエハステージ57aの上に誘電層を設けてウエハステージ57aと半導体ウエハSWとの間に電圧を印加し、両者間に発生した力によって半導体ウエハSWを吸着する機構である。吸着方式の違いによって誘電体として絶縁材料を使用するクーロン力型とジョンソン・ラベック力型とに分類されるが、低電圧で強い吸着力を有するジョンソン・ラベック力型はアルミナなどのセラミック製の静電チャックに多く、耐熱性と耐プラズマ性の面で有利であることから普及している。静電チャックは機械的な保持具を使用しないことから半導体ウエハSWの全面を均一に処理することができる。

【0083】

さらに、昇降機構を有するシャドウリング57fを半導体ウエハSWの主面上の周囲に備えており、半導体ウエハSWに接触させずに半導体ウエハSWの周囲をシャドウリング57fによって覆い、ウエハステージ57aの周囲から上方に向けてHeガス等の不活性ガスを流す。これにより、半導体ウエハSWの周囲および裏面へのドライクリーニングガスの回り込みを防いでいる。

【0084】

図17(c)は、半導体ウエハSWの側面および裏面の一部への生成物の生成を防止する第3のドライクリーニング処理方法を説明する図である。半導体ウエハSWはウエハステージ57a上に置かれており、昇降機構を有するシーリング57eを半導体ウエハSWの主面上の周囲に接触させて押さえることにより、半導体ウエハSWの周囲および裏面へのドライクリーニングガスの回り込みを防いでいる。

【0085】

さらに、シーリング57eの下部にはシーリング57eにつながる排気室57gが備わっており、ウエハステージ57aは排気室57g内に置かれている。排気室57gにはHeガス等の不活性ガスを排気室57gへ導入する配管と排気室57gから排気する配管とが設けられており、半導体ウエハSWの周囲および裏面へ不活性ガスを流入できる構造となっている。

【0086】

このように、実施の形態3によれば、ドライクリーニング処理において半導体ウエハSWの側面および裏面の一部に不要な生成物が生成せず、ドライクリーニング処理に続くシャワーヘッド57cによる半導体ウエハSWの熱処理が不要となるので、前述した実施の形態1よりも製造工程数を削減することができる。

【0087】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0088】

以下に、本願に開示された発明の概要を項に分けて簡潔に示す。

1.絶縁膜に開口した接続孔の内部にバリアメタル膜を介して金属膜を埋め込む半導体装置の製造方法であって、前記絶縁膜に前記接続孔を形成した後、前記接続孔の内部に前記バリアメタル膜を堆積する前に以下の工程を含む半導体装置の製造方法:

(a)第1のチャンバに備わるウエハステージ上に半導体ウエハを置く工程;

(b)前記ウエハステージの上方に設置されたシャワーヘッドを介して還元ガスを供給し、前記接続孔の内部をドライクリーニング処理する工程;

(c)前記シャワーヘッドの加熱温度を利用(シャワーヘッドの輻射等)した第1の温度で前記半導体ウエハに対して第1の熱処理する工程;

(d)前記半導体ウエハを前記第1のチャンバから第2のチャンバへ搬送する工程;

(e)前記第2のチャンバにおいて、前記第1の温度よりも高い第2の温度で前記半導体ウエハに対して第2の熱処理する工程。

【0089】

なお、本願では、主にバリアメタル形成前の接続孔内洗浄プロセスについて説明したが、本項1、8、または11の各サブパラグラフのプロセスは、その他のウエハ処理の前処理(ドライ洗浄)として適用できることは言うまでもない。

【0090】

すなわち、熱処理または各種の膜形成等のウエハ処理前の洗浄(例えばシリコン表面の自然酸化膜を比較的低温(例えば摂氏400度以下)で昇華、蒸発または気化する物質に変換する処理)としてドライ洗浄を実行する際に、ドライ洗浄の結果生成し、ウエハ表面(上面、側面、裏面を含む)に堆積、結露または凝結した洗浄残渣(洗浄処理生成物を含む)をドライ洗浄室と同室で、洗浄機構の一部または全部を利用して、第1の温度(ウエハ上面温度)で熱処理することによって前記洗浄残渣の一部を気化させて除去した後、ウエハを別の処理室に移動させ、そこで第1の温度よりも高い第2の温度(ウエハ上面温度)で熱処理することによって残留する残渣を気化させるものである。

【0091】

第1の熱処理は比較的低温で出来るため、装置構造を比較的簡単に出来ること、またはスループットを確保できる利点がある。また、この処理によって、ハンドリングに必要な裏面、側面の残渣は比較的完全に(ハンドリングによる汚染の伝播を回避する限度で)除去できる利点がある。第2の熱処理が必要なのは、生成物が非化学量論的な組成を含むと気化温度が上昇する場合があるほか、複雑な構造を有する実際のウエハ上面では、地形学的特徴に依存して、実効的気化温度が上昇する場合があるからである。

2.前記項1記載の半導体装置の製造方法おいて、前記第1の温度は100以上150℃未満である。

3.前記項1記載の半導体装置の製造方法において、前記第2の温度は150から400℃である。

4.前記項1記載の半導体装置の製造方法において、前記第2の温度は165から350℃である。

5.前記項1記載の半導体装置の製造方法において、前記第2の温度は180から220℃である。

6.前記項1記載の半導体装置の製造方法において、前記第2の温度は200℃である。

7.前記項1記載の半導体装置の製造方法において、前記第1のチャンバと前記第2のチャンバとの間の前記半導体ウエハの搬送は、真空搬送される。

8.絶縁膜に開口した接続孔の内部にバリアメタル膜を介して金属膜を埋め込む半導体装置の製造方法であって、前記絶縁膜に前記接続孔を形成した後、前記接続孔の内部に前記バリアメタル膜を堆積する前に以下の工程を含む半導体装置の製造方法:

(a)第1のチャンバに備わるウエハステージ上に半導体ウエハを置く工程;

(b)前記ウエハステージの上方に設置されたシャワーヘッドを介して還元ガスを供給し、前記半導体ウエハの主面上のシリコンの表面をドライクリーニング処理する工程;

(c)前記シャワーヘッドの加熱温度を利用した第1の温度で前記半導体ウエハに対して第1の熱処理する工程、

ここで、前記シャワーヘッドは180℃よりも高い温度に維持される。

【0092】

すなわち、熱処理または各種の膜形成等のウエハ処理前の洗浄(例えばシリコン表面の自然酸化膜を比較的低温(例えば摂氏400度以下)で昇華、蒸発または気化する物質に変換する処理)としてドライ洗浄を実行する際に、ドライ洗浄の結果生成し、ウエハ表面(上面、側面、裏面を含む)に堆積、結露または凝結した洗浄残渣(洗浄処理生成物を含む)をドライ洗浄室と同室で、洗浄機構の一部または全部を利用して、十分に高い温度(ウエハ上面温度)で熱処理することによって前記洗浄残渣のほぼ全部を気化させて除去するものである。

【0093】

この場合は一回の熱処理でしかも同室で出来るため、装置の処理室を有効に利用できる利点がある。

9.前記項8記載の半導体装置の製造方法において、前記第1の温度は180から220℃である。

10.前記項8記載の半導体装置の製造方法において、前記第1の温度は200℃である。

11.絶縁膜に開口した接続孔の内部にバリアメタル膜を介して金属膜を埋め込む半導体装置の製造方法であって、前記絶縁膜に前記接続孔を形成した後、前記接続孔の内部に前記バリアメタル膜を堆積する前に以下の工程を含む半導体装置の製造方法:

(a)第1のチャンバに備わるウエハステージ上に半導体ウエハを置く工程;

(b)前記ウエハステージの上方に設置されたシャワーヘッドを介して還元ガスを供給し、前記接続孔の内部をドライクリーニング処理する工程;

(c)前記半導体ウエハを前記第1のチャンバから第2のチャンバへ搬送する工程;

(d)前記第2のチャンバにおいて、第2の温度で前記半導体ウエハを熱処理(前記項1の第2の熱処理に対応)する工程、

ここで、前記工程(b)では、前記半導体ウエハの側面および裏面に前記還元ガスが供給されない。

【0094】

すなわち、熱処理または各種の膜形成等のウエハ処理前の洗浄(例えばシリコン表面の自然酸化膜を比較的低温(例えば摂氏400度以下)で昇華、蒸発または気化する物質に変換する処理)としてドライ洗浄を実行する際に、ドライ洗浄の結果生成し、ウエハ表面(このとき上面の周辺部、側面、裏面に堆積物が付着しないようにしてドライ洗浄を実行することが必要である)に堆積、結露または凝結した洗浄残渣(洗浄処理生成物を含む)をドライ洗浄室と別室で、十分に高い温度(ウエハ上面温度)で熱処理することによって前記洗浄残渣のほぼ全部を気化させて除去するものである。

12.前記項11記載の半導体装置の製造方法において、前記第2の温度は150から400℃である。

13.前記項11記載の半導体装置の製造方法において、前記第2の温度は165から350℃である。

14.前記項11記載の半導体装置の製造方法において、前記第2の温度は180から220℃である。

15.前記項11記載の半導体装置の製造方法において、前記第2の温度は200℃である。

16.前記項11記載の半導体装置の製造方法において、前記工程(b)は以下の工程を含む:

(b1)前記ウエハステージ上に置かれた前記半導体ウエハの周辺部をシーリングにより押さえる工程。

17.前記項11記載の半導体装置の製造方法において、前記工程(b)は以下の工程を含む:

(b1)前記半導体ウエハを静電チャックにより前記ウエハステージ上に吸着する工程;

(b2)前記半導体ウエハの周辺部を前記半導体ウエハと接触させずにシャドウリングにより覆い、前記ウエハステージの周辺部から不活性ガスを流入させる工程。

18.前記項11記載の半導体装置の製造方法において、前記工程(b)は以下の工程を含む:

(b1)前記ウエハステージ上に置かれた前記半導体ウエハの周辺部をシーリングにより押さえる工程;

(b2)前記ウエハステージの裏面側から不活性ガスを流入させる工程。

19.前記項11記載の半導体装置の製造方法において、前記第1のチャンバと前記第2のチャンバとの間の前記半導体ウエハの搬送は、真空搬送される。

20.前記項1、8または11記載の半導体装置の製造方法において、前記金属膜はタングステン膜であり、前記バリアメタル膜はチタン膜上に窒化チタン膜を積み重ねた積層膜、または窒化タングステン膜である。

21.前記項1、8または11記載の半導体装置の製造方法において、前記金属膜は銅膜であり、前記バリアメタル膜は窒化チタン膜、窒化タンタル膜、窒化タンタル膜上にタンタル膜を積み重ねた積層膜、または窒化タンタル膜上にルテニウム膜を積み重ねた積層膜である。

22.前記項1、8または11記載の半導体装置の製造方法において、前記金属膜はアルミニウム膜であり、前記バリアメタル膜はチタン膜上に窒化チタン膜を積み重ねた積層膜、または窒化タングステン膜である。

【符号の説明】

【0095】

1 半導体基板

4 素子分離領域

6 p型ウェル

8 n型ウェル

9 ゲート絶縁膜

10n ゲート電極

10p ゲート電極

11 ソース・ドレイン拡張領域

12 ソース・ドレイン拡張領域

13 酸化シリコン膜

15 サイドウォール

16 ソース・ドレイン拡散領域

17 ソース・ドレイン拡散領域

18 ニッケルシリサイド層

19a 第1絶縁膜

19b 第2絶縁膜

20 接続孔

21 チタン膜

22 窒化チタン膜

23 タングステン膜

24 ストッパ絶縁膜

25 絶縁膜

26 配線溝

27 バリアメタル膜

28 キャップ絶縁膜

29 層間絶縁膜

30 ストッパ絶縁膜

31 絶縁膜

32 接続孔

33 配線溝

34 バリアメタル膜

35 窒化シリコン膜

36 酸化シリコン膜

37 バンプ下地電極

38 バンプ電極

50 成膜装置

51a 第1搬送室

51b 第2搬送室

52 ゲートバルブ

53 ローダ

54 アンローダ

55,56,57 チャンバ

57a ウエハステージ

57b ウエハリフトピン

57c,57CH シャワーヘッド

57d リモートプラズマ発生装置

57e シーリング

57f シャドウリング

57g 排気室

58,59,60,61 チャンバ

62a,62b 搬送用ロボット

M1,M2,M3,M4,M5,M6 配線

SW 半導体ウエハ

【特許請求の範囲】

【請求項1】

絶縁膜に開口した接続孔の内部にバリアメタル膜を介して金属膜を埋め込む半導体装置の製造方法であって、前記絶縁膜に前記接続孔を形成した後、前記接続孔の内部に前記バリアメタル膜を堆積する前に以下の工程を含む半導体装置の製造方法:

(a)第1のチャンバに備わるウエハステージ上に半導体ウエハを置く工程;

(b)前記ウエハステージの上方に設置されたシャワーヘッドを介してプラズマ励起された還元ガスを供給し、前記接続孔の内部にドライクリーニング処理を施して、前記接続孔の内部の自然酸化膜を還元反応により除去する工程;

(c−1)前記(b)工程の後、前記半導体ウエハを前記ウエハステージから上昇させて、前記半導体ウエハの主面を前記シャワーヘッドに近接させる工程;

(c−2)前記(c−1)工程の後、前記シャワーヘッドの加熱温度を利用した第1の温度で前記半導体ウエハを熱処理して、前記還元ガスと前記自然酸化膜との前記還元反応により生成され、前記接続孔の内部に残留する化学量論的組成の生成物を除去する工程;

(d)前記(c−2)工程の後、前記半導体ウエハを前記第1のチャンバから第2のチャンバへ搬送する工程;

(e)前記(d)工程の後、前記第2のチャンバにおいて、前記第1の温度よりも高い第2の温度で前記半導体ウエハを熱処理して、前記還元ガスと前記自然酸化膜との前記還元反応により生成され、前記接続孔の内部に残留する非化学量論的組成の生成物を除去する工程、

前記還元ガスはNF3ガスとNH3ガス、またはNF3ガスとH2ガスであり、前記第1の温度は100から150℃であり、前記第2の温度は150から400℃である。

【請求項2】

請求項1記載の半導体装置の製造方法において、前記第2の温度は165から350℃である。

【請求項3】

請求項1記載の半導体装置の製造方法において、前記第2の温度は180から220℃である。

【請求項4】

請求項1記載の半導体装置の製造方法において、前記第2の温度は200℃である。

【請求項5】

請求項1記載の半導体装置の製造方法において、前記第1のチャンバと前記第2のチャンバとの間の前記半導体ウエハの搬送は、真空搬送される。

【請求項6】

請求項1記載の半導体装置の製造方法において、前記金属膜はタングステン膜であり、前記バリアメタル膜はチタン膜上に窒化チタン膜を積み重ねた積層膜、または窒化タングステン膜である。

【請求項7】

請求項1記載の半導体装置の製造方法において、前記金属膜は銅膜であり、前記バリアメタル膜は窒化チタン膜、窒化タンタル膜、窒化タンタル膜上にタンタル膜を積み重ねた積層膜、または窒化タンタル膜上にルテニウム膜を積み重ねた積層膜である。

【請求項8】

請求項1記載の半導体装置の製造方法において、前記金属膜はアルミニウム膜であり、前記バリアメタル膜はチタン膜上に窒化チタン膜を積み重ねた積層膜、または窒化タングステン膜である。

【請求項1】

絶縁膜に開口した接続孔の内部にバリアメタル膜を介して金属膜を埋め込む半導体装置の製造方法であって、前記絶縁膜に前記接続孔を形成した後、前記接続孔の内部に前記バリアメタル膜を堆積する前に以下の工程を含む半導体装置の製造方法:

(a)第1のチャンバに備わるウエハステージ上に半導体ウエハを置く工程;

(b)前記ウエハステージの上方に設置されたシャワーヘッドを介してプラズマ励起された還元ガスを供給し、前記接続孔の内部にドライクリーニング処理を施して、前記接続孔の内部の自然酸化膜を還元反応により除去する工程;

(c−1)前記(b)工程の後、前記半導体ウエハを前記ウエハステージから上昇させて、前記半導体ウエハの主面を前記シャワーヘッドに近接させる工程;

(c−2)前記(c−1)工程の後、前記シャワーヘッドの加熱温度を利用した第1の温度で前記半導体ウエハを熱処理して、前記還元ガスと前記自然酸化膜との前記還元反応により生成され、前記接続孔の内部に残留する化学量論的組成の生成物を除去する工程;

(d)前記(c−2)工程の後、前記半導体ウエハを前記第1のチャンバから第2のチャンバへ搬送する工程;

(e)前記(d)工程の後、前記第2のチャンバにおいて、前記第1の温度よりも高い第2の温度で前記半導体ウエハを熱処理して、前記還元ガスと前記自然酸化膜との前記還元反応により生成され、前記接続孔の内部に残留する非化学量論的組成の生成物を除去する工程、

前記還元ガスはNF3ガスとNH3ガス、またはNF3ガスとH2ガスであり、前記第1の温度は100から150℃であり、前記第2の温度は150から400℃である。

【請求項2】

請求項1記載の半導体装置の製造方法において、前記第2の温度は165から350℃である。

【請求項3】

請求項1記載の半導体装置の製造方法において、前記第2の温度は180から220℃である。

【請求項4】

請求項1記載の半導体装置の製造方法において、前記第2の温度は200℃である。

【請求項5】

請求項1記載の半導体装置の製造方法において、前記第1のチャンバと前記第2のチャンバとの間の前記半導体ウエハの搬送は、真空搬送される。

【請求項6】

請求項1記載の半導体装置の製造方法において、前記金属膜はタングステン膜であり、前記バリアメタル膜はチタン膜上に窒化チタン膜を積み重ねた積層膜、または窒化タングステン膜である。

【請求項7】

請求項1記載の半導体装置の製造方法において、前記金属膜は銅膜であり、前記バリアメタル膜は窒化チタン膜、窒化タンタル膜、窒化タンタル膜上にタンタル膜を積み重ねた積層膜、または窒化タンタル膜上にルテニウム膜を積み重ねた積層膜である。

【請求項8】

請求項1記載の半導体装置の製造方法において、前記金属膜はアルミニウム膜であり、前記バリアメタル膜はチタン膜上に窒化チタン膜を積み重ねた積層膜、または窒化タングステン膜である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−110418(P2013−110418A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2012−262017(P2012−262017)

【出願日】平成24年11月30日(2012.11.30)

【分割の表示】特願2006−138949(P2006−138949)の分割

【原出願日】平成18年5月18日(2006.5.18)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成24年11月30日(2012.11.30)

【分割の表示】特願2006−138949(P2006−138949)の分割

【原出願日】平成18年5月18日(2006.5.18)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]